## **Ryerson University** Digital Commons @ Ryerson

Theses and dissertations

1-1-2005

# An efficient architecture for discrete wavelet transform and best-basis algorithm for images

Aroutchelvame Mayilavelane Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

### Recommended Citation

Mayilavelane, Aroutchelvame, "An efficient architecture for discrete wavelet transform and best-basis algorithm for images" (2005). Theses and dissertations. Paper 363.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

## AN EFFICIENT ARCHITECTURE FOR DISCRETE WAVELET TRANSFORM AND BEST-BASIS ALGORITHM FOR IMAGES

by

Aroutchelvame Mayilavelane

M.Tech, Indian Institute of Technology (IIT), Chennai, India

A thesis

presented to Ryerson University

in partial fulfillment of the

requirement for the degree of

Master of Applied Science

in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2005

© Aroutchelvame Mayilavelane 2005

UMI Number: EC53738

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC53738

Copyright 2009 by ProQuest LLC

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346 I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Aroutchelvame Mayilavelane

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Aroutchelvame Mayilavelane

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

| Name  | Signature | Address | Date         |

|-------|-----------|---------|--------------|

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

| 11. / |           |         | <del> </del> |

|       |           |         |              |

|       |           |         |              |

|       |           |         | <del> </del> |

|       |           |         | -            |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

|       |           |         |              |

| İ     | 1         |         |              |

## An Efficient Architecture for Discrete Wavelet Transform and Best-Basis Algorithm for Images

© Aroutchelvame Mayilavelane 2005

Master of Applied Science

Department of Electrical & Computer Engineering

Ryerson University

### **Abstract**

The hardware acceleration of the wavelet transform for real-time systems has become an essential research field. In the first part of the thesis, an efficient architecture that performs both forward and inverse lifting-based discrete wavelet transform is proposed. The proposed architecture reduces the hardware requirement by exploiting the redundancy in the arithmetic operation involved in DWT computation. The proposed architecture does not require any extra memory to store intermediate results. The proposed architecture consists of predict module, update module, address generation module, control unit and a set of registers to establish data communication between predict and update modules. The symmetrical extension of images at the boundary to reduce distorted images has been incorporated in our proposed architecture as mentioned in JPEG2000. The DWT architecture is proposed for both (5,3) wavelet and (9,7) wavelet. Best-basis algorithm that is designed for signal compression and de-noising uses WPT to select the best-basis node for a given additive cost function. In the second part of the thesis, we propose the architecture for best-basis algorithm for images (2D signals) that uses the proposed wavelet architecture to perform WPT decomposition. A new algorithm to implement the natural logarithm function using Maclaurin series is proposed to implement the cost function used for best-basis algorithm. These architectures have been described in VHDL at the RTL level and simulated successfully using ModelSim simulation environment. These architecures are implemented in Virtex II Pro FPGA series of Xilinx.

### Acknowledgements

First of all, I would like to thank my supervisor Dr. Kaamran Raahemifar, for everything I have learned from working with him during two years of my graduate study, for his many advices, his enormous patience and for being more a friend than a boss.

I would like to thank all people in the Department of Electrical & Computer Engineering and the System-on-Chip Group in particular, for their help and cordiality. Thanks to the department for providing financial support for my study.

I would like to thank Bahman Zafarifar and Alex Pineiro for discussions on the wavelet transform and natural logarithm implementation. Also, I would like to thank all of my friends and my roommates who helped making this research a nice experience.

I thank Xilinx for providing the FPGA board and necessary softwares for the implementation of my research work.

My parents Mayilavelan & Maheswari, my brothers and cousins and my uncles and aunts have supported me in one way or another. My parents worked hard to ensure that I receive a proper education. My brothers are always ready to extend their helping hands. They are all wonderful and I take this opportunity to thank them for all their support.

Dedicated to my parents for their support and love...

## **Table of Contents**

| Abstra | act     |                                                | <u>iv</u>  |

|--------|---------|------------------------------------------------|------------|

| Ackno  | owledg  | ements                                         | <u>v</u>   |

| Table  | of Cor  | itents                                         | <u>vii</u> |

| List o | f Table | s                                              | <u>ix</u>  |

| List o | f Figur | es                                             | <u>x</u>   |

| Gloss  | ary     |                                                | <u>xii</u> |

| 1 I    | NTRO    | DUCTION                                        |            |

| 1.1    | Ov      | erview                                         | 1          |

| 1.2    | Re      | search goal and the contribution of the Author | 5          |

| 1.3    | Org     | ganization of the thesis                       | 6          |

| 2 E    | BACKO   | GROUND                                         | •••••      |

| 2.1    | Dis     | screte Wavelet Transform (DWT)                 | 8          |

| 2      | .1.1    | DWT                                            | 8          |

| 2      | .1.2    | Lifting Scheme                                 | 10         |

| 2      | .1.3    | Boundary Treatment                             | 13         |

| 2      | .1.4    | DWT Architectures                              | 14         |

| 2.2    | Bes     | st-Basis Algroithm                             | 16         |

| 2.3    | Arc     | chitectures for Elementary Functions           | 19         |

| 3 A    | RCHI    | TECTURE FOR LIFTING-BASED DISCRETE WAVELET     |            |

| TRAN   | ISFOR   | M                                              | •••••      |

| 3.1    | Intr    | oduction                                       | 22         |

| 3.2    | Ari     | thmetic Operations in Lifting-based DWT        | 23         |

| 3.3    | The     | Proposed Architecture                          | 27         |

| 3.     | .3.1    | Predict Module                                 | 27         |

| 3.     | .3.2    | Update Module                                  | 29         |

| 3.     | .3.3    | Lifting-Based (5,3) Wavelet Architecture       | 30         |

|   | 3.3. | .4  | Lifting-Based (9,7) Wavelet Architecture        | 34    |

|---|------|-----|-------------------------------------------------|-------|

| 4 | AR   | СНІ | TECTURE FOR BEST-BASIS ALGORITHM FOR 2D SIGNALS | ••••• |

|   | 4.1  | Int | roduction                                       | 40    |

|   | 4.2  | Al  | gorithm and Architecture for Logarithm Function | 41    |

|   | 4.2. | .1  | Algorithm                                       | 41    |

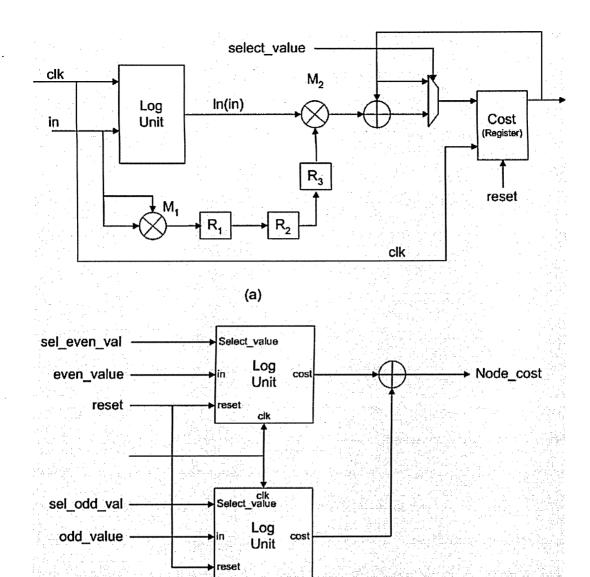

|   | 4.2. | .2  | Architecture                                    | 46    |

|   | 4.3  | Ar  | chitecture for Best-Basis Algorithm             | 49    |

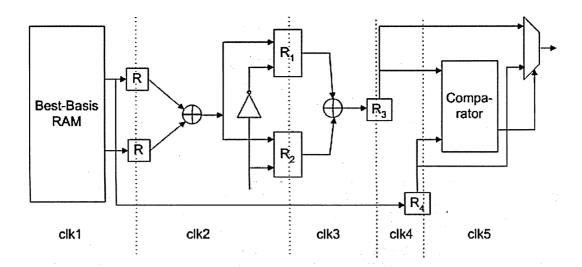

|   | 4.3. | .1  | Best-Tree Selector Architecture                 | 50    |

|   | 4.3. | 2   | Address Generator for Best-Tree Architecture    | 53    |

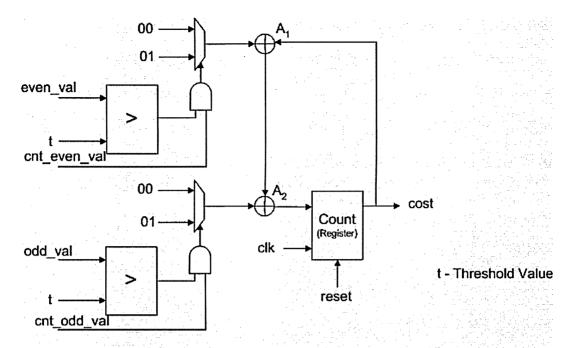

|   | 4.3. | .3  | Cost-Function Architecture                      | 54    |

| 5 | RES  | SUL | TS AND DISCUSSION                               | ••••• |

|   | 5.1  | DV  | VT                                              | 59    |

|   | 5.2  | Be  | st-Basis Algroithm for Images                   | 73    |

|   | 5.3  | FP  | GA Implementation                               | 83    |

| 6 | CO   | NCL | USION AND FUTURE WORK                           | ••••• |

|   | 6.1  | Co  | nclusion                                        | 86    |

|   | 6.2  | Fut | ture Research                                   | 89    |

|   | REI  | FER | ENCES                                           | 90    |

|   | API  | PEN | DIX A                                           | 97    |

## **List of Tables**

| Table 4.1 Signals generated for each counter value for Best-Tree Selection 52                    |

|--------------------------------------------------------------------------------------------------|

| Table 5.1 Comparison of the proposed DWT architecture with existing ones 58                      |

| Table 5.2 Average Error per pixel represented in various terminologies for the images            |

| recovered after one level of (9,7) wavelet decomposition with zero bit precision of              |

| input data63                                                                                     |

| Table 5.3 Average Error per pixel represented in various terminologies for the images            |

| recovered after two level of (9,7) wavelet decomposition with zero bit precision of              |

| input data64                                                                                     |

| Table 5.4 Average Error per pixel represented in various terminologies for the images            |

| recovered after three level of (9,7) wavelet decomposition with zero bit precision of            |

| input data65                                                                                     |

| Table 5.5 Average Error per pixel represented in various terminologies for the images            |

| recovered after one level of (9,7) wavelet decomposition with eight bits precision of            |

| input data66                                                                                     |

| Table 5.6 Average Error per pixel represented in various terminologies for the images            |

| Table 5.6 Average Error per pixel represented in various terminologies for the images            |

| recovered after two level of (9,7) wavelet decomposition with eight bits precision of            |

|                                                                                                  |

| recovered after two level of (9,7) wavelet decomposition with eight bits precision of            |

| recovered after two level of (9,7) wavelet decomposition with eight bits precision of input data |

# **List of Figures**

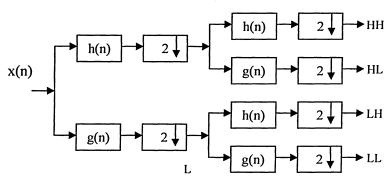

| Figure 2.1 DWT for 2D Signal                                                        | 10  |

|-------------------------------------------------------------------------------------|-----|

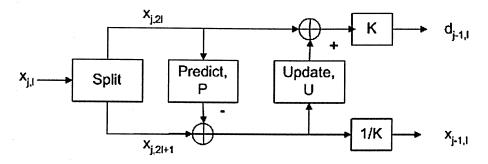

| Figure 2.2 Lifting Scheme                                                           | 11  |

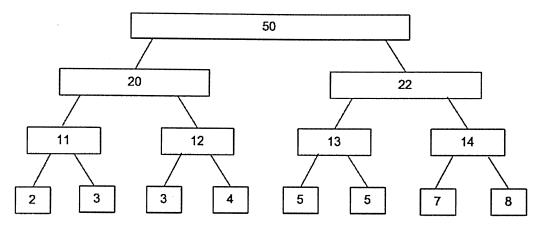

| Figure 2.3 Best-Basis Selection process                                             | 19  |

| Figure 3.1 Lifting Scheme for (5,3) wavelet                                         | 24  |

| Figure 3.2 Lifting Scheme for (9,7) wavelet without scaling                         | 26  |

| Figure 3.3 Predict Module                                                           | 29  |

| Figure 3.4 Update Module                                                            | 29  |

| Figure 3.5 Architecture for (5,3) Wavelet                                           | 32  |

| Figure 3.6 Flowchart of the 2D Forward and Inverse Transform                        | 35  |

| Figure 3.7 Architecture for (9,7) Wavelet                                           | 36  |

| Figure 3.8 Functional Output of Lifting-based (5,3) wavelet                         | 37  |

| Figure 3.9 Functional Output of Lifting-based (9,7) wavelet                         | 37  |

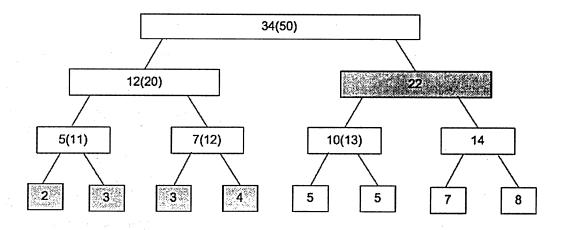

| Figure 4.1 Flowchart of Natural Logairthm Architecture using Maclaurin Series to fi | ind |

| LN(X)                                                                               | 44  |

| Figure 4.2 Natural Logairthm Architecture with 8 bits of accuracy                   | 48  |

| Figure 4.3 Timing Diagram of Natural Logarithm Architecture with 11 bits of precis  | ion |

|                                                                                     | 49  |

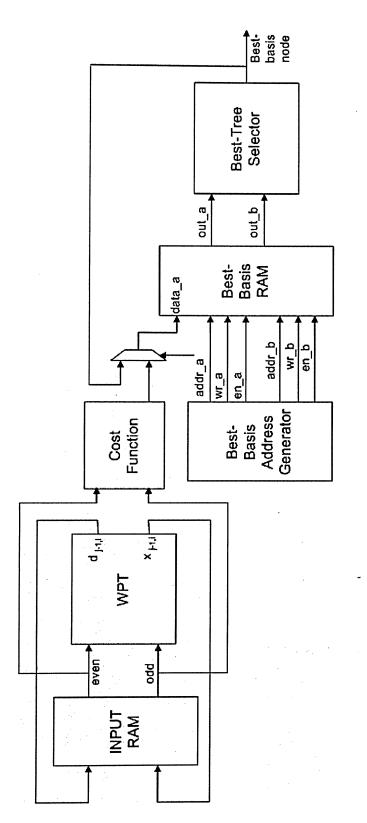

| Figure 4.4 Best-Basis Architecture                                                  | 51  |

| Figure 4.5 Best-Tree Selector                                                       | 52  |

| Figure 4.6 Best-Basis Address Generator for tree selection                          | 52  |

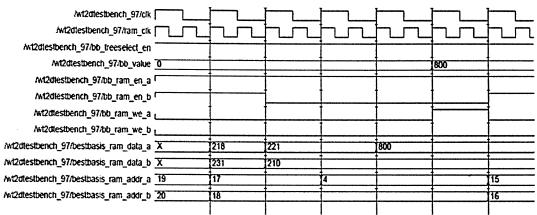

| Figure 4.7 Waveform of Best-Tree Selector                                           | 53  |

| Figure 4.8 Threshold Function Architecture                                          | 56  |

| Figure 4.9 Shannon Function Architecture                                            | 58  |

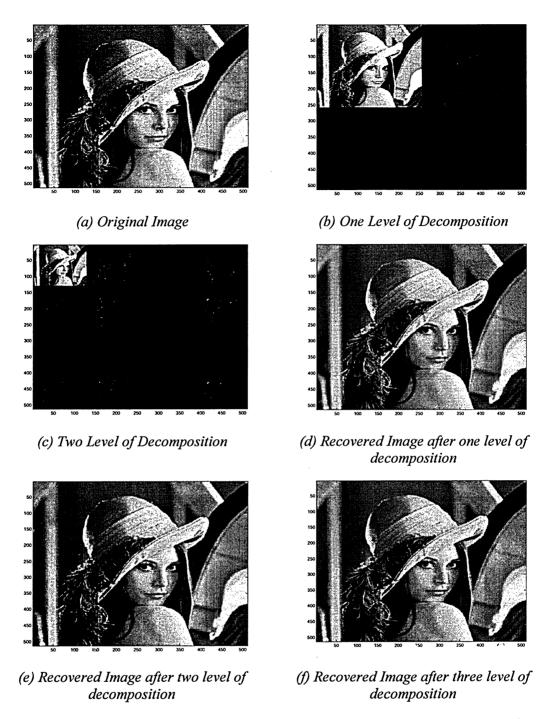

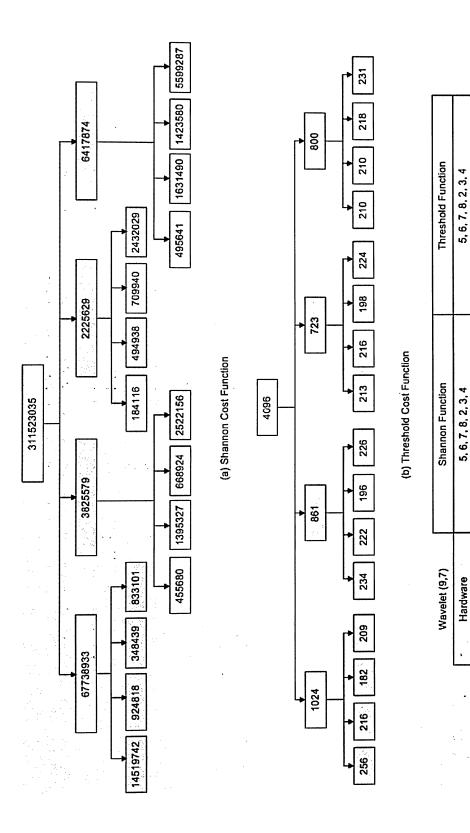

| Figure 5.1 Lena Images of size 512 x 512 after 2D WPT Decompsition using (5,3)      |     |

| Wavelet                                                                             | 70  |

| Figure 5.2 Lena Images of size 512 x 512 after 2D WPT Decompsition using (9,7)      |     |

| Wavelet                                                                             | 72  |

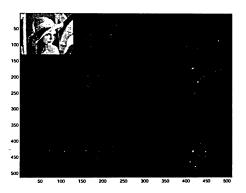

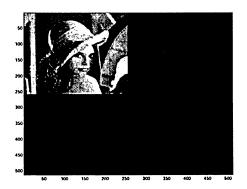

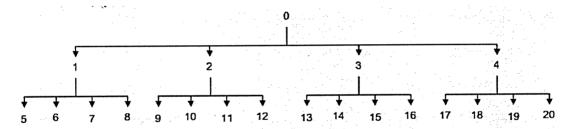

| Figure 5.3 Numbering of Wavelet Packet Node                                          |

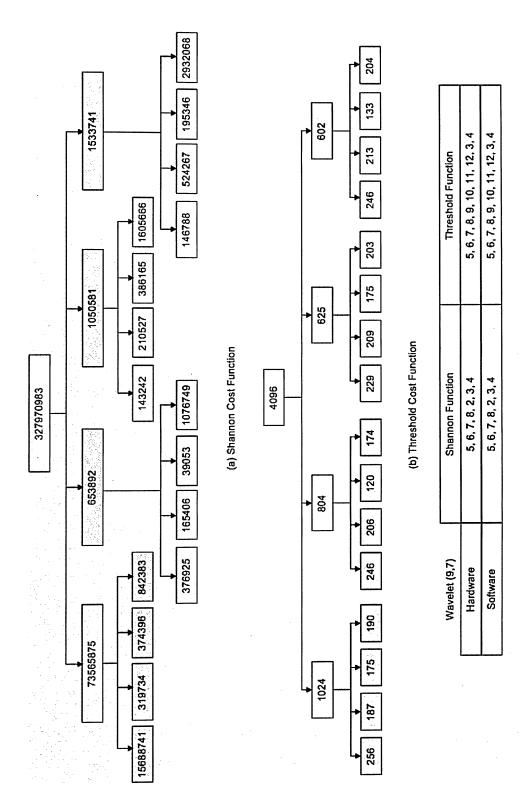

|--------------------------------------------------------------------------------------|

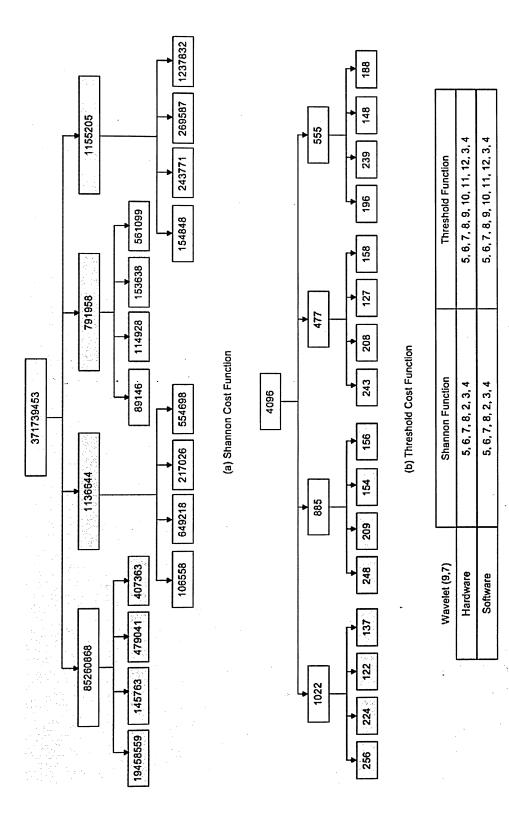

| Figure 5.4 Best-Basis Node obtained from Shannon & Threshold Cost Function for Lena  |

| Image of size 64 x 64 from two-level of (9,7) wavelet decomposition                  |

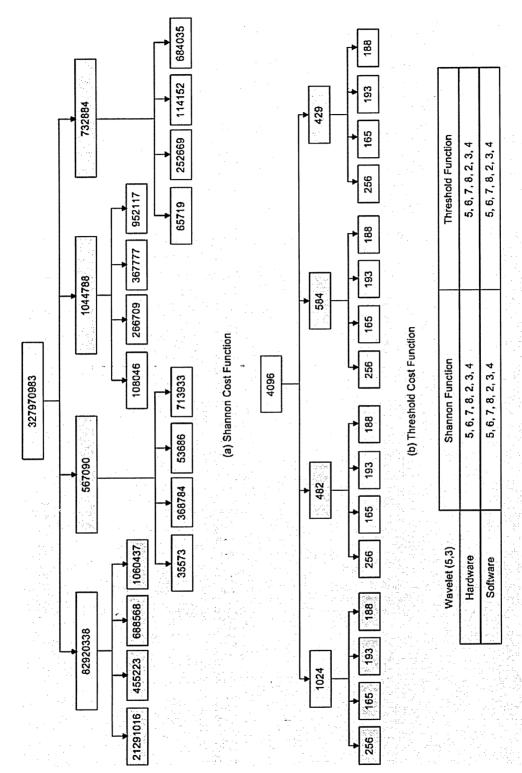

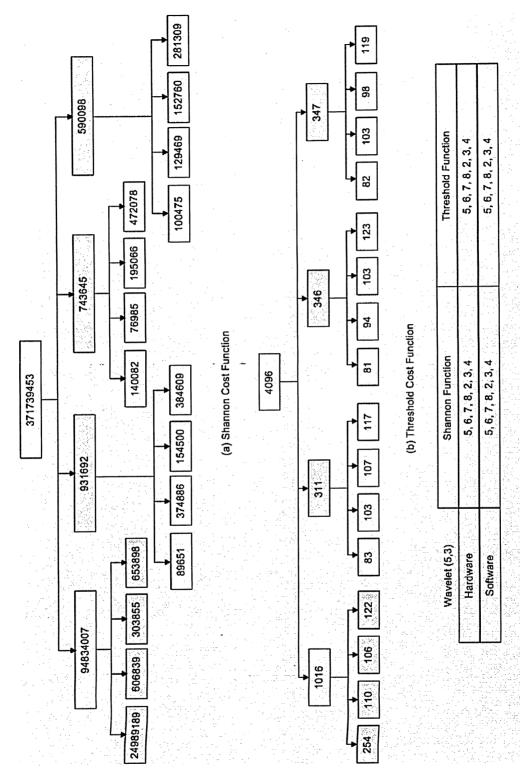

| Figure 5.5 Best-Basis Node obtained from Shannon & Threshold Cost Function for Lena  |

| Image of size 64 x 64 from two-level of (5,3) wavelet decomposition                  |

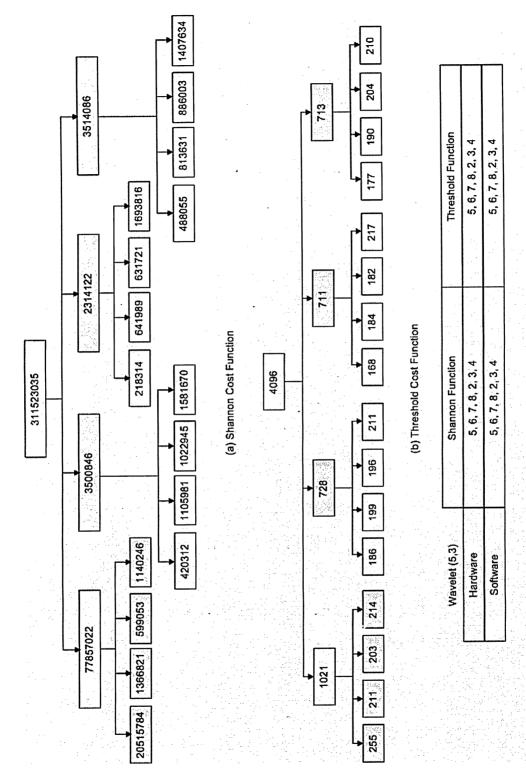

| Figure 5.6 Best-Basis Node obtained from Shannon & Threshold Cost Function for Bird  |

| Image of size 64 x 64 from two-level of (9,7) wavelet decomposition                  |

| Figure 5.7 Best-Basis Node obtained from Shannon & Threshold Cost Function for Bird  |

| Image of size 64 x 64 from two-level of (5,3) wavelet decomposition                  |

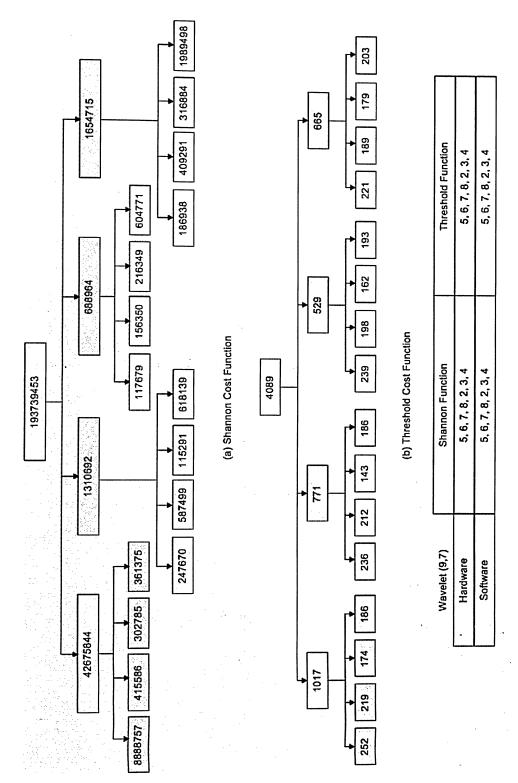

| Figure 5.8 Best-Basis Node obtained from Shannon & Threshold Cost Function for Zelda |

| Image of size 64 x 64 from two-level of (9,7) wavelet decomposition                  |

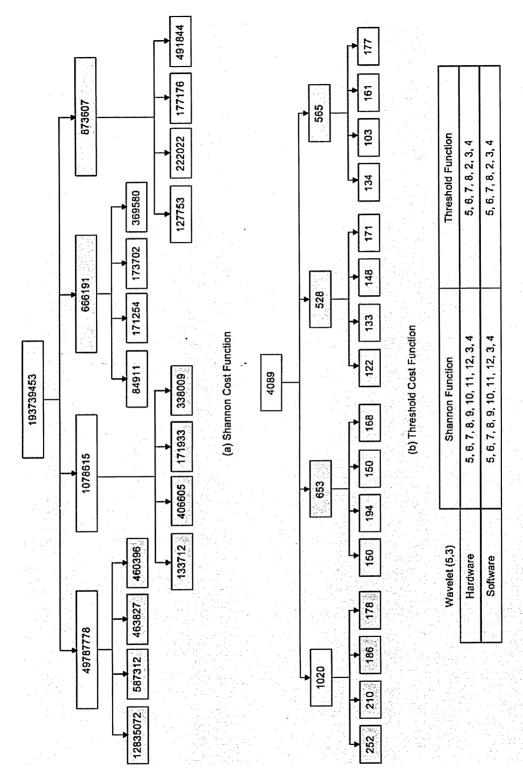

| Figure 5.9 Best-Basis Node obtained from Shannon & Threshold Cost Function for Lena  |

| Image of size 64 x 64 from two-level of (5,3) wavelet decomposition 80               |

| Figure 5.10 Best-Basis Node obtained from Shannon & Threshold Cost Function for      |

| Barbara Image of size 64 x 64 from two-level of (9,7) wavelet decomposition 81       |

| Figure 5.11 Best-Basis Node obtained from Shannon & Threshold Cost Function for      |

| Barabara Image of size 64 x 64 from two-level of (5,3) wavelet decomposition 82      |

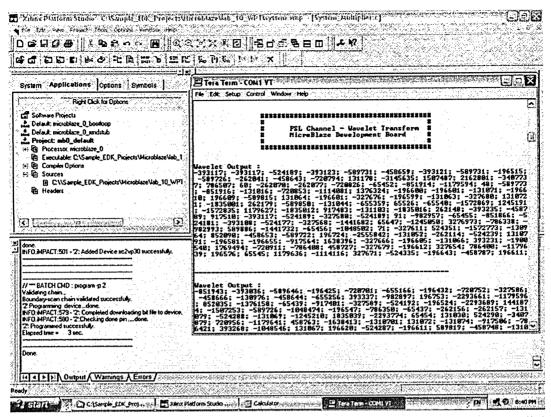

| Figure 5.12 The output read from Xilinx Virtex II Pro FPGA through serial port       |

| displayed on Tera Term Pro HTTP Terminal84                                           |

### Glossary

1D one-dimensional 2D two-dimensional 3D three-dimensional AAE Average Absolute Error

BRAM Block RAM CL Current Level

CORDIC Coordinate Rotation Digital Computer

DCT Discrete Cosine Transform

DSP Digital Signal Processing/Processor

DWT Discrete Wavelet Transform

DWPT Discrete Wavelet Packet Transform

FIFO First In First Out

FPGA Field Programmable Gate Array

FSL Fast Simplex Link

IOB Input Output Block

In Natual Logarithm

LCD Liquid Crystal Display

LDB Local Discriminant Basis

LN Natural Logarithm

LUT Look-Up Table

MSE Mean Square error

MULT 18X18 18-bit \* 18-bit Multiplier

PSNR Peak Signal-to-Noise Ratio

RAM Read Access memory

RTL Register Transfer Level SNR Signal-to-Noise Ratio

VHDL VHSIC Hardware Description Langauge VHSIC Very High Speed Integrated Circuits

WPT Wavelet Packet Transform

## **CHAPTER 1**

## INTRODUCTION

### 1.1 Overview

Interest in wavelet transformations has greatly increased, as their applications have become numerous such as image processing and image compression. Digital images have become more common in the multimedia world. The digital images replace their old analog ancestors. One such application is found in digital cameras. In digital cameras, one expects to inspect the result immediately after taking the picture. To support this behavior, the picture has to be compressed, stored on a flash memory card, decompressed and shown at LCD display in nearly real-time. Features like high-speed previews have to be provided. Furthermore, one could expect to store more number of images on memory stick. Therefore, efficient hardware image compression algorithms with excellent visual properties are necessary.

Practical image data sequences normally contain a substantial amount of redundancy. Redundancy in signals can appear in the form of smoothness of the signal or in other words correlation between the neighboring signal values. The image sequence that embeds redundancy can be presented more compactly if the redundancy is removed

by means of a suitable transform. A popular transform that has been used for years for compression of digital still images and image sequences is the Discrete Cosine Transform (DCT). The DCT transform uses cosine functions of different frequencies for analysis and for decorrelation of data. The DCT provides signal frequency content into fixed, equal bandwidth partitions. By providing only the frequency content of the signal, the DCT is unable to represent non-stationary signal properties in the transform domain. Often, images are non-stationary. To overcome this problem, the JPEG algorithm [1] uses a block based transform in which DCT is applied to image block separately. Because each block is transformed on an individual basis, there are often inefficiencies between blocks. The Discrete Wavelet Transform (DWT) rectifies this problem by providing a representation of a given image in both time and scale domains. Because of this, the DWT has been shown to significantly outperform the DCT in image compression applications, leading to their inclusion in the JPEG 2000 standard [2-3]. The DWT is a reversible transform and can be either a "lossy" or "lossless" process depending on the selection of wavelet. Besides image compression, DWT are also aptly suited for image editing and progressive transmission applications since they provide a multiresolution decomposition of a signal.

The DCT based JPEG algorithm yields good results of compression ratio till 10:1. As the compression ratio increases, the quantization of the coefficients causes blocking effects in the decompressed image. When compression ratio reaches 24:1, it only allows the DC coefficients, which are the average of the pixels of an 8x8 block, to be encoded. Consequently, the input image is approximated by a series of 8x8 blocks of local averages, which is visually very annoying. For DWT followed by Embedded Zero Tree

encoding algorithm, in contrast, compressions of the ratios of 100:1 have been achieved, while still yielding a reconstructed image with an acceptable quality.

The lifting scheme [4-7] has been introduced for efficient computation of the DWT. Its main advantage with respect to the classical filter bank structure lies in its better computational efficiency [24] and in the fact that it enables a new method for filter design. Using the lifting scheme, it is easy to use integer arithmetic without encountering problems due to finite precision or rounding. Applying the inverse transform in the lifting scheme is very easy and, as long as the transform coefficients are not quantized, would always result in a perfect reconstruction of the original picture.

Some of the applications of DWT are digital video compression, telecommunications, signal and image processing and processing of non-stationary signals in areas such as bio-medicine. In those applications, the computational burden on the transform part is very high. To meet this additional burden in real-time applications, the hardware design and implementation of these transforms has itself taken on much importance. In this case, the high-computational parts of the program are designed in hardware and loaded into reconfigurable hardware unit such as FPGA.

The performance of these applications can be increased if the transform provides good spectral and temporal resolutions in arbitrary regions of the time-frequency plane. This flexibility is provided by Wavelet Packet Transform (WPT). It is a generalized representation of DWT which allows the further decomposition of the high-pass output i.e. detailed information.

In WPT analysis, the signal of size  $N = 2^n$  can be expanded in  $2^n$  different ways and this number may be large. So, it is important to use an efficient method to find its

best-tree representation, i.e. the best-tree that minimizes certain additive cost function. Coifman and Wickerhauser proposed a classical entropy-based algorithm to find the best-tree and their algorithm is called best-basis algorithm [8]. Best basis algorithm is primarily designed to reduce the storage space needed for a signal and also it can be used for de-noising. This algorithm looks for time-frequency representation of the signal in wavelet packet or trigonometric basis. The entropy-based algorithm involves the computation of logarithm function. The hardware implementation of logarithm function and other elementary function is the performance bottleneck of the best-basis algorithm in real-time systems. The higher the number of bits of precision is required by the logarithm function, the more is the number of clock cycles required by the hardware.

Software routines applying techniques such as polynomial and rational expressions have been used to evaluate the elementary functions such as logarithm function [9]. Even though these techniques compute logarithm function with accurate results, they are often too slow compared to the real-time applications. The hardware implementation of the elementary functions have been developed as an alternative to the software routines, providing high speed solutions implemented in dedicated hardware. The CORDIC based algorithms [10-11] are considered to be one of the best hardware based methods due to their low area requirements. The main drawback in this algorithm is their approximate linear convergence of one radix-r digit per step, resulting in long execution times for small radices and high precision. The latency can be reduced by increasing the radix. However this method leads to an increase in the cost of implementation with increase in radix.

This thesis has been broadly classified into two parts. In the first part of the thesis, we propose an efficient architecture for DWT (WPT), using (5,3) and (9,7) wavelet mentioned in JPEG2000, that implements lifting scheme. The proposed DWT (WPT) architecture requires less hardware area and it does not require extra storage elements such as memory and FIFO to store the intermediate results. In the second part of the thesis, we propose architecture for best-basis algorithm for 2D signal or image. This part of the thesis also includes a proposed algorithm and architecture for implementing natural logarithm using Maclaurin series. The hardware design implements different techniques such as pipelining, parallel operation modules, data reusability and special features of FPGA to maximize its performance.

### 1.2 Research goal and the contribution of the Author

The computational complexity of DWT and best-basis algorithm is an obstacle for using those in practical applications. Therefore, the hardware implementation of the algorithm is desirable. The main objective of this thesis is to propose an efficient architecture for DWT and best-basis algorithm. The contribution of the author is described in the following:

- Proposing an efficient architecture for DWT or WPT using (5,3) and (9,7)

wavelets that requires less hardware area and does not require extra storage

devices to store the intermediate results,

- Proposing a novel algorithm and architecture for natural logarithm function using Maclaurin series,

- Proposing an efficient architecture for best-basis algorithm for 2D signal or image which includes detailed architecture description for calculation of cost-function, address generation for best-basis RAM and calculation of best-tree,

- Implementing the design in VHDL,

- Performing simulations in ModelSim to verify functional correctness of the design,

- Implementing the design in Xilinx Virtex II Pro FPGA using Xilinx

Implementation tool,

- Comparing the performance of the DWT architecture with some existing popular architectures,

- Performing simulations with large picture size for different precision of filter coefficients and analyzing the error variation for both (5,3) and (9,7) wavelets.

- Performing simulations for best-basis algorithm for different images or 2D signals to verify the architecture.

### 1.3 Organization of the thesis

The main objective of the thesis is to propose an efficient architecture for DWT or WPT, natural logarithm function and the best-basis algorithm. The thesis is organized as follows:

Chapter 2 starts with the theoretical background, briefly introducing the DWT and the best-basis algorithm. The lifting scheme based DWT computation results in less number of arithmetic operations compared to the filter-based DWT computation. The lifting-based DWT and the best-basis algorithm with detailed example are described in

this chapter. Detailed survey of some existing lifting-based DWT architectures and hardware implementation of elementary functions such as natural logarithm is presented in this chapter.

Chapter 3 proposes an efficient architecture for DWT or WPT that requires less hardware area and does not require extra storage devices to store intermediate results. The DWT architecture for both (5,3) and (9,7) wavelets is described in detail in this chapter.

Chapter 4 proposes architecture for best-basis algorithm for 2D signal or image. This chapter also discusses in detail the architecture for calculating cost-function, generating addresses for best-basis RAM and determining best-tree. The architecture for two cost functions, Threshold function and Shannon function, is also proposed. Also, an algorithm and architecture to implement natural logarithm function using Maclaurin series is proposed in this chapter.

Chapter 5 presents results and discussion for the DWT or WPT architecture and the best-basis algorithm architecture.

Chapter 6 summarizes the important contributions and results in the proposed architectures and lists out the future work related to this research.

## **CHAPTER 2**

## **BACKGROUND**

This chapter starts with a brief introduction of discrete wavelet transform and lifting scheme. It also provides survey of some of the existing DWT architectures. In the next section, some of the existing hardware implementation of elementary functions such as logarithm function is discussed. In the last section, the best-basis algorithm is briefly discussed with an example.

### 2.1 Discrete Wavelet Transform (DWT)

#### 2.1.1 Introduction

The idea of the DWT is mainly based on the sub-band coding scheme. In the discrete time function, the filters of different cutoff frequencies are used to analyze the signal at different scales. The signal is passed through a series of high pass filters to analyze the high frequencies, and it is passed through a series of low pass filters to analyze the low frequencies. The resolution of the signal, which is a measure of the amount of detail information in the signal, is changed by the filtering operations, and the

scale is changed by upsampling and downsampling (subsampling) operations. Subsampling a signal corresponds to reducing the sampling rate, or removing some of the samples of the signal. Upsampling a signal corresponds to increasing the sampling rate of a signal by adding new samples to the signal. In discrete signals, frequency is expressed in terms of radians. Accordingly, the sampling frequency of the signal is equal to  $2\pi$  radians in terms of radial frequency [12-15].

The DWT analyzes the signal at different frequency bands with different resolutions by decomposing the signal into a coarse approximation and detail information. The decomposition of the signal into different frequency bands is simply obtained by successive highpass and lowpass filtering of the time domain signal. The original signal x(n) is first passed through a halfband highpass filter h(n) and a lowpass h(n) and h(n

The DWT coefficient can be obtained for 2D signals such as image as explained below. The DWT decomposes the image/signal in the space-resolution domain. The one stage of DWT computation produces four sub-images representing an approximated image (LL) and the details along directions (HH, HL and LH) as shown in Fig.2.1. The operations involved are low-pass filtering (g(n)), high-pass filtering (h(n)) and down-sampling by 2 to keep only necessary information [14]. In one-level decomposition, the above operation is performed on the rows of the input, x(n), to generate the high-pass (H) and low-pass (L) outputs. The same operation is performed on the H and L values to

generate "HH and HL" and "LH and LL" output respectively. The LL outputs are fed to the next level of decomposition.

Fig.2.1: DWT for 2D Signals

### 2.1.2 Lifting Scheme

Wavelets discussed in the previous section are referred to as first generation wavelets. Second generation wavelets are much more flexible and used to define wavelet bases for bound intervals. The main difference between first and second generation wavelets is that it does not involve convolution. Lifting scheme can be used to construct second generation wavelet.

The basic idea of the lifting scheme is very simple – try to use the correlation in the data to remove redundancy. The 1D DWT decomposition using lifting scheme consists of three stages: split, predict, update and scaling [4-7] as shown in Fig.2.2. The 2D DWT decomposition can be easily achieved by applying the lifting scheme both rowwise and column-wise.

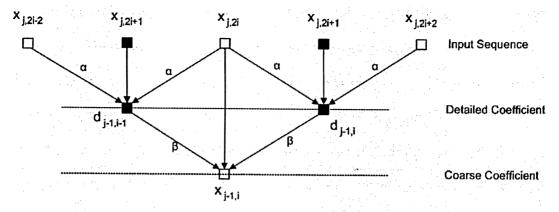

Fig2.2: Lifting Scheme

In the first stage (split), the input data is divided into two disjoint sets of samples. There is no restriction on splitting the data but the only thing needed is some procedure to join the two samples to obtain the original data [4-7]. One of the possibilities of the split of the input  $x_{j,l}$  is grouping the even indexed samples  $x_{j,2l+1}$  in different sets.

In the second stage (predict), one set of samples can be used to predict the other set of samples based on the correlation present in the input signal [4-7]. The prediction operator 'P' can be constructed based on the correlation structure of the input data. Practically, it might not be possible to accurately predict the one set of sample based on the other set of samples. Thus, the set of samples to be predicted or detailed co-efficient can be replaced with the difference between itself and the predictor output. If the samples ' $x_{2l}$ ', ' $x_{2l+1}$ ' and ' $x_{2l+2}$ ' considered in the split stage are highly correlated, one can easily device the predictor function using the even samples as variables to predict the odd samples. To predict the odd sample ' $x_{j,2l+1}$ ', the predictor function can be the average of the neighboring sample on the left ' $x_{j,2l}$ ' and the other sample on the right ' $x_{j,2l+2}$ .' The detail co-efficient can be given by  $d_{j-1,1} = x_{j,2l+1} - \frac{1}{2}(x_{j,2l} + x_{j,2l+2})$ .

The update stage utilizes the key properties of the coarser signals i.e. they have the same average value of the signal [4-7]. Thus the update stage implements this property by finding the update function 'U' using the detailed coefficients with the sample used for predictor function. In our case, this can be achieved using the equation  $x_{j-1,1} = x_{j,21} + \frac{1}{4}(d_{j-1,1-1} + d_{j-1,1})$ .

In the scaling stage, the even samples are multiplied by 1/K and odd samples by K in the case of forward transform. The inverse DWT is obtained by traversing in the reverse direction, changing the factor K to 1/K and factor 1/K to K.

All these values can be computed-in-place i.e. the even index locations can be overwritten with averages (coarse coefficient) and the odd ones with the detailed coefficient.

One can immediately build inverse scheme for it. Again the inverse lifting scheme has three stages: undo update, undo predict and merge.

Given  $d_{j-1,l}$  and  $x_{j-1,l}$ , one can recover the even samples by simply subtracting the update information as  $x_{j,2l} = x_{j-1,l} - \frac{1}{4}(d_{j-1,l-1} + d_{j-1,l})$  – undo update.

Given  $x_{j,2l}$  and  $d_{j-1,l}$ , one can recover the odd samples by adding the predict function as shown  $x_{j,2l+1} = d_{j-1,l} + \frac{1}{2}(x_{j,2l} + x_{j,2l+2})$  – undo predict.

Given both odd and even samples, one has to simply zipper them together to recover the original signal - Merge.

The main advantages [4-7] of the lifting scheme are:

Lifting scheme is fast and easy to implement in hardware because it replaces the Fourier transform.

- Lifting can be done in-place, therefore no auxiliary memory needed. At every stage, the calculated value replaces the old one.

- The inverse transform can be immediately found by undoing the operations of the forward transform. It can be realized by reversing the order of the arithmetic operation.

### 2.1.3 Boundary Treatment

Real-world signals do not extend infinitely in time or space, but are limited to a finite interval. So when the signal comes close enough to the edge, the filters need some sample values that are not defined. If zero padding is employed to avoid the boundary discontinuity, the transform results in large coefficients. This will induce artifacts in the image and severe encoding inefficiency. As a solution to this problem, classical signal processing extends the data for the computations near the boundary by either periodic extension or boundary extension.

In periodic extension, the finite signal is extended periodically by putting copies of itself in front of and behind the original signal. After the wavelet transform, the coefficients that lie outside of the interval of defined signal is simply discarded. These discarded coefficients can be recovered easily because they are the same as the retained coefficients. However, unless the first and the last samples have the same value, we introduce unwanted discontinuities at the boundaries of the original signal. These discontinuities will locally enlarge the wavelet coefficients and make compression of the signal more difficult.

An easy solution for handling the finite length signals is to extend them such that they become symmetric and periodic [16]. Symmetric extension consists in extending the signal with the signal samples obtained by a reflection of the signal centered on the first sample for extension to the left, and in extending the signal with the signal samples obtained by a reflection of the signal centered on the last sample for extension to the right.

#### 2.1.4 DWT Architectures

Several architectures have been proposed for hardware implementation of convolution-based DWT [17-21] because the DWT computation is basically the filter convolution as explained in Section 2.1.1. After introduction of second generation wavelets using lifting scheme, it has been used widely in DWT architecture because it requires fewer arithmetic computations and provides faster and efficient filtering of the DWT than that of the convolution-based DWT architecture. Thus, using lifting-based DWT architecture outperforms convolution-based DWT architectures. Also, the line-based method of computing DWT has been proposed to reduce the internal memory requirement from a frame size to a few line buffers with proper memory management [22-23]. This section discusses some of the efficient architectures for 2D DWT using the lifting scheme.

The architecture described in [24] calculates forward and inverse 2D DWT in row-column fashion on a block of data of size NxN. The architecture reads block of data, performs the transform and outputs LH, HL and HH data at each level of decomposition. The LL data is used for the next level of decomposition. The architecture consists of row

module with two row processors and register file, column module with two column processors and register files and two memory modules (one for row processing and the other for column processing). This architecture can be configured to perform 2D DWT for several DWT filterbanks. Each row and column processor comprises of a different configuration of adders, multipliers and shifters in the data path for several DWT filterbanks which was explained in detail in [24]. This architecture needs more intermediate or internal memory to perform the computation. Row processing memory module uses two banks with one read/write access for each bank whereas column processing memory module consists of four banks with one read/write operation for three banks and dual read operation for the last one.

The architecture in [25] describes hardware accelerator for the lifting scheme based DWT. For 2D signals, this architecture performs DWT in row-wise and then in column-wise. This architecture achieves the acceleration using the techniques such as pipelining, data-reusability and parallel operations. This architecture consists of predict module, update module and FIFOs to store intermediate results. The FIFOs are used to store some of the input signals and the output of the predict module and then forward those values to the update module. The filter coefficients for both predict and update modules are supplied from the memory. In order to meet the boundary conditions, different filter coefficients are supplied for the input signals at the boundary compared to the coefficients supplied for non-boundary input signals. Since the architecture uses different coefficients at various points of the input signal, this architecture was unable to exploit the redundancy in the arithmetic operations of the DWT computation.

The architecture described in [26] implements line-based architecture for the 2D inverse wavelet transform. The architecture performing row-wise computation is straightforward. The column-wise computation is started as soon as the row-wise computation is completed for the current line of the 2D signal. Line buffering in the form of FIFOs and additional logic are necessary to perform column-wise DWT computation because the data are fetched in different order for the column-wise computation. This architecture starts the computation before the whole 2D signal is stored in the input memory. However, the proposed architecture in this thesis does not involve line-based transform, therefore this architecture is not considered for comparison.

The architecture in [27] folds the computations of all decomposition levels into the same low-pass and high-pass units to achieve higher hardware utilization. The architecture requires very large quantity of registers with increase in decomposition level. Apart from that, the whole architecture has to be designed separately for various levels of decomposition. The proposed architecture utilizes the same hardware to compute DWT coefficients irrespective of the level of decomposition.

#### 2.2 Best-Basis Algorithm

The 2D DWT as shown in Fig.2.1 decomposes the image into four sub-bands: approximation, vertical detail, horizontal detail and diagonal detail. Iterating this filter structure on all sub-bands creates a so-called atomic decomposition of the image in the form of a full, balanced quad-tree. This decomposition provides a large number of all possible decompositions. Each node of that quad-tree corresponds to a sub-band that is a

projection of the image to a subset of basis functions. This decomposition is called Wavelet Packet or WPT. The octave decomposition obtained from DWT is good for images that have most of their energy in a low frequency part. For some images that contain stronger high frequency elements, WPT is a better choice. A relatively simple and effective optimization algorithm called best-basis algorithm was proposed by Coifman [8]. It trims the atomic decomposition tree to minimize some defined cost function M. This algorithm simplifies optimization of the whole tree to a parent-children comparison of criterion M in a bottom-up direction. The algorithm takes the next four steps:

- Step 1: Decompose image into an atomic tree using wavelet packet.

- Step 2: Compute cost of each node using one of the cost functions listed in the later part of this section.

- Step 3: Starting at the bottom of the tree, repeat step 4 on all the nodes except the last level leaves until the root is reached.

Step 4: Make the following decision:

If

$$\sum_{k=1}^{4} M(x_{i,kthchild}) < M(x_{ithparent})$$

then

- (i) preserve subtree below the node  $x_{ithparent}$

- (ii) Replace the cost of the parent with the total cost of the children nodes as shown below:

$$M(x_{ithparent}) = \sum_{k=1}^{2} M(x_{i,kthchild})$$

else

prune subtree below x<sub>ithparent</sub>

end if

The cost function or information cost is the essential part of best-basis algorithm.

Some of the cost functions [28] are listed below:

$$M = \sum_{k \in \mathbb{Z}} \mu(|\mathbf{u}(k)|) \tag{2.1}$$

• Number of elements above threshold value:

$$\mu(\omega) = \begin{cases} 0, & \text{if } |\omega| \ge t \\ 1, & \text{if } |\omega| < t \end{cases}$$

(2.2)

• Logarithm of energy:

$$\mu(\omega) = \log|\omega|^2$$

(2.3)

• Entropy:

$$M(u) = \sum_{k} |u(k)|^{2} \log \frac{1}{|u(k)|^{2}}$$

(2.4)

The best-basis algorithm for 1D signal is explained with an example shown in Fig.2.3. The first step of the algorithm is to decompose the signal into quadtree structure and to compute cost of each node in the tree using one of the cost functions M given in equations (2.1-2.4). Starting from the bottom level of the quadtree, the cost of parent node is compared with the total cost of the corresponding children node. The cost of each pair of adjacent children nodes are compared to that of their parent. This is simply accomplished by comparing the cost function at the parent node with sum of cost function at children nodes. Either the parent node or the total cost of whichever has less cost is selected and the search is continued to the top branch in the tree. If the total cost of the children nodes is less than that of their parent, the children nodes are the better choice. In that case, the cost of the parent node is updated with the cost of the children and the

old parent cost is mentioned inside the parenthesis as shown in Fig.2.3. The nodes whose cost has not been updated with have been selected as best-basis nodes.

First Stage: Compute cost and mark the nodes

Second Stage: Perform Step-4 of the algorithm and select best-basis

Fig.2.3: Best-basis Selection process

### 2.3 Architectures for Elementary Functions

Elementary functions such as logarithm function are important for scientific computing, logarithmic number system processor and DSP and 3D-graphics applications.

Some of other elementary functions are square-root, exponential and trigonometric functions those are widely used in scientific computations [29-31]. Software routines applying techniques such as polynomial and rational expressions have been used to evaluate it. Although these routines provide accurate results, they are often too slow for real-time applications.

The hardware implementation of the elementary functions such as logarithm, exponential has been broadly classified into two groups — non-iterative and iterative methods. The non-iterative method includes direct table look-up, polynomial and rational approximations and table-based methods [32-34] and it is usually suitable for low-precision calculations. The iterative method includes CORDIC, digit-recurrence and online algorithms [35-38] and functional iteration methods such as Newton-Raphson and Goldsmidt algorithms [39] and it is usually suitable for both low-precision and high-precision computations.

Direct table look-up is suitable for very-low precision calculations, but the huge memory requirements of such technique make it an inefficient method for even single-precision computations. Another hardware implementation is based on approximating the elementary functions in the form of polynomial approximations [40]. However, the degree of the polynomial to be employed is usually high and a large number of multiplications and additions must be performed resulting in long execution times.

Table-based methods involve both direct table look-up and polynomial approximations method. The use of table look-up allows a low-degree polynomial to be employed and the low-degree polynomial allows a significant reduction in size of the

look-up tables used for computation. Some of the table-based methods are discussed in [32-34].

High-radix CORDIC based and high-radix digit-recurrence algorithms are important methods to implement elementary functions in hardware because of their low area requirements for high-precision computations compared to that of table-based methods. The main drawback in this algorithm is their linear convergence of one radix-r digit per step, resulting in long execution times for small radices and high precision. High-radix digit recurrence methods have been proposed for the computation of several elementary functions [35-38]. However, this method leads to an increase in the cost of implementation with increase in radix.

Functional iteration methods, such as Newton-Raphson and Goldschmidt algorithms [39], are based on multiplication operations and have quadratic convergence which results in low-latency algorithms for high-precision computations at the expense of increased hardware requirements. One of the main drawbacks of using this method is the difficulty in obtaining correct rounded result.

We propose an algorithm and architecture for natural logarithm implementation using Maclaurin series in Chapter 4.

## **CHAPTER 3**

# ARCHITECTURE FOR LIFTING-BASED DISCRETE WAVELET TRANFORM

#### 3.1 Introduction

The Discrete Wavelet Transform (DWT) based on lifting scheme was discussed in detail in Section 2.1. The lifting scheme is a fast implementation of the DWT. However, the software implementation of the lifting-based DWT on general-purpose processors is often too slow for real-time applications. General-purpose processors execute the programs in a sequential manner. However, in the hardware domain, the architecture for lifting-based DWT can be implemented such that the parallelism in its implementation can be exploited methodically. Also in the hardware domain, large amount of needed data can be stored in the registers and accessed immediately for future computation.

The lifting-based DWT computation involves considerable amount of parallel operations. The proper architectural design of DWT can buffer the data read from the memory and reduce the large amount of data transfer to and from the input memory. The dual-port internal RAM blocks in Xilinx Virtex II and Virtex II Pro FPGA family can be

exploited to implement the lifting-based DWT architecture. Also, most of the existing DWT architectures use either memory or FIFOs to store the intermediate results obtained. The proposed architecture performs both forward and inverse lifting-based DWT. The architecture does not require any extra memory or FIFOs to store the intermediate results.

This chapter is organized as follows. The arithmetic operations involved in lifting-based DWT for (5,3) and (9,7) wavelets are discussed in Section 3.2. In Section 3.3, the proposed architecture is presented with detailed description of predict module, update module and their integration.

## 3.2 Arithmetic Operations in Lifting-Based DWT

The lifting scheme provides many advantages such as fewer arithmetic operations, in-place implementation and easy management of boundary extension compared to convolution-based DWT architectures. The arithmetic operations of wavelet (5,3) and (9,7) filters, adopted in JPEG 2000 [41-42], are presented in this section in order to explain the redundancy in the arithmetic operation involved in the calculation of the lifting-based DWT computation. The lifting-based implementation of (5,3) wavelet as mentioned in JPEG2000 is shown in Fig. 3.1. The calculation of two consecutive high-pass and low-pass coefficients for (5,3) wavelet for an input signal  $x_{j,i}$  is shown below: High-pass coefficients,  $d_{j-l,i}$ :

$$d_{j-1,i} = x_{j,2i+1} + \alpha^*(x_{j,2i}) + \alpha^*(x_{j,2i+2}), \tag{3.1}$$

$$d_{j-1,i+1} = x_{j,2i+3} + \alpha * (x_{j,2i+2}) + \alpha * (x_{j,2i+4}).$$

(3.2)

Fig.3.1: Lifting Scheme for (5,3) wavelet

Low-pass coefficients,  $x_{i-1,i}$ :

$$x_{j-l,i} = x_{j,2i} + \beta * (d_{j-l,i-l}) + \beta * (d_{j-l,i}),$$

(3.3)

$$x_{j-1,i+1} = x_{j,2i+2} + \beta * (d_{j-1,i}) + \beta * (d_{j-1,i+1}).$$

(3.4)

where  $\alpha = 0.5$  and  $\beta = 0.25$  are the (5,3) filter coefficients [41]. From the equations (3.1) and (3.2), it is found that the product value of  $\alpha$  times  $x_{j,2i+2}$  calculated at the particular clock cycle is required at the next clock cycle. Similarly from equations (3.3) and (3.4), the product value of  $\beta$  times  $d_{j-1,i}$  at the particular clock cycle is required at the next clock cycle. Therefore, in the proposed architecture for the predict module calculation, we perform one multiplication in each cycle for calculating  $[\alpha^*(x_{j,2i+2})]$  and the other value  $[\alpha^*(x_{j,2i})]$  can be obtained from previous clock cycle, instead of performing two multiplications in every clock cycle as mentioned in [25]. Also, the proposed architecture needs only one multiplier in the update module. Thus, the proposed architecture utilizes the redundancy of the above mentioned arithmetic operation reducing the number of multipliers required.

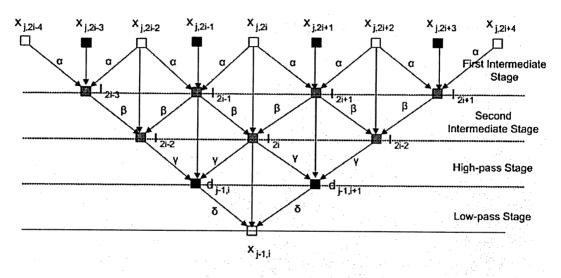

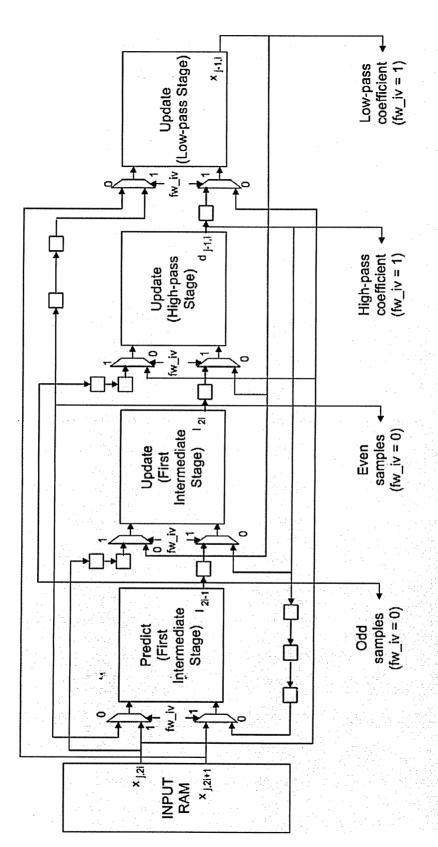

The lifting-based implementation of Daubechies 9/7 wavelet as mentioned in JPEG2000 is shown in Fig. 3.2. It involves two scaling steps and four lifting steps (first and second intermediate stages, high-pass stage and low-pass stage) as given below:

$$I_{2i+1} = x_{i,2i+1} + \alpha * (x_{i,2i}) + \alpha * (x_{i,2i+2}),$$

(3.5)

$$I_{2i} = x_{i,2i} + \beta * (I_{2i-1}) + \beta * (I_{2i+1}), \tag{3.6}$$

$$d_{j-1,i} = I_{2i-1} + \chi * (I_{2i-2}) + \chi * (I_{2i}),$$

(3.7)

$$x_{j-l,i} = I_{2i} + \delta * (d_{j-l,i}) + \delta * (d_{j-l,i+l}),$$

(3.8)

$$d'_{j-1,i} = K * (d_{j-1,i}),$$

(3.9)

$$x'_{i-1,i} = (1/K) * (x_{i-1,i}),$$

(3.10)

where  $\alpha = -1.586134342$ ,  $\beta = -0.052980118$ ,  $\chi = +0.882911075$ ,  $\delta = +0.443506852$  are the coefficients for (9,7) wavelet and K = 1.230174104 is the scaling factor [31]. Equations (3.5), (3.6), (3.7) and (3.8) represent the calculations of first intermediate, second intermediate, high-pass and low-pass stages respectively. The calculation of four lifting steps for two consecutive values for 9/7 wavelet is shown below:

First Immediate Stage, I<sub>2i+1</sub>:

$$I_{2i-1} = x_{j,2i-1} + \alpha * (x_{j,2i-2}) + \alpha * (x_{j,2i})$$

(3.11)

$$I_{2i+1} = x_{i,2i+1} + \alpha * (x_{i,2i}) + \alpha * (x_{i,2i+2})$$

(3.12)

Second Intermediate Stage, I2i:

$$I_{2i-2} = x_{i,2i-2} + \beta * (I_{2i-3}) + \beta * (I_{2i-1})$$

(3.13)

$$I_{2i} = x_{j,2i} + \beta * (I_{2i-1}) + \beta * (I_{2i+1})$$

(3.14)

High-pass Stage, di-1,i:

$$d_{j-l,i} = I_{2i-l} + \chi * (I_{2i-2}) + \chi * (I_{2i})$$

(3.15)

$$d_{j-l,i+1} = I_{2i+1} + \chi * (I_{2i}) + \chi * (I_{2i+2})$$

(3.16)

Low-pass Stage, x<sub>i-1,i</sub>:

$$x_{j-l,i} = I_{2i} + \delta^*(d_{j-l,i}) + \delta^*(d_{j-l,i+l})$$

(3.17)

$$x_{j-1,j+1} = I_{2i} + \delta * (d_{j-1,j+1}) + \delta * (d_{j-1,j+2})$$

(3.18)

Fig.3.2: Lifting Scheme for (9,7) wavelet without scaling

From the equations (3.11) and (3.12), it is found that the product value of  $\alpha$  times  $x_{j,2i}$  calculated at the particular clock cycle is required at the next clock cycle. Similar redundancy in multiplying operation can be easily observed for the other stages from equations (3.13-3.18). Thus, the proposed architecture performs one multiplying operation in every clock cycle for each stage and the other multiplier output can be obtained from the previous clock cycle.

Similarly, the proposed architecture needs two multipliers each for predict and update modules in the case of (13,7) wavelet. Thus, the proposed architecture utilizes the

redundancy of the above mentioned arithmetic operation reducing the number of multipliers required.

## 3.3 The Proposed Architecture

In this section, the architecture for (5,3) and (9,7) wavelets are described in detail. This architecture can be used to carry out both forward and inverse discrete wavelet transform.

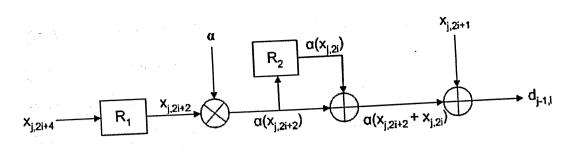

## 3.3.1 Predict Module

The predict module performs arithmetic calculation to determine detailed or high-pass coefficients,  $d_{j-1,i}$  given in equation (3.1) for (5,3) wavelet. The general-purpose processor performs four memory accesses, two multiplications and two additions to implement predict module. The hardware can be designed to perform all the arithmetic operations in parallel. Again, one multiplication output is obtained from its calculation in the previous cycle. It can be easily seen that, in every clock cycle, the module needs only one new even input sample,  $x_{j,2i+2}$ , from the memory and uses the other even input sample,  $x_{j,2i}$ , that is read in the previous cycle. This is achieved by storing the even sample,  $x_{j,2i}$ , in the register. This reduces memory read to one for all even input samples required for high-pass coefficient calculation. However, the odd input sample,  $x_{j,2i+1}$ , has to be read from the memory simultaneously. This problem is overcome by using dual-port RAM to store the input samples. The read operations of even and odd samples

occupy both ports of the dual-port RAM but the detailed or high-pass coefficient obtained from the predict module has to be written back to the RAM in the same clock cycle. In order to write the detailed or high-pass coefficient to the RAM, the input dual-port RAM has to be operated twice the frequency of the system clock.

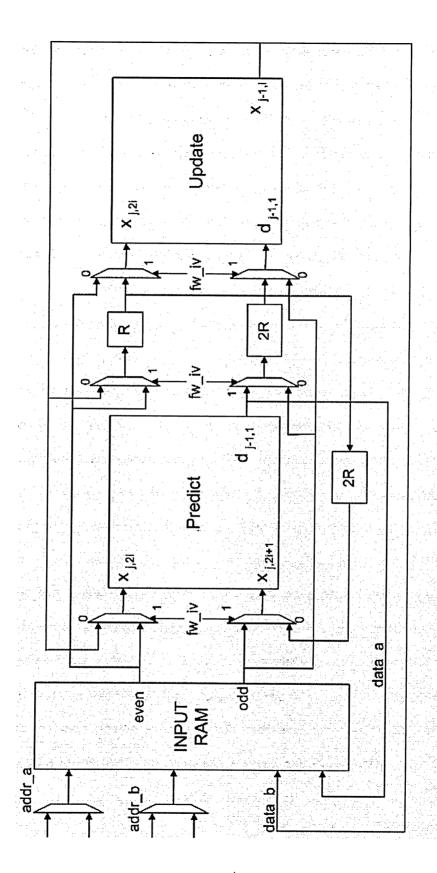

The predict module for (5,3) wavelet is shown in Fig.3.3. Initially, the input register  $R_1$  is loaded with the even sample from the input RAM. In the meantime, the predict filter coefficient ' $\alpha$ ' and the corresponding odd sample are made available to calculate the detailed coefficient  $d_{j-1,i}$ . The second register  $R_2$  stores the output of the multiplier in the current cycle and in the meantime the register  $R_2$  supplies the multiplier output obtained in the previous cycle. Thus we reduce the number of multipliers required for predict operation for (5,3) wavelet to one whereas the number required for the architecture described in [25] is two. Similarly, for (13,7) wavelet, only two multipliers required for predict module instead of four. For (5,3) wavelet, we can use shifters instead of multipliers. As pointed out in Section 2.1.2, the predict module for forward and inverse transform differs in only one arithmetic operation i.e. addition for forward transform and subtraction for inverse transform. The fw\_iv signal shown in Fig. 3.3 determines whether the predict module operates forward or inverse transform.

Fig.3.3: Predict Module

Fig.3.4: Update Module

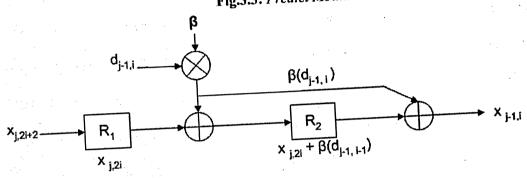

# 3.3.2 Update Module

The update module calculates the low-pass or coarse coefficients,  $x_{j-1,i}$  given in the equation (3.3) for (5,3) wavelet. Implementing update module in the general-purpose processor involves four memory accesses, two multiplications and two additions. The hardware is designed to perform all the arithmetic operations in parallel and only one multiplication is required to perform instead of two. The maximum number of memory accesses that could be carried out for each system clock cycle is four. But the predict module uses three memory accesses to the input RAM. The update module has to use the remaining one memory access to calculate and store coarse or low-pass coefficient in the same system clock cycle. The inputs of the update module are from the output of the

predict module and the even sample that is read from the input RAM for the predict module. Therefore, the output of the predict module and the even sample is fed directly to the update module instead of reading those values from the input memory again. Thus, the remaining one memory access to the input RAM is used to write the coarse or low-pass coefficient in the same system clock cycle.

The structure of the update module for (5,3) wavelet is shown in Fig. 3.4. The input register R<sub>1</sub> is loaded with the even sample. In the next clock cycle, the multiplier is fed with the detailed coefficient and the update coefficient 'β' and the output of the multiplier is fed to both the adders as shown in Fig. 3.4. Similarly, for (13,7) wavelet, the module needs only two multipliers for update module. In this case also, the multipliers can be replaced with shifters for (5,3) wavelet. The update module for forward and inverse transform differs by one arithmetic operation as mentioned in predict module. Thus, the fw\_iv signal determines the type of the transform to be performed.

As mentioned in JPEG2000 [41], the signal is symmetrically extended by two signal values on the left side and one signal value on the right side for (5,3) wavelet and four signal values on the left side and three signal values on the right side for (9,7) wavelet to reduce artifacts at the boundary. The boundary treatment problem is solved by passing proper address to the proposed architecture.

## 3.3.3 Lifting-Based (5,3) Wavelet Architecture

The proposed DWT architecture consists of predict module, update module, control unit to generate proper address and set of registers to establish data

communication between the modules. The proposed architecture calculates and writes one high-pass coefficient and one low-pass coefficient to the memory in each system clock cycle.

The predict and update modules discussed in the sections 3.3.1 and 3.3.2 are interconnected with set of registers for (5,3) wavelet as shown in Fig. 3.5. The general-purpose processor executes predict and update calculation sequentially whereas, in hardware, both calculations can be carried out simultaneously. But the problem in hardware design now is that the update module needs the outputs of the predict module in forward transform and the predict module needs the output of the update module in the case of inverse transform.

As discussed in the previous section, the predict module uses three memory accesses out of four available memory accesses to the input RAM whereas the update module requires three more memory accesses (two read operations for detailed coefficient and even sample and one write operation for coarse coefficient) to the input RAM. However, the memory accesses required for the update module can be reduced to one as given below:

- 1. The set of registers have been introduced between the output of the predict module, d<sub>j</sub>. <sub>1,i</sub>, and the input (detailed coefficient) of the update module. These numbers of registers in between both modules pass on the correct detailed coefficient required at the input of the update module.

- 2. From equations (3.1-4), it can be seen that the update module uses the same even samples that the predict module uses. However, the even sample read from the input

Fig.3.5: Architecture for (5,3) Wavelet

RAM is used by both the modules at different clock cycle i.e. the predict module uses it first and then the update module needs it. Thus, placing a few registers before the even sample is fed to the update module solves the synchronization or timing problem and the update module reuses the even sample read from the input RAM.

Thus, two read operations for the update module are avoided by using set of registers in between both modules. Only one memory access available to the input RAM for the update module is used to perform write operation of the coarse coefficient. Now, the proposed architecture is able to calculate one detailed coefficient and one coarse coefficient at every clock cycle. The proposed architecture operates dual-port RAM twice as fast as the system clock frequency to obtain detailed and coarse coefficients at every clock cycle. The first half of the system clock is used to write the detailed and coarse coefficients into the input RAM whereas the second half of the system clock is used to read even and odd samples from the input RAM. The technique discussed till this point is based on the forward transform.

For inverse transform, the two inputs for update module are read from the input RAM directly and the outputs of both predict and update modules are written back to the input RAM. Thus, all the four memory accesses available for one system clock frequency are used. The two inputs required for predict module is fed in a similar method applied to the update module in the forward transform.

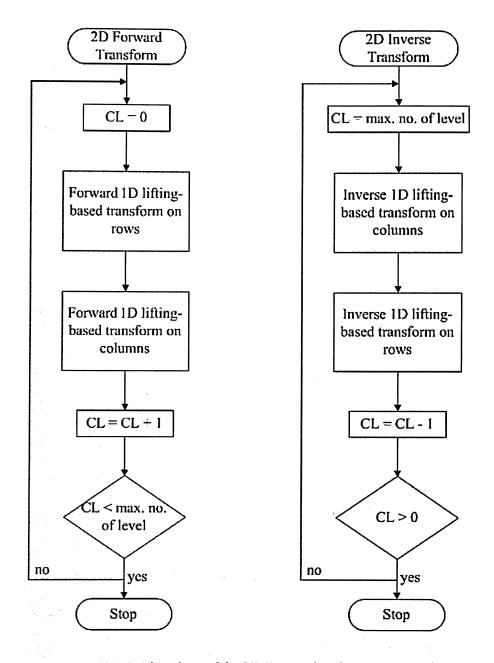

The multiplexers placed before the set of registers, the predict module and the update module select the proper signal required by them based on the forward or inverse transform. The above described architecture performs lifting scheme for 1D signal. For the forward 2D transform, it starts with iteration level zero as current level (CL). The

forward 1D transform is first applied to all the rows and then to all the columns. Subsequently, the transform starts with the next level of iteration until the required number of decomposition level is accomplished. For the inverse transform, the inverse 1D transform is applied exactly in the opposite order. Flowcharts in Fig.3.6 illustrate the 2D forward and inverse transform.

## 3.3.4 Lifting-Based (9,7) Wavelet Architecture

The proposed lifting based architecture for (9,7) wavelet consists of one predict module to perform first intermediate stage, three update module to perform second intermediate, high-pass and low-pass stages, control unit to generate proper addresses and set of registers to establish data communication between modules. This architecture can be used to perform both forward and inverse DWT and DWPT.

The proposed architecture for 9/7 wavelet with four lifting steps is shown in Fig. 3.7. The scaling steps in 9/7 wavelet have not shown in Fig. 3.7. The set of registers is used in between the stages to properly pass the output of one stage to the next stage. Because of these registers, the architecture does not require any extra memory/FIFOs to store the intermediate results. This architecture uses dual-port input RAM which operates twice as fast as the system clock frequency to obtain the high-pass and low-pass coefficients at every clock cycle. The read and write operations to the input RAM and the data transfer between stages are similar to that explained for the (5,3) wavelet architecture. The forward or inverse transform is performed based on the value of fw\_iv signal (0 or 1).

Fig.3.6: Flowchart of the 2D Forward and Inverse Transform

The lifting-based (13,7) wavelet architecture has one predict module, one update module, control unit and set of registers for data communication between the modules. However, both predict and update modules are not the same as that discussed in Sections

Fig.3.7: Architecture for (9.7) wavelet

Fig.3.8: Functional Output of Lifting-based (5,3) wavelet

Fig.3.9: Functional Output of Listing-based (9,7) wavelet

3.3.1 and 3.3.2. The predict module and the update module need two multipliers (shifters) to calculate detailed and coarse coefficients respectively. This architecture will look similar to that of (5,3) wavelet.

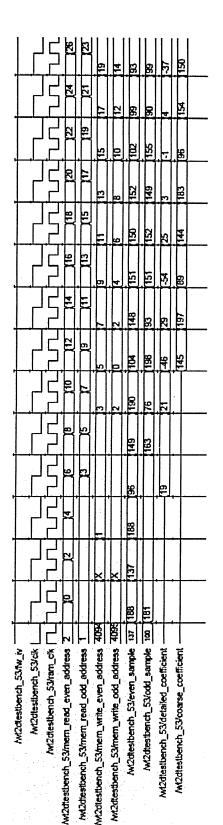

The proposed architecture for (5,3) wavelet is described in VHDL hardware description language for functional correctness and the waveform obtained from the simulator environment is shown in Fig.3.8. The "fw iv" signal is set to one to perform forward DWT transform. The input RAM (dual-port) is operated at the frequency (ram clk) twice that of the system frequency (clk). The even and odd samples are read from the input RAM when the system clock (clk) is low and the output of predict and update modules are written into the input RAM when the "clk" signal is high. The "mem read even address" and "mem read odd address" signals supply proper address to the input RAM to read the even and odd samples respectively when the system clock (clk) is low. The "mem write even address" and "mem write odd address" signals supply proper address to write the coarse (update output) and detailed (predict output) coefficients respectively when the system clock signal is high. In the first two clock cycle. the two consecutive even sample values (188 and 137 read from the even addresses 2 and 0 as shown in the Fig.3.8) are read form the input RAM and one odd sample (181 from the odd address 1) is read in the third clock cycle. The predict module calculates the detailed coefficient using those even and odd samples and writes the detailed coefficient in the input RAM (19 write into the address 1) in the fourth clock cycle. Similarly, the update module calculates the coarse coefficient and writes it in the input RAM in the seventh clock cycle (145 writes in the address 0). Since the whole process is pipelined, the predict and update modules write the detailed and coarse coefficients at every clock

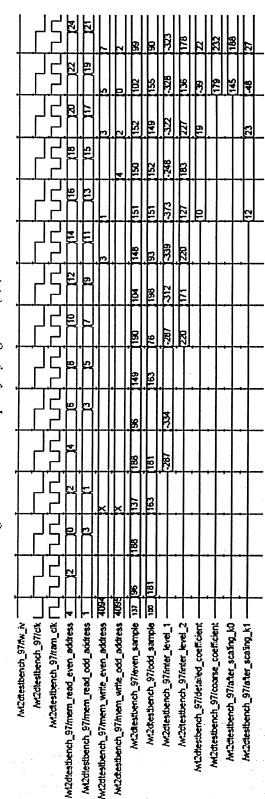

cycle. Similarly, the proposed architecture for (9,7) wavelet is described in VHDL hardware description language for functional correctness and the waveform obtained from the simulator environment is shown in Fig.3.9. The signals shown in the Fig.3.9 are meant for the same functionality described above. But (9,7) wavelet includes four stages of lifting operation i.e. first intermediate, second intermediate, predict and update stages. The outputs of these stages are represented by the signals in Fig.3.9 are inter\_level\_1, inter\_level\_2, detailed\_coefficient and coarse\_coefficient signals respectively.

## **CHAPTER 4**

# ARCHITECTURE FOR BEST-BASIS ALGORITHM FOR 2D SIGNALS

### 4.1 Introduction

Best basis algorithm belongs to a class of entropy-based algorithms for efficient representation and signal compression. Classical entropy-based algorithms for best basis selection were first introduced by Coifman and Wickerhauser [8]. Best basis algorithm is primarily designed to reduce the storage space needed for a signal and also it can be used for de-noising. When the information content of the signal coordinates in the new basis is low it means that the distribution of coefficients is such that the energy of the signal is concentrated in a few coordinates. Another natural application of best basis algorithm is de-noising. This is achieved simply by finding a representation with a few significant terms (less entropy representation) so that one can neglect the coefficients less than a threshold value [51]. If signal to noise ratio is not too low one is able to extract the desired signal from the noisy one by threshold operation hence getting rid of unimportant

coordinates. In this chapter the hardware implementation of best-basis algorithm is discussed in detail.

This chapter is organized as follows. Section 4.2 discusses the algorithm and the architecture for natural logarithm implementation. The architecture for best basis algorithm and the architecture for best tree calculation for 2D signal are discussed in detail in the Section 4.3.

## 4.2 Algorithm and Architecture for Logarithm Function

## 4.2.1 Algorithm

The proposed algorithm is based on Maclaurin (or Taylor) series for natural logarithm (ln) function [43] which is given below:

$$\ln(1+x) = x - \frac{x^2}{2} + \frac{x^3}{3} - \dots, -1 \le x \le +1$$

(4.1)

The main drawback in calculating logarithm function using Maclaurin series is that it involves more arithmetic (multiplication and addition) operations to get more accurate value. If |x| is much smaller than one, the accurate value of ln(1+x) obtained from equation (4.1) involves lesser arithmetic operations.

The proposed algorithm uses the first two terms in Maclaurin series to obtain ln(1+x) as shown below:

$$\ln(1+x) = x - \frac{x^2}{2}, -1 \le x \le +1 \tag{4.2}$$

To calculate natural logarithm of 'X' i.e. ln(X), where X > 1, divide X by another number R such that |x'| = |X/R| is close to 1 so that x = x'-1 is very small. Thus,

$$ln(X) = ln(R) + ln(x')$$

(4.3)

The constant ln(R) is read from the look-up table or memory. Since |x| is much smaller than one, the ln(x') = ln(1+x) is calculated using the equation (4.2). The value of R is chosen depending upon the number of bits of accuracy needed after the decimal point of the logarithm output. The algorithm for natural logarithm implementation is explained below:

Step 1: Determine the range  $R_{max}$ ,  $2^n cdots 2^{n+1}$ , where n is an integer, such that  $2^n < X \le 2^{n+1}$ .

Step 2: To obtain 4*l* bits or *l* decimal digits accuracy after decimal point of natural logarithm of X, divide the range  $R_{max}$  into  $m = 2^{l-1}$  equal sub-ranges  $R_1, R_2, ..., R_n$ .

i.e.

$$R_1 \rightarrow 2^n \cdots \left[\frac{2^{n+1}-2^n}{m}\right] + 2^n$$

$$R_1 \rightarrow 2^n \cdots \left[\frac{2^n}{m} + 2^n\right]$$

$$R_2 \rightarrow \left[2^n + \frac{2^n}{m}\right] \cdots \left[2^n + \frac{2 \cdot 2^n}{m}\right]$$

$$R_3 \rightarrow \left[2^n + \frac{2 \cdot 2^n}{m}\right] \cdots \left[2^n + \frac{3 \cdot 2^n}{m}\right] \cdots$$

$$R_m \rightarrow \left[2^n + \frac{(m-1)2^n}{m}\right] \cdots 2^{n+1} \tag{4.4}$$

**Step 3:** Select the range  $R_x$  in which X falls.

i.e.

$$\left[2^{n} + \frac{(x-1)2^{n}}{m}\right] < X < \left[2^{n} + \frac{x \cdot 2^{n}}{m}\right]$$

(4.5)

**Step 4:** Find the mid-point of the range,  $R_x$ .

$$R_{x}(mid) = \frac{1}{2} \left[ \left( 2^{n} + \frac{(x-1)2^{n}}{m} \right) + \left( 2^{n} + \frac{x \cdot 2^{n}}{m} \right) \right]$$

(4.6)

**Step 5:** Normalize X in the range  $R_x$  as given below:

Let x' be normalized X.

$$x' = \frac{X}{R_x \text{ (mid)}} \tag{4.7}$$

The natural logarithm of X is calculated by

$$ln(X) = ln[R_x(mid)x'] = ln[R_x(mid)] + ln(x').$$

(4.8)

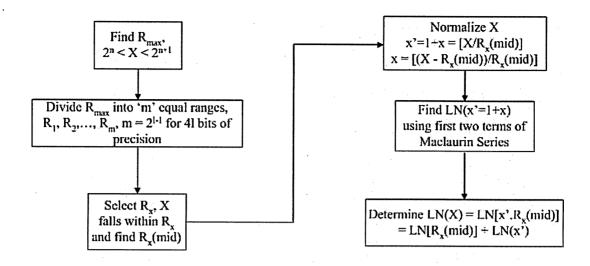

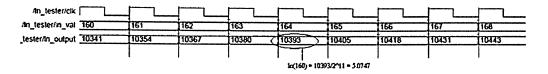

The ln(x') is obtained using equation (4.2) whereas  $ln[R_x(mid)]$  is read from lookup table or memory. The proposed algorithm for logarithm implementation is a noniterative method applying Maclaurin series and the flowchart explaining the proposed algorithm is shown in Fig.4.1. For example, calculate natural logarithm of X = 184 with I = 2 decimal digit accuracy after decimal point from the above algorithm.

Fig.4.1: Flowchart of Natural Logarithm implementation using Maclaurin series to find LN(X)

**Step 1:** The range  $R_{max}$  is  $(2^7 \dots 2^8)$ .i.e. 128 < 184 < 256.

**Step 2:** Number of sub-ranges, m = 2. The first range  $R_1$  is 128 ... 192 and the second range is  $R_2$  is 192 ... 256.

Step 3: The selected range  $R_x$  is  $R_1$  because X (=184) falls within the range of  $R_1$  i.e. 128 < X < 192.

**Step 4:** The mid-point of the selected range  $R_1$  is 160 i.e.  $R_1$ (mid) = 160.

Step 5: x = x' - 1 = (184-160)/160 = 24/160 and ln(184) = ln(160) + ln(1+x)=5.2139.

The expected value is 5.2149 and the error is 0.0010. It is evident from the error value that the natural logarithm value of X is accurate for 8 bits or two decimal digits after the decimal point.

The above example clearly explains the computation of natural logarithm value for integer numbers. We present another example to compute natural logarithm for the values of X less than one. To calculate the natural logarithm for X = 0.0512 with 16-bit

of precision i.e. four decimal digit of precision, the proposed algorithm needs a little modification which is explained with the example.

Step 1: Determine the range  $R_{max}$  in which X falls. The range  $R_{max}$  is  $(2^{-4} \dots 2^{-5})$ .i.e.  $2^{-4} < 0.0512 < 2^{-5}$ .

**Step 2:** The number of sub-ranges to obtain 16-bit of precision is m = 8 or  $2^{(l=3)}$ . The ranges are

$$R_1 - 0.03125 - 0.03515625$$

$$R_2 - 0.03515625 - 0.0390625$$

$$R_3 - 0.0390625 - 0.04296875$$

$$R_4 - 0.04296875 - 0.046875$$

$$R_5 - 0.046875 - 0.05078125$$

$$R_6 - 0.05078125 - 0.0546875$$

$$R_7 - 0.0546875 - 0.05859375$$

$$R_8 - 0.05859375 - 0.0625$$

**Step 3:** The selected range is  $R_6$ .i.e. 0.05078125 < X < 0.0546875.

**Step 4:** The mid-point of selected range is  $R_6(\text{mid}) = 0.052734375$ .

Step 5: The value of x is  $(X/R_6(mid) - 1) = -0.029096$ . The ln(1+x) = -0.02952 obtained using the equation (Y.2). Thus, the value of  $ln(X) = ln(R_6(mid)) + ln(1+x) = -2.9720$ . The actual value of ln(X) is -2.9720157 and the absolute error is 0.0000157.

The last example presented below explains the computation of natural logarithm for mantisaa part of the floating point representation [44]. The computation of ln(X = 1.5120) with 16-bit or four decimal digit of precision is explained below:

**Step 1:** The range  $R_{max}$  is always in the range from  $2^{16}/2^{15}$  to  $2^{15}/2^{15}$ .i.e. 1 < X < 2.

**Step 2:** The number of sub-ranges to obtain 16-bit of precision is m = 8 or  $2^{(l=3)}$ . The ranges are

$$R_1 - 1.000 - 1.125$$

$$R_2 - 1.125 - 1.250$$

$$R_3 - 1.250 - 1.375$$

$$R_4 - 1.375 - 1.500$$

$$R_5 - 1.500 - 1.625$$

$$R_6 - 1.625 - 1.750$$

$$R_7 - 1.750 - 1.875$$

$$R_8 - 1.875 - 2.000$$

Step 3: The selected range is  $R_5$  (1.500 – 1.625).

**Step 4:** The mid-point of the selected range is  $R_5(\text{mid}) = 1.5625$ .

Step 5: The value of x is  $(X/R_5(mid) - 1) = -0.03232$ . The ln(1+x) = -0.03284 is obtained from equation (Y.2). Thus, the value of  $ln(X) = ln(R_5(mid)) + ln(1+x) = 0.4134$ . The actual value of ln(X) is 0.413433 and the absolute error is 0.000033.

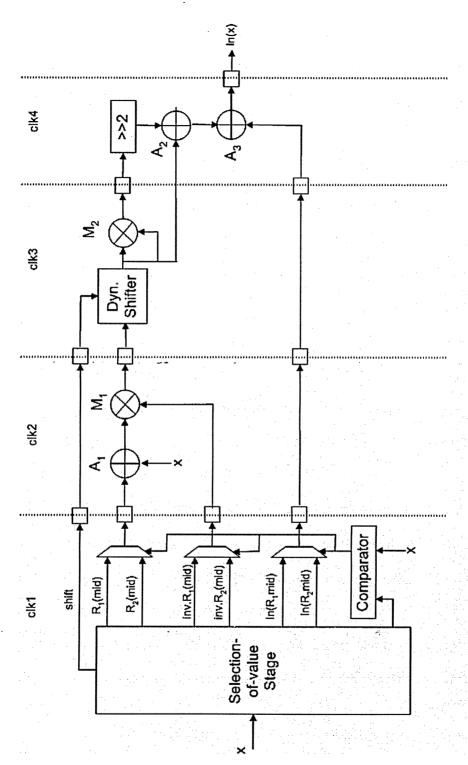

## 4.2.2 Architecture

The proposed architecture of natural logarithm implementation consists of three stages: Selection-of-value stage, Normalization stage and Log-unit stage. The architecture involves two multiplication and three addition operations irrespective of the number of