## Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2009

# RFID Security : Tiny Encryption Algorithm And Authentication Protocols

Shirley. Gilbert Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Gilbert, Shirley, "RFID Security : Tiny Encryption Algorithm And Authentication Protocols" (2009). *Theses and dissertations*. Paper 1093.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

B 1930 6>6×

# RFID SECURITY: TINY ENCRYPTION ALGORITHM AND AUTHENTICATION PROTOCOLS

By

Shirley Gilbert

A project presented to Ryerson University in partial fulfillment of the requirement for the degree of Masters in Engineering in the program of Electrical and Computer Engineering

> Toronto, Ontario, Canada, 2009 © Shirley Gilbert 2009

#### PROPERTY OF RYERSON UNIVERSITY LIBRARY

I hereby declare that I am the sole author of this project.

I authorize Ryerson University to lend this project to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this project by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

"我们的好人。"

ii

Shirley Gilbert

## **RFID Security: Tiny Encryption Algorithm and Authentication Protocols**

Shirley Gilbert, Masters in Electrical Engineering, 2009, Electrical and Computer Engineering, Ryerson University

#### Abstract

With recent advancement in Radio Frequency Identification (RFID) technology, in addition to reduction in cost of each unit, security has emerged as a major concern. Since an RFID tag has limited resources like memory, power and processing capabilities, authentication must be provided by encryption and decryption procedures that are lightweight consuming minimal resources. This report investigates some relevant RFID encryption algorithms and their possible implementations with respect to security, cost and performance. A survey and brief comparison of the algorithms are performed and the Tiny Encryption Algorithm (TEA) is selected as a feasible solution for encryption and decryption with an acceptable level of security. TEA is implemented on an FPGA (Field Programmable Gate Array) platform. After investigating several state-of-the-art authentication approaches, two protocols are designed incorporating TEA and implemented using VHDL. Simulations corroborate the functionality of the protocols and the two techniques are compared in terms of timing, cost, security and performance. Potential improvements to enhance the security and strengthen RF communication during authentication are explored.

### Acknowledgements

The author would like to thank the supervising professor Dr. Gul Khan for providing guidance and support for the successful completion of the project. The author would also like to thank the review committee members for their suggestions and valued opinions.

## Dedication

I would like to dedicate this work to my parents for their constant love, support and encouragement without which I would not be where I am today.

# **Table of Contents**

| 1. | Introduction                                                 | 1  |

|----|--------------------------------------------------------------|----|

|    | 1.1 Background                                               | 1  |

|    | 1.2 Motivation for Research                                  | 2  |

|    | 1.3 Original Contributions                                   | 3  |

|    | 1.4 Organization of Thesis                                   | 3  |

|    |                                                              |    |

| 2. | RFID Security and Encryption Algorithms                      | 4  |

|    | 2.1 Encryption Preliminaries                                 | 4  |

|    | 2.2 Advanced Encryption Standard (AES)                       | 5  |

|    | 2.3 Scalable Encryption Algorithm (SEA)                      | 6  |

|    | 2.4 International Data Encryption Algorithm (IDEA)           | 8  |

|    | 2.5 Tiny Encryption Algorithm (TEA)                          | 9  |

|    | 2.6 Extended Tiny Encryption Algorithm (XTEA)                | 12 |

|    |                                                              |    |

| 3. | RFID Authentication Protocols                                | 15 |

|    | 3.1 Introduction                                             | 15 |

|    | 3.2 Attacks to RFID System                                   | 16 |

|    | 3.3 Fundamental Approaches in Authentication                 | 17 |

|    | 3.4 Authentication for Location Privacy and Forward-Security | 19 |

|    | 3.5 Authentication for Low-cost Tags                         | 21 |

|    |                                                              |    |

| 4. | Implementation of Tiny Encryption Algorithm (TEA)            | 24 |

|    | 4.1 Overview                                                 | 24 |

|    | 4.2 Functional Requirements of TEA                           | 24 |

|    | 4.3 Input/Output Requirements of TEA                         | 25 |

|                                             | 4.4  | Design of Encryption/Decryption Modules                           |  |  |  |  |

|---------------------------------------------|------|-------------------------------------------------------------------|--|--|--|--|

|                                             | 4.5  | Testing and Verification Results                                  |  |  |  |  |

|                                             | 4.6  | Integrating Hardware Encryption and Software Decryption modules31 |  |  |  |  |

|                                             | 4.7  | Variable Rounds of Tiny Encryption Algorithm                      |  |  |  |  |

|                                             |      |                                                                   |  |  |  |  |

| 5.                                          | Im   | provements in RFID Security                                       |  |  |  |  |

|                                             | 5.1  | Introduction                                                      |  |  |  |  |

|                                             | 5.2  | Variable Key Scheme (Modified TEA)                                |  |  |  |  |

|                                             | 5.3  | Variable Round Scheme (Modified TEA)                              |  |  |  |  |

|                                             | 5.4  | HDL Implementation of Variable Key Scheme40                       |  |  |  |  |

|                                             | 5.5  | HDL Implementation of Variable Round Scheme43                     |  |  |  |  |

|                                             | 5.6  | Comparison of Variable Key and Variable Round Authentication      |  |  |  |  |

|                                             |      | Techniques45                                                      |  |  |  |  |

| 6.                                          | Co   | nclusion and Future Work48                                        |  |  |  |  |

| RE                                          | EFEI | RENCES                                                            |  |  |  |  |

| APPENDIX A – TEA (VHDL, C Code)             |      |                                                                   |  |  |  |  |

| APPENDIX B – Variable Key Scheme (VHDL)62   |      |                                                                   |  |  |  |  |

| APPENDIX C – Variable Round Scheme (VHDL)83 |      |                                                                   |  |  |  |  |

|                                             |      |                                                                   |  |  |  |  |

## List of Figures

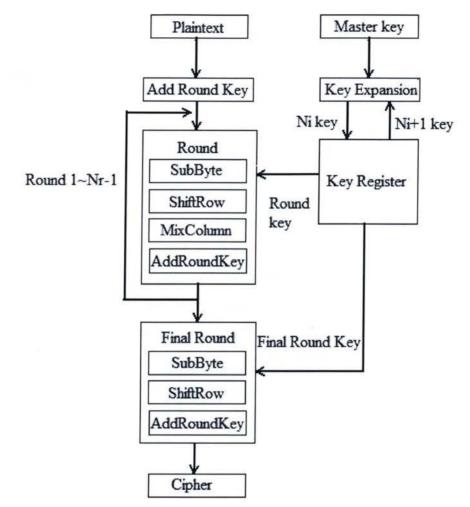

- Figure 2.1 Structure of the AES Algorithm

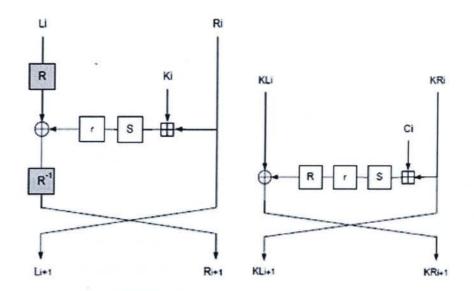

- Figure 2.2 Encrypt/Decrypt Rounds in SEA

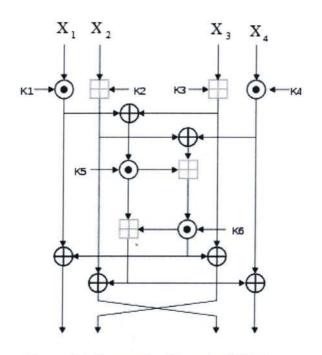

- Figure 2.3 Encryption Round of IDEA

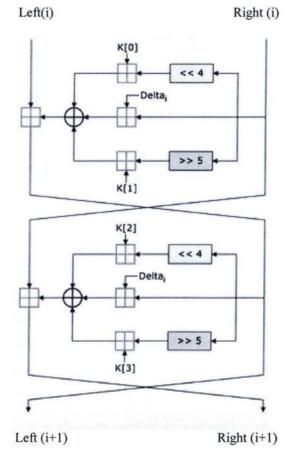

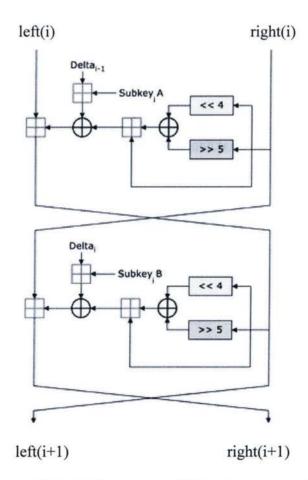

- Figure 2.4 Two Feistel rounds (One round of TEA)

- Figure 2.5 Feistel Structure for XTEA for two rounds

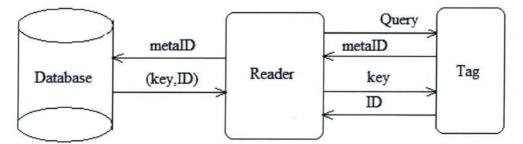

- Figure 3.1 Basic Hash-Locking based Scheme [15]

- Figure 3.2 Pseudo-Random Function (PRF) Block

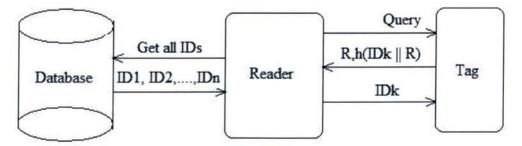

- Figure 3.3 Randomized Hash locking Scheme [15]

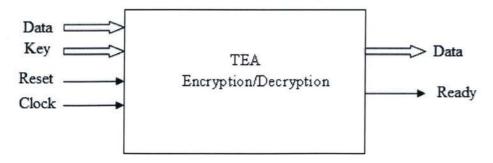

- Figure 4.1 Block Diagram for TEA algorithm

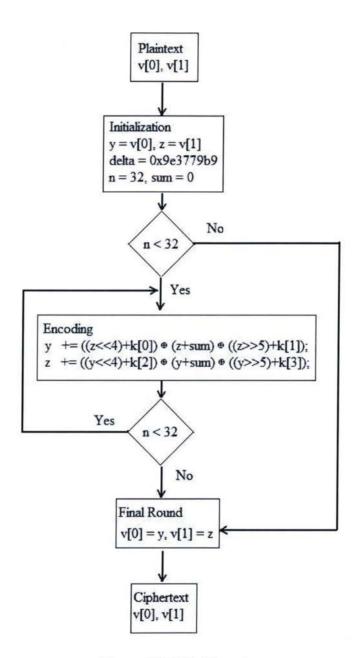

- Figure 4.2 TEA Flowchart

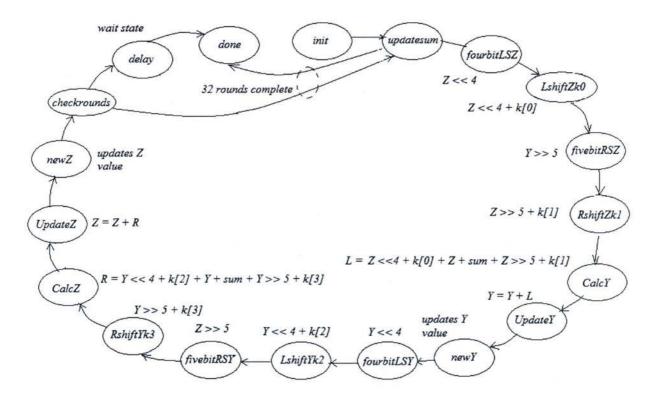

- Figure 4.3 State Diagram for TEA Implementation

- Figure 4.4 TEA Simulation waveform illustrating transition of states

- Figure 4.5 TEA Simulation First 9 rounds of encryption cycle

- Figure 4.6 TEA Simulation Waveform Output after 32 rounds

- Figure 4.7 TEA Simulation Waveform Output after 32 rounds of Decryption

- Figure 4.8 System generated by SoPC (System on a Programmable Chip) Builder

- Figure 4.9 TEA Top-Level Module Design

- Figure 4.10 Waveform New Delta Value Calculation for Decryption

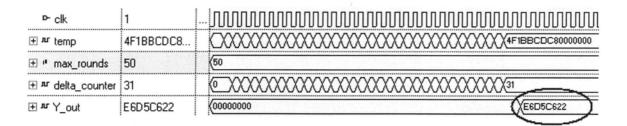

- Figure 4.11 Waveform Output of Encryption after 50 rounds

- Figure 4.12 Waveform Output of Decryption after 50 rounds

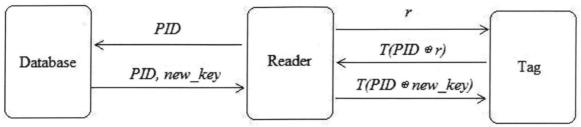

- Figure 5.1 Proposed Authentication Scheme for Variable Keys

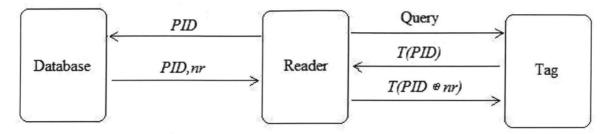

- Figure 5.2 Proposed Authentication Scheme for Variable Rounds

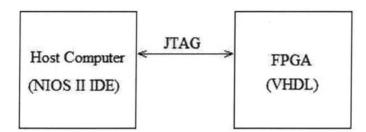

- Figure 5.3 General Setup for Hardware/Software Implementation of Variable Key and Variable Rounds approaches

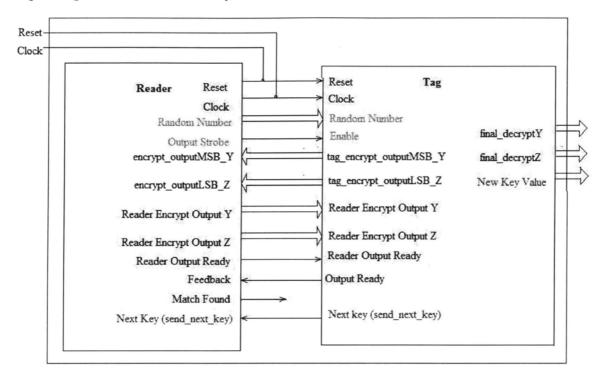

- Figure 5.4 Components and their Interface for Variable Keys Authentication

- Figure 5.5 Simulation of the Variable Key Authentication protocol

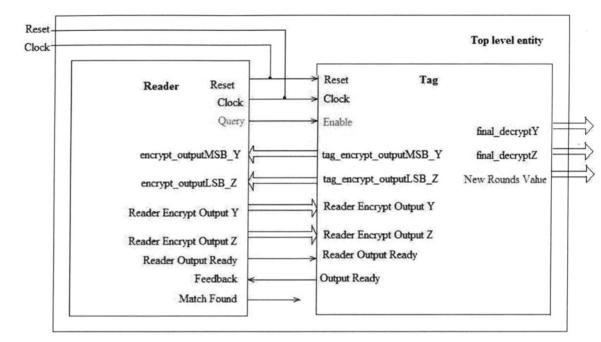

- Figure 5.6 Components and their Interface for Variable Round Authentication

- Figure 5.7 Simulation of the Variable Round Authentication protocol

## List of Tables

Table 2.1 Comparison of Implementation Results of TEA and XTEATable 5.1 Comparison of Variable Key and Variable Round Authentication

## **Glossary of Acronyms**

- AES Advanced Standard Encryption

- ANSI American National Standards Institute

- CLB Configurable Logic Block

- CMOS Complementary Metal Oxide Semiconductor

- CRC Cyclic Redundancy Check

DB – Database

DES – Data Encryption Standard

DOS - Denial of Service

- DSP Digital Signal Processor

- EPC Electronic Product Code

FPGA - Field Programmable Gate Array

- FSM Finite State Machine

- HDL Hardware Description Language

- I/O Input/Output

- ID Identification

- IDE Integrated Development Environment

- IEEE Institute of Electrical and Electronics Engineers

- IP Core Intellectual Property Core

ISO - International Organization for Standardization

- JTAG Joint Test Action Group

- LSB Least Significant Bit

- MSB Most Significant Bit

- NIST U.S National Institute of Standards and Technology

- p-box Permutation Box

PID – Pseudo-ID

PRF – Pseudo Random Function

PRNG - Pseudo Random Number Generator

- RISC Reduced Instruction Set Computer

- RFID Radio Frequency Identification

RNG - Random Number Generator

RAM - Random Access Memory

s-box - Substitution Box

SEA - Scalable Encryption Algorithm

SoPC - System on a Programmable Chip

TEA - Tiny Encryption Algorithm

UART - Universal Asynchronous Receiver-Transmitter

UHF – Ultra High Frequency

VHDL - Very High Speed Integrated Circuit Hardware Description Language

XTEA - Extended Tiny Encryption Algorithm

## Chapter 1

## Introduction

#### 1.1 Background

Radio Frequency Identification (RFID) is a rapidly developing field and technology that emerged in the last decade. This technology is employed by using implantable microchip devices also known as RFID tags (transponders); these tags communicate with a central unit/general purpose computer often called a Reader or an interrogator for exchange of information. With a plethora of applications ranging from supply chain management, retailing, theft prevention, access control and people tagging as a few examples, the need to explore factors of cost, security, performance and efficiency become imperative. Moreover, since this technology is implemented on an embedded platform, it must be accomplished by optimizing features like hardware, area, cost and latency which need to be satisfied by the available resources. It is estimated that the cost of an RFID tag is few cents and occupies an area of less than 1mm<sup>2</sup> (approx 0.4 mm<sup>2</sup>) [16], which will significantly contribute to the rise of its use in the coming years. An RFID tag has limited features which include minimal memory resources and power capabilities. Transponders are attached to a small antenna to transmit and receive radio waves and are equipped to operate in a wide range of frequencies from low frequency (120 KHz) to ultra high frequency (960 MHz). They are usually classified as active and passive tags, depending on their available resources. Active tags possess a battery and higher processing abilities as opposed to passive tags which have very limited resources and no battery. A passive tag derives its power from the radio waves generated by the reader during interrogation. Due to their restricted capabilities passive tags warrant encryption algorithms with minimal computational complexity. In addition to the tag and the reader, the entire system comprises a backend server that is employed to store all vital information including details of all tags being used. Several algorithms have been investigated, developed and compared for performance [1]. Most of these are adopted by standardizing organizations like the IEEE, the American National Standards Institute (ANSI),

(International Organization for Standardization) ISO and the U.S National Institute of Standards and Technology (NIST). Currently, it is proposed to eliminate electronic bar code systems and replaced with passive RFID tags of EPC (Electronic Product Code). These are passive UHF tags that are equipped with certain functions like anti-collision, a 10-bit pseudo random number generator (PRNG) and cyclic redundancy check (CRC). The current research is focussed on how to optimize the available resources on a tag to achieve a good balance of cost and security.

#### **1.2 Motivation for Research**

Most of the RFID applications are sensitive to protecting the information being exchanged, issues of security and privacy must be carefully planned. Moreover, the weakest link in communication is the wireless channel link between the reader and the tag. Security is assured by ensuring that the information exchange between the tag and the reader is not revealed to an unauthorized entity or eavesdropper. Several authentication protocols have been researched and put forth in literature in addition to encryption and decryption algorithms.

Once algorithms and circuits are tested for functionality, hardware area consumption and latency of the design is deemed suitable, a CMOS (semiconductor-chip) implementation of the design is adopted for mass production. Although a plethora of platforms for implementation exist to choose from, there are two ways to implement an encryption algorithm - either in hardware or software. Both realms have different characteristics and performance measurement metrics. Software implementations are compared based on their memory consumption and clock cycles whereas hardware implementations are evaluated based on the gate-count (area) and clock cycles for computation [1]. In order to be adopted as a standard, a particular algorithm is thoroughly analyzed by using fewer rounds or invocations to find a short-cut attack and then extended to the full version of the algorithm [3]. In addition, safety, performance and availability of the algorithm are considered. Availability signifies whether or not the algorithm is accessible in public domain or patented by the algorithm's designer. Safety of an algorithm is typically cited by the designer in terms of number of rounds for which the algorithm is guaranteed to

withstand any attack. Performance comparisons are also made on different platforms such as Pentium processors, RISC processors, microcontrollers, Digital Signal Processors (DSPs) and Field Programmable Gate Arrays (FPGAs) since this metric can greatly vary on the platform selected for implementation. It is clear that establishment of security and privacy in conjunction with minimal consumption of hardware to resources are requirements crucial to a secure RFID system. In order to satisfy the requirement of security and privacy, it is imperative to study and explore authentication protocols in RFID systems, and to meet the requirement of low consumption of resources use of lightweight encryption algorithms is essential.

#### **1.3 Original Contributions**

This report presents detailed implementation of the Tiny Encryption Algorithm (TEA) using an FPGA platform. Investigation of authentication protocols leads to the development of two authentication protocols with slight modifications to TEA in order to increase security and enhance resistance to attacks in an RFID system. Comparison of these two protocols is made in terms of cost and security. Furthermore, results of the implementation of these authentication protocols are presented to verify functionality of the proposed schemes.

#### 1.4 Organization of Thesis

Chapter 2 provides a brief survey of the most widely used and researched cryptographic encryption algorithms with their advantages and disadvantages. Chapter 3 discusses the various significant authentication protocols recently researched with respect to RFID systems. Chapter 4 presents details on the implementation of the Tiny Encryption Algorithm (TEA) on a hardware platform (FPGA). Chapter 5 includes possible improvisations to strengthen security in communication between a transponder and the reader and Chapter 6 draws conclusion to the research and provides suggestions for future work. The Appendix includes source code (C, VHDL) for implementation of TEA (as discussed in Chapter 5).

## **Chapter 2**

## **RFID Security and Encryption Algorithms**

The following sections outline various algorithms and encryption methods recently put forth in literature. Encryption methods are briefly classified as symmetric and asymmetric algorithms; where the former uses the same key for encryption and decryption as opposed to the latter approach. Moreover symmetric algorithms are further classified as stream and block ciphers. Stream ciphers operate on certain data to produce an encrypted bit at a time at the output whereas block ciphers operate on a block of data to produce an encrypted block of the cipher text. Symmetric methods are far less demanding in terms of hardware and software resources and hence draw focus in the context of this research.

#### 2.1 Encryption Preliminaries

In cryptography, the basic elements of logic that are used to develop an algorithm are the XOR function, hash function and substitution/permutation boxes. XOR function is very critical in cryptography; if R is a randomly generated string, C is cipher-text and P is a plain string, we can generate C = (P XOR R) and recover P = (C XOR R). Hash functions can be either cryptographic or plain; cryptographic hash functions produce an output called 'message digest' or simply 'digest' based on plaintext input where each block of data produces a particular string of bits based on a complex function (e.g. checksums or CRC). A plain hash function on the other hand maps the possible blocks of input data to a hash-table. A substitution box (s-box) is an element that accepts an input of 'n' bits and generates an m-bit output based on a carefully designed look-up table to resist cryptanalysis. A permutation box (p-box) is a technique used to shuffle bits across an s-box in order to produce an obscure relation between the input and output. The use of s-boxes and p-boxes are necessitated to follow the two most important criteria in cryptography. Shannon's property of confusion and diffusion is defined as the complexity between the key and hash value (in context of hashing) and complexity between plaintext

and cipher-text (in the context of encryption) respectively [4]. Another common concept is that of a Feistel structure, which is a symmetric structure used in encryption and decryption and it consists of a series of rounds of either bit-shuffling, use of s-boxes or XOR operations. The following section briefly analyzes the various implementations and indicates the most feasible preference for a lightweight encryption algorithm that satisfies the requirements of a small embedded platform then different comparable encryption algorithms and their advantages and disadvantages are surveyed.

#### 2.2 Advanced Encryption Standard (AES)

Advanced Encryption Standard (AES) is an encryption algorithm that is widely selected to replace its predecessor Data Encryption Standard (DES) in the U.S by the National Institute of Standards and Technology (NIST) [3]. AES proved itself as a strong symmetric key algorithm with a block size of 128 bits and keys of sizes 128, 192 and 256 respectively. AES is available world-wide and it is royalty free. Although this might seem surprising to be adopted by the U.S government; in order to be adopted commercially the algorithm must be available freely. Moreover, security of AES depends on how secret the key is kept. AES uses both s-boxes and p-boxes in its implementation and a normal round is composed of four different transformations: SubByte, ShiftRow, MixColumn and AddRoundKey. The final round is equal to the normal round except that MixColumn is eliminated. As depicted in Figure 2.1, 'SubByte' is a non-linear substitution step where each byte is replaced with another according to a lookup table. 'ShiftRows' is a transposition step where each row of the state is shifted cyclically for a certain number of steps. 'MixColumns' performs mixing operation which operates on the columns of the state, combining the four bytes in each column. 'AddRoundKey' is a state where each byte of the state is combined with the round key where each round key is derived from the cipher key using a key schedule. Different approaches for implementation based on required design criteria are explained in [10] classified as pipelining and sub-pipelining. Pipelining increases the speed of execution by processing multiple blocks of data simultaneously. Sub-pipelining inserts registers between a set of subsequent computations to obtain higher speed proportional to sets of stages; however there is control and area overhead associated with the use of extra registers and the

increase in speed depends on the number of stages chosen. Since there are a lot of resources consumed in the AES, it is not suitable for a light weight application in RFID tags.

Figure 2.1 Structure of the AES Algorithm [9]

#### 2.3 Scalable Encryption Algorithm (SEA)

Scalable Encryption Algorithm was mainly designed to target microcontroller embedded applications [2]. As its name indicates, its most important feature is its scalability; SEA is an encryption algorithm designed to be parameterized according to processor size and plaintext and key-size. Parameterization is based on the assumption that key and text block sizes are the same and in multiples of six word lengths. Although this was originally tested and developed for platforms in embedded software applications using

microcontrollers, recent investigation in hardware implementation has been accomplished [2]. Its performance has been compared to AES and it is based on Feistel structure with variable number of rounds. A SEA algorithm is denoted by SEA<sub>n,b</sub> where n is the plaintext size and key size and b is the processor and word size. The operations involved in SEA are bit-wise XOR, word rotation, inverse word rotation and substitution (s-box) box and addition mod 2<sup>b</sup>. The main advantage of SEA algorithm is its parameterization for different platforms. SEA is proven to withstand linear and differential cryptanalysis provided that the number of rounds is greater than or equal to 3n/4. The suggested number of rounds for optimum security is a minimum of (3n/4 + 2), where the second term ensures complete diffusion. A typical evaluation of consumed resources is, SEAn,b occupies 4nb words in RAM, nb + 3 registers and  $(n_r - 1) \times (22nb + 29) + 20nb + 18$ operations for encryption and decryption which is based on its implementation for Atmel's microcontroller platform (n<sub>r</sub> refers to the number of rounds). Although proven robust to a series of attacks, the trade-off is the consumption of resources in hardware. It is estimated that execution of SEA, for example on a RISC processor with 128-bit key, can take upto a few milliseconds and it requires a few hundred bytes of memory.

Figure 2.2 Encrypt/Decrypt Rounds in SEA

Figure 2.2 illustrates encrypt, decrypt and key round functions where: Encrypt round performs  $R_{i+1} = R(L_i) \oplus r(S(R_i \boxplus K_i))$ ;  $L_{i+1} = R_i$  Decrypt round performs  $R_{i+1} = R^{-1}(L_i \oplus r(S(R_i \boxplus K_i)); L_{i+1} = R_i.$ Key round consists of  $KR_{i+1} = KL_i \oplus R(r(S(KR_i \boxplus C_i))); KL_{i+1} = KR_i$ C refers to ciphertext, K is the key, R is the word rotation and r is the bit rotation function respectively.

Implementation results in hardware (Xilinx FPGA) corroborate that as long as the processor size is not a limiting factor for the frequency of operation, increasing the word size leads to the most efficient implementation for both area and throughput [2]. A disadvantage of this approach is the use of s-box that consumes considerable amount of memory and is not desirable for lightweight encryption algorithm applications. SEA employs a 3-bit substitution box; its use is not a major disadvantage and can be accommodated if the tag possesses sufficient memory. Flexibility of SEA is its most important characteristic, which can be an advantage due to the variety of implementation options (code size is different in each case). However, it can also be a disadvantage in some cases where a processor or platform prefers to use fixed size algorithms in order to consume fixed number of clock cycles. Due to the restrictions in hardware for RFID tags, the above mentioned reasons present limitations in hardware implementation.

#### 2.4 International Data Encryption Algorithm (IDEA)

International Data Encryption Algorithm was developed by Xuejia Lai and James Massey in 1991[26]. The algorithm was intended as a replacement for the DES. It uses elementary operations like bit-wise XOR, addition modulo  $2^{16}$  (square symbol) and multiplication modulo  $2^{16} + 1$  (denoted by a dot in circle symbol) as shown in Figure 2.3. IDEA operates on 64-bit plaintext block data and produces cipher text of 64 bits using a 128-bit key. The group of 64-bit data input is divided into four 16-bit sub-groups X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub> and X<sub>4</sub>, which are fed to the first round, and there are a total of eight rounds. The four sub-groups are XORed, added, and multiplied with one another and with six 16-bit subkeys in each round. Between the rounds, the second and the third sub-blocks are swapped. Finally, the four sub-blocks after the eighth round are collected and combined with four sub-keys in an output transformation. Fifty two sub-keys are needed in eight rounds and output transformation, which are generated by the sub-key generator. One of the advantages of this technique is the lack of need for s-boxes and its robustness. IDEA is a patented and universally applicable block algorithm which permits effective protection of transmitted and stored data against unauthorized access by third parties. It is widely adopted in various fields like financial sectors, broadcasting, etc.

Figure 2.3 Encryption Round of IDEA

#### 2.5 Tiny Encryption Algorithm (TEA)

Tiny Encryption Algorithm is a cryptographic algorithm developed by David Wheeler and Roger Needham in 1994 [27], in an attempt to establish lightweight encryption and decryption. TEA uses symmetric encryption; more specifically block ciphers where it encrypts a block of data (64 bits) at a time using a 128-bit key as shown in Figure 2.4. The basic operations that constitute the algorithm are bit-wise shifts and rotations, exclusive or and modulo 2<sup>32</sup> addition operations. The thirty-two bit addition is an inexpensive operation and is done by chaining four 8-bit additions in the order of least significant byte to the most significant byte. These operations satisfy the Shannon's two properties of diffusion and confusion without the explicit need of complex substitution boxes (s-boxes) and permutation boxes (p-boxes). Feistel ciphers are employed in TEA, which is a special class of iterated block ciphers. The cipher text is calculated from the plain text by repeated application of the same transformation or round function. In a Feistel cipher, the text being encrypted is split into two halves. The round function, F is applied to one half using a sub key and the output of F is XORed with the other half. The two halves are then swapped. Each round follows the same pattern except for the last round where there is no swap. This is illustrated in detail in Figure 2.4. The value of delta in the algorithm is derived from the golden number,  $delta = (\sqrt{5} - 1) 2^{31}$  that is represented as 0x9E3779B9 (Hex). It is known that TEA has certain weaknesses which are accounted for by the designers of this algorithm in an extension to the TEA algorithm called XTEA [6]. One of TEA's major weaknesses is that it suffers from equivalent keys. Each key is equivalent to three others, and this reduces the effective key size to only 126 bits. The related key attacks are possible even though the construction of  $2^{32}$  texts under two related keys seems impractical.

Figure 2.4 Two Feistel rounds (One round of TEA)

TEA is highly resistant to differential cryptanalysis and claims to provide optimum security. Differential cryptanalysis is a means of studying different methods of obtaining the hidden meaning behind the encrypted information (without access to the secret key). This is done by studying how differences in input can affect the resultant difference in the output.

The pseudo code of the algorithm is shown below.

#### **Encode Routine**

It is seen from the source code, that decryption is essentially the same as the encryption procedure with a reversal of steps.

#### **Decode Routine**

TEA is arguably neither the fastest nor the shortest algorithm however it provides a perfect balance between ease of implementation, consumption of minimal resources and

compromise between safety and size of implementation. Due to which it is an ideal choice for deployment in RFID systems.

#### 2.6 Extended Tiny Encryption Algorithm (XTEA)

As pointed out earlier, TEA presented certain weaknesses which were taken care of by introducing certain changes in the original algorithm resulting in its extended version called XTEA [6]. A block diagram of XTEA is depicted in Figure 2.5. Whilst maintaining the simplicity of the algorithm two tasks are performed:

- Adjust the key schedule

- To introduce the key material more slowly

Figure 2.5 Feistel Structure for XTEA for two rounds

There is a re-arrangement of add, XOR and shift operations in order to induce a more complex key schedule. This is illustrated in the source code given below.

#### **XTEA Encode Routine (Pseudo code)**

```

void encipher(unsigned long* v, unsigned long* k) {

unsigned long v0=v[0], v1=v[1], i;

unsigned long sum=0, delta=0x9e3779b9;

for(i=0; i<32; i++) {

v0 += ((v1 << 4 ^ v1 >> 5) + v1) ^ (sum + k[sum & 3]);

sum+=delta;

v1 += ((v0 << 4 ^ v0 >> 5) + v0) ^ (sum + k[sum>>11 & 3]);

}

```

```

v[0]=v0; v[1]=v1;

```

The changes due to XTEA bring about the following advantages:

- It corrects the mixing proportion of TEA

- Eliminates the key-related attacks due to key equivalence classes

A hardware implementation of XTEA was performed using multiplexors and registers to perform the 32-bit operations [7]. The sequence of operations is controlled by a finite state machine, which generates the required control signals to drive the datapath. A comparison of TEA and XTEA is made to compare the area consumption of different units like the adder, shifter, controller, etc. as shown in Table 2. [7]. The results clearly show that the area consumption of both approaches are nearly the same. XTEA on the other hand consumes more clock cycles (e.g. 705 clock cycles for XTEA and 289 for TEA) compared with TEA and also consumes more power (3.86 $\mu$ A compared with 3.79 $\mu$ A) [7].

| Module/component            | Chip area | ea   |

|-----------------------------|-----------|------|

|                             | (GE)      | (%)  |

| Eight 32-bit register       | 1,592     | 60.4 |

| Arithmetic-logic unit (ALU) | 347       | 13.2 |

| Constant                    | 5         | 0.2  |

| Shifter                     | 179       | 6.8  |

| Multiplexer                 | 180       | 6.8  |

| Controller (FSM)            | 258       | 9.8  |

| Others                      | 75        | 2.8  |

| XTEA total                  | 2,636     | 100  |

| TEA total                   | 2,633     | 99.9 |

Table 2.1 Comparison of Implementation Results of TEA and XTEA

XTEA thus resolves the weaknesses of TEA; however both algorithms claim to provide

extremely lightweight application and acceptable (medium) security for use in the industry.

## **Chapter 3**

## **RFID** Authentication Protocols

#### **3.1 Introduction**

Development of robust authentication protocols is imperative in today's applications; a common example is "key-less entry" in cars where the RFID tag in the key is activated as the driver approaches to open doors and control the ignition system. Other critical examples include potential applications in RFID enabled passports and human implantation for health monitoring. An authentication protocol is a safe way to identify if a particular RFID tag is genuine and belongs to the system. This is very crucial in order to avoid common problems such as replay attack, eavesdropping, cloning, counterfeiting, spoofing, jamming attack, etc. Moreover, it is important to ensure confidentiality, message integrity and availability of the system [12]. The major challenge in designing an authentication protocol is to find a compromise between security and cost. The classification of authentication protocols can be based on three points as given below

- Underlying algorithm used in the protocols.

- Procedure of message exchange.

- Secure combination of above two.

The first point has been discussed in detail in the second chapter. Chapter 5 will present possible approaches to accomplish the last goal with respect to a light-weight symmetric encryption algorithm such as TEA. Design of an optimum authentication protocol forms the crux of security and privacy of an RFID system. An authentication protocol precisely deals with the second point; specifically, the message exchange has to be performed securely or in a 'secret' manner over a wireless medium. Primitive forms of authentication include a challenge-response method between a reader and a tag. An RFID reader initializes a challenge request and a tag responds with a secret value (computed from the key – typically symmetric) and sends this result to the reader as a response. The reader verifies this result from its database to verify the authenticity of the tag.

There have been several approaches put forward recently by researchers addressing issues mentioned beforehand, and techniques to overcome them; specifically where a reader must authenticate a tag before exchange of data and also methods where a tag needs to authenticate a reader to ensure privacy [20],[28]. Moreover, mutual authentication protocols also exist, where the tag authenticates validity of a reader in addition to tag-reader authentication. The following sub sections explain various proposals and evolution of authentication protocols as of today in light of requirements such as cost and security and also resistance to various attacks.

#### 3.2 Attacks to RFID System

An authentication protocol is mainly judged by its ability to provide resistance against common attacks encountered by the system. Several attacks are possible and are taken into consideration while designing an authentication procedure. Eavesdropping is a familiar attack where an adversary intercepts a response from the tag during wireless communication between a tag and the reader, and tries to extract critical information like the tag's ID or the secret key used for secure communication [19]. This is mainly established through cryptanalysis. *Replay attack* is another form whereby an adversary intercepts response from the tag and relays it to the reader; response from the reader can be later used in another session by the impersonated tag [14]. Location tracking is an issue where if the information of a tag (such as its ID) is leaked and becomes available to the adversary, further responses from the tag can be easily tracked thereby revealing the location of the tag. Denial of Service (DOS) is a type of attack caused by an adversary to disrupt handshake between reader and a tag by intercepting or blocking the wireless transmission [19]. This leads to de-synchronization in the communication between a tag and the reader. It is thus important to keep track if a session has been terminated correctly or not. *Cloning attack* is a common form and can be accomplished in different possible ways. For example, physically cloning the contents of the tag or impersonating the original tag from its responses. Other forms of attack (counterfeiting, spoofing, etc.) more or less arise from or are closely related to the above mentioned attacks.

Other metrics include *Forward Security* where the contents of communication prior to being attacked should be safe; i.e. by finding key information from a transaction, the adversary can recalculate the key value and verify contents of the previous session. Moreover in case of a compromise, further transactions must be ensured security. This is normally established by varying the key value. In the design and analysis of any protocol (current or new) security and privacy analysis is executed by keeping these measures under consideration. The more types of attacks a particular protocol can prohibit or at least provide high resistance to, the more secure is the protocol's design.

#### **3.3 Fundamental Approaches in Authentication**

This section briefly describes the primitive approaches to establish authentication in a system. A hashed value of key is stored in the tag's memory called metaID, either wirelessly or over a secure channel and this process is termed 'locking' [15]. Once locked the tag remains in this state until it is queried by a legitimate reader to unlock it, and gain access to its contents. The reader queries the tag and gets the metaID as a response. The reader now acquires the correct ID from its back-end database and sends it wirelessly to the tag. It is clear from this simple protocol shown in Figure 3.1 that the key could be easily intercepted by an eavesdropper and the tag could be spoofed.

Figure 3.1 Basic Hash-Locking based Scheme [15]

Another approach that follows as an improvement to this method is the randomized access control [15]. In this method, the tag is equipped with a pseudo-random number generator. A random number 'R' is generated by the tag in response to a query and the value (R, h(ID || R)) is transmitted to the reader as shown in Figure 3.3. Here, 'h' is a hash function and || refers to concatenation operation. The reader uses the 'R' value to

perform calculation of h(ID || R) in a brute-force manner till it finds a match. To further improve the algorithm and provide a strong mode of secrecy a provision can be made where keys are only stored at the back-end database. In this case, the tags are equipped with a Pseudo-Random Function (PRF). A PRF is essentially a deterministic function or a module that accepts a variable number x and a constant seed (hidden value) k to produce a function f(x, k) or  $f_k(x)$ . In terms of implementation, a PRF block can be designed as a look-up table as shown in Figure 3.2.

$$x \longrightarrow \boxed{f} \longrightarrow f_k(x)$$

Figure 3.2 Pseudo-Random Function (PRF) Block

There is significant amount of research and probabilistic study to ensure that the PRF generates all values to be randomized and to gauge if a particular PRF is a 'good' or a 'bad' function. The tag is equipped to generate  $f_k(x)$  and now responds with (R, (ID ||  $h(ID)) \oplus f_k(R)$ ). As mentioned in section 1.3, if  $A \oplus B = C$  then knowing C and A, B can be recovered using the operation  $C \oplus A = B$  or  $C \oplus B = A$  (if C and B are known). Now the reader calculates  $f_k(r)$  and XORs it with (ID || h(ID))  $\oplus f_k(R)$  to get (ID || h(ID)). This value is searched among a list to find a match. This method is useful because an eavesdropper getting any information from the transaction will not be able to acquire the tag's actual ID without the PRF generated key.

Figure 3.3 Randomized Hash locking Scheme [15]

In order to reduce computational complexity at the back-end database due to brute force search method, a slight modification was proposed by Li et al. [18]. The tag sends (R,  $h(ID \parallel R), h(P_x \parallel R)$  where  $P_x$  is some product information (for example, product category code) where instead of the tag replying to a query with only (R,  $h(ID \parallel R)$ ). This enables the database to decode the value of  $P_x$  so that instead of searching the entire system of records, it can search for the ID within the product code category. This is a significant improvement for applications in retail management and stock inventory.

It is thus apparent how authentication procedures have evolved to suffice some of the basic requirements of RFID system by providing tag authentication to the reader without the exchange of the actual key. Based on research, simulations for authentication protocols in software hardly exist to the best of our knowledge, although real simulation of an RFID environment using hardware is executed in few research spaces around the world and is a far more expensive approach.

#### 3.4 Authentication for Location Privacy and Forward-Security

Although the above mentioned techniques are developed such that the key remains unexposed during wireless transmission, there are other possible attacks that may arise leading to a compromise in authentication. For example Kim et al. and others analyze the importance of protecting the tag identifier (ID) [13]. This value is typically encoded by a manufacturer and it is embedded in the tag's memory. Since it is unchanged throughout the tag's lifetime, location tracking may occur if information is leaked thus leading to a compromise in security. A method to update the key during each transaction has been put forth recently [13]. The main assumptions of this work are that the tag possesses an ID that is unique, a secret key (*key*) and has an encryption function (E). Moreover, the encryption scheme used here is a stream cipher. The reader is equipped with a pseudorandom number generator (PRNG), E and the back-end database stores details of all pairs of ID, key and E'<sub>ID</sub>, R'; where E'<sub>ID</sub> refers to the encrypted tag ID using the current key by an operation done in the database and R' refers to random bit streams generated in the database.

The reader generates a random number S and sends it to the tag. The tag now generates  $f(ID \parallel key)$  which is generated in the form of streams R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub>; from this the unique ID in the tag is XORed with R<sub>2</sub> which gives E<sub>ID</sub>. T<sub>flag</sub> is a flag kept to know whether the last authentication transaction is successful or not. If T<sub>flag</sub> is 0 it means the authentication is successful and if this is a non-zero number it means otherwise. In the latter case, R<sub>1</sub> and R<sub>2</sub> are re-generated from  $f(ID \oplus key) \parallel key \oplus S)$  while R<sub>3</sub> and R<sub>4</sub> remain the same. The tag now sends R<sub>1</sub>, E<sub>ID</sub>, T<sub>flag</sub> and S to the reader which recognizes S and therefore the validity of the tag. Also, these values are passed on by the reader to the database for verification. Meanwhile, the tag changes the value of T<sub>flag</sub> to a non-zero random number to indicate that a response from the database is awaited. The database checks the value of T<sub>flag</sub> in its records; if this is zero, then the following procedure for updating the key value is performed.

#### Procedure Challenge Responded (Pseudo Code) [13]

```

Input: R1, EID, Tflag, S

If Tflag == 0 Then Search E'ID == EID

If E'ID.count > 0

Repeat i ← i + 1

If R'1 == R1

Lkey ← Ckey

Ckey ← R'3

LR2 ← R'2

Until i <= E'ID.count

Return 0</pre>

```

In case  $T_{flag}$  has a random value, it is implied that the authentication in the previous transaction is not completed successfully leading to a loss of synchronization between the tag and the database. A new procedure is executed to establish a temporary value of  $R_{temp}$  and  $E_{tempID}$  till it finds the original ID.

#### Procedure Challenge Incomplete (Pseudo Code) [13]

```

If Rtemp == R1

Return EtempID

Until i <= EtempID.count

Return 0</pre>

```

This protocol contends to provide security against replay attack (man-in-the-middle attack). Since the value of ID characterizes the response as being from the tag, the database rejects any replay of the message sent by the tag. Moreover, since the ID is encrypted an adversary cannot gain this value through cryptanalysis.

As put forth by Kim et al., a symmetric algorithm is employed for location privacy and forward security, however it adds a huge computation load on the back-end server in case of large number of tags. It is also contented that in addition to excessive calculations, replay attack may be possible through counting statistics [14].

#### 3.5 Authentication for Low-cost tags

This section analyzes a protocol put forth very recently by Li, with a goal of lowering the cost of RFID tag production [17]. Since the area and power consumption of the circuit are directly affected by the number of gates in the system, the protocol is designed to keep computational complexity to a minimum. This is accomplished by eliminating encryption and hash functions and utilizing simple operations such as XOR and modulo 2 additions. This system assumes that a tag is equipped with a pseudo-ID (PID) which is subject to frequent changes (updates) and a permanent ID stored in its memory. Moreover, it possesses two keys K1 and K2 (which will also be updated). The database stores PID, ID, K1 and K2 for all tags in the system. Initially, the reader sends a hello message to the tag which is responded by PID from the tag. The reader finds (K1 || K2) corresponding to this PID value from the database and generates a random number r and computes A and B and sends them to the tag. The tag decodes the random number value from A and B using the secret keys K1 and K2. If both the random number values from A and B are the same (which they should be), the tag computes C and sends it back to the reader. The reader checks if there is a valid ID from the message C it just received. If it is not, then the operation is aborted otherwise it continues to the next phase of updating the keys and PID. A snapshot of the protocol's pseudo code is illustrated below. **Tag identification:**

Reader → Tag: hello

Tag → Reader: PID(n)tag(i)

#### SLMAP mutual authentication:

```

Reader \rightarrow Tag: A||B

Tag \rightarrow Reader: C (C')

where:

A = PID(n)tag(i) \oplus Kl(n)tag(i) + r

B = PID(n)tag(i) + K2(n)tag(i) \oplus r

C = (PID(n)tag(i) + IDtag(i) \oplus r) \oplus (Kl(n)tag(i) + K2(n)tag(i) + r)

```

#### After authentication of reader and tag, the keys are updated as follows,

```

PID(n+1)tag(i) = (PID(n)tag(i) + K1(n)tag(i)) @ r + (IDtag(i) +

K2(n)tag(i)) @ r

K1(n+1)tag(i) = K1(n)tag(i) @ r + (PID(n+1)tag(i) + K2(n)tag(i) +

IDtag(i))

K2(n+1)tag(i) = K2(n)tag(i) @ r + (PID(n+1)tag(i) + K1(n)tag(i) +

IDtag(i))

```

In case of a synchronization loss due to an attack, status information of previous protocol run is stored in a flag. It also establishes confidentiality since a nearby eavesdropper may capture the message but would not get any information without the actual key values as well as tag/reader authenticity (reader-to-tag and tag-to-reader due to exchange of messages A, B and C). Moreover, this algorithm may not provide the highest possible level of security. It establishes a light-weight authentication protocol with minimal number of gates (less than 300) as opposed to a few thousand gates as required by techniques employing encryption algorithms by using bit-wise operations.

The techniques for authentication studied here present a design to overcome a single or a combination of attacks in a system. The most commonly used components are hash-function generators and XOR gates as they consume very little hardware. Complex components can be integrated in the system depending on the level of security desired. Liu presents an eleven-step protocol that employs a stream cipher to overcome replay attack, loss of synchronization, wiretapping and provide security measures like forward

security, indistinguishability and synchronization between the database and the tag [19]. It is always aimed to design a protocol that provides a compromise between the cost and security.

## **Chapter 4**

## **Implementation of Tiny Encryption Algorithm**

#### 4.1 Overview

TEA was originally implemented in software (comparable to the performance of DES) however, it has conveniently migrated to hardware platforms mainly due to the ease of implementation despite restricted resources in hardware. A hardware implementation of TEA could be designed as an intellectual property (IP) core. Requirements of the design can be specified and classified as functional requirements which entail the width of input data, latency of encryption, number of gates consumed by the design, power consumption, etc.

The design is developed using a hardware description language specific to a platform (e.g. Xilinx, Altera FPGA) and tested using waveform simulations. There are several CAD tools available to establish and test the design including Active HDL, Altera Quartus and Xilinx ISE for (Hardware Description Language) HDL simulations to verify functionality of the system. There are different methods in which the system can be designed e.g. either by separating the control path and data path or using a finite state machine (FSM) to control the flow of both. Hardware implementation of TEA has been accomplished in the past using HDL leading to CMOS implementation ([6], [8]) and using a microcontroller [30]. Tiny encryption algorithm is one of the simplest algorithms to be implemented in hardware. It can be employed, where time is a constraint, i.e. a trade-off can be made between the levels of security desired and the time to encrypt or decrypt, in terms of number of cycles.

#### 4.2 Functional Requirements of TEA

The functionality of TEA must be verified using a simulator to validate the operation of both the encryption and decryption schemes using waveforms. We have used Active HDL 7.1 simulator which is chosen due to its simplicity and ease of generating and

applying test vectors. It must occupy minimum number of gates or configurable logic blocks (CLBs). Plaintext must be successfully converted to encrypted cipher text in accordance with the algorithm after 64 rounds or 32 clock cycles. The encrypted output when fed back to the decryptor must successfully retrieve the original plaintext.

## 4.3 Input/Output Requirements of TEA

The input signals of TEA are specified as following:

- 64-bit input data (plaintext)

- 128-bit key (symmetric)

- Reset signal

- Clock signal (for synchronization)

- Input data rate (32 kbps or 64 kbps)

The outputs must include the following:

- 64-bit Encrypted data (cipher text)

- Ready signal

- Output data rate (32 kbps or 64 kbps)

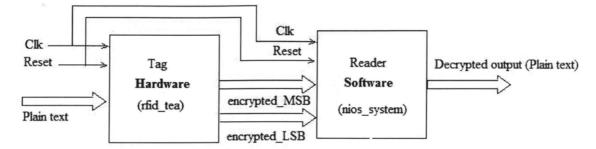

The block diagram of Figure 4.1 illustrates various I/O signals required for TEA implementation. Clock is necessary for synchronization between encryption and decryption modules. Ready is needed to specify validity of the output at the end of encryption/decryption. The input vector data refers to plaintext, key is 128 bit long and the output 'Data' refers to the cipher text. We have opted for the encryption implementation in hardware using VHDL and decryption in software using C language in Altera Nios II IDE. Details of the block diagram are explained in the following section.

Figure 4.1 Block Diagram for TEA algorithm

# 4.4 Design of Encryption/Decryption Modules

TEA can be represented as a flowchart as illustrated in Figure 4.2, where v[0] and v[1] are 32-bit plaintext inputs and 'n' represents the number of rounds. The cipher text result is available after 32 rounds are completed.

Figure 4.2 TEA Flowchart

The input data of 64 bits is split into two halves Y and Z of 32 bits each, where Y is the most significant bit (MSB) and Z is the least significant bit (LSB). The 128-bit key is also divided into four blocks of 32 bits each; k[0], k[1], k[2] and k[3] for internal calculations. The encryption module is designed as a finite state machine (FSM) having 18 states as illustrated in Figure 4.3. All the states are synchronized using the clock signal and the entire process contains clock and reset signals in its sensitivity list of inputs.

Figure 4.3 State Diagram for TEA Implementation

The symbol >> is used to indicate right shift and symbol << is used to indicate left shift respectively. Beginning with the initialization (*init* state) where all intermediate values are properly initialized, including key and input data values. The next state (*updatesum*) keeps track of the number of rounds (if less than 32) proceeds to the next state (*fourbitLSZ*) else moves to the state *done*. State *fourbitLSZ* performs a 4-bit left shift of the 32-bit LSB (Z). The next state, *LshiftZk0* calculates ((Z << 4) + k[0]) where k[0] is a 32-bit MSB of the 128 bit key. After this, the state *fivebitRSZ* performs a 5-bit right shift operation of Z and the state machine transits to the next state *RshiftZk1* that calculates ((Z >> 5) + k[1]). The next state *CalcY* computes the term L = ((Z << 4) + k[0]) + (Z + sum) + ((Z >> 5) + k[1]), where L is an intermediate register used as a buffer. Following this calculation the state *UpdateY* evaluates

$Y \mathrel{+}= ((Z \mathrel{<\!\!\!\!<} 4 + k[0]) \oplus (Z + sum) \oplus (Z \mathrel{>\!\!\!\!>} 5 + k[1]))$

or Y = Y+L in accordance with the TEA encryption source code. The *newY* state updates the newly calculated value of Y to be carried forward in the next round of encryption. This completes the first round.

The second round of the encryption algorithm, begins with the state *fourbitLSY* which calculates 4-bit left shifted value of Y. State *LshiftYk2* computes ((Y << 4) + k[2]). This is followed by *fivebitRSY* which performs a 5-bit right shift operation on Y. State *RshiftYk3* determines ((Y >> 5) + k[3]). *CalcZ* is the next state in sequence that estimates the value of R, where R is a temporary register used to store the value of R = ((Y << 4) + k[2]) + (Y + sum) + ((Y >> 5) + k[3]). The next state (*UpdateZ*) assess the value of the following,  $Z += ((Y << 4) + k[2]) \oplus (Y + sum) \oplus (Y >> 5 + k[3])$ ) where Z = Z + R. *newZ* is the next state in sequence *checkrounds* checks if 32 cycles are completed based on a counter. If so, it moves to the *delay* state otherwise it transits to the *updatesum* state to begin the next set of rounds in the cycle. The purpose of the *delay* state is to ensure enough time for the output to stabilize before it can be passed to the decryptor entity and consumes only one extra clock cycle. This completes the encryption cycle.

The decryption is implemented and tested in two ways. The first is the hardware approach using VHDL similar to the encryption implementation. This approach also utilizes 18 states in a finite state machine (FSM) to perform all the operations mentioned earlier, in the reverse order. The reason for so many states between different calculations is to ensure that the all values are updated at the rising edge of the clock cycle. The second implementation that has been accomplished is a software approach using Altera Nios II IDE. This is relatively simple to execute since the source code is readily available [27], [30]. It must be noted that the code is implemented using small C library in order to minimize the memory footprint for the FPGA platform (Altera NIOSII).

28

## 4.5 Testing and Verification Results

One of the first steps in testing the functionality of the circuit is verification using waveforms. Active HDL 7.1 provides a simple method of applying stimulus to input vectors by using a macro file (source code in Appendix) which basically defines the clock frequency, assertion of reset and duration of the simulation. The clock frequency used is 2 MHz i.e. 500 ns clock period. For example, an input of 0x0123456789abcdef (64 bits) is provided and the encrypted value received after 32 rounds (~1090 clock cycles) is 0x126CB92C0653A3E. The key value used is 0x00112233445566778899aabbccddeeff (128 bits). The encryption cycle proceeds through an FSM as described in section 4.4 and results shown in Figure 4.4. A zoomed-out version of the process presented is (first 9 rounds) in Figure 4.5. Every signal can be monitored and internal counters (counter and counter1) are employed for the left and right shift operations.

| Name                         | Value     | S 1 0,5 1 . | 1 1020 05 1 . 2 . 1 2 | 5 1 - 3 - 1 3,5 1 - 4 | . 1 4,5 1 . 5 . 1 5,5 1 . 6 . | . 6,5 7 7,5 8 . |

|------------------------------|-----------|-------------|-----------------------|-----------------------|-------------------------------|-----------------|

| <b>⊳</b> clk                 | 0         |             |                       |                       |                               |                 |

| ⊞ # delta_copy               | 9E3779B9  |             | 3779B9                |                       |                               |                 |

| <b>.</b> • • k0              | 00112233  |             | 112233                |                       |                               |                 |

|                              | 44556677  |             | 556677                |                       |                               |                 |

| <b>∓</b> № k2                | 8899AABB  |             | 99AABB                |                       |                               |                 |

|                              | CCDDEEFF  |             | CODEEFF               |                       |                               |                 |

| nr State                     | updatesum | (init )     | XfourbitIsz           | Xterm1                | Xfivebitrsz                   | Xterm2 Xterm3   |

| 🛨 🗚 Ishiftedz                | 00000000  | (00000000   |                       | X                     | X9ACE0123                     |                 |

| 🛨 📭 rshiftedz                | 00000000  | (00000000   |                       |                       |                               | χ X48A2C        |

| ± ™ Ishiftedy                | บบบบบบบบ  | (0000000    |                       |                       |                               |                 |

| 🛨 🕫 rshiftedy                | บบบบบบบบ  |             |                       |                       |                               |                 |

| E νιΓ                        | 00000000  | (00000000   |                       |                       |                               |                 |

| <b>Ξ</b> <sup>™</sup> Β      | 00000000  | (00000000   |                       |                       |                               |                 |

| <b>∓</b> <sup>∎</sup> rounds | 0         | 0           | X                     |                       |                               |                 |

| Ξ u Y                        | 01234567  | (01234567   |                       |                       |                               |                 |

| E N Z                        | 89ABCDEF  | (89ABCDEF   |                       |                       |                               |                 |

|                              | 00000000  | (00000000   |                       |                       |                               |                 |

|                              | 00000000  | (00000000   |                       |                       |                               |                 |

Figure 4.4 TEA Simulation waveform illustrating transition of states

| Name            | Value      | 5 · · 10 · · · 20 · · · 30 · · · 40 · · · 50 · · · 60 · · · 70 · · · 80 · · · 90 · · · 100 · · · 110 · · · 120 · · 130 · · · 140 · · · 150 |

|-----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| ₽ clk           | 1          |                                                                                                                                            |

| H M deka_copy   | 9E3779B9   | K9E3779B3                                                                                                                                  |

| ₩ State         | fivebitrsz |                                                                                                                                            |

| 🕀 🗸 sum         | 2E2AC13A   | (39E3779B9 X3C6EF372 XDAA66D2B X78DDE6E4 X1715609D XB54CDA56 X5384540F XFIBBCDC8 X8FF34781                                                 |

| AT rounds       | 10         | K1 X2 X3 X4 X6 X6 X7 X8 X9                                                                                                                 |

| E Ar counter    | 0          | Carlo alto alto alto alto alto alto alto al                                                                                                |

| T Ar counter1   | 0          | a ka                                                                                                   |

| ∃ # Ishiftedz   | 100968F3   | (X3ACE0123 X06CC3803 X3FAIC243 X730A4AF3 XFFF76763 XFF9EB303 X00BCIEF3 X299971D3 X8F9H2F3                                                  |

| + Jur rshiftedz | 4A1D2687   | X48A2C4E6 X4640C400 X48752EC7 X4A0EE30B X49558999 X4AD52D3F X4ABDBBF5 X4A6A2A9E X4A1D2687                                                  |

| + Ar Ishiftedy  | C4529FCB   | UUUUUUUXF3C627FB X692B7FEB X10E53A6B XAE8242EB XC9A1E38B XCA84B97B X736F274B XEDOFC03B XC452                                               |

| T ar rshiftedy  | CFFBCB79   | ишиши хонзэвэр хозоезтез хорзено хортоезне хортегне хоереене хонозено хозово хозово хо                                                     |

| ¥) M L          | 8D672DF9   | XF58F826D XE956557F X294B9BA8 X0909D088 X01B1FA0A X000E2D5F XBA8EA6DD XD7A7098F X8D672DF                                                   |

| + M R           | F8078260   | UUUUUUU XB3BFE34B X468D58C7 X3336888B XE8CED1C7 X2FFA74BA XFD11D6BF XF56DD52E XF65F7D12 X1                                                 |

| ŧ) ar Y         | 638B8F51   | XF6B2C7D4 XE0091D53 X0954B9FB X125E8983 X1410838D X44EB0EC XFEAD57C9 XD6546158 X63BB8F1                                                    |

| T N Z           | BOFF846C   | (69ABCDEF X3D6BB13A X83F90A01 XB72F928C X9FFE6453 XCFF8D90D XCD0AAFCC XC29884FA XB8F8020C X                                                |

Figure 4.5 TEA Simulation - First 9 rounds of encryption cycle

After 32 rounds the output produced can be seen in Figure 4.6 as  $encrypt\_outputMSB\_Y$  and  $encrypt\_outputLSB\_Z$ . For the purpose of testing the correctness of the encryption, after the output 0x126CB92C0653A3E is obtained it is passed on to the decryption module. If the output retrieved is the original plaintext, then this confirms the functionality of the encryption module. This is verified as shown in Figure 4.7. It is observed that after around 1090µs the output is the same as the input i.e. 0x123456789abcdef.

| ▲ State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | delay    |                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|

| ± <sup>™</sup> lshiftedz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51BB92F3 | Жезбегота Жбагеангоз Жлаеобада Жбтөвөргүз Жбтөвөргүз Жлаеобада Жбагеа    |

| Image: The second s | 447E3BAF | X4C470CF5 X46FEDD00 X4692CE0F X447E3BAF X447E3BAF X4692CE0F X46          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AF6063DB | C6B X963DCFBB X6136170B X1298ECDB X XAF6063DB X1298ECDB X5136170B        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CD715258 | B99B67 XCDE4C111 XD4423D35 XCEA2EEA0 X XCD71525B XCEA2EEA0 XD4423D35     |

| ⊞ n. Γ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D9CC7770 | X4564B535 XCBAF8475 X4C162D5D X XBB4A9332 XBD6DB3F2 XF27E204D            |