610012175

# AREA-DELAY DRIVEN LIBRARY-FREE SYNTHESIS

by

## MATTHEW PULLERITS

B.A.Sc., Queen's University, 2005

A thesis presented to Ryerson University in partial fulfillment of the requirement for the degree of Master of Applied Science in the Program of Electrical and Computer Engineering.

Toronto, Ontario, Canada, 2008

© Matthew Pullerits, 2008

#### PROPERTY OF RYERSON UNIVERSITY LIBRARY

## Author's Declaration

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Matthew Pullerits

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Matthew Pullerits

## Instructions to Borrowers

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

| Name | Signature | Address | Date |

|------|-----------|---------|------|

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

### Abstract

#### AREA-DELAY DRIVEN LIBRARY-FREE SYNTHESIS Matthew Pullerits M.A.Sc. Ryerson University, 2008

Current logic synthesis tools rely on pre-defined cell libraries to assemble an arbitrary circuit to perform a needed function. The efficiency of the synthesized circuit relies on the quality and size of the library used in terms of circuit area and critical path delay. It has been shown that in a process supporting five serial NMOS and PMOS transistors, 425803 unique logic gates may be constructed. Clearly this is beyond what is currently available in standard cell libraries.

A richer cell library allows the technology mapper more freedom to better select matches to reduce area, delay and power consumption. This thesis proposes novel algorithms for mapping an input netlist to a library of virtual cells by minimizing logical effort delay, and gate input capacitance to select an architecture which minimizes the design areadelay. An average 69.43% reduction in transistor count, 53.33% reduction in circuit area, with a 3.76% increase in delay has been realized compared to results obtained from Synopsys Design Compiler with high map effort for delay minimization.

### Acknowledgements

Firstly, I would like to thank my supervisor, Dr. Adnan Kabbani for his help and support during my research. His direction and guidance was always appreciated.

I would like to thank my parents, sister, and grandfather for always looking out for my best interest. They supported me, and were patient during my struggles and mistakes.

Lastly, my friends Raymond, Dennis, Adrian, and Edwina who understood when I needed to focus on studying, and were always there to help me.

# Table of Contents

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vii |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   |

| 1.1 Integrated Circuit Design Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 1.2 Logic Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 1.3 Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 1.4 Main Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 1.5 Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 2. LIBRARY-BASED LOGIC SYNTHESIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5   |

| 2.1 Decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 2.2 Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 2.3 Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 2.3.1 Structural Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 2.3.1.1 Simple Tree-Based Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 2.3.1.2 String Matching with Multiple Base Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 2.3.2 Boolean Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 2.3.2.1 Input Permutation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 2.3.2.2 Input Permutation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 는 [11] 중 방법은 것은 것을 통과하는 것 것, 이 특징 방법은 가격 것 같아요. 같은 것 같아요. 이 가격 것은 것은 것 같아요. 한 것은 것 같아요. 한 것 같아요. 이 것 같아요. 이 것 같아요. 이 가 가격 것 같아요. 이 있는 것 같아요. 이 것 않아요. 이 것 같아요. 이 있다. 이 것 같아요. 이 한 것 같아요. 이 있다. 이 것 같아요. 이 이 것 같아요. 이 이 것 같아요. 이 이 것 같아요. 이 이 이 것 같아요. 이 이 이 이 이 이 이 이 이 이 이 이 이 이 이 이 이 이 이 |     |

| 2.3.2.3 Output Negation<br>2.3.2.4 Boolean Signatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 2.3.2.5 Canonical Representations of Boolean Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 2.4 Covering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 2.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21  |

| 3. LIBRARY-FREE TECHNOLOGY MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22  |

| 3.1 Previous Studies in Library-Free Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23  |

| 3.2 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 4. PROPOSED SYNTHESIS ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28  |

| 4.1 Logical Effort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28  |

| 4.1.1 Estimating Gate Area with Input Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 4.2 Fast Boolean Matching of Complex Gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 4.3 Complex Gate Generation and Indexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32  |

| 4.3.1 Complex Gate Library Population                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33  |

| 4.3.2 Permutations of Order and Complementation of Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 4.3.2.1 Input Tracking in P-Canonical Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40  |

| 4.3.2.2 Input Tracking in NP-Canonical Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 4.3.3 CMOS Transistor Logic Solver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43  |

| 4.3.4 CMOS Gate Skewing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4.3.5 NMOS Network Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 4.3.5.1 NMOS Generation – Dependency on Library Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 4.4 Proposed Boolean Tree Matching                           | 52 |

|--------------------------------------------------------------|----|

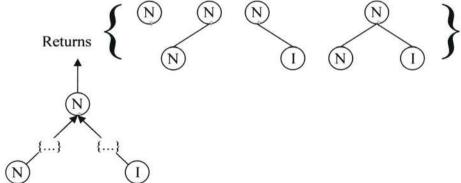

| 4.4.1 Sub-tree Extraction                                    |    |

| 4.4.2 Matching Algorithm                                     |    |

| 4.4.3 Boolean Logic Solver                                   |    |

| 4.5 Proposed Covering Algorithm                              |    |

| 4.5.1 Minimizing Logical Effort Delay                        |    |

| 4.5.2 Minimizing Circuit Area                                |    |

| 4.6. Summary                                                 | 63 |

| 5. IMPLEMENTATION                                            | 64 |

| 5.1 Synthesis Process Overview                               | 64 |

| 5.1.1 Input Parsing and DAG Storage                          | 64 |

| 5.1.2 Partitioning                                           |    |

| 5.1.3 Memory Management                                      |    |

| 5.1.4 Timing Restrictions during Sub-tree Extraction         |    |

| 5.1.5 User Interface and Result Presentation                 |    |

| 5.1.6 Automated Verification of Results                      |    |

| 5.2 Summary                                                  | 74 |

| 6. RESULTS                                                   |    |

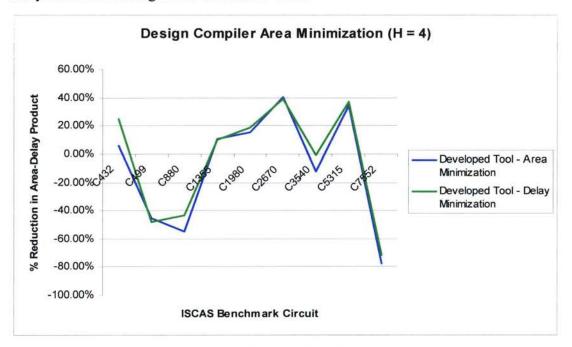

| 6.1 Design Compiler Area Minimization                        |    |

| 6.1.1 DC vs. Developed Tool Area Minimization (H = 4)        |    |

| 6.1.2 DC vs. Developed Tool Delay Minimization (H = 4)       |    |

| 6.1.3 DC vs. Developed Tool Area Minimization (H = 100)      |    |

| 6.1.4 DC vs. Developed Tool Delay Minimization (H = 100)     | 81 |

| 6.1.5 Comparison of Synthesis Algorithms                     |    |

| 6.2 Design Compiler Delay Minimization                       |    |

| 6.2.1 DC vs. Developed Tool Delay Minimization (H = 2)       | 84 |

| 6.2.2  DC vs. Developed Tool Area Minimization (H = 2)       |    |

| 6.2.3 DC vs. Developed Tool Delay Minimization ( $H = 4$ )   |    |

| 6.2.4  DC vs. Developed Tool Area Minimization (H = 4)       |    |

| 6.2.5 DC vs. Developed Tool Delay Minimization ( $H = 16$ )  |    |

| 6.2.6  DC vs. Developed Tool Area Minimization (H = 16)      |    |

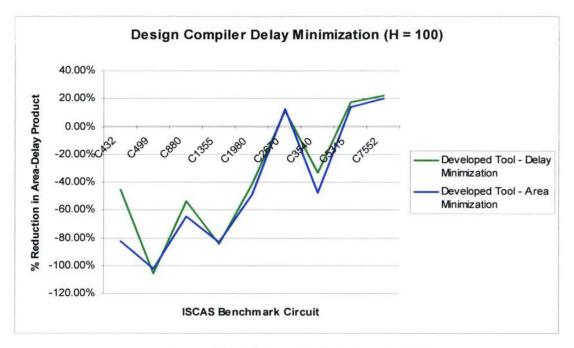

| 6.2.7 DC vs. Developed Tool Delay Minimization ( $H = 100$ ) |    |

| 6.2.8 DC vs. Developed Tool Area Minimization (H = 100)      |    |

| 6.2.9 Comparison of Synthesis Algorithms                     |    |

| 2.3 Summary                                                  | 96 |

| 7. CONCLUSIONS AND FUTURE WORK                               | 97 |

| 8. REFERENCES                                                | 99 |

# List of Figures

| Figure 2-1. Single-Fanout Partitioning                                            | 6    |

|-----------------------------------------------------------------------------------|------|

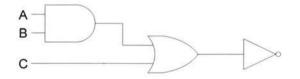

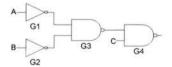

| Figure 2-2. Gate representation of function $f=(ab + c)$ '                        | 7    |

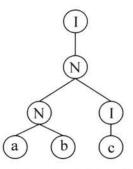

| Figure 2-3. Tree decomposition of function f=(ab + c)' into NAND & Inverter gates | 8    |

| Figure 2-4. MATCH Algorithm                                                       | 9    |

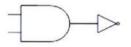

| Figure 2-5. AND function                                                          | 9    |

| Figure 2-6. AND pattern tree. Inverter = White, NAND = Black, Input = Grey)       | 9    |

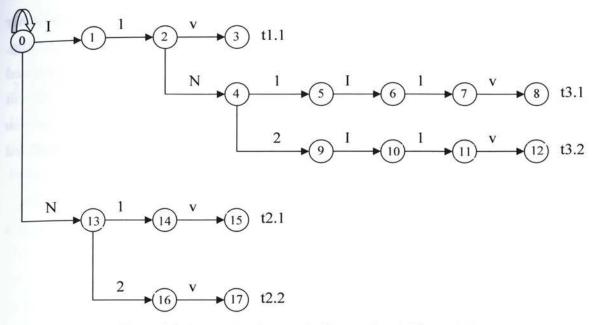

| Figure 2-7. Pattern trees, strings, tree identifiers for 3 common library cells   | . 11 |

| Figure 2-8. Automation for sample library given in Figure 2-7                     | . 12 |

| Figure 2-9. Comparisons of two Boolean functions                                  |      |

| Figure 2-10. Truth table permutations                                             |      |

| Figure 2-11. Transformations due to reordering of input variables                 | . 17 |

| Figure 2-12. Transformations due to reordering and inversion of input variables   |      |

| Figure 2-13. Number of NP-equivalents vs. number of input variables               | .18  |

| Figure 2-14. Complete Link Table for 3-input function                             | .18  |

| Figure 2-15. Sample Covering                                                      | .20  |

| Figure 2-16. Alternative Covering                                                 | 20   |

| Figure 2-17. Alternative Covering                                                 |      |

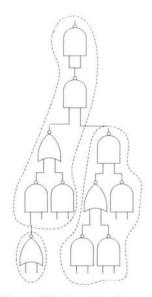

| Figure 3-1. Gate combinations possible with series NMOS & PMOS transistors        | 23   |

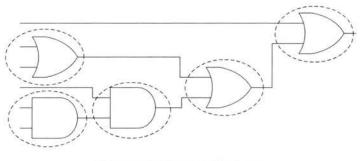

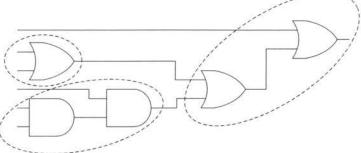

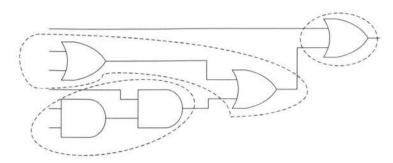

| Figure 3-2. Possible Cover                                                        | 24   |

| Figure 3-3. Alternate Cover                                                       | 25   |

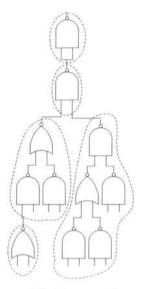

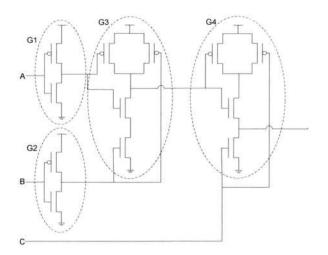

| Figure 3-4. Simple Circuit for OTR Example                                        | 25   |

| Figure 3-5. Transistor-level representation of Figure 3-4                         |      |

| Figure 3-6. Intermediate transformation of OTR method                             | 26   |

| Figure 3-7. Final transformation of OTR method: Resultant complex gate            | 27   |

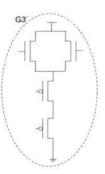

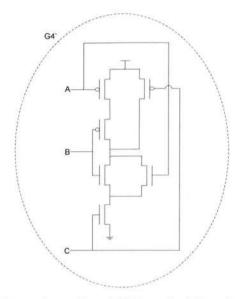

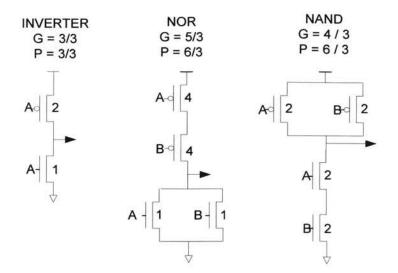

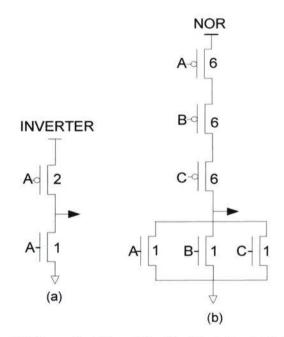

| Figure 4-1. Logical Effort of Simple Gates                                        | 30   |

| Figure 4-2. Example of Transistor Size Variation in Gates                         | 31   |

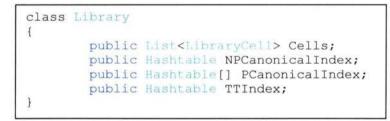

| Figure 4-3. Library Cell Data Structure                                           | 33   |

| Figure 4-4. Library Data Structure                                                | 33   |

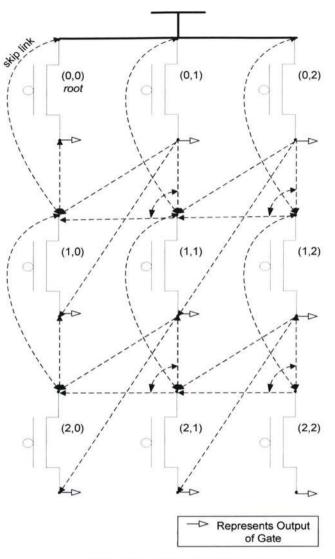

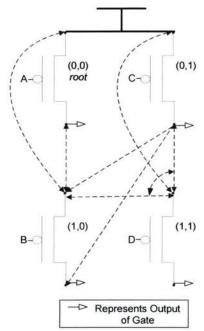

| Figure 4-5. 3x3 Generation Matrix                                                 | 35   |

| Figure 4-6. 2x2 Generation Matrix                                                 | 36   |

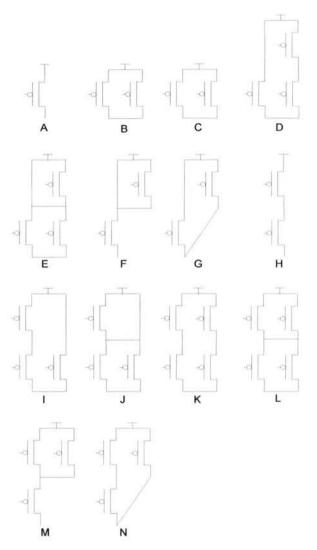

| Figure 4-7. Gates Extracted from 2x2 Generation Matrix                            |      |

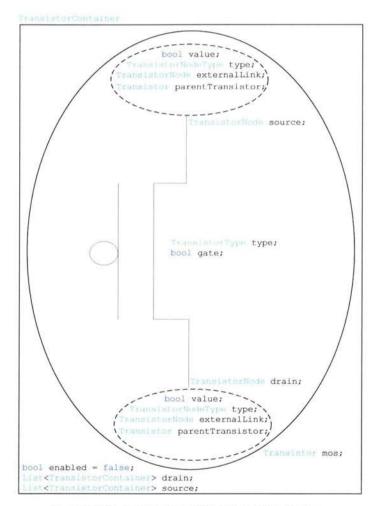

| Figure 4-8. Transistor Container Data Structure                                   | 38   |

| Figure 4-9. Transistor Data Structure                                             | 38   |

| Figure 4-10. Transistor Node Data Structure                                       | 39   |

| Figure 4-11. Hierarchy of the Transistor classes.                                 |      |

| Figure 4-12. Reference Truth Table for NP-Canonical Generation                    | 41   |

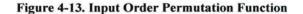

| Figure 4-13. Input Order Permutation Function                                     |      |

| Figure 4-14. Input Inversion Algorithm                                            |      |

| Figure 4-15. Sample Input Permutation & Minterm Positions                         |      |

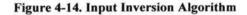

| Figure 4-16. Sizing for equal rise & fall times in CMOS gates                     |      |

| Figure 4-17. Gate generated from 4x4 Generation Matrix                            |      |

| Figure 4-18. Gate Generated from 4x4 Matrix with 6 Series Transistors             |      |

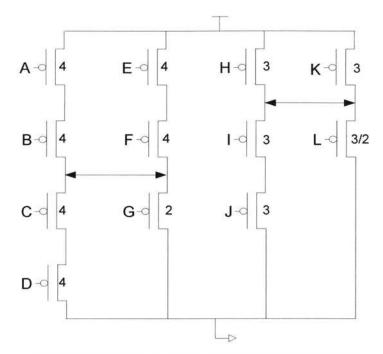

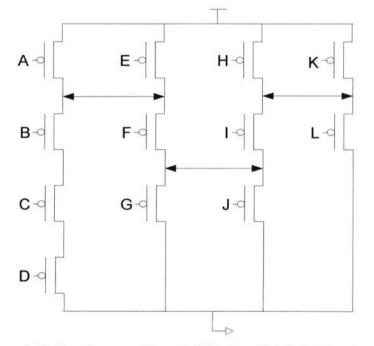

| Figure 4-19. Generating NMOS Network from PMOS Structure                          | 48   |

| Figure 4-20. Truth Table for NOR Gate                                           |      |

|---------------------------------------------------------------------------------|------|

| Figure 4-21. Truth Table for NAND Gate                                          | . 49 |

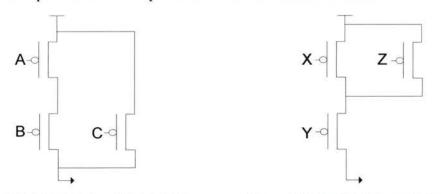

| Figure 4-22. PMOS Network f=!(A+B)C                                             |      |

| Figure 4-23. PMOS Network f=!(XZ+Y)                                             | . 50 |

| Figure 4-24. Generated Truth Tables & P-canonical form of Figure 38             | . 51 |

| Figure 4-25. Generated Truth Tables & P-canonical form of Figure 39             | . 51 |

| Figure 4-26. Extracted Sub-trees from Sample Graph                              | . 52 |

| Figure 4-27. Proposed sub-tree extraction method                                | . 54 |

| Figure 4-28. Proposed Boolean tree matching algorithm                           | . 55 |

| Figure 4-29. Recursive Boolean logic solver pseudo code                         | . 56 |

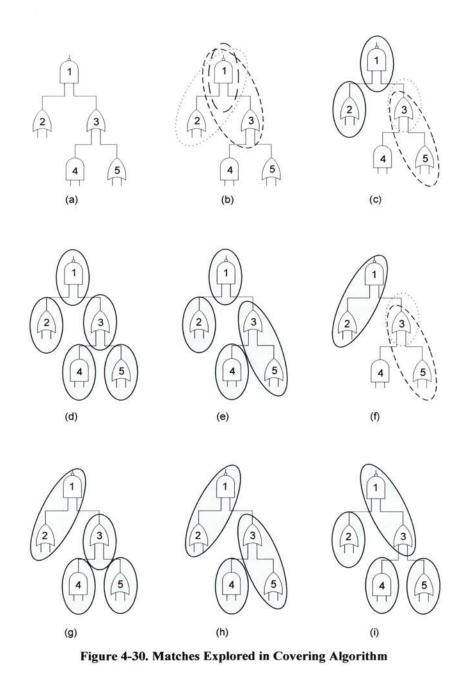

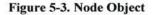

| Figure 4-30. Matches Explored in Covering Algorithm                             | . 58 |

| Figure 4-31. Gate Transformations through Boolean Matching                      | . 59 |

| Figure 4-32. Proposed logical effort delay minimizing covering algorithm        | . 60 |

| Figure 4-33. Proposed area minimizing covering algorithm                        |      |

| Figure 5-1. Simple Example of BENCH Code                                        |      |

| Figure 5-2. Boolean Representation of BENCH Code in Figure 5-1                  |      |

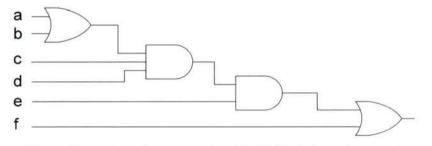

| Figure 5-3. Node Object                                                         |      |

| Figure 5-4. Partition Object                                                    |      |

| Figure 5-5. LibraryMatch Object                                                 | . 68 |

| Figure 5-6. Configuration Tab of Synthesis Tool                                 | . 69 |

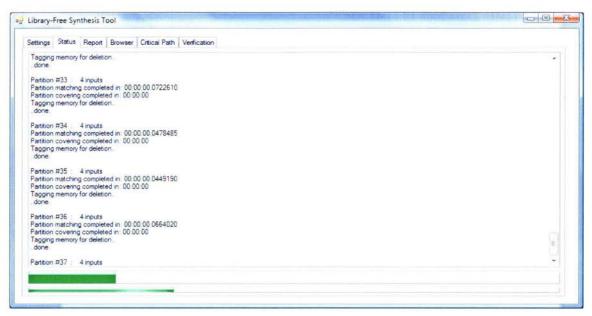

| Figure 5-7. Status of Synthesis Process                                         | . 70 |

| Figure 5-8. Sample Report Generated by Synthesis Tool                           | . 71 |

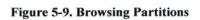

| Figure 5-9. Browsing Partitions                                                 | . 72 |

| Figure 5-10. Display of Matching Library Cell                                   |      |

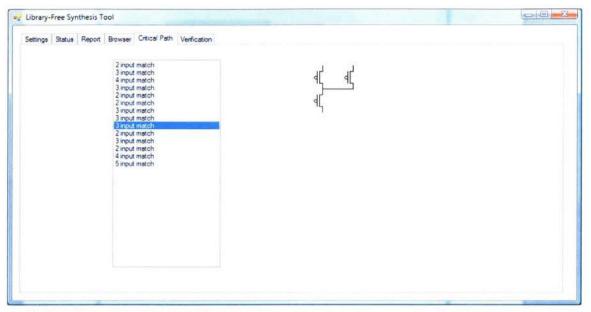

| Figure 5-11. Display of Critical Path                                           | . 73 |

| Figure 5-12. Result of Automated Verification                                   | . 74 |

| Figure 6-1. ISCAS'85 Benchmark Circuits                                         |      |

| Figure 6-2. DC Area Minimization vs. Developed Tool Area Minimization - H=4     |      |

| Figure 6-3. Design Compiler vs. Developed Tool △ Area-Delay Product             | . 78 |

| Figure 6-4. DC Area Minimization vs. Developed Tool Delay Minimization - H=4    | . 79 |

| Figure 6-5. DC vs. Developed Tool △ Area-Delay Product (Area vs. Delay)         | . 79 |

| Figure 6-6. DC Area Minimization vs. Developed Tool Area Minimization - H=100   | . 80 |

| Figure 6-7.DC vs. Developed Tool ∆ Area-Delay Product (Area vs. Area)           | . 80 |

| Figure 6-8. DC Area Minimization vs. Developed Tool Delay Minimization - H=100  |      |

| Figure 6-9. DC vs. Developed Tool △ Area-Delay Product (Area vs. Delay)         | . 81 |

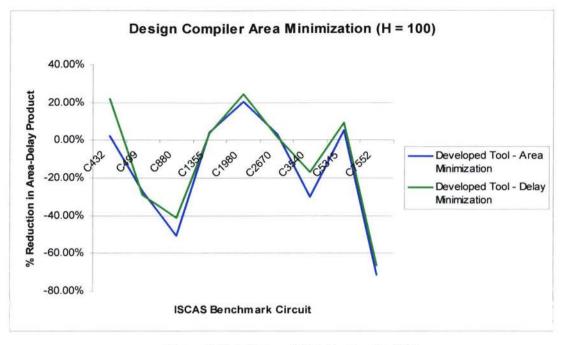

| Figure 6-10. DC Area Minimization (H=4)                                         | . 82 |

| Figure 6-11. DC Area Minimization (H=100)                                       |      |

| Figure 6-12. DC Delay Minimization vs. Tool Delay Minimization - H=2            | . 85 |

| Figure 6-13. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Delay)       |      |

| Figure 6-14. DC Delay Minimization vs. Tool Area Minimization - H=2             | . 86 |

| Figure 6-15. DC vs. Developed Tool ∆ Area-Delay Product (Delay vs. Area)        | . 86 |

| Figure 6-16. DC Delay Minimization vs. Tool Delay Minimization - H=4            | . 87 |

| Figure 6-17. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Delay)       | . 87 |

| Figure 6-18. DC Delay Minimization vs. Tool Area Minimization - H=4             | . 88 |

| Figure 6-19. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Area)        | . 88 |

| Figure 6-20. DC Delay Minimization vs. Developed Tool Delay Minimization - H=16 | 89   |

| Figure 6-21. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Delay)          |

|------------------------------------------------------------------------------------|

| Figure 6-22. DC Delay Minimization vs. Tool Area Minimization - H=16               |

| Figure 6-23. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Area)           |

| Figure 6-24. DC Delay Minimization vs. Tool Delay Minimization - H=100             |

| Figure 6-25. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Delay)          |

| Figure 6-26. DC Delay Minimization vs. Developed Tool Area Minimization - H=100 92 |

| Figure 6-27. DC vs. Developed Tool △ Area-Delay Product (Delay vs. Area)           |

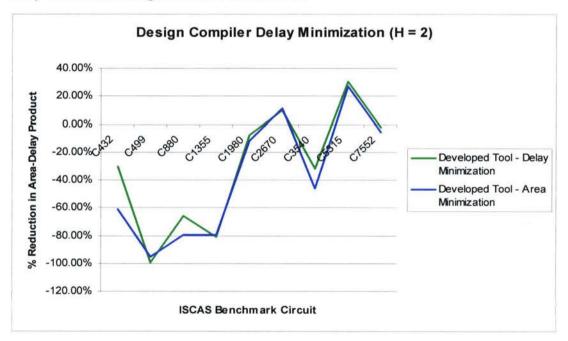

| Figure 6-28. DC Delay Minimization (H=2)                                           |

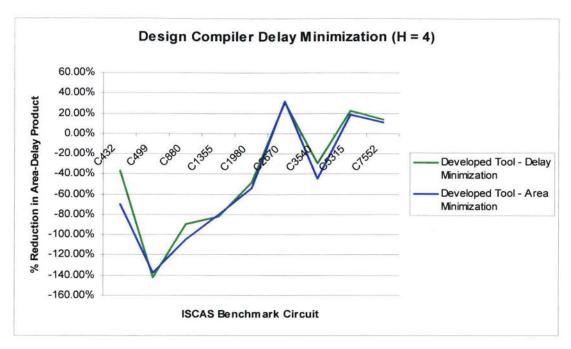

| Figure 6-29. DC Delay Minimization (H=4)                                           |

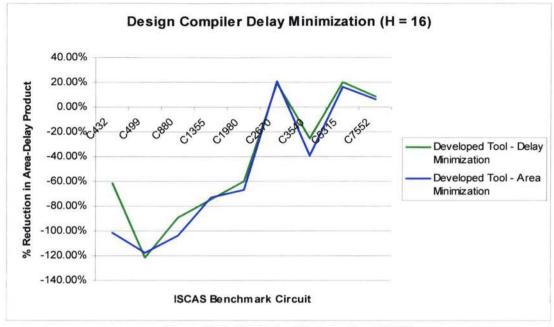

| Figure 6-30. DC Delay Minimization (H=16)                                          |

| Figure 6-31. DC Delay Minimization (H=100)                                         |

## 1. Introduction

## 1.1 Integrated Circuit Design Techniques

Since the inception of the integrated circuit in April of 1961 by Robert Noyce [1], the technology has rapidly evolved to a level where every aspect of our lives is driven by computer chips – from health care to national defense.

Application Specific Integrated Circuits (ASICs) in production today are composed of a few, to a few hundred million transistors, depending on the intended task of the chip. Transistors are composed of interconnected layers of silicon, metal (most commonly used metals are aluminum or copper), and insulator (most commonly used is  $SiO_2 - glass$ ). These ASICS may be manufactured with many interconnecting layers of metal, giving a total metal layer count in the chip of six in a 0.06µm process [2]. Individual layers are separated, and "mask layouts" are created for each layer to be produced. These mask layouts are the final step in ASIC design, and are directly used in production of the chip.

ASICs are currently produced in one of three ways: Full Custom, Fully Automatic, and Semi-Custom. In a full custom process, design engineers draw the final mask layout of the circuit to be produced using computer aided design (CAD) software. This allows the engineer to customize every aspect of the chip in regards to transistor sizing for optimal power consumption, delay, or area specifications. As modern integrated circuits may contain around 1-billion transistors, a full custom design although would result in the most optimal product with respect to speed or power consumption, is not always possible or practical due to time or budget constraints.

In a fully automatic process, circuits to be produced are defined in a high level hardware description language (HDL) such as Verilog, VHDL, or SystemC. Using these languages, a design engineer may describe their circuit in a manner similar to that of a computer

program, making use of programming techniques such as while loops, for loops, and custom data structures. Once a circuit is defined in a HDL, it may be synthesized to a production-ready mask layout easily with currently available synthesis tools, such as Synopsys Design Compiler, or the Berekley-made SIS. Relative to a fully custom design, usage of HDLs may allow for time-savings of many orders of magnitude. This is a great economic savings for the design firm with respect to engineering time required to develop a production-ready circuit.

Although synthesis allows for a great savings of time to produce a functional ASIC, current CAD tools are not able to produce circuits which are optimal with respect to area and delay. On occasion it is necessary to produce a semi custom design, in which a layout obtained from HDL synthesis is modified to conform to required design specifications.

## 1.2 Logic Synthesis

Logic synthesis is the process of converting a circuit described in a hardware definition language into a netlist of gates, which may be made to a layout ready for fabrication. Synthesis tools today rely on libraries of pre-defined cells which are used to construct the circuit. These cells act as building blocks which can be connected to produce a desired function.

Cell libraries have played an important role in logic synthesis for the past three decades. They have allowed engineers to quickly utilize these pre-designed building blocks to assemble and fabricate an arbitrary circuit to perform a needed function. While convenient, these library files require significant investment in engineering time to develop and maintain for every generation of technology process.

The efficiency of the synthesized circuit relies heavily on the quality and size of the library used [3]. However, creating rich cell libraries to facilitate the continued demand for faster, smaller, and more complex ASICs is not economically permissible. As such, many of the advances in deep sub-micron fabrication are not being fully utilized by implementing functions in complex gates [4]. It has been shown that in a technology

process capable of supporting five serial NMOS and PMOS transistors, 425803 unique logic gates may be constructed [5]. Clearly this is beyond what is currently available in standard cell libraries. A synthesis tool which is able to dynamically generate library cells during the synthesis process, rather than relying on a pre-constructed cell library, is able to much better utilize resources inside the ASIC by generating a complex gate where previously many smaller library cells would have to be used. These resources being minimized may include transistor count, silicon area, power consumption, or critical path delay.

## 1.3 Objectives

- To develop library-free synthesis algorithms which:

- o Has a complexity similar to current state-of-the-art synthesis tools

- Minimizes the power consumption and delay. Since it is well known power dissipation is proportional to the design area, this objective can be achieved by minimizing the area-delay product.

- Guarantees the consistency of the quality of the synthesized design by ensuring a) independence from the initial decomposition of the circuit, and b) absolute logic minimization

- To develop a CAD tool which implements the proposed algorithms in a high level language such as C or C++

## 1.4 Main Contributions

This thesis proposes novel synthesis algorithms for use in library-free synthesis. Using this technique allows the direct production of a transistor netlist of the design, as opposed to the cell-based synthesis method. The proposed technique is independent of the initial decomposition which improves the overall area-delay product. Finally, the developed synthesis algorithms will generate circuits which are not tied to any particular technology process, allowing inexpensive portability between processes.

## 1.5 Thesis Organization

The remainder of this document is organized as follows. An overview of library-based logic synthesis is presented in chapter 2. Chapter 3 reviews the theory of library-free logic synthesis and previous works in this area. Chapter 4 presents the proposed library-free logic synthesis algorithms. Implementation details are outlined in chapter 5. Experimental results obtained from executing the developed tool with benchmark circuits, and comparisons against industry standard synthesis tools is presented in chapter 6. Finally, conclusions and room for future work is discussed in chapter 7.

## 2. Library-Based Logic Synthesis

A cell library contains a set of pre-constructed mask layouts of logic functions which are ready for fabrication on a specific technology process. These logic functions range from simple gates such as Inverters, NANDs or NORs, to complex adders and registers. Accurate area and timing information is available for these cells, as well as various sizes of these gates in order to drive different loads.

Logic synthesis is a conversion process which translates a gate level representation of an HDL into a layout ready for further processing such as power planning for production on a particular technology using pre-characterized cells from the cell library. This process can be broken down into four unique steps: decomposition, partitioning, matching, and covering.

## 2.1 Decomposition

During the technology independent stage of logic minimization, functions are decomposed in to a network of base functions. These base functions could be a set of two input NAND, NOR and Inverter gates. Decomposition allows for a complex circuit to be broken down into smaller gates which are easier to analyze and synthesize [6]. While the structure of the circuit is modified during decomposition, the functionality is maintained. At minimum, the target technology cell library must contain the set of base functions decomposed to, in order to guarantee a complete covering.

## 2.2 Partitioning

Boolean networks may be represented as directed acyclic graphs (DAGs) with vertices representing Boolean functions, and edges representing connections, or wires. It has been shown [7] that network partitioning into trees is an essential heuristic step in the technology mapping process, as there is currently no algorithm to optimally cover a DAG

in polynomial time<sup>1</sup>. Many studies have been conducted on the complexity of covering a DAG, resulting in the conclusion that the problem is NP-hard [8]. As complex Boolean networks may contain thousands or potentially millions of functions, each with at least one, and in most cases, more than one covering, a solution is beyond the capabilities of covering tools. In order to solve the covering problem in a practical amount of time, heuristics must be applied to simplify the problem. One such heuristic is partitioning the DAG into singly-rooted trees [7] [9]. Partitioning serves two purposes: first it simplifies the covering problem so that each network being covered is smaller. Second, by this simplification, partitioning enables the covering problem to become practical. It has been shown that although the covering problem is intractable, computation time is reasonable for problems of practical size [10].

It should be noted that partitioning of a Boolean network serves as a heuristic step, and although simplifies the computation of an optimal covering, will hinder the quality of the overall result.

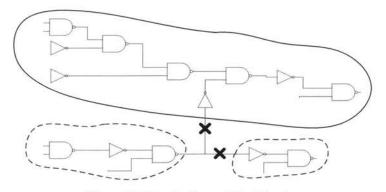

Singe-rooted trees may be partitioned by traversing the network from primary outputs to primary inputs, creating a new partition for every primary output, or for any multiple fanout traversed. Figure 2-1 illustrates the partitions obtained by traversing from outputs to inputs, with X's marking partition locations.

Figure 2-1. Single-Fanout Partitioning

<sup>&</sup>lt;sup>1</sup> Although numerous algorithms have been proposed to cover a DAG, all implement some sort of heuristic [8] [39] [24] [40] to execute within an acceptable time frame.

## 2.3 Matching

Matching can be broken down into two flavors: structural matching and Boolean matching [11]. Structural matching analyzes a decomposed, partitioned circuit as a graph, and searches for matching patterns in the cell library. Boolean matching looks at the logic *function* being accomplished by the circuit, and seeks similar functions or permutations of functions in the cell library by comparing the Boolean truth tables of the functions.

#### 2.3.1 Structural Matching

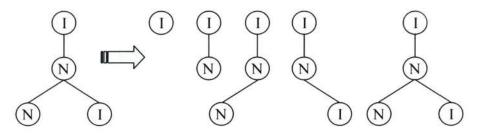

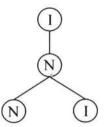

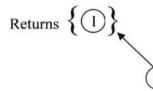

After partitioning, the original DAG will have been broken into a forest of trees. Each individual tree is called a *subject graph* [7], with edges representing wires, or connections between gates, and vertices representing logic functions. A root node is defined as the output of the function, or the node which all other nodes lead to. A child node is defined as a node which stems from another node at a higher level. Leaf nodes are always inputs to the subject graph, and are the lowest-level child nodes. These subject graphs contain multiple inputs, but only a single output.

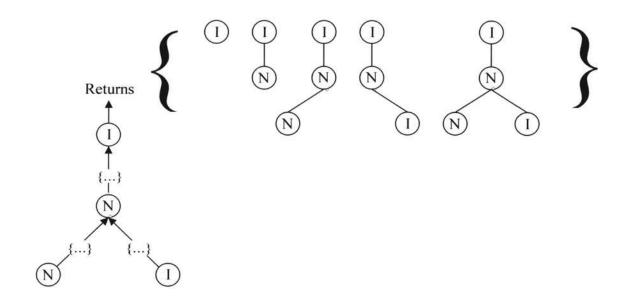

For example, consider the Boolean network illustrated in Figure 2-2, representing the function  $f = \overline{ab + c}$ .