# ARCHITECTURE SYNTHESIS METHODOLOGY FOR RUN-TIME RECONFIGURABLE MULTI-TASK AND MULTI-MODE SYSTEMS WITH SELF-ASSEMBLING MICRO-ARCHITECTURE

by

Pil Woo (Peter) Chun

B. Eng. Hon., Ryerson University, Toronto, Canada, 2002

M.A.Sc., Ryerson University, Toronto, Canada, 2004

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

**Electrical and Computer Engineering**

Toronto, Ontario, Canada, 2009

Copyright © 2009 Pil Woo (Peter) Chun

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-58995-3 *Our file Notre référence* ISBN: 978-0-494-58995-3

## NOTICE:

AVIS:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# **AUTOUR'S DECLARATION**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Pil Woo (Peter) Chun

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Pil Woo (Peter) Chun

#### ABSTRACT

Architecture Synthesis Methodology for Run-time Reconfigurable Multi-task and Multimode Systems with Self-assembling Micro-architecture

> Pil Woo (Peter) Chun Doctor of Philosophy Graduate Program of Electrical and Computer Engineering Ryerson University

> > 2009

Despite the success that programmable devices have enjoyed in the last two decades, architecture synthesis methodologies for Run-Time Reconfigurable (RTR) systems are still in their infancy. As the majority of consumer devices integrate multiplefunctionality, the cost-effectiveness becomes the main focus of computing systems design. This thesis presents a novel architecture synthesis methodology for the costeffective implementation of a multi-task and multi-mode workload. The proposed methodology creates a RTR system that changes its functionality in response to a dynamic environment and enables on-chip assembly of pre-constructed components by synthesizing a workload-specific static architecture. The proposed methodology presents novelties in design abstraction, partitioning method and in the procedure of deciding reconfiguration granularity. The experimental results show the cost benefits of the proposed architecture synthesis methodology saving 73% of area and 29.8% of power compared to fixed design approach.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                 |

|-----------------------------------------------------------------|

| LIST OF TABLES                                                  |

| ABBREVIATIONS                                                   |

| ACKNOWLEDGEMENTS                                                |

| Chapter 1 Introduction                                          |

| 1.1 Motivation1                                                 |

| 1.2 Background                                                  |

| 1.2.1 Embedded systems                                          |

| 1.2.1.1 Electronic system level design                          |

| 1.2.1.2 Field Programmable Gate Array                           |

| 1.2.2 Target Applications                                       |

| 1.2.2.1 Real-time applications                                  |

| 1.2.2.2 Stream applications                                     |

| 1.2.2.3 Characteristics of real-time and stream systems         |

| 1.2.3 Reconfigurable systems                                    |

| 1.2.3.1 Reconfigurable system design flow                       |

| 1.2.3.2 Reconfigurable system architecture                      |

| 1.2.3.3 Reconfigurable system model                             |

| 1.3 Objectives                                                  |

| 1.4 Contributions                                               |

| 1.5 Organization of Thesis                                      |

| Chapter 2 Related Works and Overviews of Reconfigurable Systems |

| 2.1 Introduction                                                |

| 2.2 Motivation                                                  |

| 2.3 Reconfigurable Computing                                    |

| 2.4 Taxonomy of Reconfigurable Computing                        |

| 2.4.1 Evolvable Hardware                                        |

| 2.4.2 Non-EHW systems                                           |

| 2.5 Terminology and notation                                    |

| 2.5.1 System for reconfiguration                                |

| 2.5.2 Real-time applications                                    |

| 2.5.3 Stream applications                                       |

| 2.6 Generic Reconfigurable Systems                              |

| 2.6.1 System-on-Chip BUS architecture                           |

| 2.6.2 Network On Chip                                           |

| 2.7 Reconfigurable Computing Systems: Architectural point of view             |     |

|-------------------------------------------------------------------------------|-----|

| 2.8 Optimizing Reconfiguration                                                | 54  |

| 2.9 Reconfigurable Computing System: Application point of view                |     |

| 2.10 Summary of RC taxonomy                                                   |     |

| 2.11 Field Programmable Gate Array                                            |     |

| 2.11.1 Reconfigurable Hardware based on FPGAs                                 |     |

| 2.11.2 History of run-time reconfigurable Xilinx FPGAs                        | 61  |

| 2.11.3 Evolution of Virtex FPGAs                                              |     |

| 2.11.3.1 Configurable Logic Block                                             | 65  |

| 2.11.3.2 Routing                                                              | 67  |

| 2.11.3.3 Configuration                                                        | 68  |

| 2.12 Summary                                                                  | 71  |

| Chapter 3 Overview and Analysis of Effectiveness of Computing Systems         | 72  |

| 3.1 Introduction                                                              |     |

| 3.1.1 Cost-effectiveness of computing system                                  | 73  |

| 3.1.2 Three levels of cost-effectiveness                                      | 74  |

| 3.2 Motivation                                                                | 76  |

| 3.2.1 A perspective of computing history                                      | 76  |

| 3.2.2 Changing economics                                                      | 79  |

| 3.2.3 Changing Market                                                         | 81  |

| 3.2.4 FPGA: the alchemist of performance and flexibility                      |     |

| 3.3 Total system Costs                                                        |     |

| 3.4 Unilateral System Costs                                                   |     |

| 3.4.1 Personnel Costs                                                         |     |

| 3.4.2 Supply Costs                                                            |     |

| 3.4.3 Software Tools Costs                                                    |     |

| 3.4.4 Unit Cost                                                               |     |

| 3.5 Unilateral System Cost Graph                                              |     |

| 3.5.1 An example: unilateral system costs                                     |     |

| 3.5.1.1 Unit Cost                                                             |     |

| 3.5.1.2 Software Tools Costs                                                  |     |

| 3.5.1.3 Development Costs                                                     |     |

| 3.6 Collateral System Costs: Trend I                                          |     |

| 3.7 Cost-effectiveness: Trend II                                              |     |

| 3.7.1 Unilateral Cost-effectiveness.                                          |     |

| 3.8 Conclusion                                                                |     |

|                                                                               |     |

| Chapter 4 Exploration of Architectural Spaces for Virtual Hardware Components | 113 |

| 4.1 Background                                                                | 114 |

| 4.2 Architecture Configuration Graph                                          |     |

| 4.3 Decomposition of design space                                             | 120 |

| 4.4 Arrangement of the ACG                                                   | 120 |

|------------------------------------------------------------------------------|-----|

| 4.4.1 Horizontal arrangement of resource variances                           | 121 |

| 4.4.2 Vertical arrangement of resources                                      |     |

| 4.5 Selecting a right architecture                                           | 124 |

| 4.5.1 Determination of architecture validity for a constraint                | 124 |

| 4.5.2 Determination of Pareto-optimal architecture subset                    |     |

| 4.5.3 Estimating the number of architecture variances                        | 126 |

| 4.6 Virtual Hardware Components Constraints                                  |     |

| 4.7 Outcome                                                                  |     |

| Chapter 5 Reconfigurable System Design Methodology for multi-task and multi- |     |

| mode applications                                                            |     |

| 5.1 Introduction                                                             | 130 |

| 5.2 Motivation                                                               |     |

| 5.3 ASIC System Design Flow                                                  |     |

| 5.4 Reconfigurable System Design Flow                                        |     |

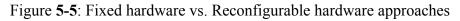

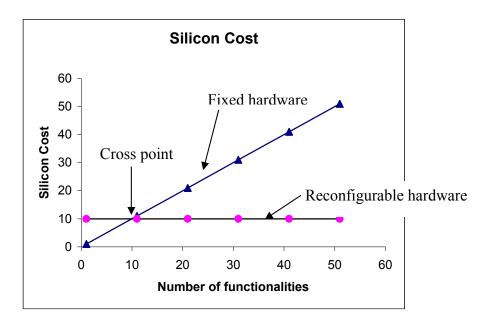

| 5.5 Silicon Cost                                                             |     |

| 5.5.1 Analysis of silicon costs                                              |     |

| 5.6 Configuration Flow Specification                                         |     |

| 5.6.1 Defining the environment.                                              |     |

| 5.6.2 Event list                                                             |     |

| 5.6.3 Context diagram                                                        |     |

| 5.6.4 Leveled context diagram                                                |     |

| 5.7 Identifying a multi-task and multi-mode workload                         |     |

| 5.8 Constructing a Static Architecture                                       |     |

| 5.9 Defining the Reconfiguration Granularity                                 |     |

| 5.10 Summary                                                                 |     |

| Chapter 6 Implementation                                                     | 183 |

|                                                                              |     |

| 6.1 System Organization                                                      |     |

| 6.1.1 System Level                                                           |     |

| 6.1.1.1 Reconfigurable Functional Module                                     |     |

| 6.1.1.2 Run-time Reconfigurable Platform (Xilinx Virtex FPGA)                |     |

| 6.1.2 Micro Level                                                            |     |

| 6.1.2.1 Abstraction of micro-level implementation                            |     |

| 6.1.2.2 Architecture of Xilinx Virtex-4 FPGA                                 |     |

| 6.1.3 Component Level                                                        | 199 |

| 6.1.3.1 Virtual Hardware Component                                           | 200 |

| 6.1.3.2 Virtual Bus                                                          |     |

| 6.1.4 Configuration                                                          |     |

| 6.1.4.1 Configuration interface                                              |     |

| 6.1.4.2 Configuration chart                                                  | 203 |

vi

| 6.1.4.3 Configuration steps                                                | 205 |

|----------------------------------------------------------------------------|-----|

| 6.1.4.4 Reconfigurable Units                                               |     |

| 6.1.4.5 On-chip assembling of Virtual Hardware Components                  |     |

| 6.2 Run-time Reconfiguration Example                                       |     |

| 6.3 Run-time partial reconfigurable implementation of on-chip multi-stream |     |

| processors                                                                 | 213 |

| 6.3.1 System Organization                                                  |     |

| 6.3.2 Multi-task Adaptive Reconfigurable System Platform                   |     |

| 6.3.2.1 Stereo camera board                                                |     |

| 6.3.3 Identifying a multi-thread and multi-mode workload                   |     |

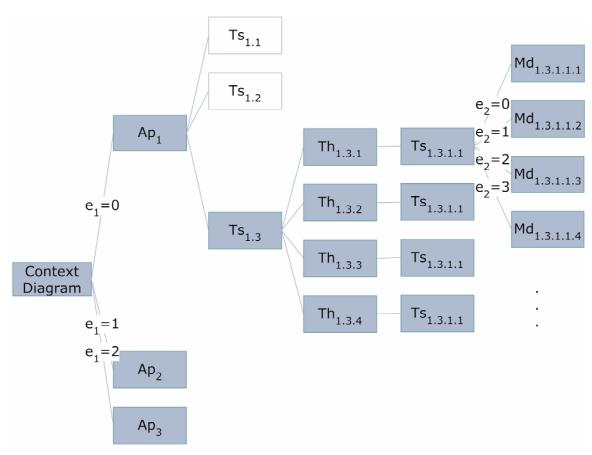

| 6.3.4 Constructing a static architecture                                   |     |

| 6.3.5 The procedure of on-chip assembly                                    |     |

| 6.4 Summary                                                                |     |

| ····                                                                       |     |

| Chapter 7 Analysis of Results                                              | 237 |

|                                                                            |     |

| 7.1 Analysis of Cost-effectiveness                                         | 237 |

| 7.2 Estimation of Configuration Granularity                                | 246 |

| 7.3 Scalability                                                            | 249 |

| 7.4 Analysis of Power Consumption                                          | 250 |

| 7.5 Summary                                                                | 254 |

|                                                                            |     |

| Chapter 8 Conclusions                                                      | 256 |

|                                                                            |     |

| Bibliography                                                               | 259 |

|                                                                            |     |

| Appendix A Cost Estimation                                                 | 267 |

| A 1 Fatimation of Unit Cost                                                | 267 |

| A.1 Estimation of Unit Cost                                                |     |

| A.2 Estimation of Software Tools Cost                                      |     |

| A.3 Development Costs                                                      | 270 |

| Appendix B Experimental Details                                            | 272 |

| Appendix D Experimental Details                                            |     |

| B.1 Estimation of Silicon Costs                                            | 272 |

| B.2 How to calculate $c_{LUT}$                                             |     |

|                                                                            |     |

| B.3 Examples of LED counter                                                |     |

| Annondix C. Power Estimation Datails                                       | 200 |

| Appendix C Power Estimation Details                                        | 280 |

| C.1 Example of Power Estimation Testbench                                  | 280 |

| C.2 Examples of Video Processors                                           |     |

|                                                                            | 200 |

vii

# **LIST OF FIGURES**

| Figure 2-1: Process technology vs. System cost                                                                                                 | 22 |

|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure <b>2-2</b> : Empirical Taxonomy of RC                                                                                                   | 25 |

| Figure 2-3: A typical example – Hierarchy of Spatial Computation (Ts denoting a task, Ap denoting an application and op denoting an operation) | 27 |

| Figure <b>2-4</b> : Temporal Computation ( <b>Th</b> denoting a thread and <b>W</b> denoting a workload)                                       | 29 |

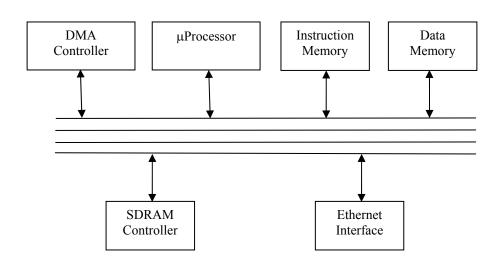

| Figure <b>2-5</b> : Conventional BUS – an example                                                                                              | 41 |

| Figure <b>2-6</b> : SoC Bus Module – an example                                                                                                | 42 |

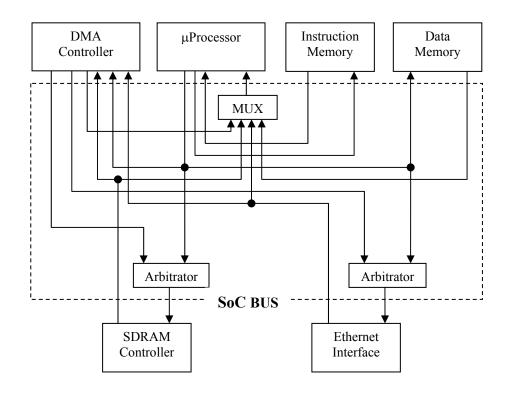

| Figure 2-7: A example of CoreConnect bus architecture                                                                                          | 44 |

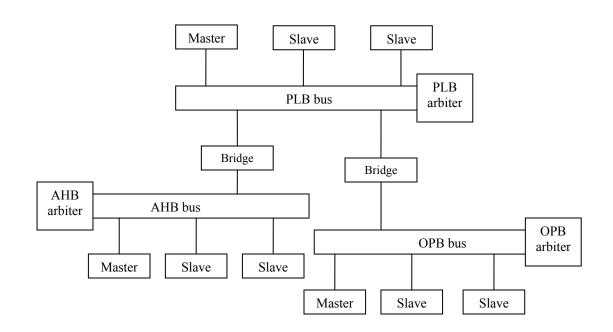

| Figure 2-8: Projected relative delays of local and global wires [29]                                                                           | 45 |

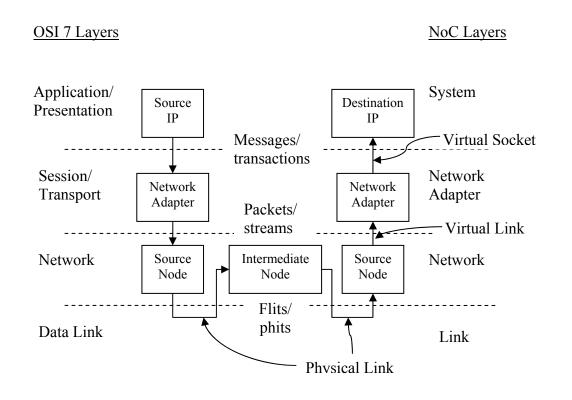

| Figure 2-9: NoC layers vs. OSI 7 layers: redrawn from [30]                                                                                     | 46 |

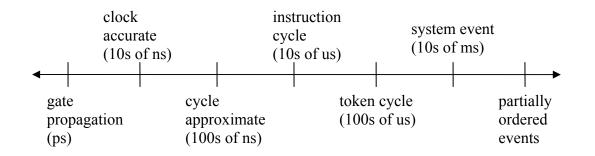

| Figure <b>2-10</b> : Temporal Resolution Axis                                                                                                  | 57 |

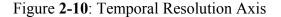

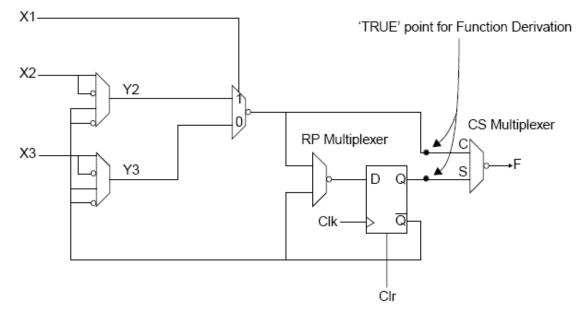

| Figure <b>2-11</b> : XC6200 Basic Cell [ <b>58</b> ]                                                                                           | 62 |

| Figure <b>2-12</b> : XC6200 Function Unit [ <b>58</b> ]                                                                                        | 63 |

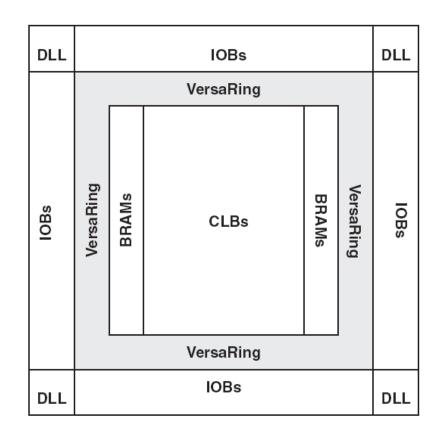

| Figure 2-13: Virtex Architecture Overview [62]                                                                                                 | 64 |

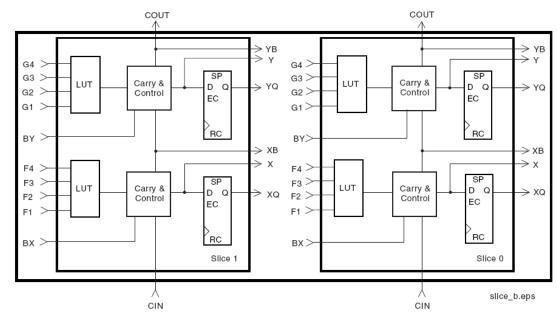

| Figure <b>2-14</b> : 2-slice Virtex CLB [ <b>62</b> ]                                                                                          | 66 |

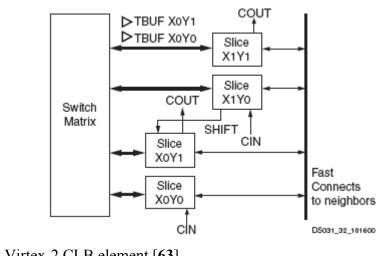

| Figure 2-15: Virtex-2 CLB element [63]                                                                                                         | 66 |

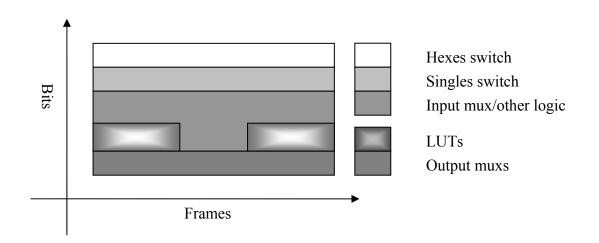

| Figure <b>2-16</b> : Graphical representation of one CLB worth configuration data for Virtex FPGA.                                             | 69 |

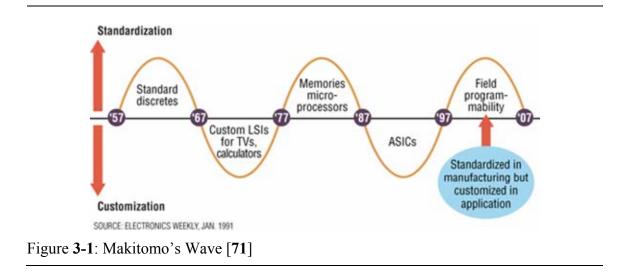

| Figure 3-1: Makitomo's Wave [71]                                                                                                               | 77 |

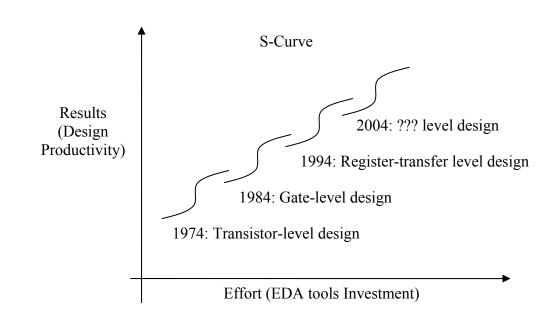

| Figure <b>3-2</b> : Design discontinuities in EDA [74]                                                                                         | 78 |

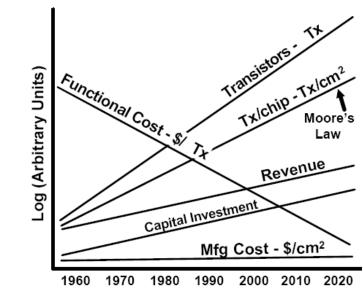

| Figure <b>3-3</b> : Functional form of key semiconductor industry business trends (Tx=transistor) [ <b>75</b> ]                                | 80 |

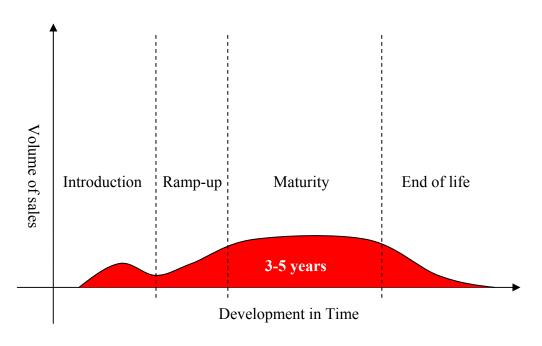

| Figure 3-4: Conventional Product Life Cycle [72]                                                                                               | 82 |

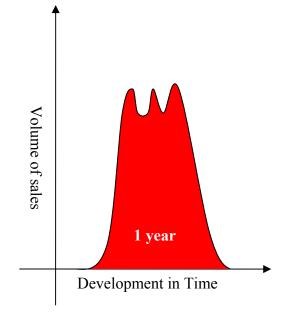

| Figure <b>3-5</b> : New Product Life Cycle [72]                                                     | . 83  |

|-----------------------------------------------------------------------------------------------------|-------|

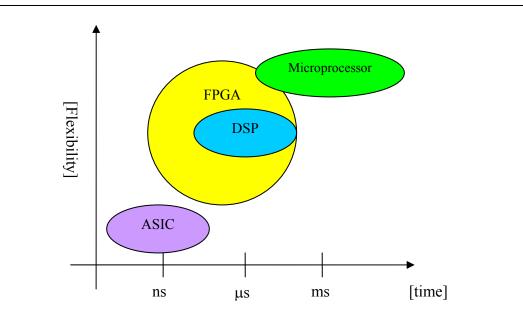

| Figure <b>3-6</b> : Flexibility vs. Operating time window                                           | . 84  |

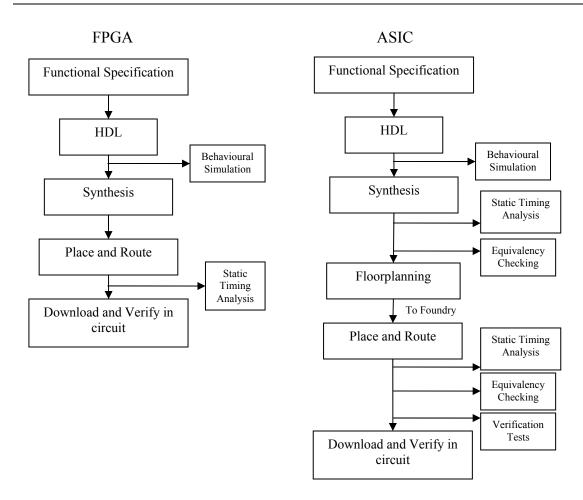

| Figure <b>3-7</b> : Design Flow FPGA vs. ASIC                                                       | . 90  |

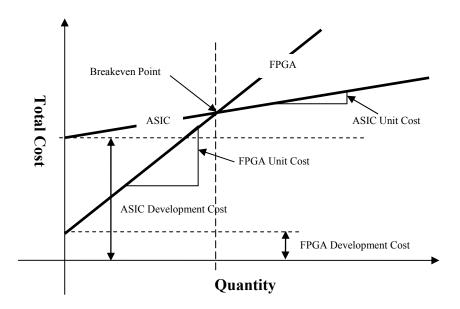

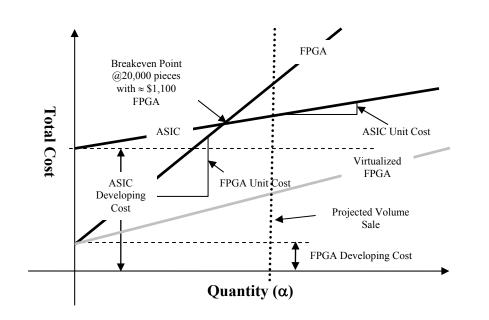

| Figure <b>3-8</b> : Conventional unilateral System Cost ASIC vs. FPGA                               | 93    |

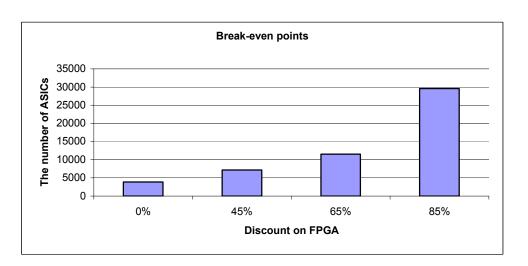

| Figure <b>3-9</b> : Breakeven points – the number of ASICs vs. FPGA unit cost in volume             | 99    |

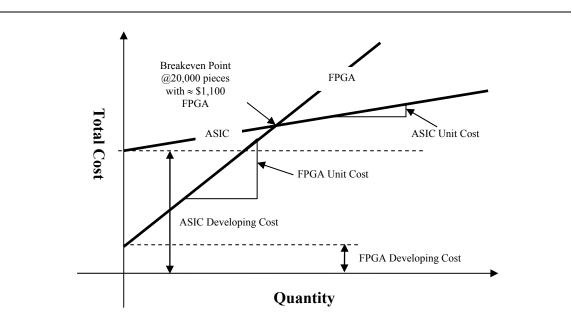

| Figure <b>3-10</b> : Cost vs. Quantity                                                              | .100  |

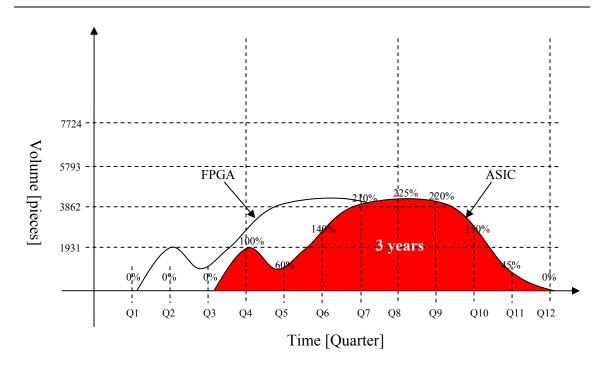

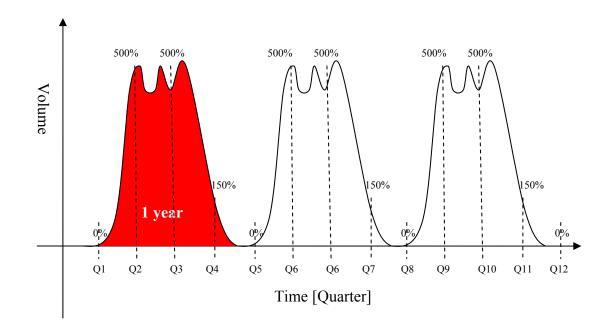

| Figure <b>3-11</b> : Sale volume estimation (conventional product life cycle)                       | . 103 |

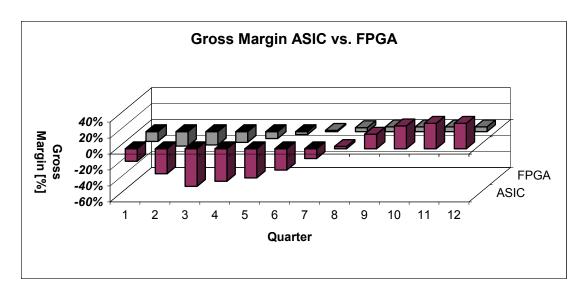

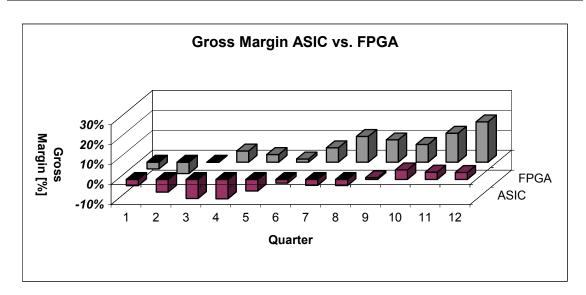

| Figure <b>3-12</b> : Gross Margin of ASIC vs. FPGA (discount of FPGA, 65%)                          | .104  |

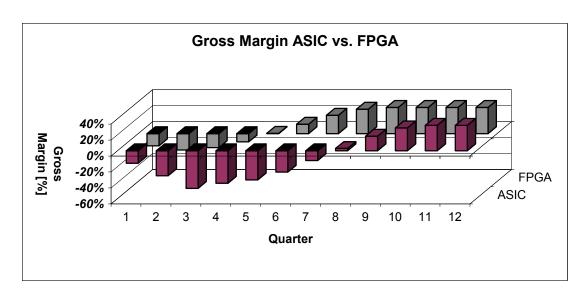

| Figure <b>3-13</b> : Gross Margin of ASIC vs. FPGA (discount of FPGA, 77%)                          | . 105 |

| Figure <b>3-14</b> : Sale volume estimation (new product life cycle)                                | . 106 |

| Figure <b>3-15</b> : Gross Margin of ASIC vs. FPGA (discount of FPGA, 77%, one-year time-to-market) | 107   |

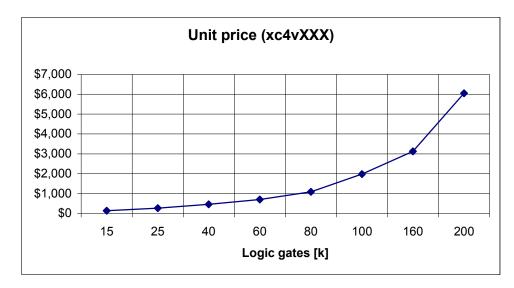

| Figure <b>3-16</b> : Unit price for Xilinx Virtex-4 FPGA LX family                                  | . 108 |

| Figure <b>3-17</b> : Quantity vs. Costs                                                             | .110  |

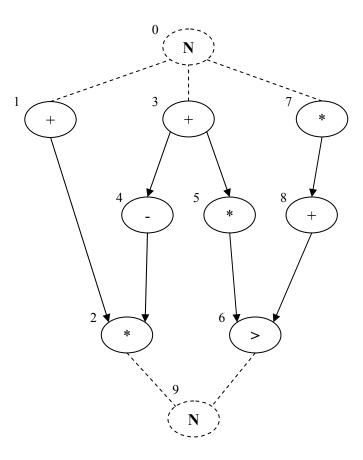

| Figure 4-1: Example of a sequencing Graph                                                           | .116  |

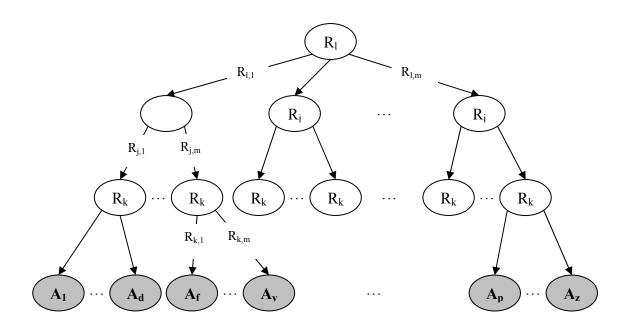

| Figure 4-2: Example of component design space exploration represented by a tree.                    | .118  |

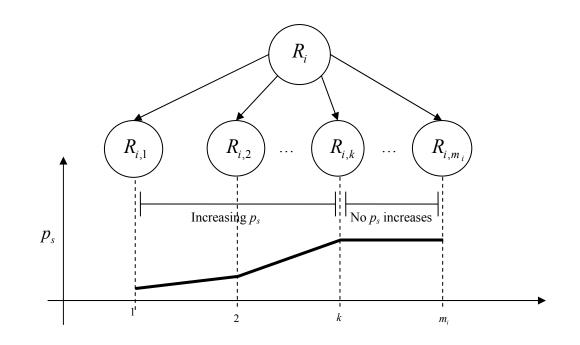

| Figure 4-3: Horizontal level Arrangement                                                            | . 122 |

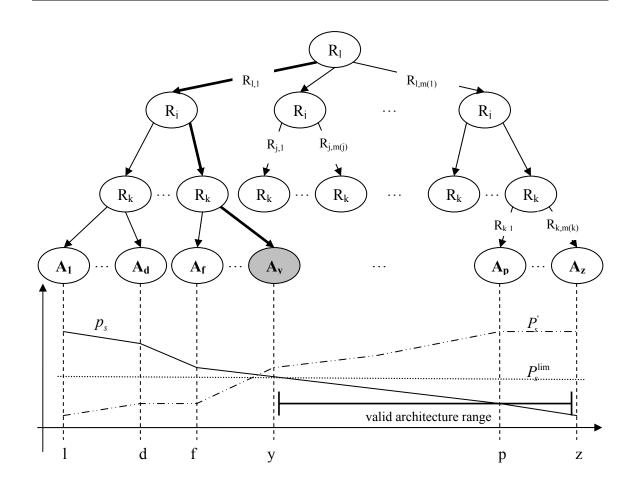

| Figure 4-4: Selecting valid architecture range with <i>P</i> <sub>s</sub>                           | . 125 |

| Figure 4-5: Determination of Pareto-optimal architecture subset                                     | . 126 |

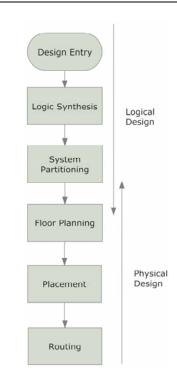

| Figure 5-1: ASIC design flow                                                                        | .134  |

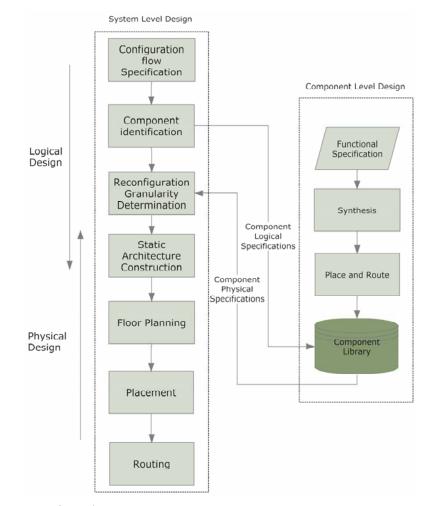

| Figure 5-2: RC Design Flow                                                                          | . 137 |

| Figure <b>5-3</b> : An example of workload representation                                           | . 138 |

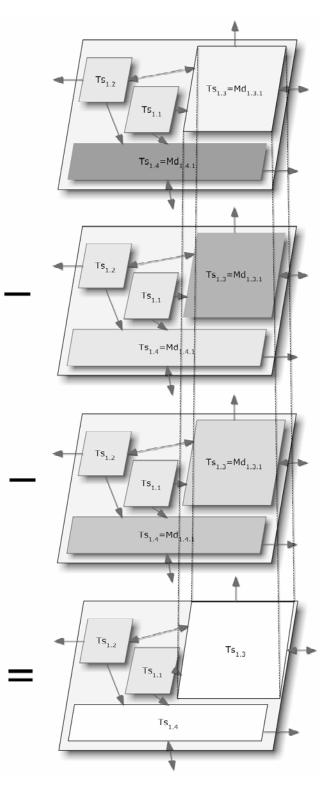

| Figure <b>5-4</b> : An illustration of static architecture extraction procedure                     | . 139 |

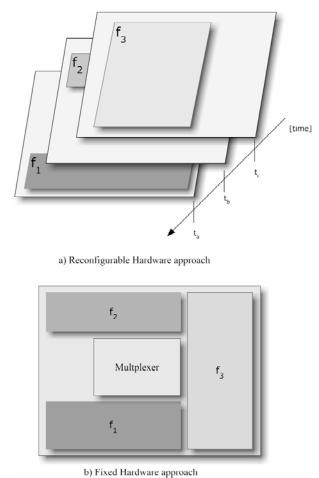

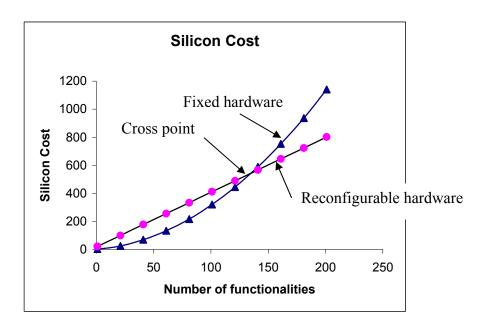

| Figure <b>5-5</b> : Fixed hardware vs. Reconfigurable hardware approaches                           | 141   |

| Figure <b>5-6</b> : Silicon Costs                                                          | 142 |

|--------------------------------------------------------------------------------------------|-----|

| Figure 5-7: Silicon Cost with quadratic increase in multiplexing area                      | 144 |

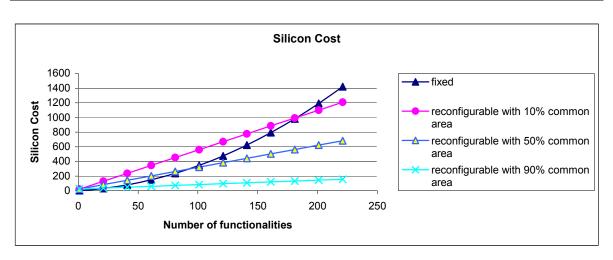

| Figure <b>5-8</b> : Silicon costs: fixed hardware vs. reconfigurable hardware              | 146 |

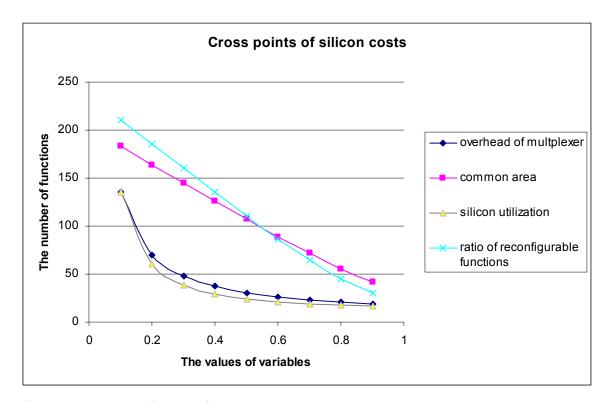

| Figure <b>5-9</b> : Cross points graph                                                     | 147 |

| Figure <b>5-10</b> : Silicon cost with varying common area                                 | 149 |

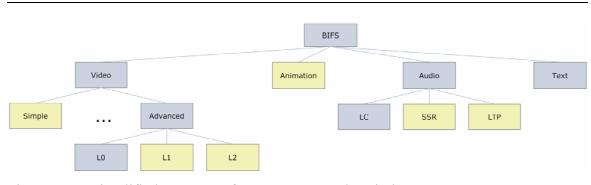

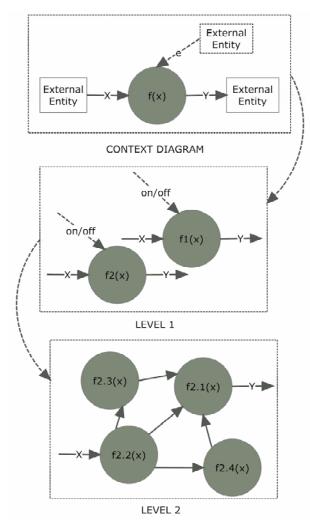

| Figure <b>5-11</b> : Simplified structure of MPEG-4 scene description                      | 150 |

| Figure <b>5-12</b> : An essential Context Diagram                                          | 155 |

| Figure <b>5-13</b> : Examples of Context Diagram                                           | 156 |

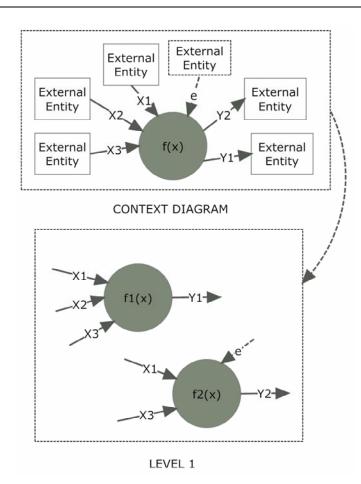

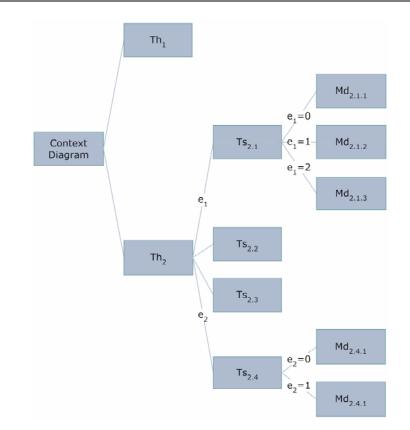

| Figure 5-14: An example of leveled context diagram                                         | 160 |

| Figure <b>5-15</b> : An example of threads in dataflow diagram                             | 162 |

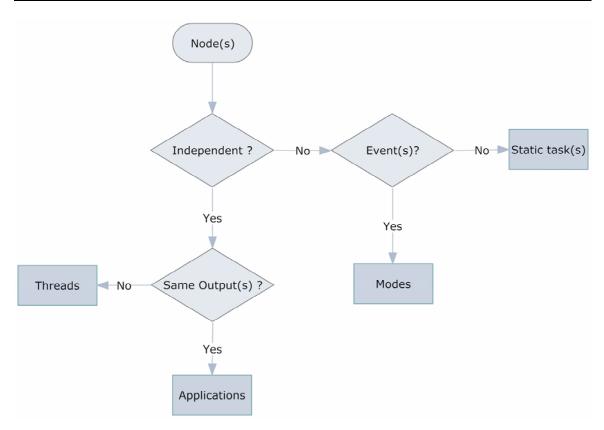

| Figure <b>5-16</b> : An example of tasks and modes in context diagram                      | 163 |

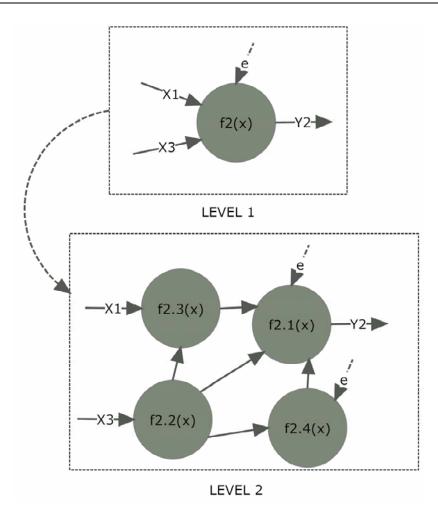

| Figure <b>5-17</b> : The decision tree for bubbles in a multi-task and multi-mode workload | 165 |

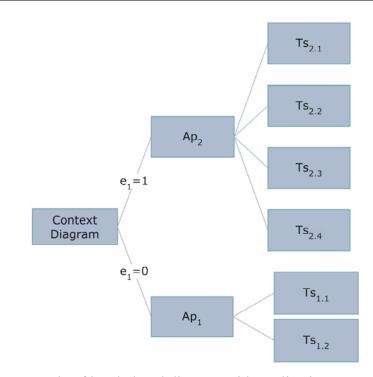

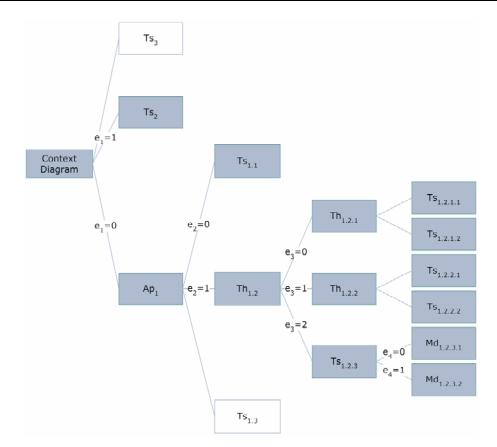

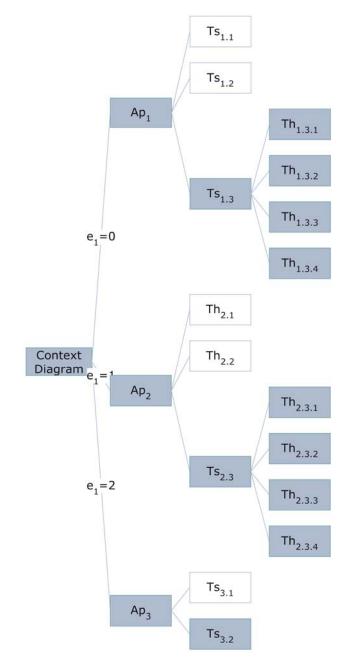

| Figure <b>5-18</b> : An example of leveled tool diagram with applications                  | 166 |

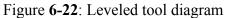

| Figure <b>5-19</b> : An example of leveled tool diagram with threads                       | 167 |

| Figure <b>5-20</b> : An example of leveled tool diagram with isolated tools                | 169 |

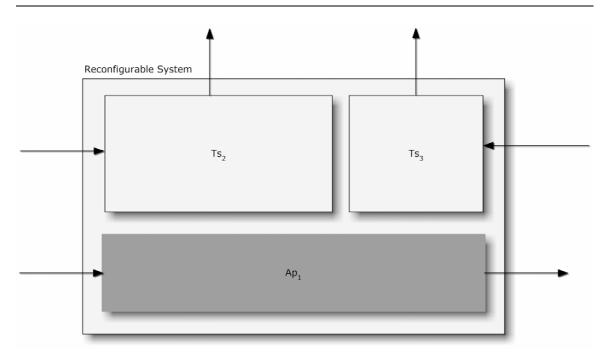

| Figure <b>5-21</b> : An example of the static architecture                                 | 174 |

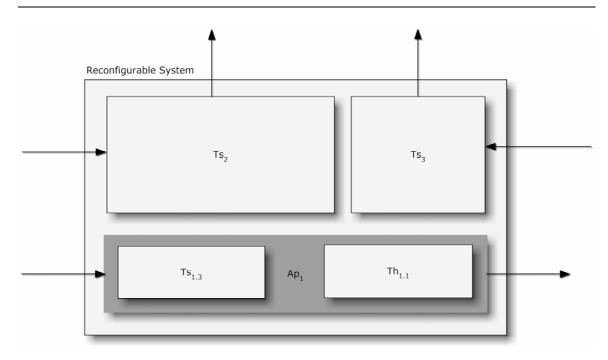

| Figure 5-22: An example of the static architecture with the pre-condition of $e_1=0$       | 175 |

| Figure <b>5-23</b> : An example of static architecture                                     | 176 |

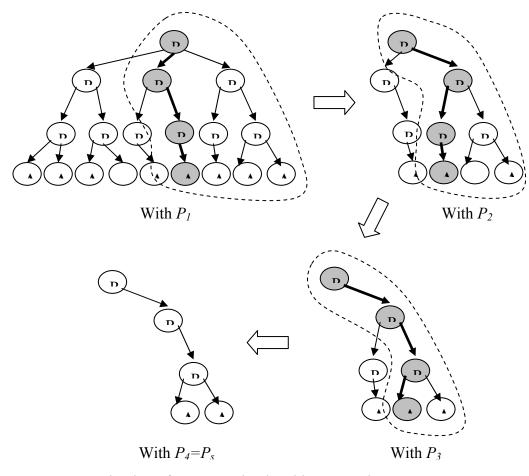

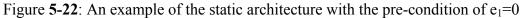

| Figure <b>5-24</b> : The steps to achieve reconfiguration granularity                      | 178 |

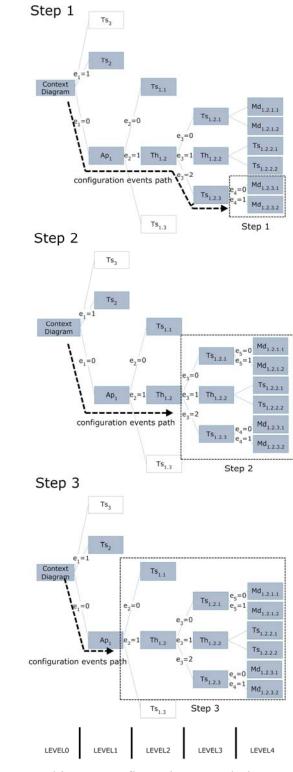

| Figure <b>5-25</b> : The flowchart to determine the reconfiguration granularity            | 181 |

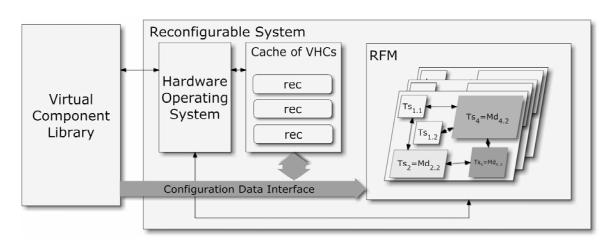

| Figure 6-1: System level architecture                                                      | 186 |

| Figure 6-2: Virtex-4 LX Architecture Overview                                              | 192 |

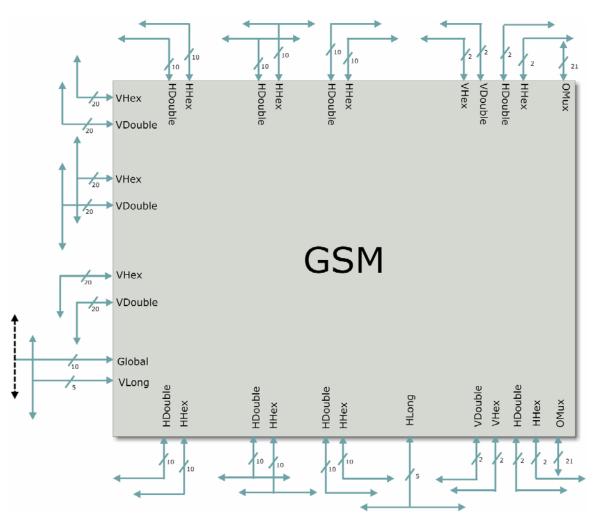

| Figure 6-3: The overview of GSM interconnects                                              | 194 |

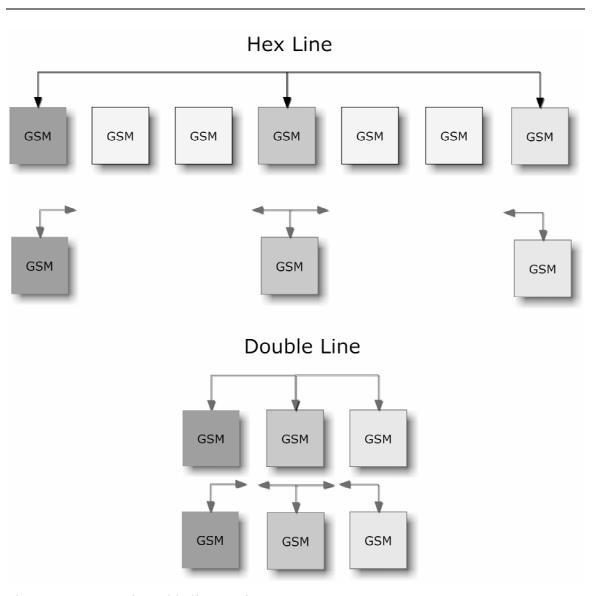

| Figure 6-4: Hex and Double line routing structure                                          | 195 |

|--------------------------------------------------------------------------------------------|-----|

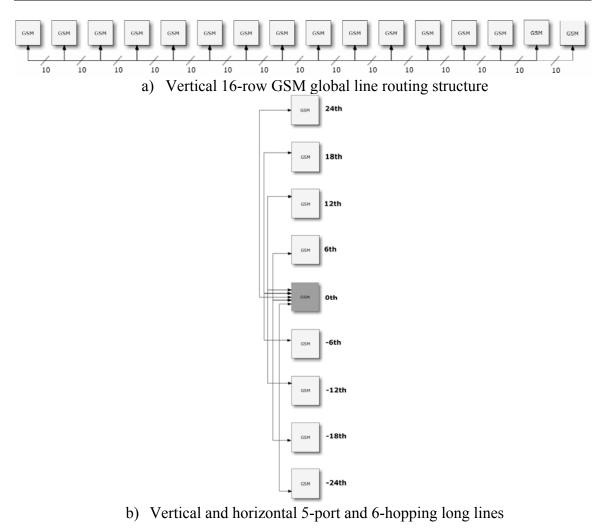

| Figure 6-5: Long & global line routing structure                                           | 196 |

| Figure 6-6: An example of sliced BUS macro                                                 | 197 |

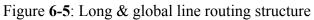

| Figure 6-7: Configuration Flow Chart                                                       | 204 |

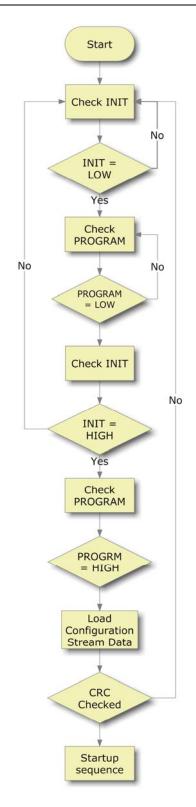

| Figure 6-8: Configuration Processing Flow                                                  | 206 |

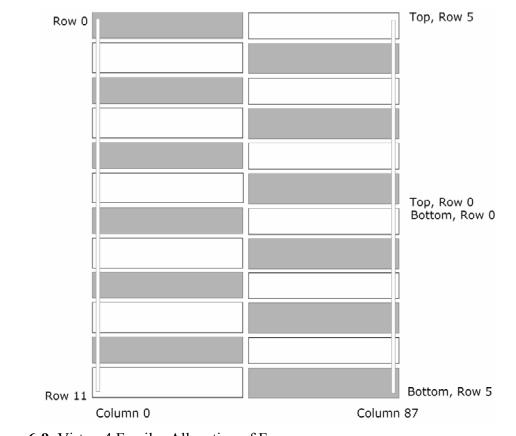

| Figure 6-9: Virtex-4 Family: Allocation of Frames                                          | 208 |

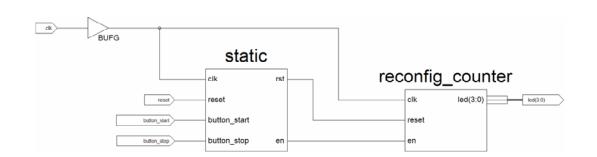

| Figure 6-10: Schematic of "LED counter" example                                            | 209 |

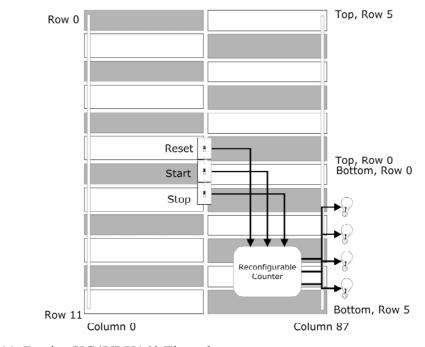

| Figure 6-11: Device XC4VLX160 Floorplan                                                    | 210 |

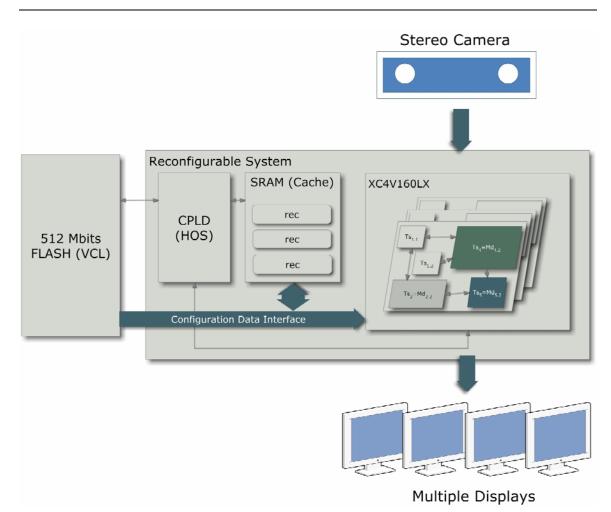

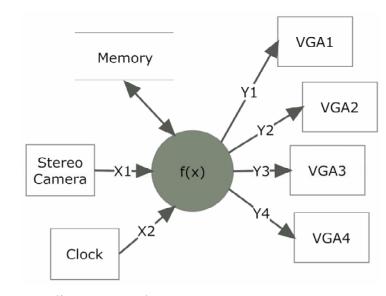

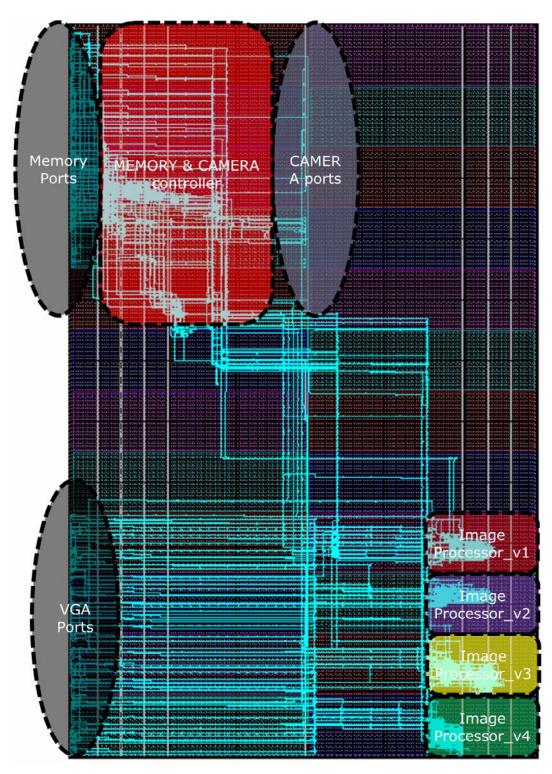

| Figure 6-12: Hardware Organization                                                         | 215 |

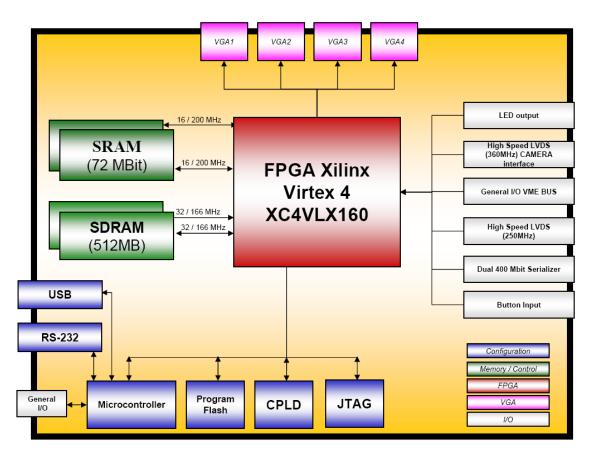

| Figure 6-13: Block diagram of MARS platform                                                | 217 |

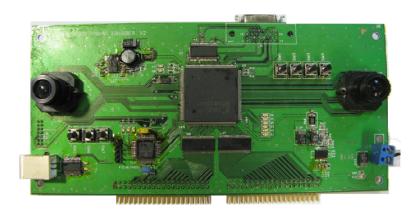

| Figure 6-14: MARS platform                                                                 | 218 |

| Figure 6-15: An illustration of aggregated operation of MARS platforms                     | 218 |

| Figure 6-16: Stereo Camera Module                                                          | 219 |

| Figure 6-17: New Stereo Capture Module                                                     | 220 |

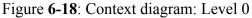

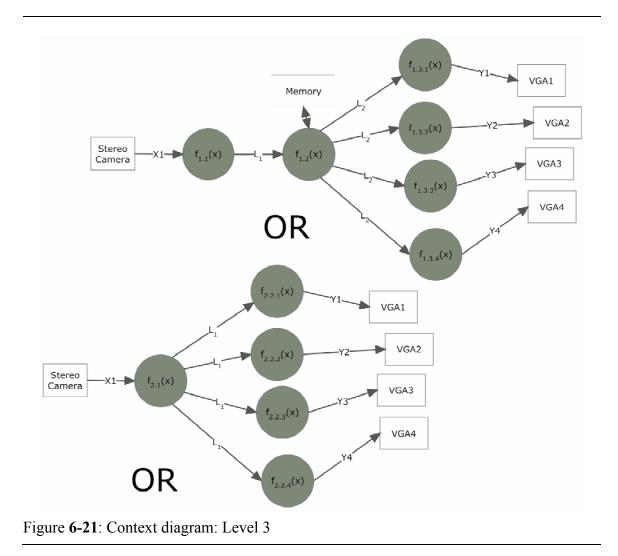

| Figure 6-18: Context diagram: Level 0                                                      | 221 |

| Figure 6-19: Context diagram: Level 1                                                      | 222 |

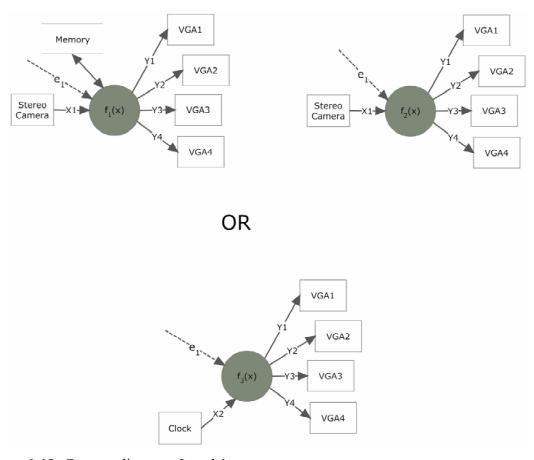

| Figure 6-20: Context diagram: Level 2                                                      | 223 |

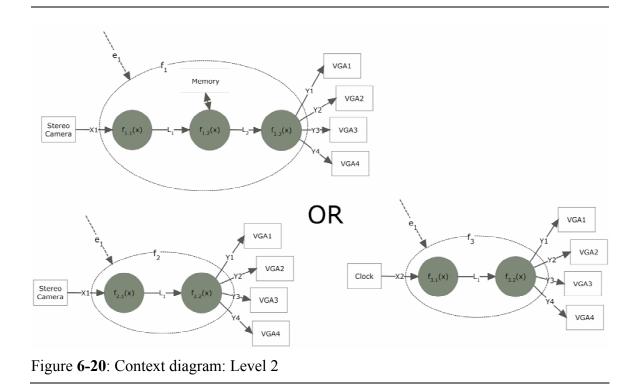

| Figure 6-21: Context diagram: Level 3                                                      | 224 |

| Figure 6-22: Leveled tool diagram                                                          | 226 |

| Figure 6-23: A portion of the leveled tool diagram for $Ts_{1.3}$                          | 229 |

| Figure 6-24: Conceptual assembly: Level 2                                                  | 230 |

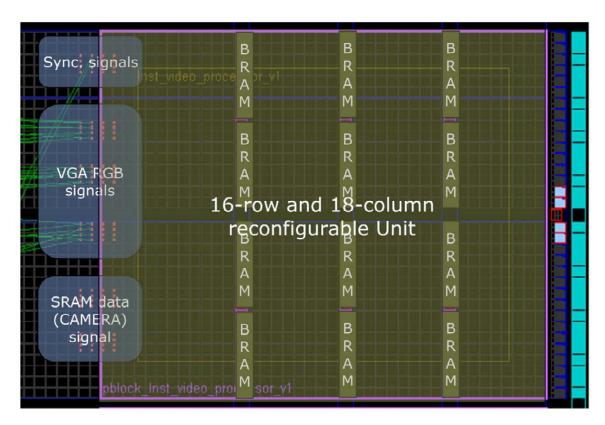

| Figure 6-25: An illustration of inst_video_processor_v1                                    | 232 |

| Figure <b>6-26:</b> An implementation with $e_1=1$ , $e_2=1$ , $e_3=1$ , $e_4=1$ , $e_5=1$ | 233 |

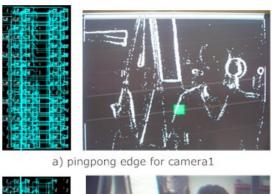

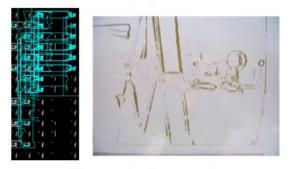

| Figure 7-1: Examples of modes in FPGA implementation vs. visual display                    | 241 |

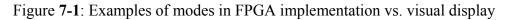

| Figure 7-2: A visual comparison of the fixed design and the reconfigurable design | 243 |

|-----------------------------------------------------------------------------------|-----|

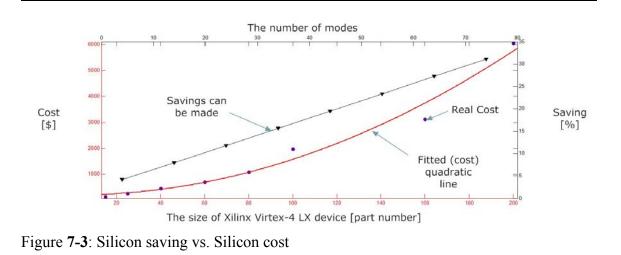

| Figure 7-3: Silicon saving vs. Silicon cost                                       | 245 |

| Figure <b>7-4</b> : An example of full configuration for a mode of functions      | 247 |

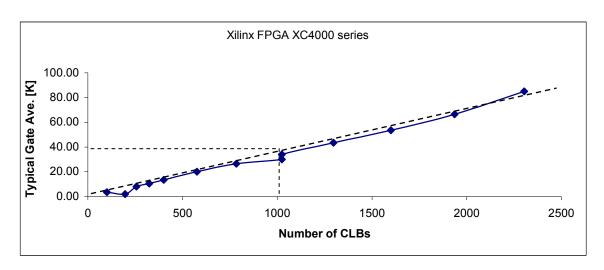

| Figure A-1: The relationship between the number of CLBs and the gate average      | 268 |

# LIST OF TABLES

| Table 2-1: Granularity of coarse-grained reconfigurable architectures                  | . 52 |

|----------------------------------------------------------------------------------------|------|

| Table 2-2: Communication topology of reconfigurable architectures                      | . 53 |

| Table 3-1: Architectural eras                                                          | .76  |

| Table 3-2: ASIC Unit Cost with 21888K gate capacity                                    | .96  |

| Table 3-3: Development Cost                                                            | .98  |

| Table 3-4: Development Cost Projection ASIC vs. FPGA                                   | .102 |

| Table 6-1: Configuration Ports                                                         | .203 |

| Table 6-2: Frame Address Fields Register (FAR)                                         | .211 |

| Table 7-1: The list of video processing modes for a camera                             | .239 |

| Table 7-2: Costs for run-time reconfiguration service hardware                         | .244 |

| Table 7-3: Different data units at 30 fps with 640×480 resolution                      | .248 |

| Table 7-4: Power measurement for reconfigurable multi-video processor implementation   | .251 |

| Table 7-5: Power consumption of VHCs in operation                                      | .252 |

| Table 7-6: Reconfigurable design power consumption                                     | .253 |

| Table 7-7: Fixed design power consumption                                              | .254 |

| Table A-1: XC4000 FPGA typical gate average (internal memory is included)              | .267 |

| Table A-2: Software Tool Usage                                                         | .269 |

| Table A-3: Detailed Software Tools Cost for an FPGA                                    | .269 |

| Table A-4: Detailed Software Tools Cost for an ASIC                                    | .270 |

| Table A-5: Assumptions given for the development costs                                 | .270 |

| Table A-6: Detailed FPGA and ASIC Development Costs                                    | .271 |

| Table <b>B-1</b> : $C_{LUT}$ values for the multi-task and multi-mode video processors | .273 |

# **ABBREVIATIONS**

| ACG Architecture Configuration Graph         |

|----------------------------------------------|

| ASIC Application Specific Integrated Circuit |

| ASMBL Advanced Silicon Modular Block         |

| ATPG Automatic Test Pattern Generator        |

| ATM Asynchronous Transfer Mode               |

| BRAM Block selectRAM                         |

| ISA Instruction Set Architecture             |

| CB Cell Based                                |

| CMOS Complementary Metal Oxide Semiconductor |

| CLB Configurable Logic Block                 |

| CPLD Complex Programmable Logic Device       |

| CPU Central Processing Unit                  |

| DAC Digital-to-Analog Converter              |

| DCM Digital Clock Manager                    |

| DSM Deep Sub-Micron                          |

| DSP Digital Signal Processor                 |

| EDA Electronic Design                        |

| EHW Evolvable Hardware                       |

| ESL Electronic System Level                  |

| FPGA Field Programmable Gate Array           |

FF Flip Flop

FIFO First In First Out

FPS Frames Per Second

GSM General Switch Module

GUI Graphical User Interface

QAM Quadrature Amplification Modulation

I/O Input/Output

IC Integrated Circuit

**IP Intellectual Property**

LAN Local Area Network

LED Light Emitting Diode

LUT Look Up Table

LVDS Low Voltage Differential Signal

NRE Non-Recurring

NOC Network on Chip

MB Mega Byte

MPEG Moving Picture Experts Group

MHz Mega Hertz

PCI Peripheral Component Interconnect

**RE Revenue Expenditure**

RC Reconfigurable Computing

PR Partial Reconfiguration

RAM Random Access Memory

RFM Reconfigurable Functional Module

RGB Red Green Blue

RTL Transfer level

HOS Hardware Operating System

SOC System On a chip

SONET Synchronous Optical Network

SCM Stereo Capture Module

SRAM Static RAM

USB Universal Serial Bus

VB Virtual Bus

VCL Virtual Component Library

VGA Video Graphics Array

VHC Virtual Hardware Component

VHDL Very High Speed Integrated Circuit Hardware Description Language

VME Versa Modular Eurocard

WLAN Wireless Local Area Network

#### ACKNOWLEDGEMENTS

First of all I would like to express my sincere gratitude to Dr. Lev Kirischian, Associate Professor of Electrical and Computer Engineering, Ryerson University, who has been my supervisor since the beginning of my study. He provided me with many helpful suggestions, important advice and constant encouragement during the course of this work.

My keen appreciation goes to Valeri Kirischian, Jamin Islam and Sergiy Zhelnakov for their valuable assistance in the field. Without their help, the field work would not have been accomplished in time.

I'd like to acknowledge the National Science and Engineering Research Council (NSERC), the Ontario Centres of Excellence (CITO), MDA Space Missions, CMC Microsystems, Unique Broadband Systems (UBS) and the Department of Electrical and Computer Engineering at Ryerson University for their financial contributions to this work.

I am also indebted to Soo Moon for editing the English of this document. My special appreciation goes to my parents, Son-ok Lee and Ki-young Chun, who introduced me into the world. I would like to express my heartiest thanks to my children, Monet, Adele, Jin-sol and Min-sol for their support and inspiration, and for always letting me feel that I am worthy.

Finally, I would like to express special thanks to my wife Cheng-hyun (Elena) Kim. She helped me to concentrate on completing this dissertation and supported me mentally during the course of this work. Without her help and encouragement, this study would not have been completed.

#### Chapter 1

## Introduction

The advent of silicon technology has enabled many hardware evolutions in the computing industry in the last half century. However, the increase of computation capacity has mostly relied on increasing computation frequency of Instruction Set Architectures (ISAs). As we face the era of deep submicron process technologies, it is hard not only to increase the operating frequency of computing systems, but also to build the computing systems that can satisfy complex and multiple functionalities of today's applications. Because the dynamic partial reconfiguration in field programmable devices can change their internal structure and behaviour in response to a dynamic environment, reconfigurable computing systems allow system designers to employ more complex systems. This thesis recognizes the cost benefits that such run-time adaptability can provide and proposes a novel reconfigurable architecture synthesis methodology to achieve a cost-effective system solution. The proposed architecture synthesis methodology establishes the design steps starting from recognition of the environment to on-chip assembling of a complete micro-level system.

### **1.1 Motivation**

As the flood of Eastern products as well as the rise of Eastern philosophical approaches inundates the industrialized part of the world, we look into the doctrine of

*"Form follows function"* which strongly exists in Eastern philosophies such as Oullium<sup>1</sup> [1] to shed light on the quest for a new Reconfigurable Architecture synthesis methodology. We strongly believe that reconfigurable systems can be more cost-effective by employing programmable fabrics and reusing them according to the applications needs in today's environment.

*"Form follows function"* is a dictum that represents the core of functionalism that Bauhaus<sup>2</sup> pioneered in 20<sup>th</sup> century. In functionalism, function is dynamic. Thus, form can only unveil through function. Form should stay shapeless unless indulged by function. In other words, *"Form follows function"* can be interpreted as deconstructionism<sup>3</sup> denying the subjective interpretation of the world. Functionalism is presented in Eastern philosophical world view – 諸去無我, there is no *T'(subjective being)*. When there is proper understanding and interpretation of environment, then only form can follow function. Form should represent lively aspects of environment.

For example, in nature, giraffes have evolved to be tall in the attempt to get to tree leaves. Flowers have beautiful colors and shapes in order to be pollinated. In human society, forks have been elaborated to have tines in order to pierce and hold the meat. Particularly there has been no unique solution to the elementary problem of food utensils as Petroski [2] states in his book. Chopsticks are evolved from Eastern cuisine as the meat is cut before cooking and forks are developed in Western cuisine to cut the meat

<sup>&</sup>lt;sup>1</sup> Oullium tries to extract the ideas that coexist in Buddhism, Taoism and Christianity.

<sup>&</sup>lt;sup>2</sup> Bauhaus is a term used for a school in Germany that combines the skill sets that train craftsmen and artists in one umbrella. The movement started from the school became the foundation of modernist architecture of  $20^{th}$  century.

<sup>&</sup>lt;sup>3</sup> Is a challenge to the attempt to "deconstruct" the ideological biases to establish any ultimate or secure meaning of "truth".

after it is cooked. The designs of things such as houses, cars, clothes, computers, utensils, etc. are not direct results of solving a particular task, but result from more complicated issues.

Particularly applicable to the computing industry, form is the product of design. It should thrive to be minimal (i.e., cost-effective). Form should not be limited as physical characteristics but should reflect specification of the running functions. According to the Bauhaus' functionalism, we need a computing system architecture (i.e., form) that reflects dynamic changes in applications and implements the applications as they are represented (i.e., function).

Moreover, some changes in environment do not happen very often borrowing the explanations from biological evolution. Therefore, for some biological beings, the environment feels like *"static"*. However, the environment is a dynamic entity. Thus, the perceived time scaling of changes determines how the system (e.g., biological being) needs to reflect them into the architecture (e.g., macroevolution and microevolution [**3**]).

For instance, high biological beings (e.g., mammals) are normally comprised of two types of forms: sea of homogenous elements (e.g., 100 millions neurons in brain) and a particular set of heterogeneous components (e.g., body parts and its structure). While homogenous elements possess only preliminary functionality compared to heterogeneous components, they can accomplish complex functionality by interconnecting their behaviours. The system is ready to adapt its functionality to *"dynamic"* changes of the environment that might occur. Thus, they represent flexibility at large. On the contrary, heterogeneous components try to achieve best results by knowing its requirements and tailoring the system for particular task(s). There is no imminent change to be updated. The environment seems to be *"static"* to the system. Because form is the product of design that thrives to be minimal, both cases achieve the minimal cost from their perspectives of a *"dynamic"* or *"static"* environment. The perceived time scaling difference results in two distinctive ways of implementing forms.

The proposed reconfigurable system needs to identify functionalities in the application(s) and associate them with events that are identifiable at the system level. Once all functionalities are organized and the reusable areas are recognized, a suitable time scaling (i.e., reconfiguration granularity) is determined to differentiate between dynamic and static components of the system as the responses of the environmental events. The reconfigurable system does not only save hardware area by reconfiguring "dynamic" requests of the environment, but also maintains reliable communication between "static" components to carry on their functionalities. Conventional Instruction Set Architectures (ISAs) can not guarantee the required performance of concurrently running multiple functionalities because the system is designed to produce the results on the fixed granularity of its instructions. However, the proposed reconfigurable design does not need to compromise the performance of required computations because it implements only *currently* needed functionalities in hardware, thus reflecting lively aspects of the environment. Due to this reason, the reconfigurable systems can reduce hardware cost by adapting its form for the tasks that are imminent from its time scale, where the remote or static part of tasks can remain to be optimized and unchanged throughout the life time of the running applications.

## **1.2 Background**

This section studies the uprising reconfigurable computing systems from various aspects: trends in embedded systems, target applications, and design methodology.

#### 1.2.1 Embedded systems

In general, embedded systems are designed to perform a specific task in the most effective way. Thus, embedded systems should be cost conscious. To name a few embedded systems, they are:

- Terminals for wireless communication termination for cellular, WLAN or mobile satellite access, QAM based terminals [4];

- Setup boxes for fixed network access X-DSL twisted pair, CATV or LAN access;

- Video and image processing applications MPEG-1/2/4 [5], teleconferencing and HDTV).

Today, these types of applications tend to co-exist in a consumer device. For example, a cellular phone can typically carry all of the above tasks. The same trend is increasingly found in many systems, standards and protocols.

The design applications (i.e., functions) which are targeted for the embedded systems increasingly require more complex functionalities with real-time and computation-intensive operations that can not be fulfilled by instruction-driven architectures (i.e., ISAs). At the same time the functionalities often become too diverse to be satisfied by Application Specific Integrated Circuits (ASICs) because of high cost associated with ASIC implementation<sup>4</sup>.

As the advent of process technology reaches the level where the programmable fabrics can consist of billons of logic gates, they become feasible to implement large and complex System-on-Chip (SoC) designs which were only possible by ASIC implementations. Furthermore, the **programmable fabric-based devices** can *provide a form that reflects the complex (dynamic) nature of today's applications.*

## 1.2.1.1 Electronic system level design

Electronic System Level (ESL) design methodology is in critical need of tackling complex design problems and improving design productivity. To speed up high-quality hardware implementation using billons of logic gates and enable fast and accurate design space exploration, the research efforts should be devoted into developing an ESL methodology. To address the speed, power, and interconnect challenges, the ESL methodology has to take meaningful physical information from potential hardware and plan the physical layout of a functional implementation. One direction is to incorporate physical planning in as early as possible, thus resulting a combined synthesis and layout optimization. Our proposed **reconfigurable system's design abstraction** that *takes the multiple-functionalities of the applications on to the planning stage of the system's architecture* can achieve this goal.

<sup>&</sup>lt;sup>4</sup> Cost analysis of ASIC vs. FPGA is given in the Chapter 3.

## **1.2.1.2 Field Programmable Gate Array**

The most successful example of a programmable fabric is the Field Programmable Gate Array (FPGA). Because of diverse functionalities and genuine structure that an FPGA provides, the design applications may have dramatically different user requirements in terms of performance, power, computational throughput, etc. To satisfy the requirements of various applications, the generations of FPGA devices have been developed to contain and support a large number of heterogeneous IP cores. As the programmable devices evolve to meet the requirements of today's applications, the layout needs to deal with the heterogeneity of the reconfigurable devices, core topology, and the specific memory and interconnect structures.

Nonetheless, due to the homogeneous logic structure that the **programmable fabrics** (e.g., run-time reconfigurable FPGAs) employ, they inherit a few advantages that can be beneficial for the ESL designs:

- *Reusability* synthesized blocks can be reused in different designs without recurring additional design costs, thus creating higher design productivity.

Conversely, processing resources can be reused for various functionalities that are executed at different times to reduce the system costs.

- *Adaptability/flexibility* allows coping with design errors and error detection and correction and accommodates last-minute changes and updates that are frequently occurring in communication and multi-media standards.

### **1.2.2 Target Applications**

Even though programmable fabrics provide very attractive advantages, the design costs and efforts associated with realizing a reconfigurable system is not trivial. Therefore, it is crucial to mainly focus on the class of applications with which the hardware design costs are justifiable and where the performance demands can not be met with other alternatives.

#### **1.2.2.1 Real-time applications**

A real time system is where its timing behaviour is as important as its functional behaviour. A real-time computing system is always associated with the real-time constraint that is a short time during when the system must produce the results as the response to an event.

Due to its *predictable timing behaviour*, the **real-time system** is used at every corner of all industries: an anti-brake system, ATM [6] and SONET network nodes [7], MPEG-4/7/21 encoders [8], an airplane controller and a cellular node [9]. They are normally classified as one of the following categories: control, adaptive and reactive systems. These applications have different timing requirements due to the environment that they interact with.

#### **1.2.2.2 Stream applications**

The computing system with which this thesis concerns is characterized by the stream data. Due to the complexity of the data set that the system deals with (i.e., multi-dimensional arrays), parallel (or concurrent) computation must be utilized to produce the expected results within a given time.

### 1.2.2.3 Characteristics of real-time and stream systems

The embedded systems that deal with real-time and stream applications show a subset of the following characteristics.

**Integration of multiple functionalities.** It summarizes the trends of SoC that implements multiple functionalities to realize a complete electronic system that can be compact and portable by reducing area, power and cost. Because of the complexity that today's systems deal with, the system design methodology needs to reuse invariable task level designs and raise design abstraction.

**Limited dynamism.** Real-time systems show only a limited dynamic character within calculated variations (e.g., buffers). Since prior system knowledge makes an estimation of system resources possible, the system resources can be allocated at compile time, resulting in an optimized solution.

**Timeliness.** Real-time systems can be associated with timing constraints that are different in nature. They are concerned with system response time interacting with the environment. The response time often decides the bandwidth of I/O signals that the system needs to allocate. Their characteristics can be represented as input-to-output latency and throughput. The interactions between the environment and the system as well as the communication among internal components are subject to timeliness of the realtime characteristics.

**Structured Data.** Regarding the timeliness of the real-time system, one assumes that our application has the associated multi-array structure that is bounded by the timing constraints. Structured data, so-called *"stream"* works as prior knowledge to estimate the computational requirements of the system.

The real-time and stream systems can be much more cost-effective than ASIC counterparts when they are designed with a novel architecture synthesis methodology that reflects the multiple functionalities of applications at the system level. The combination of the aforementioned traits makes the real-time and stream applications more applicable to be designed with reconfigurable systems.

### 1.2.3 Reconfigurable systems

One recognizes that each application is unique in its requirements. Thus, instead of providing a fixed architecture that is unique for a particular application (i.e., ASIC) or a fixed processor that is optimized for a set of general instructions (i.e., ISA), programmable fabrics (e.g., FPGA) are utilized to provide a system that can accommodate multiple functionalities of particular applications via reconfiguration.

#### 1.2.3.1 Reconfigurable system design flow

To facilitate the programmable fabrics effectively for multi-task and multi-mode applications, there is a need for modeling. Because a symbol cannot represent all the aspects of the element, modeling inevitably involves a process of abstraction. One describes the design flow of the reconfigurable system by four abstraction levels. **System level.** In the first stage of the design flow, one focuses on correct identification of system interaction with the environment. This stage determines what Input/Output ports are necessary and how they should be characterized (e.g., rate, respond time, deadline, latency, protocols, etc). The system ports are tied with the responses that are considered in the algorithm level.

**Algorithm level.** After the boundary of the system is decided, the reactions of the system are determined depending on the characteristics of real-time and stream data. Then we focus on a correct functional specification of the design. In this stage there still can be design exploration relating to transformations and refinement of the data and their interpretation by the system.

**Task level.** After the algorithm level, the designer ends up with an optimized system specification consisting of a number of concurrent tasks, annotated with a number of timing requirements which define the boundaries for temporal correctness. The concurrent tasks are interconnected by the fixed interfaces that can tolerate limited dynamism occurring due to the timing variation of results. Then, temporal boundaries are assigned by the *system level control data* that differentiates temporal functionality of the system.

**Network level.** Each level should be concerned with technological limitations. Due to the physically imposed constraints under deep submicron geometry devices, today's systems put utmost importance in physical limitation of the system such as placement, routing, layout, etc. The existing systems (e.g., micro-network, network-on-a-chip, etc.) attempts to solve the physical problems of communication by imposing network-level and pre-constructed architecture. Our approach does not suggest any novel solution to the physical constraints but uses an ad-hoc approach to provide a "*micro-network*" solution. One assumes that the system consists of two routing structures that are distinctively built for global communication between coarse tasks and local communication designed for concurrent operations within the tasks. Reconfigurable system design flow should be able to account for the physical constraints and to reflect the physical specifications into the system level design.

## 1.2.3.2 Reconfigurable system architecture

The architecture of a computer illustrates what the computer does. From the architecture of the computer, the user should be able to perceive the conceptual structure of the computer. For this reason, the system is considered as the layered structure of subsystems keeping the hierarchical view of functionalities. The layered structure of intercommunication permits the network of elements to be viewed as one logical entity. The layered structure provides independent services that allow the insertion/omission of layers based on the necessity of services [10] without affecting the overall functionality

of the system. Services can be tackled at each layer to employ optimal and tractable solution [11].

To provide the flexibility of implementing multiple functionalities and the reusability of processing resources, the service that the system needs is dynamic reconfiguration. Since the flexibility and reusability requires built-in service hardware and interconnects between components, the system is implemented into three layers: System-level, Network-level and Micro-level architecture.

- System-level architecture: specifies the reconfiguration mechanism and places the necessary service hardware (e.g., configuration loader, component library, configuration interfaces) for reconfiguration. Thus, it can estimate the reconfiguration overhead that can be used for deciding applicable applications.

- Network-level architecture: deploys appropriate network elements and layout interconnections to ensure reliable communication through specifications of modular blocks.

- **Micro-level architecture**: creates and establishes modular block components in a library for a given technology, thus enabling model-driven virtual assembly of components.

There are a few differences that the proposed reconfigurable system makes compared with others. The network architecture is unique in a sense that it is task-driven. As tasks are inserted or removed from the scene of workload, the network architecture itself reflects interconnections between tasks (and/or modular blocks constituting a task). As long as the tasks stay in the same format, the network architecture preserves its topology throughout its execution. Hence, the dynamic partial reconfiguration is applied to the region of a reconfigurable block that requires altering the structure of logics (e.g., Sobel, Laplacian or Canny algorithms for edge detection). This approach ensures the minimum reconfiguration overhead while guaranteeing on-going operations of other blocks.

When the architecture is modeled based on immediate application and associated requirements, the reconfigurable system can reflect the optimal solution for the given application which is interpreted by the hierarchical structure of multiple functionalities in the application. The proposed system is elaborated under the context of predefined architectural synthesis that is task-driven. The design procedure such as run-time Place-and-Route is excluded to keep the complexity of hardware operating system low and to allow heterogeneous structure of network architecture that is workload-driven.

### 1.2.3.3 Reconfigurable system model

The most common way is to think of the system as a collection of simpler subsystems. If the subsystem represents a particular application, then a group of subsystems can create a complex system that has multiple functionalities. A subsystem should possess no ambiguity and it also should be complete, comprehensive and easy to parameterize.

The (sub) systems should be able to generate specifications by being described in a particular language. A language can capture many different models, and a model can be captured in many different languages. Our models provide abstractions of a physical system and applications that allow system designers to partition the system by ignoring extraneous details while focusing on only relevant ones. Extraneous details constitutes

building modular blocks in a size (i.e.,  $<50,000 \sim 100,000$  gates [12]) on a specific technology to ensure that the module achieves required functionality without facing timing-closure problem and deep-submicron (DSM) effects (e.g., RC delay, noise, interconnect delay and drive current). Relevant details signify the ongoing efforts of SoC to employ network into a system. However, there is significant difference in their objective between network in LAN or WAN level and network in a chip level. LAN or WAN network is designed for the systems to reduce the number of interconnections because the system cost heavily depends on the number of interconnects. The "micronetwork" mainly concerns how reliably network elements can communicate because of problems raised from characteristics of data path and data pattern within its medium. Traditionally the main design technology for real-time and stream application has been ASIC whose main focus had been to minimize gate resources by applying global optimization. However, the technology seems to push towards subsystem level taxonomy rather than global optimization when there are many logics available and verification is hard to come by.

The purpose of the reconfigurable system model is to imprint the high-level structural view of applications onto physical aspects of a system by dynamic reconfiguration. The reconfigurable system model consists of a set of configurations and associated system events that trigger the transition between configurations. The system's temporal behaviour is explicitly expressed by applications, threads, tasks and modes<sup>5</sup> and implemented by reconfiguration via system events.

<sup>&</sup>lt;sup>5</sup> Refer to section **2.5** for more information.

## **1.3 Objectives**

Traditionally, the reconfigurable systems (e.g., FPGAs) have been used as the glue logic or prototyping system mainly due to its logic density. As the logic density increases there seems a broadening niche market that exists for the reconfigurable systems. However, for the idea of reconfigurable systems to be successful, one needs to accomplish the following:

- Adapting run-time programmable fabrics to reflect the demands for multifunction capability for cost-sensitive devices;

- Instituting Virtual Hardware Component (VHC) Library to enable fast and correct assembly of reconfigurable systems;

- Establishing the *system-level* design methodology to recognize multi-function applications that can benefit from the reconfigurable design approach;

- Developing systematic methods that enable the construction of workloadspecific multi-task and multi-mode architecture;

- Enabling on-chip assembly mechanism for dynamic adaptation of multi-task and multi-mode workload;

- Determining a cost-effective reconfigurable granularity depending on the dynamic nature of the multi-function applications.

Many of these objectives bring the fundamental changes into the existing system design flow. By investigating many aspects of electronic digital systems and market

trends<sup>6</sup>, this thesis attempts to provide the reason(s) why it is necessary to use dynamic reconfiguration to express systems' multi-functionality and why a new architecture synthesis methodology is necessary to realize their counterparts in hardware.

Because the thesis aims to establish a new architecture synthesis methodology for building a cost-effective reconfigurable system, the author uses the system cost matrices to prove the advantage of reconfigurable design approach throughout the thesis. As the thesis proceeds, the architecture of the reconfigurable system will begin to emerge with more details being added to each chapter of the thesis.

# **1.4 Contributions**

Reconfigurable computing, with the usage of programmable fabrics as the platform, offers a much more effective solution to address the multi-functionalities of today's applications and to reduce the system cost by reusing costly hardware. However, the reconfigurable system design encompasses much more than just reflecting dynamic changes in the applications.

In this thesis, a novel architecture synthesis methodology is developed to costeffectively implement a multi-task and multi-mode workload. The methodology identifies the multi-task and multi-mode workload and divides the workload hierarchically according to the dynamic characteristics of the environment. The dynamic characteristics

$<sup>^{6}</sup>$  To find out what aspects and market trends are considered, refer to Chapter 3.

of the environment are modeled as the configuration events<sup>7</sup>. Then the methodology brings the identification to structural and physical representations of the reconfigurable system which associates the physical layout of the programmable device with the multitask and multi-mode workload. The main novel contributions of this thesis are as follows:

- A new system-level design abstraction of a multi-task and multi-mode workload to bring structural, physical and behavioural specifications together;

- A novel partitioning method to construct an optimal system-level architecture that integrates static and dynamic components together;

- A new procedure to estimate an appropriate reconfiguration granularity.

The novel architecture synthesis methodology starts from the concept of virtualization of programmable hardware that enables the re-usability of pre-designed components. The cost-effective reconfigurable system can be realized based upon the availability of Virtual Hardware Component (VHC) library where the parametric search of components for the reconfigurable system can be systematically accomplished for a large pool of VHCs. With the suggested parametric search method<sup>8</sup>, the reconfigurable system can construct an optimal system that is assembled with pre-synthesized VHCs in the library. To complete the assembling steps of the reconfigurable system methodology, the system needs to provide detailed parameters that result from the steps of the architecture synthesis methodology.

<sup>&</sup>lt;sup>7</sup> The configuration events presumably contain the dynamic request of the environment for different functionalities.

<sup>&</sup>lt;sup>8</sup> It offers faster computation than other search methods. For details, refer to the Chapter 4

Based on the detailed specifications of a multi-task and multi-mode workload and the conditions of real-time stream applications, the thesis proposes the novel architecture synthesis methodology to achieve a cost-effective system solution. The Multi-task Adaptive Reconfigurable System (MARS) platform is constructed to analyze the implementation of dynamic functional changes and to analyze the cost benefits of the proposed methodology. In the implementation:

- The feasibility of on-chip assembly via run-time reconfiguration is demonstrated;

- The procedures for on-chip self-assembly is developed and implemented;

- The concept of run-time reconfigurable system based on static architecture is created;

- The dynamic reconfiguration of various tasks (i.e., VHCs) driven by configuration events is demonstrated.

#### **1.5 Organization of Thesis**

The remainder of this thesis is structured as follows. **Chapter 2** conducts a broad survey of reconfigurable approaches that classifies the reconfigurable systems based on their view point. As a necessary supplement, **Chapter 2** investigates the architectural evolution of programmable devices using Xilinx Dynamic Reconfigurable FPGAs as a case study. **Chapter 3** explores the current market trends and correlates system costs of ASICs and FPGAs. It also shows how FPGA systems become more cost-effective as the market trends become more aggressive. **Chapter 4** proposes a methodology that explores

various architectural spaces and demonstrates how this method obtains faster results for building a large amount of Virtual Hardware Components (VHCs) for the VHC library. **Chapter 5** presents a new architecture synthesis methodology that introduces a new design flow for identifying a multi-task and multi-mode workload, constructing a static architecture and defining the optimal reconfiguration granularity. **Chapter 6** encompasses the implementation details of a reconfigurable system using the optimized static architecture and acquired reconfiguration granularity via a Xilinx Virtex-4 FPGA platform. **Chapter 7** analyzes the experimental results. Then, **Chapter 8** summarizes the final outcomes and reports on possible future research directions.

#### Chapter 2

# **Related Works and Overviews of Reconfigurable Systems**

## **2.1 Introduction**

There are many computing approaches that can be classified as Reconfigurable Computing (RC). Many of the RC research have focused on providing the hardware solutions for different architectural problems. However, their attention was not paid on how to optimally design a RC system for a particular application. As the applications increasingly become computing intensive and complex, the cost of a computing system becomes too expensive to implement or manufacture in a conventional platform. It becomes necessary that a new system level design methodology needs to be combined with reconfigurable devices to provide a cost-effective system solution.

In the course of searching for an application-centric RC design methodology, one must first take a look at the broad classification of RCs, and then define some terminologies used for classification and the underlying domains of applications. To summarize the architectural centric research efforts, the specific comparisons of the RC platforms are presented according to their architectural characteristics. Finally, we explore a system design methodology of how to optimize a particular set of applications for the given RC platform.

#### 2.2 Motivation

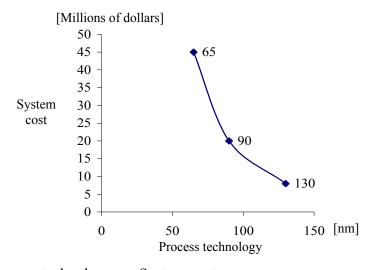

Moore's prophecy was widely adapted to justify the success of the semiconductor industry for the past 30 years. It states that functionality of chip should increase twice every 1.5 to 2 years. His prophecy was very attractive not only because of increase in logic density but also because of "*doing it at the same price*". Entering Deep Submicron process technology acclaims the difficulties of keeping the manufacturing costs the same, which are associated with new lithography tools, unreliable mask accuracy and multiple emerging technologies [13]. Moreover shortened time-to-market and hastened product life cycle put pressure on reducing test and verification, and R&D periods for increasingly complex systems [14]. Figure 2-1 shows a typical example of high-end design costs associated with the process technology that shrinks as the time progresses [15].

Figure 2-1: Process technology vs. System cost

We recognize that there are the hurdles to provide the promise of Moore's law with the existing computing systems. In order to solve the riddle of *"doing it at the same price"*, we look into an unconventional solution, *Reconfigurable computing*.

#### 2.3 Reconfigurable Computing

Reconfigurable computing (RC) can carry many different meanings. However, we believe RC is a computing paradigm that can integrate the flexibility of software into the parallel computing fabrics. The main attraction of the approach is the capability of *"tailoring"* reconfigurable computing fabrics while exploiting the performance of the available algorithms from utilization of parallel processing resources. The system can also reduce the costs by reusing valuable processing resources at run-time. The current application trends of continuously evolving multi-media and network standards showcase the benefits that are applicable via reconfigurability.

However, reusing hardware requires "*virtualizing*" processing resources – more precisely modeling. Virtualization in modeling requires establishing higher levels of abstraction (i.e., system-level abstraction). The approach with a *system-level abstraction* allows the reconfigurable system to *reuse hardware spaces via coarse control flow* while accommodating fine data flow with continuous execution of programmable parallel fabrics.

The system-level design should be written with the implementation concerns that satisfy the requirements of the underlying applications. In order to reflect technological and algorithmic limitations onto the system at early stage of the system design, it first needs to be concerned with the following topics and recognize the differences that exist between the reconfigurable systems:

- How to describe major blocks (hardware, netlist or hard/soft description);

- How big they should be (gate-level as fine granularity, function level coarse granularity, 50K gates – physical limitation, Network node – abstraction level or application specific);

- How they are connected (SoC BUS, NoC or P-to-P) and they need to communicate.

The goal of our approach is to provide a task-specific hardware system that can respond to the current requirements of applications while reducing system cost by reusing the processing resources for multiple tasks over times. Even though our solution focuses on its effectiveness towards computing intensive applications such as real-time and stream applications, we will explore various types of the RC systems. Each type of RC renders the different merits and employs the architectural choices that target different types of applications. We will start by categorizing the RCs by widely renowned fields.

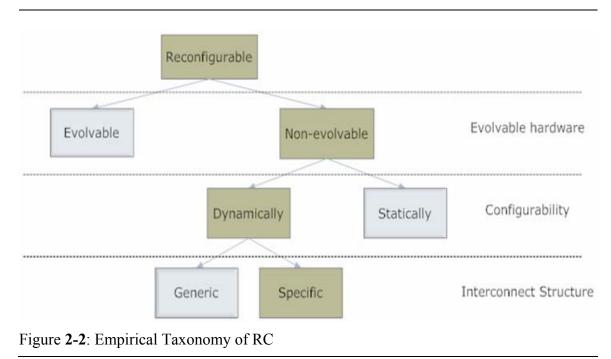

# 2.4 Taxonomy of Reconfigurable Computing

Many different areas of applications have adapted reconfigurable computing as a tool to create a new computing paradigm. The classification of these approaches leads us into a focused study of RC's promises and problems associated with the underlying applications. The taxonomy of RC is depicted empirically as in Figure **2-2**.

Under the umbrella of reconfigurable computing, the reconfigurable systems can be divided into evolvable and non-evolvable hardware systems. When a system is evolvable, it generally contains homogeneous cells that reconfigure their own interconnects by simple rules to achieve the desired functionality. Conversely, nonevolvable systems have pre-fixed structure that is dictated by human guidance. Nonevolvable hardware systems can be further divided with respect to how the system applies changes – reconfigurability. Once reconfigurability is chosen, we pay a visit to the structures of communication – generic or specific structure. It is our interest to investigate the reconfigurable computing systems that fall in the path of the gray shaded boxes.

#### 2.4.1 Evolvable Hardware

The RC can be first divided into evolvable and non-evolvable hardware (EHW and non-EHW). The EHW is a research area that looks for a methodology to obtain an optimal presentation by adapting its own structure to the environment [16] [17]. The main focus of the EHW is the evolutionary computation to design specialized circuits without explicit guidance of users [18], so-called embryonics [19].

The EHW borrows the conceptual understanding of how biological beings evolve and adapt to the environment – so-called Bio-inspired systems. Especially, it identifies that the growth and the operation of all living beings are the interpretations of how their unit cells react to one another (e.g., genome). The start of the embryonic is based on the hypothesis of the environment that is assumed to be homogeneous cellular array that evolve its state and values over time [**20**].

Generally speaking, the EHW starts by embedding fundamental rules that all entities of the EHW follow. The EHW possesses an efficient mechanism to adapt cell configuration and interconnections via enabling dynamic and autonomous reconfigurations. Then, based on the specifications of the desired circuit, the EHW starts to evolve towards the optimal circuit via self-reproduction. The EHW also can explore fault-tolerance architectures via self-healing (or self-repair) mechanisms [**21**].

However, the complexity of circuits that are synthesized using the EHW is normally limited at the functional level due to the time that takes to render the optimal results that are significantly inferior with other approaches. Additionally, unpredictability of time and quality of the design raises the reluctance to use the approach in many areas of applications. On the other hand, the non-EHW approaches normally result in predictable performance and timing closure depending on the complexity of the algorithms and the communication bandwidth. We pay attention to non-EHW (manguided) systems that can be reconfigured to achieve higher cost effectiveness.

## 2.4.2 Non-EHW systems

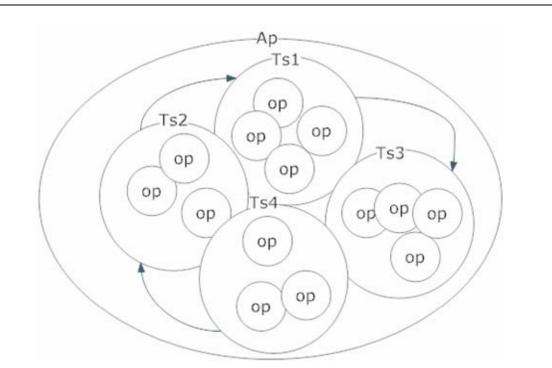

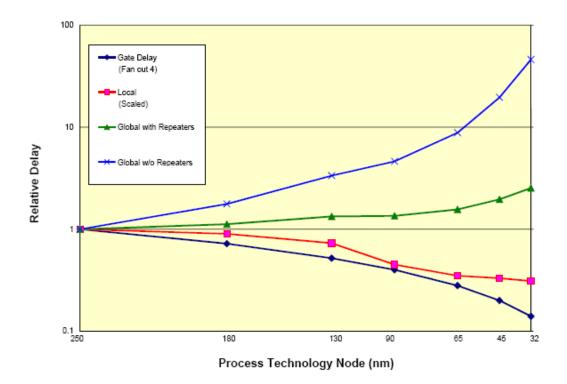

Once the EHW is excluded, the non-EHW reconfigurable systems can be boldly divided into two categories, *dynamically* reconfigurable and *statically* reconfigurable systems. In order to distinguish how these categories play a role in dealing with tasks, we illustrate the hierarchy of the application as shown in Figure **2-3**.

Figure 2-3: A typical example – Hierarchy of Spatial Computation (Ts denoting a task, Ap denoting an application and op denoting an operation)

It is first assumed that every application is fundamentally comprised of operations that are arithmetic or logical. Associated operations are grouped together to create a *task*. Each task is independent in a sense that they do not use output(s) of operations from other task(s). Yet, they are linked by input(s)/output(s) of other task(s) or the system to map functional requirements of the application. At the same time, excessive data flow might demand adequate control by implementing internal or external memories to contain required data by tasks. Once all interactions and communication between tasks are arranged, a higher level of computation can be formed. An application is a set of tasks that are connected (or disjointed) for the system at times. The application essentially portrays a snapshot of currently required operations. The connected set of tasks in an application is referred to as a *thread*. The application may contain many threads.

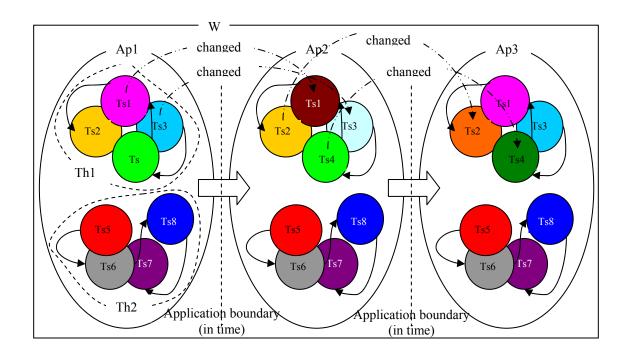

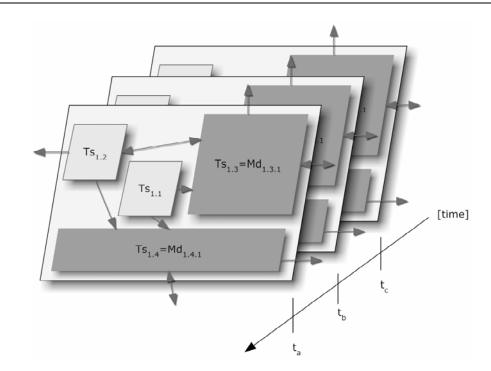

Complex systems generally require multiple applications to be available as shown in Figure **2-4**. Depending on the physical and timing requirements, there can be different approaches to arrange the applications on a device – where the arrows indicate the time displacement of applications where they are functionally different. Depending on the level of change necessary, the designers must navigate between the choices of systems to reflect the requirements and produce an optimal solution.

As the name – Application Specific Integrated Circuit (ASIC), states, the ASIC is the best solution when it is *"application specific"* and fixed. Because the ASICs physically implement all applications and optimize the common operations that are timely shared among the applications, there should be virtually no application change(s) necessary to minimize the hardware idling within the ASICs. If there is a considerable amount of changes necessary between applications, the ASIC can become too expensive to manufacture.

However, alternatively RCs can use *static (full)/dynamic (partial)* reconfigurations to reflect the necessary changes. If the timing allowance in the applications is more than the configuration time of a full device, then the full reconfiguration can be employed. If the applications have stricter timing constraint but require small changes, the RC can use *dynamic* reconfiguration to echo the changes in the application without halting the rest of system's functionality.

This thesis focuses on Dynamic reconfiguration that reconfigures a portion of the device for task-level changes without disruption of links between tasks.

Figure 2-4: Temporal Computation (Th denoting a thread and W denoting a workload)