## SYNTHESIS OF CLASSICAL AND NON-CLASSICAL CMOS TRANSISTOR FAULT MODELS MAPPED TO GATE-LEVEL FOR RECONFIGURABLE HARDWARE-BASED FAULT INJECTION

By

Raha Abedi Bachelor of Electrical Engineering Amir Kabir University of Technology Tehran, Iran, 2002

A thesis

presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Applied Science in the program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2005

© Raha Abedi 2005

PROPERTY OF RYERSON LAUVERSITY LIBR

#### UMI Number: EC52998

#### All rights reserved

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC52998 Copyright 2008 by ProQuest LLC All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

## ABSTRACT

Title of Thesis:

## SYNTHESIS OF CLASSICAL AND NON-CLASSICAL CMOS TRANSISTOR FAULT MODELS MAPPED TO GATE-LEVEL FOR RECONFIGURABLE HARDWARE-BASED FAULT INJECTION

Raha Abedi, Master of Applied Science, 2005

Thesis Directed By:

Dr. Reza Sedaghat, Electrical and Computer Engineering Department

One of the main goals of fault injection techniques is to evaluate the fault tolerance of a design. To have greater confidence in the fault tolerance of a system, an accurate fault model is essential. While more accurate than gate level, transistor level fault models cannot be synthesized into FPGA chips. Thus, transistor level faults must be mapped to the gate level to obtain both accuracy and synthesizability.

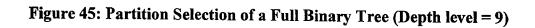

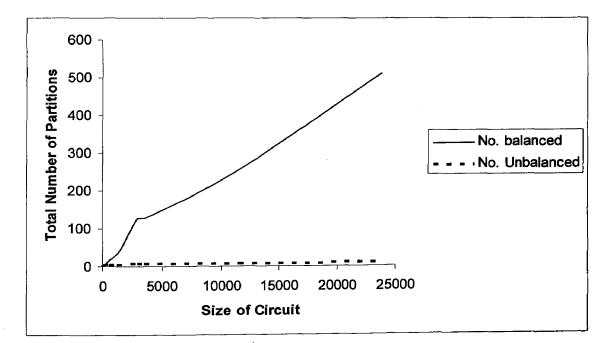

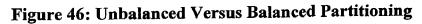

Re-synthesizing a large system for fault injection is not cost effective when the number of faults and system complexity are high. Therefore, the system must be divided into partitions to reduce the re-synthesis time as faults are injected only into a portion of the system. However, the module-based partial reconfiguration complexity rises with an increase in the total number of partitions in the system. An unbalanced partitioning methodology is introduced to reduce the total number of partitions in a system while the size of the partitions where faults are to be injected remains small enough to achieve an acceptable re-synthesis time.

## Acknowledgment

I would like to thank Dr. Sedaghat and OPR-AL lab for their contribution and support.

I would like to express my gratitude to my parents who have always immensely encouraged and inspired me. They are my great teachers in life.

I am grateful to my husband who guided and helped me all the way. Without his support this work would have not been accomplished.

n Ben di sente di stato - 人名马赫尔德斯特 医心疗疗法 . موجود المراجعين المراجع المحمول المحمول والمحمول المحمول المحمول المحمول المحمول المحمول المحمول المحمول الم الم المانية (1997) - المراجعة منهم (1997) - المحكمية والمراجع المراجع (1997) . The second s and the second • ....

## Table of Contents

| ABSTRACT                                                                                                                                               |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Table of Contents                                                                                                                                      | vi          |

| List of Tables                                                                                                                                         | . viii      |

| List of Figures                                                                                                                                        | x           |

| Nomenclature                                                                                                                                           | xii         |

| Chapter 1 Introduction                                                                                                                                 | 1           |

| <ul> <li>1.1 Accurate Fault Model</li> <li>1.2 FPGA-based Fault Injection</li> <li>1.3 Summary of Contributions</li> <li>1.4 Thesis Outline</li> </ul> | 2<br>3<br>4 |

| Chapter 2 Fault Modeling                                                                                                                               | 6           |

| <ul> <li>2.1 Logical Fault Model.</li> <li>2.2 Logical Fault Types</li></ul>                                                                           | 7<br>7<br>8 |

| Chapter 3 Transistor Level to Gate Level Comprehensive Fault Model Mapping                                                                             | 11          |

| 3.1 CMOS Physical Failures and defects                                                                                                                 | 11          |

| 3.2 Transistor to Gate Level Fault Mapping<br>3.2.1 Transistor Level Representation of Primitive Gate Circuits                                         | 13          |

| <ul> <li>3.3 NORn Complete Fault List Pattern</li></ul>                                                                                                | 15          |

| <ul> <li>3.3.3 Open Faults:</li></ul>                                                                                                                  | 25          |

| <ul> <li>3.5 Inverter Complete Fault List</li> <li>3.6 D-Latch Complete Fault List</li> <li>3.6.1 Input / Output Stuck-at Faults</li> </ul>            | . 29        |

| 3.6.2 Short Faults                                                                                                                                     | 32<br>34    |

| <ul><li>3.7 D Flip-Flop Complete Fault List.</li><li>3.7.1 Input / Output Stuck-at Faults.</li><li>3.7.2 Short Faults</li></ul>                        | . 36        |

| 3.7.3 Open Faults                                                                                       |                    |

|---------------------------------------------------------------------------------------------------------|--------------------|

| Chapter 4 User-Defined VHDL Library of Transistor Level Faults                                          |                    |

| 4.1 VHDL Presentation of Faulty Gates                                                                   |                    |

| 4.2 Creating Faulty VHDL Components Automatically                                                       |                    |

| 4.3 Designing a User-defined Library                                                                    |                    |

| 4.3.1 Existing Libraries                                                                                |                    |

| <ul><li>4.3.2 Library management</li><li>4.3.3 Aliasing the faulty components to WORK library</li></ul> |                    |

| 4.5.5 Anasing the faulty components to wORK notary                                                      | , <b></b>          |

| Chapter 5 Fault Injection into Circuit VHDL Description                                                 |                    |

| 5.1 Behavioural Feature of Hardware Languages                                                           |                    |

| 5.2 Structural Feature of Hardware Languages                                                            | ,                  |

| 5.3 Fault Injection in VHDL Description                                                                 |                    |

| Chapter 6 Binary Tree-based Partitioning Methodology                                                    | ,                  |

| 6.1 Balanced Versus Unbalanced Partitioning                                                             |                    |

| 6.2 Binary Tree Approach                                                                                |                    |

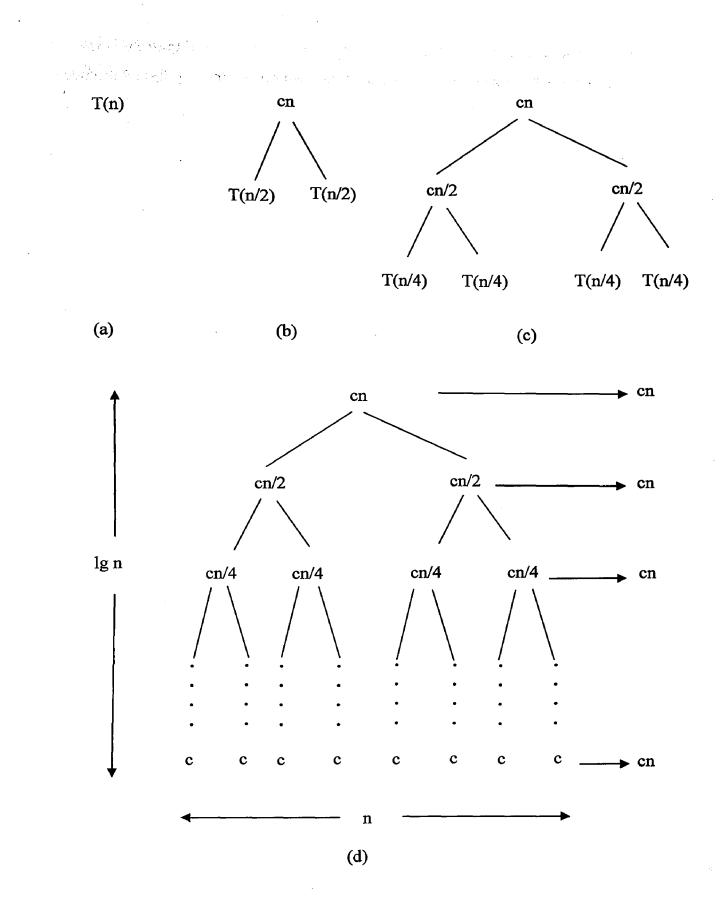

| 6.2.1 Analyzing Merge and Sort Algorithm                                                                |                    |

| 6.3 Generating VHDL Full Binary Tree                                                                    |                    |

| Chapter 7 Automating the Synthesis Procedure of Module-Based Dynamic I                                  | Partial            |

| Reconfiguration                                                                                         | ,                  |

| 7.1 Partial Reconfiguration                                                                             |                    |

| 7.2 Modular Design                                                                                      |                    |

| 7.2.1 Modular Design Entry and Synthesis Phase                                                          |                    |

| 7.2.2 Modular Design Implementation Phase                                                               |                    |

| 7.3 Automating the Synthesis Procedure of Module-based Fault Injection I<br>7.4 Experimental Results    |                    |

| Chapter 8 Conclusion                                                                                    |                    |

| 8.1 Research Contribution                                                                               |                    |

| 8.2 Future Work                                                                                         |                    |

| Appendices                                                                                              |                    |

| Appendix A: ORn Complete Fault List Pattern                                                             |                    |

|                                                                                                         | ****************** |

| Appendix B: ANDn Fault Pattern                                                                          |                    |

-...

x

## List of Tables

Table 1: A Short between PMOS Drain and Power

Table 2: Short between Two Inputs

Table 3: Short between One Input and One PMOS Drain

Table 4: When  $D_i$  is connected to  $D_k (1 \le k \le n-1 \text{ and } K \ne i)$

Table 5: When  $Di (1 \le i \le n-1)$  is shorted to Dn

Table 6: I<sub>iP</sub> Open

Table 7: I<sub>iN</sub> Open

Table 8: NANDn Input/Output Stuck-at-faults

Table 9: NANDn Short Faults

Table 10: NANDn Open Faults Categories

Table 11: NANDn Open Faults

Table 12: Inverter Input / Output Stuck-at Faults

Table 13: Inverter Short Faults

Table 14: Inverter Open Faults

Table 15: D-Latch Input / Output Stuck-at Faults

Table 16: Short between Each Node and VCC or the Ground in D-latch

Table 17: D-Latch Short Faults between Two Nodes

Table 18: D-Latch Open Faults

Table 19: Fault Free D Flip-Flop

Table 20: D Flip-Flop Input / Output Stuck-at Faults

Table 21: D Flip-Flop Short Faults

Table 22: D Flip-Flop Open Faults

Table 23: Total Number of Faults for Each Gate

Table 24: Total Number of Subroutines

Table 25: S38417 Partition Size

Table 26: ORn Input/Output Stuck-at-faults

Table 27: ORn Short Faults

Table 28: ORn Open Faults Categories

Table 29: ORn Open Faults

Table 30: ANDn Input/Output Stuck-at-faults

Table 31: ANDn Short Faults

Table 32: ANDn Open Faults Categories

Table 33: ANDn Open Faults

Table 34: Buffer Input/Output Stuck-at-faults

Table 35: Buffer Shore Faults

Table 36: Buffer Open Faults

.

1.17

지원감자

生生 一定 人名英格兰 医脊髓炎 化乙烯酸化化乙烯酸化乙烯

the second second second

tabara Maria 1934

. . .

. 1. 45314

S MARCH

Sec. Sec.

141

1.8.

### List of Figures

48月1日1日1月1月1日日本 1月11日日本1月1日日本1月

Figure 1: DRAM Cell

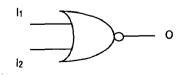

Figure 2: 2-input NOR (gate-level)

Figure 3: 2-input NOR (transistor-level)

Figure 4: I<sub>2</sub> Stuck-at-0 Fault of 3-input NOR

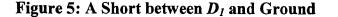

Figure 5: A Short between  $D_1$  and Ground

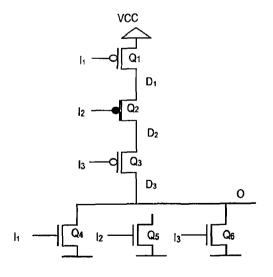

Figure 6: NORn Transistor Level

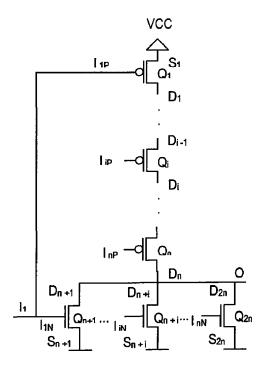

Figure 7: Faulty NOR3 Transistor Level

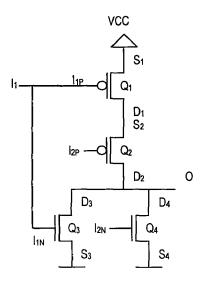

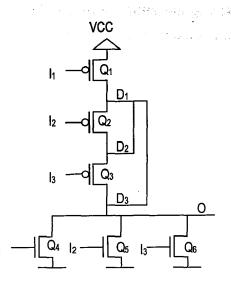

Figure 8: NANDn Transistor Level

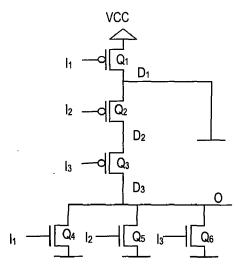

Figure 9: CMOS Inverter

Figure 10: T-gate

Figure 11: CMOS D-Latch

Figure 12: D Flip-Flop

" Figure 13: NOR2 Short Fault Synthesizable VHDL code

Figure 14: NOR2 open fault synthesizable VHDL code

Figure 15: Perl Program Section for NORn Input stuck-at-1 Fault

Figure 16: C17.vhd

Figure 17: C17.prj

Figure 18: Half-adder Behavioural Model

Figure 19: Half-adder Structural Model

Figure 20: Faulty AND2 Instantiation

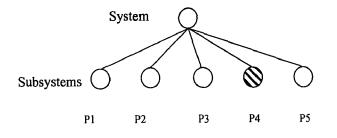

Figure 21: Balanced Partitioning

Figure 22: Balanced Partitioning Graph

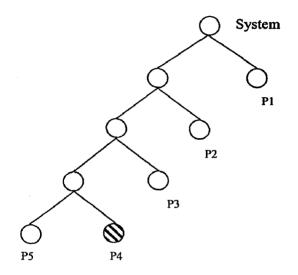

Figure 23: Unbalanced Partitioning

Figure 24: Unbalanced Partitioning Graph

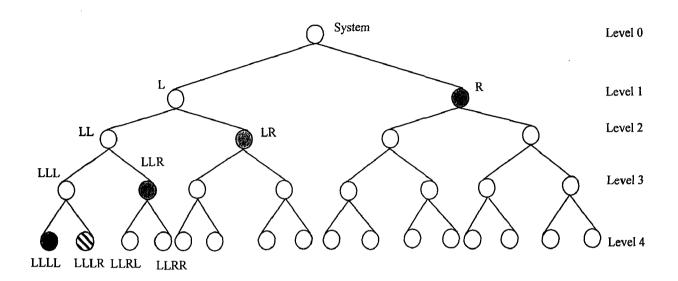

Figure 25: Full Binary Tree (Depth level = 4)

Figure 26: The Construction of a Recursion Tree for the Recurrence T(n) = 2T(n/2) + cnFigure 27: The Flow of Binary Tree Based Partitioning and Modification of the VHDL Code for Fault Injection

X

Figure 28: Modular Design Entry and Synthesis Flow

Figure 29: Circuit Name Assignment

Figure 30: S1238 Step 2

Figure 31: Verifying the Entered Branch Length

Figure 32: Verifying the Entered Branch Characters

Figure 33: Making a Partition Directory inside the Circuit Directory

Figure 34: Copy a Partition VHDL Code to Its Directory

Figure 35: An Example of Fault List for S1238

Figure 36: S1238 Circuit Directory

Figure 37: S1238 Partition LLLL XST Script File

Figure 38: S1238\_Partition\_LLLL Directory Files

Figure 39: Executing the Script File (xst.scr)

Figure 40: Size of Circuits

Figure 41: Full Binary Tree Depth Level of Circuits

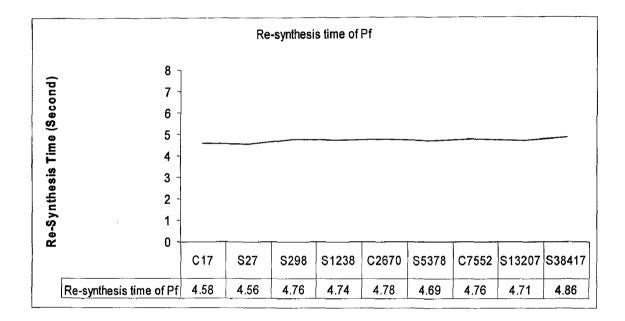

Figure 42: Re-synthesis Time of the Faulty Partition

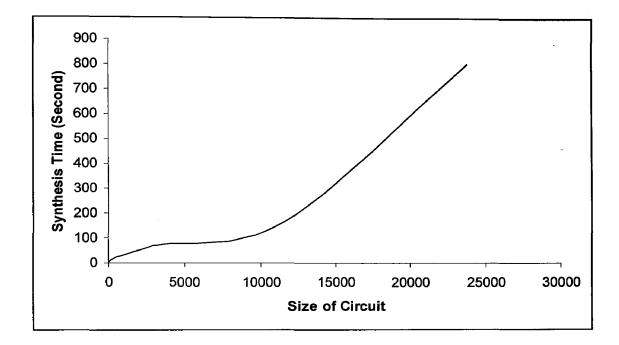

Figure 43: Benchmarks Synthesis Time

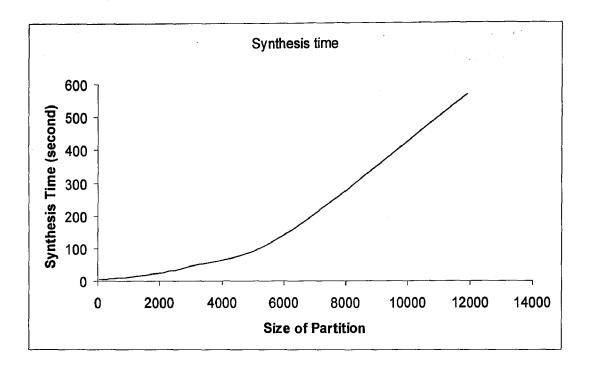

Figure 44: S38417 Partition synthesis time

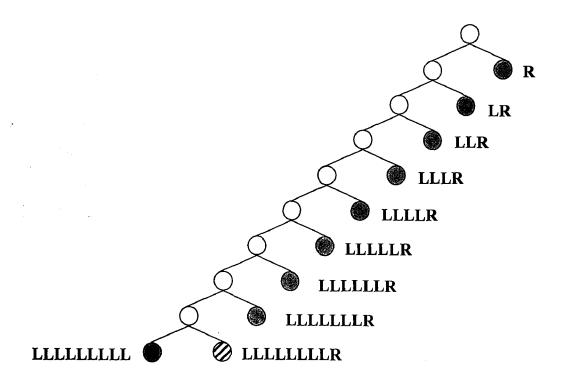

Figure 45: Partition Selection of a Full Binary Tree (Depth level = 9)

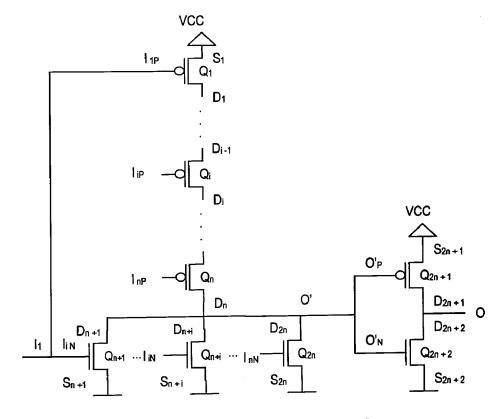

Figure 46: Unbalanced Versus Balanced Partitioning

Figure 47: ORn Transistor Level

Figure 48: ANDn Transistor Level

Figure 49: Buffer Transistor Level

## Nomenclature

| C                  | Constant                                      |

|--------------------|-----------------------------------------------|

| С                  | Clock                                         |

| D <sub>i</sub>     | Drain of the i <sup>th</sup> CMOS transistor  |

| G                  | Ground                                        |

| G <sub>T</sub>     | Total number of gates                         |

| i, j, k, n         | Integers                                      |

| Ii                 | i <sup>th</sup> input of a gate               |

| I <sub>iP</sub>    | Input of the i <sup>th</sup> PMOS transistor  |

| I <sub>iN</sub>    | Input of the i <sup>th</sup> NMOS transistor  |

| nC                 | Not Clock                                     |

| Ν                  | Total number of partitions                    |

| Pi                 | i <sup>th</sup> partition                     |

| P <sub>f</sub>     | Partition with injected faults                |

| Qi                 | i <sup>th</sup> CMOS transistor               |

| Q <sup>-</sup>     | State of Q at time t-1                        |

| Si                 | Source of the i <sup>th</sup> CMOS transistor |

| S-on               | Stuck-on                                      |

| S(P <sub>i</sub> ) | Size of the i <sup>th</sup> partition         |

| T <sub>i</sub>     | T-gate number i                               |

| ν                  | Logic value                                   |

| X                  | unknown                                       |

| Ζ                  | high impedance                                |

| $\oplus$           | XOR                                           |

| ∀i                 | For all values of i                           |

| <0   1>            | Zero or One                                   |

| γ                  | Cost function                                 |

ï

## Chapter 1

### Introduction

As systems become more complex it becomes increasingly difficult to provide comprehensive fault testing to determine the validity of a system. Hence, faults can remain in a system and manifest themselves as errors. Furthermore, faults may be introduced into a hardware system from external sources such as electromagnetic interference. Not only can components within a system fail, no transistor will function forever. These faults can ultimately cause a system to fail. The ability of a system to function in the presence of faults, i.e. to become fault tolerant, is a rapidly growing area of research. A fault tolerant system has the ability to respond gracefully to an unexpected hardware or software failure. The need for fault tolerant systems is driven by various factors such as extremely high reliability and availability needs, reduced life-cycle costs, and long-life requirements.

The second s

Most real-time systems must function with very high availability even under hardware fault conditions. To design a fault tolerant system many fault injection techniques to evaluate the dependability of the system have been proposed. In all of these techniques single or multiple faults are intentionally inserted into the system to study the behaviour of the system in the presence of faults.

Physical failures or defects in a circuit may cause faulty circuit behaviour and thus reduce the fault tolerance rate of the system. To evaluate the fault tolerance of a system, an accurate fault model is required. Next, an approach to inject each fault into the system is essential and finally, an adequate test pattern to determine if the fault has changed the behaviour of the circuit. We will focus mainly on defining an accurate fault model and a method of injecting faults into a system.

#### **1.1 Accurate Fault Model**

More accurate fault models are usually defined below the gate level. The major disadvantage of using a transistor level (low level) fault model is the performance degradation of fault simulation, fault emulation and test pattern generation [3]. Therefore, there is a critical need to map the transistor level fault model onto the gate level without any performance degradation, while at the same time obtaining an accurate fault model.

For many years the only practical approach has been based on the stuck-at fault model. However, problems arise in CMOS LSI and VLSI circuits. The stuck at fault model is not sufficient for systems that require high reliability or high availability such as pacemakers, ABS (anti-lock braking systems) in automobiles, or air traffic control. There are other types of physical failures and defects, i.e. short or open faults that disturb system performance.

There are many studies which model physical failure and defect in CMOS circuits. In [32, 33, and 34], the main focus is on modeling short faults between a gate and a source of one CMOS transistor in a circuit. A methodology to obtain a minimal set of faults is proposed in [35]. This methodology is based upon theoretical basis allowing the determination of the equivalence and dominance of non-classical CMOS faults. In [5, 36] short, open and stuck-at faults are presented for CMOS circuits based on simulation results and thoroughly cover open and stuck-at faults. However, the fault model they present only considers short faults for one transistor in the circuit at a time, such as a short between a gate and a drain of the same transistor. However, in [3] all the possible short faults are taken into account in the fault model, including connecting two nodes from different CMOS transistors.

In this research, all shorts that could possibly occur among transistors (e.g. a short between the gate of one transistor and the drain of another transistor) in the circuit in addition to all possible stuck-at and open faults are considered. By applying a complete version of accurate fault models [3, 5] to each gate to generate a complete fault list, it is revealed that the fault list for each type of primitive gate follows a specific pattern regardless of its number of inputs. The number of gate inputs can be used to calculate the total number of possible faults at the transistor level using general formulas presented in this research.

#### **1.2 FPGA-based Fault Injection**

After generating a fault model, software simulation and hardware emulation are the main techniques that researchers follow to inject faults into a system. Fault simulation provides a high degree of controllability [37, 38] and design mistakes in the fault-tolerant system can be detected and corrected at a very early stage in the design process [38]. However, the main drawback related to fault simulation is that it is time-consuming when many faults have to be injected in a complex circuit [39, 16]. For fault emulation a prototype of the system is needed. An advantage of prototyping is the possibility to perform "in-system" emulation before any manufacturing. Reconfigurable devices such as FPGAs are appropriate to implement and test the prototype. To cope with the time limitation imposed by simulations, it has been proposed to take advantage of hardware prototyping using FPGA-based hardware emulators [40]. Another advantage of emulation is to allow the designer to study the actual behaviour of the system in the application environment, taking into account real-time interactions of various hardware and software components [15].

FPGA-based fault injection has been an area of increased research. For example, [41, 42] discuss injecting faults through fault injectors for stuck-at faults and [43] applying a FPGAbased fault injection method through fault injection chain hardware. Another method is to inject faults by using scan-chain hardware for injecting bit-flip faults into flip-flop of the target system [44, 39, and 26]. In [21, 45, and 46] FPGA-based emulators have been used to only inject stuck-at faults for test pattern generation purposes without evaluating the faulttolerance of the system. Using run-time reconfiguration (RTR) for fault injection is another approach proposed by [47] to save time by reconfiguring only a few resources of the device. However, because this approach modifies bitstreams it is not capable of accessing the drain of specific CMOS transistor in the circuit to make it an open node or to short it to the others nodes of the circuit. This is due to the fact that bitstrams represent the Look Up Table (LUT) values of the circuit and not the gate level description. During the synthesis some gates may be mapped into other gates due to optimization. Therefore, there is no possibility to access the transistor level description of those gates to inject faults. The FPGA-based fault injection into switch-level of a model which is in abstraction level between gate level and transistor level is discussed in [48].

,

When an emulator is used, the initial VHDL description must be synthesizable. It is apparent that a transistor level fault model cannot be synthesized into FPGA chips. Therefore, the fault model mapping from transistor level to gate level has a critical role in our study for injecting transistor level faults into the FPGA.

In this work, first the transistor fault model is mapped to gate level fault model. Next, a method is described to inject this fault model into the FPGA by considering the advantages of module-based dynamic partial reconfiguration.

#### **1.3 Summary of Contributions**

This thesis contributes to the following areas:

- Generating a complete fault list of primary gates (NOR, NAND, OR, AND, Inverter, Buffer, D-Latch, D Flip-Flop).

- Presenting a fault pattern for each type of gate regardless of its number of inputs.

- Extracting a general formula for each type of gate to calculate the total number of faults according to the gate number of inputs.

- Generating automatically a faulty component library that represents the transistor level faults at a gate level description.

- Presenting a methodology to partition a high level (e.g.VHDL) description of a circuit to reduce the synthesis time as well as module-based circuit design complexity.

- Generating faulty VHDL partitions exhaustively and providing a data base.

- Automate the synthesis process of faulty and fault free partitions based on a desired fault list and modular design regulations.

#### **1.4 Thesis Outline**

The necessity of fault modeling as well as different fault classifications are discussed in Chapter 2. Chapter 3 presents a complete transistor to gate level fault mapping of primary gates and their related fault pattern as well as general formulas to calculate the total number of faults. Generating and automating a user-defined library based on the fault patterns from Chapter 3, is described in Chapter 4. In Chapter 5 the behavioural and structural VHDL description features are discussed and an appropriate approach to inject faults in the VHDL description of a circuit is introduced. A methodology of partitioning a system to reduce the synthesis time and system module-based complexity is discussed in Chapter 6. The automation of synthesis procedure based on modular design parameters and experimental results are presented in Chapter 7. Chapter 8 is dedicated to conclusions and intended future works.

I there are a set to a general to a set of the

## Chapter 2

## **Fault Modeling**

An instance of an incorrect operation of the system being tested is referred to as an observed error. Causes of observed errors may be design errors, fabrication errors, fabrication defects, or physical failures. Design errors can be detected and corrected at an early stage of the design process by simulating the design. Fabrication defects are not directly attributable to human error; rather, they result from an imperfect manufacturing process. Physical failures occur during the lifetime of a system due to component wear-out and/or environmental factors.

and dear a how we are a survey of the

e e contra de la contra de la

the constitution and the second se

In general, Physical faults do not allow a direct mathematical treatment of testing and diagnosis. The solution is to deal with logical faults, which are a convenient representation of the effect of physical faults on the operation of the system. The basic assumptions regarding the nature of logical faults are referred to as a fault model [1].

#### 2.1 Logical Fault Model

Logical faults represent the effect of physical faults on the behaviour of the modeled system. Given a logical fault and model of a system, we should be able in principle to determine the logic function of the system in the presence of the fault. Thus, fault modeling is closely related to the type of modeling used for the system.

The advantages of modeling physical faults as logical faults can be described as follows [1]:

• The problem of fault analysis becomes a logical rather than a physical problem.

- The complexity is greatly reduced since many different physical faults may be modeled by the same logical fault.

- Some logical fault models are technology-independent in the sense that the same fault model is applicable to many technologies.

- Tests derived for logical faults may be used for physical faults whose effect on circuit behaviour is not completely understood or is too complex to be analyzed.

A logical fault model can be defined in different levels of circuit descriptions. Transistor, gate, and RTL level of circuit descriptions, each have their own logical fault models. As mentioned, these fault models are related to the type of modeling used for the circuit.

#### **2.2 Logical Fault Types**

Faults can be categorized into two major groups of classical and non-classical faults.

#### **2.2.1 Classical Faults**

The classical faults can be categorized as follows [1, 2]:

- Single (line) stuck-at fault: The given line has a constant value (0/1) independent of the other signal values in the circuit. In many technologies, a short between ground or power and a signal line can make the signal remain at a fixed voltage level. The corresponding logical faults consist of the signal being stuck at a fixed logic value v (v = 0/1), and is denoted by stuck-at-v.

- Multiple stuck fault: Several signal stuck-at faults occur simultaneously.

For a circuit with k lines, i.e., k input signals and input/output elements, there are 2k single stuck faults, and 3<sup>k</sup>-1 multiple stuck faults. For a large combinational circuit with multiple outputs, almost all multiple faults can be covered by test patterns derived for single faults.

- Bridging fault: Two or more normally distinct points (lines) are shorted together. A short between two signal lines usually creates a new logic function. The logical fault representing such a short is referred to as a bridging fault. Input bridging can form a wired logic or voting model.

Input-to-output bridging can introduce feedback or cause oscillation or latching.

#### **2.2.2 Non-classical Faults**

In general, non-classical faults are categorized as follows [2, 3]:

• Pattern-sensitive fault: The presence of a faulty signal depends on signal values of nearby points (most common in DRAMs).

| 0 | 0 | 0 | $a = b = 0 \Rightarrow d = 0$                            |

|---|---|---|----------------------------------------------------------|

| 0 | d | b | $\mathbf{a} = \mathbf{b} = 1  \clubsuit  \mathbf{d} = 1$ |

| 0 | a | 0 |                                                          |

#### Figure 1: DRAM Cell

- Coupling fault: Pattern sensitivity between a pair of cells.

- Crosspoint fault: A PLA (Programmable Logic Array<sup>1</sup>) inherently has a device (diode or transistor) at every crosspoint in the (AND and OR) arrays, even if not used. The connection of each diode is programmed to realize the desired logic. A crosspoint fault can be caused by an extra or missing device.

- Transistor stuck-open fault: Transistor (switch) is always off, not controllable by gate input. This fault can turn the circuit into a sequential one. This type of fault is more difficult to test and needs a sequence of at least 2 tests to detect a single fault. Transistor stuck-open fault is unique to CMOS circuits.

- Transistor stuck-on fault: Transistor (switch) is always on, not controllable by gate input. This kind of fault can be caused by a permanently conducting transistor and also occurs in CMOS circuits.

- (Line) break (stuck-open) fault: An open wire.

<sup>&</sup>lt;sup>1</sup> PLA is an array of gates having interconnections that can be programmed to perform a specific logical function.

- (Line stuck) short fault: A short is formed by connecting points not intended to be connected.

- Delay fault: Propagation (transition) delays along a path (gate) that fall outside the desired limits are referred to as either path delay faults or gate delay faults.

- Function conversion fault: Defects inside a CMOS gate may result in an incorrect function of the gate. If there is a short between input and output of an inverter the gate is no longer inverting. Furthermore, conversion of an AND into a NAND, OR into NOR etc. is possible.

- Conditional fault: A conditional fault is defined as a fault which can only be detected if one or more conditions are satisfied. Each condition consists of a fixed logical value (0 or 1) at a specified mode. This kind of fault is defined for CMOS and it is similar to pattern-sensitive fault of DRAMs.

Stuck-open and stuck-on faults are transistor level faults; stuck-at, bridging, delay faults are gate level faults; pattern-sensitivity, crosspoint faults are function level faults.

Most of the non-classical faults can be mapped onto classical stuck-at faults [4], bridging faults and transition faults. The transition fault is based on the assumption that a transition at a gate never occurs in a combinational circuit. In a sequential circuit, transition does not occur within a clock cycle.

#### 2.3 Transistor level fault model

Let's see how a transistor fault can affect the behaviour of the circuit. In the presence of transistor faults or an interconnection wiring faults circuit will not function correctly. Many things can go wrong, leading to a variety of faults. A transistor switch can break so that it is either permanently closed or open. A wire in the circuit can be shorted to VCC or to ground, or it can simply be broken. There can be an unwanted connection between two wires. A logic gate may generate a wrong output signal because of a fault in the circuitry that implements the gate. CMOS logic circuits present some special problems in terms of faulty behaviour. The transistors may fail in a permanently open or shorted (closed) state. Many such failures manifest themselves as stuck-at faults. However, some produce entirely different behaviour.

For example, transistors that fail in the shorted state may cause a continuous flow of current from VCC to ground, which can create an intermediate output voltage that may not be determined as either logic 0 or 1. Transistors failing in the open state may lead to conditions where the output capacitor retains its charge level because the switch that is supposed to discharge it is broken. The effect is that a combinational CMOS circuit starts behaving as a sequential circuit [7].

As CMOS has emerged as an important technology for VLSI, testing of large CMOS networks has become a crucial issue. The classical stuck-at fault model assumptions are not sufficient for modeling certain faults that are specific to a CMOS-based VLSI technology. This applies particularly when systems with a high reliability or high availability such as space applications are considered. Depending on the technology, typical physical defects as such as CMOS stuck-open faults may not be covered by a stuck test set. Therefore, new fault models have been introduced at different description levels to increase the accuracy of fault modeling.

Transistor level fault model is more accurate than gate level fault model. However, its fault simulation, fault emulation, and test pattern generation are degraded in comparison to the gate level.

In order to maintain the efficiency resulting from gate level modeling while the accuracy of the fault model is increased, transistor to gate level fault mapping is required. Next chapter is directed towards a mapping of classical and non-classical transistor level faults to the gate level.

物品 化静脉 法有效 化分子 建立分子 化分子合金

10

## **Chapter 3**

## Transistor Level to Gate Level Comprehensive Fault Model Mapping

In order to have greater confidence in the fault tolerance of a system more accurate fault models are needed. An accurate fault model cannot be attained unless all faults in the transistor level (low level) are considered thoroughly. However, these transistor-level faults must be mapped onto gate level (higher level) so that the efficiency of fault simulation, fault emulation and test pattern generation on the gate level is not sacrificed. This chapter considers single physical failures for static CMOS primitive gates and shows their effects in the output behaviour in terms of gate level faults. We have found a specific fault pattern for each type of gate regardless of its number of inputs is proposed. All kinds of faults from stuck-at to short and open faults have been considered in these patterns. A general formula to calculate the total number of faults for each type of gate is extracted from these patterns.

#### 3.1 CMOS Physical Failures and defects

Failures in CMOS circuits can be classified into shorts, opens, and circuit degradation. Shorts are due to oxide breakdown and metal bridging, and are caused by static discharge and time-dependent defects, while metallization problems caused by electro-migration or electromechanical corrosion can produce shorts and opens. Degradations include threshold voltage shifts caused by ionic contamination, surface-charge spreading, and the trapping of hot electrons in the gate oxide. However, these degradations, if permanent, will consequently be translated into classical type of faults at the input(s) and/or output(s) [5].

It should be noted that 75 percent of the cases are shorts and opens, while the rest could be considered unobservable or insignificant [6]. Hence, physical faults of CMOS cells have been divided into two groups, namely shorts and opens. For example, for any two-input CMOS gate, the following faults are considered:

1) Short Faults:

- Short between gate and source in both p-channels;

- Short between gate and drain in both p-channels;

- Short between source and drain in both p-channels;

- Short between gate and source in both n-channels;

- Short between gate and drain in both n-channels;

- Short between source and drain in both n-channels.

- 2) Open (Floating) Faults:

- Open gate in both p-channels and n-channels;

- Open source in both p-channels and n-channels;

- Open drain in both p-channels and n-channels.

- 3) Input / Output Stuck-at Faults:

- Input #1 stuck-at-0 or 1;

- Input #2 stuck-at-0 or 1;

- Output stuck-at-0 or 1.

However, it should be noted that some faults are redundant, which consequently reduces the number of faults.

#### **3.2 Transistor to Gate Level Fault Mapping**

The complexity of integrated circuits requires that a practical approach to fault simulation, fault emulation, and test pattern generation be based on a higher level of circuit description. The adequate fault model depends on the desired accuracy for modeling the actual defects and the complexity of the circuit description. For years the only practical approach has been based on the classical stuck-at fault model and a gate level description of the circuit. The main reason is that fault simulators and fault emulators can handle the gate level descriptions efficiently and in a timely manner. However, the conventional stuck-at fault assumptions are not sufficient for modeling certain faults that are specific to some VLSI technology, especially, when certain physical failures such as shorts between two nodes or open nodes occur in CMOS technology [3].

The general idea of transistor to gate level fault mapping is to combine the accuracy of modeling faults at the transistor level with the efficiency of fault simulation, emulation, and test pattern generation based on gate level description of the circuit. The starting point in this research is to consider all the faults that can possibly occur in a transistor level description of the standard cell library [3]. The main focus of this study will be on static CMOS library.

In this study NAND, NOR, AND, OR, Inverter, Buffer, D-latch and D flip-flop cells are considered. For each cell the effect of each transistor level fault on the gate level fault model is determined using the results given in [3, 5]. By applying an accurate fault models to each gate (cell) to generate a complete fault list in this work, we have found that the fault list for each type of primitive gate follows a specific pattern regardless of the number of inputs. The number of gate inputs can be used to calculate the total number of possible faults at the transistor level using general formulas which will be described later.

#### 3.2.1 Transistor Level Representation of Primitive Gate Circuits

The accuracy such as internal nodes values cannot be reached by just considering a circuit at the gate level. Figure 2 shows a gate level NOR circuit. At the gate level, faults can only be injected or diagnosed on input and output pins. There is no way to access the gate internally to inject more faults, nor to observe its fault tolerance or diagnose the fault after its detection. Therefore, we must use the transistor level of primitive gates in order to cover more faults and obtain a more accurate fault model. Figure 3 shows the 2-input NOR (NOR2) transistor level circuit.

Figure 2: 2-input NOR (gate-level)

Injecting a fault in a CMOS gate may result in different output values according to different input combinations. The relationship between inputs and the faulty output shows the faulty function of the CMOS gate. For example, if  $I_I$  is shorted to  $D_I$  the output of NOR2 gate in Figure 3 will be:

的现在分词 化自动输送器 化合理合理 化合理合理 化合理

$$O = \begin{cases} I_1 & \text{if } I_2 = 0\\ 0 & \text{else} \end{cases}$$

The relationship between inputs and the faulty output will be thoroughly discussed in following sections for all possible faults in the CMOS gates.

Figure 3: 2-input NOR (transistor-level)

These relations between inputs and output follow a specific pattern regardless of gate input numbers for each gate. We will discuss and explain an example of this pattern for a NOR gate with n inputs in the next section.

こう 小学者

#### **3.3 NORn Complete Fault List Pattern**

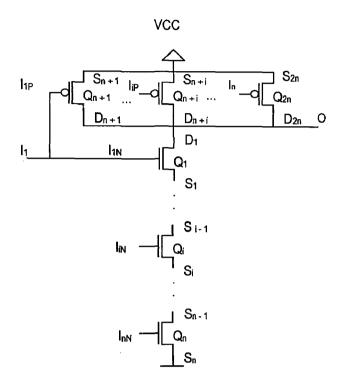

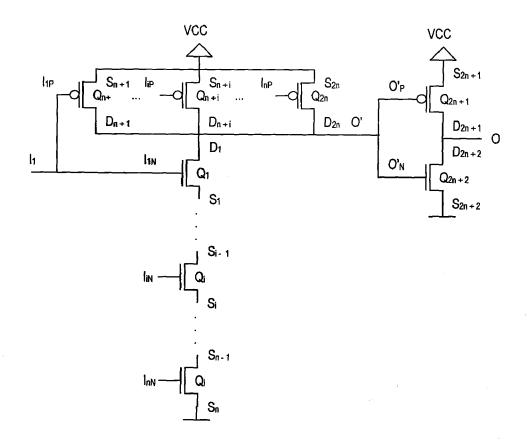

Figure 6 shows a CMOS NOR gate with *n* inputs. *n* is an integer where  $(n \ge 2)$ .  $I_i$  symbolizes one of the NOR i<sup>th</sup> input where  $(l \le i \le n)$ .

$I_{iN}$  and  $I_{iP}$  are the inputs of i<sup>th</sup> NMOS and PMOS transistors respectively. They are both connected to  $I_i$ . For stuck-at-faults and short faults  $I_i$ ,  $I_{iP}$  and  $I_{iN}$  function as the same node. Thus, they will be generally labeled as  $I_i$ . However, in the open fault case, they act as separate nodes.

The three groups of faults (stuck-at, short, and open) and their effects on the output of NORn are represented as follows with respect to the above assumptions:

#### 3.3.1 Input / Output Stuck-at Faults

NORn is faulty if either  $I_i$  or O is stuck-at-0 or 1. When  $I_i$  is stuck-at-1 it turns its NMOS on thus, the output is connected to ground and results in low output (O = "0"). In contrast, when  $I_i$  is stuck-at-0 it turns its PMOS on and NMOS off. Therefore, the faulty NORn gate still acts as a NOR gate but without  $I_i$  input. The output is the result of NOR( $I_1$ ,  $I_2$ ,...,  $I_{i-1}$ ,  $I_{i+1}$ ,...,  $I_n$ ). Figure 4 illustrates  $I_2$  stuck-at-0 faults. In this case  $Q_2$  is switched on and  $Q_5$  is switched off. Therefore, the output is the result of NOR with only two inputs of  $I_1$  and  $I_3$  (NOR( $I_1$ , $I_3$ )).

If (n = 2) and one of the two inputs is stuck-at-0 then the output will be the NOR of the remaining non-faulty input which acts as an inverter. When the output is stuck-at-0 or 1, it will no longer be dependent on inputs.

The total number of input/output stuck-at faults for NORn gate is (2n+2).

#### Figure 4: I<sub>2</sub> Stuck-at-0 Fault of 3-input NOR

#### **3.3.2 Short Faults**

The many types of short faults that may occur in a NORn circuit are categorized as follows:

1) Short between a PMOS drain and ground or power:

As far as output stuck-at-0 and stuck-at-1 are concerned, there is no need to analyze the  $D_n$  connection to ground and power due to the similarities in results. For any  $i \ (1 \le i \le n-1)$ ,  $D_i$  can be shorted to ground or power thus, the total number of faults for this category will be 2(n-1).

If  $D_i$  is shorted to ground, noted as  $(D_i \leftarrow \rightarrow G)$ , the output O will always be low. When the circuit is fault free by applying low inputs the output is connected to VCC through conducting PMOS transistors. Given the presence of a short fault between  $D_i$  and ground, the output will be connected to ground through the PMOS transistors located below the node  $D_i$  and the short between  $D_i$  and ground. This will result in a low value for the output of this faulty circuit. For the rest of the input combinations, where at least one input with a high value exists, i.e. at least one NMOS transistor is conducting; the output is forced to low again. Figure 5 illustrates  $D_1 \leftarrow \rightarrow G$  fault in NOR3 gate. When  $I_2$  and  $I_3$  are low  $Q_2$  and  $Q_3$  are switched on and the output is connected to ground through  $Q_2, Q_3$ , and  $D_1$ .

If  $D_i$  is connected to VCC,  $(D_i \leftarrow \forall VCC)$ , the circuit will behave differently with regard to its inputs. When all inputs are low  $(I_j=0, 1 \le j \le n)$  the output will be high. As soon as one of the inputs, connected to the PMOS transistor located above  $D_i$ , goes high it switches one NMOS transistor on and the related PMOS transistor off. In this case, a path is established between ground and VCC, through  $D_i$ , output and NMOS transistor. This condition takes the output to an uncertain value between 0 volt and VCC. The output is called stuck-on in this situation [5]. For the rest of the input combinations the output will be low while  $D_i$  is shorted to VCC. All the conditions are summarized in Table 1.

In fact Table 1 shows the output pattern with regard to input conditions when any drain of the n-input NOR gate is shorted to VCC. In Table 1,  $I_j = 0 \quad \forall \ 1 \le j \le n$  indicates all inputs from  $I_i$  to  $I_n$  are low. In this case the output is high.  $I_j = 0 \quad (\forall \ i+1 \le j \le n)$  denotes all inputs of PMOS transistors below the shorted drain  $(D_i)$  are low and  $(I_1 \parallel I_2 \parallel ... \parallel I_i) = 1$  indicates at least one of the PMOS transistor inputs above the shorted drain is high. In this case the output has an unknown value between 0 and VCC volt (stuck-on).

Figure 6: NORn Transistor Level

| Shore faults              | Input conditions                                                                                        | Faulty output (O) |

|---------------------------|---------------------------------------------------------------------------------------------------------|-------------------|

|                           | $I_i = 0  \forall \ 1 \le j \le n \text{ (means all inputs from } I_i \text{ to } I_n \text{ are low)}$ | 1                 |

|                           | $I_{j}=0  (\forall i+1 \le j \le n)$ $\&$ $(I \parallel I \parallel \parallel  I )=1$                   |                   |

| $D_i \leftrightarrow VCC$ | &                                                                                                       | S-on (Stuck-on)   |

|                           | $(I_1 \parallel I_2 \parallel \parallel I_i) = 1$                                                       |                   |

| L                         | For all other input combinations                                                                        | 0                 |

11 13 63

#### Table 1: A Short between PMOS Drain and Power

2) Short between two inputs:  $(I_i \leftarrow \rightarrow I_k \text{ where } l \leq k \leq n \text{ and } k \neq i)$

Assume  $I_i$  is shorted to  $I_k$ . The output is unknown when these two inputs have opposite values while the rest of the inputs are low. The circuit output can have a high or low value depending on the input combinations. The faulty output pattern for this kind of fault is shown in Table 2.

In Table 2,  $I_j = 0 \forall (1 \le j \le n \text{ and } j \ne i, j \ne k)$  denotes all inputs except  $I_i$  and  $I_k$  are low and  $I_i \oplus I_k = 1$  indicates  $I_i$  and  $I_k$  have different values. In this case the output is unknown.

The total number of short faults that connect two inputs undesirably can be computed from equation (3.3.2.1).

$$(n-1)+(n-2)+...+(n-(n-1))=\sum_{j=1}^{n-1}(n-j)$$

(3.3.2.1)

| Short faults                                              | Input conditions                                                                                        | Faulty output (O) |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|

|                                                           | $\mathbf{I}_{\mathbf{j}} = 0  \forall  1 \leq \mathbf{j} \leq \mathbf{n}$                               | 1                 |

| $I_i \leftrightarrow I_k$<br>(1 \le k \le n and k \neq i) | $I_{j} = 0  \forall  (1 \le j \le n \text{ and } j \ne i, j \ne k)$<br>&<br>$I_{i} \bigoplus I_{k} = 1$ | х                 |

|                                                           | For all other input combinations                                                                        | 0                 |

#### **Table 2: Short between Two Inputs**

3) Short between one input and one PMOS drain:  $(I_i \leftarrow \rightarrow D_k \text{ where } l \leq k \leq n)$

The total number of faults in this category is  $n^2$ . There are two cases for determining the output value given this type of fault. The first case occurs when I<sub>i</sub> is

shorted to a drain of any PMOS transistor located below it  $(I_i \leftrightarrow D_k \text{ where } i \leq k \leq n)$ . The second case considered is when  $I_i$  is shorted to the drain of one of the PMOS transistors above it  $(I_i \leftrightarrow D_k \text{ where } l \leq k \leq i-1)$ .

In the first case the output is equal to  $I_i$  if all the PMOS inputs located below the  $D_k$  are low. Thus, the output is connected to  $I_i$  through conducting PMOS transistors and the short between  $I_i$  and  $D_k$ . But even if one of the inputs, located below  $D_k$ , has a high value it turns its related PMOS transistor off and NMOS transistor on. Therefore, the output will be low [3]. If  $I_i$  is shorted to  $D_n$  the output equals  $I_i$  for any inputs combination. These are shown in Table 3.

In Table 3,  $I_j = \langle 0 | 1 \rangle$   $\forall 1 \leq j \leq k$  points out that PMOS transistor inputs above  $D_k$  can be either high or low and  $I_j = 0$   $\forall k+1 \leq j \leq n$  indicates all PMOS transistor inputs below  $D_k$  are low. In this case the output has the exact value of  $I_i$ .

In the second case, the output remains low for all input combinations [1]. If all inputs located below  $D_k$  including  $I_i$  are low the output, which is connected to  $I_i$  through conducting PMOS transistors and the short between  $D_k$  and  $I_i$ , will be low. If one of these inputs has a high value the path between the output and  $I_i$  is disconnected; the output will be connected to the ground through conducting NMOS transistors.

| Short faults                                                                                              | Input conditions                                                                                          | Faulty output (O) |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|

| $I_i \leftrightarrow D_k$<br>(i \le k \le n-1)<br>(1 \le i \le n-1)                                       | $I_{j} = \langle 0   1 \rangle  \forall  1 \leq j \leq k$<br>&<br>$I_{j} = 0  \forall  k+1 \leq j \leq n$ | Ii                |

| $D_k$ is located below the $I_i$ .                                                                        | For all other input combinations                                                                          | 0                 |

| $ \begin{array}{c} I_i \leftrightarrow D_n \\ (1 \le i \le n) \end{array} $                               | For all input combinations                                                                                | I <sub>i</sub>    |

| $I_i \longleftrightarrow D_k$<br>(1 ≤ k ≤ i-1)<br>D <sub>k</sub> is located above<br>the I <sub>i</sub> . | For all input combinations                                                                                | 0                 |

**Table 3: Short between One Input and One PMOS Drain**

4) Short between two PMOS drains:  $(D_i \leftarrow \rightarrow D_k \text{ where } (l \le k \le n \text{ and } k \ne i))$

Another type of short faults occurs when  $D_i$  is shorted to another drain. There will be a difference in the output results if  $D_i$  is shorted to  $D_n$ , considered the same as the output, or if it is shorted to one of the other PMOS drains.

- If  $D_i$  is connected to  $D_k (1 \le k \le n-1 \text{ and } K \ne i)$ :

The output is stuck-on if all inputs, except the inputs between two shorted drains, are low. If at least one input of any transistor between the two shorted drains is high, the related NMOS transistor is turned on and a conducting path between VCC and ground appears. Figure 7 illustrates the short fault between  $D_1$  and  $D_2$  for NOR3. By applying (010) as an input vector,  $Q_1$ ,  $Q_3$  and  $Q_5$  turn on and VCC is connected to the ground through  $Q_1$ ,  $D_1D_2$ ,  $Q_3$  and  $Q_5$ .

The output will be high if all inputs are low and will be low for all other input combinations. The output faulty pattern for short between two drains is shown in Table 4.

In Table 4,  $I_j = 0$  ( $\forall 1 \le j \le i$  and  $m < j \le n$  ( $i+1 \le m \le n-1$ )) denotes all PMOS transistor inputs except those between  $D_i$  and  $D_k$  are low and  $(I_{i+1} \parallel I_{i+2} \parallel ... \parallel I_m)=1$  shows at least one of the inputs of PMOS transistors between  $D_i$  and  $D_k$  is high. In this case the output has an unknown value between 0 and VCC volt (stuck-on).

| Short faults                                                                       | Input conditions                                                                                                               | Faulty output (O) |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                                    | $I_i = 0 \forall 1 \le j \le n$                                                                                                | 1                 |

| $D_i \leftrightarrow D_k$<br>(1 \le k \le n-1,<br>1 \le i \le n-1<br>and k \neq i) | $I_{j} = 0 (\forall 1 \le j \le i \text{ and } m < j \le n (i+1 \le m \le n-1)) \\ \& \\ (I_{i+1}    I_{i+2}       I_{m}) = 1$ | S-on (Stuck-on)   |

|                                                                                    | For all other input combinations                                                                                               | 0                 |

#### Table 4: When $D_i$ is connected to $D_k$ ( $1 \le k \le n-1$ and $K \ne i$ )

- If  $D_i$   $(1 \le i \le n-1)$  is shorted to  $D_n$  the output will correspond to Table 5.

In this case, the reason behind a stuck-on faulty output is similar to the explanation of stuck-on for Table 4.

Figure 7 illustrates this situation for NOR3 when  $D_1$  is connected to  $D_3$  (n=3). If a (010) input vector is applied, a conducting path from VCC to ground will go through  $Q_1$ ,  $D_1D_3$  and  $Q_5$  whereas when a (001) input vector is applied, the conducting path will go through  $Q_1$ ,  $D_1D_3$  and  $Q_6$ . Thus, the output is stuck-on if the input of at least one transistor between two shorted drains is high.

The total number of faults that short two drains can be computed from equation (3.3.2.2).

$$(n-1)+(n-2)+...+(n-(n-1))=\sum_{j=1}^{n-1}(n-j)$$

(3.3.2.2)

| Short faults                                                                    | Input conditions                                                                  | Faulty output (O) |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|

|                                                                                 | $I_i = 0  \forall  1 \le j \le n$                                                 | 1                 |

| $ \begin{array}{l} D_i \leftrightarrow D_n \\ (1 \leq i \leq n-1) \end{array} $ | $I_{j} = 0 (\forall 1 \le j \le i) \\ \& \\ (I_{i+1}    I_{i+2}       I_{n}) = 1$ | S-on (Stuck-on)   |

|                                                                                 | For all other input combinations                                                  | 0                 |

Table 5: When  $D_i$   $(1 \le i \le n-1)$  is shorted to  $D_n$

5) Short between one input and the output  $(I_i \leftarrow \rightarrow O \text{ where}(1 \le i \le n))$ This fault was discussed in 3), where inputs are shorted to  $D_n$ .

All five types of short faults have been covered in detail. The total number of short faults from the first to the last category is:

$$2\sum_{j=1}^{n-1} (n-j) + n^2 + 2n - 2 \qquad (3.3.2.3)$$

**Figure 7: Faulty NOR3 Transistor Level**

#### 3.3.3 Open Faults:

Open faults occur after breaking at least one connection (channel) in the circuit. The source of the open state is a logic fault, which prevents the channel from conducting [5]. Under these circumstances every node in the circuit must be considered separately, since each node contributes to a different output result in the fault analysis. For instance, in the case of NORn,  $I_{i}$ ,  $I_{iN}$  and  $I_{iP}$  as well as  $D_m$ ,  $D_{n+1}...,D_{2n}$  and O are all separate nodes.

Different types of open faults that can occur in the circuit are classified as follows:

1)  $I_{iP}$   $(1 \le i \le n)$ : Open

When  $I_{iP}$  is open the logical fault type, which represents the  $I_{iP}$  open physical failure, is equivalent to VCC stuck open. This results in  $I_{iP}$  stuck- at -1 and  $I_{iN} = I_i$  [5]. When  $I_{iP}$  is stuck-at-1 the output will be in a tri-state if all inputs are low. In this case all PMOS transistors except the one with  $I_{iP}$  input, which is stuck-at-1, are turned on and all NMOS transistors are off due to the low input values. The output has neither a path to VCC nor to ground. This is shown in Table 6.

The total number of faults for  $I_{iP}$  open fault is equal to n.

| Open faults           | Input conditions                   | Faulty output (O) |

|-----------------------|------------------------------------|-------------------|

| I <sub>iP</sub> :Open | $I_i = 0  \forall \ 1 \le j \le n$ | Z                 |

| $(1 \le i \le n)$     | For all other input combinations   | 0                 |

#### Table 6: I<sub>iP</sub> Open

#### 2) $I_{iN}$ $(1 \le i \le n)$ : Open

The logical fault type of  $I_{iN}$  open fault is identical to  $I_i$  open fault which is similar to the situation where  $I_{iN}$  is stuck-at-0 and  $I_{iP} = I_i$  [5]. In the  $I_{iN}$  stuck-at-0 condition, the output is high impedance if all NORn inputs except  $I_i$  are low. In this case, all PMOS transistors conduct except that with input  $I_i$ . Although  $I_i$  is high, its NMOS transistor ( $Q_{n + i}$ ) is off since  $I_{iN}$  is stuck-at-0. Therefore, the output is neither connected to VCC nor ground. However, if  $I_i$  and the other inputs have low values the NORn output will be connected to the VCC and will go high. This is shown in Table 7.

The total number of faults for  $I_{iN}$  open fault is equal to n.

| Open faults                                                       | Input conditions                                                         | Faulty output (O) |

|-------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------|

|                                                                   | $I_i = 0  \forall \ 1 \le j \le n$                                       | 1                 |

| $\begin{array}{l} I_{iN} : Open \\ (1 \leq i \leq n) \end{array}$ | $I_j = 0 (\forall 1 \le j \le n \text{ and } j \ne i)$<br>&<br>$I_i = 1$ | Z                 |

|                                                                   | For all other input combinations                                         | 0                 |

#### Table 7: I<sub>iN</sub> Open

#### 3) $I_i$ $(1 \le i \le n)$ : Open

$I_i$  open fault acts similar to when  $I_{iN}$  is stuck-at-0 and  $I_{iP} = I_i$  [5]. The NORn output results for  $I_i$  open fault is the same as  $I_{iN}$  open fault. The total number of faults in this case is also n.

#### 4) Di: Open

$D_i$  represents a drain belonging to NMOS or PMOS transistors. When  $(1 \le i \le n)$ ,  $D_i$  is a PMOS drain. The logical fault type  $D_i$  open fault is VCC stuck open, which can be replaced by  $I_{iP}$  stuck-at-1,  $I_{iN} = I_i$  fault model. Therefore, the output will be the

same as  $I_{iP}$  open fault.  $D_i$  is a NMOS drain if  $(n+1 \le i \le 2n)$  and the output result will be the same as an  $I_{iN}$  open fault.

The total number of faults in this category is 2n.

5) Si: Open

If (i = 1) the result of  $S_i$  open will be the same as  $I_{iP}$  open fault and if  $(n+1 \le i \le 2n)$  then  $S_i$  open fault behaves like an  $I_{iN}$  open fault [5]. The PMOS sources, other than  $S_i$ , have not been considered since they are the same node as other PMOS drains which have been taken into account in the previous category.

The total number of faults is 2n+1 for source open faults.

6) *O*: Open

A stuck open fault causes the output to be connected neither to power nor to ground. Therefore, the output is in a tri-state (O = Z). The number of faults in this category is 1.

All open faults of the NORn gate have been analyzed and the total number of open faults from all six categories is 6n+2.

The general formula for the total number of faults for NORn is concluded by adding the total number of faults from all groups of faults (stuck-at, short, and open):

$$2\sum_{j=1}^{n-1} (n-j) + n^2 + 10n + 2 \qquad (3.3.3.1)$$

The patterns and formulas for the total number of faults for other primary gates can be calculated in the same manner. The final results for NAND, Inverter, D-latch, and D flip-flop gates are presented in the following sections. Fault list patterns for AND and OR gates can be concluded from NOR, NAND, and Inverter. The D flipflop fault list can be concluded from the D-latch fault list.

# 3.4 NANDn Complete Fault List Pattern

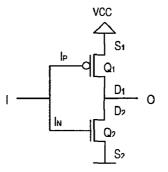

Figure 7 presents a NANDn gate. The output pattern in the presence of faults is presented in three groups of faults in Table 8 for I/O stuck-at –faults, Table 9 for short faults and Table 10 and Table 11 for open faults.

#### Figure 8: NANDn Transistor Level

| Input/output stuck-at-faults               | Faulty output (O)                         |

|--------------------------------------------|-------------------------------------------|

| I <sub>i</sub> : stuck-at-0                | 1                                         |

| I <sub>i</sub> : stuck-at-1                | NAND $(I_1, I_2, I_{i-1}, I_{i+1},, I_n)$ |

| O: stuck-at-0 (for any input combinations) | 0                                         |

| O: stuck-at-1 (for any input combinations) | 1                                         |

#### Table 8: NANDn Input/Output Stuck-at-faults

The many types of short faults that may occur in a NANDn circuit are categorized as follow:

1) Short between a NMOS source and ground or power

2) Short between two inputs

· 영화한 말했다는 학회원 독자의 신하다.

-

. Sina

- 3) Short between one input and one NMOS source

- 4) Short between two NMOS sources

- 5) Short between one NMOS source and the output

- 6) Short between one input and the output

| Short faults                                                                           | Input conditions                                                                                                                              | Faulty output (O) |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                                        | $I_i = 1  \forall \ 1 \le j \le n$                                                                                                            | 0                 |

| $S_i \leftrightarrow G$ (ground)<br>(1 $\leq i \leq n-1$ )                             | $I_{j}=1 (\forall 1 \le j \le i) \\ \& \\ (I_{i+1} \& I_{i+2} \& \dots \& I_{n})=0 \\ For all other input combinations$                       | S-On              |

| $S_i \leftrightarrow VCC$<br>(1 \le i \le n-1)                                         | For any input combination                                                                                                                     | 1                 |

|                                                                                        | $I_i = 1 \forall 1 \le j \le n$                                                                                                               | 0                 |

| $I_{i} \leftrightarrow I_{k}$<br>(1 \le k \le n and k \ne i)                           | $I_{j}=1 (\forall 1 \le j \le n \text{ and } j \ne i, j \ne k) \\ \& \\ I_{i} \bigoplus I_{k}=1$                                              | Х                 |

|                                                                                        | For all other input combinations                                                                                                              | 1                 |

| $l_i \leftarrow \mathbf{S}_k$<br>(i \le k \le n-1)                                     | For any input combination                                                                                                                     | 1                 |

| $I_i \leftarrow \mathbf{S}_k$<br>(1 ≤ k ≤ i-1)<br>(1 ≤ i ≤ n)                          | $I_{j}=1  \forall \ 1 \le j \le k$<br>&<br>$I_{i}= <0 1>  \forall \ k+1 \le j \le n$<br>For all other input combinations                      | I.                |

|                                                                                        | $I_i = 1 \forall 1 \le j \le n$                                                                                                               | 0                 |

| $S_i \longleftrightarrow S_k$<br>(1 \le k \le n-1<br>1 \le i \le n-1<br>and k \neq i): | $I_{j}=1 (\forall 1 \le j \le i \text{ and } m < j \le n (i+1 \le m \le n-1))$<br>&<br>$(I_{i+1} \& I_{i+2} \& \dots \& I_{m}) = 0$           | S-on              |

|                                                                                        | For all other input combinations                                                                                                              | 1                 |

| $S_i \leftrightarrow O$<br>(1 \le i \le n-1)                                           | $I_{j}=1 \forall 1 \le j \le n$ $I_{j}=1 \forall (i+1 \le j \le n)$ & $(I_{1} \& I_{2} \& \dots \& I_{i})=0$ For all other input combinations | 0<br>S-on<br>1    |

| $I_{i} \leftrightarrow O$<br>(1 \le i \le n)                                           | For any input combination                                                                                                                     | I <sub>i</sub>    |

**Table 9: NANDn Short Faults**

Many open faults turn out to have a similar logical fault type. Table 10 puts these faults into logical fault categories and Table 11 shows the output result for each category.

| Open faults                          | Logical fault type           |

|--------------------------------------|------------------------------|

| $I_{iP}$ : open ( $1 \le i \le n$ )  |                              |

| $S_i$ : open (n+1 $\leq i \leq 2n$ ) | L totuals at 1               |

| $D_i$ : open (n+1 $\leq i \leq 2n$ ) | I <sub>iP</sub> : stuck-at-1 |

| $I_i$ : open ( $1 \le i \le n$ )     |                              |

| $I_{iN}$ : open ( $1 \le i \le n$ )  |                              |

| $S_i$ : open ( $1 \le i \le n$ )     | I <sub>iN</sub> : stuck-at-0 |

| $D_i$ : open ( i =1)                 |                              |

| O: open                              | Ζ                            |

**Table 10: NANDn Open Faults Categories**

| Logical fault type of open faults | Input conditions                                                          | Faulty output (O) |

|-----------------------------------|---------------------------------------------------------------------------|-------------------|

|                                   | $I_i = 1 \forall 1 \le j \le n$                                           | 0                 |

| I <sub>iP</sub> : stuck-at-1      | $I_{j}=1 (\forall 1 \le j \le n \text{ and } j \neq i)$<br>&<br>$I_{i}=0$ | Z                 |

|                                   | For all other input combinations                                          | 1                 |

| I <sub>iN</sub> : stuck-at-0      | $I_{j}=1 \forall 1 \leq j \leq n$                                         | Z                 |

| I <sub>iN</sub> . Stuck-at-0      | For all other input combinations                                          | 1                 |

| Z (O: open)                       | For any input combination                                                 | Z                 |

#### **Table 11: NANDn Open Faults**

The general formula for the total number of faults for NANDn is:

$$\sum_{j=1}^{n-1} (n-j) + \sum_{k=2}^{n-1} (n-k) + n^2 + 11n + 1$$

(3.4.1)

The fault list patterns of OR and AND gates with n inputs can easily be concluded from NORn and NANDn. The complete tables of patterns for these gates are presented in the appendices.

Inverter, D-Latch, and D Flip-Flop have a specific number of inputs. Therefore, it is not appropriate to say they are following a specific fault list pattern due to their number of inputs. Each has only one complete fault list which will be presented in Sections 3.6 and 3.7.

# **3.5 Inverter Complete Fault List**

The most important CMOS gate is the CMOS inverter. It consists of only two transistors, a pair of one N-type and one P-type transistor.

Figure 9 shows an inverter gate. The output pattern in the presence of faults is presented in three groups of faults in Table 12 for input / output stuck-at faults, Table 13 for short faults and Table 14 for open faults. The total number of faults for the inverter is: 13

**Figure 9: CMOS Inverter**

| Input/output stuck-at fault | Faulty output (O) |

|-----------------------------|-------------------|

| I: stuck-at-0               | 1                 |

| I: stuck-at-1               | 0                 |

| O: stuck-at-0               | 0                 |

| O: stuck-at-1               | 1                 |

### Table 12: Inverter Input / Output Stuck-at Faults

| Short faults   | Faulty output (O) |

|----------------|-------------------|

| 0 <b>← →</b> I | Ι                 |

**Table 13: Inverter Short Faults**

| <b>Open</b> faults    | Input conditions   | Faulty output (O) |

|-----------------------|--------------------|-------------------|

| O: open               | For any I          | Z                 |

| I.: open              | I = 1              | 0                 |

| I <sub>P</sub> : open | I = 0              | Z                 |

| I <sub>N</sub> : open | $\mathbf{I} = 0$   | 1                 |

| IN. Open              | I = 1              | Z                 |

| I: open               | N/A                | Z                 |

| S <sub>1</sub> : open | I = 1              | 0                 |

|                       | I = 0              | Z                 |

| S <sub>2</sub> : open | $\mathbf{I} = 0$   | 1                 |

| 5 <sub>2</sub> . open | I = 1              | Z                 |

| D <sub>1</sub> : open | I = I              | 0                 |

|                       | $\overline{I} = 0$ | Ζ                 |

| D <sub>2</sub> : open | I = 0              | 1                 |

|                       | I = 1              | Z                 |

#### **Table 14: Inverter Open Faults**

#### **3.6 D-Latch Complete Fault List**

aut.

Constraint States

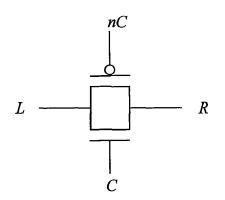

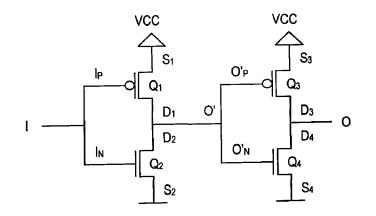

In CMOS technology, T-gates allow efficient realizations of several important logical functions [9]. Such a circuit consisting of one N-type and one P-type transistor connected in parallel and controlled by inverted gate voltages is shown in Figure 10. This circuit is defined as a transmission gate (T-gate) circuit. If the gate voltage of the N-type transistor is 'GND' and the P-type transistor has a gate voltage of 'VCC', both transistors are non-conducting. On the other hand, if the gate voltage of the N-type transistor is 'GND', both transistors are conducting. If the source voltage is near VCC, there is a voltage drop across the N-type transistor but (almost) no voltage drop across the P-type transistor. If the source voltage is near GND, the N-type transistor has (almost) no voltage drop. Due to the symmetry of standard MOS transistors, there is no reason to differentiate between source and drain in a T-gate. The contacts are therefore usually referred to as 'L' (left) and 'R' (right).

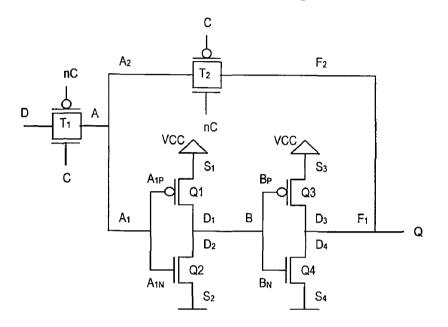

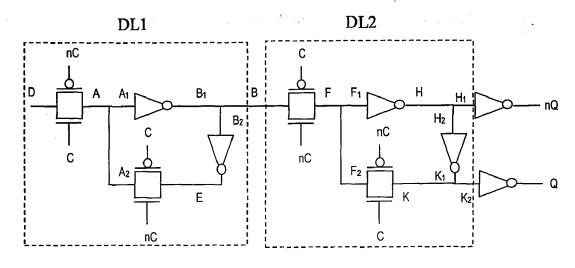

Figure 11 illustrates a D-latch by using only 8 transistors (2 inverters and 2 T-gates) for cases where both the clock (C) and the inverted clock (nC) signals are available. If the inverted clock is not available, an additional inverter is required to provide the control signal for the two T-gates [9].

A standard D-latch can be built from four 2-input NAND gates [8]. Thus, 16 transistors are needed for one D-latch. However, in this study we consider the D-latch circuit in Figure 11 in order to reduce the number of transistors leading to a lower number of possible faults. The case of a faulty inverter has been discussed in previous sections. Here, we assume that:

- 1. Both the clock and the inverted clock signal are available.

- 2. All signals are propagated up to the edge of the D-latch cell correctly.

The similar approach to NOR gate is applied to the D-latch to obtain its faulty output in the presence of a single fault. Later, the results from a D-latch fault list can be used to determine the fault list of a D flip-flop.

Figure 10: T-gate

#### **3.6.1 Input / Output Stuck-at Faults**

D, C (Clock), nC (inverted clock), and Q represent the input/output nodes of the D-latch in Figure 11. These nodes can be stuck-at-1 or stuck-at-0 leading to a faulty output. The results are shown in Table 15.

Q represents the previous state of output Q. When D is a stuck-at-fault, the output remains in its previous state as long as the clock is low. The output shows a faulty value for D when the clock goes high. When C and Q are stuck-at-faults the result of the faulty output can be easily computed. For example, when C is stuck-at-0 the feedback T-gate  $(T_2)$  is always conducting so the output remains in its previous state if nC is high. When nC is low and C is stuck-at-0  $T_1$  gate also conducts,

therefore the output has the value of D. When C is stuck-at-1  $T_1$  is always conducting and the value of D goes directly to the output.

$T_2$  conducts while nC is stuck-at-1. The output remains in its previous state if C is low. Once C becomes high, the  $T_1$  gate conducts and the value of D goes to the Q. If nC is stuck-at-0 gate  $T_1$  conducts and the output has the value of D.

Figure 11: CMOS D-Latch

| Stuck-at-fault   | Input conditions | Faulty output (Q)               |

|------------------|------------------|---------------------------------|

| D: stuck-at-1    | C = 0            | Q <sup>-</sup> (previous state) |

| D. Stuck-at-1    | C = 1            | 1                               |

| D: stuck-at-0    | C = 0            | Q                               |

| D. Sluck-al-0    | C = 1            | 0                               |

| C: stuck-at-1    | N/A              | D                               |

| C: stuck-at-0    | nC = 1           | Q                               |

| C. Stuck-at-0    | nC = 0           | D                               |

| Q: stuck-at-1    | For any D and C  | 1                               |

| Q: stuck-at-0    | For any D and C  | 0                               |

| nC: stuck-at-1   | C = 1            | D                               |

| nc: stuck-at-1   | C = 0            | Q <sup>-</sup>                  |

| a Custovali at 0 | C = 1            | D                               |

| nC: stuck-at-0   | C = 0            |                                 |

Table 15: D-Latch Input / Output Stuck-at Faults

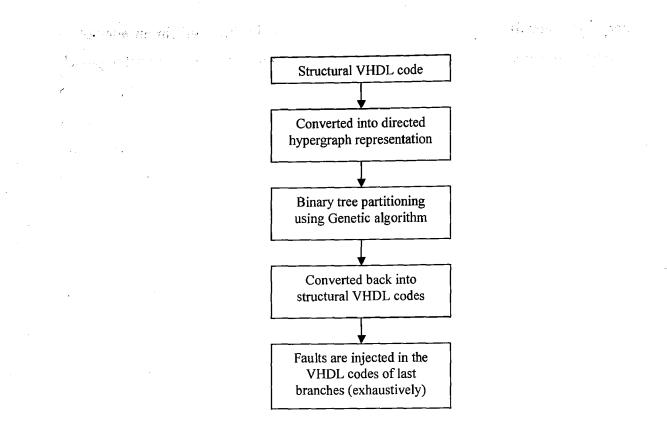

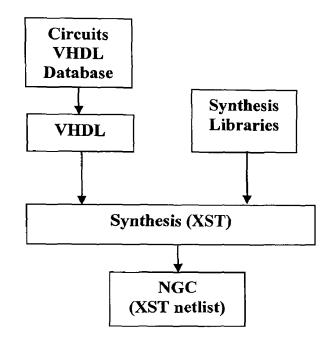

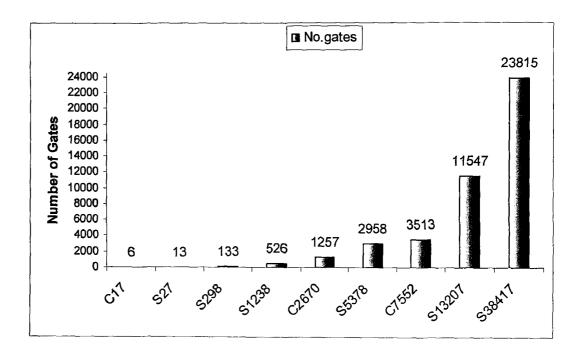

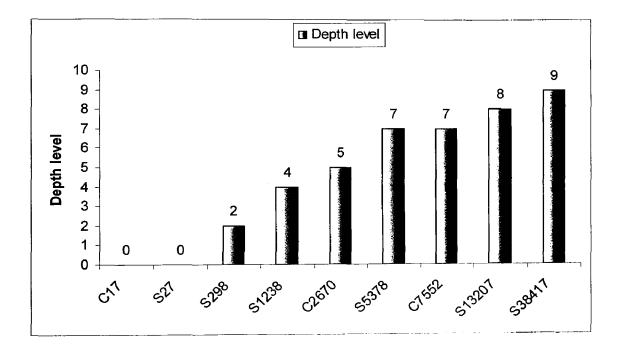

#### **3.6.2 Short Faults**