### ADAPTIVE DECISION FEEDBACK EQUALIZATION FOR MULTI-Gbps DATA LINKS

by

Alaa R. Abdullah Bacelor of Science, University of Technology, Baghdad, Iraq, 1989 Master of Science, Ryerson University, Toronto, Canada, 2010

> A dissertation presented to Ryerson University in partial fulfillment of the requirement for the degree of Doctor of Philosophy in the Program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2014 ©Alaa R. Abdullah, 2014

## Author's Declaration For Electronic Submission of A Dissertation

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners. I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

### Abstract

#### Adaptive Decision Feedback Equalization For Multi-Gbps Data Links

©Alaa R. Abdullah, 2014 Doctor of Philosophy Electrical and Computer Engineering Ryerson University

Channel equalization combats the effects of the imperfection of wire channels. This dissertation deals with adaptive decision feedback channel equalization. The dissertation starts with an in depth study of the challenges encountered in the design of adaptive DFE and techniques that address these challenges. Various 2-dimensional eye-opening monitors (EOMs) based adaptive DFE are proposed and implemented. A novel 2-dimensional hexagon EOM is proposed and its effectiveness is validated using simulation. A simplified and power efficient 2-dimensional hexagon EOM is also introduced. Both EOMs are capable of differentiating the severity of the violation of the minimum eye-opening so as to allow the DFE to take different actions adaptively and achieve desired eye-opening more rapidly. A maximum-jitter EOM-based adaptive DFE is also introduced to greatly reduce system complexity. The adaptive DFE is taped out in a 130nm 1.2V CMOS technology and finally an improved adaptive engine that outperforms DFE utilizing sign-sign least-mean-square is proposed.

### Acknowledgements

I am heartily thankful to my supervisor, Professor Fei Yuan, for his wonderful guidance throughout all the stages of my PhD studies. Without his continued encouragement and support, this dissertation would not have been possible. I am also thankful for the excellent example Professor Fei Yuan has provided as a successful researcher, wonderful teacher and role model.

I wish to express my sincere gratitude to my co-supervisor Dr. Andy Ye who helped and supported me in every aspect during the completion of my studies.

I offer my regards and blessings to my colleagues and staff at Integrated Circuits and Systems Research Group at Ryerson University who provided me with valuable technical supports during my studies.

Last but not least, I would like to gratefully acknowledge the financial support of Ryerson University especially Electrical and Computer Engineering department and Ontario Graduate Scholarship OGS for their financial support during my studies.

## Dedication

To my wonderful wife, daughter and sons, Nissreen, Nursan, Hussin, Yousif and Saif, for their unconditional love, enormous support and continuous encouragement...

## Contents

| 1        | Intr | roduction                           | 1         |

|----------|------|-------------------------------------|-----------|

|          | 1.1  | Motivation                          | 1         |

|          | 1.2  | Objective of The Dissertation       | 4         |

|          | 1.3  | Chapter Organization                | 5         |

|          | 1.4  | Inter-Symbol Interference           | 5         |

|          | 1.5  | Channel Equalization                | 6         |

|          |      | 1.5.1 Near-End Channel Equalization | 7         |

|          |      | 1.5.2 Far-End Channel Equalization  | 10        |

|          | 1.6  | Decision Feedback Equalization      | 13        |

|          | 1.7  | Chapter Summary                     | 17        |

|          | 1.8  | Contributions of The Dissertation   | 17        |

|          | 1.9  | Organization of The Dissertation    | 18        |

| <b>2</b> | Des  | ign Challenges in DFE               | <b>21</b> |

|          | 2.1  | Bit Error Rate Test                 | 21        |

|          | 2.2  | Timing Constraints                  | 22        |

|          | 2.3  | Timing Alignment                    | 24        |

|          | 2.4  | Error Propagation                   | 26        |

|          | 2.5  | Calibration of Slicer               | 27        |

|          | 2.6  | Delay Cells                         | 30        |

|          | 2.7  | Arithmetic Operation                | 31        |

|          | 2.8  | Channels with Severe Dispersity     | 33        |

|   | 2.9          | Power Consumption                            | 34 |

|---|--------------|----------------------------------------------|----|

|   | 2.10         | Adaptive Decision Feedback Equalization      | 34 |

|   |              | 2.10.1 Least-Mean-Square Adaptive DFE        | 35 |

|   |              | 2.10.2 Eye-Opening Adaptive DFE              | 37 |

|   |              | 2.10.3 Jitter-Based Adaptive DFE             | 38 |

|   |              | 2.10.4 Comparison                            | 40 |

|   | 2.11         | Chapter Summary                              | 40 |

| 3 | <b>2-D</b> i | imensional Hexagon Eye-Opening Monitor       | 41 |

|   | 3.1          | Eye-Opening Monitors                         | 41 |

|   |              | 3.1.1 One-Dimensional EOMs                   | 42 |

|   |              | 3.1.2 Two-Dimensional EOMs                   | 43 |

|   |              | 3.1.3 Jitter-Based EOMs                      | 43 |

|   |              | 3.1.4 Eye-Pattern Monitors                   | 45 |

|   | 3.2          | Proposed Two-Dimensional EOM                 | 46 |

|   |              | 3.2.1 Drawbacks of Rectangular EOM           | 46 |

|   |              | 3.2.2 Diamond EOM                            | 47 |

|   |              | 3.2.3 Hexagon EOM                            | 47 |

|   |              | 3.2.4 Discussion                             | 50 |

|   | 3.3          | Implementation                               | 53 |

|   | 3.4          | Chapter Summary                              | 60 |

| 4 | <b>2-D</b> i | imensional Half-Hexagon Eye- Opening Monitor | 61 |

|   | 4.1          | Half Hexagon Eye-Opening Monitor             | 61 |

|   | 4.2          | Implementation                               | 63 |

|   | 4.3          | Simulation Results                           | 66 |

|   | 4.4          | Chapter Summary                              | 71 |

| 5 | Ada          | ptive DFE Uing 2-Dimensional Hexagon EOM     | 73 |

|   | 5.1          | The Principle                                | 74 |

|   | 5.2 | The Algorithm                                 |

|---|-----|-----------------------------------------------|

|   | 5.3 | Implementation                                |

|   |     | 5.3.1 The Architecture                        |

|   |     | 5.3.2 Slicer                                  |

|   |     | 5.3.3 Error Detection Unit                    |

|   |     | 5.3.4 Digital-To-Analog Converter             |

|   |     | 5.3.5 XOR Gate                                |

|   | 5.4 | Simulation Results                            |

|   | 5.5 | Chapter Summary                               |

| 6 | Ma  | ximum-Jitter Adaptive DFE 91                  |

|   | 6.1 | Maximum-Jitter Adaptive DFE                   |

|   |     | 6.1.1 The Principle                           |

|   | 6.2 | Implementation                                |

|   |     | 6.2.1 Error Detection Unit                    |

|   |     | 6.2.2 Digital-to-Analog Converter             |

|   | 6.3 | Simulation Results                            |

|   | 6.4 | Drawbacks of Adaptive DFE Using SS-LMS or EOM |

|   |     | 6.4.1 Drawbacks of Adaptive DFE Using SS-LMS  |

|   |     | 6.4.2 Drawbacks of Adaptive DFE Using EOM     |

|   | 6.5 | The Solution                                  |

|   | 6.6 | Simulation Results                            |

|   | 6.7 | Chapter Summary                               |

| 7 | Cor | nclusions and Future Work 113                 |

|   | 7.1 | Conclusions                                   |

|   | 7.2 | Future Work                                   |

|   | 7.3 | List of Publications                          |

## List of Figures

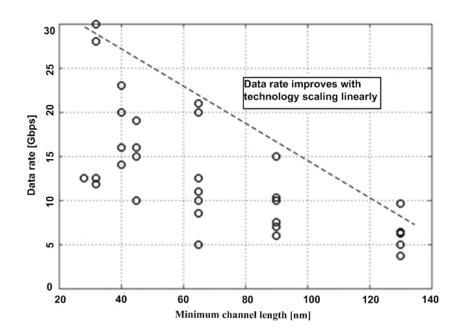

| 1.1 | Dependence of data rate on the minimum channel length of MOS transistors.      | 2  |

|-----|--------------------------------------------------------------------------------|----|

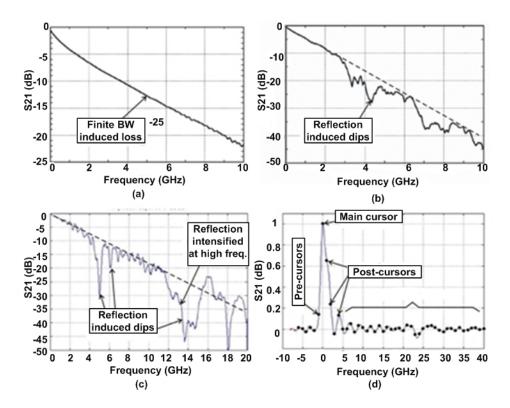

| 1.2 | (a) Frequency response of a 30" trace on a Nelco4000-13SI board [1]. (b) Fre-  |    |

|     | quency response of a 16" Tyco legancy backplane with two daughter cards [4].   |    |

|     | (c,d) Frequency response and impulse response of a highly reflective backplane |    |

|     | [5] (Copyright ©IEEE)                                                          | 3  |

| 1.3 | Pre-cursors, main cursor, and post-cursors of data symbol at the far end of a  |    |

|     | wire channel.                                                                  | 6  |

| 1.4 | Inter-symbol interference in multi symbols                                     | 6  |

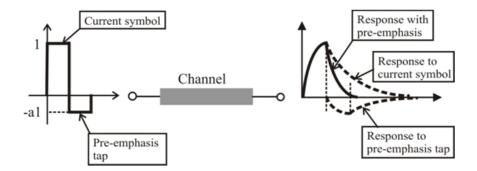

| 1.5 | Near-end channel equalization with first-order pre-emphasis. The added pre-    |    |

|     | emphasis tap shortens the duration of the received symbol thereby improving    |    |

|     | data rate.                                                                     | 8  |

| 1.6 | Frequency response of an equalized channel with pre-emphasis. The high-        |    |

|     | frequency components of data symbols are boosted prior to their transmission.  | 9  |

| 1.7 | Frequency response of an equalized channel using de-emphasis. The low-         |    |

|     | frequency components of data symbols are attenuated prior to their transmis-   |    |

|     | sion                                                                           | 10 |

| 1.8 | Continuous-time linear equalizers with inductor series peaking, source degen-  |    |

|     | eration, and negative capacitors                                               | 11 |

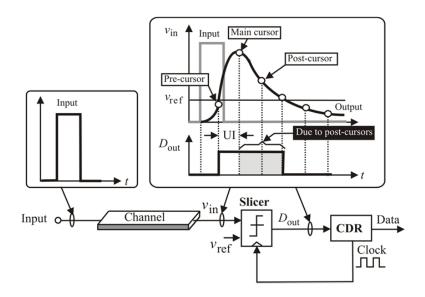

| 1.9  | Basic configuration and operation of decision feedback equalization. Legends:                 |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | UI - Delay cell with one unit delay, $v_s = v_{in} - v_f$ is the symbol before the            |    |

|      | slicer. $v_{ref}$ is the threshold of the slicer, $D_{j=1}$ is the delayed version of $D_j$ , |    |

|      | $c_1,,c_N$ are the weighting factors of feedback taps, $T_s$ is the symbol time, $H_{j,k}$    |    |

|      | denote the kth post-cursor of symbol- $j$ and $H_{0,j}$ the main cursor of symbol- $j$ .      | 14 |

| 2.1  | Dependence of horizontal eye-opening on BER.                                                  | 22 |

| 2.2  | Tap-1 feedback is implemented using loop-unrolling                                            | 23 |

| 2.3  | Half-rate decision feedback equalization. Tap-1 is implemented using loop-                    |    |

|      | unrolling while the remaining taps are implemented using direct feedback.                     |    |

|      | Note that complementary clocks are used for upper and lower paths of DFE.                     | 24 |

| 2.4  | Post-cursor cancellation error due to timing error of delay stages                            | 25 |

| 2.5  | Error in data slicing affects the removal of post-cursors                                     | 27 |

| 2.6  | Clocked re-generative sense amplifier as slicer [37]                                          | 28 |

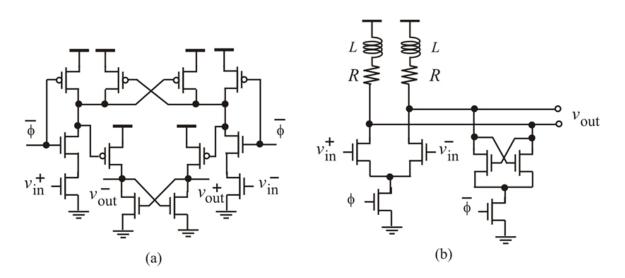

| 2.7  | (a) Clocked re-generative sense amplifier as delay cell [25], (b) Clocked current-            |    |

|      | mode delay cells [44]                                                                         | 30 |

| 2.8  | Current-mode summer with resistive load.                                                      | 32 |

| 2.9  | Least-mean-square adaptive DFE                                                                | 35 |

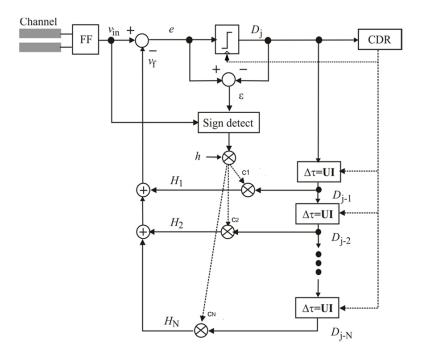

| 2.10 | Configuration of SS-LMS adaptive DFE                                                          | 36 |

| 2.11 | Eye-opening monitors.                                                                         | 38 |

| 2.12 | 1-dimensional Eye-opening adaptive DFE [53]                                                   | 38 |

| 2.13 | Relation between vertical opening and edge jitter                                             | 39 |

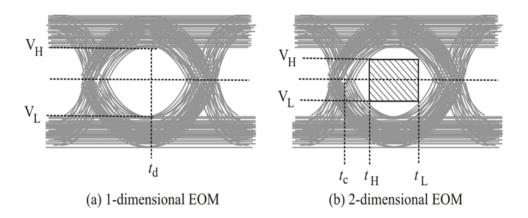

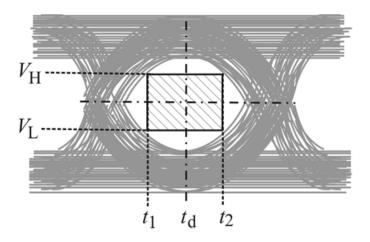

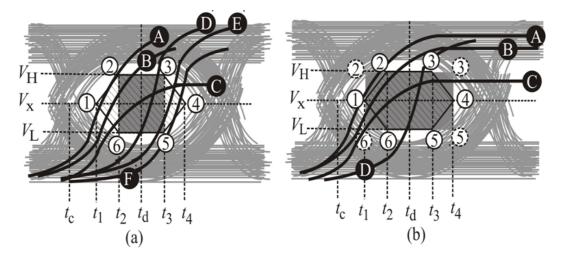

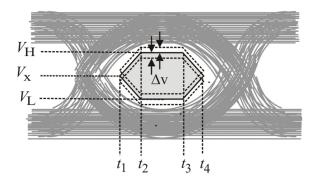

| 3.1  | One dimensional EOM quantified by $V_H$ and $V_L$ at $t_d$ vertically. Two-dimensional        |    |

|      | EOM quantified by $V_H$ and $V_L$ vertically and $t_1$ and $t_2$ horizontally                 | 42 |

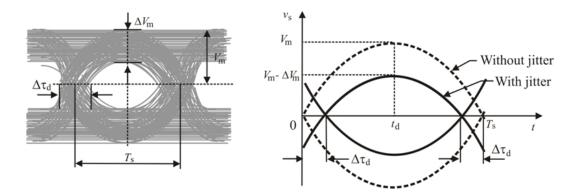

| 3.2  | Relation between vertical opening and edge jitter                                             | 43 |

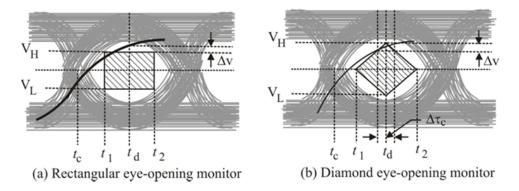

| 3.3  | Rectangular and diamond EOMs                                                                  | 46 |

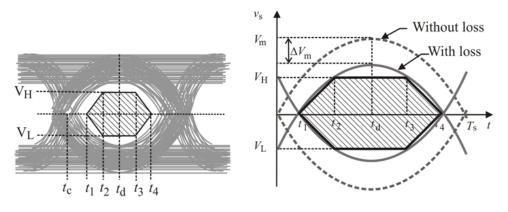

| 3.4  | Hexagon EOM.                                                                                  | 48 |

| 3.5  | (a) Hexagon EOM that has the same vertical opening but different horizontal     |    |

|------|---------------------------------------------------------------------------------|----|

|      | opening as that of rectangular EOM. (b) Hexagon EOM that has the same           |    |

|      | horizontal opening as that of rectangular EOM                                   | 49 |

| 3.6  | Asymmetrical hexagon EOMs                                                       | 51 |

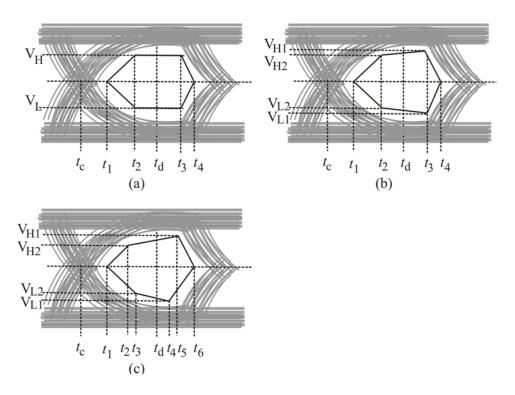

| 3.7  | Serial link with a hexagon EOM. For the purpose of comparison, a rectangular    |    |

|      | EOM in parallel with the hexagon EOM is also employed                           | 53 |

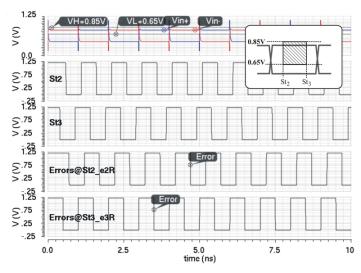

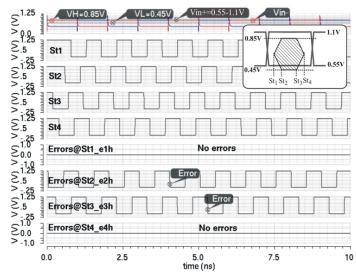

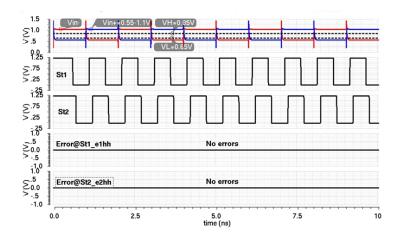

| 3.8  | Simulated output of the error generators of rectangular EOM with $v_{in,max} >$ |    |

|      | $V_H$ and $v_{in,min} < V_L$                                                    | 55 |

| 3.9  | Simulated output of the error generators of rectangular EOM with $v_{in,max} <$ |    |

|      | $V_H$ and $v_{in,min} < V_L$                                                    | 55 |

| 3.10 | Simulated output of the error generators of rectangular EOM with $v_{in,max} >$ |    |

|      | $V_H$ and $v_{in,min} > V_L$                                                    | 56 |

| 3.11 | Simulated output of the error generators of hexagon EOM with $v_{in,min} < V_L$ |    |

|      | and $v_{in,max} > V_H$                                                          | 56 |

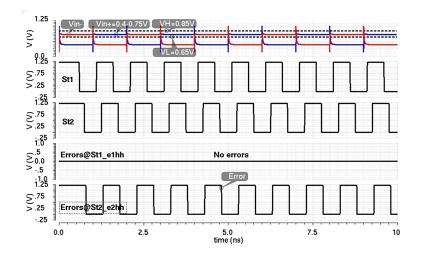

| 3.12 | Simulated output of the error generators of hexagon EOM with $v_{in,max} < V_H$ |    |

|      | and $v_{in,min} < V_L$                                                          | 57 |

| 3.13 | Simulated output of the error generators of hexagon EOM with $v_{in,min} > V_L$ |    |

|      | and $v_{in,max} > V_H$                                                          | 57 |

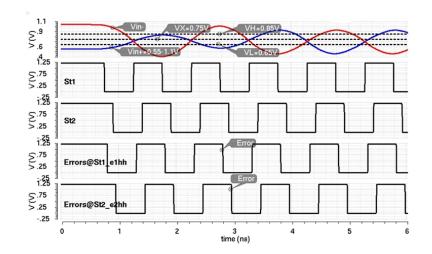

| 3.14 | Simulated output of the error generators of rectangular EOM and hexagon         |    |

|      | EOM with a 1-mm channel, $v_{in,min} < V_L$ , and $v_{in,max} > V_H$            | 58 |

| 3.15 | Simulated output of the error generators of rectangular EOM and hexagon         |    |

|      | EOM with a 40-mm channel                                                        | 59 |

| 3.16 | Output of error generator of hexagon EOM                                        | 60 |

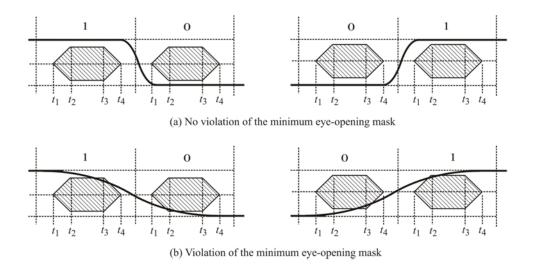

| 4.1  | Detection of violation of the minimum eye-opening using half hexagon mask.      | 62 |

| 4.2  | Left : Full and half rectangular Eye-Opening patterns. Right : Full and half    |    |

|      | hexagon Eye-Opening patterns                                                    | 62 |

|      |                                                                                 |    |

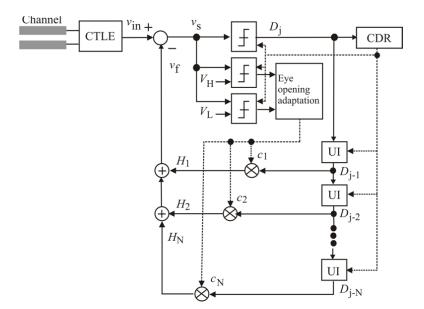

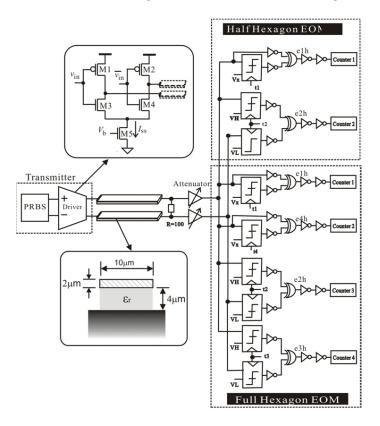

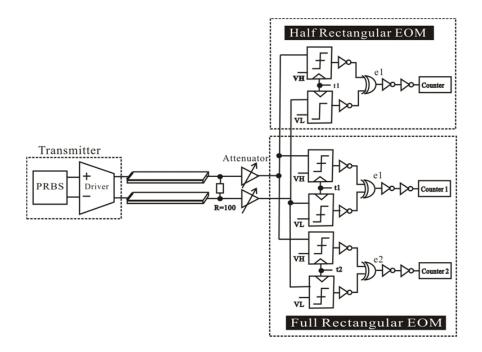

| 4.3  | Serial link with half and full hexagon EOMs. Circuit parameters : $W_{1,2}$ =                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $6.5\mu m, W_{3,4} = 4\mu m, W_5 = 50\mu m. L = 0.13\mu m$ for all transistors. $V_b = 0.7 V$                                       |    |

|      | with tail current $I_{ss} = 2$ mA                                                                                                   | 63 |

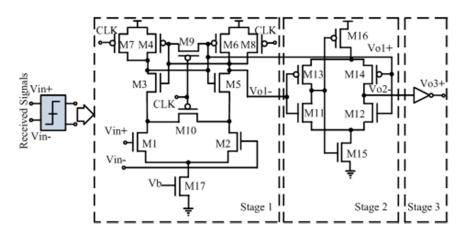

| 4.4  | Clocked comparator. Circuit parameters : Circuit parameters : $W_{1,2} = 4.5 \mu m$ ,                                               |    |

|      | $W_{3,5} = 4\mu m, W_{4,6,7,8} = 8\mu m, W_{9,10} = 1\mu m, W_{11,12} = 1\mu m, W_{13,14} = 2\mu m$ , and                           |    |

|      | $W_{15,16,17} = 60 \mu \text{m}. \ L = 0.13 \mu \text{m}$ for all transistors. $I_{ss} = 2 \mu \text{A}, V_b = 0.8 \text{V}. \dots$ | 64 |

| 4.5  | Effect of duty-cycle distortion on hexagon EOM                                                                                      | 65 |

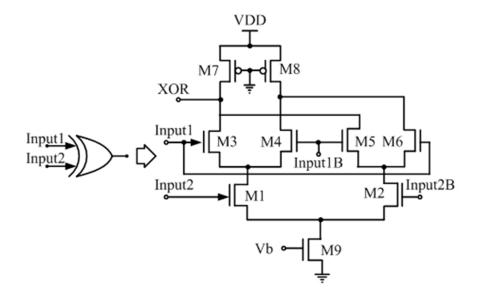

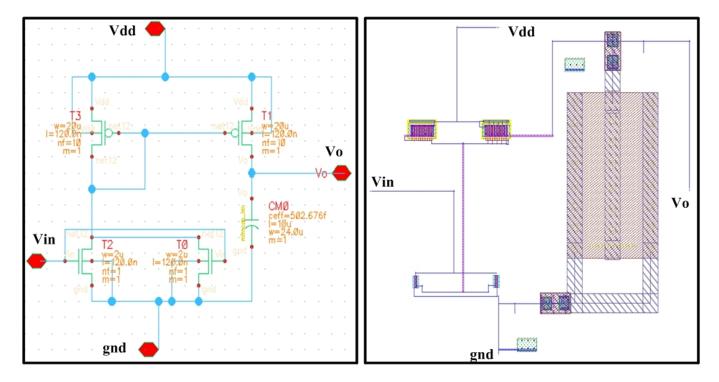

| 4.6  | Schematic of XOR2. Circuit parameters: $W_{1,2} = 3\mu m$ , $W_{7,8} = 1.5\mu m$ , and                                              |    |

|      | $W_9 = 50 \mu m$ . $L = 0.13 \mu m$ for all transistors, $V_b = 0.8V$                                                               | 65 |

| 4.7  | Serial link with half and full rectangular EOMs. The same circuit and channel                                                       |    |

|      | parameters as those in Fig.4.3 are used                                                                                             | 66 |

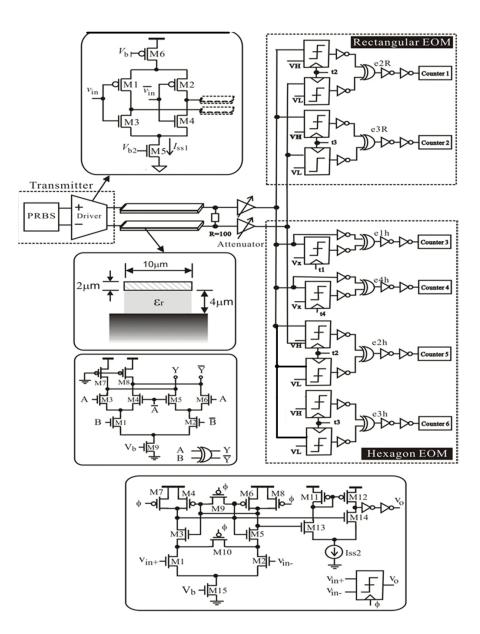

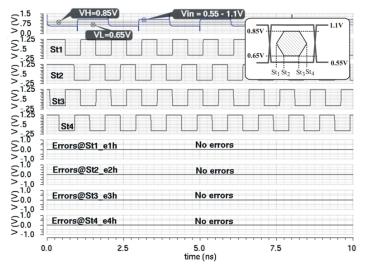

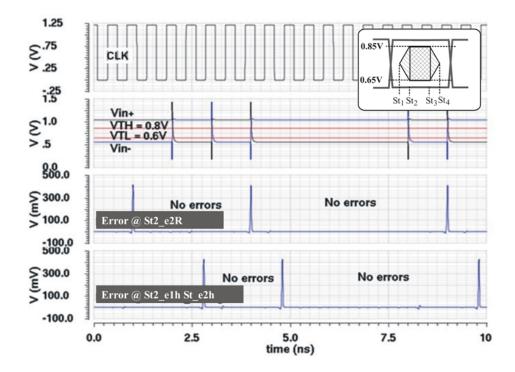

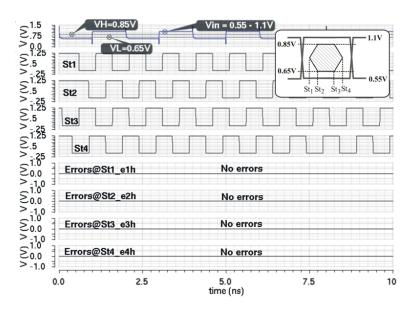

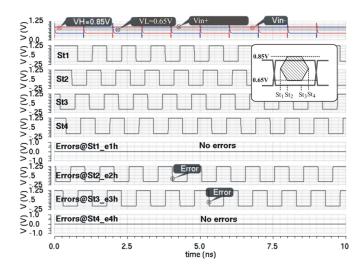

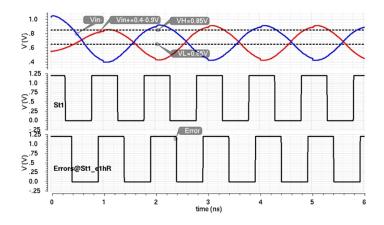

| 4.8  | Simulated output of full hexagon EOM with $v_{in,min} < V_L$ and $v_{in,max} > V_H$ .                                               |    |

|      | No error is detected at $St_2$ and $St_3$ . Top plot : Received data. 2nd-5th plots                                                 |    |

|      | : Sampling clocks $St_2 \sim St_4$ . 6th-9th plots : Error outputs $e1h \sim e4h$                                                   | 67 |

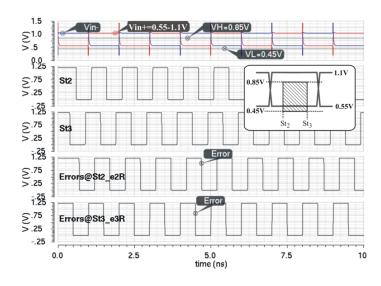

| 4.9  | Simulated output of half hexagon EOM with $v_{in,min} < V_L$ and $v_{in,max} > V_H$ .                                               |    |

|      | No error is detected at $St_2$ and $St_3$ . Top plot : Received data. 2nd-3rd plots                                                 |    |

|      | : Sampling clocks $St_2 \sim St_2$ . 4th-5th plots : Error outputs $e1h \sim e2h$                                                   | 68 |

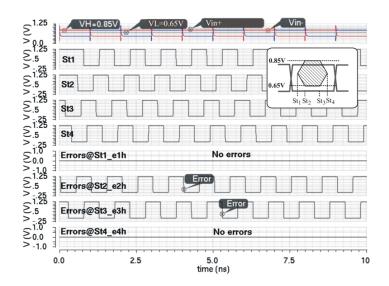

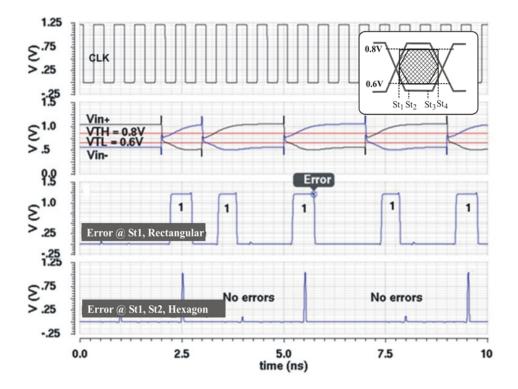

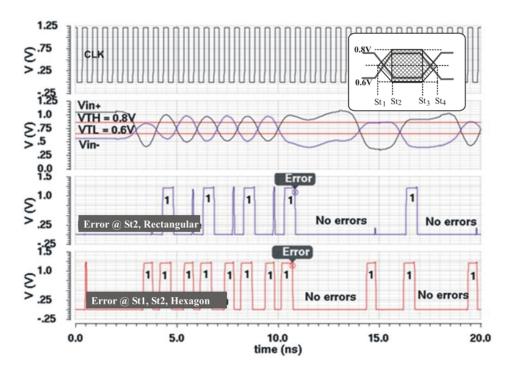

| 4.10 | Simulated output of full hexagon EOM with $v_{in,max} < V_H$ and $v_{in,min} < V_L$ .                                               |    |

|      | Errors are detected at $St_2$ and $St_3$ . Top plot : Received data symbol. 2nd-5th                                                 |    |

|      | plots : Sampling clocks $St_2 \sim St_4$ . 6th-9th plots : Error outputs $e1h \sim e4h$ .                                           | 68 |

| 4.11 | Simulated output of half hexagon EOM with $v_{in,max} < V_H$ and $v_{in,min} < V_L$ .                                               |    |

|      | Errors are detected at $St_2$ . Top plot : Received data symbol. 2nd-3rd plots :                                                    |    |

|      | Sampling clocks $St_2 \sim St_3$ . 4th-5th plots : Error outputs $e1h \sim e2h$                                                     | 69 |

| 4.12 | Simulated output of half hexagon EOM with a 200-mm channel. Top plot :                                                              |    |

|      | Received data. 2nd and 3rd plots : Sampling clocks $St_2 \sim St_3$ . 4th and 5th                                                   |    |

|      | plots : Output of half-hexagon EOM                                                                                                  | 69 |

| 4.13 | Simulated output of half rectangular EOM with a 200-mm channel. Top plot                                |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | : Received data. 2nd plot : Sampling clock $St_1$ . 3rd plot : Output of half-                          |    |

|      | rectangular EOM                                                                                         | 70 |

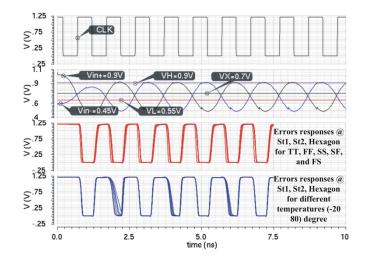

| 4.14 | Simulated output of hexagon EOM with a 200-mm channel. Top plot :                                       |    |

|      | sampling clock. 2nd plot : Received data symbol and the minimum verti-                                  |    |

|      | cal eye-opening. 3rd plot : Output of EOM at process corners (TT: typi-                                 |    |

|      | cal nMOS/typical pMOS; FF: fast nMOS/fast pMOS; FS: fast nMOS/slow                                      |    |

|      | $\rm pMOS,SF:$ slow nMOS/fast pMOS, and SS: slow nMOS/slow pMOS). Bottom                                |    |

|      | plot : Output of EOM with temperture from -20 $\sim$ 80C                                                | 70 |

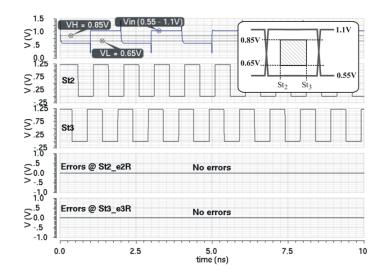

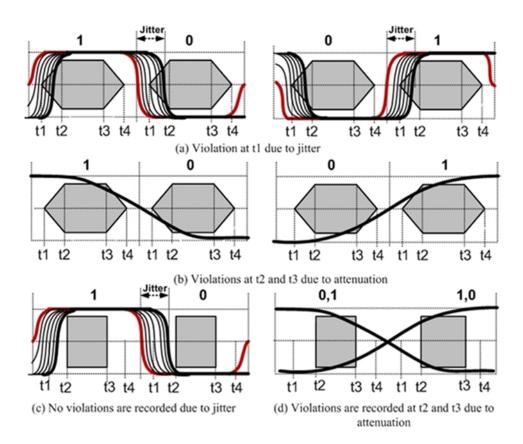

| 5.1  | (a) Violation of the minimum eye-opening at $t_1$ only. (b)Violation of the                             |    |

|      | minimum eye-opening at $t_1$ and $t_2$ . (c) No violation of the minimum hexagon                        |    |

|      | EOM but violation of the minimum rectangular EOM exists                                                 | 74 |

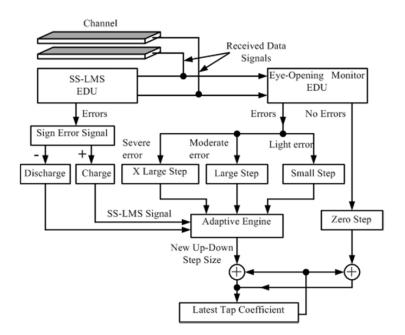

| 5.2  | Search engine of proposed hexagon EOM based adaptive DFE                                                | 76 |

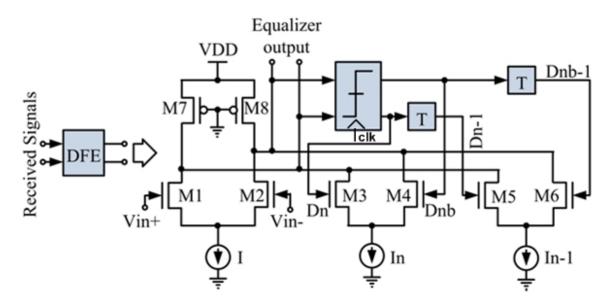

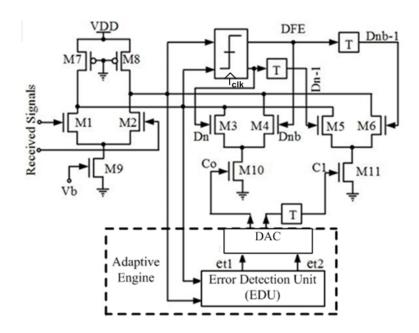

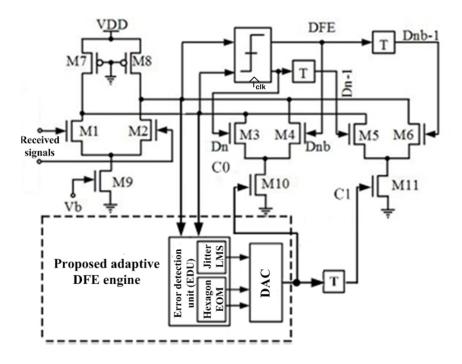

| 5.3  | DFE core. Transistor sizes: $W_{1,2} = 4\mu m$ , $W_{3,4,5,6} = 3\mu m$ , $W_{7,8} = 1\mu m$ , $W_9$    |    |

|      | = 40 $\mu$ m, and $W_{10,11}$ = 30 $\mu$ m, $L$ = 0.13 $\mu$ m. For all transistors biasing: $I_{ss}$ = |    |

|      | $2\mu A, V_b = 0.8 V$                                                                                   | 77 |

| 5.4  | Error detection units.                                                                                  | 79 |

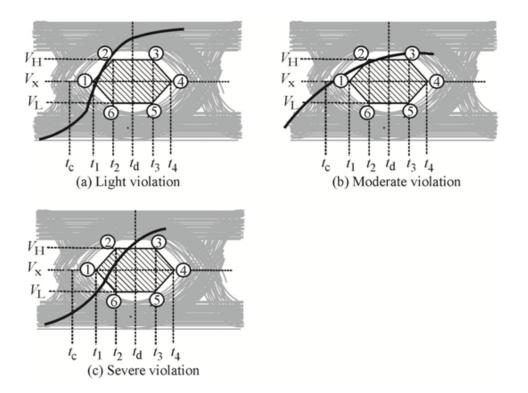

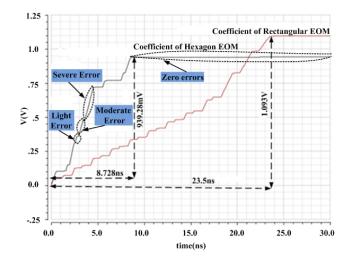

| 5.5  | Severity of violation with hexagon EOM                                                                  | 80 |

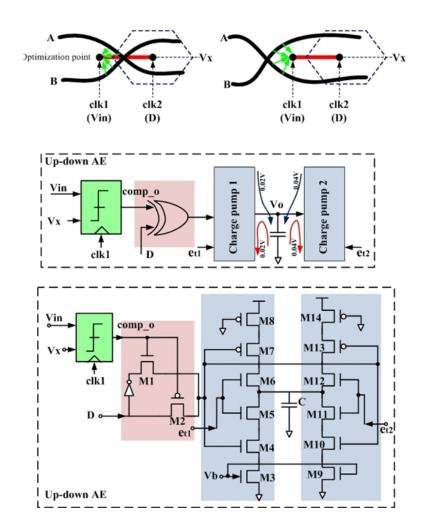

| 5.6  | Configuration (top) and schematic (bottom) of variable step-size DAC. Charge                            |    |

|      | pump $M_3$ - $M_8$ is enabled when $e_{t1}=1$ . Charge pump $M_9$ - $M_{14}$ is enabled when            |    |

|      | $e_{t2}=1$ .                                                                                            | 81 |

| 5.7  | Proposed adaptive DFE                                                                                   | 83 |

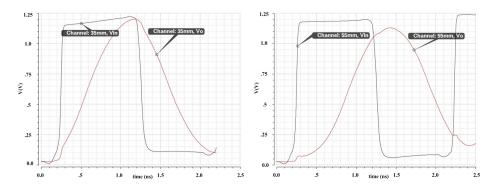

| 5.8  | Response of channels of length 35 mm (left) and 55 mm (right) to a pulse                                |    |

|      | input at the near end of the channel                                                                    | 84 |

| 5.9  | Tap coefficients of adaptive DFE with hexagon and rectangular EOMs                                      | 85 |

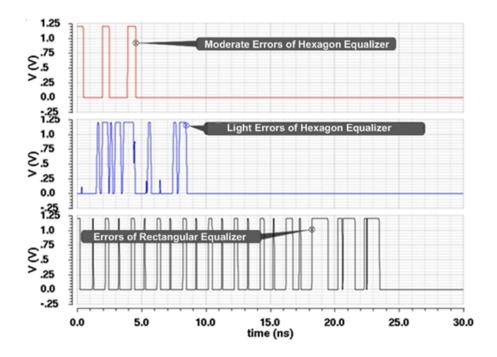

| 5.10 | Error detection of rectangular and hexagon adaptive DFE                                                 | 86 |

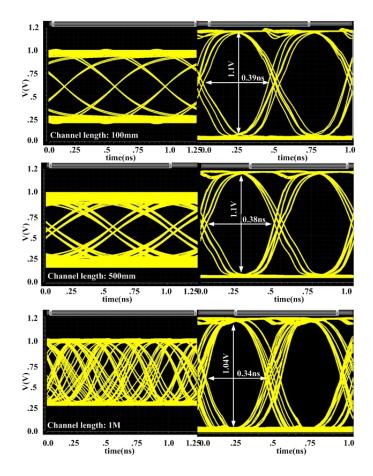

| 5.11 | Waveform of data before (left) and after (right) the proposed adaptive DFE.                                                                |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Top: channel length=100 mm. Middle: channel length=500mm. Bottom:                                                                          |     |

|      | channel length=1M                                                                                                                          | 87  |

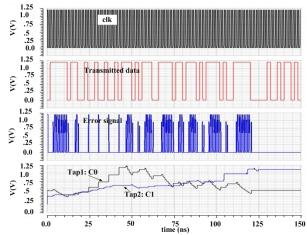

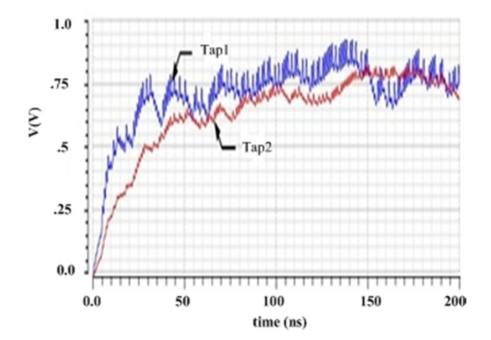

| 5.12 | Error detection and tap coefficients of proposed adaptive DFE with $35 \text{ mm}$                                                         |     |

|      | channel length.                                                                                                                            | 88  |

| 5.13 | Error detection and tap coefficients of proposed adaptive DFE with 55 mm $$                                                                |     |

|      | channel length.                                                                                                                            | 88  |

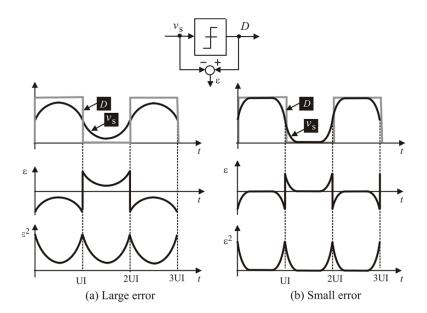

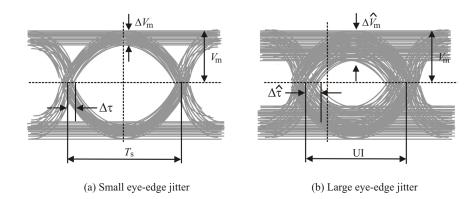

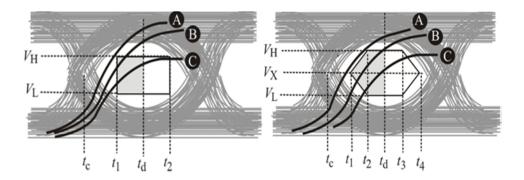

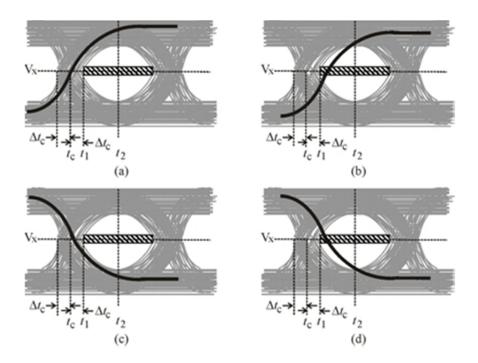

| 6.1  | Jitter-based of error detection. (a,c) - No error exists. (b,d) - Errors exist. $% \left( {\left( {{{\bf{n}}_{\rm{c}}} \right)} \right)$ . | 92  |

| 6.2  | Adaptive engine of proposed jitter-based adaptive DFE                                                                                      | 94  |

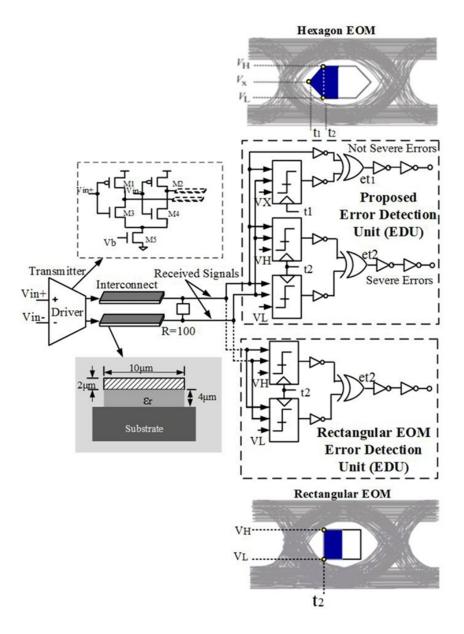

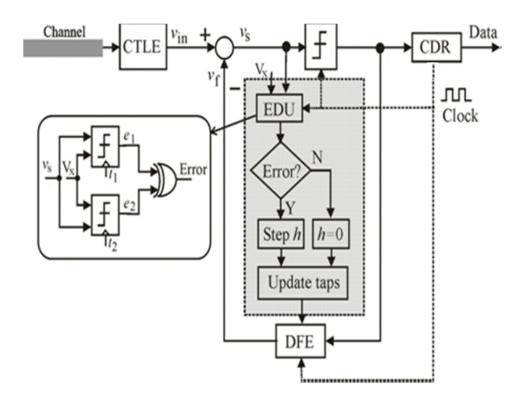

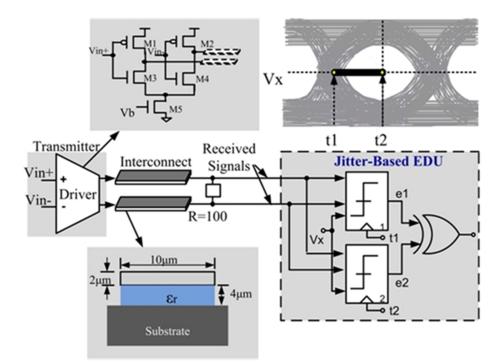

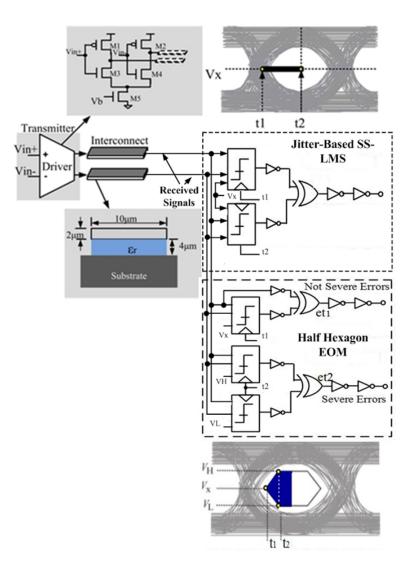

| 6.3  | Error Detection Unit. Channel parameters : Microstrip with width $10\mu\mathrm{m},$                                                        |     |

|      | height 2 $\mu{\rm m},$ and length 80 $\mu{\rm m}.$ Dielectric constant of field oxide : $\epsilon_r=5.$                                    | 95  |

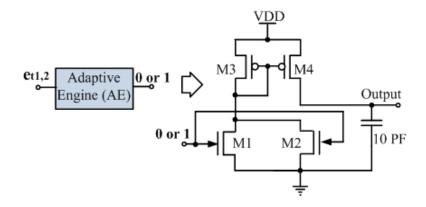

| 6.4  | Schematic of digital-to-analog converter (DAC)                                                                                             | 96  |

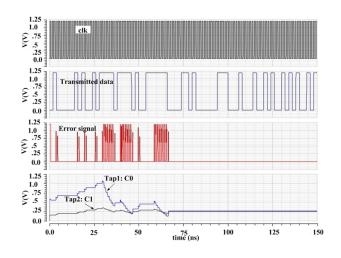

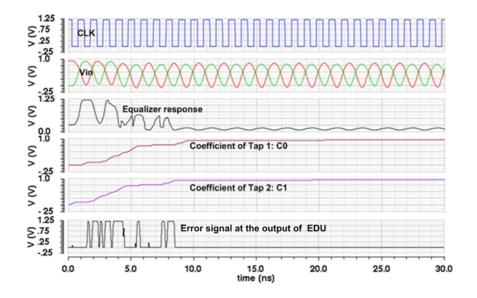

| 6.5  | Adaptation process of proposed jitter-based adaptive DFE with a 20 $\rm mm$                                                                |     |

|      | channel                                                                                                                                    | 97  |

| 6.6  | Waveforms of data symbols without (left) and with (right) the proposed 2-tap                                                               |     |

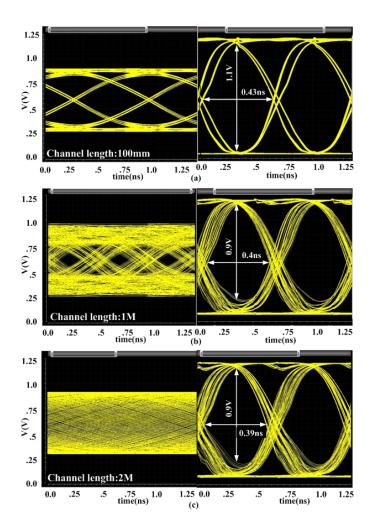

|      | jitter-based adaptive DFE. Channel lengths : (a) 100 mm, (b) 1M, and (c) 2M.                                                               | 98  |

| 6.7  | (a) : Simulated eye diagram of the data link. Channel length : 50 mm. Top                                                                  |     |

|      | : Data conveyed to the channel. Middle : Data at the far-end of the channel                                                                |     |

|      | without the proposed DFE. Bottom : Data at the far-end of the channel with                                                                 |     |

|      | the proposed DFE. (b) : The left edge of the simulated eye diagram of the data $\$                                                         |     |

|      | link. Channel length : 50 mm. Top : Data conveyed to the channel. Middle :                                                                 |     |

|      | Data at the far-end of the channel without the proposed DFE. Bottom : Data                                                                 |     |

|      | at the far-end of the channel with the proposed DFE                                                                                        | 99  |

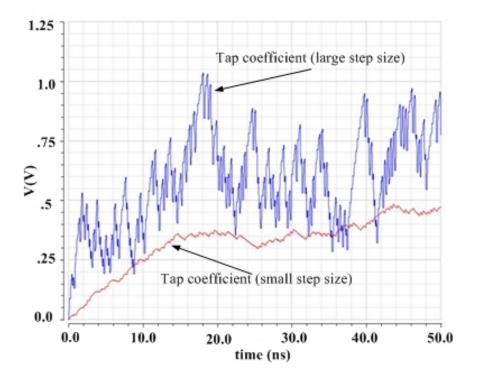

| 6.8  | LMS tap coefficients                                                                                                                       | 100 |

| 6.9  | LMS step size                                                                                                                              | 101 |

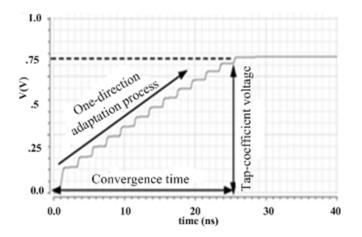

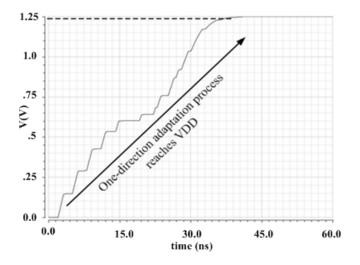

| 6.10 | One-direction step size of EOM                                                                                                             | 102 |

| 6.11 | Drawback of one-direction step size of EOM                                                                                                 | 102 |

| 6.12 | The schematic of proposed adaptive DFE including the proposed adaptive |     |

|------|------------------------------------------------------------------------|-----|

|      | engine                                                                 | 103 |

| 6.13 | Search engine of proposed new adaptive engine for adaptive DFE         | 104 |

| 6.14 | Serial link including two error detection units.                       | 105 |

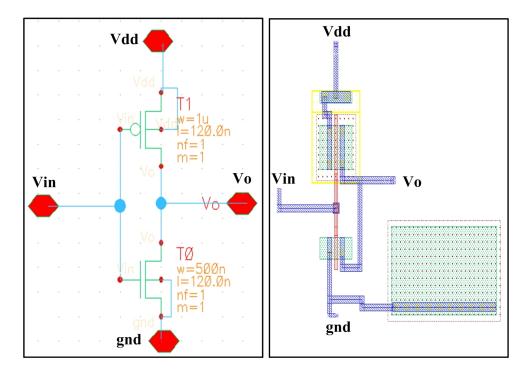

| 6.15 | Inverter: schematic (left) and layout (right).                         | 108 |

| 6.16 | NOR2: schematic (left) and layout (right)                              | 108 |

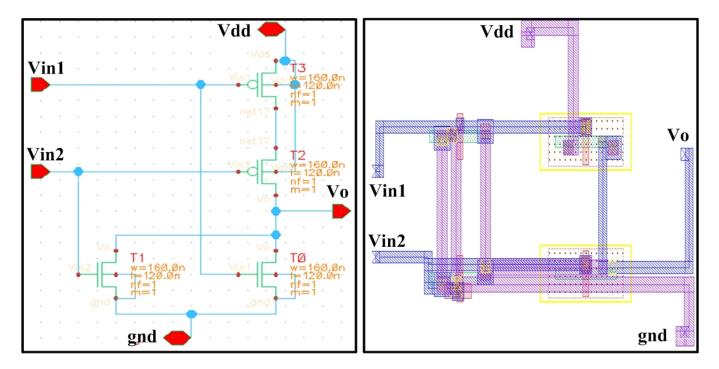

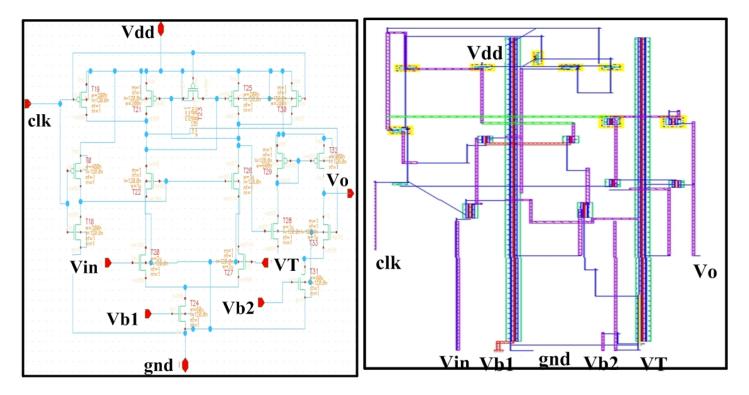

| 6.17 | XOR2: schematic (left) and layout (right)                              | 109 |

| 6.18 | Delay cell: schematic (left) and layout (right)                        | 109 |

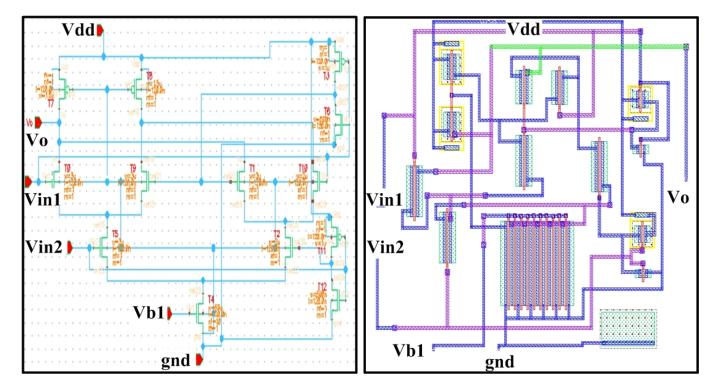

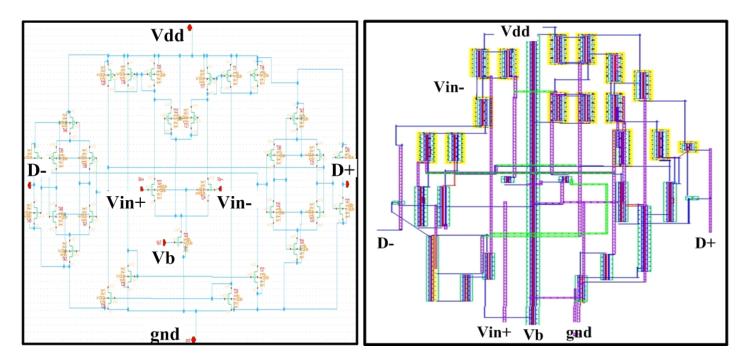

| 6.19 | Clocked-comparator: schematic (left) and layout (right).               | 110 |

| 6.20 | Non-clocked-comparator: schematic (left) and layout (right)            | 110 |

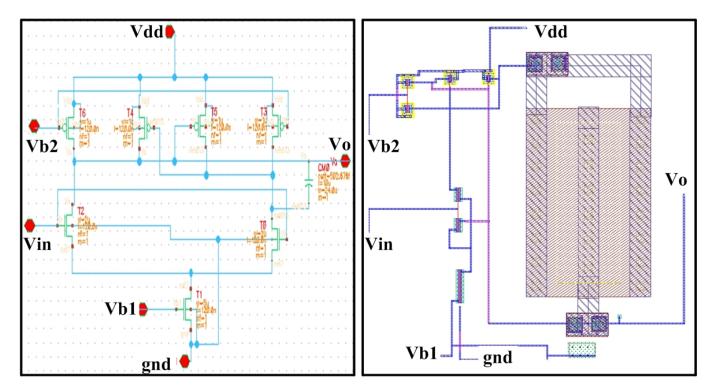

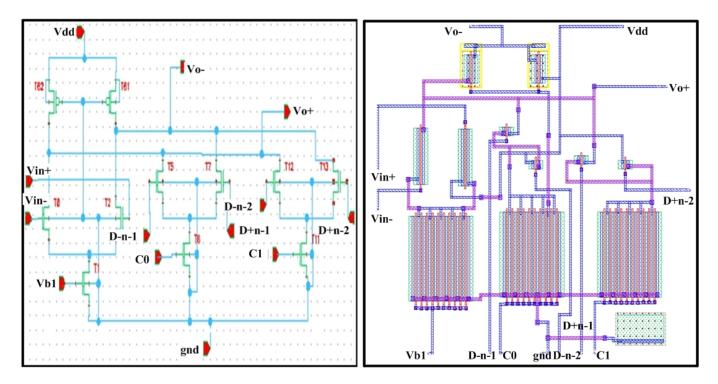

| 6.21 | Adaptive engine: schematic (left) and layout (right).                  | 111 |

| 6.22 | DFE core: schematic (left) and layout (right).                         | 111 |

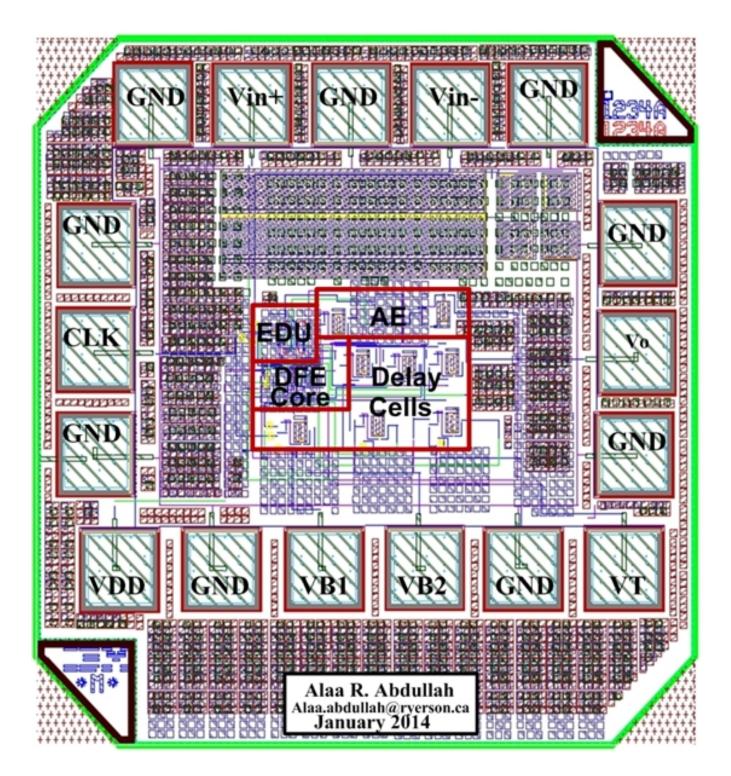

| 6.23 | Layout of maximum-jitter adaptive DFE                                  | 112 |

## List of Tables

| 1.1 | Data rate of serial links utilizing decision feedback equalization. Channel loss |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | is measured at half baud-rate frequency                                          | 20  |

| 3.1 | Eye-opening monitors                                                             | 45  |

| 4.1 | Reference comparison of proposed works                                           | 71  |

| 4.2 | Reference comparison of adaptive DFEs                                            | 71  |

| 5.1 | Performance of proposed hexagon eye-opening monitor adaptive DFE (2 Me-          |     |

|     | ter FR4 channel)                                                                 | 89  |

| 6.1 | Performance of proposed jitter adaptive DFE (1 meter channel length)             | 107 |

## Table of Abbreviations and Symbols

| Abbr.  | Full Name                              | Symb.                | Full Name                  |

|--------|----------------------------------------|----------------------|----------------------------|

| ADFE   | Adaptive DFE                           | $C_k$                | Weighting factor           |

| ADC    | Analog to digital converter            | $_{\rm ck,clk,\phi}$ | Clock signal               |

| BER    | Bit error rate                         | $D_k$                | Comparator decision        |

| CDR    | Clock and data recovery                | $e_n$                | Error signal               |

| CTLE   | Continuous time linear equalizer       | $g_m$                | Trans-conductance of CMOS  |

| DAC    | Digital to analog converter            | $H_n$                | Equalized feedback cursors |

| DFE    | Decision feedback equalizer            | h                    | Step size                  |

| EOM    | Eye-opening monitor                    | $t_n, S_{tn}$        | Sampling time              |

| FFE    | Feed forward equalizer                 | $V_b$                | Bias voltage               |

| FIR    | Finite impulse response                | $V_H$                | Voltage high               |

| Gbps   | Gigabit per second                     | $V_{in}$             | Input voltage              |

| HEOM   | Hexagon EOM                            | $V_L$                | Voltage low                |

| IIR    | Infinite impulse response              | $V_o$                | Output voltage             |

| I.Cs   | Integrated circuits                    | $V_{th}$             | Threshold voltage          |

| ISI    | Inter symbol interference              |                      |                            |

| LFSR   | Linear feedback shift register         |                      |                            |

| LMS    | Least mean square                      |                      |                            |

| NRZ    | Non return to zero                     |                      |                            |

| PCB    | Printed circuit board                  |                      |                            |

| PRBS   | Bseudo Random bit stream               |                      |                            |

| PVT    | Process of voltage and temp. variation |                      |                            |

| RX     | Receiver                               |                      |                            |

| SNR    | Signal to noise ratio                  |                      |                            |

| SS-LMS | Sign-sign LMS                          |                      |                            |

| ΤХ     | Transmitter                            |                      |                            |

| UI     | Unit interval                          |                      |                            |

# Chapter 1 Introduction

This chapter provides a comprehensive review of decision feedback equalization (DFE) for multi-giga-bit-per-second (Gbps) data links. The state-of-the-art of DFE for multi-Gbps serial links reported in the past decade is presented. The imperfections of wire channels, in particular, finite bandwidth, reflection, and cross-talk, and their impact on data transmission are investigated. The fundamentals of both near-end and far-end channel equalization to combat the effect of the imperfection of wire channels at high frequencies are explored. Finally, a detailed examination of the principle, configuration, operation, and limitation of DFE is discussed.

#### 1.1 Motivation

The explosive growth of data processed by integrated circuits (ICs) demands that data be transmitted over wire channels (interconnects, vias, connectors, package pins, printed circuit boards PCBs, and coaxial cables) at multiple Gbps. Although increasing the number of wire channels directly improves the total data bandwidth, a large number of parallel channels not only increase the cost of routing, the overall data rate is also affected by clock and data skews caused by the mismatch of the channels [1]. As a result, parallel links are only attractive for short-range data communications such as multi-processor systems, processor-to-memory interfaces, and network switches. Unlike parallel links, serial links transmit data and clock using a single wire channel, typically a differential pair to minimize electromagnetic interference with neighboring devices. The elimination of a dedicated channel for clock transmission removes the difficulties associated with clock skew. The use of only a single wire channel also eliminates the bottle neck associated with data skew. Moreover, it greatly reduces the cost associated with routing. As a result, serial links are very attractive in applications such as block-to-block (on-chip), chip-to-chip, chassis-to-chassis, and computer-to-computer links where the distance over which data are transmitted is large and the number of channels available is small.

Figure 1.1: Dependence of data rate on the minimum channel length of MOS transistors.

Although the maximum transit frequency of MOS transistors has well exceeded 100 GHz, the data rate of serial links is much lower, as evident in Table 1.1, despite the nearly linear improvement of the maximum data rate with technology scaling, as shown in Fig.1.1. The low data rate is mainly due to inter-symbol interference (ISI) arising from channel imperfections with limited bandwidth, reflection, and cross-talk the most critical.

**Figure 1.2:** (a) Frequency response of a 30" trace on a Nelco4000-13SI board [1]. (b) Frequency response of a 16" Tyco legancy backplane with two daughter cards [4]. (c,d) Frequency response and impulse response of a highly reflective backplane [5] (Copyright ©IEEE).

The limited bandwidth of channels caused by the rising resistive and dielectric loss of the channels at high frequencies gives rise to a long channel impulse response or equivalently frequency-dependent attenuation, as shown in Fig.1.2(a). Reflection caused by the impedance mismatch of channels, largely due to the inclusion of vias, connectors, and branches in the channels, results in crests and troughs that are non-uniformly distributed over a large number of symbol intervals in channel impulse response or equivalently sharp troughs in frequency domain response, as shown in Fig.1.2(b) [2], [3], [4]. Note that troughs are due to capacitive impedance mismatches. For channels with severe reflection, deep troughs exist, as shown in Fig.1.2(c,d). Crosstalk is primarily due to capacitive and inductive coupling with neighboring devices and manifests itself as crests and troughs in the channel impulse response. As a result, received data symbols at the far end of the channel consist of precursors, main cursor, and post-cursors with the number of post-cursors significantly larger than that of the pre-cursors, as shown in Fig.1.2(d). The main cursor is used for data recovery while pre-cursors and post-cursors need to be removed. They can be removed using near-end and far-end channel equalization.

### 1.2 Objective of The Dissertation

The main objective of this dissertation is to develop a new adaptive decision feedback equalizer (DFE) to mitigate the channel imperfections for multi-Gbps serial links. The proposed adaptive DFE consists of three blocks: DFE core, error detection unit (EDU), and adaptive engine (AE). The following list highlights our intended objectives chosen for this dissertation:

- 1. Modify and improve a summer circuit based on noise, speed, and power consumption to consider it as the core of the proposed adaptive DFE.

- 2. Create a new technique in the error detection unit (EDU) to efficiently detect the violations of the received data symbols with minimum requirements to safely detect the symbols at the clock and data recovery (CDR) operation.

- 3. Improve the schematic of EDU to minimize the power consumption.

- 4. Develop a new adaptive engine (AE) to update the DFE tap coefficients at Giga-bit-per second data rate and improve the convergence time of the adaptation process.

- 5. Combine the proposed DFE core, error detection unit, and adaptive engine in a comprehensive schematic to form an adaptive DFE and validate it for the speed and power consumption.

- Prepare a chip layout for the proposed adaptive DFE and fabricate it using an IBM 130 nm 1.2V CMOS technology.

### **1.3** Chapter Organization

The remainder of the chapter is organized as the followings : Section 1.4 addresses the effect of inter-symbol interference (ISI) on the integrity of received data signals. Section 1.5 investigates the imperfections of wire channels, in particular, finite bandwidth, reflection, and cross-talk, and their impact on data transmission. The fundamentals of both near-end and far-end channel equalization to combat the effect of the imperfection of wire channels at high frequencies are explored. Section ?? provides a detailed examination of the principle, configuration, operation, and limitation of DFE. Design challenges encountered in the design of DFE for multi-Gbps data links including timing constraints, sampling, error propagation, arithmetic operation, highly dispersive channels, power consumption, and techniques and circuit implementations that address these challenges are studied. Section 2.10 investigates the need for adaptive DFE and the principles of adaptive DFE. The performance of various adaptive DFEs is examined and their pros and cons are compared. The chapter is summarized in Section 2.11. The contributions of the dissertation are provided in Section 1.8 and finally, the organization of the dissertation is given in Section 1.9.

#### **1.4 Inter-Symbol Interference**

Inter-symbol interference (ISI) occurs when data symbols pass through a channel of finite bandwidth. It stretches the rising and falling times exceeding the symbol unit interval (UI) and interferes with previous symbols creating pre-cursors and post-cursor, as shown in Figs.(1.3) and (1.4). At a high data rate, the finite channel bandwidth caused by skin effect, dielectric loss due to the parasitic capacitances between the channel and the substrate, the cross-talk between the channel and its neighbors, and the reflections arising from impedance mismatches at both near and far ends of the channel are the main channel imperfections that contribute most ISI. Due to these effects, the received data symbol at the far end of the channel contains a long tail reducing the opening of the received data eye.

Figure 1.3: Pre-cursors, main cursor, and post-cursors of data symbol at the far end of a wire channel.

Figure 1.4: Inter-symbol interference in multi symbols.

### 1.5 Channel Equalization

Equalization techniques are widely used to combat ISI. In wire channels, where the channel can roughly be modeled as a low-pass filter, ISI is introduced when the data rate becomes higher than the bandwidth of the channel. This causes the frequency spectrum of the data to suffer from unequal magnitude attenuation and phase shifts leading to the distortion of the received signal [6]. Equalization is basically the process of generating a response opposite to the transfer function of the channel. It can be implemented at the channel near end called pre-emphasis, de-emphasis or at the channel far end known as post equalization.

#### **1.5.1** Near-End Channel Equalization

Pre-cursors and post-cursors can be removed by boosting the high-frequency components [7], [8] or attenuating the low-frequency components of data symbols [9], [10] prior to transmission. The former increases cross-talk as cross-talk intensifies at high frequencies. The latter reduces the power of the transmitted symbols as the power of non-return-to-zero (NRZ) data is largely concentrated at half baud-rate frequency. Since it increases the relative strength of the high-frequency components of the transmitted signals, cross-talk is also reduced [11]. Near-end channel equalization is often implemented using finite impulse response (FIR) filters that introduce zeros to offset the effect of the poles of the channels [12], [55]. For example, the first-order pre-emphasis FIR filter shown in Fig. 1.2(b) and given by  $y(n) = x(n) - a_1x(n-1)$  where x(n) and y(n) are the input and output of the FIR filter, respectively, has its transfer function  $H_{FIR}(z) = 1 - a_1 z^{-1}$ . Clearly it introduces a zero at z = 0 that will impact all the poles of the channels. To demonstrate this, since  $\omega T_s << 1$  where  $T_s$  the symbol time, we have  $z = e^{sT_s} \approx 1 + sT_s$ . As a result,

$$H_{FIR}(s) \approx (1 - a_1)(\frac{s}{\omega_z} + 1),$$

(1.1)

where  $\omega_z = (1 - a_1)/(a_1T_s)$ . If we model the channel as a first-order low-pass, i.e.  $H_{ch}(s) = 1/(\frac{s}{\omega_{ch}}+1)$  where  $\omega_{ch}$  is the channel bandwidth, the transfer function of the equalized channel is given by

$$H_{eq}(s) = (1 - a_1) \left[ \frac{\frac{s}{\omega_z} + 1}{\frac{s}{\omega_{ch}} + 1} \right].$$

(1.2)

It becomes apparent that if we choose  $\omega_z = \omega_{ch}$ , the pole of the channel will be canceled by the zero of the pre-emphasis FIR, resulting in a desirable all-pass. Also observed is that since  $(1 - a_1) < 1$ , there is a loss of signal energy in pre-emphasis.

Since the characteristics of the channel are not known prior to data transmission, the optimal tap coefficients of pre-emphasis FIR filters can only be obtained if a back channel exists. This constraint undermines the robustness of pre-emphasis channel equalization. Another limitation of pre-emphasis channel equalization is its inability to remove ISI caused by reflection and crosstalk as these ISI manifest themselves as crests and troughs rather than uniformly sloped attenuation, as shown earlier in Fig.1.5. ISI caused by reflection and crosstalk is typically significant when data rate is high and channels contain multiple vias, connectors, and branches (highly reflective channels).

Figure 1.5: Near-end channel equalization with first-order pre-emphasis. The added pre-emphasis tap shortens the duration of the received symbol thereby improving data rate.

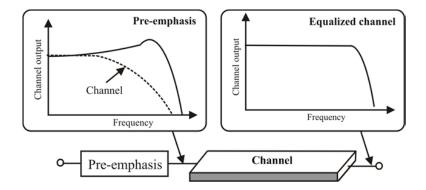

#### **Pre-Emphasis Equalization**

Figure 1.6 shows graphically the principle of the pre-emphasis equalization at the channel near end. The high-frequency components of the transmitted symbol are boosted prior to transmission. The result is flattened frequency response of the received data symbol at the channel far end and improved the serial links bandwidth.

Figure 1.6: Frequency response of an equalized channel with pre-emphasis. The high-frequency components of data symbols are boosted prior to their transmission.

#### **De-Emphasis Equalization**

De-emphasis equalization is the other technique falls within the classification of pre-emphasis. The principle of this technique is depicted in Fig.1.7. The low-frequency components of the transmitted symbol are attenuated while keeping the high-frequency components intacted. The received symbol at the channel far end is flattened. De-emphasis reduces the total amount of the transmitted-symbol-power subsequently deteriorates the bit-error-rate (BER) of the data link. This is because the power of the data symbol is largely concentrated at low frequencies.

Figure 1.7: Frequency response of an equalized channel using de-emphasis. The low-frequency components of data symbols are attenuated prior to their transmission.

#### 1.5.2 Far-End Channel Equalization

Far-end channel equalization also known as post-equalization combats ISI by either amplifying the high-frequency components of received data symbols in the analog domain or removing post-cursors in the digital domain prior to clock and data recovery (CDR). As compared with near-end equalization, post-equalization offers the ability to combat ISI caused by reflection and crosstalk.

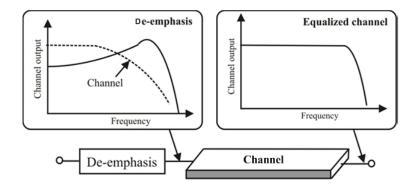

#### Linear Post-Equialization

Linear post-equalization boosts the high-frequency components of received data-symbols with a continuous-time linear equalizer (CTLE). CTLE provides zeros to cancel out the poles of the channels so that the equalized channel exhibits an all-pass transfer characteristic. To demonstrate this, consider the CTLE in Fig.1.8 and neglect the capacitance of MOSFETs. We examine three cases :

• If only  $C_x$  is considered (neglect  $R_x$ , L, and  $C_L$ ), the transfer function is given by

Figure 1.8: Continuous-time linear equalizers with inductor series peaking, source degeneration, and negative capacitors.

$$\frac{V_o(s)}{V_{in}(s)} = -\frac{sRC_x}{\frac{sC_x}{g_m} + 1},\tag{1.3}$$

where  $g_m$  is the transconductance of the MOSFETs. The feedback provided by  $C_x$ adds a zero at frequency  $\omega_z = 0$ . The pole provided by  $C_x$  is at frequency  $\omega_p = g_m/C_x$ .  $\omega_p$  must be sufficiently higher than the half baud-rate frequency so that its impact is negligible. The domain in which the added zero is effective in compensating the effect of the poles of the channel is given by  $\omega_z \leq \omega \leq \omega_p$ .

• If we consider both  $C_x$  and  $R_x$  (Neglect L and  $C_L$ ), the transfer function becomes

$$\frac{V_o(s)}{V_{in}(s)} = -\frac{Rg_m(sR_xC_x+1)}{(R_xg_m+1)(\frac{sR_xC}{R_xg_m+1}+1)},$$

(1.4)

The zero is now located at  $\omega_z = 1/(R_x C_x)$  and the pole is at  $\omega_p = 1/(R_x g_m + 1)/(R_x C_x) \approx g_m/C_x$  provided  $R_x g_m >> 1$ . It is evident that  $\omega_z$  is now tunable by varying  $C_x$  and  $R_x$ .

• If L,  $R_x$ ,  $C_x$ , and  $C_L$  are all considered, the transfer function becomes

$$\frac{V_o(s)}{V_{in}(s)} = -\frac{Rg_m(sR_xC_x+1)(\frac{sL}{R}+1)}{(R_xg_m+1)LC_L(\frac{sR_xC}{R_xg_m+1}+1)(s^2+\frac{sL}{R}+\frac{1}{LC_L})},$$

(1.5)

It is seen from Equation(1.5) that the addition of the inductor peaking introduces another zero at  $\omega_{z2} = R/L$ . This is in addition to the zero introduced by  $C_x$  and  $R_x$ at  $\omega_{z1} = 1/(R_x C_x)$ . It also introduces complex conjugate poles with natural resonant frequency  $\omega_n = 1/\sqrt{LC_L}$ . It is well understood that complex conjugate poles improve bandwidth [16]. The zeros are used to cancel the effect of the poles of the channel so as to increase the bandwidth while the complex conjugate poles improve the bandwidth through resonance. The higher the quality factor, the larger the bandwidth improvement. The addition of the negative capacitors reduces  $C_L$ , which in turn boosts the natural resonant frequency  $\omega_n$  subsequently the bandwidth.

The use of zeros to offset the effect of the poles of wire channels bears a strong resemblance to the use of filtering mechanisms to compensate for the loss of wireless channels so as to shorten channel impulse response length or equivalently improve the channel bandwidth, for example, the time truncation of channel impulse response by filtering proposed in [17]. The computational cost of these mechanisms, however, makes them difficult to meet the ever stringent timing constraints of multi-Gbps serial links. As the received symbol is severely attenuated by the channel upon arriving CTLE, input offset voltage compensation is also required in CTLE [66]. The order of CTLE is determined by the attenuation of the channel and the sensitivity of the slicer. High-order CTLE can be obtained by cascading low-order CTLEs at the cost of more power consumption [19]. CTLE is often used in conjunction with nonlinear post-equalization with the former providing secondary channel equalization. As a result, low-order DFE can be used without sacrificing performance [20]. CTLE has also been used as a solo post-equalizer for channels with negligible reflection and cross-talk. The absence of feedback in this case allows CTLE to support higher data rates. For example, CTLE in 130 nm CMOS enables 10 Gbps transmission over 30 FR4 channel of -21 dB loss at half baud-rate frequency and achieves  $10^{-13}$  BER [21]. Similarly, CTLE implemented in 130 nm CMOS supports 10 Gbps transmission over 34 FR4 channel with -14 dB loss and consumes 6 mW [22]. It should be emphasized that CTLE is only effective in removing channel loss-induced ISI and ineffective in eliminating crosstalk/reflection-induced ISI [21].

#### **Nonlinear Post-Equalization**

Non-linear equalization is another technique of an equalization that is used at the channel far-end prior to a clock and data recovery operation. It uses past decisions rather than amplifying the high-frequency components or attenuating the low-frequency components of the received symbol to mitigate ISI in the time domain. Decision feedback equalization DFE technique is the most widely used nonlinear equalization at the far end of the channel.

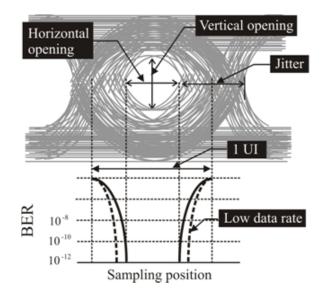

#### **1.6** Decision Feedback Equalization

Nonlinear post-equalization compensates the high frequency loss of the channel by removing the long tail of the received symbol in the time domain. The most widely used non-linear equalization is the decision feedback equalization (DFE) introduced by Austin in 1967 with its basic configuration shown in Fig.1.9 [23].

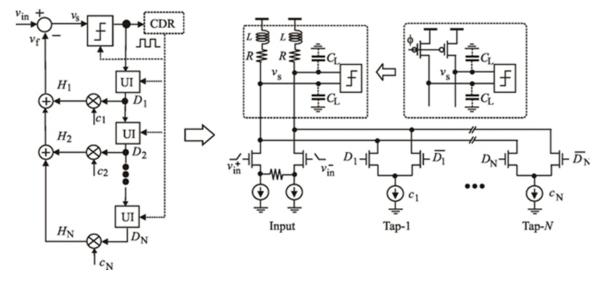

Figure 1.9: Basic configuration and operation of decision feedback equalization. Legends: UI - Delay cell with one unit delay,  $v_s = v_{in} - v_f$  is the symbol before the slicer.  $v_{ref}$  is the threshold of the slicer,  $D_{j=1}$  is the delayed version of  $D_j$ ,  $c_1,...,c_N$  are the weighting factors of feedback taps,  $T_s$  is the symbol time,  $H_{j,k}$  denote the kth post-cursor of symbol-j and  $H_{0,j}$  the main cursor of symbol-j.

The voltage comparator known as data slicer is clocked by the recovered clock. It samples the difference between the current symbol and the feedback signal, and makes a Boolean decision based on the comparison. To minimize the error in data slicing, the received symbol needs to be sufficiently large. This is achieved by amplifying the received symbol prior to slicing [20]. Because the amount of amplification needed in forward equalization at the farend of the channel is set by the sensitivity of the data slicer, which is typically much smaller as compared with that required for channel equalization with a linear equalizer at the near end of the channel, the cross-talk induced by feed-forward equalization at the receiver is minimal. The output of the slicer passes through N delay stages where N is the number of the post-cursors of the current symbol. The output of each delay stage is multiplied by a proper weighting factor  $c_k$  such that  $H_k = c_k D_{j-k}$  holds where  $H_k$  is the  $k^{th}$  post-cursor of the current symbol and  $D_{j-k}$  is the  $(j - k)^{th}$  past decision of the slicer. It becomes evident that the functionality of the feedback network of DFE is to replicate the post-cursors of the current symbol using the past decisions such that when the feedback is subtracted from the current symbol, the post-cursors of the current symbol are removed ideally.

To illustrate how DFE removes the post-cursors of the current symbol in an intuitive way, let us assume that the current and previous symbols at the far-end of the channel have a main cursor, and four post-cursors. Further, let us assume that there are consecutive logic-1s and the response of the channel to logic-1s is identical, i.e., the response of the channel has the same main cursor and post-cursors. Assume symbol-1 has been correctly detected and DFE is now processing the next symbol. The output of the data slicer for symbol-1 is delayed by one unit interval (1UI), typically one symbol time, with a delay cell and then multiplied by a proper weighting factor  $c_1$  to create  $H_1 = c_1 D_{j-1}$  where  $H_1$  is the amplitude of the first post-cursor of the current symbol such that when subtracted from the current symbol, the first post-cursor of the current symbol is removed, as illustrated graphically in Fig.1.9. To remove the remaining post-cursors, an additional three delay cells and multipliers are needed. Mathematically, if we let symbol j be  $v_{in,j}$ , then in the discrete domain, it can be written as

$$v_{in,j} = v_j + \sum_{k=1}^{4} v_{j-k} + n_j, \qquad (1.6)$$

where  $v_j$  denotes the main cursor of symbol j,  $v_{j-k}$ , k = 1, 2, 3, 4 denote the four postcursors of symbol j, and  $n_j$  denotes the noise present in the symbol and sampled at the time when the main cursor is sampled. Note that  $v_{j-k} = 0$  if i < k. The output of the feedback network is given by

$$v_{f,j} = \sum_{k=1}^{4} c_k + D_{j-k}, \qquad (1.7)$$

where  $D_{j-k}$ , k = 1, 2, 3, 4 are the four past decisions of the slicer and  $c_k$  is the weighting factor assigned to  $D_{j-k}$ . The input of the slicer is given by

$$e_j = v_{in,j} - v_{f,j},$$

(1.8)

$$e_j = v_j + \sum_{k=1}^{4} [v_{j-k} - c_k D_{j-k}] + n_j.$$

(1.9)

It becomes clearly that if  $c_k$  is properly chosen, the term in the brackets in (1.9) will vanish, i.e., the post-cursors of the symbol will be completely removed. Also observed is that DFE operation has no impact on the noise present in the current symbol. Since DFE restores square-wave-like symbols by removing the post-cursors, it is equivalent to boosting the highfrequency components of the received symbol in the frequency domain. Although DFE has no effect on the precursors of the current symbol, fortunately ISI is primarily caused by post cursors. DFE is proven to be an effective, robust, and perhaps the most widely used technique to combat ISI of Gbps data links.

### 1.7 Chapter Summary

The imperfections of wire channels and their impact on data transmission were investigated. The pros and cons of near-end and far-end channel equalizations that combat ISI were explored. A detailed examination of the principle, configuration, operation, and limitation of DFE was provided.

### **1.8** Contributions of The Dissertation

The contributions of this dissertation are:

- 1. A comprehensive review of DFE for multi-Gbps data links is conducted. The review examines: i) The imperfection of wire channels, in particular, finite bandwidth, reflection, and cross-talk, and their impact on data transmission. ii) The fundamentals of both near-end and far-end channel equalization to combat the effect of the imperfection of wire channels at high frequencies. iii) Design challenges encountered in design of DFE for multi-Gbps data links including timing constraints, sampling, error propagation, arithmetic operation, highly dispersive channels, power consumption, and techniques and circuit implementations that address these challenges. iv) The need for adaptive DFE, the principles of adaptive DFE, the performance of various adaptive DFEs and their pros and cons.

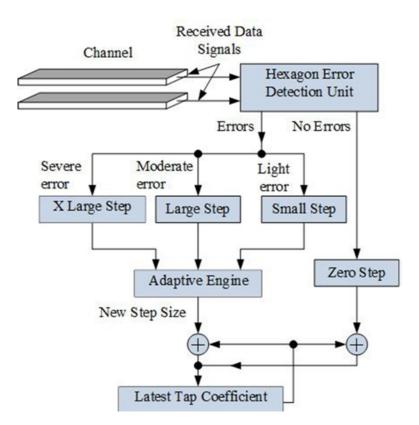

- 2. A two-dimensional hexagon eye-opening monitor (EOM) for Gbps serial links is proposed. As compared with rectangular EOM, the proposed EOM provides a tightened control of data jitter at the edge of data eyes and eliminates unnecessary errors flagged by the rectangular EOM. Moreover, it is able to recognize the severity of the errors. This allows the adaptive engine to provide variable step-size for updating DFE tap coefficients and reduces the convergence time of the adaptation process.

- 3. A power-efficient two-dimensional on-chip EOM for Gbps data links is proposed. The proposed EOM employs the half pattern of hexagon and rectangle EOMs to detect the violation of received data signals with the minimum required detection at the clock and data recovery (CDR) operation. As compared with full hexagon and rectangular EOMs, the proposed EOM eliminates half of the required comparators while keeping the same accuracy of error detection.

- 4. A hexagon EOM-based variable step-size adaptive DFE for multi-Gbps data links is proposed. The proposed adaptive DFE utilizes a half-hexagon EOM to detect the error of the received data signals. The step size used in search for the optimal tap coefficients of DFE is set by the severity of the violation of the pre-defined minimum eye-opening by received data symbols so as to achieve both a fast convergence of adaption and the maximum eye-opening. The effectiveness of the proposed adaptive DFE is evaluated by embedding it in a 1 Gbps serial link implemented in an IBM 130 nm 1.2V CMOS technology. For the purpose of comparison, an adaptive DFE with a rectangular EOM is also designed and included in the same data link. Simulation results demonstrate that the proposed adaptive DFE maximizes the eye-opening of received data symbols. Also, it outperforms the adaptive DFE with a rectangular EOM by reaching the convergence approximately 4 times faster.

- 5. A jitter-based adaptive decision feedback equalizer for high-speed serial links is proposed. The adaptation in search for the optimal tap coefficients of DFE is set by the detection of the violation of the maximum allowable jitter by the received data.

#### **1.9** Organization of The Dissertation

The dissertation is organized in 7 chapters. Chapter 1 provides a comprehensive review of decision feedback equalization for multi-Gbps data links. In the chapter, we examine the effect of iner-symbol interference on the integrity of received data signal, the imperfections of wire channels, in particular, finite bandwidth, reflection, and cross-talk, and their impact on

data transmission. Also, in this chapter, we reveal a detailed examination of the principle, configuration, operation, and limitation of DFE. Design challenges encountered in design of DFE for Gbps data links and techniques and circuit implementations that address these challenges address in Chapter 2. Chapter 3 proposes a two-dimensional hexagon EOM for Gbps data links. We show that the proposed EOM outperforms diamond and rectangular EOMs for a better error detection and shorter adaptive time. A power efficient hexagon EOM is presented in Chapter 4. Chapter 5 presents an adaptive decision feedback equalizer utilizing the proposed hexagon EOM for detecting errors. In Chapter 6, a maximum jitter based decision feedback equalizer is proposed. Chapter 7 concludes the dissertation and outlines future works.

| Table 1.1:                            | Data rate o | of serial lin | s utilizing | decision | feedback | equalization. | Channel loss is |

|---------------------------------------|-------------|---------------|-------------|----------|----------|---------------|-----------------|

| measured at half baud-rate frequency. |             |               |             |          |          |               |                 |

| Ref. | Tech.             | Channel loss        | Data rate             | Tx      | Rx              | BER                 |

|------|-------------------|---------------------|-----------------------|---------|-----------------|---------------------|

| [68] | 130  nm           | -8 dB               | $3.7 { m ~Gbps}$      | _       | 3 IIR           | $10^{-12}$          |

| [34] | 130  nm           | -21 dB (36" FR4)    | $6.25 \mathrm{~Gbps}$ | _       | 5-tap           | $10^{-15}$          |

| [30] | $130~\mathrm{nm}$ | -18 dB (33" FR4)    | $9.6 { m ~Gbps}$      | 2-tap   | CTLE/1-tap      | $10^{-15}$          |

| [11] | 130  nm           | -18 dB (30" FR4)    | $6.4 \mathrm{~Gbps}$  | 4-tap   | 5-tap           | $10^{-15}$          |

| [15] | $130~\mathrm{nm}$ | -12 dB (26" FR4)    | $5~\mathrm{Gbps}$     | _       | 1-tap           | _                   |

| [20] | $130~\mathrm{nm}$ | -(40"  FR4)         | $6.4 { m ~Gbps}$      | 2-tap   | 4-tap           | $2 \times 10^{-15}$ |

| [31] | 90  nm            | -6.2 dB (10" SMA)   | $6.0 { m ~Gbps}$      | _       | 2-tap           | $10^{-12}$          |

| [45] | 90  nm            | -12 dB (16" Tyco)   | $7.0 { m ~Gbps}$      | _       | 2-tap           | $10^{-13}$          |

| [69] | 90  nm            | – (18" BP)          | $-7.5 \mathrm{~Gbps}$ | _       | 10-tap          | $10^{-12}$          |

| [29] | 90  nm            | -33 dB (16" FR4)    | $10 { m ~Gbps}$       | 4-tap   | 5-tap           | $10^{-12}$          |

| [66] | 90  nm            | -25.4 dB (29" FR4)  | $10.3 \mathrm{~Gbps}$ | 2/3-tap | CTLE/1-tap      | $10^{-13}$          |

| [70] | 90  nm            | -25.4 dB (15" FR4)  | $10 { m ~Gbps}$       | _       | 2-tap           | $10^{-12}$          |

| [71] | 90  nm            | -32.7 dB (5.5" FR4) | $6 { m ~Gbps}$        | —       | 1-tap & IIR     | $10^{-12}$          |

| [72] | 90  nm            | -14 dB (20" Nelco)  | $15 { m ~Gbps}$       | _       | 1-tap           | $10^{-13}$          |

| [75] | 65  nm            | -16 dB (30" PCB)    | $11 { m ~Gbps}$       | 3-tap   | 5-tap           | $10^{-15}$          |

| [25] | 65  nm            | -21 dB (50" Nelco)  | $10 { m ~Gbps}$       | _       | 1-tap & IIR     | $10^{-12}$          |

| [19] | 65  nm            | -24 dB (28" FR4)    | $8.5 { m ~Gbps}$      | _       | 3-tap           | —                   |

| [58] | 65  nm            | -24 dB (12" PCB)    | $12.5 \mathrm{~Gbps}$ | 4-tap   | 2-tap FFE/5-tap | —                   |

| [56] | 65  nm            | -13.3 dB (34" FR4)  | $5~\mathrm{Gbps}$     | _       | 1-tap           | $10^{-12}$          |

| [74] | 65  nm            | -13.3 dB (34" FR4)  | $5~\mathrm{Gbps}$     | _       | 1-tap           | $10^{-12}$          |

| [76] | 65  nm            | -13.3 dB (16" FR4)  | $21 { m ~Gbps}$       | 3-tap   | 1-tap           | $10^{-12}$          |

| [42] | 65  nm            | -22.3 dB (14" FR4)  | $20 { m ~Gbps}$       | —       | CTLE/1-tap      | $10^{-12}$          |

| [77] | 45  nm            | -21 dB (50" Nelco)  | $10 { m ~Gbps}$       | _       | DFE-IIR         | $10^{-12}$          |

| [78] | 45  nm            | -25 dB (18" FR4)    | $15 { m ~Gbps}$       | _       | 2-tap           | $10^{-12}$          |

| [79] | 45  nm            | -32 dB (40" Nelco)  | $16 { m ~Gbps}$       | 3-tap   | 12-tap          | $10^{-15}$          |

| [80] | 45  nm            | -25 dB (20" PCB)    | $19  \mathrm{Gbps}$   | —       | 4-tap FFE/5-tap | $10^{-13}$          |

| [81] | 40 nm             | -10 dB (3" FR4)     | $16 { m ~Gbps}$       | _       | 1-tap           | $10^{-12}$          |

| [82] | 40  nm            | -15 dB (3" FR4)     | $20 {\rm ~Gbps}$      | 1-tap   | CTLE/1-tap      | $10^{-12}$          |

| [83] | 40  nm            | -34 dB (24" FR4)    | $16 { m ~Gbps}$       | 3-tap   | 14-tap          | $10^{-12}$          |

| [84] | 40  nm            | -20 dB (8" FR4)     | $23 { m ~Gbps}$       | 2-tap   | CTLE/1-tap      | $10^{-12}$          |

| [85] | 32  nm            | -25 dB (14" PCB)    | $11.8 \mathrm{~Gbps}$ | 3-tap   | 4-tap           | $10^{-12}$          |

| [86] | 32  nm            | -27 dB (39" PCB)    | $12.5 \mathrm{~Gbps}$ | _       | CTLE/8-tap      | $10^{-12}$          |

| [87] | 32  nm            | -35 dB (15" PCB)    | $28 { m ~Gbps}$       | 4-tap   | CTLE/15-tap     | $10^{-13}$          |

| [88] | 28  nm            | -33 dB BP           | $12.5 \mathrm{~Gbps}$ | 5-tap   | CTLE/3-tap      | $10^{-15}$          |

# Chapter 2 Design Challenges in DFE

This chapter provides design challenges encountered in the design of DFE for multi-Gbps data links including timing constraints, sampling, error propagation, arithmetic operation, highly dispersive channels, power consumption, and techniques and circuit implementations that address these challenges. In the chapter, we investigate the need for adaptive DFE and the principles of adaptive DFE. Finally, we addres the performance of various adaptive DFEs and their pros and cons.

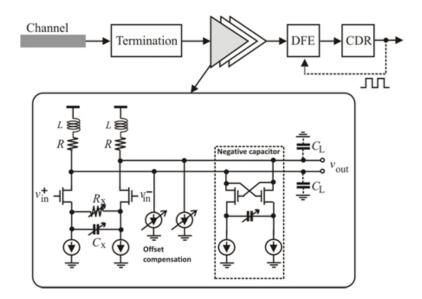

# 2.1 Bit Error Rate Test

The performance of serial links is primarily quantified by *Bit Error Rate* (BER) obtained by transmitting a *Pseudo-Random Bit Stream* (PRBS) to the channel and recording the number of transmission errors, typically  $BER = 10^{-12}$  is required. Transmission errors are obtained using a PRBS checker that compares the transmitted bits with the corresponding received bits. Although PRBS7 (7-bit PRBS) has been used [25], they are primarily for testing serial links with 8B/10B encoded data. PRBS31 (*31-bit PRBS*) that provides a sufficient transition density is preferred especially for those using 64B/66B encoded data. PRBS can be generated using *Linear Feedback-Shift Registers* (LFSR), although parallel PRBS generators are also available [26]. Since the data eye-opening is typically maximized at the center of the data eye where BER is minimized and gradually levels off towards the edges of the data

eye where BER climbs, the horizontal eye-opening at a given BER, for example  $10^{-8}$  [27],  $10^{-9}$  [25] or  $10^{-10}$  [86], is usually used as a figure-of-merit to quantify the performance, as shown in Fig.2.1. The bathtub curves are obtained by varying the sampling instant within *One Unit Interval* (One UI) while evaluating BER for each sampling instant [29]. It is seen that BER is minimized at the center of the data eye and gradually levels up when sampling instant moves away from the center towards the edge of the data eye.

Figure 2.1: Dependence of horizontal eye-opening on BER.

# 2.2 Timing Constraints

The operation performed by DFE including the delay of the previously recovered data, the multiplication of the recovered data by an appropriate weighting factor, the subtraction of the feedback signal from the current symbol, and data slicing must be completed in one UI, i.e., before the arrival of the next symbol. Since there is only one UI between the arrival of the current symbol and tap-1 feedback is allowed, tap-1 delay loop bears most of the timing

constrain. It becomes increasingly difficult to complete delay, multiplication, subtraction, and data slicing operations within one UI when data rate is high. An effective way to overcome this difficulty is to feed the error signal, i.e., the difference between the signal from the preceding forward equalizer and the feedback signal, to two identical slicers that are in parallel and operated simultaneously, for possible feedback signals, i.e.  $H_1$ . As shown in Fig.2.2, the decisions of the slicers are then multiplexed by a 2-to-1 multiplexer with the select signal the previous decision [30].

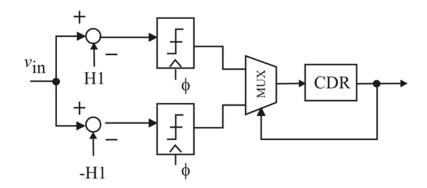

Figure 2.2: Tap-1 feedback is implemented using loop-unrolling.

This approach was originally proposed by Kasturia et al. [31] and is known as *loop unrolling*, *speculation*, *look-ahead* [32], or *partial-response* [33]. Since the multiplication, subtraction, and slicing can be conducted without waiting for the delay and the delay of 2-to-1 multiplexing is small, the stringent timing constrain on tap-1 feedback loop is greatly relaxed. The use of loop unrolling, however, is typically limited to tap-1 only simply because the number of slicers increases exponentially with the number of taps.

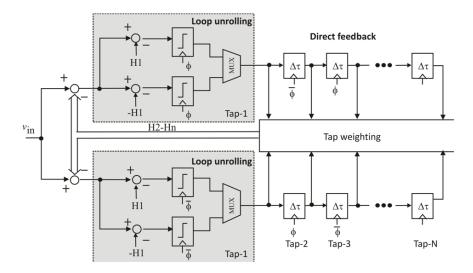

As pointed out in [34], the delay of the regenerative-configured slicer will be overly long once its input is small. To reduce the delay of the slicer, the insertion of an auxiliary amplifier between the forward equalizer and the slicer is proven to be beneficial. The speed gained from the insertion of the auxiliary amplifier overwhelms the delay of the auxiliary amplifier itself. To relax timing constraint and lower power consumption, the half-rate approach where all units of the DFE are operated at only half the data rate is widely favored, as depicted graphically in Fig.2.3. Two identical DFE paths are driven by a non-overlapping clock whose frequency is only half that required for the data rate as the two paths operate in an interleaved manner [11]. The relaxed timing constraint not only greatly simplifies design but also lowers power consumption. The timing constraint can be further relaxed using a quarter-rate approach with further reduced power consumption at the cost of power and silicon consumption [31].

Figure 2.3: Half-rate decision feedback equalization. Tap-1 is implemented using loop-unrolling while the remaining taps are implemented using direct feedback. Note that complementary clocks are used for upper and lower paths of DFE.

# 2.3 Timing Alignment

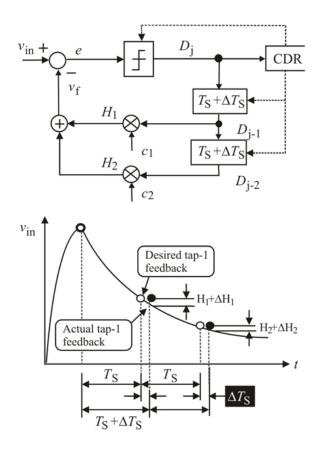

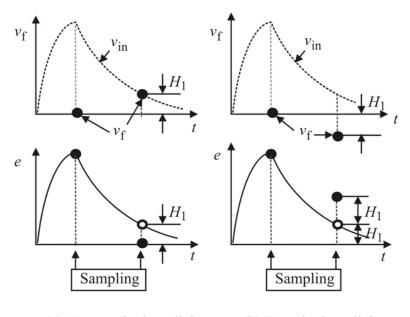

The removal of the post-cursors of the current symbol is achieved by subtracting the weighted past decisions from the current symbol. This approach is effective only if the characteristics of the channel does not change over N consecutive UIs, where N is the number of the taps of DFE. If there exists a timing alignment error between the post-cursors of the current symbol and the feedback signal, the post-cursor will not be removed completely even though the amplitude of the feedback signal is identical to that of the post-cursor, as illustrated graphically in Fig.2.4 where a DFE with 2 taps is shown. As can be seen that the timing error of the delay stages  $\Delta T_s$  where  $T_s$  is the symbol time, i.e.  $T_s$ =UI, will give rise to a

Figure 2.4: Post-cursor cancellation error due to timing error of delay stages.

$$\Delta H_k \approx \left[\frac{\partial v_{in}}{\partial t}\right]_{t=kT_s} \Delta T_s \tag{2.1}$$

feedback error  $\Delta H_k$ . When subtracted from the current symbol,  $\Delta H_k$  of the kth postcursor of the current symbol will remain. Clearly  $\Delta H_k$  is directly related to  $\Delta T_s$  and the profile of the impulse response of the channel.

Since the feedback signal passes through a train of delay stages whose delay is subject to

the effect of process spread, voltage fluctuation, and temperature variation (PVT), a timing alignment error between the incoming signal and the DFE feedback at the input of the slicer will exist. One solution for this is to clock all delay stages, as shown in Fig.2.3. This, however, might become difficult when data rate is high. Also, the delay of  $v_f$  consists of the delay of the delay stages and that of the summer. The delay of the summer is not controlled by the clock.

In [6], a variable delay block whose input is the recovered clock and whose output controls the delay stage and the operation of the summer of the DFE was used. The delay of the delay stage is adjusted in a training phase. A training sequence is used prior to the normal operation to allow the receiver to adjust the delay of the delay blocks such that the timing error between the input and the DFE feedback is minimized.

## 2.4 Error Propagation

If an erroneous decision is made by the slicer, for example, the slicer outputs a logic-0 even though it supposes to output a logic-1, the summer will subtract a weighted decision from the current symbol even though it supposes to add the weighted decision to the current symbol. Clearly the error will impact the next decision of the slicer. The error of the slicer will also propagate through the delay chain and affect the remaining DFE operations, as illustrated in Fig.2.5 where the response of a channel with 1 post-cursor is used to demonstrate the effect of the error of data slicing on the removal of the post-cursors. This error propagation characteristic of DFE is an intrinsic drawback of DFE -based channel equalization. To minimize the possibility of slicer errors, at least three approaches are at our disposal. The first is to sample the incoming signal multiple times and the correct decision is made from majority voting [35]. This approach, though effectively, might become difficult and also costly when data rate is high. Second, the error of the data slicer can also be reduced using current- integrating where the incoming signal is integrated over a capacitor and the resultant capacitor voltage is sampled at the end of integration phase [36]. Current-integration essentially forms a low-pass filter capable of filtering out spikes whose duration is much smaller as compared with UI. For disturbances with a large duration, its effectiveness diminishes. Finally, the error of the slicer can be minimized if the incoming signal is sufficiently large.

(a) No error in data slicing (b) Error in data slicing

Figure 2.5: Error in data slicing affects the removal of post-cursors.

This can be achieved by pre-amplifying the signal at the far-end of the channel prior to slicing, i.e. feed-forward equalization.

# 2.5 Calibration of Slicer

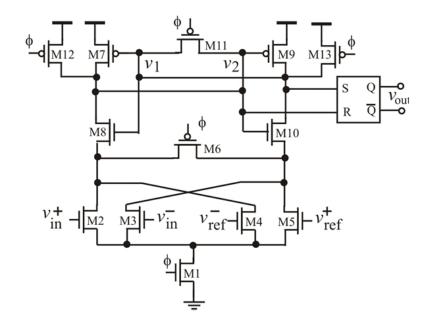

The slicer is typically implemented using a re-generative configuration where a pair of crosscoupled inverters is used for speed improvement during latching and noise rejection when latch is established, as shown in Fig.2.6 [37]. When  $\phi = 0$ , the regenerative mechanism is disabled and the input and output of the cross-coupled inverters are set to be equal, driving the operating point of the inverters to the transition region where its voltage gain is maximized. The input and reference voltage, in the mean time, are sampled by the input capacitors of the slicer. In the following phase where  $\phi = 1$ , the re-generative mechanism is activated and the voltage sampled in the previous phase is sensed by  $M_2 - M_5$ .

Figure 2.6: Clocked re-generative sense amplifier as slicer [37].

Depending upon the polarity of  $v_{in} - v_{ref}$ , the output of the slicer will be set. The regenerative mechanism ensures that the delay of the slicer is minimized. Transistor  $M_6$ ensures that when closed, the identical transistors  $M_2$  and  $M_5$  will have the same input capacitance.  $M_{11}$ , when closed, forces the cross-coupled inverters to set their operating point to the transition region where a maximum voltage gain exists. Transistors  $M_{12}$  and  $M_{13}$ , then closed, force the output of the slicer to be at logic-1.

As pointed out earlier that post-cursor elimination is critically affected by the correctness of the decision of the slicer. If the slicer makes an erroneous decision, the erroneous decision will propagate down the delay chain and affect other feedback taps. Whether the slicer will make a correct decision or not largely depends upon the threshold sensing of the input signal. Clearly a safe margin between the input and the threshold of the slicer is therefore needed in order to minimize the error of the slicer.

Since the signal at the far end of the channel is severely attenuated due to the loss of the channel, the input offset voltage of the slicer must be sufficiently small in order for the slicer to pick up the severely attenuated signal and make a correct decision. It was shown in [66], the BER of a slicer with an input offset voltage  $V_{os}$  is given by

$$BER \approx \frac{1}{2} Err\left(\frac{V_m - V_{os}}{\sqrt{\overline{V_n^2}}}\right), \qquad (2.2)$$