# ARCHITECTURE AND IMPLEMENTATION OF A HIGH FRAME-RATE STEREO VISION SYSTEM

by

Jamin Islam, B.Eng

Ryerson University, Toronto, Canada, 2006

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2008

Copyright © 2008 by Jamin Islam

PROPERTY OF

## Author's Declaration

| I hereby declare that I am the sole author of this thesis.                                      |

|-------------------------------------------------------------------------------------------------|

| I authorize Ryerson University to lend this thesis to other institutions or individuals for the |

| purpose of scholarly research.                                                                  |

|                                                                                                 |

|                                                                                                 |

| Jamin Islam                                                                                     |

| I further authorize Ryerson University to reproduce this thesis by photocopying or by other     |

| means, in total or in part, at the request of other institutions or individuals for the purpose |

| of scholarly research.                                                                          |

|                                                                                                 |

|                                                                                                 |

| Jamin Islam                                                                                     |

#### Abstract

### Architecture and Implementation of a High Frame-Rate Stereo Vision System

Jamin Islam

Master of Applied Science

Graduate Program of Electrical and Computer Engineering

Ryerson University

2008

For the purpose of autonomous satellite grasping, a high-speed, low-cost stereo vision system is required with high accuracy. This type of system must be able to detect an object and estimate its range. Hardware solutions are often chosen over software solutions, which tend to be too slow for high frame-rate applications. Designs utilizing field programmable gate arrays (FPGAs) provide flexibility and are cost effective versus solutions that provide similar performance (*i.e.*, Application Specific Integrated Circuits). This thesis presents the architecture and implementation of a high frame-rate stereo vision system based on an FPGA platform. The system acquires stereo images, performs stereo rectification and generates disparity estimates at frame-rates close to 100 fps; and on a large-enough FPGA, it can process 200 fps. The implementation presents novelties in performance and in the choice of the algorithm implemented. It achieves superior performance to existing systems that estimate scene depth. Furthermore, it demonstrates equivalent accuracy to software implementations of the dynamic programming maximum likelihood stereo correspondence algorithm.

#### Acknowledgments

There are many people that I would like to thank for making this thesis possible. First, my deepest gratitude goes out to my co-supervisors, in no particular order, W. James MacLean and Lev Kirischian. Thank you both for taking me as your student, I was lucky to have you as mentors. James, I enjoyed our weekly meetings and learning about computer vision. I am in debt to you for all the comments and advice that you had to share. Without you, this work would not be as well written as it is now. Lev, I appreciated all your efforts as our manager at the Embedded and Reconfigurable Systems Lab. Your stories and enthusiasm were extremely helpful and motivating when things didn't seem to go as they should. I hope that I am closer to becoming that ripe red tomato! I'd like to further extended my gratitude towards Professors Michael Greenspan and Vadim Geurkov.

I'd also like to thank the supporting cast of the FastTrack team: Valeri Kirischian, Peter (Pil Woo) Chun, Siraj Sabihuddin, Sergei Zhelnakov and Michael Belshaw. My experience on this project truly allowed me to learn what team-work means. This experience was great, I learned a lot from each one of you. Furthermore, I'd like to acknowledge the Ontario Centres of Excellence (CITO), MDA Space Missions, CMC Microsystems and the Department of Electrical and Computer Engineering at Ryerson University for their financial contributions with this work.

Finally, I'd like to thank my family for supporting and encouraging me to pursue this degree. This thesis is dedicated to them, especially to my dad, who gave us all a great scare with his health. There were times when I didn't know if I would be able continue, however, I'm glad that you're okay now and I hope we enjoy the many years ahead.

# Contents

| 1 | Inti | roductio | on                                         | ]  |

|---|------|----------|--------------------------------------------|----|

|   | 1.1  | Motiva   | tion                                       | 4  |

|   | 1.2  | Object   | ives                                       | 2  |

|   | 1.3  | Contril  | butions                                    | 9  |

|   | 1.4  | Thesis   | Organization                               | 4  |

| 2 | The  | eory and | d Related Works                            |    |

|   | 2.1  | Introdu  | iction                                     | į  |

|   | 2.2  | The H    | ıman Vision System                         | Ę  |

|   | 2.3  | Camera   | a Modeling                                 | .( |

|   |      | 2.3.1    | The Camera Model: Single-view Geometry     | .0 |

|   |      | 2.3.2    | Camera Calibration                         | ć  |

|   |      | 2.3.3    | The Camera Calibration Toolbox             | Ę  |

|   |      |          | 2.3.3.1 Intrinsic Parameters               | .6 |

|   |      |          | 2.3.3.2 Extrinsic Parameters               | 8  |

|   |      | 2.3.4    | The Stereo Camera Model: Two-view Geometry | 8  |

|   |      | 2.3.5    | Stereo Calibration                         | g  |

|   | 2.4  | Stereo   | Vision System                              | C  |

|   |      | 2.4.1    | Stereo Image Rectification                 | 1  |

|   |      |          | 2.4.1.1 Algorithm                          | 1  |

|   |     | 2.4.2   | The Depth Estimation Problem: Stereo Correspondence                |

|---|-----|---------|--------------------------------------------------------------------|

|   |     |         | 2.4.2.1 Stereo Issues                                              |

|   |     |         | 2.4.2.2 Dynamic Programming Maximum Likelihood Stereo Algorithm 25 |

|   | 2.5 | FPGA    | s                                                                  |

|   |     | 2.5.1   | VHDL                                                               |

|   | 2.6 | Litera  | ture Review                                                        |

|   |     | 2.6.1   | Image Rectification                                                |

|   |     | 2.6.2   | Stereo Correspondence                                              |

|   |     | 2.6.3   | Stereo Vision Systems                                              |

|   | 2.7 | Summ    | ary                                                                |

| 3 | Arc | hitectı | are and Hardware Implementation 39                                 |

|   | 3.1 | Introd  | uction                                                             |

|   | 3.2 | Overv   | iew of the System Architecture                                     |

|   | 3.3 | Archit  | ecture of Video Pre-processor                                      |

|   |     | 3.3.1   | Architecture-to-task vs. Task-to-architecture Designs 41           |

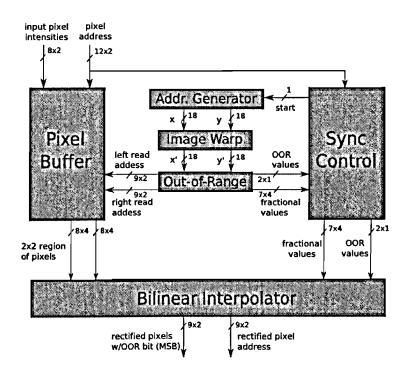

|   |     | 3.3.2   | Architecture of Image Warp Module                                  |

|   |     | 3.3.3   | Architecture of Bilinear Interpolation Module                      |

|   |     | 3.3.4   | Architecture of Pixel Buffer                                       |

|   |     | 3.3.5   | Architecture of Stereo Rectification Module                        |

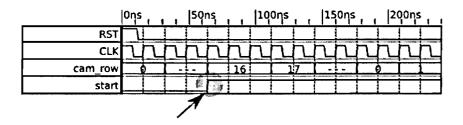

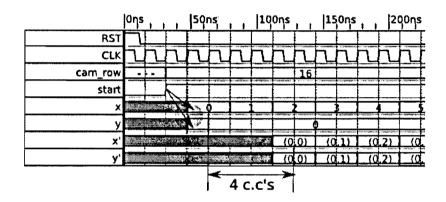

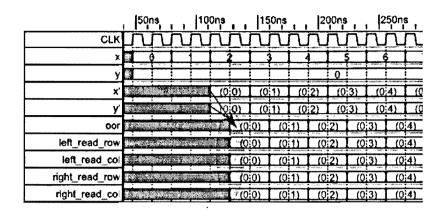

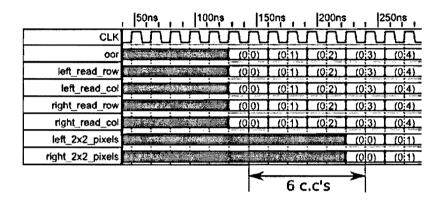

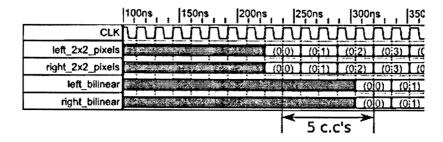

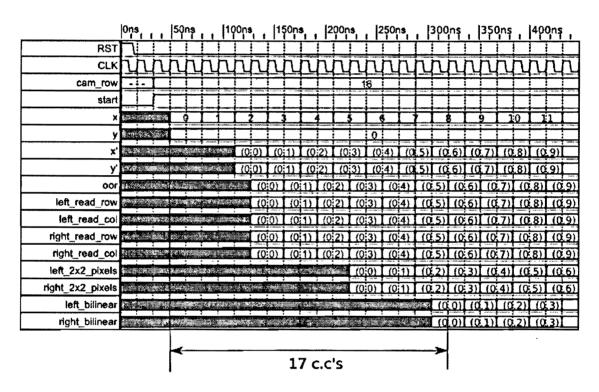

|   |     | 3.3.6   | Timing Analysis                                                    |

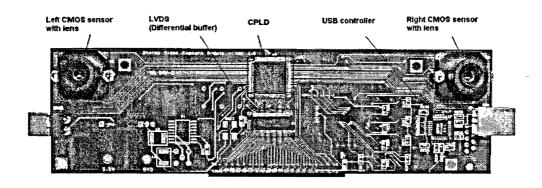

|   | 3.4 | Video-  | acquisition system                                                 |

|   |     | 3.4.1   | 30 fps Video-acquisition                                           |

|   |     | 3.4.2   | 200 fps Video-acquisition                                          |

|   | 3.5 | Amirix  | AP1100 Platform                                                    |

|   | 3.6 | System  | n Integration and Verification                                     |

|   |     | 3.6.1   | Hardware Interfacing                                               |

|   |     | 3.6.2   | Software Integration                                               |

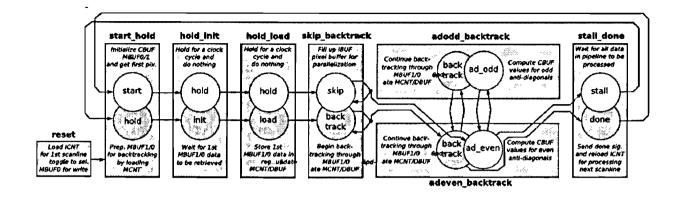

|   |     | 3.6.3  | Stereo Extraction Module Modifications                    | 71 |

|---|-----|--------|-----------------------------------------------------------|----|

|   |     |        | 3.6.3.1 Backward-pass Hardware Re-design                  | 72 |

|   |     |        | 3.6.3.2 Pipelining of the Forward-pass                    | 73 |

|   |     |        | 3.6.3.3 Interleaving the SEM                              | 73 |

|   |     |        | 3.6.3.4 Modifications to the SEM State Machine            | 74 |

|   |     |        | 3.6.3.5 Modification to PMIN Component for OOR            | 75 |

|   | 3.7 | Summ   | nary                                                      | 75 |

| 4 | Eva | luatio | n of Results                                              | 77 |

|   | 4.1 | Introd | luction                                                   | 77 |

|   | 4.2 | Stereo | Rectification Module                                      | 77 |

|   |     | 4.2.1  | Resource Utilization                                      | 78 |

|   |     | 4.2.2  | Performance                                               | 79 |

|   |     | 4.2.3  | Power Consumption                                         | 80 |

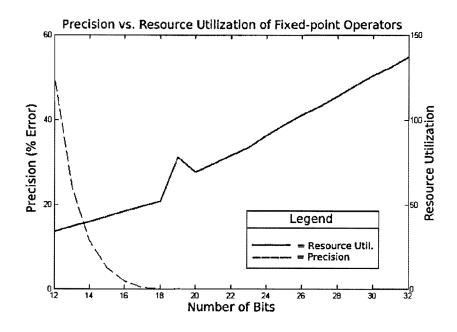

|   |     | 4.2.4  | Fixed-point Precision                                     | 81 |

|   |     | 4.2.5  | Quality: Hardware vs. Software                            | 82 |

|   | 4.3 | Stereo | Extraction Module                                         | 86 |

|   |     | 4.3.1  | Performance                                               | 87 |

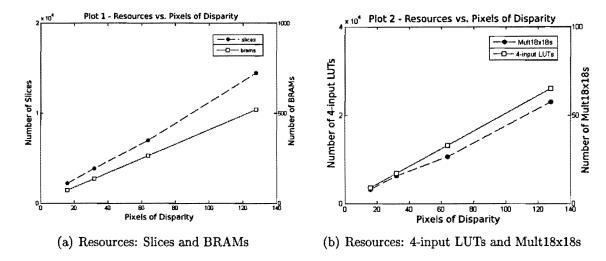

|   |     | 4.3.2  | Resource Utilization                                      | 88 |

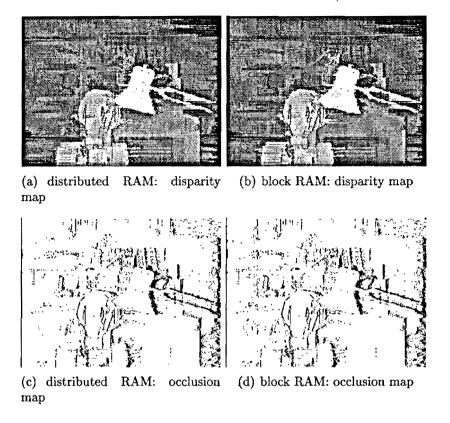

|   |     |        | 4.3.2.1 Distributed RAM vs. Block RAM Implementation      | 88 |

|   |     |        | 4.3.2.2 Interleaved Implementation                        | 89 |

|   |     | 4.3.3  | Quality: Hardware vs. Software                            | 89 |

|   |     |        | 4.3.3.1 Distributed RAM vs. Block RAM Implementation      | 90 |

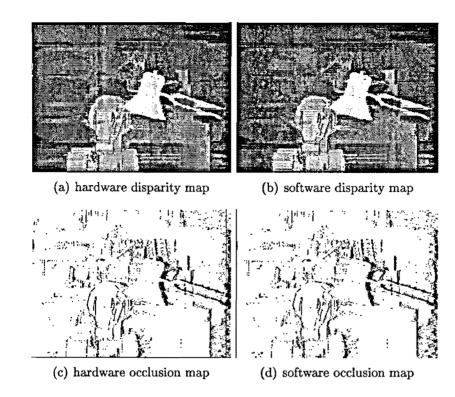

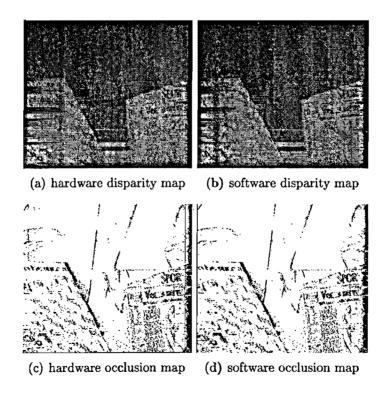

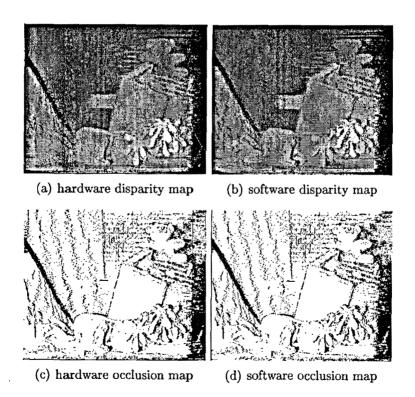

|   |     |        | 4.3.3.2 Interleaved Implementation: Hardware vs. Software | 92 |

|   | 4.4 | System | n Integration                                             | 95 |

|   | 4.5 | Summ   | ary                                                       | 97 |

| 5 | Con | clusio | n and Future Work                                         | 99 |

# List of Tables

| 2.1  | Summary of SAD-based stereo implementations                                           | <b>3</b> 4 |

|------|---------------------------------------------------------------------------------------|------------|

| 2.2  | Summary of the reported stereo vision systems                                         | 36         |

| 3.1  | 30 fps TSP coefficients for left view                                                 | 47         |

| 3.2  | 30 fps TSP coefficients for right view                                                | 48         |

| 3.3  | 200 fps TSP coefficients for the left view                                            | 50         |

| 3.4  | 200 fps TSP coefficients for the right view                                           | 50         |

| 3.5  | Testing and debugging methods                                                         | 66         |

| 4.1  | Resource utilization for the 30 fps SRM                                               | 78         |

| 4.2  | Resource utilization for the 200 fps SRM                                              | 78         |

| 4.3  | Performances of the high frame-rate SRM                                               | 80         |

| 4.4  | Power consumption of the SRM                                                          | 81         |

| 4.5  | Resources used by $x$ -bit fixed-point multipliers                                    | 82         |

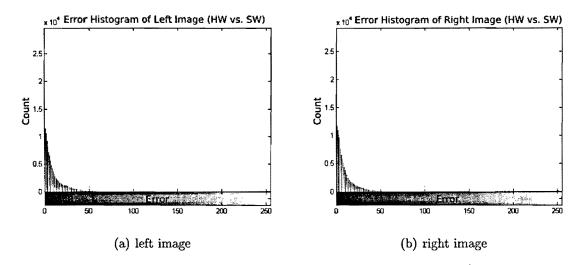

| 4.6  | RMSE of the error histograms                                                          | 86         |

| 4.7  | SEM performance with varying disparity levels on $640 \times 480$ images              | 88         |

| 4.8  | Resources utilized by the distributed and block RAM implementations (D $_{max}$       |            |

|      | = 128) of the 39 fps SEM                                                              | 89         |

| 4.9  | Interleaved SEM resource utilization for varying disparity levels on $640 \times 480$ |            |

|      | resolution images                                                                     | 90         |

| 4.10 | Accuracy of the distributed RAM and block RAM outputs                                 | 91         |

| 4.11 | Accuracy of the interleaved SEM                               | 92 |

|------|---------------------------------------------------------------|----|

| 4.12 | Resource utilization for the integrated stereo vision system  | 95 |

| 4.13 | Quality of the hardware simulation and FPGA hardware download | 97 |

# List of Figures

| 2.1  | The human eye [5]                                             | 6  |

|------|---------------------------------------------------------------|----|

| 2.2  | The visual pathway                                            | 7  |

| 2.3  | The relative position of given scene points on the retinae    | 9  |

| 2.4  | The pinhole camera model                                      | 11 |

| 2.5  | Camera calibration checkerboard images                        | 16 |

| 2.6  | Camera calibration user interface                             | 17 |

| 2.7  | A binocular (two-view) stereo camera model                    | 19 |

| 2.8  | Stereo calibration user interface                             | 20 |

| 2.9  | Flow chart of sparse and dense disparity estimations          | 24 |

| 2.10 | Ordering and uniqueness constraints                           | 26 |

| 2.11 | VHDL code for a 1-bit full-adder                              | 30 |

| 2.12 | VHDL code for a 8-bit full-adder                              | 31 |

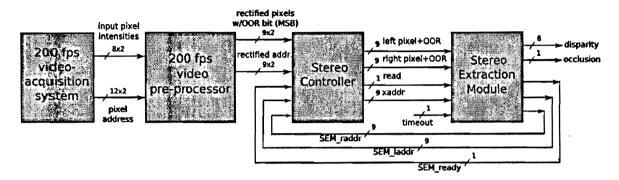

| 3.1  | Overview of the system architecture                           | 40 |

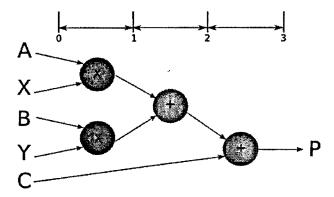

| 3.2  | Taylor Series Polynomial computation data-flow graph          | 43 |

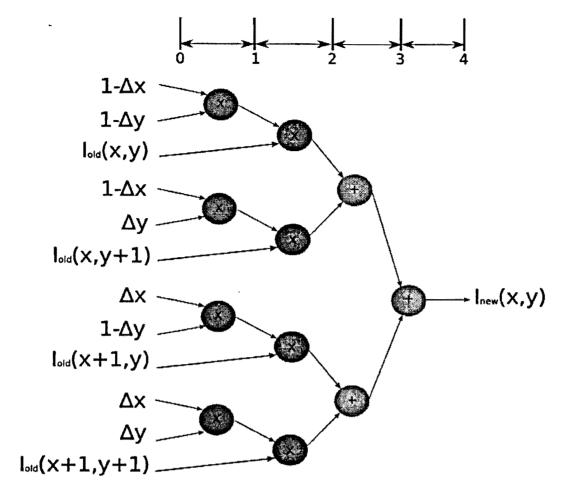

| 3.3  | Bilinear Interpolation computation data-flow graph            | 45 |

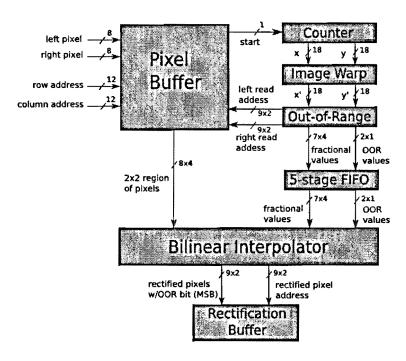

| 3.4  | 30 fps SRM block diagram                                      | 48 |

| 3.5  | 200 fps SRM block diagram                                     | 49 |

| 3.6  | Timing diagram of the start signal                            | 50 |

| 3.7  | Timing diagram of the Address Generator and Image Warp Module | 51 |

| 3.8  | Timing diagram of the Out-of-Range Module                     | 52 |

| 3.9  | Timing diagram of the Pixel Buffer                                  | 52         |

|------|---------------------------------------------------------------------|------------|

| 3.10 | Timing diagram of the Bilinear Interpolation Module                 | 53         |

| 3.11 | Timing diagram of the SRM                                           | 53         |

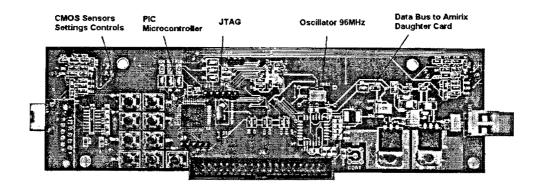

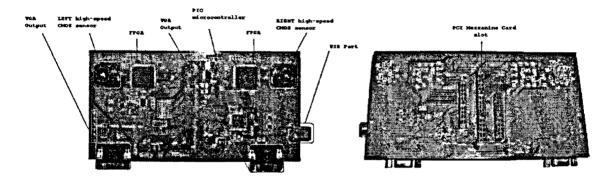

| 3.12 | 30 fps Stereo Frame Grabber (front)                                 | 54         |

| 3.13 | 30 fps Stereo Frame Grabber (back)                                  | 54         |

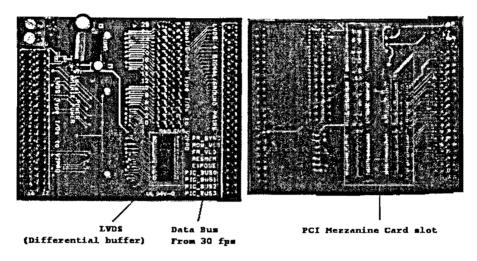

| 3.14 | Amirix Daughter Board - front & back views                          | 55         |

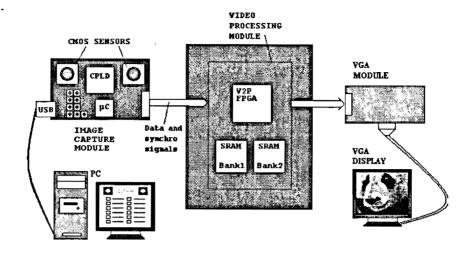

| 3.15 | Block diagram of 30 fps video-acquisition system [46]               | 57         |

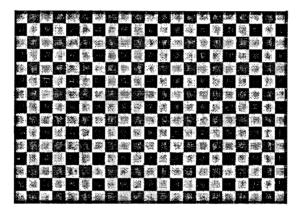

| 3.16 | Bayer pattern array                                                 | 57         |

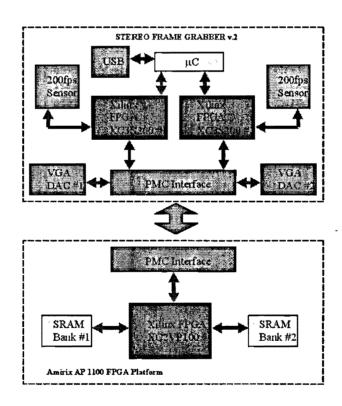

| 3.17 | Front and back views of the Stereo Frame Grabber v.2                | 59         |

| 3.18 | Amirix PCI Adapter Board                                            | 59         |

| 3.19 | Stereo Frame Grabber v.2 Block Diagram                              | 60         |

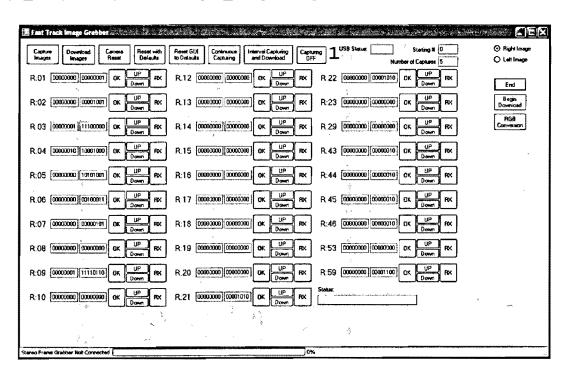

| 3.20 | Screen Capture of FastTrack Image Grabber                           | 61         |

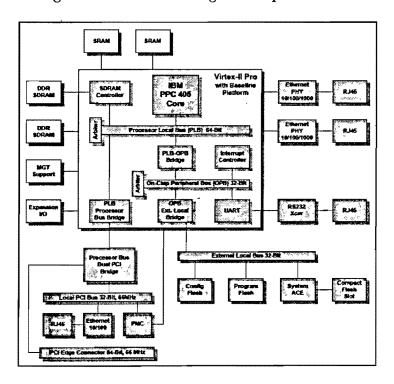

| 3.21 | Amirix AP1100 PCI Platform block diagram                            | 63         |

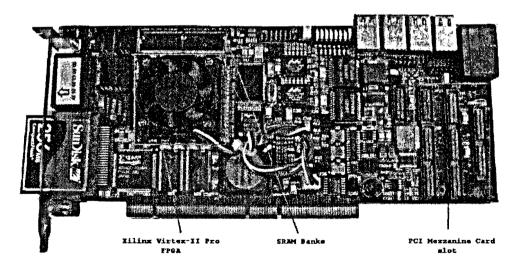

| 3.22 | Amirix AP1100 FPGA Development Board                                | 64         |

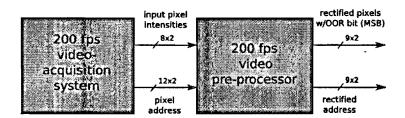

| 3.23 | Interfacing of the video-acquisition system and video pre-processor | 66         |

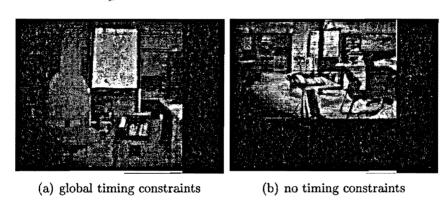

| 3.24 | Comparison of rectified right image with timing constraints         | 67         |

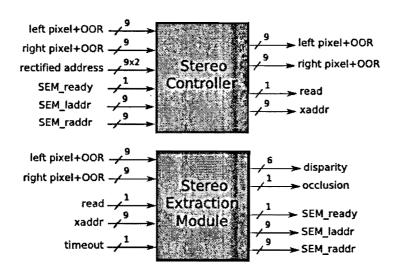

| 3.25 | Symbols of the Stereo Controller and Stereo Extraction Module       | 69         |

| 3.26 | Block diagram of integrated stereo vision system                    | <b>7</b> 0 |

| 3.27 | Hardware download of disparity meshed with the scene                | 71         |

| 3.28 | Hardware download of correct disparity information                  | 71         |

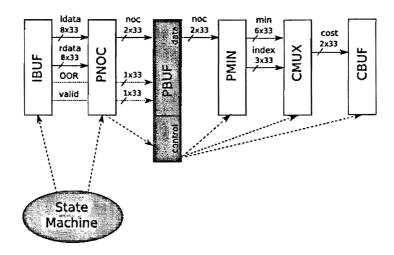

| 3.29 | Pipelined forward-pass hardware                                     | 74         |

| 3.30 | State machine of the Stereo Extraction Module                       | <b>7</b> 5 |

| 4.1  | Plot of Precision vs. Area for the fixed-point operator             | 83         |

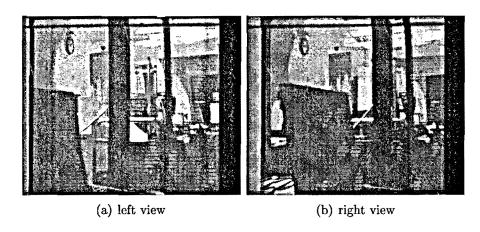

| 4.2  | 30 fps SRM outputs displayed on a VGA monitor                       | 84         |

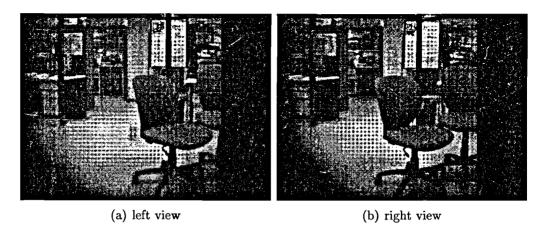

| 4.3  | Original images captured by the Stereo Frame Grabber v.2            | 85         |

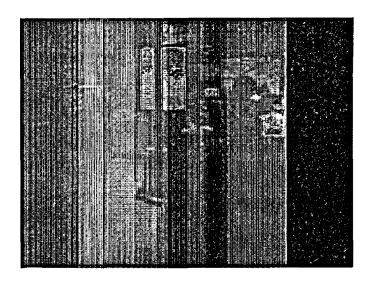

| 4.4  | Outputs of the 200 fps Stereo Rectification Module                  | 85         |

| 4.5  | Outputs generated by software                                       | 85         |

| 4.6  | Error histograms                                                      | 86  |

|------|-----------------------------------------------------------------------|-----|

| 4.7  | Plots of Resources vs. Pixels of Disparity                            | 90  |

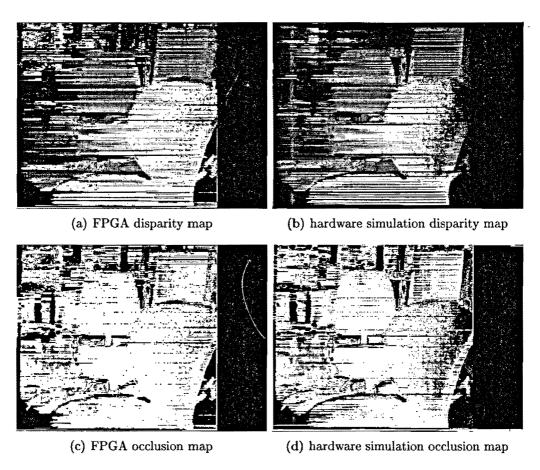

| 4.8  | Outputs of the distributed and block RAM versions of the SEM          | 92  |

| 4.9  | Tsukuba: results of the interleaved SEM, $D_{max} = 16$ pixels        | 93  |

| 4.10 | Results of the interleaved SEM, $D_{max}$ = 32 pixels                 | 93  |

| 4.11 | Results of the interleaved SEM, $D_{max} = 64$ pixels                 | 94  |

| 4.12 | Results of the interleaved SEM, $D_{max} = 128$ pixels                | 94  |

| 4.13 | Results of the integrated stereo vision system, $D_{max} = 64$ pixels | 96  |

| A.1  | Response of cells to different binocular disparities [6]              | 103 |

| A.2  | Selection of the four extreme corners of the checkerboard pattern     | 104 |

| A.3  | Extracted corners of the checkerboard pattern                         | 105 |

| A.4  | A Xilinx logic cell                                                   | 105 |

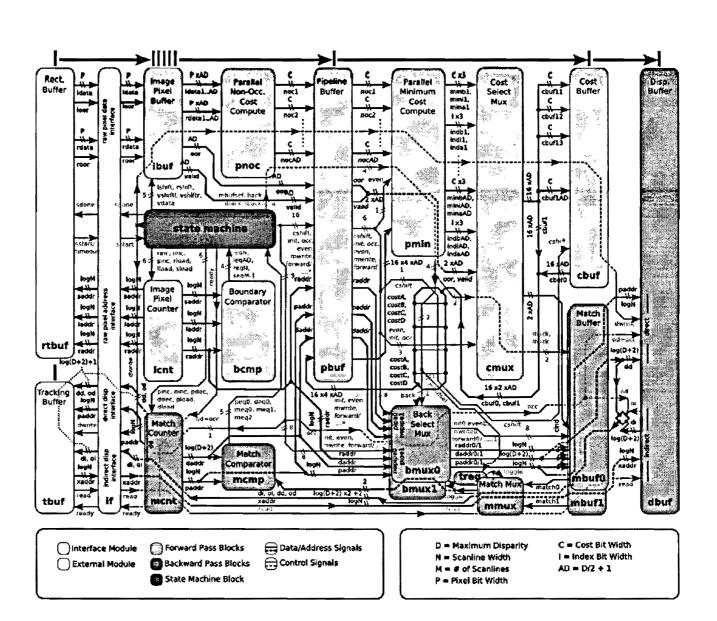

| A 5  | Schematic of the interleaved Stereo Extraction Module                 | 106 |

# Chapter 1

## Introduction

Computer vision is an important technology for autonomous space robotics. Consider the following scenarios: 1) When satellites are in orbit they face the risk of colliding with debris that can cause structural damage. It is often more economical to repair the damages that occur from these types of events, rather than to deploy brand new equipment into orbit. New emerging research allows developers to design modules that can be added to the satellites to collect more meaningful information. However, in order to perform repairs or upgrades, the satellite, much like a car being serviced on a hoist, must be linked to a base station. Due to the relative lack of humans in outer space, the satellites are required to have the base stations rendezvous and dock autonomously to them. 2) When satellites are launched in space, they are supplied with enough fuel to keep them in orbit for a number of years before the reserve depletes. When the fuel reserve does deplete, the satellites begin to move into the atmosphere where they being to corrode and become debris. This situation can be avoided, while increasing the lifetime of the device by a routine refueling process. Similar to the first scenario, the satellites are required to have the base stations, containing the fuel, rendezvous and dock autonomously to them. 3) While satellites are in orbit, preventative maintenance steps can be taken to ensure that the device does not fail (e.g., replacing the gyroscope, thrusters, etc.). Much like the first and second scenario, the satellite and base station required docking.

Each of the scenarios described above requires using a three-dimensional (3-D) computer vision system. The stereo vision system is needed to detect a target satellite from a distance, and in an arbitrary orientation, to guide the service module to the docking port of the satellite.

#### 1.1 Motivation

This thesis represents part of a project, known as FastTrack, to develop a stereo vision system to track and follow moving objects (e.g., satellites) at fast speeds, equivalent to 200 frames per second (fps). The deployment of this system is targeted for space applications, but many other applications exist. This 3-D computer vision system requires having high frame-rate image capturing to measure the motion of the satellite in very small increments, while preventing motion blur, which often occurs on frame-rate (i.e., 30 fps) capturing systems when objects are moving at high-speeds. As an example, light detection and ranging (LiDAR) technology is currently used on the Canadarm2 to guide and control spacecraft docking. This technology works well for objects in long ranges, however its accuracy is poor for shorter ranges (between zero to five metres). The system proposed in this thesis can be used to resolve the accuracy problem for short ranges.

#### 1.2 Objectives

This project has been divided among three research groups, where each group is responsible for designing a portion of the system. The research team from Ryerson University is responsible for the design and development of the high frame-rate stereo vision camera, while research teams from the University of Toronto and Queen's University are responsible for the hardware implementations of stereo correspondence and object tracking algorithms, respectively. Each portion of the system is to be designed, tested and verified on a field pro-

grammable gate array (FPGA). These FPGAs contain arrays of reconfigurable logic blocks that allow for rapid hardware prototyping at relatively low costs. Other methods, such as application specific integrated circuits (ASICs), often perform better and consume less power, but are compromised by large costs and lengthy design periods. The complete system is to be implemented on one FPGA-based platform. This requires interfacing and integrating the stereo camera and the hardware algorithms to the processing platform.

One objective of this thesis is to develop the architecture of a high frame-rate stereo image rectification module, which places corresponding points (features) on the same scanline in both images. Another objective of this work is to combine the individual portions of the system together, to form the high frame-rate stereo vision system.

#### 1.3 Contributions

In this work, we develop a 3-D vision system that achieves benchmarks that no other state-of-the-art frame-rate vision system accomplishes. This system presents novelty in its performance, as it achieves superior frame-rates (>100 fps) to existing systems that perform stereo matching in an attempt to estimate depth in the scene. Furthermore, the system is also novel in its quality as compared to other frame-rate systems, as the stereo correspondence algorithm used is globally optimal over a scanline [1], while existing frame-rate implementations use local algorithms. The best stereo matching results are obtained using graph cuts algorithms [2], however, they are extremely difficult, if not impossible, to implement efficiently on FPGAs. For example, a graph-cuts algorithm could be designed using a soft-processor on an FPGA, however, its likely that it wouldn't even approach frame-rate performances. The contributions made to this project, which are discussed in later stages of this thesis, include:

- the on-chip design of a high frame-rate stereo image rectification module,

- interfacing the video-acquisition system with the stereo image rectification module,

- assisting in hardware modifications to the stereo extraction module,

- developing the interface between the stereo image rectification module and the stereo extraction module,

- the integration of the stereo vision system on the FPGA-based platform and analysis of results.

#### 1.4 Thesis Organization

This document begins in Chapter 2 with an introduction to the human vision system, camera systems, FPGAs and a review of recent literature. Following this, Chapter 3 explores the hardware architecture and implementation of our state-of-the-art stereo vision system. The chapter describes a high-speed implementation of a stereo image rectification module. It also overviews the video-acquisition system and our processing platform. Furthermore, the chapter describes the integration of the system with an FPGA implementation of a dynamic programming maximum likelihood (DPML) stereo matching algorithm developed by Sabihuddin et al. [3]. In Chapter 4, the results obtained from the hardware implementations are evaluated. Chapter 5 concludes with possible directions for future work associated with this project.

# Chapter 2

# Theory and Related Works

#### 2.1 Introduction

This chapter contains background information for many of the concepts and ideas discussed in later chapters of this thesis. Section 2.2 explores how the brain and eyes interact to form the human vision system. Sections 2.3 and 2.4 introduce a background on camera modeling and stereo vision systems, which are used to model the human vision system. Section 2.5 briefly discusses FPGAs and VHDL. Section 2.6 presents a literature review of previous hardware implementations of image rectification, stereo correspondence and stereo vision systems. Finally, Section 2.7 summarizes the chapter's contents.

#### 2.2 The Human Vision System

This section is included in this thesis as an attempt to explain the contents in the rest of the chapter in a more meaningful way. The study of the human vision system gives us an idea of how images of the scene are captured by the eye and processed by the brain. This knowledge will allow us to use machines to implement similar functionalities. Furthermore, knowledge of how the human vision system uses the scene information to estimate depth will give us an idea of how to implement this type of functionality with a machine. This study

also gives us an idea of the complexity of performing this sort of information.

The human vision system is composed of interconnections between the brain and the eyes. The human brain is a very complex organ in nature, as humans have the ability to see, breathe, cough, sneeze, vomit, mate, swallow, urinate and think. We can also do arithmetic, speak, write, sing and compose poems. We even have the ability to play sports and play musical instruments. The brain contains approximately  $10^{12}$  cells, which is an astronomical number compared to any other organ in the body. Better evidence of the brain's complexity is seen by the number of interconnections it possesses. A typical nerve cell in the brain receives information from hundreds or thousands of other nerve cells and in turn transmits information to hundreds or thousands of other cells. The total number of interconnections in the brain should therefore be somewhere around  $10^{14}$  to  $10^{15}$  [4]. A limited amount of the brain's functionality is understood, however a good understanding about the machinery of the visual system and how the brain interprets this information exists.

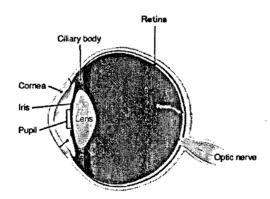

Figure 2.1: The human eye [5]

The design of our eyes allows us to have high resolution vision, as a result of the 125 million receptors in the retina. The light focuses onto these receptors, which are known as rods and cones. These receptors are nerve cells specialized to emit electrical signals when photons hit them. The task of the rest of the retina and the brain is to properly make sense of these signals and to extract information that is useful to us. An illustration of the human eye is shown in Figure 2.1. The function of the non-retinal parts of the eye is to keep a clear,

focused image of the outside world stabilized on the two retinas. The cornea and the lens together form the equivalent of the camera lens. Two-thirds of the eyes' focusing power is supplied at the air-cornea interface, while the remaining one-third is supplied by the lens. The main job of the lens is to make adjustments and focus on objects at various distances. For cameras, the focus is achieved by changing the distance between the lens and the film. We focus our eyes, not by changing the distance between the lens and the retina, but by changing the shape of the lens using cilliary muscles. The iris muscle changes the diameter of the pupil in the eye, thus it adjusts the amount of light allowed in. The blinking of the eyelids and the lubrication from the tear glands serves as a self-cleaning mechanism for the front cornea.

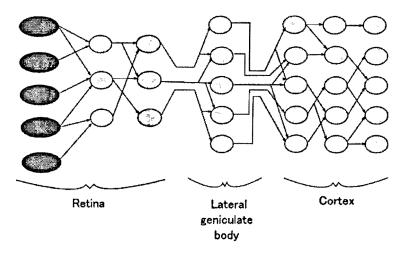

Figure 2.2: The visual pathway

The region of the brain which deals with the visual system is known as the *primary visual* cortex, or striate cortex. This part is perhaps the best understood part of the brain today, as it is known what each of its nerves are doing at most times in a person's everyday life, and what each nerve contributes to the analysis of the visual information. The primary visual cortex is a serially connected system of neurons. This visual pathway is shown in Figure 2.2. The retina of each eye consists of a plate having three layers of cells, one of which contains the light-sensitive receptor cells. The two retinae send their output to two peanut-sized nests of cells deep within the brain known as the lateral geniculate body. These structures in turn

send their fibres to the striate cortex. After being passed from layer to layer through several sets of synaptically connected cells, the information is sent to several neighbouring higher visual areas; each of these sends its output to several yet-higher cortical areas.

Stereopsis is a strategy used for judging the depth by comparing the images on our two retinas. The images cast on our retinas are two-dimensional, however we look out onto a three-dimensional world. Having a sense of how far away things are from us is important for many of the things we do in our everyday lives. We judge depth in many ways. One way is when we roughly know the size of something, such as a person, tree or cat, we can judge its distance from its apparent size in the image. Another way is if one object is partly in front of another and blocks its view, we judge the front object as closer. A powerful indicator of depth (known as perspective) occurs when the image of parallel lines, like railroad tracks, draw together as they go off into the distance. Stereopsis is perhaps the most important mechanism for assessing depth and is dependent on the use of the two eyes together. In any scene with depth our eyes receive two slightly different images. The brain compares them and estimates relative depths with great accuracy.

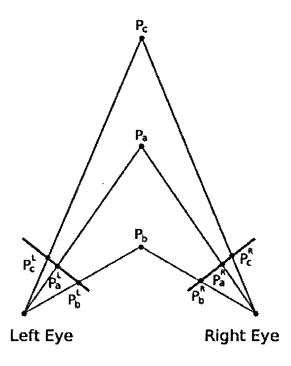

The term disparity is the computed difference in retinal position between corresponding points. When we stare at an object it is imaged on the fovea of each eye, which is responsible for high resolution vision. Scene points which are imaged on the same point of both retinae (i.e., foveae) are said to have zero disparity. Closer and more distant objects are imaged on different parts of each retina and are said to have retinal disparity. The retinal disparity can be either positive or negative. Positive disparity means that a scene point images further to the right in the right image than it does in the left image. Negative disparity means that a scene point images further to the left in the left images than it does in the right image. Objects further away from the fixated scene point are said to have a positive disparity, while closer objects are said to have a negative disparity. Figure 2.3 illustrates the relative position of given scene points on the retinae. It can be noticed at point  $P_a$ , the relative position on the retinae are equal and this represents zero disparity ( $P_a^R - P_a^L = 0$ ). The relative

position on the retinae of point  $P_b$  are less than zero and this represents a negative disparity  $(P_b^R - P_b^L < 0)$ . Furthermore, point  $P_b$  is comparatively closer than point  $P_a$ . Finally, when we look at point  $P_c$ , we notice that it is further away than

Figure 2.3: The relative position of given scene points on the retinae

\_

point  $P_a$  and accordingly has a positive disparity. The relative position of the point  $P_c$  on the retinae is greater than zero  $(P_c^R - P_c^L > 0)$ . If we extract this information about retinal disparity we then have valuable information about depth relative to where we are looking. Things with a negative disparity are closer and those with positive disparities are further away. Furthermore, the greater the disparity, the closer or further away the object will be [6].

The physiology of stereopsis uses the information presented about retinal disparity as a major cue to depth. We should therefore expect to find cells within the brain that are sensitive to retinal disparity. The first place where information from both eyes come together is in the striate cortex and it has been shown that many of these cells are sensitive to retinal disparity of the images in the two eyes [4]. Figure A.1 (see Appendix A) shows the firing rates

of four cells as a function of the retinal disparity. The first column in this figure represents the position of two objects and defines the disparity of the test area. We can see that the cell illustrated in the second column responded vigorously to small disparities (particularly, slightly negative ones) but not to large disparities. These types of cells are known as tuned excitatory. Other cells fire only to large disparities and are termed tuned inhibitory, as seen in the third column in the illustration. Some cells fired most when the test stimulus was further away from the fixation point (i.e., positive disparity) and this type of response is shown in the fourth column and is termed a far cell. There are similar cells which respond well to negative disparities, shown in the last column and are termed near cells. Please refer to the work published by Hubel in [4] for more information about the visual interaction of the brain and the eyes.

#### 2.3 Camera Modeling

In computer vision systems we must rely on cameras to capture images of the scene at hand and thus must understand the image formation process. Section 2.3.1 discusses the geometry of a single-view pinhole camera model. Section 2.3.2 describes a calibration algorithm which is used for obtaining the camera parameters mentioned in Section 2.3.1. Section 2.3.3 describes using the Camera Calibration Toolbox for Matlab which is a common tool used for obtaining the camera parameters. Section 2.3.4 discusses a stereo camera model, which is important for solving the problem of stereo correspondence (see Section 2.4.2). Finally, Section 2.3.5 discusses a special case of the Camera Calibration Toolbox for Matlab which deals with stereo calibration.

#### 2.3.1 The Camera Model: Single-view Geometry

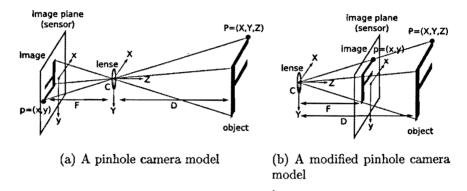

Modeling cameras is commonly done using the *pinhole camera model*. The pinhole camera requires no lens, but uses instead a very small aperture. Such cameras require excessively long

exposure times in reality, but provide a good model for perspective projection. Perspective projection is the process of transforming the three-dimensional visual information received by the camera into a two-dimensional (2-D) image. Figure 2.4a shows an illustration of the pinhole camera model. From this, it can be seen that rays of light pass through a lens and intersect with an image plane. The image plane is usually a light sensitive film, or more recently, digital image sensors. It is common to model the image plane as being in front of the lens for mathematical convenience, as shown in Figure 2.4b.

Figure 2.4: The pinhole camera model

In Figure 2.4, f represents the focal length of the camera lens, while D represents the distance of the object. The focal length and distance measurements are typically relative to the camera centre, C. The optic axis of the lens assembly is perpendicular to the image plane and passes through the camera centre. The image is then projected on to the image plane. It should be noted that the image plane is described in reference to the 2-D image coordinate system. The point of intersection of the optic axis with the image plane is called the principle point or image centre. The perspective transformation of a 3-D point,  $P = (X, Y, Z)^T$ , on to a 2-D image,  $p = (x, y)^T$  is given by Equation 2.1.

$$-\frac{f}{Z} = \frac{x}{X} = \frac{y}{Y} \tag{2.1}$$

This equation can be re-written as a set of equations in homogeneous coordinates (with  $\bar{p} = [p^T|1]^T$  and  $\bar{P} = [P^T|1]^T$ ) as shown in Equation 2.2. It should also be noted that

$\lambda = 1/Z$  in Equation 2.2.

$$\overline{p} = \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \lambda \begin{bmatrix} -f & 0 & 0 \\ 0 & -f & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \\ 1 \end{bmatrix} = \lambda K [I_3|0] \overline{P}$$

(2.2)

The pinhole camera model gives us a good starting point, however it deviates from real camera systems. The pinhole camera model assumes that the optic axis and the image plane are perfectly perpendicular in the alignment of the lens assembly. However, in reality the alignment of the lens can never be exact and the lack of perpendicularity causes skew distortions [7]. Other examples of distortions appearing from the lens assembly are scale, radial and tangential distortions. Assuming that there is no radial or tangential distortions, the pinhole camera model maps lines to lines, but does not preserve lengths, ratios or angles.

The distortions that may appear due to the lens assembly can be corrected for by using parameters that modify Equation 2.2. These parameters are modeled in Equation 2.3 and are known as the *intrinsic* parameters of the camera. The matrix  $\overline{K}$ , forms what is known as the camera calibration matrix. This includes the skew parameter, s, camera principal point  $(x_0, y_0)$  and scaling factors  $k_x$  and  $k_y$  (in millimeters). The radial distortion,  $L(\overline{r})$ , presented by the lens assembly, is a non-linear function of the radius,  $\overline{r}$ , where  $\overline{r}$  is relative to the principal point. The parameters of this distortion model are considered part of the intrinsic parameters. The tangential distortion component is omitted from the model as it is typically not a significant contributor to distortion in the resulting image.

$$\overline{p} = \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \lambda L(\overline{r}) \overline{K} [I_3|0] \overline{P} = \lambda L(\overline{r}) \begin{bmatrix} k_x f & s & x_o \\ 0 & k_y f & y_o \\ 0 & 0 & 1 \end{bmatrix} [I_3|0] \overline{P}$$

(2.3)

The 3-D point coordinates,  $P = (X, Y, Z)^T$ , are defined in terms of a camera centric-

coordinate system. It is possible to transform the camera centric-coordinate system to some world coordinate system,  $\tilde{P} = (\tilde{X}, \tilde{Y}, \tilde{Z})^T$ , by knowing the extrinsic parameters of the camera. The extrinsic parameters include a rotation, R, and a translation,  $\vec{T}$ . These allow one to perform an Euclidean transformation to align the two coordinate systems by forming the relationship seen in Equation 2.4. The extrinsic parameters are defined by the matrix  $\tau$ . The combination of the intrinsic and extrinsic parameters into a projection matrix,  $P_r$ , is shown in Equation 2.5.

$$\overline{P} = \begin{bmatrix} X \\ Y \\ Z \\ 1 \end{bmatrix} = \begin{bmatrix} R & \overrightarrow{T} \\ 0^T & 1 \end{bmatrix} \begin{bmatrix} \tilde{X} \\ \tilde{Y} \\ \tilde{Z} \\ 1 \end{bmatrix} = \tau \begin{bmatrix} \tilde{P} \\ 1 \end{bmatrix}$$

(2.4)

$$\overline{p} = \lambda L(\overline{r})\overline{K} \left[ I_3 | 0 \right] \tau \begin{bmatrix} \tilde{P} \\ 1 \end{bmatrix} = P_r \begin{bmatrix} \tilde{P} \\ 1 \end{bmatrix}$$

(2.5)

A good reference for more in-depth theory associated with camera modeling and single-view geometry can be found in work by Harley and Zisserman in [8].

#### 2.3.2 Camera Calibration

Camera calibration is the process of estimating the camera parameters of Equations 2.3 and 2.4 through simultaneous measurement of corresponding coordinate pairs  $\left\{\bar{p}_i, \tilde{P}_i\right\}_{i=1}^N$ . In order to estimate the coordinates  $\tilde{P}_i$  of 3-D scene points, camera calibration methods rely on one or more images of a calibration pattern. The calibration pattern is a 3-D object of known geometry, possibly located in a known position in space and generating images features that can be located accurately. A common calibration pattern is a checkerboard. The use of camera calibration procedures opens up the possibility of using a wide range of existing algorithms for 3-D reconstruction and recognition, all relying on the knowledge of

the camera parameters. One method we can use to retrieve the camera parameters is by estimating the projection matrix (see Section 2.3.1),  $P_r$ , without solving explicitly for the intrinsic and extrinsic parameters, assuming that  $L(\bar{r}) = 1$ . This calibration method consists of two sequential stages:

- 1. estimate the projection matrix linking the world and image coordinates

- 2. compute the camera parameters as closed-form functions of the entries of the projection matrix

Work by Hartley and Zisserman in [8], recommend "renormalizing" the observed data of both  $\tilde{P}_i$  and  $\bar{p}_i$ . For points in the world coordinate system, they recommend creating a matrix, U, such that for  $\ddot{P}_i = U\tilde{P}_i$ , then  $\frac{1}{N}\sum_i \ddot{P}_i = [0,0,0,1]^T$  and  $\sqrt{\frac{1}{N}\sum_i (\ddot{P}_{i1}^2 + \ddot{P}_{i2}^2 + \ddot{P}_{i3}^2)} = 1/\sqrt{2}$ . Similarly, for points in the camera coordinate system, they recommend creating a matrix, W, such that for  $\ddot{p}_i = W\bar{p}_i$ , then  $\frac{1}{N}\sum_i \ddot{p}_i = [0,0,1]^T$  and  $\sqrt{\frac{1}{N}\sum_i (\ddot{p}_{i1}^2 + \ddot{p}_{i2}^2)} = 1/\sqrt{2}$ . As seen in Equation 2.5, the matrix  $P_r$  is defined up to an arbitrary scale factor and therefore has only 11 independent entries, which can be determined through a homogeneous linear system formed by writing Equations 2.6 and 2.7 for at least 6 world-image point matches.

$$\bar{p}_1 = \frac{\tilde{p}_{r11}\tilde{P}_1 + \tilde{p}_{r12}\tilde{P}_2 + \tilde{p}_{r13}\tilde{P}_3 + \tilde{p}_{r14}}{\tilde{p}_{r31}\tilde{P}_1 + \tilde{p}_{r32}\tilde{P}_2 + \tilde{p}_{r33}\tilde{P}_3 + \tilde{p}_{r34}}$$

(2.6)

However, by using the calibration patterns, many more correspondences and equations can be obtained. This allows estimating using least-squares techniques.

$$\bar{p}_2 = \frac{\check{p}_{r21}\tilde{P}_1 + \check{p}_{r22}\tilde{P}_2 + \check{p}_{r23}\tilde{P}_3 + \check{p}_{r24}}{\check{p}_{r31}\tilde{P}_1 + \check{p}_{r32}\tilde{P}_2 + \check{p}_{r33}\tilde{P}_3 + \check{p}_{r34}}$$

(2.7)

If we assume that we are given N matches for the homogeneous linear system we have  $A\breve{p}_r = 0$  (see Equations 2.8 and 2.9), where  $\breve{p}_r$  is the normalized vector of the projection matrix  $P_r$ . Since A has rank 11, the vector  $\breve{p}_r$  can be recovered from singular value decomposition (SVD) techniques as the column of V corresponding to the zero (in practice the smallest) singular

value of A, with  $A = UDV^T$ . It is required to de-normalize the subsequent matrix to get  $P_r = W^{-1} \check{P}_r U$ .

$$A = \begin{bmatrix} X_1 & Y_1 & Z_1 & 1 & 0 & 0 & 0 & -x_1X_1 & -x_1Y_1 & -x_1Z_1 & -x_1 \\ 0 & 0 & 0 & X_1 & Y_1 & Z_1 & 1 & -y_1X_1 & -y_1Y_1 & -y_1Z_1 & -y_1 \\ X_2 & Y_2 & Z_2 & 1 & 0 & 0 & 0 & 0 & -x_2X_2 & -x_2Y_2 & -x_2Z_2 & -x_2 \\ 0 & 0 & 0 & X_2 & Y_2 & Z_2 & 1 & -y_2X_2 & -y_2Y_2 & -y_2Z_2 & -y_2 \\ \vdots & \vdots & \ddots & \vdots & \ddots & \vdots & \ddots & \vdots & \vdots & \vdots \\ \vdots & \ddots & \vdots & \vdots \\ X_N & Y_N & Z_N & 1 & 0 & 0 & 0 & 0 & -x_NX_N & -x_NY_N & -x_NZ_N & -x_N \\ 0 & 0 & 0 & 0 & X_N & Y_N^{\top} & Z_N & 1 & -y_NX_N & -y_NY_N & -y_NZ_N & -y_N \end{bmatrix}$$

$$(2.8)$$

$$\breve{p}_r = \begin{bmatrix} \breve{p}_{r11}, & \breve{p}_{r12}, & \dots, & \breve{p}_{r33}, & \breve{p}_{r34} \end{bmatrix}^T$$

(2.9)

With the projection matrix,  $P_r$ , recovered we can use an "RQ" decomposition on the first three columns of  $P_r$  to compute the camera parameters,  $\overline{K}$ . Here "R" is an upper-triangular matrix, representing the intrinsic parameters. It should be noted that to get proper scaling, the first two rows will have to be divided by  $\overline{K}_{33}$ . The "Q" matrix is an orthogonal matrix and represents the rotation, R.

This matrix is guaranteed to be orthogonal (within the limits of numerical precision) due to the properties of the "RQ" decomposition. Once the rotation, R, and the intrinsic parameters are known, we can easily recover the translation,  $\overrightarrow{T}$ . When  $L(\overline{r}) \neq 1$ , a further step involving non-linear optimization is required to refine parameter estimates. For further details on performing the SVD and "RQ" decomposition, please refer to [9] and [10], respectively.

#### 2.3.3 The Camera Calibration Toolbox

We utilize the Camera Calibration Toolbox for Matlab, developed by Jean-Yves Bouguet of the California Institute of Technology [11]. The toolbox provides the user with a simple yet powerful approach for tackling the camera calibration algorithm seen in Section 2.3.2. The only requirements needed for this process is that a set of calibration images are captured from the camera system. The toolbox returns the intrinsic and extrinsic parameters of the camera system to the user. The main calibration procedure is for extracting the intrinsic parameters. The design of the toolbox does not only allow the extraction of data for just one camera, it also allows calibration of binocular stereo systems. Furthermore, the toolbox allows using its calibration engine on calibration data that was previously produced using other tools. The calibration data sets include: Zhengyou Zhang [12], Heikkila [13], Bakstein and Halir [14]. The extraction of the intrinsic and extrinsic parameters is an offline process and is explained in Sections 2.3.3.1 and 2.3.3.2.

#### 2.3.3.1 Intrinsic Parameters

In order for the Camera Calibration Toolbox to extract the intrinsic parameters of the camera system, a set of calibration images are required. The computer vision community generally uses a standard checkerboard pattern for the calibration images. An example of the checkerboard pattern used is shown in Figure 2.5. Generally, a set of 10-15 calibration images are required to extract accurate values.

Figure 2.5: Camera calibration checkerboard images

The process in Matlab begins by running the Matlab script calib\_gui.m. This opens up a window which allows selecting the mode of operation. The two modes consist of Standard and Memory efficient. The Memory efficient mode is useful on older computers where CPU

resources are often low. Here, the calibration images are loaded one by one, rather than loading the full set. Regardless of which mode is chosen, a new window will appear with all the calibration options. The different options for calibration include Load, Save, Read images, Extract grid corners, Calibration, and Comp. Extrinsic, among others as seen in Figure 2.6.

| J Camera Calibration Toolbox - Standard Version 👶 🔭 🔛 🖾 🖾 🗷 |                     |                      |                    |  |  |  |

|-------------------------------------------------------------|---------------------|----------------------|--------------------|--|--|--|

| Image names                                                 | Read images         | Extract grid corners | Calibration        |  |  |  |

| Show Extrinsic                                              | Reproject on images | Analyse error        | Recomp. corners    |  |  |  |

| Add/Suppress images                                         | Save                | Load                 | Exit               |  |  |  |

| Comp. Extrinsic                                             | Undistort image     | Export calib data    | Show calib results |  |  |  |

Figure 2.6: Camera calibration user interface

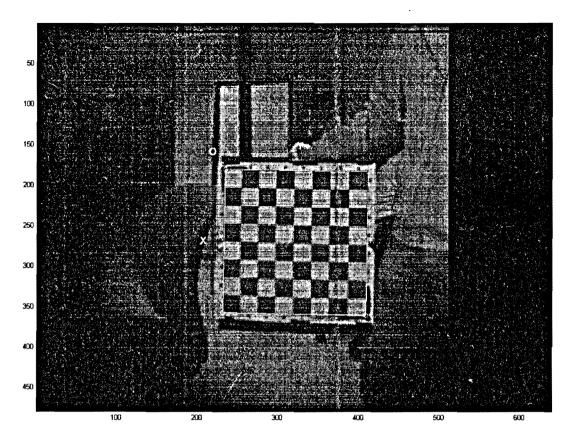

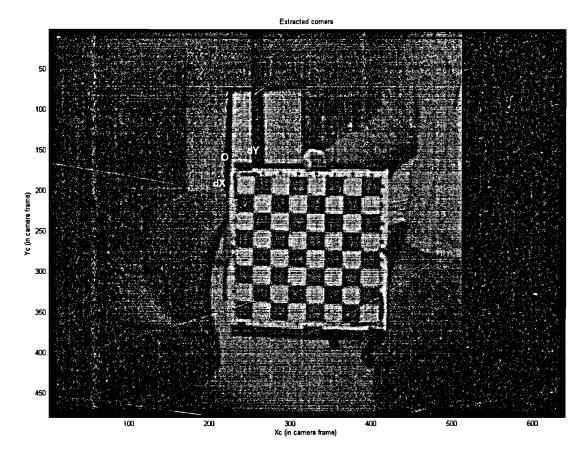

Loading the calibration images for processing purposes is achieved by selecting the Read images option. Once the set of images are known to the toolbox they can be used for determining the coefficients needed for solving the equations presented in Section 2.3.2. Solving these equations is simplified by using the  $Extract\ grid\ corners$  option. This allows the user to manually select the four outer corners of the checkerboard, enter the number of rectangles in the x and y directions, followed by the height and width of each rectangle in millimetres. An illustration of this is shown in Figure A.2 (see Appendix A), where O, represents the origin and  $\{X, Y\}$ , represent the directions of the rectangle. With this information provided, a Matlab routine automatically estimates and shows the locations of corners on the checkerboard as seen in Figure A.3 (see Appendix A), where O, represents the origin and  $\{dX, dY\}$ , represent the size of the sides of each rectangle. Some images may be effected by lens distortion produced by the camera, there is an option for entering a distortion coefficient to improve the corner extraction accuracy. These steps must be repeated for each image in the set.

The completion of the corner extraction procedure allows us to begin the main calibration step, this is started by selecting the *Calibration* option from the GUI. Calibration is done in two steps, these steps include initialization and optimization. The initialization step computes a sub-optimal linear closed-form solution (as described in Section 2.3.2) for the calibration parameters. This is followed by an optimization step which minimizes the total reprojection error over all calibration parameters by iterative gradient descent with an explicit (closed-form) computation of the Jacobian matrix [11].

#### 2.3.3.2 Extrinsic Parameters

In order for the Camera Calibration Toolbox to extract the extrinsic parameters of the camera system, one new calibration image that was not used in the main calibration procedure (of Section 2.3.3.1) is needed to provide a world coordinate system origin.

The process for extracting these values is quite similar to the main calibration procedure. To begin this procedure, the Comp. Extrinsic option must be chosen from the GUI. Then, the four extreme corners are selected by the user on the calibration image. This is then followed by entering the number of rectangles in the x and y directions. The height and width of each rectangle are also entered for an accurate estimate of the corners in the image. The toolbox then returns the computed values for the rotation and translation. In order to further utilize this information along with the intrinsic parameters, they must be saved by selecting the Save option found on the GUI. The file will be named  $< Calib\_Results.mat >$ .

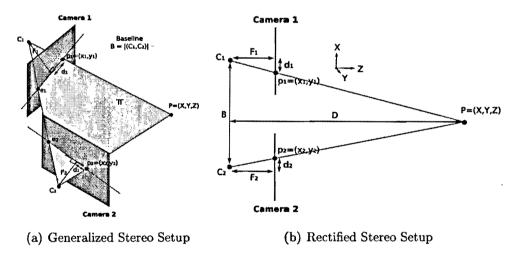

#### 2.3.4 The Stereo Camera Model: Two-view Geometry

A two-camera view of the scene presented can reduce the depth estimation to a problem of triangulation. Triangulation relies on the fact that most points in each of the two images can be identified as representing the same 3-D position. Figure 2.7a presents a binocular stereo vision camera model. Each camera is represented by the pinhole camera model. The points  $e_1$  and  $e_2$  are the epipoles of the camera model and are given by the intersection of the baseline with the image planes of each camera. The baseline, B, is the distance of separation between the principle points of the two camera (i.e.,  $B = |c_1 - c_2|$ ). A scene point,  $P = (X, Y, Z)^T$ , is projected onto each camera at points  $p_1 = (x_1, y_1)^T$  and  $p_2 = (x_2, y_2)^T$  such that they lie

on epipolar lines defined by  $(e_1, p_1)$  and  $(e_2, p_2)$ , respectively. The plane represented by these two lines is known as the epipolar plane,  $\pi$ . The epipolar plane contains the scene point and the corresponding centres of the two cameras. Given a point in one image, the epipolar line in the other image contains the matching (corresponding) point.

Being able to match point correspondences can allow us to determine the depth, Z, of a point in the scene, given two different views. The problem of stereo correspondence can be reduced to a one-dimensional (1-D) search once the epipolar lines are known. If we know the principle points of the two cameras  $(c_1 \text{ and } c_2)$  and the orientation of the image planes  $(p_1 \text{ and } p_2)$ , then knowing the location of the image of a scene point in one image completely specifies the entire epipolar line (along with the matching scene point) in the other image. This can be easily seen from Figure 2.7.

Figure 2.7: A binocular (two-view) stereo camera model

#### 2.3.5 Stereo Calibration

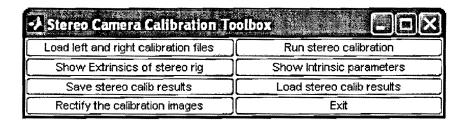

A special case of the Camera Calibration Toolbox for Matlab, discussed in Section 2.3.3, can be used to perform stereo calibration. Two-camera stereo calibration requires obtaining the left and right camera parameters. Once the camera parameters are obtained, the saved files should be re-named to Calib\_Results\_left.mat and Calib\_Results\_right.mat for each

associated view. Following this step, the stereo calibration process begins by running the Matlab script file  $stereo\_gui.m$ . The Stereo Calibration user interface is shown in Figure 2.8. Performing stereo calibration is straight forward. Once the camera parameters are loaded, an

Figure 2.8: Stereo calibration user interface

initial calibration is executed which gives a rough estimation of the stereo rig. A better, more accurate estimation of the stereo rig can be found by selecting the Run stereo calibration option on the GUI. This performs a global stereo optimization procedure which recomputes the intrinsic and extrinsic parameters for the cameras. The stereo calibration results can be saved by choosing the Save option. The file will be named < Calib\_Results\_stereo.mat >.

#### 2.4 Stereo Vision System

Having knowledge of the camera models, this section looks further into using computer vision approaches to interpreting the captured information. Section 2.4.1 introduces stereo image rectification, which is used to place points and features of two different images of the same scene on corresponding scanlines. This is done in an attempt to extract depth information from the scene in a less complex manner. Section 2.4.2 introduces stereo correspondence and a dynamic programming solution which allows machines to perform stereopsis much like we do. A brief literature review is found in Section 2.6, which discusses previous hardware implementations of image rectification, stereo correspondence and stereo vision systems.

#### 2.4.1 Stereo Image Rectification

In stereo camera geometry, matching points are constrained to lie on epipolar lines in both the left and right image. The main goal of stereo image rectification is to transform the stereo images into a camera geometry where the optic axes are parallel, so that the images of corresponding 3-D scene points will lie on the same scanline in both images, as illustrated in Figure 2.7b. Misalignments in the assembly of the stereo camera image sensors may cause slight rotations and translations between the image pairs. This may result in features that appear in both images being placed on different scanlines in the two images. The importance of performing stereo image rectification is to help reduce the complexity of stereo correspondence problem. Typically, images that are un-rectified require searching along a non-horizontal epipolar line, which is complex. The complexity arises as different epipolar lines would be needed for every point and due to image resampling, among other things. However, after performing stereo image rectification, the problem of matching corresponding points is reduced to a 1-D search.

#### 2.4.1.1 Algorithm

Assuming that the stereo camera has been calibrated and the stereo parameters are known, two homography matrices can be defined in order to transform the original images. The transformation rotates the (virtual) image planes about their optical centres and re-projects the scene on to them. This makes the epipolar lines of the image planes collinear and horizontal. Equivalently, this means that the epipoles ( $e_1$  and  $e_2$ ) are at infinity. The following steps from [7] describe how the rotation matrix,  $R_{rect}$ , can be computed assuming we know the relative translation (baseline),  $\overrightarrow{T} = c_1c_2$ , and rotation, R, of the right camera with respect to the left camera.

1. Choose:  $\overrightarrow{e_1} = \frac{\overrightarrow{T}}{\|\overrightarrow{T}\|}$  to make the epipole of the left camera perpendicular to the optic axis

- 2. Choose:  $\overrightarrow{e_2} = \overrightarrow{e_1} \times \hat{z} = \frac{[-T_y, T_x, 0]^T}{\sqrt{T_x^2 + T_y^2}}$  to make  $\overrightarrow{e_2}$  perpendicular to both  $\overrightarrow{e_1}$  and the optic axis  $(\hat{z})$

- 3. Cross-product:  $\overrightarrow{e_3} = \overrightarrow{e_1} \times \overrightarrow{e_2}$

- 4. Create the rotation matrix:  $R_{rect} = \begin{bmatrix} \overrightarrow{e_1^T} \\ \overrightarrow{e_1^T} \\ \overrightarrow{e_2^T} \\ \overrightarrow{e_3^T} \end{bmatrix}$

It should be noted that  $\overrightarrow{e_1}$  and  $\overrightarrow{e_2}$  are not the epipoles. The images are resampled via a homography, H, which is also known as a projective collineation. A homography is a  $3 \times 3$  non-singular matrix, and can be used to transform an image I to create an image I'  $(H:I\to I')$ . Remapping the points in the left image is achieved by setting the left homography  $H_L = R_{rect}$ . In a similar manner, the points in the right image are remapped by setting the right homography  $H_R = R_{rect}R^T$ . Each image location,  $\overrightarrow{x_L}$  and  $\overrightarrow{x_R}$ , in each of the left and right image is mapped to  $\overrightarrow{x_L}' = H_L \overrightarrow{x_L}$  and  $\overrightarrow{x_R}' = H_R \overrightarrow{x_R}$ . A problem here exists since  $\overrightarrow{x_L}'$  and  $\overrightarrow{x_R}'$  may not be integral pixel locations. Thus we perform an inverse map for each (integral) image location  $\overrightarrow{x_L}'$  and  $\overrightarrow{x_R}'$ , we compute  $\overrightarrow{x_L} = H_L^{-1} \overrightarrow{x_L}'$  and  $\overrightarrow{x_R} = H_R^{-1} \overrightarrow{x_R}'$ . The image data must be "normalized" if the assumption of  $x_o = y_o = 0$  is untrue. This requires  $H_L^{-1} = \overline{K}_L H_L^{-1} \overline{K}_L^{-1}$  and  $H_R^{-1} = \overline{K}_R H_R^{-1} \overline{K}_R^{-1}$ . The intrinsic parameter of each view is represented by matrix  $\overline{K}$  (see Section 2.3.1). It will typically be the case that  $\overrightarrow{x_L}$  or  $\overrightarrow{x_R}$ will not represent an integral image location. We can however, use the exact value of  $\overrightarrow{x_L}$ or  $\overrightarrow{x_R}$  to interpolate the intensity values of neighbouring pixel locations. This is achieved using various interpolation methods; we chose bilinear interpolation as it provides a simple yet accurate estimate of pixel intensities.

#### 2.4.2 The Depth Estimation Problem: Stereo Correspondence

In Figure 2.7b, the values of  $d_1$  and  $d_2$  allow the computation of the disparity,  $d = d_1 - d_2$ . The disparity of corresponding pixels is the displacement of the images of a scene point with respect to each other, measured relative to the principal points. The process of rectification allows this to be possible because the principal points of the two images are aligned to the same image coordinates. The depth, D, of a 3-D world point that corresponds to the matched feature pair can be computed using Equation 2.10, where  $f = f_1 = f_2$  (assumption of rectification) represents the focal length of the two cameras, while d, B and  $\alpha$  represent the disparity, baseline length and scale factor (pixel/mm), respectively. Often, the scale factor is set to 1 (i.e.,  $\alpha = 1$ ) if the focal length is measured in pixels. It can be noticed that the depth is inversely proportional to disparity, up to some scale factor.

$$D = \frac{f\alpha B}{d} \tag{2.10}$$

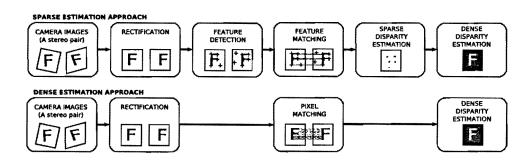

A technique used for identifying corresponding points in each of the two images from a stereo camera system is known as stereo matching. As mentioned earlier, having knowledge of point correspondences provides a means to perform triangulation. Methods used for identifying matches among pairs of points across images include similarity metrics, cost functions or even likelihood functions, to name a few. The computer vision community has studied the stereo correspondence problem extensively and many algorithms exist for determining matching points. Such algorithms are grouped into two classes: sparse and dense. Sparse methods use feature-based matching techniques, such as corners or scaleinvariant feature transform (SIFT), to identify matching points in each view of the stereo image. The disparity estimates for the matching points are used to generate sparse disparity maps. The dense method uses matching techniques which are pixel-based rather than featurebased, so the disparity values are estimated for all pixels. Matching based on a correlation window computes a correlation score between windows centred at a particular pixel (feature) in each of the two images of the stereo pair. For a given pixel (feature) in one image, the window slides over nearby coordinates in the other image to produce other correlation scores. The best scoring pixel (feature) pairs are deemed as being matched and a corresponding disparity estimate is computed from the relative shift of the windows. Figure 2.9 shows

a flow chart of sparse and dense disparity estimation methods. Equations 2.11, 2.12 and 2.13, define three commonly used cost functions that can be used for locally matching pixels or features. The Sum of Squared Difference (SSD) and Sum of Absolute Difference (SAD) functions are shown in Equations 2.11 and 2.12, where  $w_1$  and  $w_2$  are the windows containing pixels (features)  $p_1$  and  $p_2$  of camera 1 and 2, respectively. The Normalized Cross-Correlation (NCC) based function is shown in Equation 2.13. This function takes into account image statistics within a window which include the mean  $(\mu_{w_1}, \mu_{w_2})$  and standard deviation  $(\sigma_{w_1}, \sigma_{w_2})$ .

$$C_{SSD} = \sum_{\forall p_{1,2} \in w_{1,2}} \left[ I(p_1) - I(p_2) \right]^2$$

(2.11)

$$C_{SAD} = \sum_{\forall p_{1,2} \in w_{1,2}} |I(p_1) - I(p_2)|$$

(2.12)

$$C_{NCC} = \sum_{\forall p_{1,2} \in w_{1,2}} \frac{[I(p_1) - \mu_{w_1}][I(p_2) - \mu_{w_2}]}{\sigma_{w_1} \sigma_{w_2}}$$

(2.13)

Figure 2.9: Flow chart of sparse and dense disparity estimations

#### 2.4.2.1 Stereo Issues

A number of issues arise when performing stereo matching. The first issue deals with occlusions. Occluded pixels (features) are visible in the view of one camera, but not in the

other. During local stereo matching occlusions can result in an attempt to assign a depth estimate to a pixel (feature) that has no corresponding point for triangulation. The stereo correspondence algorithm used in this thesis was designed to take occlusions into account by including a penalty term in the cost function. Not all algorithms do this.

The second issue occurs as a result of thin objects. Typically the relative ordering of neighbouring scene points is assumed to be preserved in the two images. This is an assumption which is often made for stereo matching. However, an exception can be made for objects known as thin occluders. Thin occluders violate the ordering assumption mentioned previously. A good example to verify this is to consider a particular scene point which generates corresponding images points  $p_1$  and  $p_2$ , in cameras 1 and 2, as a result of perspective projection. Suppose that a narrow object, such as a pencil, is positioned near the stereo camera at a central location. The image of the pencil in camera 1 might generate an image point,  $p_1$ , to the left of  $p_1$  while generating an image point,  $p_2$ , to the right of  $p_2$  in camera 2. It can be noticed here that the ordering assumption fails, as  $p_2$  does not appear before  $p_2$  in camera 2.

Aside from the issues concerning occlusions and thin objects, some other issues effect the detection of pixels (features). These issues include differences in magnification between the two images, regions of low texture and changes in illumination across the cameras. It should be mentioned that magnification changes violate uniqueness.

#### 2.4.2.2 Dynamic Programming Maximum Likelihood Stereo Algorithm

The stereo matching process imposes the epipolar line constraint as discussed earlier. Another constraint made for the search process is to assume that all objects in the scene are thick, allowing us to assume the ordering constraint. An additional set of constraints include the uniqueness constraint and disparity range constraint. The ordering constraint says that the order of neighbouring correspondences on a particular epipolar line is always preserved. The uniqueness constraint requires that each pixel in one image only maps to at most one

pixel in the other image. Lack of a match can be used to determine occlusions. Finally, the disparity range constraint indicates that corresponding pixels in one image can be found within some limited distance in the other image. This range limit can be predicted from camera and scene geometry.

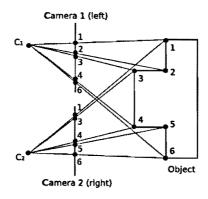

An illustration of the ordering and uniqueness constraints is shown in Figure 2.10. This graphical description demonstrates that these constraints hold true given opacity and thick scene objects. It can be seen that points on the object map appear on the left and right cameras in a unique order. The point map obtained in the view of Camera 1 shows that point 5 of the object is occluded. Similarly, for the point map of Camera 2, point 2 is found to be occluded.

Figure 2.10: Ordering and uniqueness constraints

Given that pre-rectified images are used for the extraction of depth information, a Dynamic Programming Maximum Likelihood (DPML) optimization approach can be used to estimate disparities. We use an algorithm originally developed by Cox et al. in [1]. For any optimization problem to be solvable with dynamic programming, it must include optimal substructure and overlapping subproblems. Dynamic programming solves problems by combining the solutions to subproblems. If the sub-problem solutions can be reused several times, it is said to have overlapping substructure. The optimization problem is said to have optimal substructure if each subproblem can be shown as the optimal solution within the scope of its inputs. Memoization is a technique of storing values of a function, rather

than recomputing them each time the function is called. This technique is used as a variant method for taking advantage of the overlapping subproblem property [15].

The stereo correspondence algorithm developed in [1] is for cases of dense disparity estimation. The DPML optimization approach is used to determine the Longest Common Subsequence (LCS), where the sequence is defined by the pixel intensity values. Each input scanline from either view (left or right) can be viewed as two distinct subsequences. The optimal substructure of the DMPL solution means that the disparity results generated from input scanlines are globally optimal [16]. The DPML algorithm consists of two phases which execute in sequence: a forward-pass and a backward-pass. A Matlab-like outline of the forward-pass is shown in Algorithm 1 (see Appendix B). The forward-pass begins by initializing the match matrix, MM and cost matrix, CM. Here, N represents the number of pixels per scanline. The cost matrix is initialized with constant occlusion costs, OC, given by Equation 2.14, where  $P_d$  is the probability of each camera imaging a point in the scene,  $\phi$ is the associated field of view and  $\sigma^2$  represents the variance associated with camera sensor noise. Following this, left and right image pixel streams from corresponding scanlines are compared to each other sequentially up to some maximum disparity range,  $D_{max}$ . The pixel comparisons are used to produce a cost estimate given by Equation 2.15, where  $I_L(x)$  and  $I_R(x)$  are pixel values at position x in corresponding scanlines. Cost values are generated by comparing every pixel in the left stream to every pixel in the right stream. For each cost matrix entry, an associated entry is also made to the match matrix which stores values indicating the presence of occlusions occurring between the two subsequences, or non-occlusions when a match is deemed to exist.

$$OC(P_d, \sigma^2, \phi) = \log \frac{P_d \phi}{(1 - P_d)} \sqrt{\frac{2\pi}{\sigma^2}}$$

(2.14)

$$NOC(I_L(x), I_R(x+d), \sigma) = \frac{[I_L(x) - I_R(x+d)]^2 \sigma^2}{4}$$

(2.15)

The backward-pass initiates following the storage of all cost values to the  $N \times N$  cost matrix by the forward-pass, as shown in Algorithm 2 (see Appendix B). Minimizing the cost value is accomplished by backtracking through the match matrix to reveal the lowest-cost path. The left and right pixel locations corresponding to points along the shortest path are used to compute the disparity or to indicate an occlusion [16]. It should be mentioned that dynamic programming is particularly suited to hardware implementations. For more details on this algorithm please refer to [1, 17, 16].

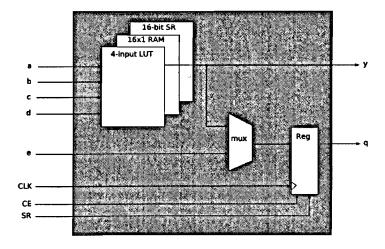

## 2.5 FPGAs

The term FPGA is an acronym for Field Programmable Gate Array. Essentially, FPGAs are digital integrated circuits (ICs) that contain configurable (programmable) blocks of logic along with configurable interconnects between them. Design engineers can configure (i.e., rewire on the fly) such devices to perform a tremendous variety of tasks. All FPGAs include three major components: I/O blocks, logic blocks and programmable routing. These components can be configured to implement basic combinational logic (e.g., AND, OR, NOT, NAND, NOR functions) or more complex synchronous logic (e.g., a microprocessor). Xilinx FPGAs contain a large quantity of sub-circuits known as Configurable Logic Blocks (CLBs), which are made up of modules known as slices. The interconnection between CLBs use long wires to transfer information. Slices consist of two logic cells and are interconnected in a more localized manner using shorter wire segments. A logic cell comprises a 4-input Look-up Table (LUT), which can also act as a 16×1 RAM or a 16-bit shift register, a 2-to-1 multiplexer and a register. A 4-input LUT can synthesize any Boolean-valued function with (up to) four Boolean inputs. Figure A.4 (see Appendix A) shows an illustration of a logic cell.

FPGAs are powerful tools for realizing custom hardware solutions. Other solutions can utilize Application Specific Integrated Circuits (ASICs), Digital Signal Processors (DSPs)

or even microprocessors. General purpose processors are often too slow due to their sequential nature of processing, while DSPs are often best-suited to applications that utilize MAC (multiply-accumulate) operations. On the other hand, ASICs often provide the best performance and power consumption. However, similar to the DSPs and microprocessors, ASICs have some drawbacks. The main problem with ASICs is the long development cycle required to get from the initial design to the final product. Another problem is in the cost of developing an ASIC: often ASIC designers spend millions of dollars for specialized equipment, which requires a high degree of expertise. Furthermore, any changes in the design can be costly and may result in time-to-market delays. The typical cost of producing a single 90 nm ASIC design ranges between \$20-30 million according to [18]. FPGAs are commonly used for rapid prototyping, as they have the advantage of quickly reprogramming the device as many times as required. This feature is useful when design flaws are found, as fixes can be made and verified quickly. Another advantage of the FPGA is that it is cost-effective when used for products of a limited quantity. When production is in large quantities, ASICs are often more cost-effective [19]. FPGAs also provide flexibility to the user, as the large array of configurable logic allows the implementation to be accelerated by duplicating (or parallelizing) functional units. Furthermore, some FPGAs include dynamic reconfiguration (or partial reconfiguration) capabilities [20]. This capability allows a portion of the configurable logic on the device to be loaded with a new design while the rest of the custom logic operates normally. A good reference for learning more on FPGAs is [20].

#### 2.5.1 VHDL

The design of digital logic circuits on FPGAs is achieved by coding in a hardware-description language such as VHDL. This name is an acronym for VHSIC Hardware Description Language, where VHSIC stands for Very High Speed Integrated Circuit. This language is used to describe the behavior and structure of digital hardware designs. Another commonly used coding language for the design of digital circuits is Verilog.

VHDL provides support for describing concurrent events, which takes advantage of the FPGA's ability to perform multiple operations concurrently. This concurrency differentiates VHDL from other high-level languages (e.g., Pascal, C and C++) which are primarily used for software design. The coding of the design allows using parameters, known as parametrization, which allows application and design specific changes to be made without having to re-code the design. Without parameters, large designs would require a significant amount of time to incorporate simple changes. Coding in VHDL also allows the behavior of complex circuits to be captured into a design system for automated synthesis or for functional simulation.

As an example, the VHDL code shown in Figure 2.11 describes a 1-bit full-adder. The design has three inputs and two outputs. The inputs consists of two addends (x and y) and a carry-in (Cin). The two outputs generated are a sum (s) and a carry-out (Cout). The code in Figure 2.11 highlights VHDL keywords in bold face. The ENTITY section of the code is essentially a black-box description of the design, as it contains and describes the inputs and

```

- 1-bit full adder designed in VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fulladd1 IS

PORT(Cin, x, y : IN STD_LOGIC;

s,Cout : OUT STD_LOGIC);

END fulladd1;

ARCHIECTURE description OF fulladd1 IS

BEGIN

s <= x XOR y XOR Cin;

Cout <= (x AND y) OR (Cin AND x) OR (Cin AND y);

END description;

```

Figure 2.11: VHDL code for a 1-bit full-adder

outputs. The ARCHITECTURE section of the code describes the internal functionality of the design, it can be seen that the outputs are assigned by a logical expression of the inputs. The code shown in Figure 2.12 describes an 8-bit full-adder. This example makes use of the '+' operator, which exploits the high-level nature of the language. A complete reference for VHDL and a guide for synthesis can be found in [21] and [22], respectively.

```

— 8-bit full adder designed in VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENITTY fulladd8 IS

PORT(x, y : IN STD_LOGIC_VECTOR(7 downto 0);

: IN STD LOGIC;

: OUT SID_LOGIC_VECTOR(7 downto 0);

Cout : OUT STD LOGIC);

END fulladd8;

ARCHIECTURE description OF fulladd8 IS

signal tmp: std_logic_vector(8 downto 0);

BEGIN

tmp \ll x + y + Cin;

SUM \le tmp(7 downto 0);

Cout \leq tmp(8);

END description;

```

Figure 2.12: VHDL code for a 8-bit full-adder

### 2.6 Literature Review

A brief overview on different hardware implementations of image rectification is given in Section 2.6.1. Similarly, previous hardware implementations of stereo correspondence algorithms are discussed in Section 2.6.2. Finally, an overview of fully integrated stereo vision systems are presented and compared in Section 2.6.3.

## 2.6.1 Image Rectification

A number of different hardware based image rectification modules were developed and reported in [23, 24, 25, 26, 27]. Most of these image rectification modules were developed on reconfigurable devices with the exception of the work produced by Courtney et al. [23], which