# HIGH EFFICIENCY HIGH POWER DENSITY ISOLATED MATRIX-TYPE RECTIFIER FOR TELECOM AND DATA CENTER APPLICATIONS

By

#### Jahangir Afsharian

B. Sc., Ryerson University, Toronto, Canada, 2005M. A. Sc., Ryerson University, Toronto, Canada, 2009

A dissertation presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2019

© Jahangir Afsharian 2019

### **AUTHOR'S DECLARATION**

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION.

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

# HIGH EFFICIENCY HIGH POWER DENSITY ISOLATED BUCK MATRIX-TYPE RECTIFIER FOR TELECOM AND DATA CENTER APPLICATIONS

Jahangir Afsharian

Doctor of Philosophy

Electrical and Computer Engineering

Ryerson University, Toronto, 2019

### **Abstract**

With the fast development of information technology (IT) industry, the demand and market volume for off-line power supplies keep increasing, especially those for telecommunication, computer servers and data centers. As the capital expenditure was measured by the square footage occupied rather than power consumption, the development of high power density converter system is of greater interesting. The rising energy prices have resulted in the cost of power and cooling exceeding the purchase cost in less than two years. Therefore, highly efficient power conversion is required for the power converter system. Generally, the power supply unit (PSU) for power distribution system (PDS) in data center and telecom are the standard two-stage approach which normally consists of power factor correction (PFC) circuit and isolated DC-DC converter. The two-stage power conversion has demonstrated excellent performance and high reliability, since the design can be optimized for each stage. However, limitations to prevent the existing two-stage PSU to fulfill future requirements for the PDS in data center and telecom applications are revealed, and a very promising and fundamentally different approach with the single-stage isolated converter is proposed in this dissertation.

The development of single-stage converters with the option of placing the energy storage outside of the PSU creates new degrees of freedom regarding e.g. simplified rectifier racks in telecom and data center. This provides tangible benefits in the form of space saving, better

airflow for power unit in rectifier racks and improved lifespan. The three-phase isolated buck matrix-type rectifier, capable of achieving high power density and high efficiency, is identified as an excellent candidate for the medium power level (5 kW~10 kW) single-stage power supply design. Nevertheless, the matrix-type rectifiers are known for their relatively complex modulation and commutation techniques, and lack of ride-through capability such as the stringent case of one phase loss operation.

This dissertation work provides comprehensive study on the commutation method and modulation scheme design for the isolated buck matrix-type rectifier. It aims to analyze the operation principle of the rectifier and propose viable modulation and commutation schemes for this rectifier under both three-phase and single-phase operation. The method is verified by the hardware experiments of the PSUs with high efficiency (> 98%) and high power density (> 70 W/in<sup>3</sup>) for 54 V and 380 VDC applications. The prototypes demonstrated in the experiments show the effectiveness of the proposed modulation and commutation schemes for industry.

Dedicated to the memory of my father and my brother.

# Acknowledgement

I would like to express my deep gratitude to my supervisor, Professor David Xu, for his support and help during my graduate studies at Ryerson University. His valuable advice and guidance has greatly enhanced my academic knowledge, scientific inspiration and practical skills.

I would also like to thank my previous supervisor Dr. Bin Wu who taught me how to conduct independent research, and for his attitude toward research and research methodologies, which can be applied to all aspects of life and will benefit me for the rest of my life.

My appreciation also goes to Dr. Dushan Boroyevich at CPES (Center for Power Electronics Systems) in Virginia Tech University, for his valuable discussion on my research topic.

I would also like to thank the committee member, respected professor Dr. Fred C. Lee, for his valuable questions, feedback, and time.

Thanks are extended to the rest of members of my thesis defense Dr. Vadim Geurkov, Dr. Amirnaser Yazdani and Dr. Bala Venkatesh.

I am grateful to fellow workers at Murata Power Solutions for their support and funding on building prototypes.

Finally, I wish to share my achievements with my family for their endless love and support.

# **Table of Contents**

| Abstract     | iii                                                                              |

|--------------|----------------------------------------------------------------------------------|

| Acknowledg   | gementvi                                                                         |

| List of Tabl | esxii                                                                            |

| List of Figu | resxiii                                                                          |

| Acronyms     | xxiii                                                                            |

| Chapter 1    | Introduction1                                                                    |

| 1.1 D        | OC Power Distribution Systems (PDS)                                              |

| 1.2 C        | Configuration PSU/Battery in Rack Level                                          |

| 1.3 T        | echnical Requirements for PSU                                                    |

| 1.4 T        | The Existing Commercialize Isolated Three-phase PSU and Proposed PSU             |

| 1.4.         | 1 Single-Phase Modules                                                           |

| 1.4.         | 2 Direct Three-Phase                                                             |

| 1.4.         | 3 Isolated DC/DC Converter in Second-Stage                                       |

| 1.4.         | 4 Proposed Single-Stage PSU for PDS in Telecom and Data center Applications . 12 |

| 1.5 T        | Opology Overview of Single-Stage Isolated Three-Phase Rectifiers                 |

| 1.5.         | 1 Boost Derived Indirect and Direct Matrix-Type Rectifiers                       |

| 1.5.         | 2 Buck Derived Indirect and Direct Matrix-Type Rectifiers                        |

| 1.6 D        | Dissertation Objectives                                                          |

| 1.7 D        | Dissertation Outline                                                             |

| Chapter 2 Comparative Evaluation PWM and Commutation Schemes for ZVS Isolated Buck Matrix-Type Rectifier  |

|-----------------------------------------------------------------------------------------------------------|

| 2.1 Space Vector Modulation for Buck Matrix-Type Rectifier                                                |

| 2.2 Several Practical PWM Schemes for Three-Phase Isolated Buck Matrix-Type                               |

| Rectifier                                                                                                 |

| 2.3 An Optimal PWM Scheme Candidate for MOSFET Devices                                                    |

| 2.4 Principle Operation of Rectifier with "Type A"PWM Scheme                                              |

| 2.5 Analysis of ZVS Transition and Commutation Method for "Type A" PWM Scheme                             |

| 2.6 Steady-State Analysis of "Type A" and Performance Comparison with "Type E" 42                         |

| 2.6.1 Analysis of Duty-Cycle Loss                                                                         |

| 2.6.2 Analysis of Output Inductor Current Ripple                                                          |

| 2.6.3 Analysis of Switching Loss                                                                          |

| 2.7 Experimental Verification                                                                             |

| 2.7.1 Experimental Waveforms for Duty-cycle Loss and Output Inductor Current Ripple                       |

| 2.7.2 Converter MOSFET Switching Dynamics Behavior with "Type A"PWM 52                                    |

| 2.7.3 Verification of Input current THD54                                                                 |

| 2.8 Conclusions 55                                                                                        |

| Chapter 3 Improved "Type E" PWM and Efficiency and Power Density Evaluation for 380 V and 54 V Prototypes |

| 3.1 Improved "Type E" PWM                                                                                 |

| 3.1.1 Full ZVS Turn-ON for Devices with Proposed Commutation Scheme                                       |

| 3.1.2 Reduced Output Inductor Current Ripple with the Proposed Optimized Zero-                            |

| Vector Dwell Times                                                                                        |

| 3.1.3 Simulation and Experimental Verification for Imporved "Type E"                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 Loss Breakdown and Efficiency Comparisons for 380 V and 54 V Prototypes 69                                                              |

| 3.2.1 Conduction Losses on Semiconductors                                                                                                   |

| 3.2.2 Analsis of Switching Loss of the Bidirectional Devices in Isolated Buck Matrix-<br>Type Rectifier with "Tpe A" and Imporoved "Type E" |

| 3.2.3 Analsis of Switching Loss on the Secondary Side of the Rectifier with "Type A" and Imporoved "Type E"                                 |

| 3.2.4 Loss Breakdown and Efficiency Comparisons for "Type A" and Improved "Type E" on SiC-Based 380 V Prototype                             |

| 3.2.5 Comparative Efficiency and Power Density Evaluation of Si IGBT-Based and SiC MOSFET-Based 380 V Prototypes                            |

| 3.2.6 Analysis of Loss Breakdown and Efficiency for SiC MOSFET-Based 54 V                                                                   |

| Prototype                                                                                                                                   |

| Prototype                                                                                                                                   |

| 3.3 Conclusions                                                                                                                             |

|                                                                   | Commutation Scheme for One-Phase Loss to Three-Phase Operation with "Type                                                                                              |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A''                                                               |                                                                                                                                                                        |

|                                                                   | Commutation Scheme for One-Phase Loss to Three-Phase Operation with 1 "Type E"                                                                                         |

| 4.4 Sir                                                           | nulation Results                                                                                                                                                       |

| 4.4.1                                                             | Discussion of Output Voltage Regulation during One Phase Loss Operation with                                                                                           |

| Different                                                         | $m_a$                                                                                                                                                                  |

| 4.5 Ex                                                            | perimental Verification                                                                                                                                                |

| 4.5.1                                                             | Experimental Waveforms for One Phase Loss Operation with "Type A" 123                                                                                                  |

|                                                                   | Converter MOSFET Switching Dynamics Behavior during One Phase Loss                                                                                                     |

| Operation                                                         | 1                                                                                                                                                                      |

| 4.5.3                                                             | Experimental Verification for One Phase Loss Operation with Improved "Type E"                                                                                          |

| 4.6 Co                                                            | nclusions                                                                                                                                                              |

|                                                                   |                                                                                                                                                                        |

| Chapter 5                                                         | Isolated Buck Matrix-Type Rectifier with Integrated Boost Output Stage 130                                                                                             |

| _                                                                 | Isolated Buck Matrix-Type Rectifier with Integrated Boost Output Stage 130 alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131          |

| 5.1 An<br>5.1.1                                                   | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One             |

| 5.1 An<br>5.1.1                                                   | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131                                                                                     |

| 5.1 An<br>5.1.1<br>Phase Op<br>5.1.2                              | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One bened Fault |

| 5.1 An<br>5.1.1<br>Phase Op<br>5.1.2                              | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One pened Fault |

| 5.1 An<br>5.1.1<br>Phase Op<br>5.1.2<br>Phase Op<br>5.1.3         | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One bened Fault |

| 5.1 An 5.1.1 Phase Op 5.1.2 Phase Op 5.1.3 Phase Sh               | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One bened Fault |

| 5.1 An 5.1.1 Phase Op 5.1.2 Phase Op 5.1.3 Phase Sh 5.2 Sin       | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One bened Fault |

| 5.1 An 5.1.1 Phase Op 5.1.2 Phase Op 5.1.3 Phase Sh 5.2 Sin 5.2.1 | alysis of Operation of the Rectifier during One Phase Loss (opened or shorted) 131  Analysis Of Operation to Achieve Miminum Ouput Voltage Drop during One bened Fault |

| 5.3 Expe    | rimental Verification                                                       | 150      |

|-------------|-----------------------------------------------------------------------------|----------|

| 5.3.1 E     | experimental Verification to Achieve Minimum Output Voltage Drop            | in One   |

| Phase Open  | ned Operation                                                               | 150      |

| 5.3.2 E     | experimental Verification to Achieve Minimum Input Current THD in O         | ne Phase |

| Loss Opera  | tion                                                                        | 152      |

|             | Experimental Verification to Achieve Tight Ouput Voltage Regulation Shorted | J        |

| 5.4 Conc    | lusions                                                                     | 155      |

| Chapter 6 C | Conclusions                                                                 | 157      |

| 6.1 Main    | Contributions and Conclusions                                               | 157      |

| 6.2 Sugg    | ested Future Works                                                          | 159      |

| Appendix A  | Detailed ZVS Operation of "Type A" at Different Load Conditions             | 161      |

| Appendix B  | ZVS Range for Six-Segment and Eight-Segment PWM Schemes                     | 167      |

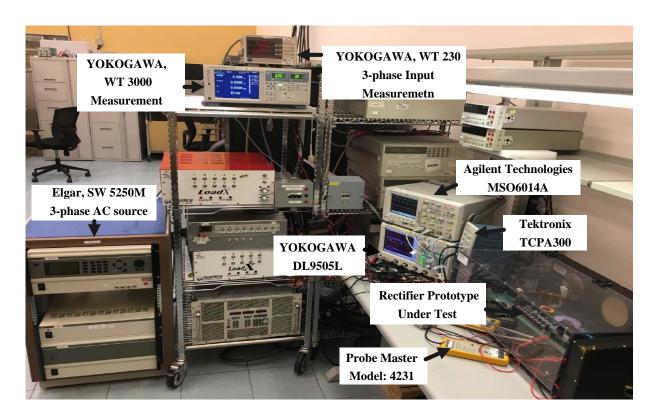

| Appendix C  | Test-Setup for Experimental Verification                                    | 169      |

| References  |                                                                             | 170      |

# **List of Tables**

| Table 2-1 | Constraints of SR Operation                                                              |

|-----------|------------------------------------------------------------------------------------------|

| Table 2-2 | Comparison of Normalized Total Duty-Cycle Losses                                         |

| Table 2-3 | Switching Loss Comparison of "Type A" and "Type E" PWM Under ZVS Operation 49            |

| Table 2-4 | Experimental Prototype parameters                                                        |

| Table 3-1 | Summary of the turn-ON and turn-OFF loss calculation for "Type A" and improved "Type E". |

|           | 72                                                                                       |

| Table 3-2 | Experimental prototype parameters for 380 V output                                       |

| Table 3-3 | Experimental prototype parameters for 54 V output                                        |

# **List of Figures**

| Fig. 1-1 Block diagram of the two-stage power supply (PSU).                                    | 2          |

|------------------------------------------------------------------------------------------------|------------|

| Fig. 1-2 Block diagrams of power distribution systems for data center and telecom [1]          | 3          |

| Fig. 1-3 Various configuration of battery backup system in 48 V and 380 V power distribution   | n system   |

| (note: PDU is not drawn and VR (Buck DC-DC converter) is redrawn as part of PSU for simplici   | ty)5       |

| Fig. 1-4 Input power quality.                                                                  | 7          |

| Fig. 1-5 Output voltage requirement.                                                           | 7          |

| Fig. 1-6 Hold-up time voltage waveforms.                                                       | 7          |

| Fig. 1-7 Various configuration of PSUs with estimated power density in cubic block for data co | enter and  |

| telecom applications: (a) single-phase module (bridgeless PFC + LLC) (b) direct three-phase    | (Vienna    |

| rectifier + LLC) (c) proposed single-stage PSU (isolated buck matrix-type rectifier)           | 9          |

| Fig. 1-8 Three-Phase high-frequency isolated matrix-type rectifier                             | 13         |

| Fig. 1-9 An example of proposed PSU in configuration with separated battery charger and diode  | in 380V    |

| DC PDS                                                                                         | 13         |

| Fig. 1-10 Basic structures of isolated matrix-type three-phase rectifiers.                     | 17         |

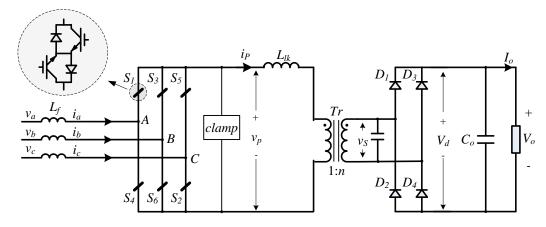

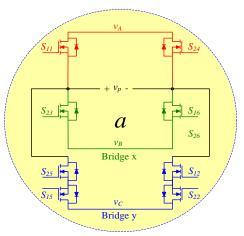

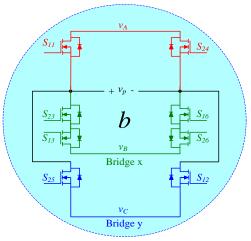

| Fig. 2-1 ZVS three-phase isolated buck matrix-type rectifier                                   | 26         |

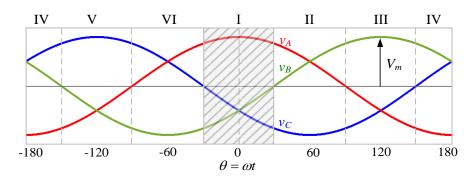

| Fig. 2-2 Input phase voltages.                                                                 | 26         |

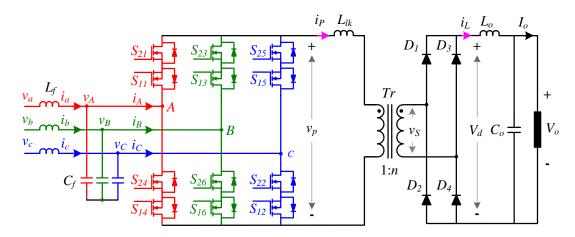

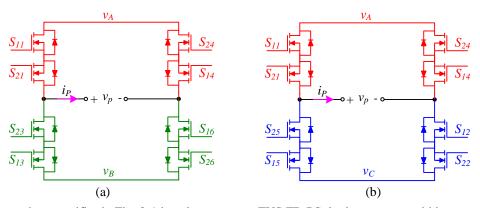

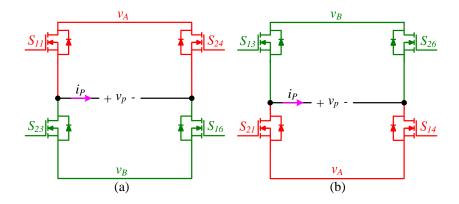

| Fig. 2-3 Three-phase rectifier in Fig. 2-1 is redrawn as two ZVS FB-PS dc-dc converter within  | n sector I |

| operation with "leg A" as a common leg of (a) "bridge x" and (b) "bridge v"                    | 27         |

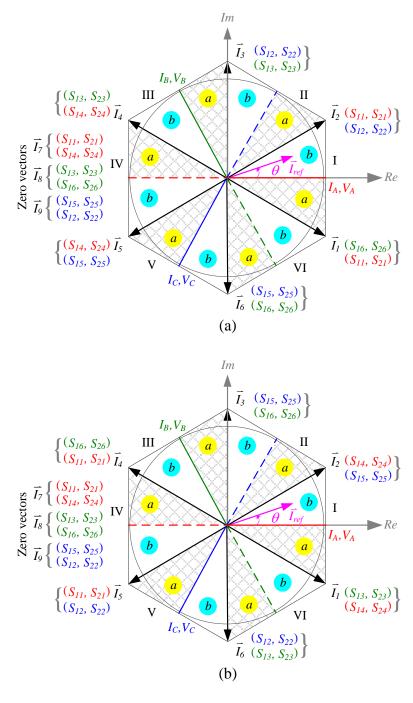

| Fig. 2-4 Current Space vector representation. (a) $I_P = nI_L$ , $V_P > 0$ and (b) $I_P = -nI_L$ , $V_P < 0$                 |

|------------------------------------------------------------------------------------------------------------------------------|

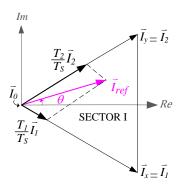

| Fig. 2-5 Synthesis of $\vec{I}_{ref}$ by $\vec{I}_1, \vec{I}_2$ and, $\vec{I}_0$                                             |

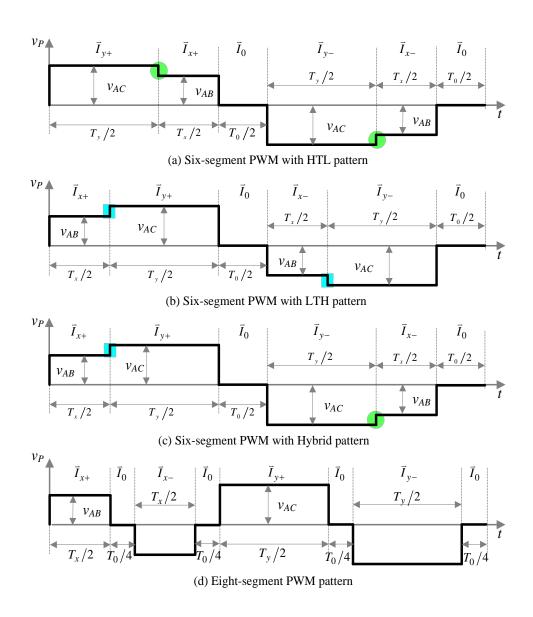

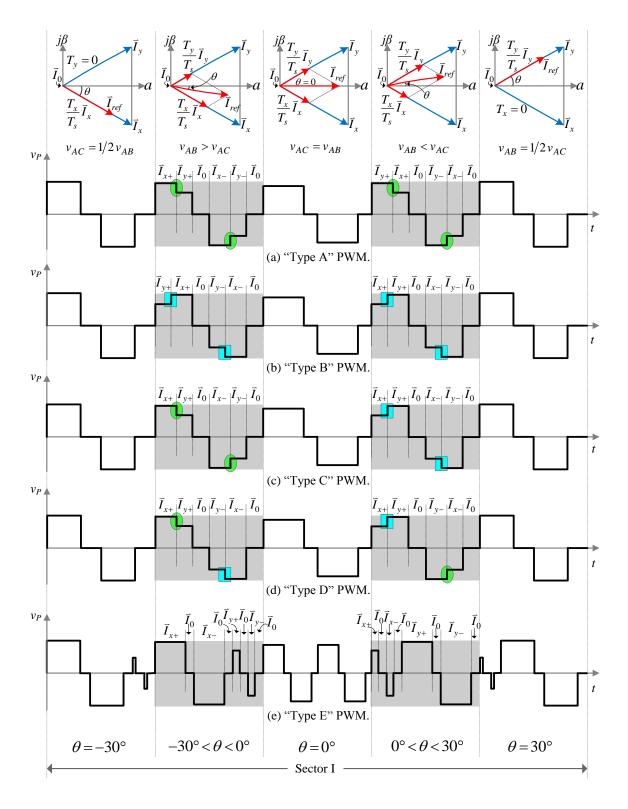

| Fig. 2-6 The transformer primary voltage within a switching cycle with different switching patterns when                     |

| $\vec{I}_{ref}$ is located in $0^{\circ} < \theta < 30^{\circ}$                                                              |

| Fig. 2-7 Transformer primary voltage with different PWM schemes when $\bar{I}_{ref}$ is moving within sector I.              |

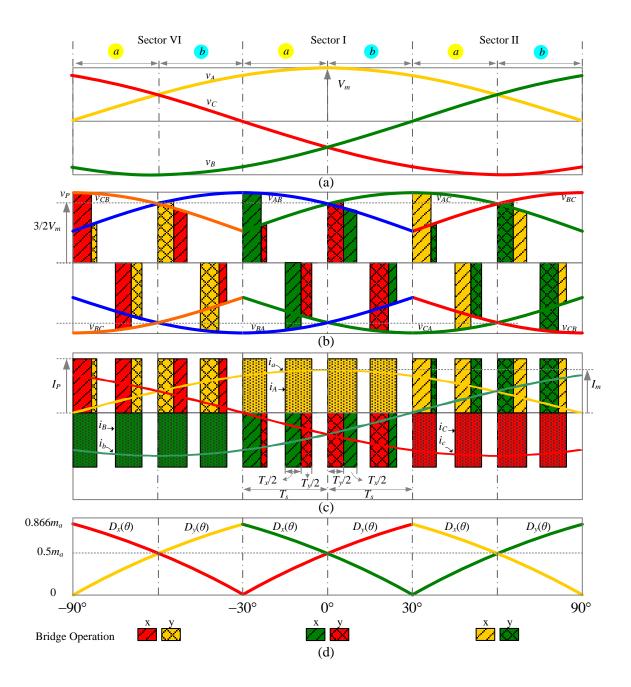

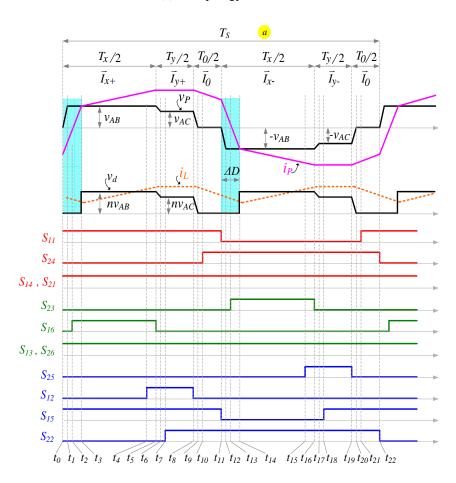

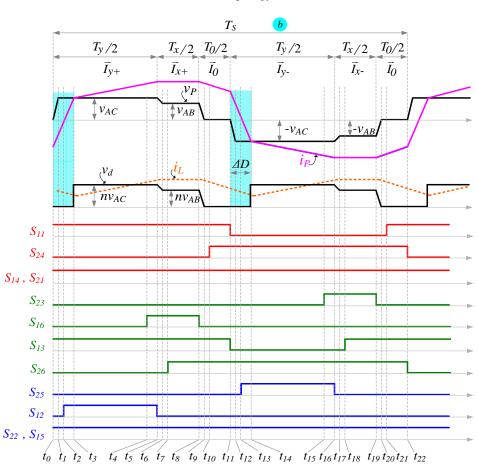

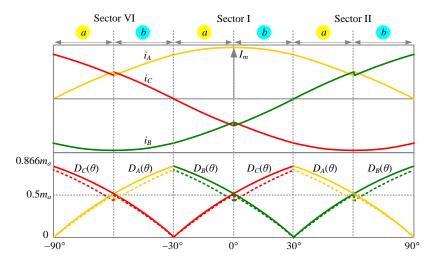

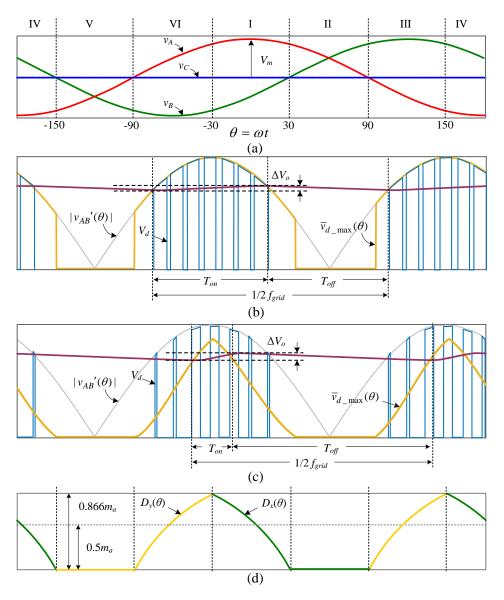

| Fig. 2-8 Waveforms of "Type A" PWM with excessively increased switching period $T_s$ : (a) phase                             |

| voltages, (b) primary voltage, and (c) phase currents $i_A$ , $i_B$ and $i_C$ (d) $D_x(\theta)$ duty-cycle of "bridge x" and |

| $D_{y}(\theta)$ duty-cycle of "bridge y"                                                                                     |

| Fig. 2-9 Sector I (a) when $\theta \in [-\pi/6,0]$ $v_{AB} > v_{AC}$ :                                                       |

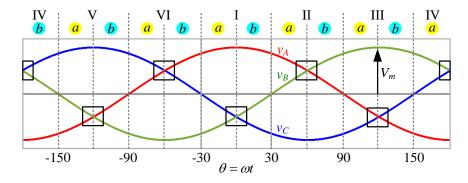

| Fig. 2-10 Sector I (b) when $\theta \in [0, \pi/6]$ $v_{AC} > v_{AB}$ :                                                      |

| Fig. 2-11 Input phase voltages with sector division. In the vicinity of each bundary between part a and                      |

| part b (inside the retangular box), two phase voltages are very close and contraints of the SR switches                      |

| associated with both these two phases need to be applied                                                                     |

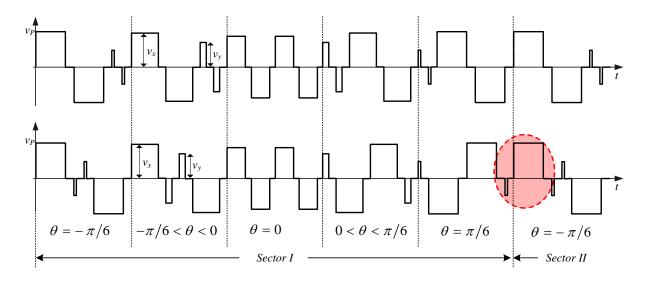

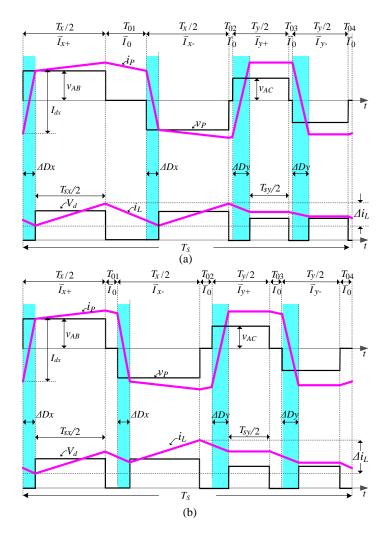

| Fig. 2-12 Waveforms of the steady state operation in sector I (a)                                                            |

| Fig. 2-13 Distorted input phase current waveforms without duty-cycle compensation (solid line: applied                       |

| duty-cycle; dashed line: effective duty-cycle)                                                                               |

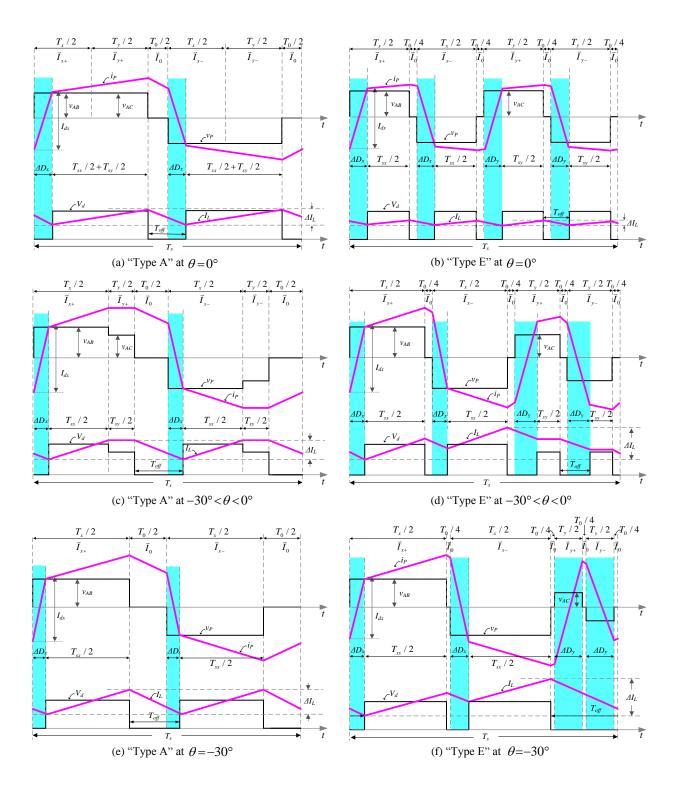

| Fig. 2-14 Comparison waveforms of the duty-cycle loss and the output inductor current ripple for "Type A" and "Type E" PWM   |

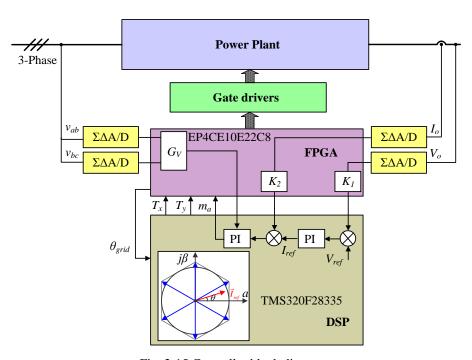

| Fig. 2-15 Controller block diagram                                                                                           |

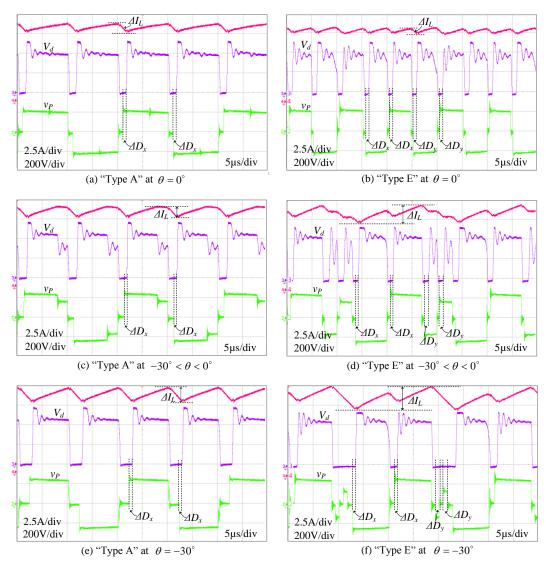

| Fig. 2-16 Experimental waveforms of the transformer primary voltage $v_P$ , rectifier voltage $v_d$ and                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| inductor current ripple $\Delta I_L$                                                                                                      |

| Fig. 2-17 Experimental waveforms for rectifier MOSFETs switching behavior with "Type A" PWM                                               |

| implementation                                                                                                                            |

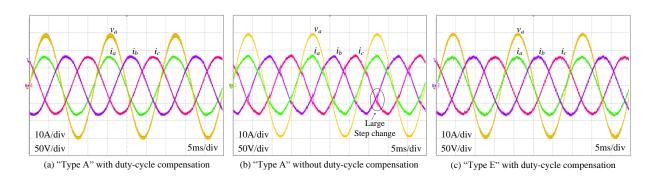

| Fig. 2-18 Waveforms of grid voltage $v_a$ and currents $i_a$ , $i_b$ and $i_c$ at the rated power                                         |

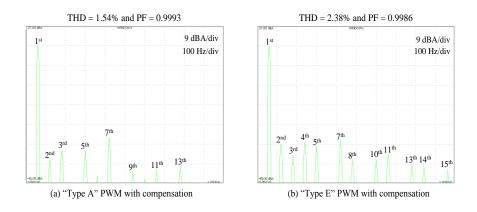

| Fig. 2-19 Experimental spectrums of Input phase current                                                                                   |

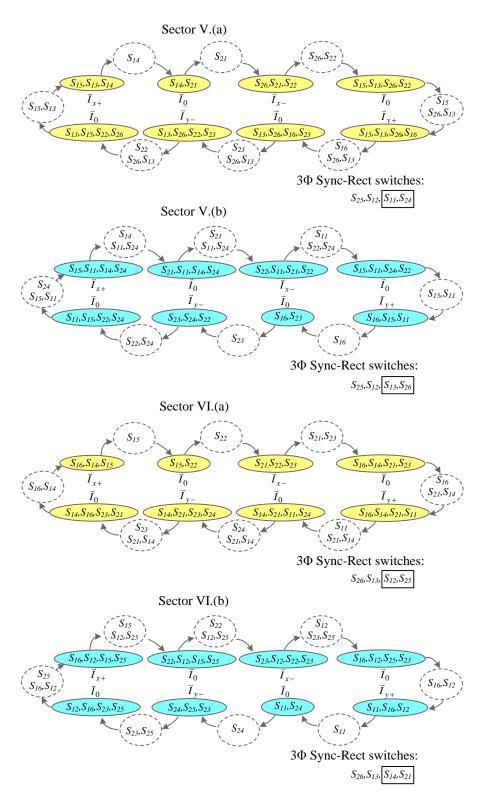

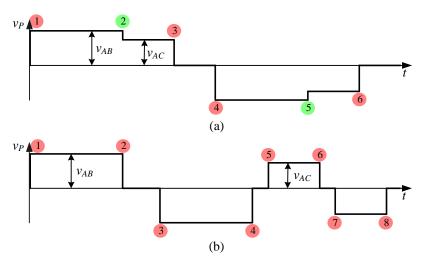

| Fig. 3-1 Transformer primary voltage waveform with Eight-segment PWM scheme: (a) desireable PWM                                           |

| pattern (b) traditionl PWM pattern                                                                                                        |

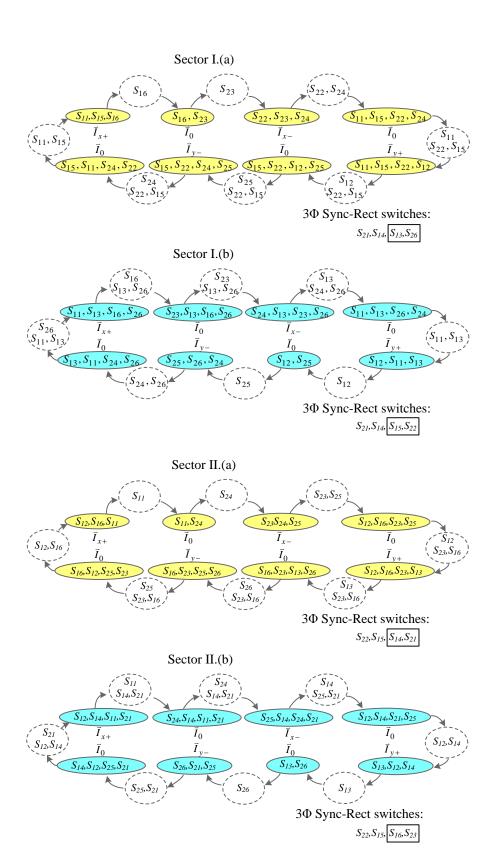

| Fig. 3-2 Finite commutation state-machine in all sectors for improved "Type E" PWM (Not: all the                                          |

| primary MOSFET switches are turned ON under ZVS with the proposed commutation method) 62                                                  |

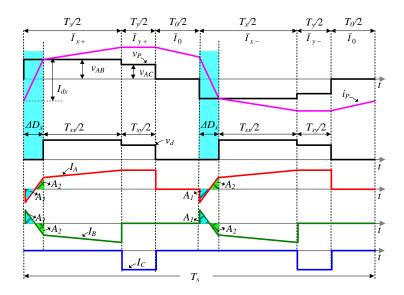

| Fig. 3-3 Envelope of output inductor current ripple, $i_L$ of the isolated buck matrix-type rectifier with: (a)                           |

| improved "Type E" PWM and (b) "Type E" PWM                                                                                                |

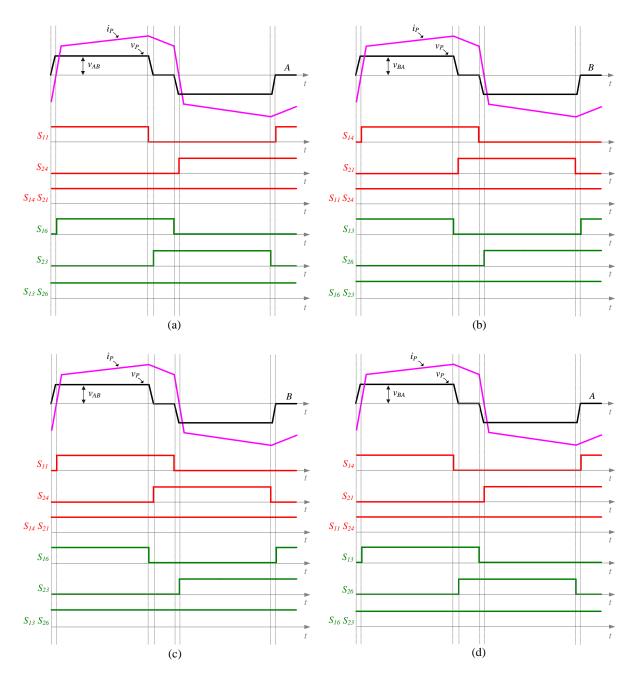

| Fig. 3-4 Zoom-in waveforms of the primary side voltage $v_P$ , primary side current $i_P$ , output bridge diode                           |

| rectifier $V_d$ and outtut inductor current $i_L$ of the isolated buck matrix-type rectifier with (a) improved                            |

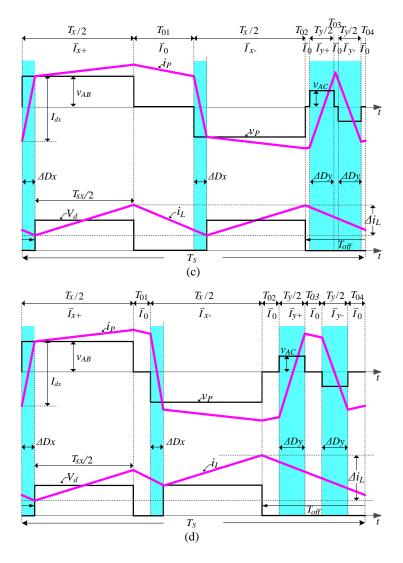

| "Type E" PWM, (b) "Type E" PWM, (c) improved "Type E" PWM and (d) "Type E" PWM66                                                          |

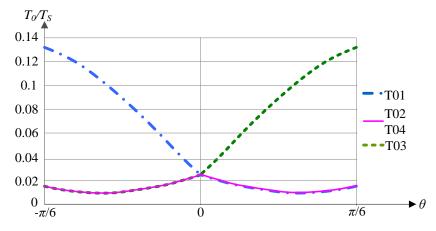

| Fig. 3-5 Four zero-vector intervals of the improved "Type E" PWM (condition: $m_a = 0.8$ and $\Delta D_{total}(\theta) =$                 |

| $\Delta D_{total}(0) = 0.1)67$                                                                                                            |

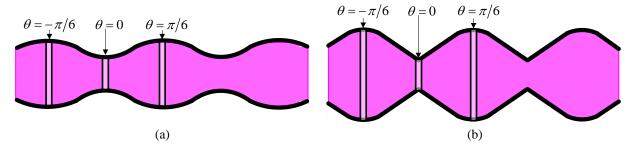

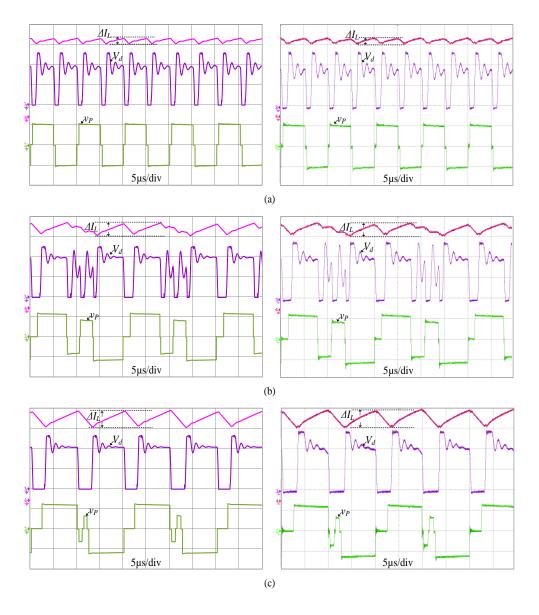

| Fig. 3-6 Simulated waveforms (left) and experimental waveforms (right) of the transformer primary                                         |

| voltage $v_P$ , rectifier voltage $V_d$ and inductor current ripple $\Delta I_L$ with implementation of improved "Type E"                 |

| PWM: (a) at $\theta = 0^{\circ}$ , (b) $-\pi/6 < \theta < 0$ and (c) at $\theta = -\pi/6$ . (Ch2 = 200 V/div, Ch3 = 200 V/div, Ch4 = 2.5) |

| A/div)                                                                                                                                    |

| Fig. 3-7 Switching events for (a) "Type A" and (b) improved "Type E"                                                                      |

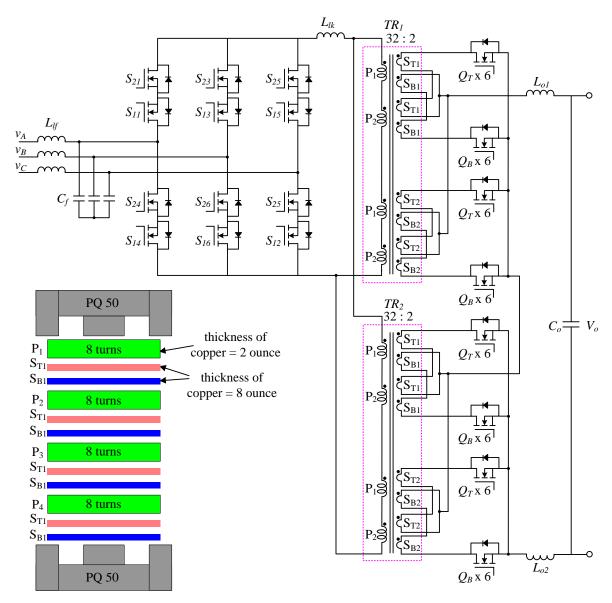

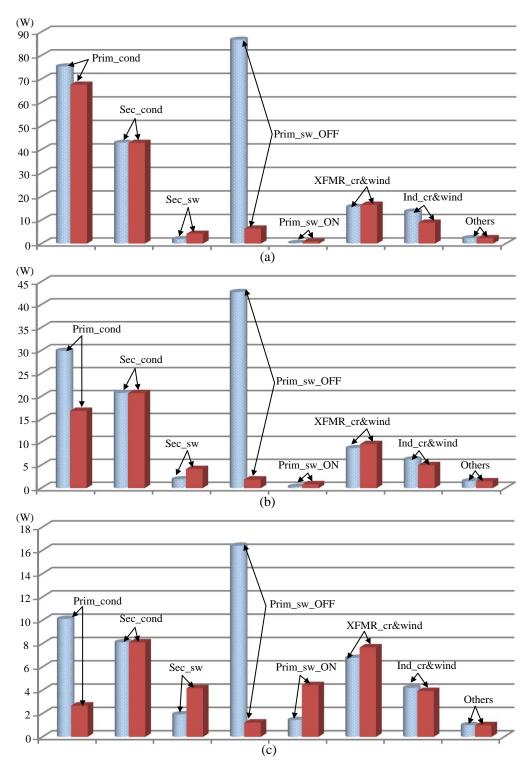

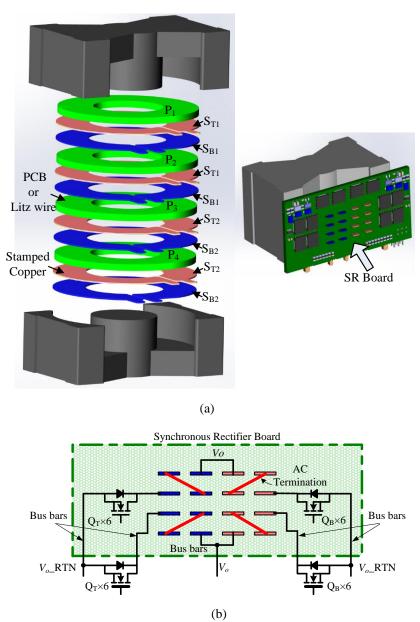

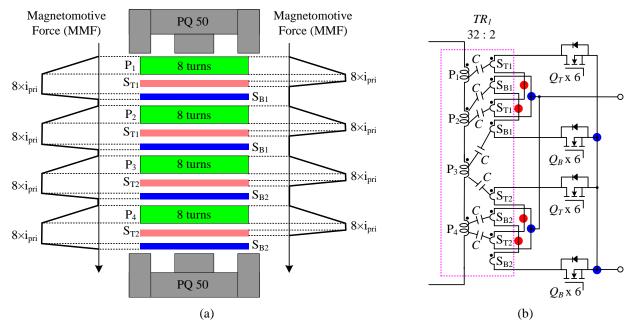

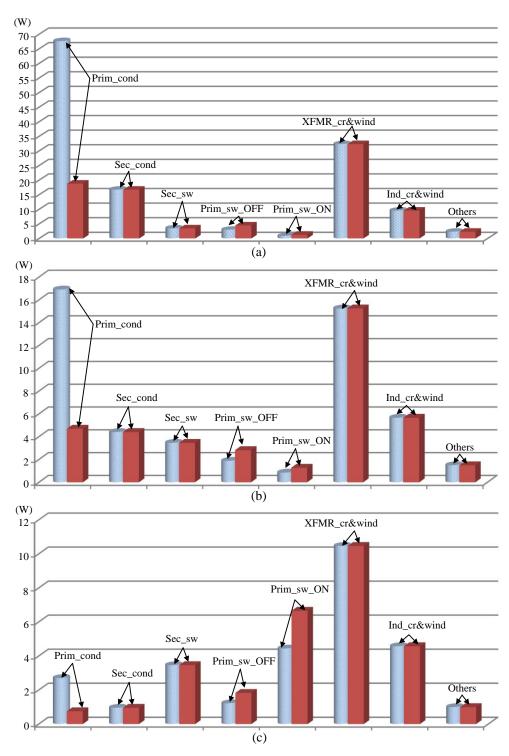

| Fig. 3-8 Proposed transformer circuit diagram for 54 V PSU.                                         | 75   |

|-----------------------------------------------------------------------------------------------------|------|

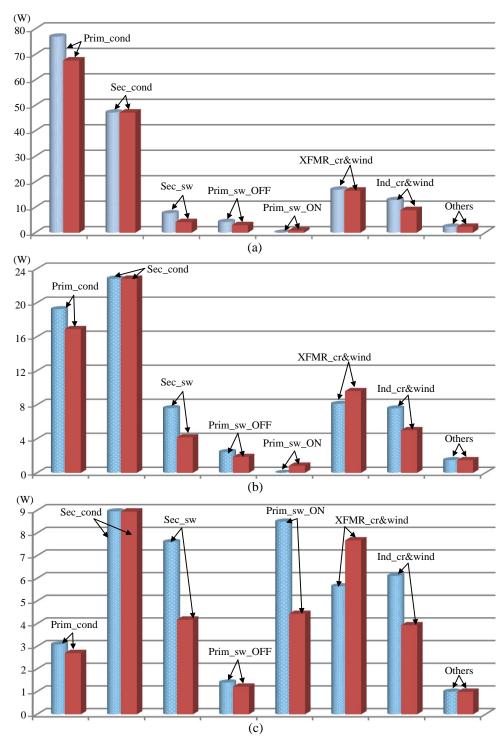

| Fig. 3-9 Loss breakdown comparison of "improved Type E" (left bar) and "Type A" (right bar) PV      | VМ   |

| schemes conducted on SiC MOSFET-based prototype with $V_o = 380$ V and $v_{LL} = 480$ V: (a) L      | LOSS |

| comparison at 5 kW (100% load) (b) Loss comparison at 2.5 kW (50% load) and (c) Loss comparison at  | at 1 |

| kW (20% load)                                                                                       | 78   |

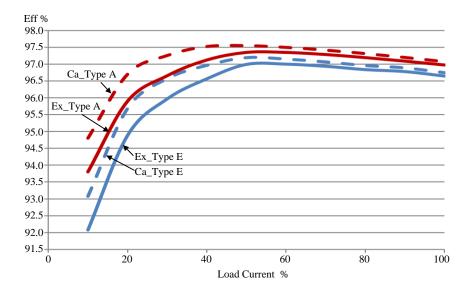

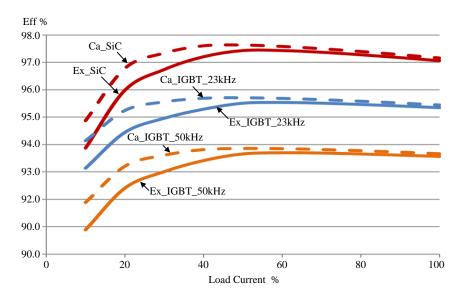

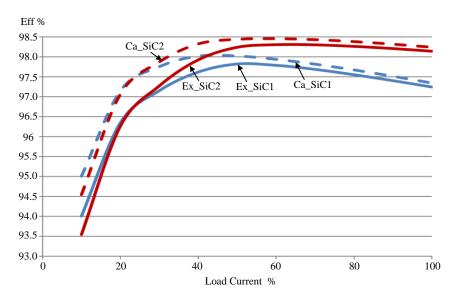

| Fig. 3-10 Experimental (solid-line) and calculated (dash-line) efficiency comparison on "Type A"    | and  |

| improved "Type E" PWM schemes conducted on SiC MOSFET-based 380 V prototype                         | 79   |

| Fig. 3-11 Experimental efficiency comparison between proposed PSU with implementation of "Type      | A'   |

| and improved "Type E" PWM schemes and benchmark (Vienna rectifier + LLC).                           | 79   |

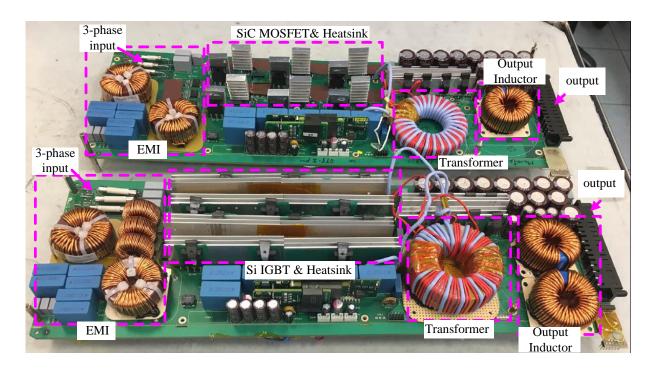

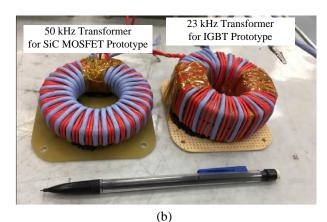

| Fig. 3-12 Power denisty comparison on Si IGBT-based and SiC MOSFET-based 380 V: (a) prototy         | pes  |

| and (b) transformers.                                                                               | 80   |

| Fig. 3-13 Loss breakdown comparison on Si IGBT-base (left bar) and SiC MOSFET-based (right bar)     | bar) |

| 380 V prototypes: (a) Loss comparison at 5kW (100% load), (b) Loss comparison at 2.5kW (50% load)   | oad) |

| and (c) Loss comparison at 1 kW (20% load).                                                         | 82   |

| Fig. 3-14 Experimental (solid-line) and calculated (dash-line) efficiency comparison on SiC MOSF    | ET-  |

| based and Si IGBT-based 380 Vprototype.                                                             | 83   |

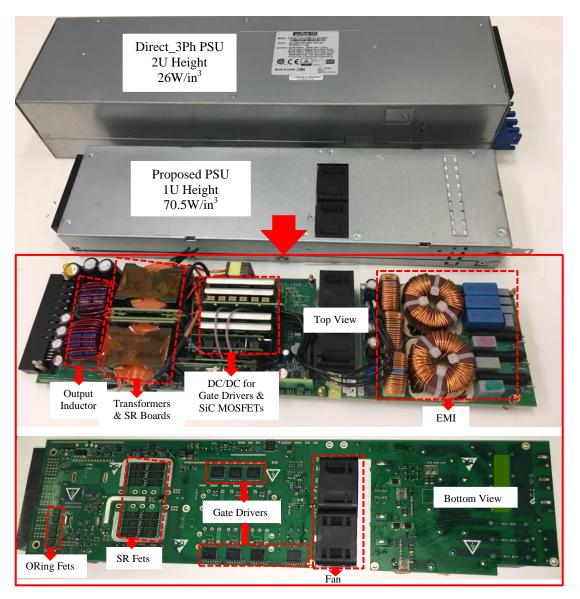

| Fig. 3-15 High-density transformer structure for the 54 V application: (a) integrated with synchron | ous  |

| rectification (SR) board and (b) connection of secondary stamped copper windings to SR board        | 85   |

| Fig. 3-16 Interleaved transformer structure (a) Magnetomotive Force (MMF) (b) with Inter-wind       | ling |

| capacitance and terminations (red circle is ac termination, blue circle is dc termination)          | 86   |

| Fig. 3-17 Power density comparison of proposed PSU (isolated buck matrix-type rectifier) and dis    | rect |

| three-phase PSU (Vienna rectifer + LLC) for 54 V output application.                                | 87   |

| Fig. 3-18 Loss breakdown comparison on 110 m $\Omega$ (left bar SiC1) and 35 m $\Omega$ (right bar SiC2) SiC                               |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| MOSFET-based prototype with $V_o = 54 \text{ V}$ and $v_{LL} = 480 \text{ V}$ : (a) Loss at 5 kW (100% load), (b) Loss at 2.5              |

| kW (50% load) and (c) Loss at 1 kW (20% load)                                                                                              |

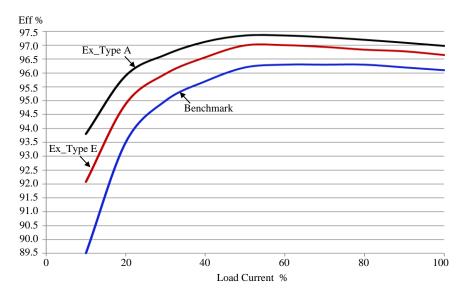

| Fig. 3-19Experimental (solid-line) and calculated (dash-line) efficiency comparison on 110 m $\Omega$ and 35                               |

| mΩ SiC MOSFET-based 54 V prototype90                                                                                                       |

| Fig. 3-20Experimental efficiency comparisons between proposed PSU (isolated buck matrix rectifier                                          |

| using 35 m $\Omega$ SiC MOSFET) and two types of the benchmark PSUs: single-phase PSU (bridgeless PFC +                                    |

| three-phase interleaved LLC resonant converter) and direct three-phase PSU (Vienna rectifier + LLC                                         |

| resonant converter)90                                                                                                                      |

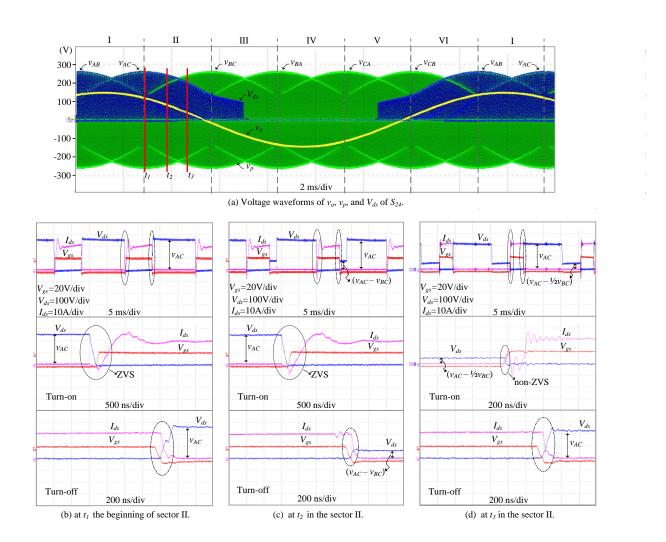

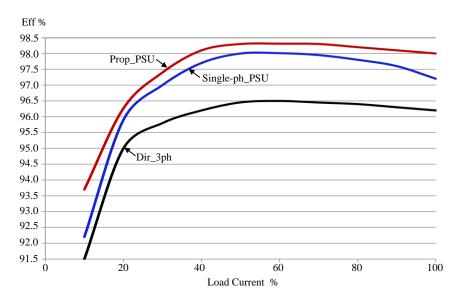

| Fig. 4-1 Voltage waveforms correspond to circuit in Fig. 2-1: (a) three-phase operation (normal operation)                                 |

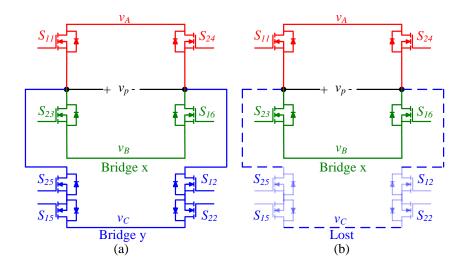

| Fig. 4-2 Three-phase rectifier redrawn as: (a) two FB-PS DC-DC converters when the three phases are                                        |

| connected and (b) a single FB-PS converter during one phase loss ("phase C")                                                               |

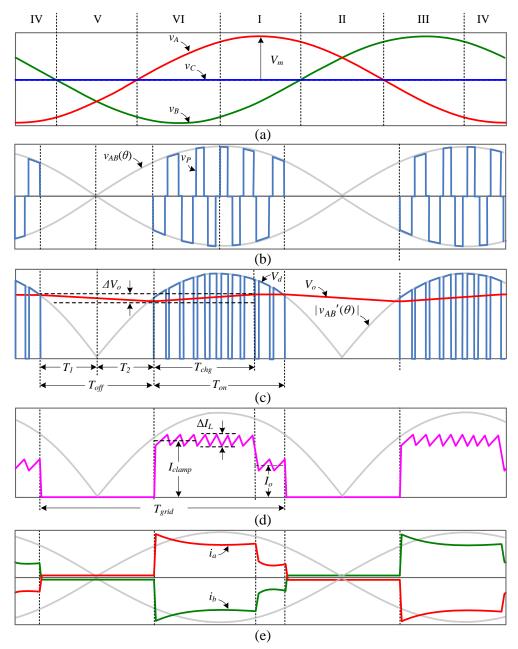

| Fig. 4-3 One phase loss operation of three-phase buck matrix rectifer: (a) three-phase grid voltages with                                  |

| "phase $C$ " is shorted, (b) with desired fault PWM for one phase loss operation converter, (c) with normal                                |

| PWM applied to one phase loss operaion and (d) the duty-cyle corresponding to $V_d$ in Fig. 2(c)98                                         |

| Fig. 4-4 Rectfier operation with "phase C" is shorted                                                                                      |

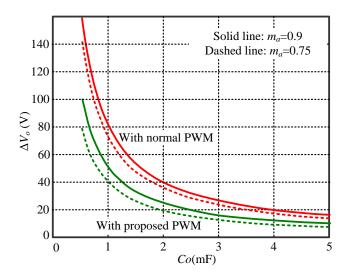

| Fig. 4-5 The output voltage drop $\Delta V_o$ versus $C_o$ in one phase loss operation at $I_o = 2/3I_{rated}$ and $f_{grid} = 50$         |

| Hz                                                                                                                                         |

| Fig. 4-6 The over current ratio $I_{clamp\_min}/I_{rated}$ versus $m_a$ in one phase loss operation at $I_o = 2/3I_{rated}$ and $f_{grid}$ |

| = 50 Hz103                                                                                                                                 |

| Fig. 4-7 Equivelant circuit for "Phase C" lost when (a) $v_A > v_B$ in sector VI and I (b) $v_A < v_B$ in sector III                       |

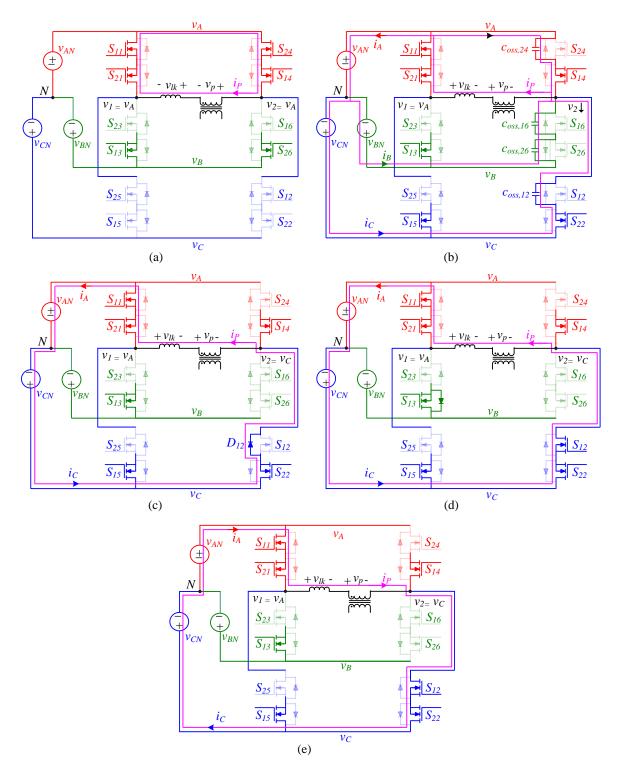

| and IV                                                                                                                                     |

| Fig. 4-8 Rectifier operation during one phase lost in interval of: (a) sector I with phase "leg A" for                      |

|-----------------------------------------------------------------------------------------------------------------------------|

| by passing time at the end of the switching cycle, (b) sector III with phase " $leg B$ " for by passing time at             |

| the end of the switching cycle, (c) sector VI with phase "leg $B$ " for bypassing time at the end of the                    |

| switching cycle, (d) sector IV with phase "leg A" for bypassing time at the end of the switching cycle. 106                 |

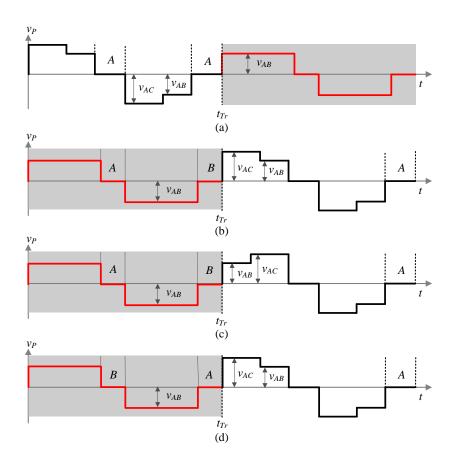

| Fig. 4-9 Transformer primary side voltage transition in sector I (b) (shaded area represents one phase loss                 |

| operation): (a) from normal operation to one phase loss operation, (b) from one phase loss operation to                     |

| normal operation using phase "leg $B$ " for bypassing prior to $t_{Tr}$ , (c) from one phase loss operation to              |

| normal operation using phase "leg $B$ " for bypassing prior to $t_{Tr}$ and with modified switching sequenc for             |

| first cycle of normal operation (LTH), (d) from one phase loss to normal operation using phase "leg $A$ "                   |

| for bypassing prior to $t_{Tr}$                                                                                             |

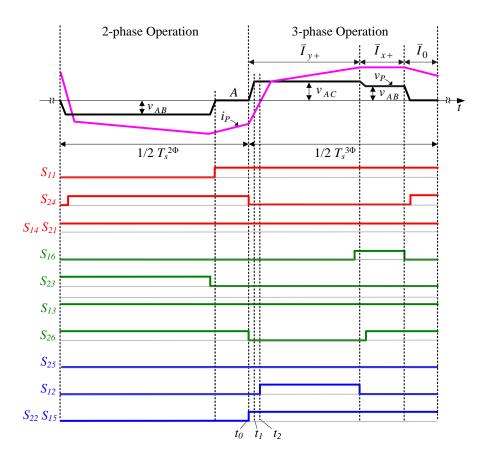

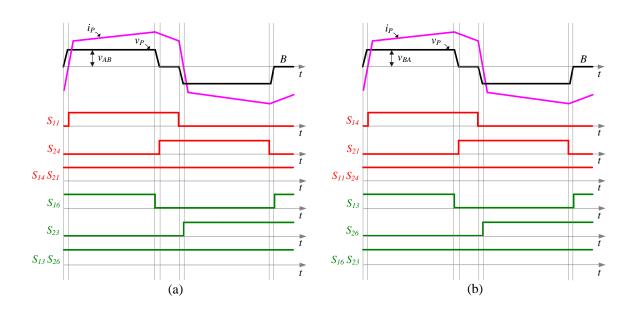

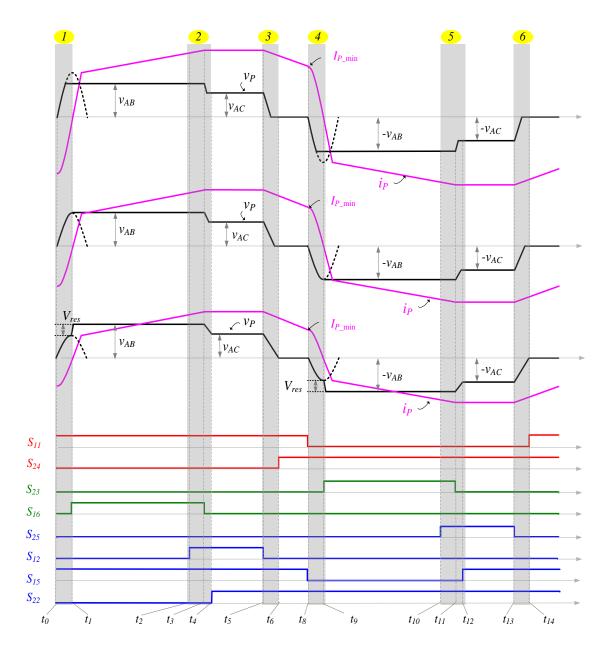

| Fig. 4-10 The detail transition from one phase loss to normal operation: with the waveforms of                              |

| transformer primary side voltage $v_P$ and current $i_P$ and corresponding switch gate signals $(T_s^{2\Phi})$ is period of |

| 2-phase operation and $T_s^{3\phi}$ period of 3-phase operation)                                                            |

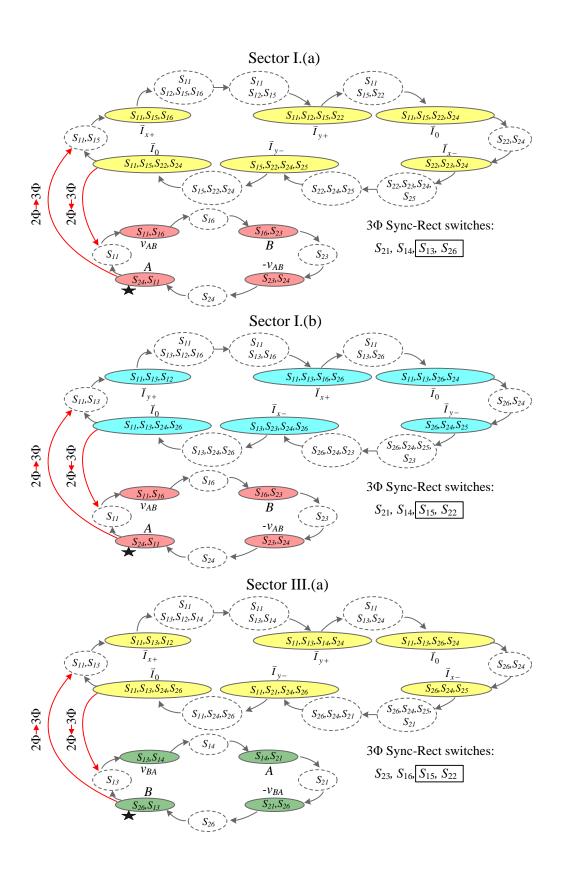

| Fig. 4-11 Switching transitions during one phase loss operation to normal operation: (a) at $t_0^-$ , (b) at $t_0^+$ , (c)  |

| at $t_1$ , (d) at $t_2$ , (e) at $t_2^+$                                                                                    |

| Fig. 4-12 One phase loss operation of rectifier during interval of: (a) sector I and sector VI ( $v_A > v_B$ ) with         |

| "phase B" for bypassing time at the end of the switching cycle, (b) sector III and sector IV $(v_B > v_A)$ with             |

| "phase <i>B</i> " for bypassing time at the end of the switching cycle                                                      |

| Fig. 4-13 Circuit waveforms: Primary voltage and current and corresponding switch gate signals for the                      |

| transition from one phase loss to normal operation (with eight-segment PWM scheme) in sector III (a).                       |

|                                                                                                                             |

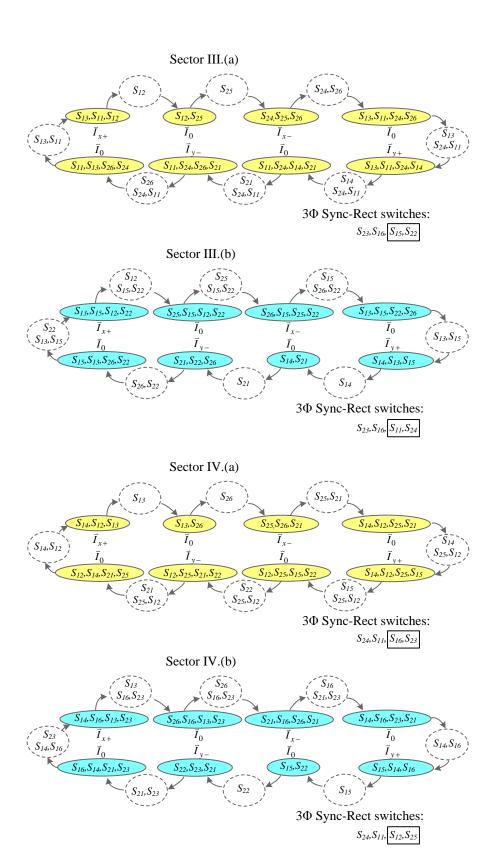

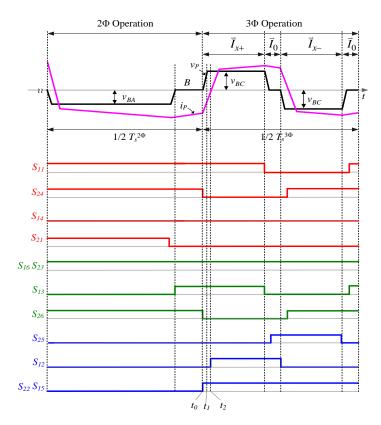

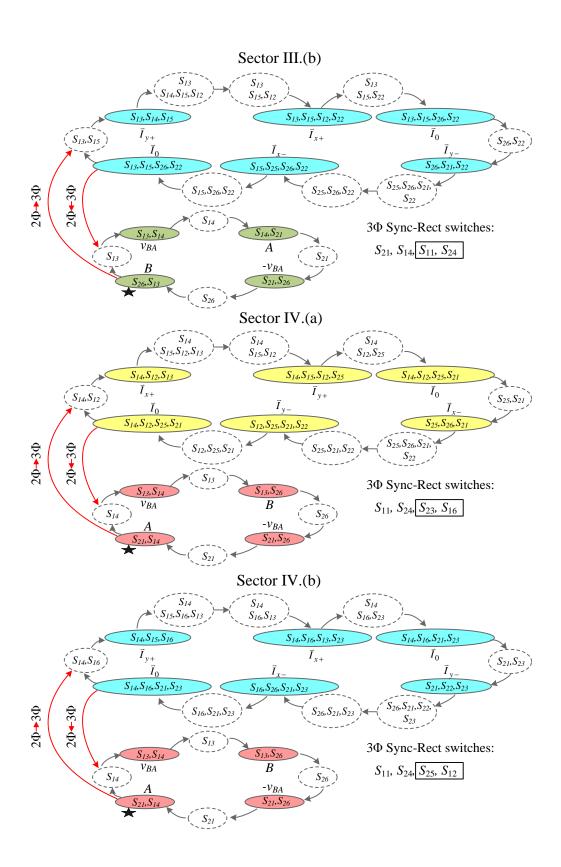

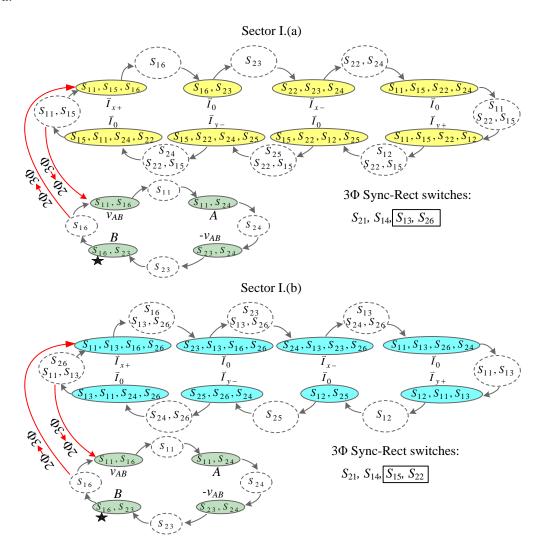

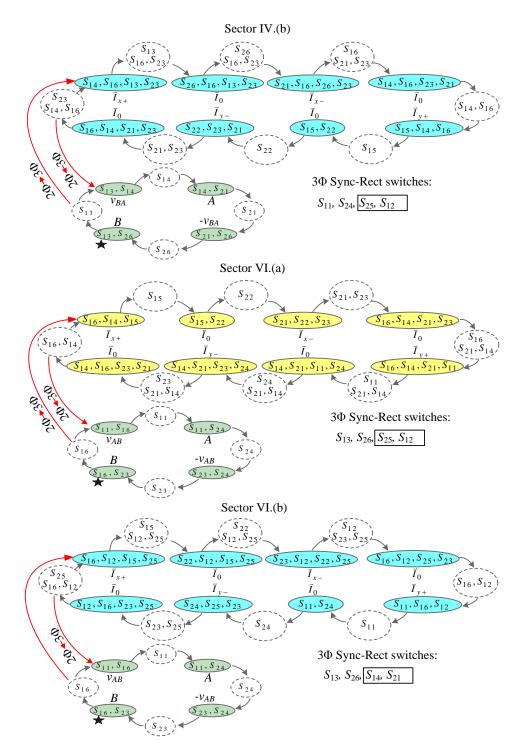

| Fig. 4-14 Finite commutation state machine from normal operation ( $3\Phi$ represents 3-phase operation) to                 |

| one phase loss ( $2\Phi$ represents 2-phase operations) and vice versa: two-step commutation realized for one               |

| phase loss operation, for the transition from one phase loss to normal operation and vice versa, for normal                 |

| operation of zero vector to active vector and vice versa, three-step commutation realized for active vector                      |

|----------------------------------------------------------------------------------------------------------------------------------|

| to another active vector in normal operation. (star represents the end of switching cycle of one phase loss                      |

| operation; Note: the switches in the rectangular boxes are the syncronous rectification switches for $3\Phi$                     |

| operation and constraits should be applied on them in the the vicinity of the boundary between part a and                        |

| part b per Table 2-1.)                                                                                                           |

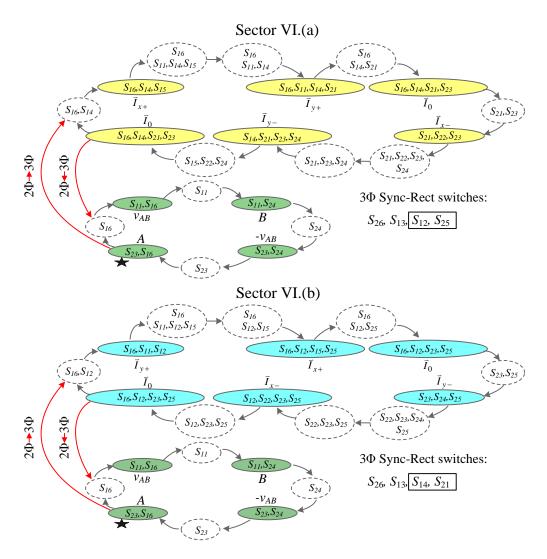

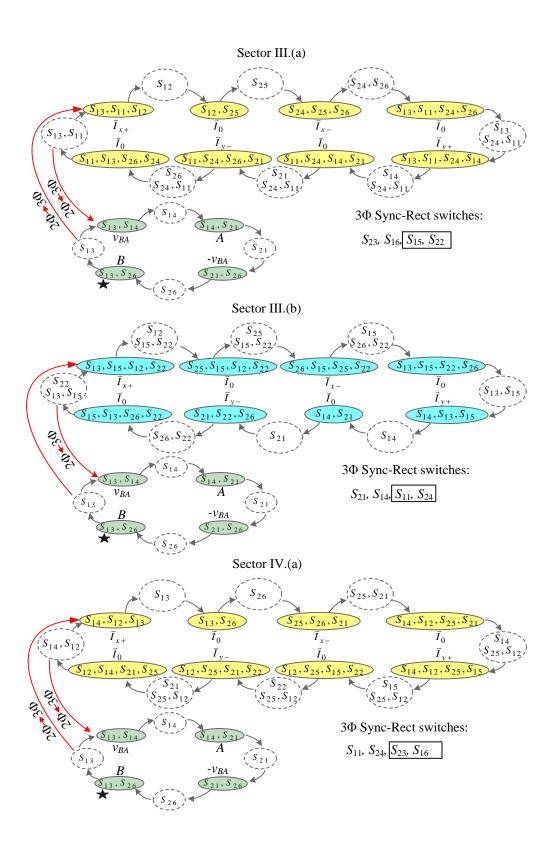

| Fig. 4-15 Commutation state machine for normal operation (3 $\Phi$ ) and one phase loss (2 $\Phi$ ): two-step                    |

| commutation realized for one phase loss operation, normal operation, transition from one phase loss to                           |

| normal operation and from normal operation to one phase loss operation. (Note: star represents the end of                        |

| switching cycle of one phase loss operation. Note: the switches in the rectangular boxes are the                                 |

| syncronous rectification switches for $3\Phi$ operation and constraits should be applied on them in the the                      |

| vicinity of the boundary between part a and part b per Table 2-1.)                                                               |

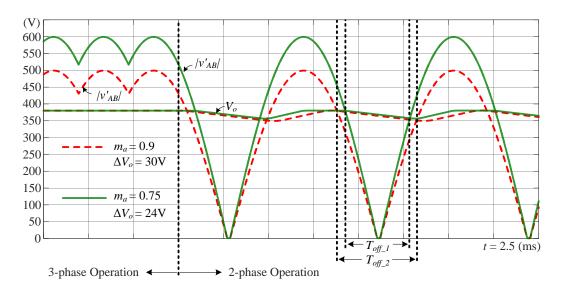

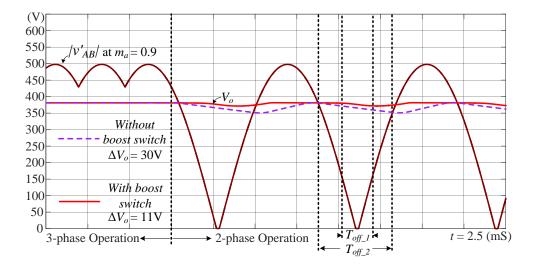

| Fig. 4-16 Comparison of output voltage drop $\Delta V_o$ for case 1) at $m_a = 0.8$ and case 2) at $m_a = 0.9$ with $f_{grid}$   |

| = 60 Hz120                                                                                                                       |

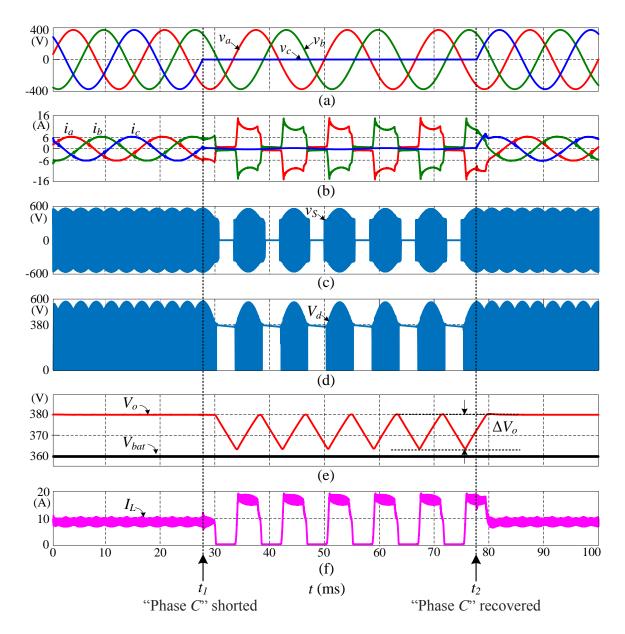

| Fig. 4-17 Simulated waveforms for $2/3P_{O\_max}$ , $v_{LL} = 480$ V and $m_a = 0.75$ when "phase C" is shorted at $t_I$         |

| and recovered at $t_2$ : (a) input phase voltages, (b) input phase currents, (c) transformer secondary voltage,                  |

| (d) output of bridge rectifier, (e) output voltage and battery voltage set point, (f) output inductor current.                   |

| 121                                                                                                                              |

| Fig. 4-18 Comparison of output voltage drop $\Delta V_o$ for $m_a = 0.75$ and $m_a = 0.9$ with $f_{grid} = 60$ Hz                |

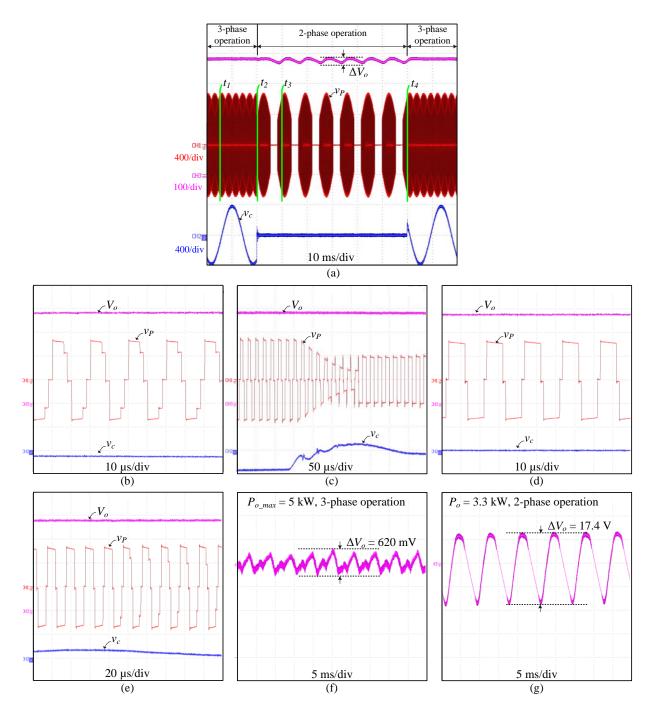

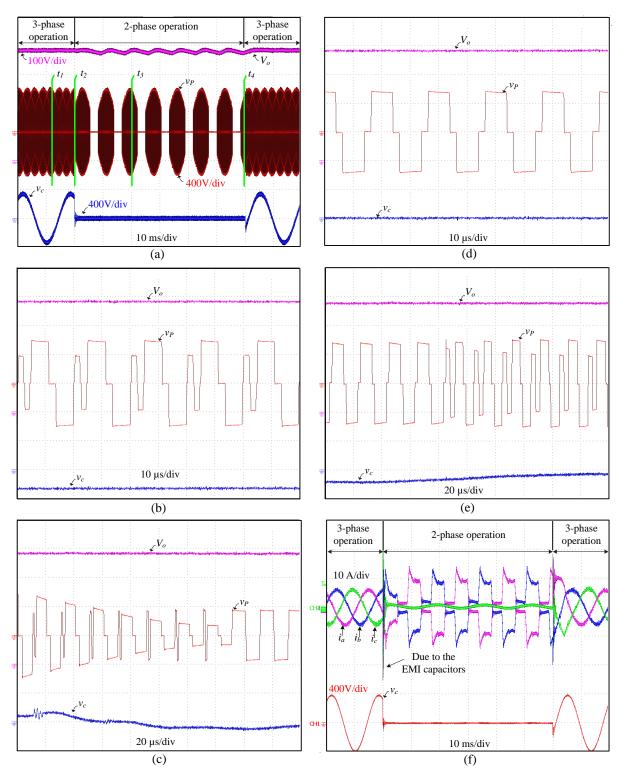

| Fig. 4-19 Experimental waveforms for $2/3P_{o\_max} = 3.3$ kW, $v_{LL} = 480$ V, $f_{grid} = 60$ Hz: (a) voltage                 |

| waveforms of $v_P$ , $v_{LL}$ , $V_o$ , (b) at $t_1$ , normal operation (3-phase operation), (c) at $t_2$ , instant "phase C" is |

| shorted, (d) at $t_3$ , one phase loss operation (2-phase operation), (e) at $t_4$ , instant "phase C" recovered, (f) ac         |

| ripple of voltage $V_o$ in normal operation at maximum output power $P_{o\_max} = 5 \text{ kW}$ , (g) ac ripple of               |

| voltage V in one phase loss operation 124                                                                                        |

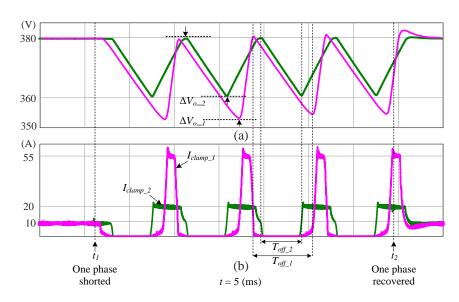

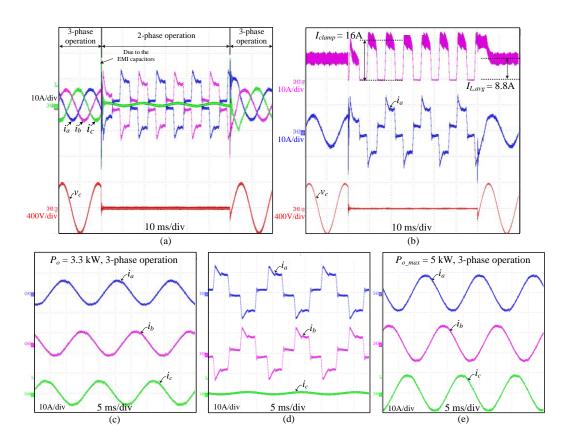

| Fig. 4-20 Experimental waveforms for $v_{LL} = 480$ V, $f_{grid} = 60$ Hz, $m_a = 0.75$ at at $2/3P_{o\_max} = 3.3$ kW: (a)                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| input phase currents and voltage waveforms of $i_a$ , $i_b$ , $i_c$ and $v_c$ , (b) output inductor current $I_L$ and input                    |

| phase currents and voltage, (c) normal operation (3-phase operation) (d) one phase loss operation (2-phase                                     |

| operation), (e) normal operation at maximum output power $P_{o\_max} = 5 \text{ kW}.$ 125                                                      |

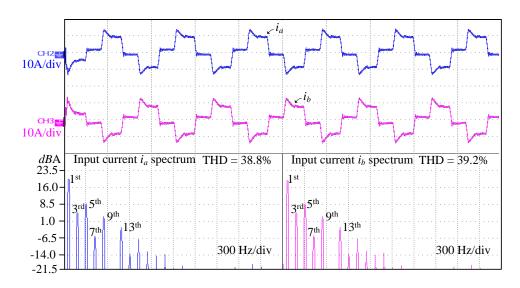

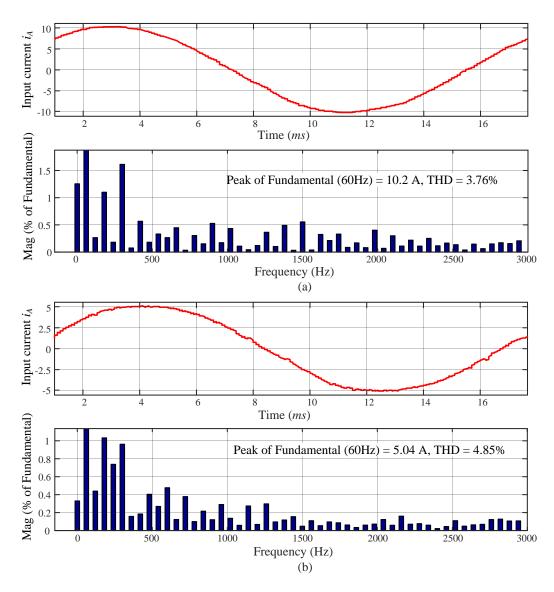

| Fig. 4-21 Experimental spectrums of input phase currents of $i_a$ and $i_b$ at $2/3P_{o\_max} = 3.3$ kW                                        |

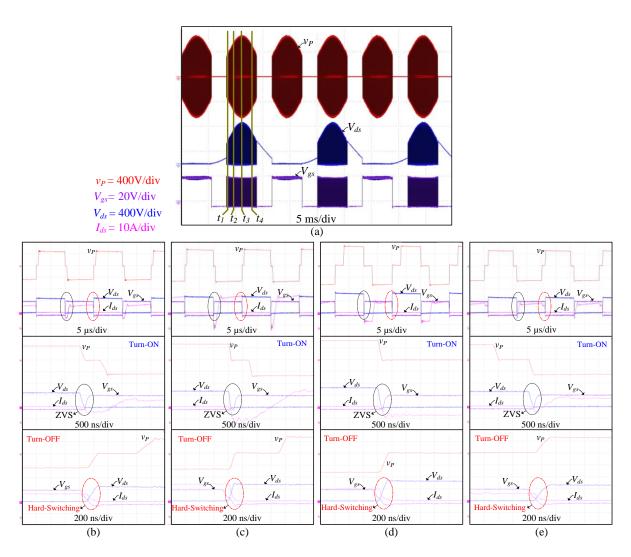

| Fig. 4-22 Experimental waveforms for converter MOSFETs switching behavior (turn-ON and turn-OFF                                                |

| actions) during one phase loss operation: (a) voltage waveforms of $v_P$ , $V_{ds}$ and $V_{gs}$ , (b) at $t_1$ (c) at $t_2$ , (d) at          |

| $t_3$ and (e) at $t_4$                                                                                                                         |

| Fig. 4-23 Experimental waveforms at $2/3Po\_max$ , $v_{LL} = 480 \text{ V}$ , $f_{grid} = 60 \text{ Hz}$ : (a) normal operation (3 $\Phi$ ) to |

| one phase loss operation (2 $\Phi$ ), (b) at $t_1$ , normal operation, (c) at $t_2$ , instant "phase C" is shorted, (d) at $t_3$ ,             |

| one phase loss operation, (e) at $t_4$ , instant "phase C" recovered, (f) input phase currents and voltage                                     |

| waveforms of $i_a$ , $i_b$ , $i_c$ and $v_c$                                                                                                   |

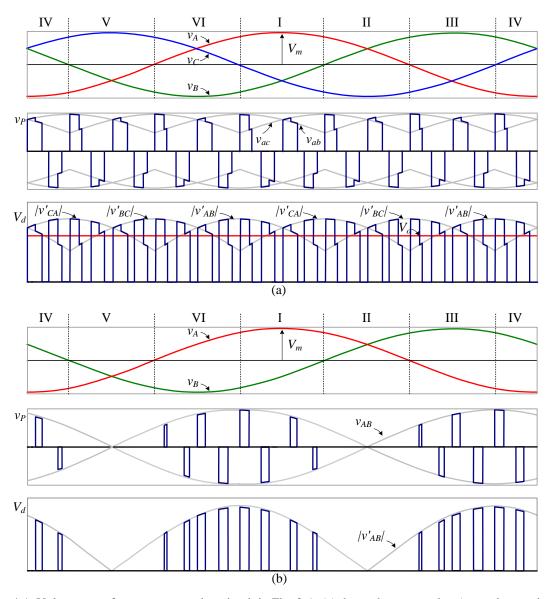

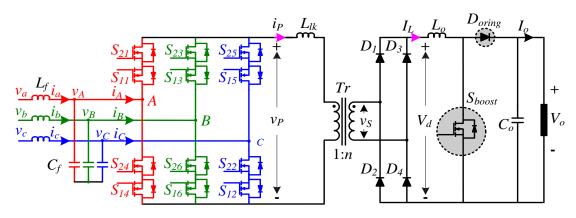

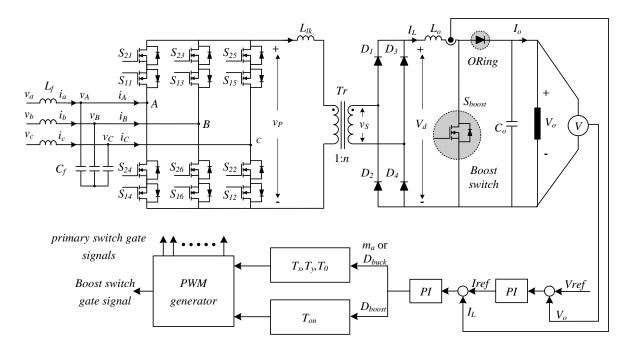

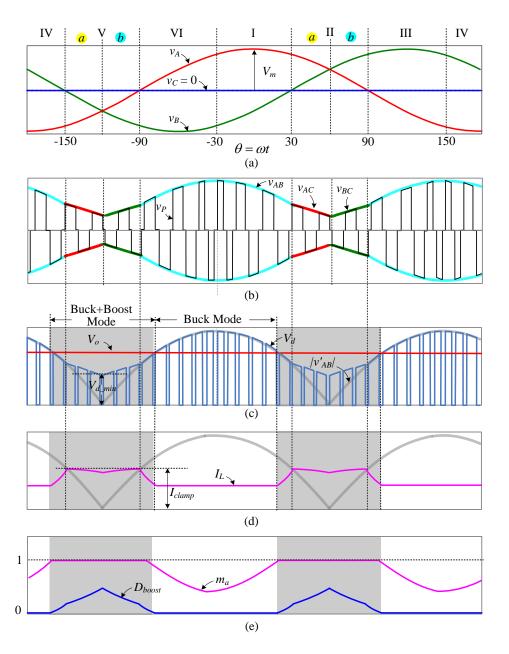

| Fig. 5-1 Three-phase isolated buck matrix-type rectifier with a boost switch                                                                   |

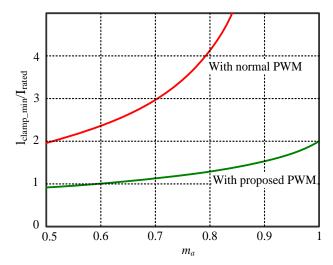

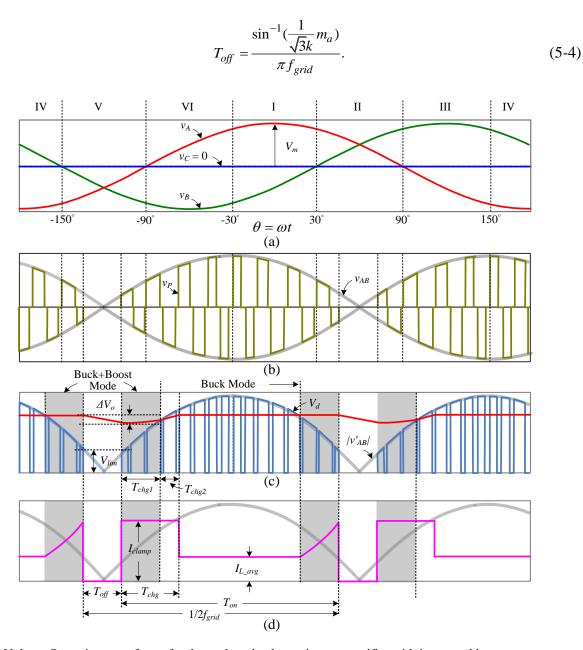

| Fig. 5-2 Voltage Operation waveforms for three-phase buck matrix-type rectifier with integrated boost                                          |

| output stage to achieve minimum output voltage drop during one phase opened                                                                    |

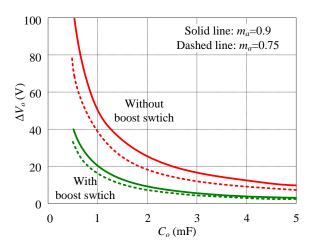

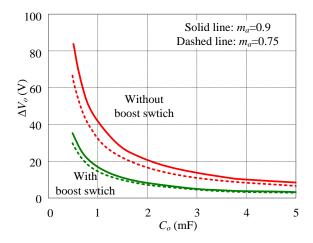

| Fig. 5-3 The output voltage drop $\Delta$ Vo versus Co in one phase loss operation with and without boost                                      |

| switch at                                                                                                                                      |

| Fig. 5-4 The output voltage drop $\Delta V_o$ versus $C_o$ in one phase loss operation with and without boost                                  |

| switch at                                                                                                                                      |

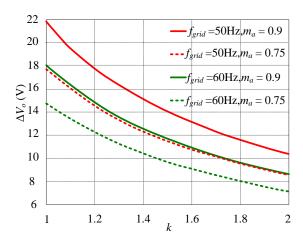

| Fig. 5-5 The output voltage drop $\Delta$ Vo versus the over current racial k in one phase loss operation with                                 |

| boost switch at ma = $0.75$ and $0.9$ respectively with $C_o = 1.4$ mF                                                                         |

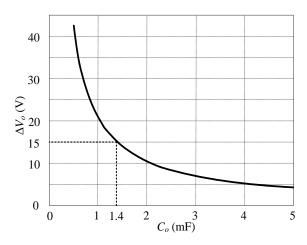

| Fig. 5-6 The output voltage drop $\Delta V_o$ versus output capacitance $C_o$ in one phase loss operation with boost                           |

| switch at $m_a = 0.9$ , $f_{grid} = 50$ Hz and $I_{clamp} = 1.4I_{rated}$                                                                      |

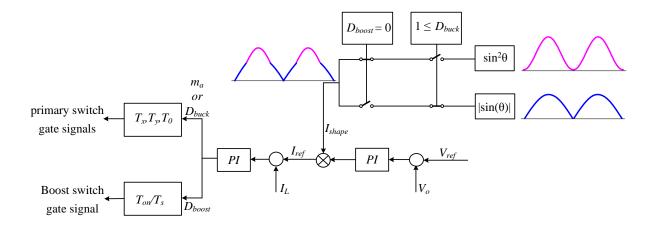

| Fig. 5-7 The control block diagram of the converter for buck+boost and buck operation                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 5-8 The simplyfied equivalent circuits of the converter during one phase loss operation (a)                                          |

| buck+boost operation (b) boost operation and (c) buck operation. (Note: $v_{in}$ is the same as $ v'_{AB} $ ) 141                         |

| Fig. 5-9 Operation waveforms for Three-phase buck matrix rectifier with integrated boost output stage to                                  |

| achieve minimum input current THD during one phase opened.(d) output inductor current (e) duty cycle                                      |

| of Buck mode and buck+boost mode                                                                                                          |

| Fig. 5-10 Output voltage drop vs capacitor for different operations of rectifier during one phase loss                                    |

| operation                                                                                                                                 |

| Fig. 5-11 Complete control structure enabling sinusoidal input currents under one phase loss operation.                                   |

| Fig. 5-12 Operation waveforms for Three-phase buck matrix rectifier with integrated boost output stage to                                 |

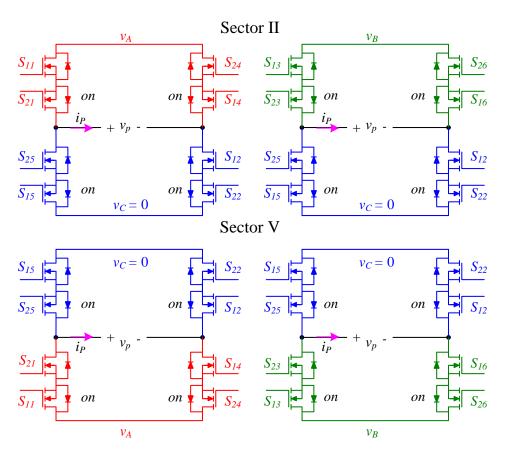

| achieve minimum output voltage drop during one phase shorted                                                                              |

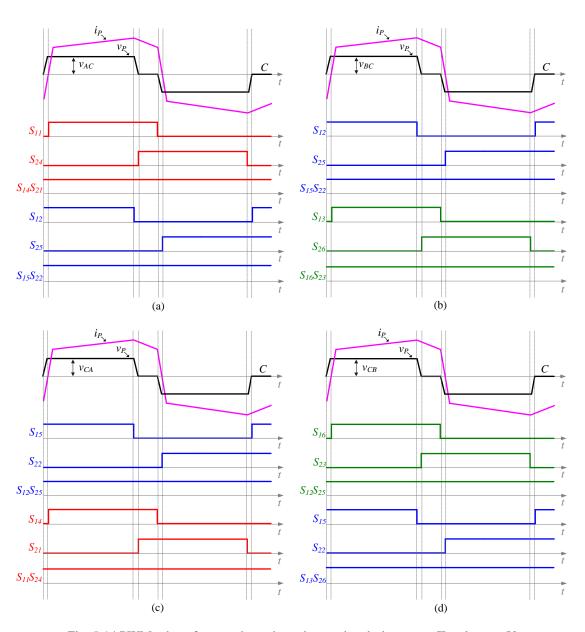

| Fig. 5-13 The Equivalent circuit for one phase shorted operation during sector II and sector V                                            |

| Fig. 5-14 PWM schem for one phase shorted operation during sector II and sector V                                                         |

| Fig. 5-15 Comparison of output voltage drop $\Delta V_o$ for conventional buck rectifier and buck rectifier with                          |

| boost switch at $m_a = 0.9$ and $f_{grid} = 60$ Hz. 148                                                                                   |

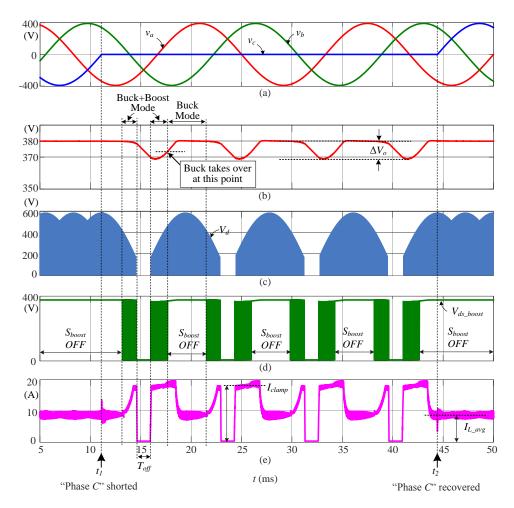

| Fig. 5-16 Simulated waveforms for buck matrix rectifier with boost switch activated: $v_{LL} = 480 \text{ V}$ (at $m_a = 480 \text{ V}$ ) |

| 0.75), $f_{grid} = 60 \text{ Hz}$ , $k = 1.4 \text{ and } 2/3Po\_max \text{ when "phase } C$ " is sorted and recovered                    |

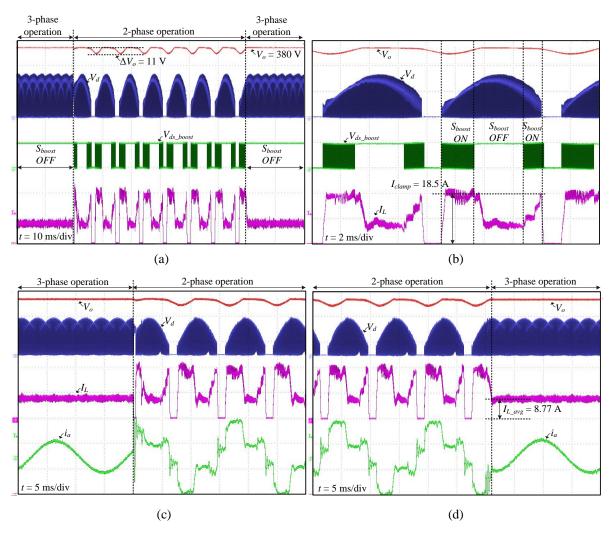

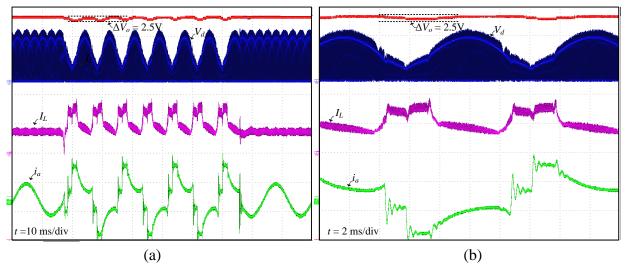

| Fig. 5-17 Experimental waveforms of the converter with a boost switch for $2/3Po\_max$ , $v_{LL} = 480 \text{ V}$ (at                     |

| $m_a = 0.75$ ), $f_{grid} = 60$ Hz: (a) voltage waveforms of $V_o$ (50 V/div), $V_d$ (400 V/div), $V_{ds\_boost}$ (400 V/div),            |

| and $I_L$ (10 A/div) (b) Zoom in waveformes of (a) during one phase opened (c) Waveforms from 3-phase                                     |

| operation to one phase opened operation , $i_a$ (10 A/div) (d) Waveforms from one phase opened operation                                  |

| to 3-phase operation.                                                                                                                     |

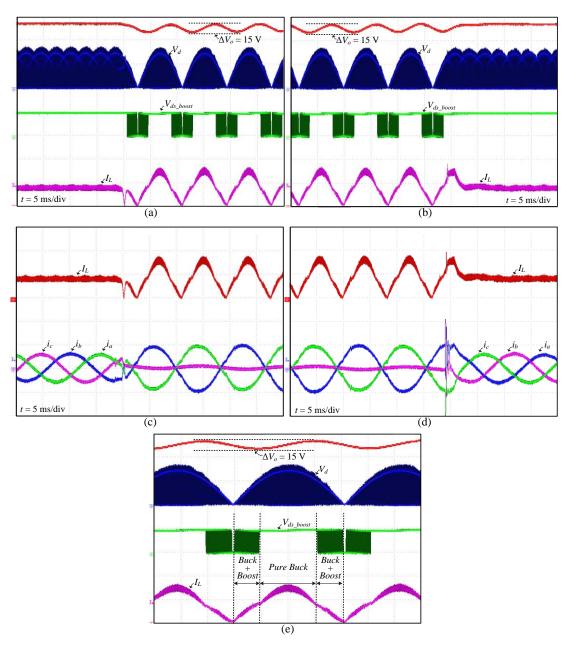

| Fig. 5-18 Experimental waveforms of the converter with a boost switch for $2/3Po\_max$ , $v_{LL} = 480 \text{ V}$ (at              |

|------------------------------------------------------------------------------------------------------------------------------------|

| $m_a = 0.75$ ), $f_{grid} = 60$ Hz: (a) Waveforms of output voltage $V_o$ , rectifier output voltage $V_d$ , boost switch $V_{ds}$ |

| and inductor current $I_L$ during transition from 3-phase operation to one phase loss operation (b) Waveforms                      |

| during transition from one phase loss operation to 3-phase operation. (c) current waveforms of $i_a$ , $i_b$ , $i_c$               |

| and $I_L$ (10 A/div) from 3-phase operation to one phase loss operation (d) current waveforms of $i_a$ , $i_b$ , $i_c$             |

| and $I_L$ (10 A/div) from one phase loss operation to 3-phase operation. Good input current THD can be                             |

| maitained for both three phase operation and one phase loss operation (e) zoom-in waveforms shows                                  |

| smoth transition between pure buck mode and buck+boost mode                                                                        |

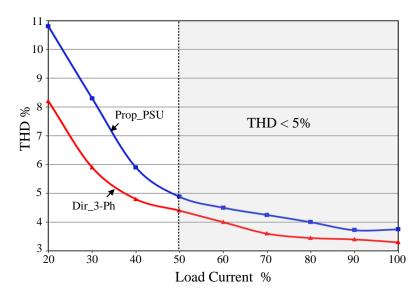

| Fig. 5-19 Experimental spectrum analysis of input grid current wave during one phase loss operation                                |

| shows low THD and its individual harmonics (a) at 100% load (3.3 kW) and (b) at 50% load (1.65 kW).                                |

|                                                                                                                                    |

| Fig. 5-20 Measured input grid current THD (%) vs load (%) during one phase loss operation for direct                               |

| three-phase (Dir_3-Ph) and proposed PSU (Prop_PSU)                                                                                 |

| Fig. 5-21 Input grid current wave and its indivitual harmonic in one phase loss operation: (a) at 100%                             |

| load and (b) at 50% load                                                                                                           |

# Acronyms

CRM Critical-Conduction-Mode

DCM Discontinuous-Conduction-Mode

EMI Electromagnetic Interference

FB-PS Full-Bridge Phase-Shifted

FPGA Field Programmable Gate Array

GaN Gallium-Nitride

IGBT Insulated Gate Bipolar Transistor

PSU Power Supply Unit

PDS Power Distributed System

PDU Power Distribution Unit

PWM Pulse-Width Modulation

SiC Silicon Carbide

SVM Space Vector Modulation

THD Total Harmonic Distortion

ZCS Zero-Current Switching

ZVS Zero-Voltage Switching

# Chapter 1

## Introduction

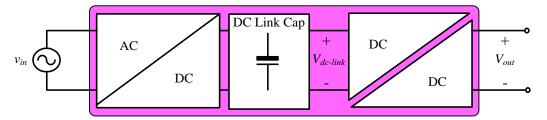

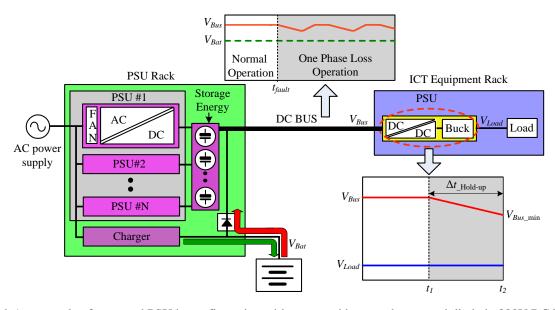

With the explosive development of information technology, the communication and computing systems, such as data centers, telecoms, and servers have become a large market for the power supply industry. In a typical data center, less than half of the energy consumed is delivered to the compute load, which includes microprocessors, memory and disk drives. The rest of the power is lost in power conversion, distribution, and cooling, resulting in high utility bills, a large environmental footprint and the inability to fill equipment racks [1]. Power savings in the power distribution system (PDS) result in further savings in the facility cooling system, because less heat is generated in the distribution and therefore less heat has to be cooled [1, 2]. Cooling is often the limiting factor in data center capacity (heat removal can be a bigger problem than getting power to the equipment) [3, 4]. Over the past decade energy efficiency and power density have become the top concerns for power conversions in data center and telecom. Rising energy intensity leads to a higher cost for delivering power. Meanwhile, the demand for compact power supply unit (PSU) grows significantly. It requires PSU with high efficiency, low profile and high power density. Generally, the power supplies for power distribution system in data center and telecom are the standard two-stage approach [5, 6, 7, 8]. It consists of a front-end power-factor-correction (PFC) rectifier with bulky dc-link capacitor followed by an isolated DC-DC converter as shown in Fig. 1-1. In general, the two-stage power conversion has demonstrated excellent performance and high reliability, since the design can be optimized for each stage. However, the cost for this type of approach is high due to relatively large number of components to accomplish the required functions of the front-end converters.

Fig. 1-1 Block diagram of the two-stage power supply (PSU).

Before studying deeper into details of this growing application, the configuration and technical requirement of rectifier in DC PDS must be considered to fully understand the context of the dissertation and rationalize for using single-stage approach.

#### 1.1 DC Power Distribution Systems (PDS)

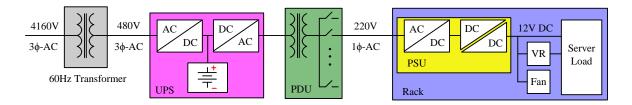

The basic structures of a conventional AC power distribution system (PDS) and a facilitylevel DC PDS are shown in Fig. 1-2. As can be noticed, the conventional AC PDS in Fig. 1-2 (a) includes multiple conversion stages, which lead to a strongly reduced overall efficiency. In the ac delivery system, the power immediately undergoes a double conversion in a centralized uninterruptable power supplies (UPS) which supplies power to many racks. Power is rectified to DC to feed an intermediate backup storage system, and then it is inverted back to AC and sent to the power distribution unit (PDU). At the PDU, voltage is stepped down to 208/120 V to feed each PSU in the server rack. The PSU in each server rectifies the 220 V AC to a DC voltage typically 380Vdc. The 380 V is then converted with an isolated DC-DC converter to 12 V. Some loads, such as hard drives, can take 12 V directly. Other loads, such as processors, need voltage regulators (VR) to step down the voltage. Depending on the efficiency of the different components, the overall efficiency of such an AC PDS is between 50% and 70% [1]. In a facility-level DC PDS, however, several conversion steps can be avoided to improve the efficiency. As shown in Fig. 1-2 (b) and (c), the DC-AC conversion in the UPS, the transformer in the PDU and the AC-DC conversion in the PSU are eliminated, resulting in a higher efficiency of the power distribution system [1].

(a) Conventional AC power distribution.

(b) 48V DC facility-level power distribution.

(c) 380V HVDC facility-level PDS.

Fig. 1-2 Block diagrams of power distribution systems for data center and telecom [1].

The 48 V and 380 V solutions architecture help reducing power loss from the data center facility, to the rack, and the server board level [9, 10, 11]. For example, compared with the current mainstream approach (12 V power distribution), 48 V architecture provides better power conversion efficiency at rack level, and works at lower current levels to deliver a sixteen times reduction in power distribution. Intel concluded that DC power distribution system (both 400 V and 48 V) was consistently more efficient than AC at all voltages.

#### 1.2 Configuration PSU/Battery in Rack Level

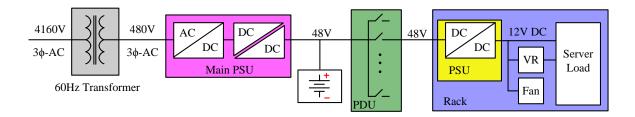

Given the trend towards high-density rack in the infrastructure, it is likely that the future may bring racks at a higher density than the existing equipment in the data center [3]. Data centers today use more kilowatts (kW) per rack or per square foot than ever before. As the rack power climbs, conversion efficiency becomes more important. A 1% efficiency improvement can result in saving hundreds of watts at rack level, and kilowatts in the data center [9]. The power is processed by redundant two-stage front-end converters represented by the power supplies (PUSs) #1 through #N+1 in Fig. 1-3. Each PSU consists of a PFC stage and a DC-DC converter used to regulate the DC bus. Conversion efficiency and total volume of the power distribution system (PDS) depend largely on PSU performance [13]. It is important to mention the main focus of the work in this dissertation is conducted on development of high efficiency and high power density PSU for this application.

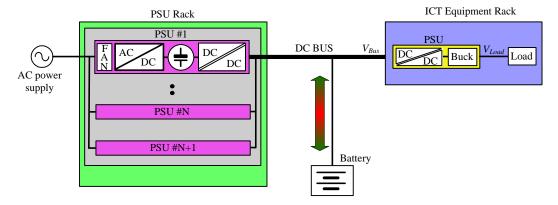

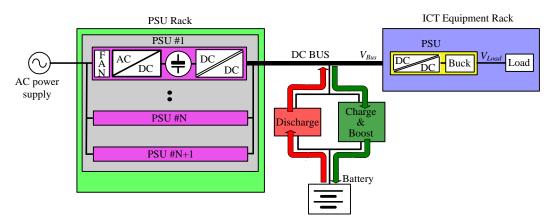

There are various configurations of PSU connected to a backup battery as shown in Fig. 1-3. In common power architecture of a UPS system shown n Fig. 1-3 (a), a load is connected through a DC bus to both a main PSU and a backup battery [1]. The load is typically powered from the main PSU, for example through mains power. If the AC power supply is disrupted, for example, because of a power outage, the load is switched to the backup battery, which ensures continuous power supply. One drawback is that after a battery discharge, the DC bus voltage determined by the battery voltage is much lower than the battery floating voltage which results in a higher current at constant power ICT load. This higher current flowing through PDUs and power distribution lines impacts the design by increasing the cross-sectional area of distribution power lines and rated current of protection devices. In addition, the main PSU may require a wide operational range of DC bus voltage, e.g, in the order of tens of Volts. Such a wide operational voltage range may lower the power efficiency and increase cost and complexity of the supply and conversion operations in the system [14].

For the implementation of battery backup system architecture in Fig. 1-3 (b) [14], different charging and discharging paths may be used between the battery module and the DC bus such that the battery voltage is controlled to be higher than the DC bus voltage.

(a) 380V DC with direct battery connection.

(b) Battery backup with different charging and dischargin path in 48V DC Google system.

(c) Separated battery charger with boost option in 380 V DC NTT system.

Fig. 1-3 Various configuration of battery backup system in 48 V and 380 V power distribution system (note: PDU is not drawn and VR (Buck DC-DC converter) is redrawn as part of PSU for simplicity).

As a result, the DC bus voltage may operate at a narrower range than the battery voltage. This may improve overall efficiency and reduce cost of operation of the UPS system. The separation of charging and discharging path can also increase protection against system faults such as thermal runaways, short-circuits, and battery over and under voltage.

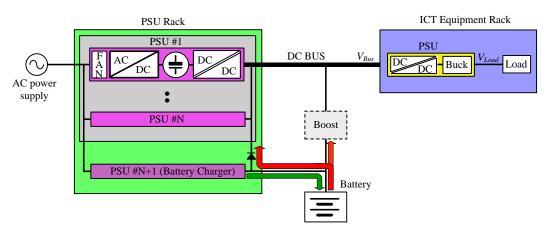

Fig. 1-3 (c) shows other configurations of the rectifier with a separate charger. Diode and battery rapidly provides the system with a nominal output voltage after the supplies are down. In addition to this, the PSUs separated by a diode from the battery do not need to have a battery charger function. Only the PSU directly connected to the battery needs to have a battery charger function. Redundancy of the charger is better for high reliability. If the range of the operation voltage defined by each PSU in ICT Equipment is narrow, the voltage DC bus must be compensated without interruption in the load. In this case, a system configuration with a boost is recommended [12].

## 1.3 Technical Requirements for PSU

The purpose of the front-end converter is to regulate the DC output voltage tightly, supply all the load connected to the distributed bus, guarantee current sharing, provide isolation and charge a bank of batteries to provide backup energy when the grid breaks down. The rectifier achieves N+1 parallel redundancy and increases reliability. In case of a failure in a rectifier unit in the cabinet, each PSU unit must be able to operate and maintain safe operation. These units are commonly modular and hot plug capable for simplifying maintenance and reducing repair time.

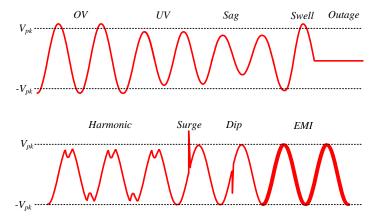

In addition to those basic PSU requirements, the front-end PSUs are required to operate with a wide input-voltage and/or output-voltage range. The front-end PSUs must meet the input stringent international requirements, such as the IEC 61000-3-2, to limit the harmonic currents drawn by the off-line equipment and provide unity power factor. As other requirements, PSU has to meet some abnormal input operation as shown in Fig. 1-4: voltage sag, surge, unbalanced input three-phase, and the most stringent one is one phase loss operation.

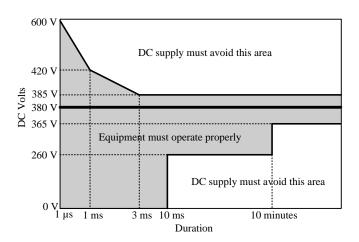

Fig. 1-4 Input power quality.

Fig. 1-5 Output voltage requirement.

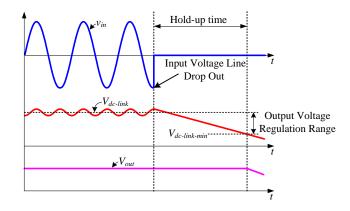

Fig. 1-6 Hold-up time voltage waveforms.

The new international standardization, ITU-T L.1200 specifies the direct current (DC) interface between the power feeding system and ICT equipment connected to it. It describes normal and abnormal voltage ranges, and immunity test levels for ICT equipment to maintain the stability of telecommunication and data communication services. The output voltage range of rectifiers should be adapted to interface based on ITU-T L.1200 as shown in Fig. 1-5.

Another obstacle for front-end PSU design is the hold-up time requirement. It requires the front-end system to provide full power output and regulate output voltage for a few mili-second, after the AC line is lost as shown in Fig. 1-6 (circuit block shown in Fig. 1-1). This hold-up time will ensure the digital system to have enough time to respond to power failure.

# 1.4 The Existing Commercialize Isolated Three-phase PSU and Proposed PSU

In following section, a review on the existing power supply technologies is provided, including the pros and cons of each technology. The existing three-phase isolated AC-DC converters for PDSs can be implemented either with three single-phase isolated AC-DC converters, or with a direct three-phase PFC rectifier front-end such as the Vienna rectifier or the six-switch PFC boost rectifier followed by an isolated DC-DC converter [15]. To be able to employ single-phase modules designed for 220/277 V<sub>rms</sub> phase-to-neutral voltage in three-phase power systems with nominal phase-to-phase voltage of 380/480 V<sub>rms</sub>, the three single-phase modules must be connected in star (Y) configuration. The delta (Δ) configuration cannot be used since it would require that single-phase modules be connected across two phases, i.e., to a voltage exceeding their rating.

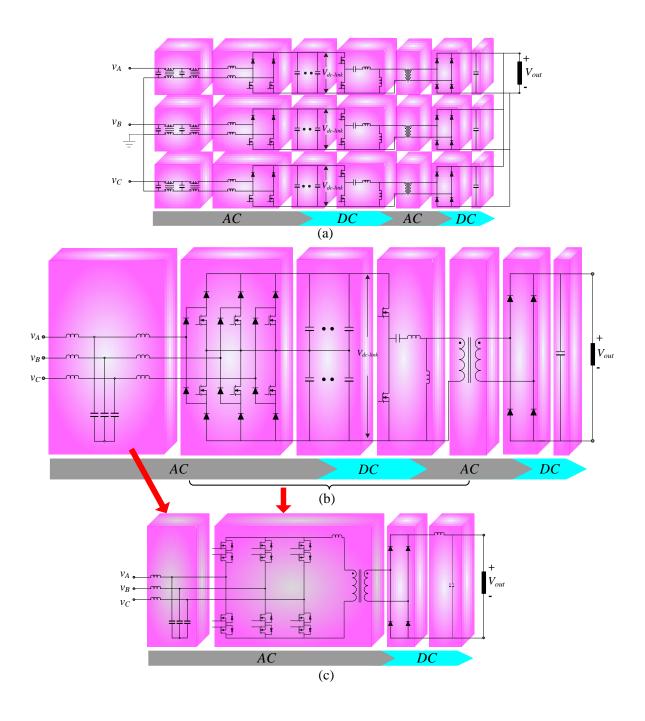

Fig. 1-7 Various configuration of PSUs with estimated power density in cubic block for data center and telecom applications: (a) single-phase module (bridgeless PFC + LLC) (b) direct three-phase (Vienna rectifier + LLC) (c) proposed single-stage PSU (isolated buck matrix-type rectifier).

#### **1.4.1 Single-Phase Modules**

Fig. 1-7 (a) shows three single-phase isolated AC-DC converters modules employed to implement an isolated three-phase, three-wire AC-DC converter. The single-phase isolated AC-DC module is a two-stage converter that consists of a PFC rectifier followed by an isolated DC-DC converter. The PFC rectifier can be a high frequency PWM rectifier of boost type to perform the PFC function to meet harmonic current standards [6]. The intermediate dc-link capacitor at the output of the PFC rectifier is to limit the bus voltage ripple due to the double grid frequency pulsating power and provide hold-up time. The DC-DC converter provides high frequency isolation, voltage scaling, and further output regulation [16]. LLC resonant topology [17] is commonly used for the second-stage isolated DC-DC converter. With advent of gallium-nitride (GaN) power semiconductor devices and SiC MOSFET, the efficiency and the power density of the two-stage converter can be significantly improved since the converter can operate at much higher switching frequency with minimum switching losses. Recently, the totem-pole bridge-less PFC rectifier with GaN implementation [18-19], has become a popular solution for application like front-end converter. The efficiency higher than 99% can be achieved with the CRM Totempole bridge-less PFC using GaN devices while the converter is switched at megahertz. A twostage single-phase 3 kW module with 54 V output is demonstrated with 98% peak efficiency and close to 60 W/in<sup>3</sup> power density in today's power supply market [20].

However, the two-stage single-phase module exhibits some drawbacks as highlighted in below. One of the drawbacks is that, regardless of hold-up time requirement, the two-stage power converters are enforced large intermediate dc-link capacitors to limit the bus voltage ripple and handle the pulsating power in single phase module. As shown in Fig. 1-7 (a) the intermediate dc-link capacitors usually occupy more than 20% of the volume of the PSU with today's power density of 60 W/in<sup>3</sup>. With increasing switching frequency in the range of MHz, the magnetics components get smaller in size and it is expected the power density of single-phase module PSU exceeds three times of today's market in the future. This indicates that the space inside the PSU will be dominated by the bulky dc-link capacitors which cannot be avoided due to pulsating power operation. In addition, the pulsating capacitors make the PCB layout and packaging to be more difficult for high-power-density PSU since these capacitors must be placed

on the main PCB of PSU. Therefore, the thermal cooling is more challenge for major power components in the PSU such as switching power devices, heatsink and magnetic components as a result of the fan airflow blocked by these bulky capacitors.

In standard telecom power supplies, where the source neutral point is not provided, any unbalance in the three-phase source phase voltages and/or in the three single-phase modules shown in Fig. 1-7 (a) will create a potential difference between the Y point of the single-phase modules and the source neutral point, resulting in oscillations and significant variations of the input voltages of the single phase converters [15]. Therefore, a balancing control of the three single-phase modules is necessary for a stable and reliable steady-state operation, where the input voltage always stays within a specified range. The balancing control between the three single-phase modules can be achieved with additional passive components used to create a virtual (artificial) neutral point and by using balancing control methods [21-25], or without additional passive components by using only balancing control methods [26].

#### 1.4.2 Direct Three-Phase

A significant breakthrough in simplifying the single-phase modules was achieved by three-phase PFC rectifiers as shown in Fig. 1-7 (b). Three-phase isolated AC-DC converters can be implemented with a direct three-phase PFC rectifier front end such as Vienna [27] or six-switch boost PFC rectifier [28] followed by an isolated DC-DC converter. With direct three-phase rectifier, the three-phase load balancing can be achieved automatically. The Vienna rectifier does not require a large bus capacitance because the three-phase input voltages eliminate the pulsating power in the dc-link. As a result, the amount of bus capacitance in the Vienna rectifier is reduced with respect to the single-phase PFC approach. Another advantage of this rectifier is that the voltage stress across the switches are subject to only half of the total bus voltage, thus allowing 500 V MOSFETs to be used in the VIENNA rectifier. Despite the power stage simplification achieved by the Vienna rectifier, the power density of direct three-phase rectifier is normally lower than the single-phase modules. Because the three-phase PFC converter in the first stage is usually hard switched and the converter cannot operate at very high switching frequency which

results in large size of input chokes. It is also noteworthy to mention the \$/kW with direct three-phase solution is relatively higher than single-phase module PSUs.

#### 1.4.3 Isolated DC/DC Converter in Second-Stage

The LLC resonant converters have been widely used as the isolated DC-DC converter in the second-stage in off-line power supplies of data centers due to its high efficiency and hold-up capability. Using LLC converters can minimize switching losses and reduce electromagnetic interference. Almost all the high-end offline power supplies employ LLC converters as the DC-DC converter. But there are few major challenges and limitation in using LLC converters. Generally, the detrimental effect of wide input and/or output voltage range on the conversion efficiency is more severe in resonant converters than in pulse-width-modulated (PWM) converters. LLC resonant converter regulates the output voltage by changing the switching frequency, i.e., by moving the operating point away from the resonant frequency as the input voltage and/or output voltage changes.

As a result, they suffer from progressively increased losses as the input- and/or output-voltage range is widened. This is the major reason LLC resonant converter, is not able to maintain high efficiency across the entire range when input voltage or output-voltage range is wide [29]. This significantly limits the power handling of LLC converter for constant power and constant current operations, since the output voltage relatively needs to be changed under these operations.

# 1.4.4 Proposed Single-Stage PSU for PDS in Telecom and Data center Applications

It is of paramount importance to minimize the cost of components, design complexity, to eliminate the bulky dc-link capacitors and at the same time realizing high efficiency and high power density PSU by choosing a reasonable converter topology.

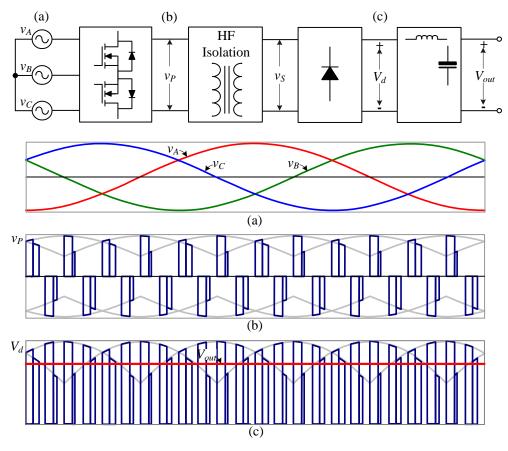

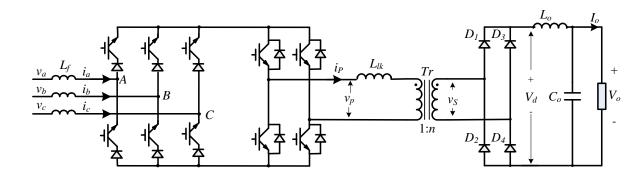

Fig. 1-8 Three-Phase high-frequency isolated matrix-type rectifier.

Fig. 1-9 An example of proposed PSU in configuration with separated battery charger and diode in 380V DC PDS.

Since conversion efficiency and total volume of the PDS in telecom and data center depend largely on the front-end PSU performance. Therefore, we are highly motived to study possibility of different topology which can be adopted for future PSU in telecom and data center applications. The advantage of performing PFC functionality and galvanic isolation in a single-stage conversion make the isolated single-stage topology to be considered as an attractive solution for the future front-end PSU in telecom and data center applications. Typically, the single-stage power conversion directly converts the mains-frequency AC voltage into a high-frequency AC voltage which is supplied to a high-frequency isolation transformer whose secondary voltage is then rectified to the desired DC output voltage as shown in Fig. 1-8 [30-31].

High conversion efficiency and compact construction stemming from the non-existence of an intermediated dc-link capacitors and the second stage DC-DC conversion can be achieved. Improved lifespan due to elimination of the bulky and often trouble-causing dc-link component is another benefit of using single-stage approached PSU. With single-stage approached PSU, the rack can be greatly simplified in PDS. The storage energy capacitors at the output of PSU can be placed outside of the PSUs as shown in the example of Fig. 1-9. This provides tangible benefits in the form of space saving, and better airflow for front-end PSUs which result in higher power density and smaller fans.

However, there have always been some concerns about employing single-stage PSU in telecom and data center applications such as continuous operation of single-stage PSU during faulty mode one phase loss and hold-up time requirement during input AC source drop out. Regarding the first concern, the single-stage PSU is able to deliver continuous power to the ICT load during one phase loss operation, but the DC bus (output of PSU) may contain output voltage ripple at double of the line frequency as shown in Fig. 1-9. The configuration of battery backup system in Fig. 1-9 is similar to the NTT solution described in Fig. 1-3 (c). In this example, the battery voltage set point is lower than DC bus voltage such that the battery will not be engaged in one phase loss operation. However, the downstream PSU in ICT equipment has to be able to operate at wide input range, which is normally true in real application, in order to take into account the DC bus voltage variation. Likewise, the hold-up time requirement can also be met thanks to the wide input range of the PSU in ICT equipment. By selecting reasonable small size

of storage energy at the output of PSU, the DC bus can ramp down with small slew rate and provide a few millisecond hold-up time within the range of input voltage of the first-stage (DC-DC converter) in ICT equipment when the power outage is occurred as shown in Fig. 1-9.

It is also important to note that, during one phase loss operation, the single-stage PSU for battery charger will exhibit different charging behavior. Prior to time  $t_{fault}$  (normal operation), the output voltage of the charger is tightly regulated and the battery is in floating state. After  $t_{fault}$  (during one phase loss), the charger output voltage may contain ripple which results in discontinuity of the float charging current of battery. However, this may not harm the battery since the battery consumes very small charging current during float state.

### 1.5 Topology Overview of Single-Stage Isolated Three-Phase Rectifiers

The power stage design clearly depends on the converter circuit topology. Therefore to achieve a high-efficiency and high-density design, it is a logical and necessary step to carry out the systematic design and evaluation for the topologies that meet the application requirements, and select among them the most suitable candidate. Several novel single-stage isolated threephase rectifier topologies such as buck, boost, buck-boost, flyback/forward, and buck and boost matrix-type have been reported in [32-34]. In [35], an isolated single-stage (boost) topology is presented based on a two-switch three-phase rectifier. This topology is easy to control and it operates in discontinuous conduction mode (DCM). Thus it shows higher RMS current which can be useful for high frequency low-medium power application. An isolated single-stage Swiss-Forward (buck) topology is proposed in [36], showing lower number of high frequency transistors but higher voltage stress on semiconductors because of the forward structure. In addition, a single-stage three-phase AC-DC converter with high frequency isolation-could be also realized by the Cuk-based or SEPIC-based single-switch converters as proposed in [37-39] or single-switch three-phase flyback converters as proposed in [33]. These converters show a very simple structure of the power and control circuits which is paid for, however, by a high voltage and current stress on the devices and by a relatively high filtering effort for suppressing

electromagnetic interferences (discontinuous input current shape). The systems are economically applicable, therefore, only for output power levels below 3.5 kW and/or they are of minor importance for the realization of high power, high efficiency and high power density converter needed for PDS in telecom and data center applications.

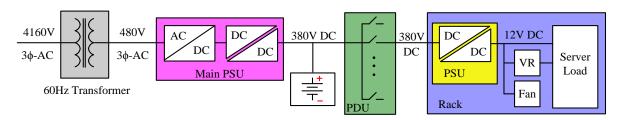

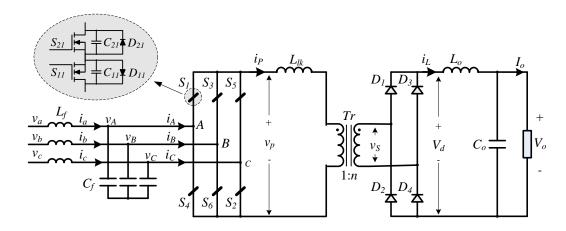

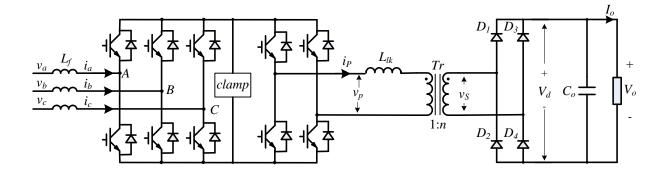

For higher power (≥ 3.5 kW), the single-stage isolated matrix-type rectifiers are the most favorable in terms of high power density and high efficiency [30, 32, 34] and [40-42]. These single-stage isolated matrix-type rectifiers can be classified into four major categories as shown in Fig. 1-10 (a) buck derived indirect matrix-type rectifier; (b) buck derived matrix-type (direct matrix) rectifier; (c) boost derived indirect matrix-type rectifier; (d) boost derived matrix-type (direct matrix) rectifier.

(a) Buck derived indirect matrix-type rectifier.

(b) Buck derived matrix-type (direct matrix) rectifier.

(c) Boost derived indirect matrix-type rectifier.

(d) Boost derived matrix-type (direct matrix) rectifier

Fig. 1-10 Basic structures of isolated matrix-type three-phase rectifiers.

### 1.5.1 Boost Derived Indirect and Direct Matrix-Type Rectifiers

The structures in Fig. 1-10 (c) and (d) are of boost derived indirect and direct matrix-type rectifiers. As shown in Fig. 1-10 (c), the boost derived indirect matrix-type rectifier is quite similar to the two stage PWM rectifier with a three-phase boost rectifier as an AC-DC stage and a full-bridge converter as a DC-DC stage. Due to the still missing intermediate energy storage, it is called indirect matrix-type PWM rectifier. The front end of boost derived matrix-type (direct matrix) rectifier in Fig. 1-10 (d) has a similar structure of a three-phase boost rectifier. However, all the six active switches are bidirectional for matrix-type and operating in DCM.

It is also observed that the boost derived indirect and direct matrix-type rectifiers are not strong candidate for PDS in telecom and data center applications, since the facility-level PDS is powered from the three-phase  $(400\text{V}/480\text{V}) \pm 10\%$  with the mentioned output voltage of 380 V or 54 V the boost-type PFC rectifiers may not be suitable. The main reasons can be highlighted as follows:

- High Voltage stress may require clamping: the DC output voltage of boost-type PFC rectifiers has to be at least 15% above the peak value of the mains line-to-line voltage; thus, with a wide input voltage range up to (480 V<sub>rms</sub>) ±10%, the output voltage is typically selected to be 850 V DC in ideal case. If the effect of the leakage inductance of the transformer is considered, the device voltage will be well above 1.2 kV. Therefore, the voltage clamping is required, which will increase the losses and complexity of the converter.

- Low Power Density: ZCS operation can be achieved with boost matrix-type rectifiers. ZCS is usually employed to alleviate the turn-OFF losses of devices that possess slow turn-OFF such as IGBT. However, Si IGBT devices cannot operate at high switching frequency due to the large turn-ON losses. As a result, the input boost inductors need to be to design with larger size.

- **High RMS current:** at the medium power levels considered in this study (5 kW), DCM converters are not appropriate because they have high RMS currents in the semiconductor devices, inductor and the transformer windings which result in high conduction losses.

Due to aforementioned drawbacks, boost derived indirect and direct matrix-type rectifiers will not be discussed further in this dissertation.

### 1.5.2 Buck Derived Indirect and Direct Matrix-Type Rectifiers

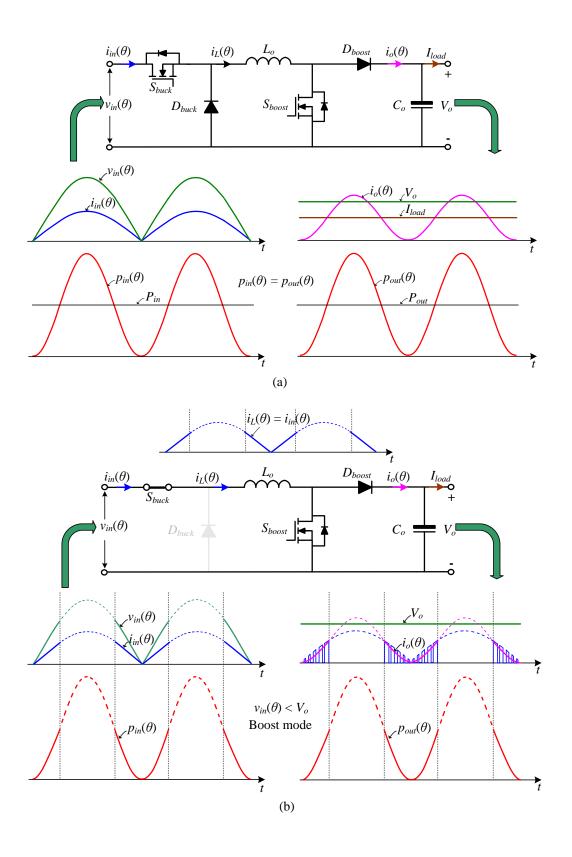

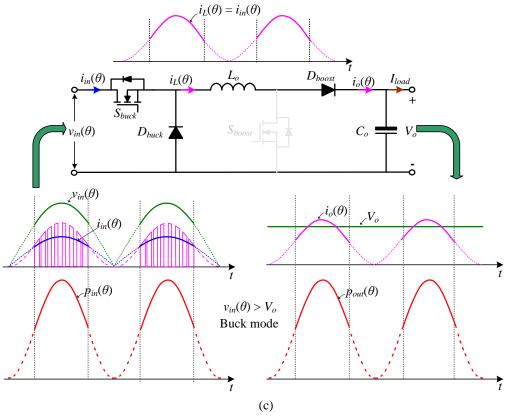

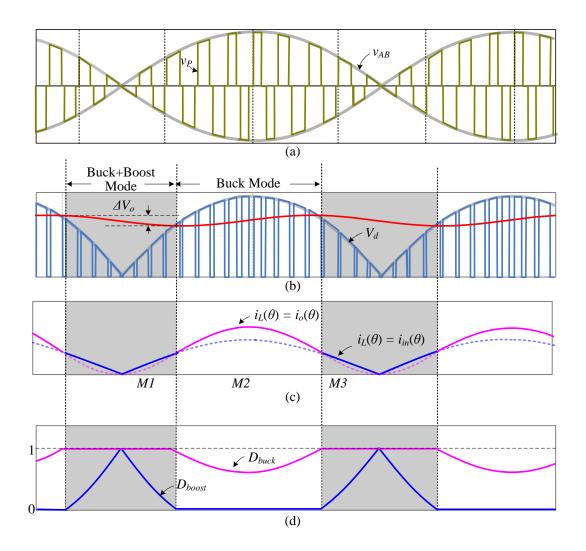

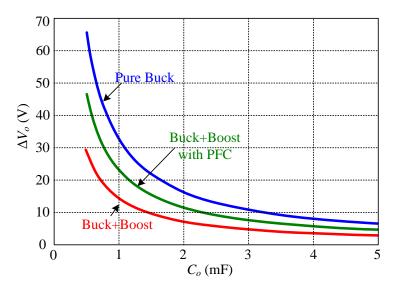

In the case of buck derived indirect matrix-type rectifier in Fig. 1-10 (a), the first-stage is buck type three-phase rectifier and the second-stage can be applied any high-frequency DC-DC converters. As proposed in [30, 32] a conventional buck-type PFC rectifier in combination with a phase-shift DC-DC converter or LLC resonant converter could be used. However, the