b 18813469

## DIRECT VOLTAGE CONTROL FOR STAND-ALONE WIND ENERGY CONVERSION SYSTEMS WITH ENERGY STORAGE

by

#### **WEI HUANG**

BSc, Huazhong University of Science and Technology, China, 2005

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Canada © Wei Huang 2008

PROPERTY OF

RYERSON UNIVERSITY LIBRARY

#### **ABSTRACT**

Direct Voltage Control for Stand-alone Wind Energy Conversion Systems with Energy Storage

Wei Huang

**Electrical and Computer Engineering**

**Ryerson University**

#### Toronto 2008

A control method for the stand-alone wind power generation system with induction generator and energy storage devices is proposed in this thesis. A fixed-speed self-excited induction generator is directly connected to the standalone power system, while battery powered energy storage devices are employed to balance the system power flow. A DC-AC power converter is connected between the energy storage device and the standalone power system, which maintains the voltage and frequency constant. Direct voltage control with current limits is developed for the converter with dynamic fast response. Mathematical models are developed to analysis the system performance as well as to design the lead-lag regulators in the control system. The proposed system is verified in the simulation and experiment.

#### **ACKNOWLEDGMENTS**

I wish to express my deep gratitude to my supervisor, Professor Dewei Xu for his support and the knowledge he shared during my graduate studies at Ryerson University.

I am grateful to Professor Bin Wu, Professor Richard Cheung, Dr. Yongqiang Lang, and all fellow students at LEDAR for their useful discussions on my research.

I also wish to share my achievements with my families and my wife Wei Li. I am very grateful for her understanding and support.

## TABLE OF CONTENTS

| CHA | PTER  | 1 INTRODUCTION                                   | 1    |

|-----|-------|--------------------------------------------------|------|

| 1.1 | Win   | d Energy Conversion System                       | 1    |

| 1.2 | Stan  | nd-alone Wind Energy Conversion System           | 4    |

| 1.3 | Mot   | ivation and Objective                            | 7    |

| 1.4 | The   | sis Outline                                      | 8    |

| СНА | PTER  | 2 MODEL DEVELOPMENT FOR THE STANDALONE WECS      | 5 10 |

| 2.1 | Intr  | oduction                                         | 10   |

| 2.2 | Win   | d Turbine Characteristic                         | 11   |

| 2.3 | Indu  | ıction Generator Model                           | 12   |

| 2.4 | Indu  | ıctive Load and Self-Excitation Capacitor Model  | 15   |

| 2.5 | Ene   | rgy Storage System Model                         | 15   |

| 2.6 | Stan  | dalone WECS Model                                | 16   |

| 2.7 | Sma   | ll Signal Model                                  | 17   |

| 2.8 | Con   | clusions                                         | 20   |

| СНА | PTER  | 3 CONTROL OF STANDALONE WECS                     | 21   |

| 3.1 | Intr  | oduction                                         | 21   |

| 3.2 | Dire  | ct Voltage Control                               | 22   |

|     | 3.2.1 | Voltage and Frequency Control                    | 22   |

|     | 3.2.2 | Direct Voltage Controller Design                 | 23   |

| 3.3 | Con   | clusions                                         | 28   |

| СНА | PTER  | 4 SIMULATION AND EXPERIMENTAL RESULTS            | 29   |

| 4.1 | Intro | oduction                                         | 29   |

| 4.2 | Sim   | ulation Model                                    | 30   |

| 4.3 | Sim   | ulation Results                                  | 32   |

|     | 4.3.1 | Non-ESS Stand Alone Wind Power Generation System | 32   |

|     | 4.3.2 | Simulation Results with ESS                      | 33   |

| 4.4 | Exp   | erimental Setup                                  | 37   |

| 4.5 | Exn   | erimental Results and Analysis                   | 40   |

|     | 4.5.1  | Resistive Load Test   | 40 |

|-----|--------|-----------------------|----|

|     | 4.5.2  | Inductive Load Test   | 44 |

| 4.6 | Con    | clusions              | 48 |

| СНА | PTER   | 5 CONCLUSIONS         | 49 |

| 5.1 | Con    | iclusions             | 49 |

| 5.2 | Maj    | or Contributions      | 50 |

| 5.3 | Fur    | ther Research Works   | 50 |

| REF | EREN   | CES                   | 52 |

| APP | ENDIC  | CES                   | 55 |

| Ap  | pendix | A Simulation Models   | 55 |

| Ap  | pendix | B System Parameters   | 56 |

| Ap  | pendix | C Code for Bode Plots | 57 |

|     | _      | D DSP Program Code    |    |

## LIST OF TABLES

| Table 3-1: Parameters of the Lab Prototype System | . 25 |

|---------------------------------------------------|------|

| Table 3-2: Parameters of lead-lag Controller      | . 27 |

| Table 4-1: System parameters of prototypes system | . 31 |

| Table B-1 Parameters of DC Motor                  | . 56 |

| Table B-2: System Parameters of Prototypes System | . 56 |

## LIST OF FIGURES

| Figure 1-1: Typical diagram of wind energy conversion systems                                        | 2  |

|------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: Constant-speed wind energy conversion systems                                            | 2  |

| Figure 1-3: Typical configurations of variable speed wind energy conversion systems                  | 3  |

| Figure 1-4: Schematic of general wind-diesel system                                                  | 5  |

| Figure 1-5: Proposed wind energy conversion system                                                   | 8  |

| Figure 2-1: Proposed wind energy conversion system                                                   | 10 |

| Figure 2-2: Variables in three-phase $(abc)$ stationary frame and two-phase $(dq)$ synchronous frame | 13 |

| Figure 2-3: Induction generator equivalent circuits under synchronous reference frame                | 14 |

| Figure 2-4: Energy storage system circuit                                                            | 16 |

| Figure 2-5: d-q Equivalent circuits in synchronous reference frame                                   | 17 |

| Figure 2-6: Small signal model for d-q equivalent circuits in synchronous reference frame            | 20 |

| Figure 3-1: Control block diagram of the whole system                                                | 21 |

| Figure 3-2: Block diagram using transfer functions                                                   | 22 |

| Figure 3-3: System blocks model in S- domain                                                         | 24 |

| Figure 3-4: Bode plots of uncompensated loop                                                         | 25 |

| Figure 3-5: Bode plots of uncompensated loop with different loads                                    | 26 |

| Figure 3-6: Bode plot of compensated loop gain                                                       | 27 |

| Figure 4-1: Block diagram of experimental set-up                                                     | 29 |

| Figure 4-2: System models of proposed WECS                                                           |    |

| Figure 4-3: Direct voltage controller model                                                          | 31 |

| Figure 4-4: Wind power generation system without ESS                                                 | 32 |

| Figure 4-5: System voltage and frequency without ESS                                                 | 32 |

| Figure 4-6: Local bus voltage and frequency during load step change (with R Load) in Simulation      | 33 |

| Figure 4-7: d-q axis inverter voltage during load step change (with R Load) in Simulation            | 34 |

| Figure 4-8: d-q axis inverter current during load step change (with R Load) in Simulation            | 34 |

| Figure 4-9: Current waveforms during load step change (with R load) in simulation                    | 35 |

| Figure 4-10: Voltage and frequency during load step change (with RL load) in simulation              | 36 |

| Figure 4-11: Currents waveforms during load step change (with RL load) in simulation                 | 36 |

| Figure 4-12: d-q axis inverter voltages during load step change (with RL Load) in Simulation         | 37 |

| Figure 4-13: d-q axis inverter currents during load step change (with RL Load) in Simulation         | 37 |

| Figure 4-14: Experimental setup                                                                      | 38 |

| Figure 4-15: DSP controller board                                                                    | 39   |

|------------------------------------------------------------------------------------------------------|------|

| Figure 4-16: Steady-State waveforms with resistive load                                              | 41   |

| Figure 4-17: Transient waveforms of local bus voltage and load current during load step change       | 42   |

| Figure 4-18: Transient waveforms of generator and converter currents during load step change (with l | R    |

| Load)                                                                                                | 43   |

| Figure 4-19: d-q axis Inverter side current during load step change (with R Load)                    | 44   |

| Figure 4-20: Steady-State voltage and current waveforms with RL load                                 | 45   |

| Figure 4-21: Transient waveforms of local bus voltage and load current during load step change (with | ı RL |

| load)                                                                                                | 46   |

| Figure 4-22: Transient waveforms of currents of generator and inverter during load step change (with | RL   |

| load)                                                                                                | 46   |

| Figure 4-23: d-q axis Inverter side current and voltage during step load change (with RL Load)       | 47   |

| Figure 4-24: d-q axis Inverter current during step load change with compensation (with R-L Load)     | 47   |

| Figure A-1: Simulink model of WECS                                                                   | 55   |

| Figure A-2: Direct voltage controller model                                                          | 55   |

## LIST OF PRINCIPAL SYMBOLS

| ρ                      | Air density (kg/m³)                                               |

|------------------------|-------------------------------------------------------------------|

| A                      | Turbine swept area (m <sup>2</sup> )                              |

| $\mathcal{V}_{wind}$   | Wind velocity (m/s)                                               |

| λ                      | Tip speed ratio of the blade tip speed to wind speed              |

| β                      | Blade pitch angle (deg)                                           |

| $P_m$                  | Mechanical output power of the turbine (W)                        |

| $\omega_e$             | Angular electrical speed                                          |

| $\omega_r$             | Angular rotor speed                                               |

| $T_e$                  | Electrical torque of the induction machine                        |

| $i_{ds}(t), i_{qs}(t)$ | Stator side current of induction generator in d-q reference frame |

| $i_{dr}(t), i_{qr}(t)$ | Rotor side current of induction generator in d-q reference frame  |

| $v_{ds}(t), v_{qs}(t)$ | Local bus terminal voltage in d-q reference frame                 |

| $v_{dr}(t), v_{qr}(t)$ | Rotor side voltage of induction generator in d-q reference frame  |

| $i_{Cd}(t), i_{Cq}(t)$ | Self-excited capacitor current in d-q reference frame             |

| $v_{ld}(t), v_{lq}(t)$ | Load voltage in d-q reference frame                               |

| $i_{1d}(t), i_{1q}(t)$ | Load current in d-q reference frame                               |

| v(t)                   | Converter output voltage                                          |

| i(t)                   | Converter output current                                          |

| $E_s$                  | Ideal voltage source representing the energy storage devices      |

| L                            | Inductance of converter side filter             |  |

|------------------------------|-------------------------------------------------|--|

| C                            | C Capacitance of self-excited capaciton         |  |

| $f_{\it ref}$                | $f_{ref}$ Reference frequency for the local bus |  |

| $v_{ref}$                    | Reference voltage for the local bus             |  |

| v                            | Converter-side feedback voltage                 |  |

| $T_s, f_s$                   | Sampling period, sampling frequency             |  |

| $G_{c0}$                     | Gain of the lead-lag regulator                  |  |

| $T_i, T_z, T_p$              | Time constant of lead-lag regulator             |  |

| $K_{\scriptscriptstyle PWM}$ | Gain of the PWM converter                       |  |

| $m_a$                        | Modulation index of the converter               |  |

## Chapter 1 Introduction

Currently the world's energy consumption is greatly dependent on exhaustible fossil fuel, which is also main source contributing the green house gas and pollution to the environment. In this perspective, utilization of renewable energy, such as wind and solar energy, has gained considerable momentum since the oil crises of the 1970s. Wind power, as one of the alternative energy options, is gaining increasing significance throughout the world. Wind energy is non-depleting, site-dependent, non-polluting, becoming the most promising energy source for the future. Large and grid tired wind energy conversion system has been widely installed in many countries, in the effort to minimize the dependence on fossil based non-renewable fuels [1]. Wind energy has experienced accelerated expansion in recent years and its global production is predicted to grow from 60,000 MW in 2005 to 300,000 MW in 2015 [2].

#### 1.1 Wind Energy Conversion System

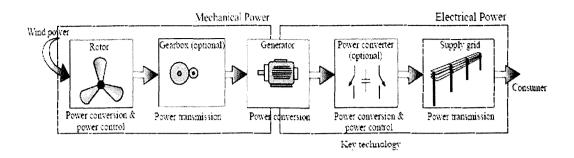

A basic wind energy conversion system (WECS) consists of a wind turbine with tower, gearbox, generator, power converter and control system, as shown in Figure 1-1[3]. There are two types of wind turbines used in practice: vertical wind turbine and horizontal wind turbine according to the rotating of the blades. Most modern wind turbines are horizontal type with two or three blades due to higher efficiency and higher power capability.

Figure 1-1: Typical diagram of wind energy conversion systems

WECS can also be classified into two types of the systems according to its operation: constant speed or variable speed operation systems. Fix speed WECS operate at a nearly fix speed while variable speed system adjusts its rotor speed according to different wind speed. Generally variable speed system extracts more wind energy (10-15%) than the fixed speed system.

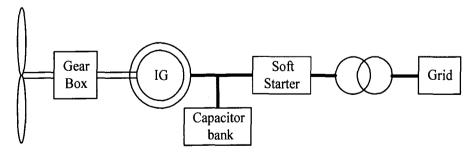

A constant speed WECS usually contains a squirrel cage induction generator, as shown in Figure 1-2. Gearbox is necessary for the coupling of the low speed wind turbine and the high speed induction generator. SCR controlled starter between the generator and the grid aims at reducing the inrush current during connection to the grid. In normal operation, induction generator absorbs reactive power. Capacitor bank provides the required reactive power for generator. If enough capacitor is provided, the generator can be self-excited, which is useful when grid is not available. The speed of the generator varies little when the power changes. Thus the speed is almost constant. Constant speed WECS is usually easier to built up and cost less than the variable speed WECS. But because of the fixed speed, the overall energy conversion efficiency is not high.

Figure 1-2: Constant-speed wind energy conversion systems

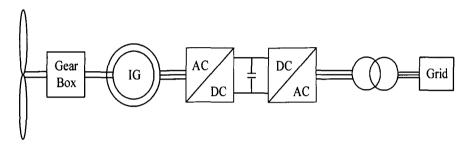

Variable speed configurations allow the rotor to rotate at required speed by introducing power electronic converters between the generator and the grid. Wind turbine system can operate at its optimum tip-speed ratio[4]. Thus more energy can be converted into electricity. Double-fed induction generators (DFIG), wound field synchronous generators and permanent magnet synchronous generators are three typical generators used in high power WECS. For medium and small power wind turbines, permanent magnet generators and squirrel cage induction generators are more often used because of their reliability and cost effectiveness. The typical configurations of variable speed WECS are shown in Figure 1-3[5].

(a) Inductor generator with full power converter

(b) Doubly-fed induction generator with fractional power converter

Figure 1-3: Typical configurations of variable speed wind energy conversion systems

Power converters are used to control the power flow between the wind turbine and grid when the variable frequency and variable voltage energy from generator is fed to the grid with fixed frequency and voltage. Most modern power converters are forced commutated PWM converters to provide a fixed voltage and frequency output with a high power capability. Both voltage source voltage controlled converters and voltage source current controlled converters have been

applied in wind energy applications. For certain high power wind turbines, effective power flow control can be achieved where real power and reactive power are independently controlled.

Most of the large wind energy conversion systems are grid connected. And many turbines are installed in a utility level wind farm with several hundred MW installed capacity. The prediction and power fluctuation are the main problem for the integration of wind farm to the grid. Many research efforts have been to solve these problems.

WECS sometimes can be used in the standalone power system in remote area where grid connection is not available. Hybrid system with battery, diesel generator and wind turbine/generator are connected together to provide a quality power to the load. The systems are often used in the small community; the capacity varies from several kilo-watts to hundreds of kilo-watt.

#### 1.2 Stand-alone Wind Energy Conversion System

Many remote communities around the world cannot be physically or economically connected to an electric power grid. The electricity demand in these areas is conventionally supplied by small isolated diesel plants. These have the advantage of being able to deliver the required power whenever it is necessary. However, they also suffer from a number of drawbacks. Diesel generator engines are inherently noisy and expensive to run, especially for consumers in rural areas where fuel delivery costs may be high. In addition, small consumers always have a low load factor; this in turn reduces the overall efficiency and increases percentage maintenance costs. Considerable fuel savings can be achieved by integrating renewable sources such as wind and/or solar energy with existing diesel plants.

However, many off-grid places are in regions of high wind energy potential. Wind energy is one of the most important and promising forms of renewable energy sources. Its use is becoming more and more popular nowadays. This is because the price of fossil fuels is continuously increasing and the wind energy is a clean and inexhaustible energy source. But due to great varia-

tion in wind speed which occurs from season to season, it can not be used as an autonomous source of generation. Hence, it is necessary to explore possibilities of combining a wind generator with the diesel generator in order to reduce the running cost per kWh and to increase the reliability of the power supply[6].

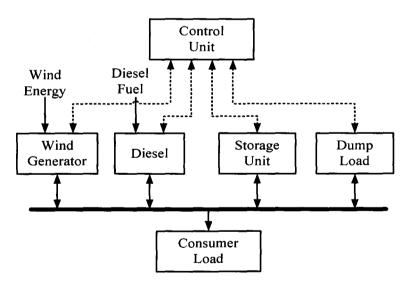

A schematic diagram of a wind-diesel system is shown in Fig. 1-4. A classic wind-diesel power system consists of the following components: one or more wind turbines, one or more diesel generators, consumer load, an additional controllable dump load, energy storage system and control unit[7]. In order to save the fuels cost, it is desirable to shut off the diesel generator(s) whenever possible. Energy storage system is used to compensate the fluctuation in the system coming from the wind fluctuation and to provide the short period energy during the diesel generator on or off periods. For the excess power from wind turbines, dump load will be used to resolve this problem.

Figure 1-4: Schematic of general wind-diesel system

From the configuration of wind-diesel power system, it obviously shows that wind-diesel hybrid system has its own problems. Power fluctuation issue is one of the most important issues. It is well known that the mechanical shaft power obtained from a wind turbine may be approximated by [8]:

$$P_{m} = \frac{1}{2} \rho \pi R^{2} C_{p}(\lambda, \beta) V^{3}$$

$$\tag{1-1}$$

where  $\rho$  is the air density,  $C_p(\lambda, \beta)$  is the power coefficient, R is the blade radius,  $\beta$  is the blade pitch angle,  $\lambda$  is the tip speed ratio and V is the effective wind speed respectively.

Equation (1-1) shows that small variations in the wind speed produce large changes in the captured power. These power fluctuations transferred to the output by the conversion system, including generator, power converter if existed, especially when the system is a fix speed system. For variable speed systems, part of the power fluctuation is absorbed as kinetic energy in the turbine. However, even for variable speed systems, power fluctuations can still be a serious problem if the generator is feeding a weak grid or a stand-alone load. For these applications, the wind turbine is augmented by an additional source, usually a diesel generator. In such hybrid systems, wind speed fluctuations not only produce fluctuations in the generator output voltage, but also an unacceptable number of start/stop cycles of the diesel generator if a temporary energy buffer is not available.

In [11-14], flywheel energy storage device is used as energy storage system to smooth the fluctuations in the wind-diesel system when the energy storage system is needed. Papers [11, 12] suggest that use vector control to control the induction machine to drive the flywheel system. [13] also shows a new sensorless field oriented control method to drive the induction machine. Almost all the control methods are based on the front-end converter. There are other papers [15-17] using battery bank or super-capacitor as the energy storage devices. The different kinds of energy storage device have its own advantages and disadvantages. Battery is a cost effective solution which is widely used in the energy storage system. But it has a high maintenance cost and low cycle life. Super-capacitor is a new energy storage device with much higher life but the capacity is low.

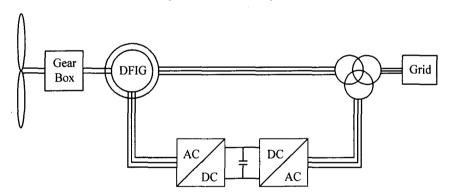

In [9, 10], sensorless control for double-fed induction generator in stand-alone system are presented. For the Doubly-fed induction generator, sensorless operation is desirable because the use of a position encoder has several drawbacks in term of robustness, cost, cabling and mainte-

nance. Most of the sensorless control methods are all based on the principle of rotor position observers using the rotor current error. For DFIG, itself can regulate the output voltage and the frequency regardless of the load and rotational speed. Batteries, as the energy storage devices, are integrated into the dc link of back-to-back converter for the DFIG, which enhance the system performance by expanding the operation range.

#### 1.3 Motivation and Objective

Based on the configuration of the stand-alone system presented in the previous sections, the typical system consists of wind turbine, diesel engine, energy storage system and control part. In this project, the induction generator is used to be the wind turbine generator. For a small scale wind-diesel wind power system, squirrel cage induction generator is a better choice when cost and reliability are the first two considerations. As long as the energy storage devices are always need, a fixed-speed self-excited induction generator has its own advantages including cost, robustness and reliability can be used in the stand-alone system. The fluctuation in the power from the wind can be smoothed by the energy storage system with an appropriate controller.

As presented in the former section, many researches have been done on doubly-fed induction generator control. It usually uses a fractional size back-to-back converter to control the active power and reactive power to keep the constant voltage and frequency. And the controller usually contains two control loops to regulate the voltage and frequency. For a doubly-fed generator based system, the control of system voltage and frequency are very complicated since it is coupled by the control of induction generator's speed and torque.

Most of the control strategies for power balance controlling in the stand-alone system contain two cascaded loops: voltage loop and frequency loop, which based on the assumption that frequency loop is usually slower than the voltage loop. In these control systems, the dynamic response of grid voltage sometimes is not satisfied when the load is light.

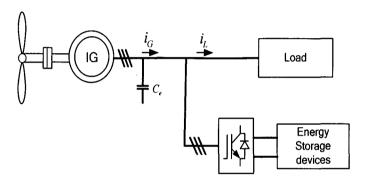

In this thesis, the induction generator with self-excitation capacitor is directly connected to the standalone power system, as shown in Fig.1-5. The energy storage system (ESS) is employed to maintain the system frequency as well as voltage at collect bus. It supplies or absorbs the fractional power of the system, and keeps the system power flow balanced. When the wind energy is not enough for a long period, the back-up generators including diesel generator should be turned on to provide the rest of the energy. The renewable energy converters in the system are maintained at highest efficiency with the employed ESS, which reduces the energy consumption from diesel generators, reduces system operation cost as well as the greenhouse gas emission and pollution to the environment.

Figure 1-5: Proposed wind energy conversion system

Therefore, the main objectives of the thesis are:

- 1. Design a suitable controller for converter, which smooth the power fluctuation of wind energy conversion system.

- 2. Develop mathematical models for the system with induction generator and energy storage converter. This model will be used in the controller design.

- 3. Conduct variety of experiments to verify the performance of the developed control system.

#### 1.4 Thesis Outline

This thesis is organized to provide the detailed information about the research work on standalone wind energy conversion system with induction generator and energy storage devices in five chapters. This chapter, chapter 1 presents the background of wind energy conversion systems, including the configurations, operation and grid connection. Standalone power system with integrated wind energy is introduced. Research motivation is discussed in this chapter.

Chapter 2 presents the development of mathematical model for each component in the standalone system with wind turbine and energy storage devices. The model is developed in the d-q reference frame. Finally the whole system model is developed.

Chapter 3 presents the direct voltage controller design for standalone WECS. Small signal model of wind energy power system is developed, followed by theoretical analysis of the control scheme with dump load and current protection. The diagram of controller scheme is discussed.

Chapter 4 shows all the simulation models for different components in Matlab/Simmulink. The simulation results are also given in this chapter. Experimental results are provided to compare with simulation.

Chapter 5 presents the conclusions of the thesis, major contributions and future work are discussed later.

All other relevant supporting materials are attached in appendices.

# Chapter 2 Model Development for the Standalone WECS

#### 2.1 Introduction

The diagram of the proposed wind energy conversion system is shown in Fig. 2-1. The electrical part consists of the induction generator with self-excitation capacitors, the energy storage devices with power converter, consumer load and dump load.

Figure 2-1: Proposed wind energy conversion system

In the system, self-excitation capacitors are needed to provide sufficient reactive power to the induction generator, which reduce the reactive power consumption from the power converter. It is assumed that the wind turbine is properly selected, which can provide most of the energy to the load. Thus the power converter and energy storage devices only provide fractional power to maintain the power balance between generator and load. In the system, the dump load will be connected to absorb these extra powers from induction generator. The dump load can be represented additional resistor. In the practical industry application, most of the energy storage devices usually can only store or supply limited power. So a back-up generator is essentially re-

quired if continuous power flow is required. In this thesis, energy storage devices are treated as an ideal voltage source. Different characteristics of the batteries are not the main research focus. Battery management is also not a consideration in this thesis.

Power fluctuation in the standalone system is one of the most common problems. Before deriving a solution for the controller, it is imperative to produce a comprehensive mathematical model of the whole electrical system that can be used in the controller design. The following sections provide different part mathematical models and the whole system model is presented in the last section.

#### 2.2 Wind Turbine Characteristic

Generally, the wind turbine systems can be classified according to their aerodynamic configuration, transmission design and their operational speed range. Further classification can be performed based on the power output, the generator types, grid connection, etc.

The aerodynamic configuration divides the wind turbines in two main categories: the horizontal axis wind turbine (HAWT) and vertical axis wind turbine (VAWT). Due to reasons of mechanical resonance, efficiency and size more than 95 percent of the currently operating wind turbine designs are HAWT. The choice of this configuration has one major disadvantage that the main components of the energy conversion system such as generator, gearbox, pitch control mechanism, the power converter and the grid-interface device, have to be located in the nacelle of the turbine. This leads to the increased demands on the stability, strength and cost of the support structure.

Regardless of the aerodynamic configuration of the wind turbine, its absolute maximum power extraction efficiency is restricted by the Betz limit of 59.3 percent.

The mechanical power extracted from the wind is mainly governed by three quantities namely, the area swept by rotor blades, the upstream wind velocity and rotor co-efficient.

$$P_{m} = \frac{1}{2} \rho \pi R^{2} C_{p}(\lambda, \beta) V^{3}$$

$$\tag{2-1}$$

Cp, the power coefficient of rotor, itself is a function of tip speed ratio and pitch angle. A typical coefficient of the wind turbine is given at  $0^{\circ}$  pitch angle. The optimal Cp is only possible at certain speed ratio. Yet, it is not always possible to maintain zero blade pitch, because it would create unwanted output fluctuations as well as greatly increase the electrical and mechanical load on the whole system when the wind is too strong. In order to partially cure this problem, the pitch control mechanisms (or stall control) are installed to regulate the position of the blades and maintain the highest possible power the system can deliver.

#### 2.3 Induction Generator Model

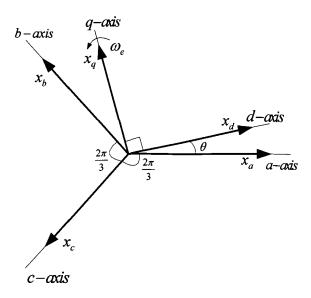

The use of reference frame theory can simplify the analysis of electric machines and also provides a powerful tool for the digital implementation of sophisticated control schemes. The synchronous reference frame is one of the most commonly used in the research and application. The transformation of the three-phase (abc-axis) variables of an induction motor to the equivalent two-phase (dq-axis) variables can be performed by[19].

$$\begin{bmatrix} x_d \\ x_q \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos \theta & \cos(\theta - 2\pi/3) & \cos(\theta - 4\pi/3) \\ -\sin \theta & -\sin(\theta - 2\pi/3) & -\sin(\theta - 4\pi/3) \end{bmatrix} \cdot \begin{bmatrix} x_a \\ x_b \\ x_c \end{bmatrix}$$

(2-2)

where x represents either current, voltage, or flux linkage, and  $\theta$  is the angular displacement between the a-axis and d-axis of the three-phase and two-phase reference frames as shown in Fig. 2-2. The three-phase variables,  $x_a$ ,  $x_b$  and  $x_c$ , are in the stationary reference frame which does not rotate in space whereas the two-phase variables,  $x_d$  and  $x_q$ , are in the synchronous reference frame whose direct (d) and quadrature (q) axes rotate in space at the synchronous speed  $\omega_e$ . Note that  $\omega_e$  is the angular electrical speed of the rotating magnetic field of the motor, given by

Figure 2-2: Variables in three-phase (abc) stationary frame and two-phase (dq) synchronous frame

$$\omega_e = 2\pi f_s \tag{2-3}$$

where  $f_s$  is the frequency of the stator variables. The angle  $\theta$  can be found from

$$\theta(t) = \int_0^t \omega_e(t)dt + \theta_0 \tag{2-4}$$

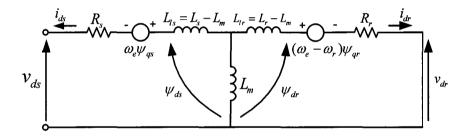

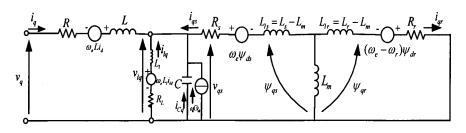

In order to model the induction generator, the d-q equivalent circuit of induction machine is obtained. Refer all the variables of rotor side to stator side, following equations can be obtained by using Clark-Park transformation. The corresponding equivalent circuits are shown in Fig. 2-3.

$$v_{ds} = -R_s i_{ds} + \frac{d\psi_{ds}}{dt} - \omega_e \psi_{qs}$$

(2-5)

$$v_{qs} = -R_s i_{qs} + \frac{d\psi_{qs}}{dt} + \omega_e \psi_{ds}$$

(2-6)

Where:

$$\psi_{qs} = -L_{ls}i_{qs} - L_m(i_{qr} + i_{qs})$$

$$\psi_{ds} = -L_{ls}i_{ds} - L_m(i_{dr} + i_{ds})$$

Since the rotor rotates at speed  $\omega_r$ , the d-q axes rotate at the speed  $\omega_e - \omega_r$  referred to the rotor frame. Therefore, the equations are:

$$v_{dr} = 0 = -R_r i_{dr} + \frac{d\psi_{dr}}{dt} - (\omega_e - \omega_r)\psi_{qr}$$

(2-7)

$$v_{qr} = 0 = -R_r i_{qr} + \frac{d\psi_{qr}}{dt} + (\omega_e - \omega_r)\psi_{dr}$$

(2-8)

Where:

$$\psi_{dr} = -L_{lr}i_{dr} - L_m(i_{dr} + i_{ds})$$

$$\psi_{ar} = -L_{lr}i_{ar} - L_{m}(i_{ar} + i_{as})$$

The rotor speed  $\omega_r$  in equations (2-7) and (2-8) usually is treated as a constant during the electrical transient. The electrical torque of the induction machine is given by

$$T_e = \frac{3P}{2L_m} (i_{ds} i_{qr} - i_{qs} i_{dr})$$

(2-9)

Where P is the number of the poles.

(a) d-axis equivalent circuit

(b) q-axis equivalent circuit

Figure 2-3: Induction generator equivalent circuits under synchronous reference frame

#### 2.4 Inductive Load and Self-Excitation Capacitor Model

Capacitor is necessary in the standalone WECS. The capacitor can provide reactive power to the induction generator. The equations (2-12) and (2-13) represent the relation between capacitor currents and voltages in synchronous reference frame. For the load current and voltage, it has

$$i_s = i_C + i_I + i (2-10)$$

$$v_l = Ri_l + \omega L_l i_l \tag{2-11}$$

Through the Clark-Park transformation, the d-q synchronous reference frame equations can be obtained:

$$i_{ds} = i_{Cd} + i_{ld} + i_d + C\omega_e v_{qs}, \quad i_{qs} = i_{Cq} + i_{lq} + i_q - C\omega_e v_{ds}$$

(2-12)

$$\frac{d}{dt}v_{ds} = (\frac{1}{C}i_{ds} - \frac{1}{C}i_{ld} - \frac{1}{C}i_{d}) + \omega_{e}v_{qs}, \quad \frac{d}{dt}v_{qs} = (\frac{1}{C}i_{qs} - \frac{1}{C}i_{lq} - \frac{1}{C}i_{q}) - \omega_{e}v_{ds}$$

(2-13)

Equations (2-14) shows the load voltages and currents in reference frame, assume of inductive load.

$$v_{ld} = R_L i_{ld} + L_l \frac{d}{dt} i_{ld} - \omega_e i_{lq}, \quad v_{lq} = R_L i_{lq} + L_l \frac{d}{dt} i_{lq} + \omega_e i_{ld}$$

(2-14)

#### 2.5 Energy Storage System Model

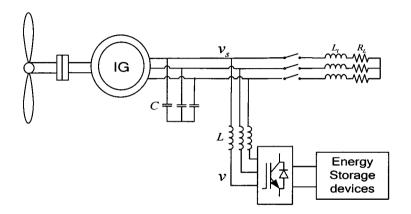

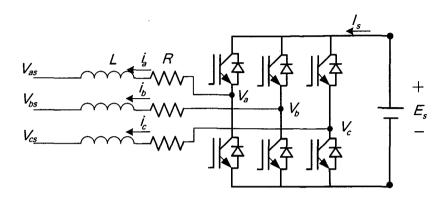

The storage system consists of a bi-directional PWM voltage source based converter, grid connection inductors and batteries. In this thesis, the battery's characteristic is neglected and ideal voltage source *Es* is adopted. Since battery power management is another complex topic, the research here focuses on the converter control to maintain a smooth power flow to the load. The differential equations can be established for the energy storage system.

$$v(t) = dE_a \tag{2-15}$$

$$\frac{di(t)}{dt} = \frac{1}{I} [v(t) - Ri(t) - v_s(t)]$$

(2-16)

In Eq. 2-15 and 2-16, d is the duty ratio,  $v(t) = \begin{bmatrix} v_a(t) & v_b(t) & v_c(t) \end{bmatrix}^T$  is converter output phase voltage.  $v_s(t) = \begin{bmatrix} v_{as}(t) & v_{bs}(t) & v_{cs}(t) \end{bmatrix}^T$  is terminal (or bus) voltage and  $i(t) = \begin{bmatrix} i_a(t) & i_b(t) & i_c(t) \end{bmatrix}^T$  is converter side current.

Figure 2-4: Energy storage system circuit

The above equations can be transferred to selected dq reference frame by applying parkclark transformation. Assume that the three-phase system is balanced three-phase three-wire system, in which zero components can be removed. The two differential equations can be written in Eq. (2-17) and (2-18), where  $\omega$  is the rotating speed of reference frame.

$$\frac{di_d(t)}{dt} = \frac{1}{L} [v_d(t) - Ri_d(t) - v_{ds}(t)] + \omega_e i_q(t)$$

(2-17)

$$\frac{di_{q}(t)}{dt} = \frac{1}{L} [v_{q}(t) - Ri_{q}(t) - v_{qs}(t)] - \omega_{e}i_{d}(t)$$

(2-18)

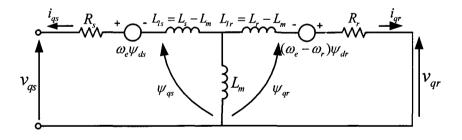

#### 2.6 Standalone WECS Model

The completed dynamic model can be presented based on the previous analysis. According to the set of 10 differential equations corresponding to variables  $i_{ds}$ ,  $i_{qs}$ ,  $i_{dr}$ ,  $i_{qr}$ ,  $v_{ld}$ ,  $v_{lq}$ ,  $i_{ld}$ ,  $i_{lq}$ ,  $i_{d}$ ,  $i_{q}$ , the d-q equivalent circuit at synchronously rotating frame can be obtained, as shown in figure 2-5.

(a) d-axis equivalent circuit

(b) q-axis equivalent circuit

Figure 2-5: d-q Equivalent circuits in synchronous reference frame

#### 2.7 Small Signal Model

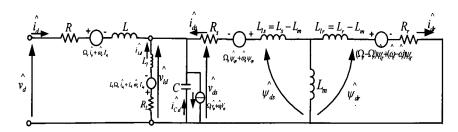

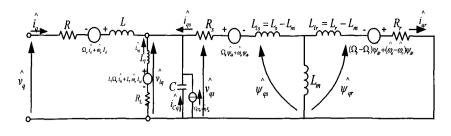

Eq. (2-5—2-18) present the whole system mathematical model. Base on that, the whole system small signal models can be obtained by introducing the small variation.

To construct a small-signal ac model at a quiescent operation point, assume that system currents and voltages are equal to some given steady state values I and V (quiescent operating point), plus superimposed small ac variations  $\hat{i}$  and  $\hat{v}$ . Hence, we have

$$v_d = V_d + \hat{v_d}$$

;  $v_{ds} = V_{ds} + \hat{v_{ds}}$ ;  $v_{ld} = V_{ld} + \hat{v_{ld}}$ ;  $i_d = I_d + \hat{i_d}$ ;  $i_{ds} = I_{ds} + \hat{i_{ds}}$ ;  $i_{ld} = I_{ld} + \hat{i_{ld}}$  (2-19)

$$v_q = V_q + \hat{v_q}$$

;  $v_{qs} = V_{qs} + \hat{v_{qs}}$ ;  $v_{lq} = V_{lq} + \hat{v_{lq}}$ ;  $i_q = I_q + \hat{i_q}$ ;  $i_{qs} = I_{qs} + \hat{i_{qs}}$ ;  $i_{lq} = I_{lq} + \hat{i_{lq}}$  (2-20)

$$\omega_e = \Omega_e + \hat{\omega_e}; \ \omega_r = \Omega_r + \hat{\omega_r}$$

(2-21)

With the assumptions that the ac variations are small in magnitude compared to the steady values, then the equations can be simplified. This is done by substituting Eqs. (2-20) and (2-21) into Eqs. (2-5) and (2-6).

$$V_{ds} + v_{ds}^{\hat{}} = -R_s (I_{ds} + i_{ds}^{\hat{}}) + \frac{d(\psi_{ds} + \psi_{ds}^{\hat{}})}{dt} - (\Omega_e + \omega_e^{\hat{}})(\psi_{qs} + \psi_{qs}^{\hat{}})$$

(2-23)

$$V_{qs} + \hat{v_{qs}} = -R_s (I_{qs} + \hat{i_{qs}}) + \frac{d(\psi_{qs} + \psi_{qs})}{dt} + (\Omega_e + \hat{\omega_e})(\psi_{ds} + \psi_{ds})$$

(2-24)

By cancelling the steady-state terms and neglecting high order ac terms in Eqs. (2-23) and (2-24), the first-order ac terms on both side of the equations are left. Hence,

$$\hat{v_{ds}} = -R_s \, \hat{i_{ds}} + \frac{d \, \hat{\psi_{ds}}}{dt} - \Omega_e \, \hat{\psi_{qs}} - \hat{\omega_e} \, \psi_{qs}$$

(2-25)

$$\hat{v_{qs}} = -R_s \, \hat{i_{qs}} + \frac{d \, \psi_{qs}}{dt} + \Omega_e \, \hat{\psi_{ds}} + \hat{\omega_e} \, \psi_{ds} \tag{2-26}$$

Where:

$$\hat{\psi}_{as} = -L_{ls} \hat{i}_{as} - L_{m} (\hat{i}_{ar} + \hat{i}_{as})$$

$$\hat{\psi_{ds}} = -L_{ls} \hat{i_{ds}} - L_m (\hat{i_{dr}} + \hat{i_{ds}})$$

Similarly, eqs. (2-25) - (2-26) can be derived.

$$\hat{v_{dr}} = -R_r \hat{i_{dr}} + \frac{d\hat{\psi_{dr}}}{dt} - (\Omega_e - \Omega_r)\hat{\psi_{qr}} - (\hat{\omega_e} - \hat{\omega_r})\psi_{qr}$$

(2-27)

$$\hat{\mathbf{v}_{qr}} = -R_r \, \hat{i}_{qr} + \frac{d \, \hat{\psi}_{qr}}{dt} + (\Omega_e - \Omega_r) \, \hat{\psi}_{dr} + (\hat{\omega}_e - \hat{\omega}_r) \psi_{dr}$$

(2-28)

Where:

$$\hat{\psi_{dr}} = -L_{lr} \, \hat{i_{dr}} - L_m (\hat{i_{dr}} + \hat{i_{ds}})$$

$$\hat{\psi_{qr}} = -L_{lr} \hat{i_{qr}} - L_m (\hat{i_{qr}} + \hat{i_{qs}})$$

And similar procedures can be done on Eqs (2-130, (2-14), (2-16) to (2-18).

$$\frac{d}{dt}\hat{v}_{ds}^{\hat{}} = \frac{1}{C}\hat{i}_{ds}^{\hat{}} - \frac{1}{C}\hat{i}_{ld}^{\hat{}} - \frac{1}{C}\hat{i}_{d}^{\hat{}} + \Omega_{e}\hat{v}_{qs}^{\hat{}} + \hat{\omega}_{e}V_{qs}$$

(2-29)

$$\frac{d}{dt}\hat{v_{qs}} = \frac{1}{C}\hat{i_{qs}} - \frac{1}{C}\hat{i_{lq}} - \frac{1}{C}\hat{i_{lq}} - \frac{1}{C}\hat{i_{q}} - \Omega_e \hat{v_{ds}} - \hat{\omega_e}V_{ds}$$

(2-30)

$$\hat{v}_{ld} = R \, \hat{i}_{ld} + L_l \, \frac{d}{dt} \, \hat{i}_{ld} - L_l \, \Omega_e \, \hat{i}_{lq} - L_l \, \hat{\omega}_e \, I_{lq}$$

(2-31)

$$\hat{v}_{lq} = R \, \hat{i}_{lq} + L_l \, \frac{d}{dt} \, \hat{i}_{lq} + L_l \, \Omega_e \, \hat{i}_{ld} + L_l \, \hat{\omega}_e \, I_{ld}$$

(2-32)

$$\frac{d\hat{i_d}}{dt} = \frac{1}{L} [\hat{v_d} - R\hat{i_d} - \hat{v_{ds}}] + \Omega_e \hat{i_q} + \hat{\omega_e} I_q$$

(2-33)

$$\frac{d\hat{i_q}}{dt} = \frac{1}{L} [\hat{v_q} - R\hat{i_q} - \hat{v_{qs}}] - \Omega_e \hat{i_d} - \hat{\omega_e} I_d$$

(2-34)

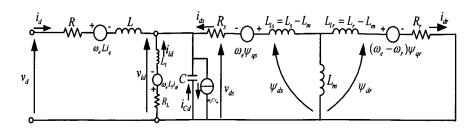

The small signal equivalent circuit for the whole system can be given based on Eqs. (2-25) – (2-34), as shown in Fig. 2-6.

(a) d-axis equivalent circuit

(b) q-axis equivalent circuit

Figure 2-6: Small signal model for d-q equivalent circuits in synchronous reference frame

#### 2.8 Conclusions

In this chapter, the models of wind energy conversion system with induction generator and energy storage system are presented based on the model for each component. System model is developed to describe the dynamic behavior. Small signal model is derived based on the quiescent operating point and linearization. The model will be used for the controller design in Chapter 3.

### Chapter 3 Control of Standalone WECS

#### 3.1 Introduction

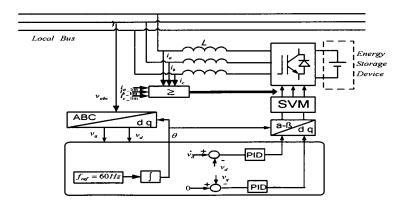

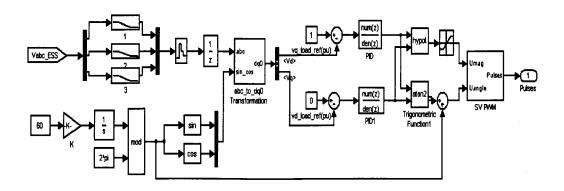

Based on the small signal model in the last chapter, the system transfer function can be obtained. Traditional control method can be used in the regulator design. Direct voltage control with current limit is developed for energy storage system to regulate the system voltage and frequency, and meanwhile, the real power and reactive power. In this research, compared with conventional power control with cascaded loops, the direct voltage control has faster dynamic performance with higher system bandwidth. The block diagram of the whole system is shown in Figure 3-1. And the controller design will be discussed in the followed sections.

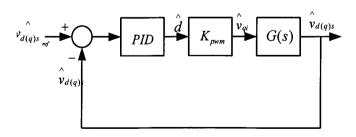

Figure 3-1: Control block diagram of the whole system

The stability analysis of the control system is based on the conventional method by using bode plots of the control loop in s-domain. Once the transfer function of the open loop is derived, the bode plots can be easily analyzed with the toolboxes in Matlab.

#### 3.2 Direct Voltage Control

#### 3.2.1 Voltage and Frequency Control

In Figure 3-1, the displacement angle for the synchronous reference frame is generated by a given frequency, which is the reference frequency in the standalone WECS. In a standalone system, no synchronization is needed since the induction generator is indirectly controlled by the power converter through adjusting the bus voltage. In the diagram, transformation block receives the synchronous angle and transform the three phase local bus voltage into d-q reference frame. Two lead-lag regulators are employed to directly regulate the d and q component voltages. The target of the control system is to force the bus voltage follow the reference voltage through a fixed frequency transformation. The frequency is indirectly controlled through the transformation block by the given frequency. Reference  $v_d^*$  and  $v_q^*$  are the desired bus voltage and the fixed frequency is the desired system operating frequency. If the system outputs follow the references, then active and reactive power balances are maintained.

The system can be decoupled on a d-q reference frame. The plant transfer functions can be derived from the small signal model in the Chapter2. Figure 3-2 shows the block diagram using transfer functions for d or q axis, while the cross-coupling terms in the system in the system are treated as the disturbances. In Figure 3-2, the PWM converter is treated as a power amplifier with the gain  $K_{PWM}$  and G(s) is the transfer function from  $v_{d(g)}$  to  $v_{d(g)s}$ .

Figure 3-2: Block diagram using transfer functions

The controller for each axis uses a single loop to directly regulate the voltage. In this case, compared with conventional power control with cascaded loops, it has a much faster dynamic performance with even higher system bandwidth. Two lead-lag regulators are employed to regulated the d and q component voltages to obtain a higher phase margin and highest control bandwidth. The reference voltages can be arbitrary selected as long as the magnitude of the voltage is desired voltage. Usually the d-component reference voltage  $v_d^*$  is selected as the required local bus voltage, while the q-component reference voltage  $v_q^*$  is set to be zero. Space vector modulation (SVM) method is adapted to generate desired PWM gating signals.

It should be noted that the proposed system has no capability to protect the energy storage system (EES) from overload since the output current is not sensed in the control system. In order to protect the device from overload, several protection schemes have been developed. In this paper, dump load and current limit are employed together as the protection scheme. When the EES side current exceeds the maximum operating current of switching devices, the proper gating signal will be turned off to prevent the increase of current. The input power to EES is also detected, and the dump load is switched on when the input power exceeds the maximum power capability of the converter (or an energy storage device is applicable). The protection scheme with combination of fast act current limit and slow act dump load (due to power detection) functions well during overload. Other protections regarding over voltage, over temperature and devices short through are similar to regular converter system.

#### 3.2.2 Direct Voltage Controller Design

Shown in Figure 3-3, the system transfer function G(s) can be obtained from the small signal model. The cross-coupling terms in the system are neglected since they are treated as the disturbances and compensated by either feed-forward or regulators.

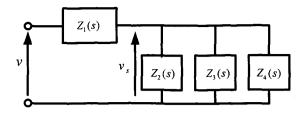

Figure 3-3: System blocks model in S-domain

The local bus voltage is the system output. The converter voltage, which controlled by the PWM signals is the system input. Then converter voltage to local bus voltage transfer function G(s) is shown in Eq. (3-1).

$$G(s) = \frac{v_s(s)}{v(s)} = \frac{Z_2(s)Z_3(s)Z_4(s)}{Z_2(s)Z_3(s)Z_4(s) + Z_1(s)[Z_3(s)Z_4(s) + Z_2(s)Z_3(s) + Z_2(s)Z_4(s)]}$$

(3-1)

Where  $Z_1(s)$  is the transfer function of converter side filter.  $Z_2(s)$  and  $Z_3(s)$  are the transfer functions of load and self-excitation capacitors. In the analysis, resistive load is assumed since most of the consumer loads in the home are resistance loads, such as lighting, heating devices and so on.

$$Z_1(s) = sL (3-2)$$

$$Z_2(s) = R_L \tag{3-3}$$

$$Z_3(s) = \frac{1}{sC} \tag{3-4}$$

$Z_4(s)$  represents the induction generator in S domain. The magnetization inductance is much bigger than the stator and rotor leakage inductances. So  $L_m$  can be neglected and the transfer function can be simplified in Eq.(3-5).

$$Z_4(s) = (R_s + R_r) + s(L_s + L_r)$$

(3-5)

Substitute the Eqs. (3-2) - (3-5) into Eq. (3-1), we have

$$G(s) = \frac{R_L[(R_s + R_r) + s(L_s + L_r)]}{(R_L + sL + s^2R_LLC_e)[(R_s + R_r) + s(L_s + L_r)] + sLR_L}$$

(3-6)

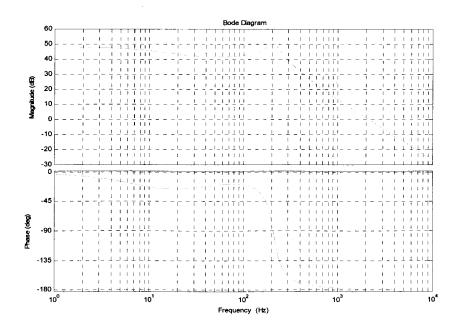

The bode plots of the uncompensated loop gain Tu(s) is shown in Figure 3-3, where

$$T_u(s) = K_{pwm}G(s) \tag{3-7}$$

The parameters are selected based on the 2kW lab prototype system which is shown in Table 3-1.

Table 3-1: Parameters of the Lab Prototype System

| Load, $R_L$                      | 22 Ω     |

|----------------------------------|----------|

| Converter filter inductance, L   | 10mH/20A |

| Excitation Capacitance, C        | 141 μF   |

| Stator Resistance, $R_s$         | 0.46Ω    |

| Rotor Resistance, R,             | 0.7Ω     |

| Stator Leakage Inductance, $L_s$ | 3.5mH    |

| Rotor Leakage Inductance, $L_r$  | 3.5mH    |

| Converter Gain, $K_{PWM}$        | 245      |

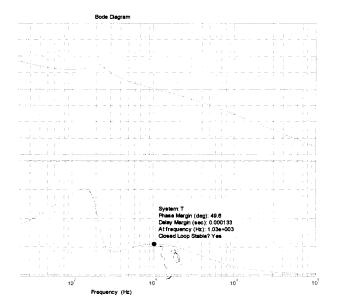

Figure 3-4: Bode plots of uncompensated loop

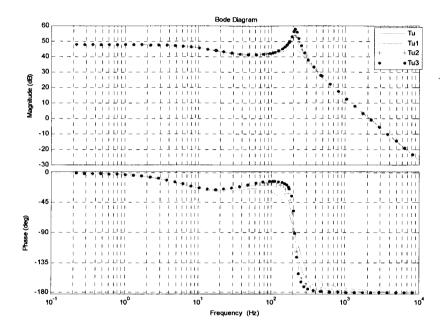

To analysis the load effect on the Bode plots, Fig. 3-5 shows the plots of the uncompensated loop under different loads. The load changes from 10 ohm to 100ohm in four steps. It can be seen that different loads only affect the overshoot value in magnitude plot and the slope of the curve at in phase plot (at resonant frequency). If the control bandwidth is selected to be much higher than the resonant frequency, the load variation has little effect to the dynamic response. In the prototype system, the bandwidth is selected at 1kHZ while the switching frequency of the converter is 10kHz.

Figure 3-5: Bode plots of uncompensated loop with different loads

For the uncompensated loop, the cross-over frequency is around 2kHz, and the phase margin is no more than 5 degrees. For a stable system, the best phase margin should be around 52 degrees. In order to gain a higher bandwidth and enough phase margin, lead-lag regulators are used in equation 3-8. Thus the dynamic response of the control system will be faster than the cascaded system using PI regulators. In the prototype system the switching frequency is 10kHz. So the cross-over frequency of the compensated loop is selected to be around 1kHz (1/10<sup>th</sup> of the switching frequency). By proper selecting the regulator parameters, the compensated loop has

around 52 degrees phase margin at 1kHz. The bode plots of compensated loop gain T(s) (Eq.3-9) are shown in Figure 3-6.

$$G_c(s) = G_{c0} \frac{1 + T_z s}{1 + T_p s} \frac{1 + T_i s}{T_i s}$$

(3-8)

$$T(s) = G_c(s)K_{pwm}G(s)$$

(3-9)

The parameters value of the lead-lag controller is shown in table 3-2, which are calculated through traditional method.

Table 3-2: Parameters of lead-lag Controller

| $T_z$        | $T_p$                   | $T_i$        |  |

|--------------|-------------------------|--------------|--|

| 1            | 1                       | 1            |  |

| $2\pi * 340$ | $\frac{1}{2\pi * 2900}$ | $2\pi * 100$ |  |

5: Bode plot of compensated loop gain

# 3.3 Conclusions

In this chapter, a novel direct voltage control is proposed. Based on this analysis, the system local bus voltage and frequency can be regulated by the two control loops for d-q reference frame. But due to the non-sensed current, current protection scheme is employed in this control system. Based on the developed system transfer function, the direct voltage controller can be designed based on the traditional lead-lag regulator with increased the system phase margin and extended the system bandwidth. Thus reliability and dynamic performance are improved.

# Chapter 4 Simulation and Experimental Results

### 4.1 Introduction

Both simulation models and experimental setup were built for the verification of the proposed wind energy conversion system with induction generator and energy storage. The whole system model was created using Simulink/Matlab. In the simulation, the system consists of the three major components: the wind power generation system with energy storage devices, the controller for power converter and the load. The wind turbine drives the induction generator to run at the based speed. In order to simulate the wind fluctuation, the wind speed is assumed to have the random changing around the base speed time by time. And the controller is used to regulate the local bus voltage and frequency constant. The details will be presented in the following sections.

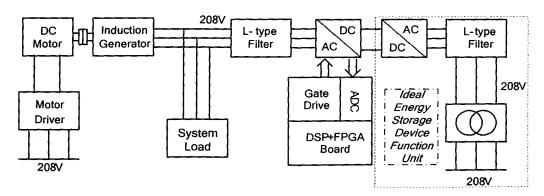

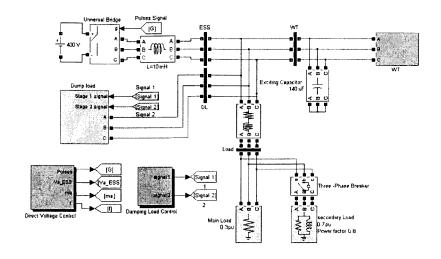

As shown in Figure 4-1, the experimental set-up consists of a back to back converter, isolated transformer, a DC motor, an induction generator and a DSP-FPGA based digital controller. The proposed system is based on the 2kW LabVolt wound-rotor induction machine set.

Figure 4-1: Block diagram of experimental set-up

The multipurpose back to back power converter was designed and built for several projects. In this project, one side of the converter works as a PWM rectifier, which maintains the DC link voltage constant. This part is functional as an ideal energy storage device. And the other side works as an inverter to maintain the local bus voltage and frequency constant with direct voltage control. The DC motor and induction generator are mechanically coupled together. The DC motor is operated as a prime mover to drive the induction generator in the super-synchronous speed mode. The Texas instruments TMS320F2812 DSP and Altera's Cyclone FPGA were employed as the core of the digital controller. Some experimental variables, such as dq components voltage and current, are captured form DSP internal memory since these variables are not directly available on the oscilloscopes.

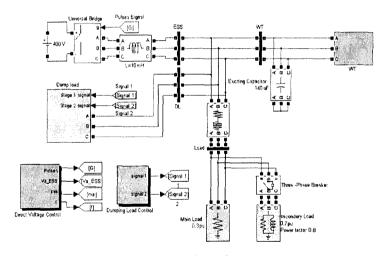

## 4.2 Simulation Model

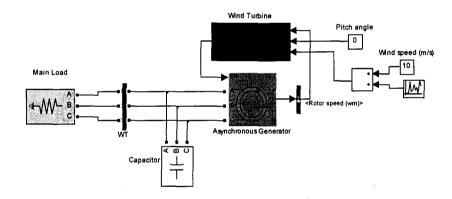

The whole system consists of the three major components: the wind power generator with energy storage, the controller for power converter and the load, as shown in Fig. 4-2.

Figure 4-2: System models of proposed WECS

The system parameters of the prototypes system is shown in Table 4-1. Same parameters are used in the simulation.

Table 4-1: System parameters of prototypes system

| System Ratings |            | Generator Parameters |       |                                        |         |

|----------------|------------|----------------------|-------|----------------------------------------|---------|

| Power          | 2kW        | Current              | 5.55A | Stator, Rotor Resistances              | 0.032pu |

| Voltage        | 208V       | Frequency            | 60Hz  | Stator, Rotor Leakage Induct-<br>ances | 0.061pu |

| Exitation      | Capacitor  | 141 μ                | F     | Magnetization Inductance               | 0.875pu |

| Converter      | Inductance | 0.2рі                | ]     | Pole Pairs                             | 2       |

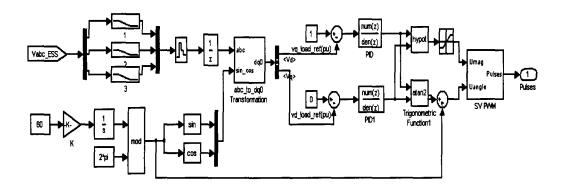

Figure 4-3 shows the implementation of the controller outlined in Chaper3. The voltage references and frequency reference are given as constant values. The local bus voltages in pu system are sensed and feedback to the controller. The lead-lag regulators are used to regulate the bus voltage. The output of the regulator is used to generate the reference voltage for power converter, from where PWM gating signals are generated using SVM.

Figure 4-3: Direct voltage controller model

The energy storage devices (here is the ideal voltage source) are connected to the local bus through the inverter. Through the proposed controller, the local bus voltage and frequency should be kept constant in steady-state, and meanwhile, the system power flow should maintain balanced.

## 4.3 Simulation Results

#### 4.3.1 Non-ESS Stand Alone Wind Power Generation System

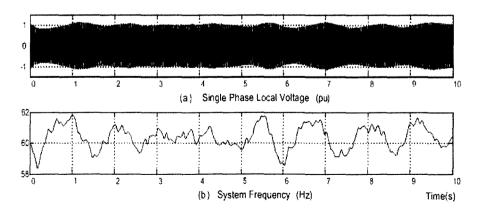

When the WECS is connected to the load without the energy storage system, the local bus voltage and frequency will have a large fluctuation due to the wind speed fluctuation. The system configuration in simulation is shown in Figure 4-4. The wind turbine model use the standard block provided with the Simulink's Simpowersystem block set. The based wind speed is set to be 10m/s. A random source, whose range is from -1 to +1, is used to simulate the fluctuation in the wind. As shown in Fig. 4-5, the voltage and frequency have large fluctuations produced by wind generator without ESS. Both are not constant. So the power quality is not acceptable.

Figure 4-4: Wind power generation system without ESS

Figure 4-5: System voltage and frequency without ESS

## 4.3.2 Simulation Results with ESS

## A. Resistive load Step Change

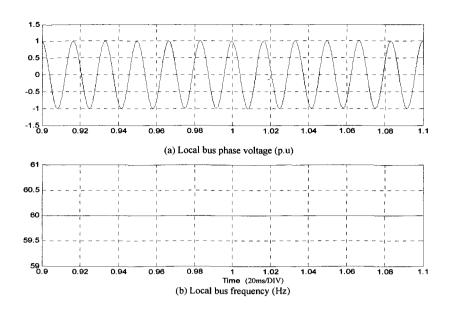

In order to test the controller performance both in steady state and transient response, a step load change was held at 1.0s in the simulation. The results are shown in Figure 4-6—4-13. With the EES, the voltage and frequency keep constant whenever before or after the load change. And meanwhile, the system power flow is maintained balanced.

Figure 4-6: Local bus voltage and frequency during load step change (with R Load) in Simulation

Figure 4-7: d-q axis inverter voltage during load step change (with R Load) in Simulation

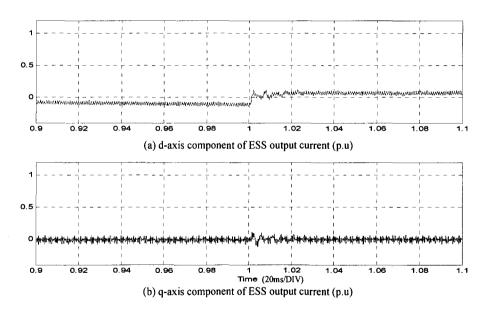

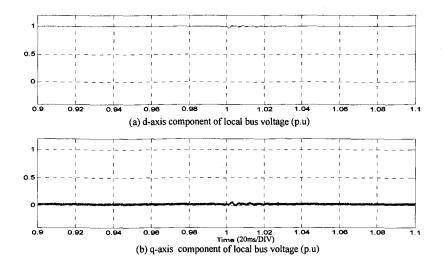

Figure 4-8: d-q axis inverter current during load step change (with R Load) in Simulation

In Fig.4-5, the voltage and frequency have large fluctuations by wind generator without ESS. When the EES is employed with proposed control system, the voltage and frequency are maintained constant as shown in Fig.4-6. Figure 4-7 and Figure 4-8 show the waveforms of d,q axis voltages and currents. During the load change, the voltages track the reference voltages in

very well with a small transient. It also can be observed from the waveforms that the frequency transient is less than  $\pm 0.1$ Hz and voltage dip is less than 1%. There is no steady-state error in the voltage and frequency due to the merits of synchronous frame and lead-lag regulators.

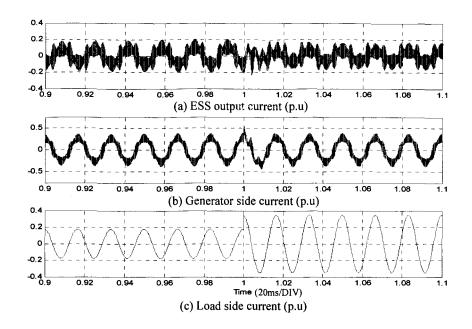

Figure 4-9: Current waveforms during load step change (with R load) in simulation

Fig.4-9 shows the current waveforms from the generator, ESS and load. The ESS absorbs the real power before 1.0s and provides real power after 1.0s. EES also compensates the fluctuation in the real power due to wind fluctuation at the same time. In the whole process, the power flow in the system maintained balance all the time.

#### B. Inductive Load Step Change

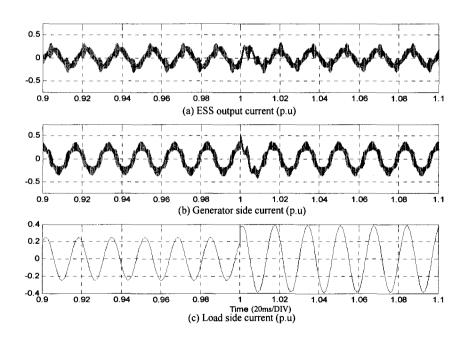

Fig.4-10 to Fig.4-13 show the simulation results with RL-load change at 1.0s. Fig.4-10 shows the local bus voltage and frequency. It has a similar response with the R load change. There's no significant change both in voltage and frequency. Fig. 4-11 shows the current waveforms with RL-load in simulation. The generator and EES together provide the real power. The reactive power is compensated from ESS. Fig. 4-12 and Fig.4-13 shows the d-q axis voltage and current simulation waveforms during load change. The d/q component voltages have very small dip. The d/q current components reflected the real power and reactive power from the EES respectively.

Figure 4-10: Voltage and frequency during load step change (with RL load) in simulation

Figure 4-11: Currents waveforms during load step change (with RL load) in simulation

Figure 4-12: d-q axis inverter voltages during load step change (with RL Load) in Simulation

Figure 4-13: d-q axis inverter currents during load step change (with RL Load) in Simulation

Simulation results clearly show that the direct voltage control has good steady-state performance and fast transient response. The experimental results will be presented in the following section. Companied with the experimental results, the controller performance can be better tested.

# 4.4 Experimental Setup

The whole system experimental setup is shown in Fig.4-14, where part "A" is the DC motor, and part "B" is the induction generator. The DC motor and induction generator are mechanically coupled together. The DC motor is operated as a prime mover to drive the induction generator in the super-synchronous speed mode. Part "C" is the self-excition capacitor. The output of the induction generator is connected to the local bus, and only provides the real power to the load. The energy storage system is simulated by a back-to-back converter, which is part "D" in Figure 4-14. One side of the converter works as a PWM rectifier, which maintains the DC link voltage constant. This part is functional as an ideal energy storage device. The power fluctuation is buffed through the grid. And the other side works as an inverter to maintain the local bus voltage and frequency constant with direct voltage control, and meanwhile, keep the system power balanced. The DC link voltage is rated at 400V, and the Local bus voltage was rated at 208V/5.55A. Part "F" is the DSP-FPGA controller board. And part "E" is the filter inductor for PWM converter.

Figure 4-14: Experimental setup

(A: DC motor; B: Induction generator; C: Self-excited capacitor; D: Converter; E: Line indcutors; F: DSP-FPGA controller board)

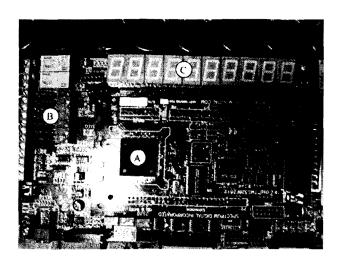

The controller design developed in Chapter3 was implemented using the DSP-FPGA platform as shown in Fig.4-15. The controller hardware used in this experiment consisted of the analogue signal conditioning board, DSP ("A"), FPGA, interface circuit ("B")and a LED display ("C").

Figure 4-15: DSP controller board

(A: DSP chip; B: Interface circuit; C: LED display)

The controller algorithm from chapter3 was transferred into the DSP using C programming language. The complete code for the controller is given in Appendix D.

The system voltages and currents are sensed and fed to the conditioning circuit, which fed the signals to the A/D converter. The results of A/D converter are fetched by the DSP and used as the feedback signals. The final output signals of the DSP board are the switch signals for the PWM converter. The role of the FPGA in this experiment is to provide the phase information for the grid-side rectifier and to provide protection for the power converter in case of abnormal conditions. For this purposes the over-voltage, over-current and over-temperature protection circuits are interfaced directly with the FPGA to provide instantaneous protection of the power devices. In this system, the switching frequency is selected at 4.5 kHz. Higher switching frequency obviously would be better in the performance, but switching loss should be considered in the practical design.

The operational sequence of the controller is developed as following. First the gird side converter is energized. Once it is activated, the converter boosts the DC voltage to the required 400V. At this time the local bus side converter is turned on and works with constant V/f control strategy to drive the induction generator speeding up until it goes into steady state. The large starting current in the induction machine is avoided in the V/F control. And then, adjust the DC

motor input voltage to increase the input power until the rotating speed beyonds the synchronous speed. Now, the induction machine is operating in generator mode. The load then is connected to the local bus. And the controller starts to maintain the local bus voltage and frequency constant. The turn-off sequence for the converter is the opposite procedure of the start-up. In practical, the wind turbine speeds up the generator. The generator builds up the voltage with self-excitation capacitor. When the voltage reaches the desired level, the generator is brought to the local bus and ESS is started to maintain the local bus voltage and current. During the connection, synchronization is needed between ESS and generator. But in the experimental setup the synchronization is not necessary since the machine is started through the converter directly.

# 4.5 Experimental Results and Analysis

The performance of the direct voltage control was evaluated on the prototype system at several load conditions. The load step change is necessary. Through the load step change, the transient procedures are captured using the oscilloscopes through the voltage and current sensors. For different kind of loads, the local bus voltage and frequency are kept constant with direct voltage control. And the system power flow is maintained balanced with the ESS.

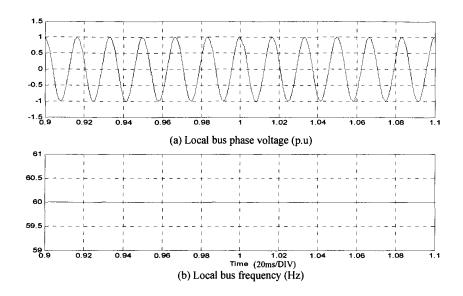

#### 4.5.1 Resistive Load Test

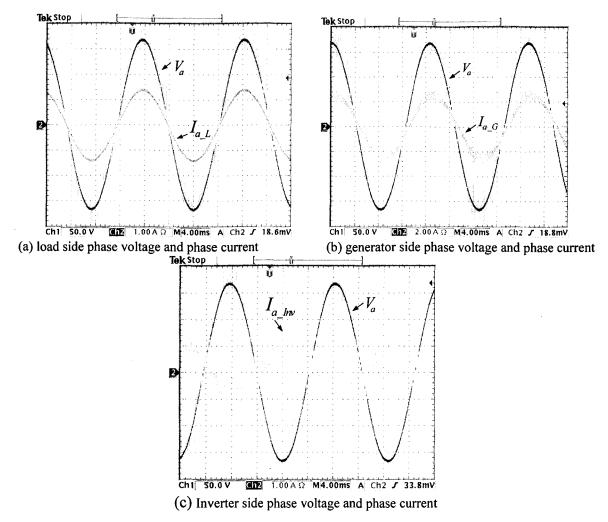

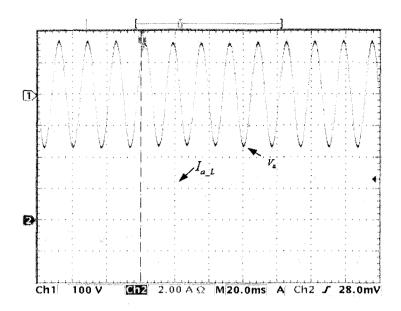

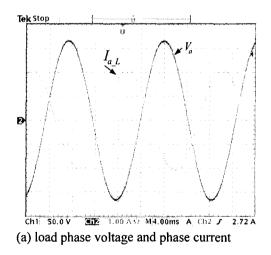

Resistive load is connected on the local bus. When the generator starts up and goes into steady state, a three phase resistive load is connected to the system local bus. The resistor value is  $120\Omega$ . The steady state waveforms of the voltage and current at different sides are shown in Fig. 4-16.

Figure 4-16: Steady-State waveforms with resistive load

Fig. 4-16(a) shows the waveforms of local bus voltage and the load current. As we can see, the local bus voltage is 120V in steady state. The load current is around 1A. Fig 4-16(b) and (c) shows the local bus voltage, generator side current and inverter side current. The generator provides the real power to load and EES. From Fig.4-16(b), the generator side current is around 1.7A. The load current is 1A. Fig.4-16(c) shows the additional 0.7A current entering the converter. From the current waveforms, it can be concluded that the system real power is balanced by ESS. Under same local bus voltage, the current reflects the system power flow.

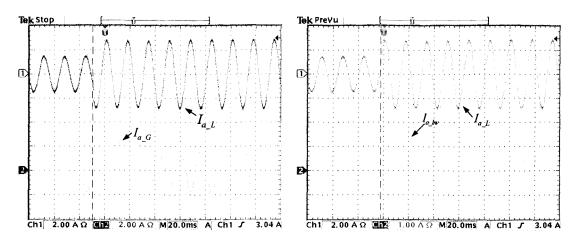

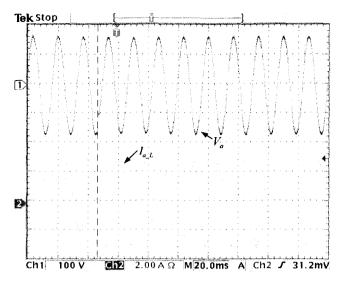

When the wind power generation system runs in the steady state, another resistive load is switched on and off from the local bus. The transient waveforms of local bus voltage and currents were captured, as shown in Fig. 4-17.

Figure 4-17: Transient waveforms of local bus voltage and load current during load step change

Fig. 4-17 shows the waveforms of local bus voltage and load current during the load change. After the additional resistor is switched on, the load current increases twice. From Fig.4-17, it can be seen that the local bus voltage has very small transient and thus a very small frequency change.

Fig 4-18 shows the waveforms of generator side current, inverter side current and load side current in the transient. It should be noted that the fluctuation in the generator current came from the oscillation of motor/generator set caused by load change. EES quickly compensates this oscillation and maintain the bus voltage/frequency constant. It also shows in Fig.4-18(b) that the ESS changes the power directional from absorbing excess real power to supplying the additional real power to the load.

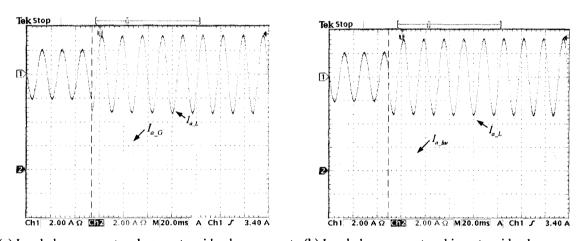

(a) Load phase current and generator side phase current (b) Load phase current and inverter side phase current Figure 4-18: Transient waveforms of generator and converter currents during load step change (with R Load)

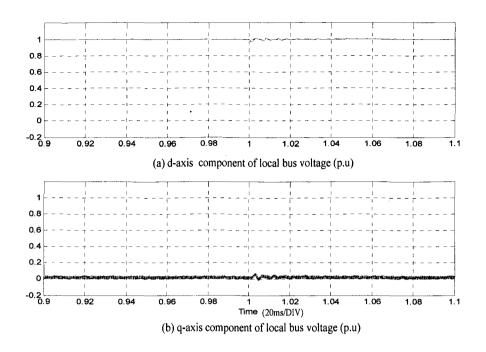

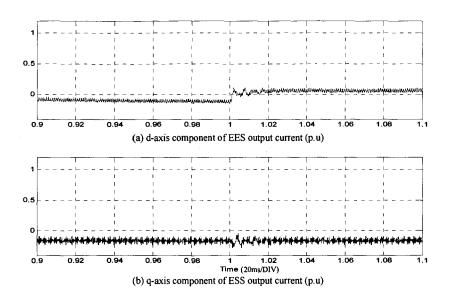

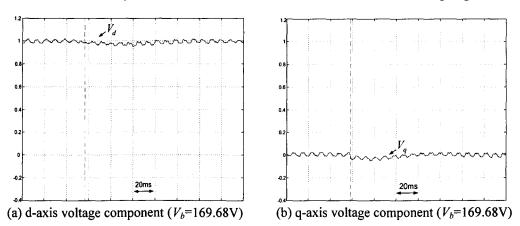

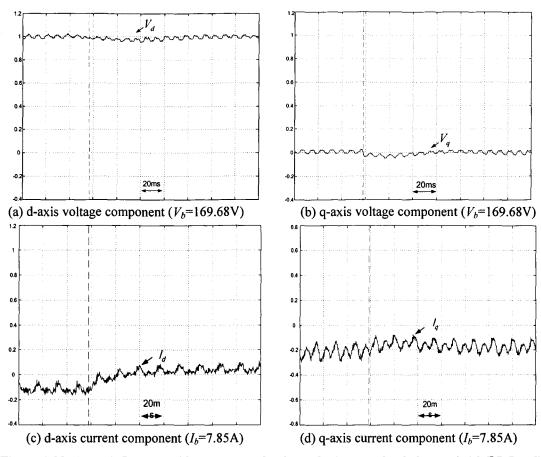

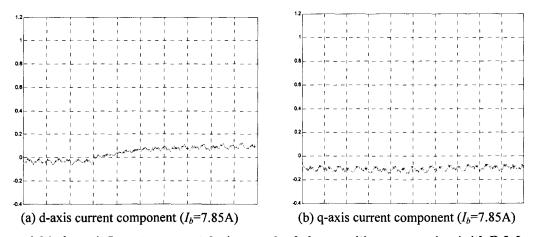

Voltage and current dq components waveforms of converter side are also captured from the DSP memory during the load change, as shown in Fig. 4-19. The reference voltage for  $v_d$  and  $v_q$  are 1.0 pu and 0 pu respectively. The voltage dq components trace the references very well. The current dq components are often referred to the real power and reactive power respectively. As it can be seen,  $i_d$  changes from negative to positive, indicating the power flow change for ESS. From the waveforms, it can be concluded that the control system has fast dynamic response during transient. And the steady-state error is almost zero because of the lead-lag regulators.

Figure 4-19: d-q axis Inverter side current during load step change (with R Load)

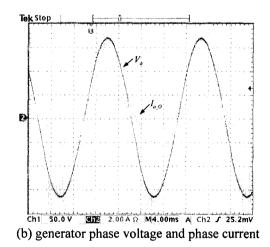

#### 4.5.2 Inductive Load Test

The system performance is also verified by connecting the inductive load. A three-phase  $120\Omega$  resistor bank and a 0.31H inductor bank are connected to the bus in parallel. With RL load, the controller still maintains the local bus voltage and frequency constant by providing the reactive power to the load. The steady state waveforms are shown in Fig. 4-20.

Figure 4-20: Steady-State voltage and current waveforms with RL load

Fig.4-20(a) shows the waveforms of local bus voltage and load current. Because of the RL load, the load current and voltage have about 45 degree phase displacement. Fig.4-20(b) and (c) show the waveforms of local bus voltage, generator side current and inverter side current. The generator only provides the real power to the load. So the current and voltage are almost in phase. The inverter absorbs the extra real in the system and provides the reactive power to the load. So the inverter side current lags the voltage at about 45 degree. From the Fig.4-20, it reflects the system power flow always maintains balance with the EES in the steady state.

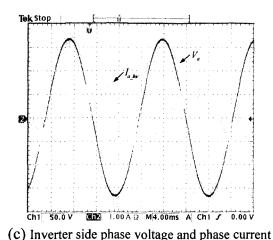

Load step change is also carried in the RL load condition. When the whole system runs into steady state, an additional load (1200hm) is switched on and off. The transient waveforms are shown in Fig. 4-21 and Fig.4-22.

The local bus voltage and load current transient waveforms are given in Fig.4-21. It is similar to the waveforms with pure resistive load, and the local bus voltage has a very small transient. Fig. 4-22 shows the transient waveforms of the load current, generator side current and inverter side current.

Figure 4-21: Transient waveforms of local bus voltage and load current during load step change (with RL load)

(a) Load phase current and generator side phase current

(b) Load phase current and inverter side phase current

Figure 4-22: Transient waveforms of currents of generator and inverter during load step change (with RL load)

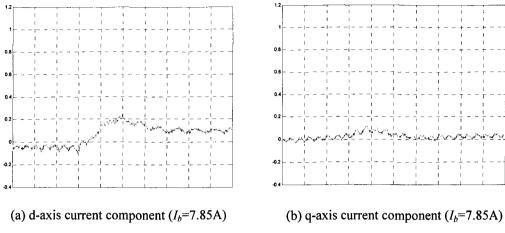

Inverter side voltage and current dq components waveforms are also given in Fig. 4-23. The voltage dq components are very similar to the pure resistive load. During the load change,  $v_d$  has a very small dip and then went back to the reference value quickly. Current waveforms are also similar to the resistive load condition. Since the load change is only on resistance,  $i_d$  has the same waveform as resistive load and  $i_q$  maintains at -0.2 pu.

Figure 4-23: d-q axis Inverter side current and voltage during step load change (with RL Load)

Figure 4-24: d-q axis Inverter current during step load change with compensation (with R-L Load)

It should be noted that current dq components waveforms contain an ac component at fundamental frequency both in R load and R-L load situations. It is verified that the inverter side current has a very small DC component. There are several reasons including non-symmetrical voltage output, sensor dc calibration and temperature drifting of the analog conditioning circuits. The last

two problems can be compensated through DSP using carefully calibrated circuit and dc bias compensation. But the unsymmetrical devices can not be avoided. The small DC voltage will cause large DC current in the system due to small resistance. This is the drawback of the proposed control system, which has no capability to direct regulate the current. So a simple DC compensation scheme is necessary in order to avoid the large DC current. The dq component current waveforms after compensation is are shown in Figure 4-24.

## 4.6 Conclusions

The model for standalone WECS with induction generator and energy storage system is constructed in the Simlink/Matlab software. The whole system with direct voltage control is verified in simulation and experiment. Different load conditions and load changes are carried in this project to verify the effectiveness of the controller. From the simulation and experimental results, it can be seen that the directly voltage control can achieve desired steady state performance with fast dynamic response.

# Chapter 5 Conclusions

### 5.1 Conclusions

From the simulation and experimental results obtained in this thesis, several conclusions can be drawn regarding the design of the directly voltage controller for the standalone wind energy conversion system with induction generator and energy storage system.

The dynamic mathematical model for the whole system is developed. Small signal model is derived based on the dynamic model. The small signal model provides the basis for the controller design. A lead-lag regulator based controller is developed to regulated the local bus voltage constant in synchronous reference frame. The reference frequency and voltages are selected at the desired values. The transformer functions for d-q axis are developed. The regulator parameters is calculated through the traditional design using phase margin and system bandwidth. lead-lag regulators successfully improve system bandwidth while maintain high phase margin. Thus fast dynamic response and small overshoot/undershoot can be expected. The system stability is also improved.

The control scheme developed for the direct control of the system local bus voltage and frequency in the WECS has been tested using the simulation model and experimental setup. The control system successfully maintains the system voltage and frequency constant under different load condition and power fluctuation. The power flow in the system maintains balanced by the power converter and ESS. The transient waveforms shown in the experimental results, corresponding with the simulation results, verify the expected response from controller design.

Overall, this research work has shown that the energy storage system with direct voltage control can be effectively used in the stand-alone WECS. Though this kind of control scheme has

its own drawbacks such as no capability of current protection, simple scheme can be used to overcome the problems of overload protection as well as the dc current. In this thesis, the employment of squirrel cage induction generator gives benefit for reducing the manufacturing and maintainance cost. The system reliability can also be improved compared to DFIG or permanent magnetic machines. Only fractional capacity power converter is required in this configuration, which further reduce the system cost.

## 5.2 Major Contributions

One of the main contributions of this work is the design of the direct voltage control for the stand-alone WECS with induction generator and ESS. The control scheme shown in Figure 3-1 provides a novel control method compared with conventional cascaded control method. It directly regulated the local bus voltage and frequency, and maintained the power flow balance in the system. It has a faster dynamic performance and higher stability.

The configuration using induction generator is another contribution of this research work. Because its own advantages, such as reliable, low cost, low maintenance, this configuration has better cost per kW. The development of the small signal model is very useful for the controller design. The model accurately represents of the system behaviour around the quiescent operating point.

## 5.3 Further Research Works

In order to accommodate the system variations and improve the control system performance, the following research work should be done in the further.

1) Overload test should be done in the experimental conditions. The drawback of the direct voltage control is capability of current control. Current protection scheme should be improved if necessary.

- 2) Multiple generators operation should be investigated in the future research. Sometimes there are more than one wind turbine generators are connected to the local bus. The system model will become complicated and the control of ESS will be difficult.

- 3) The characteristics of the different energy storage devices should be considered. In this thesis, the energy storage device is assumed as an ideal source. In practice, the characteristic of the energy storage device needs to be considered and optimized power management should be implemented to increase the battery life.

# References

- [1] M. A. Elhadidy and S. M. Shaahid, "Role of hybrid (wind+diesel) power systems in meeting commercial loads ", IEEE Transaction on Renewable Energy, vol. 29 pp. 109-118, 2004.

- [2] L. Wei, G. Joos, and C. Abbey, "Wind Power Impact on System Frequency Deviation and an ESS based Power Filtering Algorithm Solution," Conference record of Power Systems Conference and Exposition, 2006. PSCE '06. 2006 IEEE PES, 2006.

- [3] J. M. Carrasco, E. Galvan, R. Portillo, L.G. Franquelo and J. T. Bialasiewicz. "Power Electronics Systems for the Grid integration of Wind Turbine," Conference record of IE-CON 2006- 32<sup>nd</sup> Annal Conference, 2006.

- [4] J. Marques, H. Pinheiro, H. A. Gründling, J. R. Pinheiro, and H. L. Hey, "A Survey on Variable-Speed Wind Turbine System," conference record of CE. 7° Congresso Brasileiro Eletrônica Potência COBEP'03, Fortaleza, Brazil, 2003.

- [5] Chen, Z and Spooner, E., "Grid interface options for variable-speed, permanent-magnet generators," Electric Power Applications, IEE Proceedings, Vol 145, pp 273-283, July 1998.

- [6] A. S. Kini, A. S. Kini, and R. Y. Udaykumar, "Modelling And Performance Analysis of A Wind/Diesel Hybrid Power System," conference record of Industry Applications, 2006. 41st IAS Annual Meeting.

- [7] R. Sebastian, M. Castro, E. Sancristobal, F. A. Yeves, J. A. Peire, and J. A. Quesada, "Approaching hybrid wind-diesel systems and controller area network," Conference record of IECON 02, 2002.

- [8] W. E. Leithead, "Dependence of performance of variable speed wind turbines on the turbulence, dynamics and control," Generation, Transmission and Distribution, vol. 137, pp. 403-413, 1990.