## Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2010

# Unidirectional Multi-Bit FPGA Architecture For Area Efficient Implementation of Datapath Circuits

Omesh Mutukuda Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Mutukuda, Omesh, "Unidirectional Multi-Bit FPGA Architecture For Area Efficient Implementation of Datapath Circuits" (2010). *Theses and dissertations.* Paper 1440.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# UNIDIRECTIONAL MULTI-BIT FPGA ARCHITECTURE FOR AREA EFFICIENT IMPLEMENTATION OF DATAPATH CIRCUITS

by

## **Omesh Mutukuda**

B. Sc. in Electrical and Computer Engineering, University of Windsor, Windsor, ON, 2006

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science (MASc)

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2010

© Omesh Mutukuda, 2010

## **Author's Declaration**

I hereby declare that I am the sole author of this thesis

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Signature

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Signature

## Abstract

## UNIDIRECTIONAL MULTI-BIT FPGA ARCHITECTURE FOR AREA EFFICIENT IMPLEMENTATION OF DATAPATH CIRCUITS

Omesh Mutukuda

Master of Applied Science (MASc), 2010 Department of Electrical and Computer Engineering Ryerson University

Field Programmable Gate Arrays (FPGAs) are increasingly being used to implement large datapath-oriented applications that are designed to process multiple-bit wide data. Studies have shown that the regularity of these multi-bit signals can be effectively exploited to reduce the implementation area of datapath circuits on FPGAs that employ the traditional bidirectional routing. Most of modern FPGAs, however, employ unidirectional routing tracks which are more area and delay efficient. No study has investigated the design of multi-bit routing resources that can effectively transport multiple-bit wide signals using unidirectional routing tracks. This paper presents such an investigation of architectures which employ multi-bit connections and unidirectional routing resources to exploit datapath regularity. It is experimentally shown that unidirectional multi-bit architectures are 8.6% more area efficient than the conventional architecture. Additionally, this paper determines the most are efficient proportion of multi-bit connections.

## Acknowledgements

I would like to take this opportunity to express my gratitude and appreciation to my graduate supervisors, my family and friends.

It has been a privilege to work with Dr. Andy Ye and Dr. Gul Khan as they have made my post-graduate career a rewarding experience. I am especially grateful to Dr. Ye for his generosity, patience and keeping an open door in order to help me see through the challenges in my research. I would also like to thank Dr. Khan for the motivation and guidance on the practical aspects of my research. Their extensive knowledge and thoughtful advice will have made a remarkable influence on my entire engineering career.

This thesis would not have been possible if not for the moral and financial support from my parents Indra and Soma Mutukuda. Since childhood, my parents sacrificed their chances at many of life's opportunities (sometimes even their own happiness) in ensuring I had the freedom and ability to pursue my dreams. It is to them I would like to dedicate this thesis.

I would also like to thank my aunt Priyanthie for taking me out to enjoy the fine cuisine of Toronto and looking out for my general well being all while keeping a cheerful smile.

Finally, I would like to thank my friends David, Mustafa, Thuan and Sebastian for the good times full of youthful folly and hijinx. Their friendship, support and encouragement meant a great deal to me.

## **Table of Contents**

| Chapter 1 : Introduction                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Thesis Motivation                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.2 Thesis Contribution                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.3 Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 2 : Background                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1 FPGA Architecture                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1.1 Single-bit Bidirectional Architecture                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1.1.1 Logic Block Structure                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1.1.2 Routing Architecture                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1.2 Bidirectional Multi-bit Architecture                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1.2.1 Multi-bit Logic Block                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1.2.2 Multi-bit Routing                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1.3 Single-bit Unidirectional Routing Architecture                                                                                                                                                                                                                                                                                                                                                           |

| 2.2 FPGA CAD Algorithms and Tools                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2.1 Synthesis & Packing                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2.2 Placement & Routing                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2.2 Placement & Routing 23   VPR Placement 23                                                                                                                                                                                                                                                                                                                                                                |

| -                                                                                                                                                                                                                                                                                                                                                                                                              |

| VPR Placement                                                                                                                                                                                                                                                                                                                                                                                                  |

| VPR Placement                                                                                                                                                                                                                                                                                                                                                                                                  |

| VPR Placement                                                                                                                                                                                                                                                                                                                                                                                                  |

| VPR Placement 23   VPR Routing 24   2.2.3 MB-FPGA CAD Flow 26   Chapter 3 : Unidirectional Bus Connections 28                                                                                                                                                                                                                                                                                                  |

| VPR Placement    23      VPR Routing    24      2.2.3 MB-FPGA CAD Flow    26      Chapter 3 : Unidirectional Bus Connections    28      3.1 The Conventional Routing Architecture    28                                                                                                                                                                                                                        |

| VPR Placement    23      VPR Routing    24      2.2.3 MB-FPGA CAD Flow    26      Chapter 3 : Unidirectional Bus Connections    28      3.1 The Conventional Routing Architecture    28      3.2 Unidirectional Routing Bus Connections and Their Advantages    29                                                                                                                                             |

| VPR Placement    23      VPR Routing    24      2.2.3 MB-FPGA CAD Flow    26      Chapter 3 : Unidirectional Bus Connections    28      3.1 The Conventional Routing Architecture    28      3.2 Unidirectional Routing Bus Connections and Their Advantages    29      Chapter 4 : Unidirectional Multi-bit Architecture & Modeling.    37                                                                    |

| VPR Placement23VPR Routing242.2.3 MB-FPGA CAD Flow26Chapter 3 : Unidirectional Bus Connections283.1 The Conventional Routing Architecture283.2 Unidirectional Routing Bus Connections and Their Advantages29Chapter 4 : Unidirectional Multi-bit Architecture & Modeling374.1 Unidirectional Multi-bit Architecture37                                                                                          |

| VPR Placement23VPR Routing242.2.3 MB-FPGA CAD Flow26Chapter 3 : Unidirectional Bus Connections283.1 The Conventional Routing Architecture283.2 Unidirectional Routing Bus Connections and Their Advantages29Chapter 4 : Unidirectional Multi-bit Architecture & Modeling374.1 Unidirectional Multi-bit Architecture374.2 Buffer and Transistor Sizing41                                                        |

| VPR Placement22VPR Routing242.2.3 MB-FPGA CAD Flow26Chapter 3 : Unidirectional Bus Connections283.1 The Conventional Routing Architecture283.2 Unidirectional Routing Bus Connections and Their Advantages29Chapter 4 : Unidirectional Multi-bit Architecture & Modeling374.1 Unidirectional Multi-bit Architecture374.2 Buffer and Transistor Sizing414.3 Parameters42                                        |

| VPR Placement22VPR Routing242.2.3 MB-FPGA CAD Flow26Chapter 3 : Unidirectional Bus Connections283.1 The Conventional Routing Architecture283.2 Unidirectional Routing Bus Connections and Their Advantages29Chapter 4 : Unidirectional Multi-bit Architecture & Modeling374.1 Unidirectional Multi-bit Architecture374.2 Buffer and Transistor Sizing414.3 Parameters424.4 Routing Resource Graph Generation43 |

| 5.3 Delay ar   | d Track Segment Results                       | 55   |

|----------------|-----------------------------------------------|------|

| Chapter 6 : Co | nclusion                                      | . 58 |

| 6.1 Summar     | у                                             | . 58 |

| 6.2 Future V   | Vork                                          | . 59 |

| Appendix A:    | Results for $F_{cif} = .4$ and $F_{cic} = .4$ | 60   |

| A.1 Area Re    | sults                                         | 60   |

| A.2 Delay a    | nd Channel Width Results                      | 62   |

| Appendix B:    | Graphical Outputs of Circuit Implementations  | . 64 |

| References     |                                               | . 79 |

## List of Tables

| Table 3.1 Impact of Routing on Total FPGA Area.                                                  | 30 |

|--------------------------------------------------------------------------------------------------|----|

| Table 3.2 Conventional and Multi-bit Area of an FPGA Tile                                        | 35 |

| Table 4.1 Internal Multi-bit Logic Block Delays                                                  | 42 |

| Table 5.1. Architecture Parameters and Values                                                    | 51 |

| Table 5.2. Routing Area vs. Proportion of Routing Buses Per Circuit                              | 54 |

| Table 5.3. Critical Path Delays of Benchmark Circuits                                            | 56 |

| Table A.1. Routing Area vs. Proportion of Routing Buses per Circuit ( $F_{cif} = F_{cic} = .4$ ) | 61 |

| Table A.2. Critical Path Delays of Benchmark Circuits ( $F_{cif} = F_{cic} = .4$ )               | 63 |

# **List of Figures**

| Fig. 2.1. Layout of an (a) Island-style FPGA and (b) a FPGA tile                          | 6  |

|-------------------------------------------------------------------------------------------|----|

| Fig. 2.2. Basic Logic Element (BLE)                                                       | 7  |

| Fig. 2.3. Internal logic block structure                                                  |    |

| Fig. 2.4. FPGA routing architecture with wire segments of length 2                        | 9  |

| Fig. 2.5. A (a) switch block with (b) half and (c) full switch block connections          | 10 |

| Fig. 2.6. Disjoint switch block topology ( $L=2$ ) using half and full switch connections | 11 |

| Fig. 2.7. Connection block with (a) input and (b) output connections                      | 12 |

| Fig. 2.8. Output connections using configuration memory sharing (CMS)                     |    |

| Fig. 2.9. Multi-bit FPGA                                                                  | 14 |

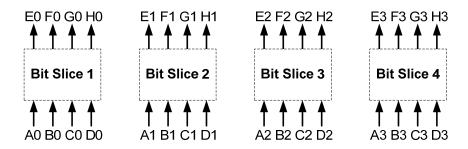

| Fig. 2.10. Mapping of a 4-bit adder into a Multi-bit logic block                          | 15 |

| Fig. 2.11. Input and output connections of the connection block                           | 17 |

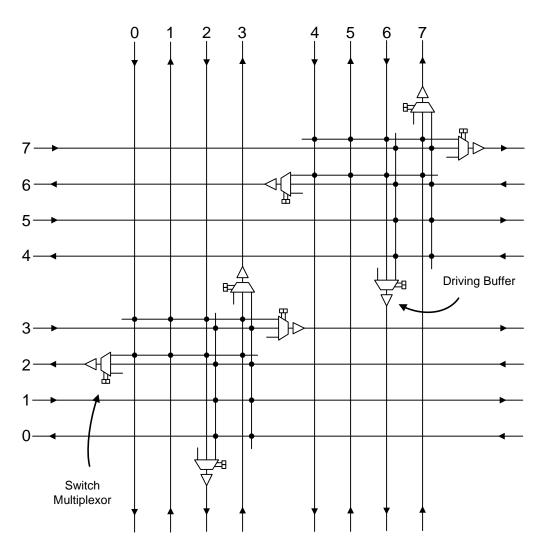

| Fig. 2.12. Conventional switch block with unidirectional wires of length 2                | 19 |

| Fig. 2.13. Switch block connections for a horizontal channel                              | 20 |

| Fig. 2.14. FPGA CAD flow                                                                  | 21 |

| Fig. 2.15. Modelling (a) a connection between two output pins on (b) a directed graph     |    |

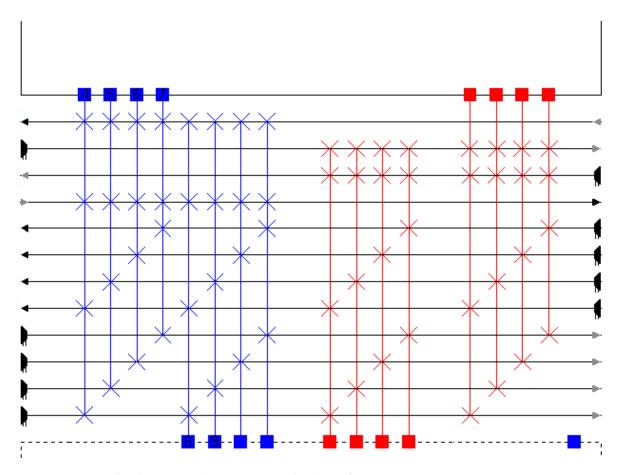

| Fig. 3.1. Bit-slice partitioned datapath circuit                                          | 31 |

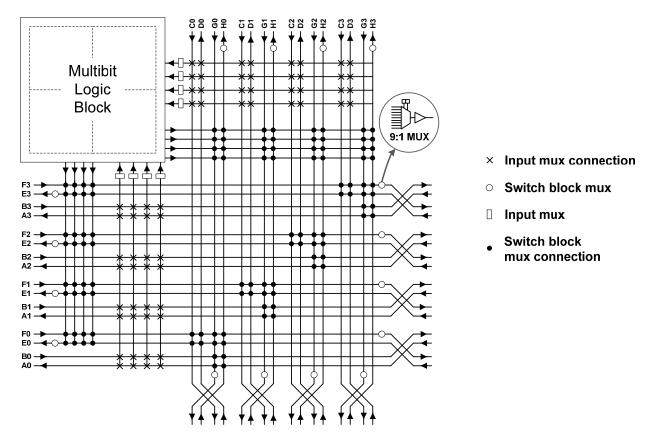

| Fig. 3.2. Bit-slice circuit implementation on a conventional FPGA tile                    | 32 |

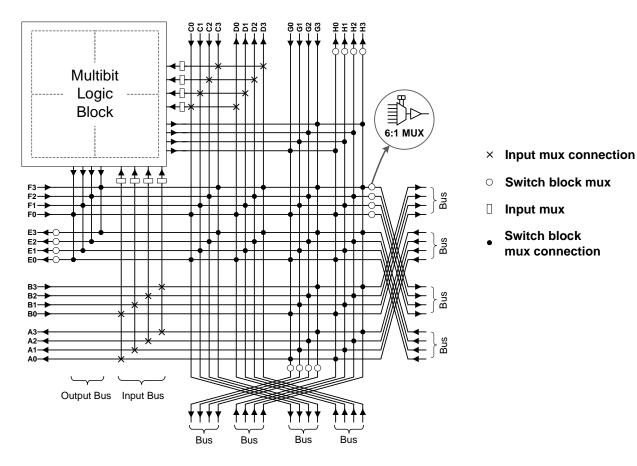

| Fig. 3.3. Bit-slice circuit implementation on a FPGA tile with routing buses              | 34 |

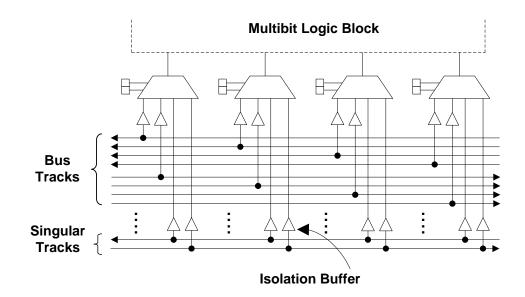

| Fig. 4.1. Multi-bit logic block input connections                                         | 39 |

| Fig. 4.2. Switch block with multi-bit logic block output connections                      | 40 |

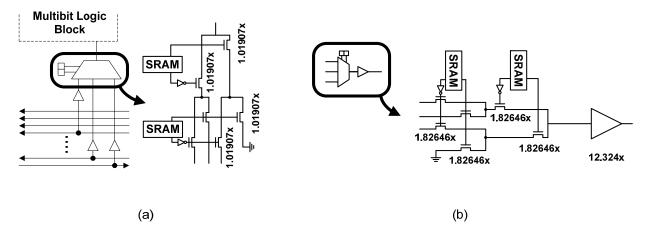

| Fig. 4.3. Input and routing switch multiplexors implemented as a pass-transistor tree     | 41 |

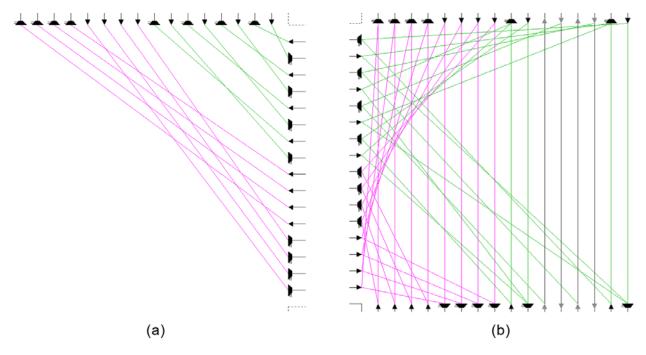

| Fig. 4.4. Core switch block (disjoint topology)                                           | 45 |

| Fig. 4.5. Corner (a) and fringe (b) switch blocks (disjoint topology)                                    | 46 |

|----------------------------------------------------------------------------------------------------------|----|

| Fig. 4.6. Switch block connection pattern generation                                                     | 47 |

| Fig. 4.7. Input and Output connection buses from VPR (MB-FPGA) output                                    | 48 |

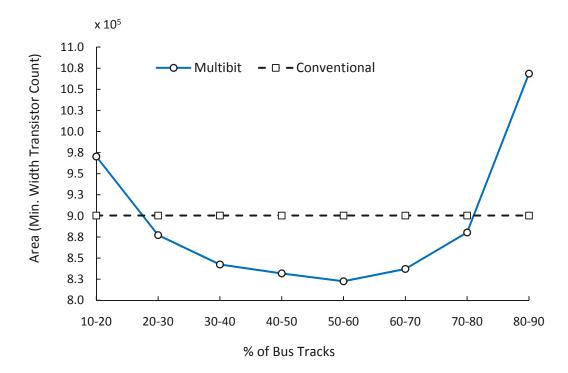

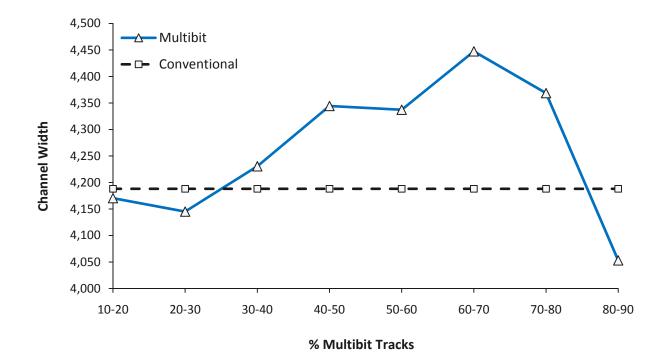

| Fig. 5.1. Area as a function of the percentage of multi-bit tracks                                       | 52 |

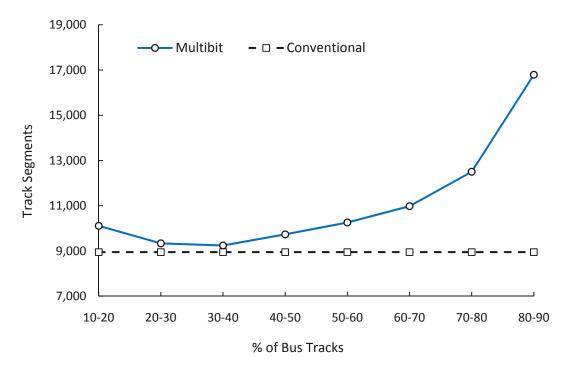

| Fig. 5.2. Number of track segments as a function of the percentage of multi-bit tracks                   | 55 |

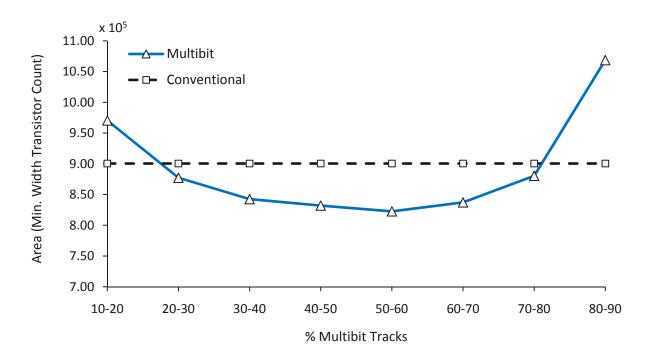

| Fig. A.1. Area as a function of the percentage of multi-bit tracks ( $F_{cif} = F_{cic} = .4$ )          | 60 |

| Fig. A.2. Channel width as a function of the percentage of multi-bit tracks ( $F_{cif} = F_{cic} = .4$ ) | 62 |

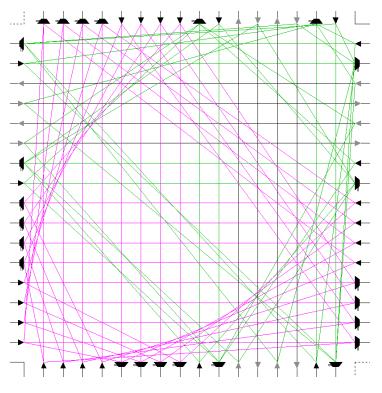

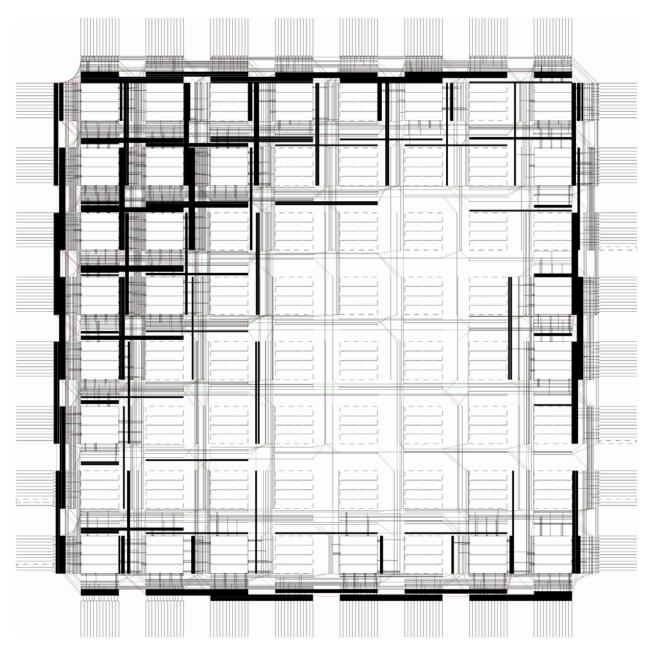

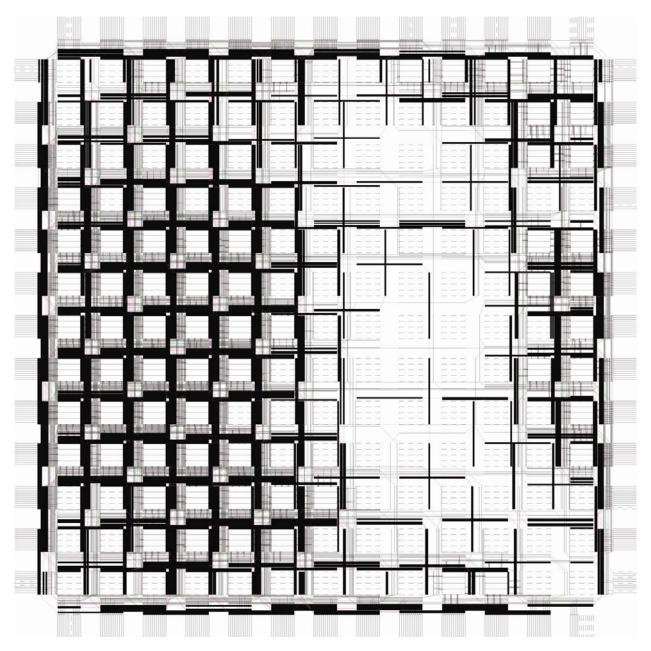

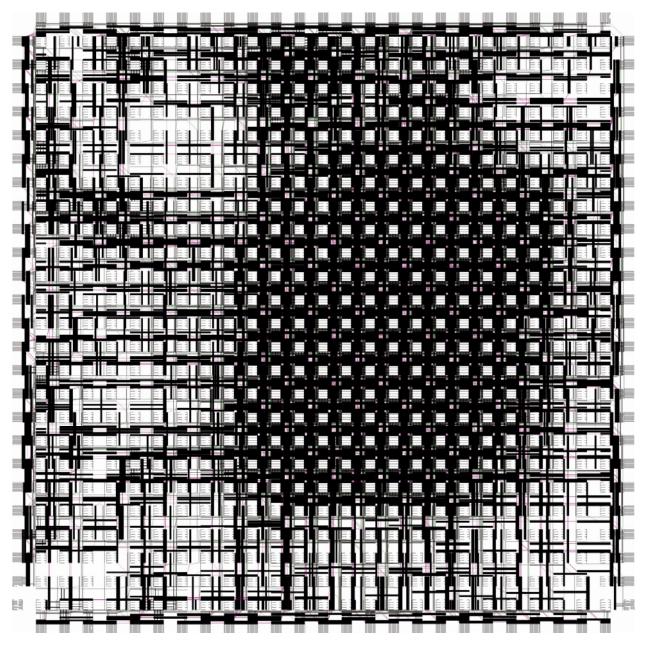

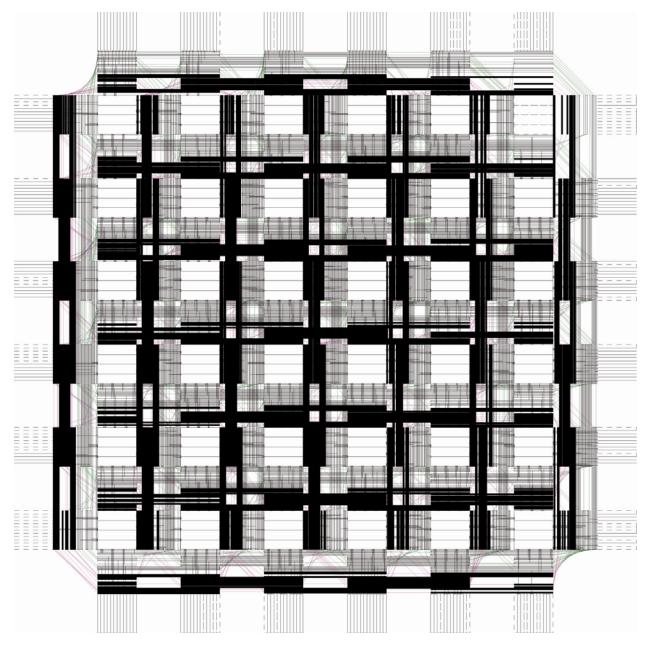

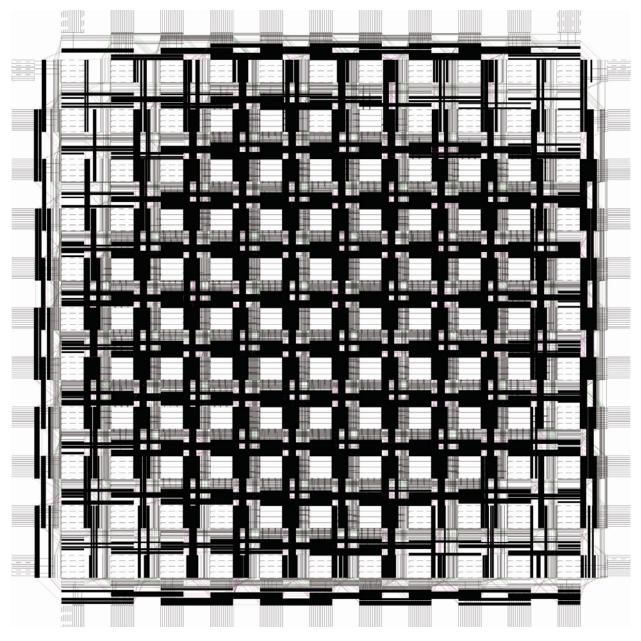

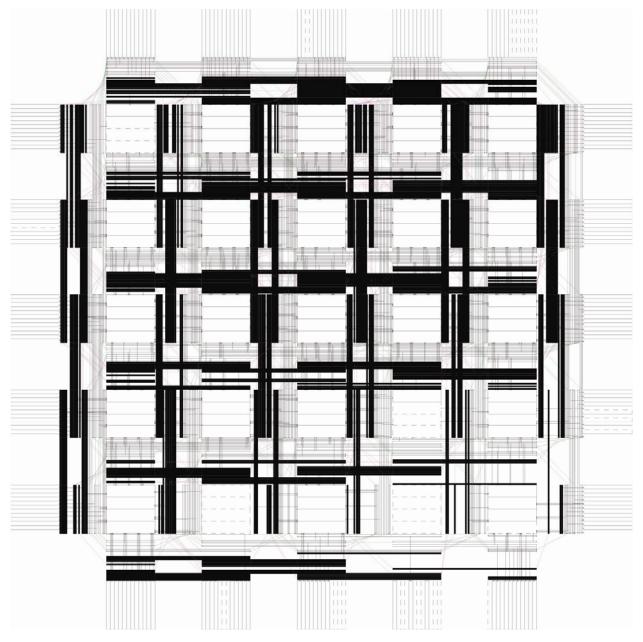

| Fig. B.1. Routed nets of circuit: code_seq_dp                                                            | 64 |

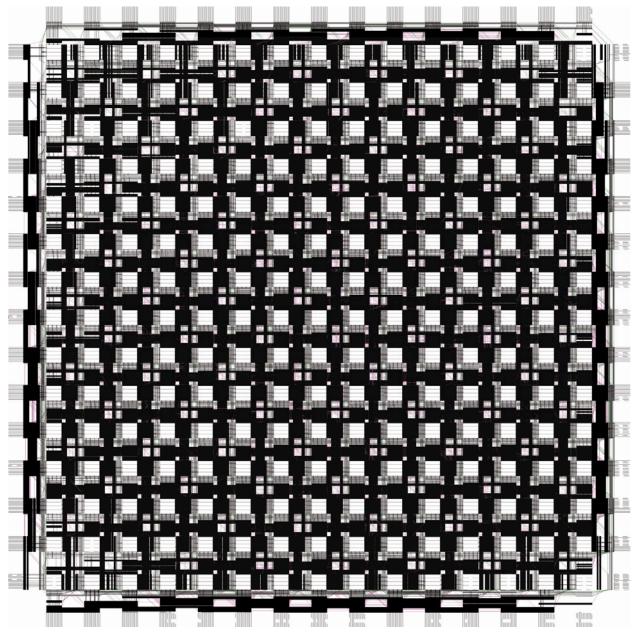

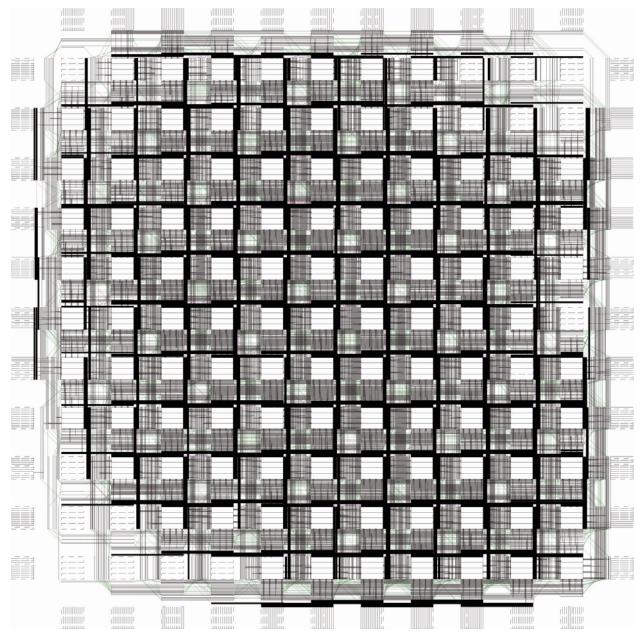

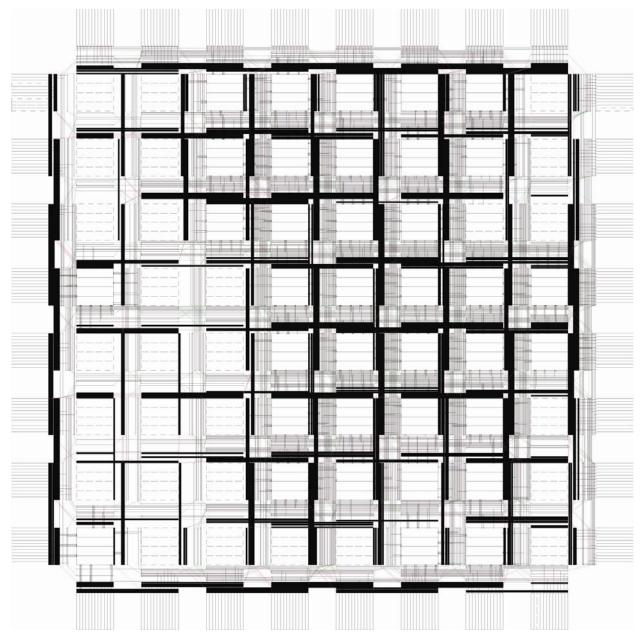

| Fig. B.2. Routed nets of circuit: dcu_dpath                                                              | 65 |

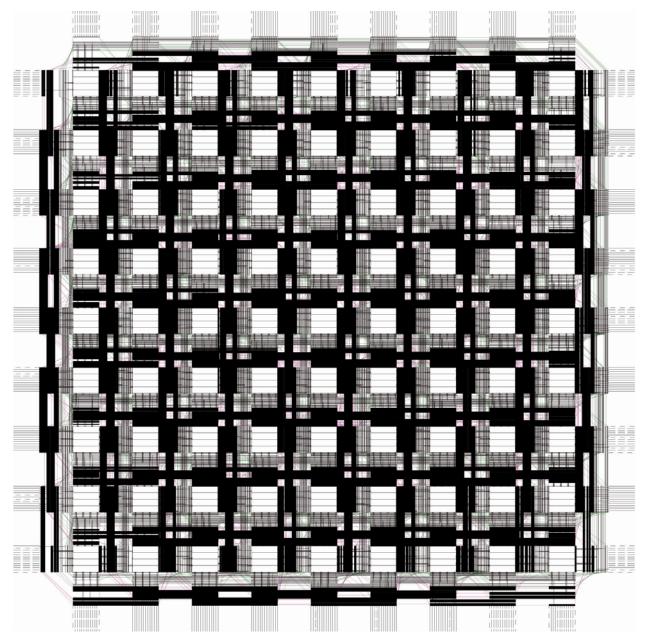

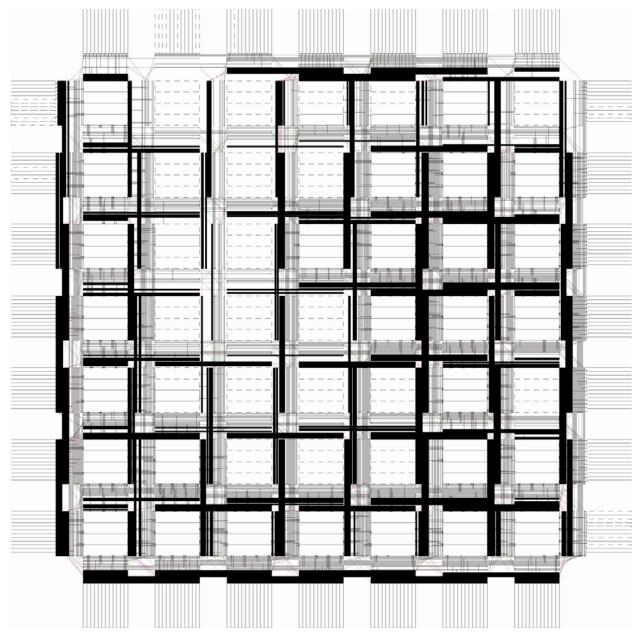

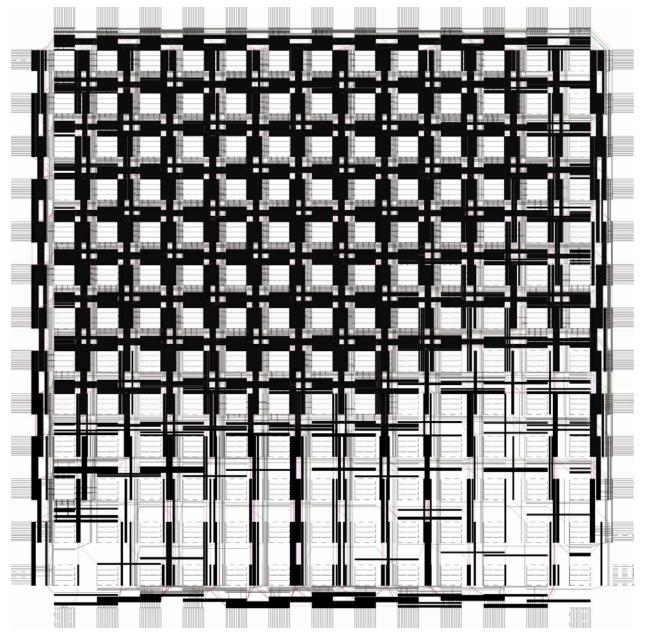

| Fig. B.3. Routed nets of circuit: ex_dpath                                                               | 66 |

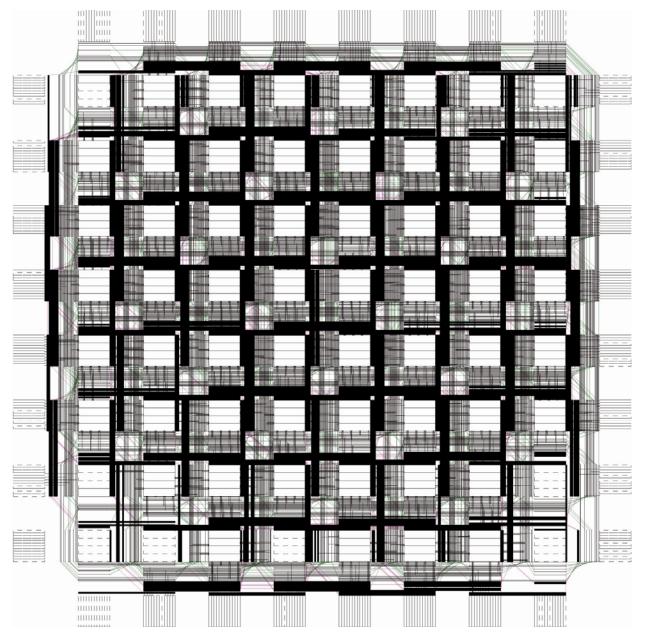

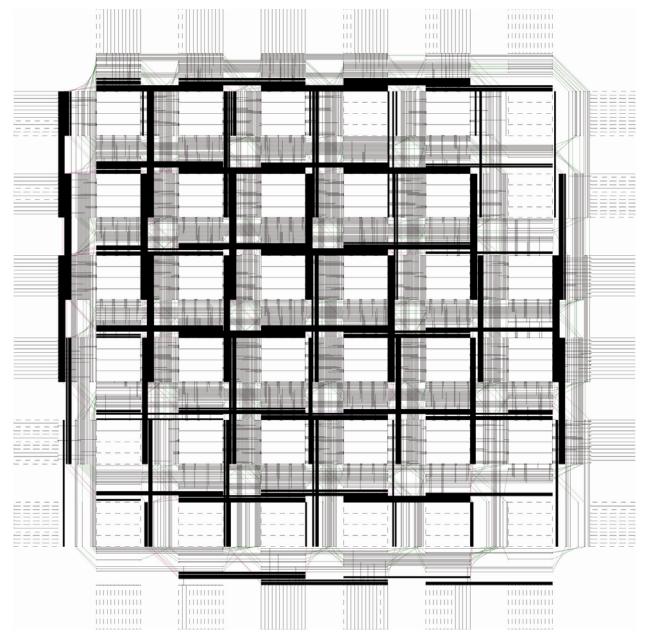

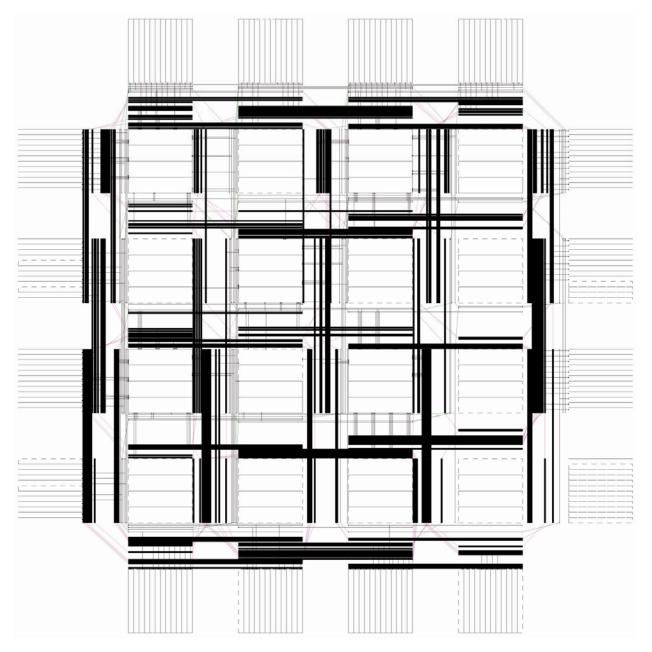

| Fig. B.4. Routed nets of circuit: exponent_dp                                                            | 67 |

| Fig. B.5. Routed nets of circuit: icu_dpath                                                              | 68 |

| Fig. B.6. Routed nets of circuit: imdr_dpath                                                             | 69 |

| Fig. B.7. Routed nets of circuit: incmod                                                                 | 70 |

| Fig. B.8. Routed nets of circuit: mantissa_dp                                                            | 71 |

| Fig. B.9. Routed nets of circuit: multmod_dp                                                             | 72 |

| Fig. B.10. Routed nets of circuit: pipe_dpath                                                            | 73 |

| Fig. B.11. Routed nets of circuit: prils_dp                                                              | 74 |

| Fig. B.12. Routed nets of circuit: rsadd_dp                                                              | 75 |

| Fig. B.13. Routed nets of circuit: smu_dpath                                                             | 76 |

| Fig. B.14. Routed nets of circuit: ucode_dat                                                             | 77 |

| Fig. B.15. Routed nets of circuit: ucode_reg                                                             | 78 |

## List of Abbreviations

| FPGA    | Field Programmable Gate Array           |

|---------|-----------------------------------------|

| CLB     | Configurable Logic Block                |

| BLE     | Basic Logic Element                     |

| MUX     | Multiplexor                             |

| CAD     | Computer-aided Design                   |

| VPR     | Versatile Placement and Routing         |

| CMS     | Configuration Memory Sharing            |

| MB-FPGA | Multi-bit Field Programmable Gate Array |

| LUT     | Look-up Table                           |

| SRAM    | Static Random Access Memory             |

| ASIC    | Application Specific Integrated Circuit |

| I/O     | Input/Output                            |

## **Chapter 1 : Introduction**

Developed in 1984, Field Programmable Gate Arrays (FPGAs) are user programmable integrated circuit devices which have the ability to implement almost any digital circuit. FPGAs consist of blocks containing simple digital logic interconnected by channels of routing wires and programmable electrical switches. Circuits are implemented on FPGAs by programming the electrical switches to connect logic blocks together to form larger and more complex circuits. Programming requires only a few minutes thus making hardware verification and upgrades relatively effortless as design changes or corrections can be performed by reprogramming the FPGA. Comparable technologies such as standard cell-based ASICs (Application-Specific Integrated Circuit) require a new integrated circuit to be manufactured for each design. Additionally, FPGAs are programmed via specialized Computer-Aided Design (CAD) tools which are cheaper to obtain than comparable Electronic Design Automation (EDA) tools for ASIC designs. In summary, circuits designed on FPGAs have an advantage of lower nonreoccurring engineering (NRE) costs and shorter time-to-market. FPGAs are the ideal for implementation of small to medium volume designs or prototyping digital circuits prior to implementation using standard cell based technologies.

Modern FPGAs are densely packed devices, containing more than 800,000 logic elements with the ability to operate at clock speeds of 600MHz or more [1] [2]. Despite these features, the programmability of FPGAs incurs a cost. The addition of programmable logic and switches forces circuit implementations on FPGAs to be slower and consume more area than those implemented on ASICs. These programmable features contribute to the large size of FPGA implementations and thus make it more expensive to design applications for mass-production. Once programmed, it is observed that over 70% of the total FPGA area is devoted to the routing resources which interconnect the logic blocks [3]. The actual computational logic occupies the remaining FPGA area (which is typically less than 30%). This motivates FPGA designers to consider ways to reduce the area impact of routing resources as well as that of computational logic.

In general, FPGA are increasingly used to implement large arithmetic circuits which inturn demand, from FPGA vendors, an increase in the amount of logic elements in each generation of FPGAs. The wide range of applications employing arithmetic operations has also motivated FPGA vendors to include a variety of multiple-bit wide computing elements including embedded memory, Digital Signal Processors (DSP), processor cores and even hard intellectual property (IP) blocks.

Many of the applications implemented on FPGAs are arithmetic intensive and include large fractions of regularly structured components called datapaths. Typically, datapaths are composed of identical blocks of logic which process and transport several bits of data as a unit (called a *multi-bit signal*) at one time. The correlation between individual bit-based signals travelling from a common source to a common end introduces *regularity* among datapath circuits. This regularity can be preserved and exploited to increase FPGA area efficiency by employing multiple bit processing (multi-bit) architectural features. Specifically, multi-bit signals can be transported as a single unit on *multi-bit based routing tracks* to be processed by *multi-bit based logic blocks*. Unlike single-bit logic blocks which treat the signals at the input and output pins as independent bits of data, the signals at the input and output pins of multiple-bit logic blocks are processed as multiple-bit wide data. Subsequently, the signals at each pin are considered as unique bit positions of a wider multi-bit signal.

Since the release of Altera's Stratix II series of FPGAs [4], most commercial FPGAs have replaced bidirectional routing resources with buffered unidirectional routing resources. Unidirectional routing resources have been shown to be more area efficient while reducing delay and wire capacitance over bidirectional routing resources [5]. The work done in [5] also outlines the two major optimizations of unidirectional routing over bidirectional routing: 1) Using pairs of directional wires 2) Replacing tri-state drivers and track to track connections with non-tristate drivers and multiplexers respectively. While multi-bit connections using bidirectional routing have resulted in FPGA area savings, the behaviour of multi-bit connections employing unidirectional components is unknown.

The multi-bit architecture described in this work is an adaptation of the MB-FPGA architecture presented in [6] and contains groups of multi-bit unidirectional routing buses as well as singular unidirectional tracks (independent tracks to route non-mult-bit signals). We experimentally evaluate the area efficiency and performance of this architecture based on the methodology proposed in [7].

In order to experimentally investigate the effects of multi-bit signals on unidirectional routing, a set of datapath-rich benchmark circuits are implemented on multi-bit and non-multi-bit architectures. To this end, the Virtual Place and Route (VPR) CAD tool [8] employing placement and routing algorithms is used while modifications are made to support both multi-bit and unidirectional architectural features. In order to preserve the regularity (amount of related signals travelling from a common source to a common destination) of the benchmark circuits, datapath-oriented synthesis [9] and packing [10] tools are used to generate the netlists used during the placement and routing operations in this thesis.

### 1.1 Thesis Motivation

The motivation of this thesis centres on investigating how using multi-bit based connections on unidirectional routing resources affect FPGA area efficiency. In this research we determine the theoretical area savings of a purely routing bus-based FPGA tile over that of a conventional tile; both of which employ unidirectional routing. We then introduce the multi-bit architecture which employs both bus-based and singular unidirectional routing elements. In practical FPGAs, architectural aspects such as channel width and I/O connectivity are pre-fabricated and therefore the goal of this research is to determine a suitable architecture to efficiently implement datapathoriented applications. Previous studies [11] [12] [13] [14] [15] have proposed various FPGA architectures containing specialized computing elements that are designed to process multiple-bit wide data. None of the studies, however, have investigated the design of multi-bit routing resources that can effectively transport multiple-bit wide signals using unidirectional routing tracks.

### 1.2 Thesis Contribution

This thesis investigates the area and delay performance of a multi-bit FPGA architecture using unidirectional routing tracks and is the first study to do so. Furthermore, this research reflects the transition undertaken by academic and commercial FPGA designers towards conventional unidirectional routing architectures employing directional wires and non-tristate drivers.

In this research an analysis on the effect of routing resources on total FPGA area is presented. These area results are then compared to those of an equivalent architecture utilizing only routing buses and related connections. Both analyses take into account a transistor sizing of a modern process technology. Modifications to the routing resource graph and output display of the VPR tool are made to reflect the architecture under investigation. To conduct an empirical investigation, this work places and routes a set of pre-synthesized and pre-packed benchmark circuits of varying datapath regularities to measure the active area, track count and critical path delay. As it shall be shown, the multi-bit architecture is found to be more area efficient when implementing a wide range of datapath rich circuits over the conventional architecture without a significant effect on delay.

### 1.3 Thesis Organization

The thesis is organized as follows. Chapter 2 presents a background on FPGA architectures relevant and leading up to this work including two previous architectural studies regarding multibit based connections and unidirectional routing. Additionally, a review of the relevant academic CAD tools is presented. Chapter 3 analytically compares the theoretical advantages of an architecture using multi-bit connections over the conventional routing architecture. Chapter 4 describes the unidirectional multi-bit architecture including a description of logic and routing components modeled using a modern process technology (predictive technology models) to generate accurate area and delay results. Chapter 4 also presents the modeling of this architecture on a modified version of the VPR CAD tool (introduced in Chapter 2) to be used in evaluating the unidirectional multi-bit architecture described earlier in Chapter 4. Chapter 5 presents the results and analysis of the experiments. Finally, Chapter 6 concludes this thesis by providing a summary of the results and proposes future work.

## **Chapter 2 : Background**

This chapter presents background information on the architectural aspects of FPGAs, the CAD flow and related academic CAD tools used to implement circuits. Section 2.1 briefly reviews the various programmable technologies followed a discussion on the structure of logic components and routing networks of the bidirectional FPGA architecture. Furthermore, two prior architectures relevant to this work are reviewed. Section 2.2 describes the typical CAD flow used to implement circuits on FPGAs with bidirectional single-bit routing. Lastly, the CAD flow to implement datapath circuits on bidirectional multi-bit routing resources will be reviewed.

### 2.1 FPGA Architecture

The majority of modern FPGAs, including devices from Xilinx [16] and Altera [1], rely on static random access memory (SRAM) based programming technology. SRAM cells are used to program FPGA logic and routing components such as pass transistors, multiplexors and look-up-tables (LUTs). Other programming technologies include one-time programmable antifuses,

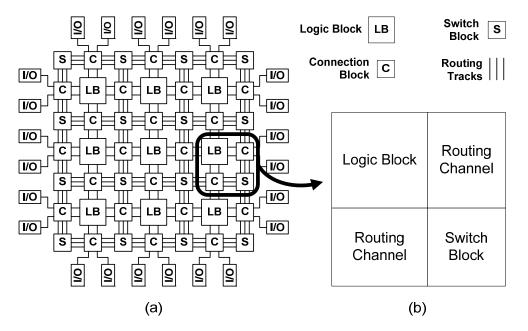

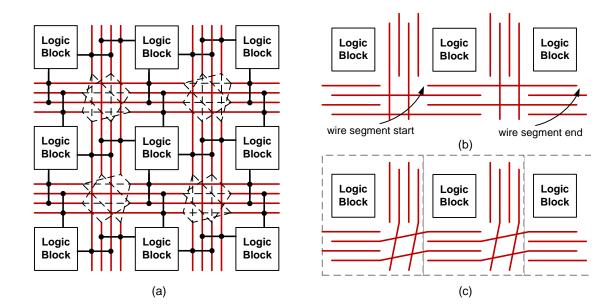

Fig. 2.1. Layout of an (a) Island-style FPGA and (b) a FPGA tile

erasable programmable read-only memories (EPROMs) and flash-erase EPROMs. This research focuses particularly on FPGAs employing SRAM cells.

The FPGA architectures considered in this research are based on the island style topology shown in Fig. 2.1 (a) which is segmented into *tiles* as shown in Fig. 2.1 (b). An FPGA tile consists of a *logic block*, one vertical and one horizontal *routing channel* containing a finite number of routing tracks and a *switch block* where the routing channels intersect. Connections between the routing tracks in a channel and the input/output pins of an adjacent logic block are made inside of a *connection block*. Finally the I/O blocks allow for external circuitry to interact with the FPGA.

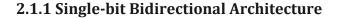

Fig. 2.2. Basic Logic Element (BLE)

#### 2.1.1.1 Logic Block Structure

Logic blocks contain the basic digital logic required to implement sequential or combinational circuits. Most current commercial FPGAs and academic architectures employ logic blocks containing a LUT paired with a register element. As such, this research will focus on these LUT-based logic blocks. Fig. 2.2 illustrates how a 4 input LUT and a D flip-flop are used to form a *Basic Logic Element* (BLE) which is situated inside a logic block. In general, an k-input LUT is implemented using a  $2^{k}$ :1 multiplexor and  $2^{k}$  SRAM cells, where any function of

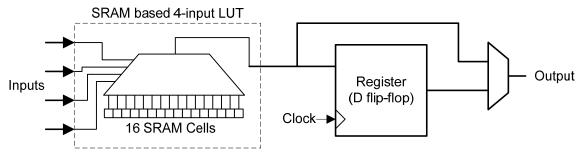

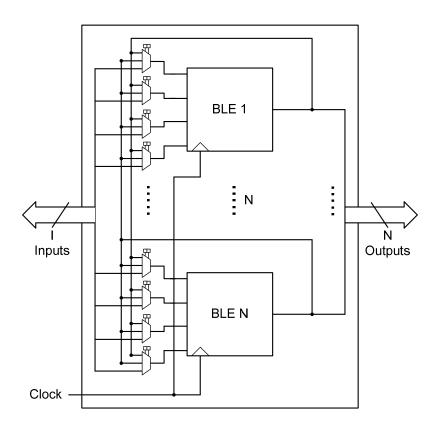

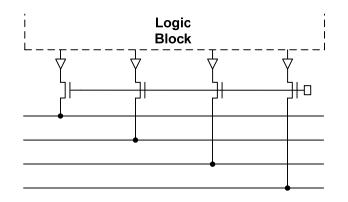

Fig. 2.3. Internal logic block structure

k-inputs (reflecting the truth-table values of the function) can be programmed into the 2<sup>k</sup> SRAM cells. The inputs to the LUT connect directly to the selection inputs of the multiplexor and the output of the multiplexor is synonymous with the LUT output. The work in [17] has shown that using a 4-input LUT (4-LUT) in FPGAs achieves the greatest area-efficiency by providing the most functionality per pin. Additionally, attaching a D flip-flop to the output of the 4-LUT results in a registered BLE output and allows for the implementation of sequential logic. As shown in Fig. 2.2, the output of the BLE is wired in such a way that either a registered or unregistered version of the 4-LUT function implementation can be chosen. Therefore this research employs the 4-LUT based BLE shown in Fig. 2.2 for the remainder of this thesis.

A typical logic block contains several BLEs connected together by local routing resources and is alternatively known as either a *logic cluster* or *configurable logic block* due to its 'clusterlike' topology. While the terms logic block and logic cluster are synonymous for this architecture, Section 2.1.2.1 will show how several logic clusters can be combined to form a multi-bit logic block. As shown in Fig. 2.3, a logic cluster can be described as having I inputs, N BLEs of size 4 and N cluster outputs. Each BLE input has access to any of the logically equivalent cluster inputs through the use of a multiplexor. The same multiplexors also allow BLE outputs to connect to any BLE input. Logic clusters are know to be 'fully connected' when the flexibility of BLE inputs allows connections to any of the cluster inputs or BLE outputs.

#### 2.1.1.2 Routing Architecture

Fig. 2.4. FPGA routing architecture with wire segments of length 2

Routing tracks and programmable switches enable logic blocks to be interconnected and allow signals to traverse the FPGA. The routing tracks are contained in routing channels which run adjacent to the logic blocks both horizontally and vertically. Each channel contains a fixed number of routing tracks on which signals travel in a bidirectional fashion. The number of routing tracks in a channel is represented by W – its channel width. Every routing track is composed of a series of wire segments of length L, where the L is the number of logic blocks that each wire segment spans. Fig. 2.4 (a) shows a 3x3 size FPGA layout with each routing channel

containing 4 routing tracks which consist of wire segments of length 2. It can be seen that the wire segments in every channel are staggered [18] (adjacent wire segments start and end at different locations in a channel), as some wires will continue through a switch block while others end. Fig. 2.4 (b) shows this staggering clearly as the logic block in the middle is able to connect to the adjacent logic blocks on either side using a single wire segment. Hence, the staggering of wire segments significantly increases the routing flexibility of the FPGA. Furthermore, Fig. 2.4 (c) shows wire segments which are staggered and shift upwards (called track shifts). Incorporating wire segments with track shifts and staggering start positions simplify the layout process of FPGAs, since a single tile is replicated to construct the complete FPGA. At the intersection of a vertical and horizontal channel, there exists a *switch block*, where individual wire segments are connected together allowing signals to continue on the same track or turn. The dashed lines in Fig. 2.4 (a) indicate connections from the end of one wire segment to the beginning of another inside a switch block. The I/O pins of logic blocks are connected to the routing network via programmable switches inside *connection blocks*.

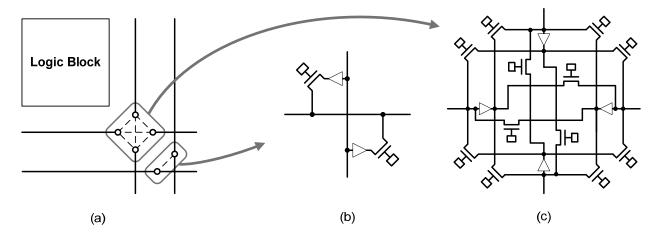

Groups of connections within a switch block can be classified as either full-switch

Fig. 2.5. A (a) switch block with (b) half and (c) full switch block connections

Fig. 2.6. Disjoint switch block topology (L=2) using half and full switch connections

connections or half-switch connections. Fig. 2.5 (a) illustrates these two types of switches in a simplified FPGA tile. Internal connections between wires that continue through a switch block are made using the half-switch shown in Fig. 2.5 (b). The full-switch pictured in Fig. 2.5 (c) shows the end point of a wire segment in any direction drives up to three other wire segments, all of which also end at this location. Both types of switch connections employ tri-state buffers.

The number and arrangement of both full-switch and half-switch connections inside a switch block are the function of its topology. Furthermore, the topology describes how many and specifically which tracks an ending wire segment can connect to. The most common switch block topologies include the *disjoint* topology [19] and the *Wilton* topology [20]. The results in [7] show that the disjoint topology is more area-efficient than the Wilton topology for wire segment lengths greater than 2 and have the same area efficiency as the *Wilton* for segment lengths equal to 2. Hence, the disjoint topology is used in this work, since the focus of this work is on architectures containing wire of length 2 and laying the foundation of longer wire lengths in future work. Fig. 2.6 (a) and (b) illustrate the connections of the disjoint topology in a switch block using half-switch and full-switch connections. A wire segment ending at this switch block

Fig. 2.7. Connection block with (a) input and (b) output connections

location connects to exactly 3 other wire segments beginning at this switch block with the same track position. To demonstrate this, take for example the horizontal wire segment 3 entering the switch block from the left in Fig. 2.6 (a). This segment connects to: the horizontal wire segment 3 on the opposite side, vertical wire segment 3 entering from the top and vertical wire segment 3 entering from the bottom. As mentioned before, full-switch connections are employed at wire segment endpoints, while half-switch connections occur at internal locations along a wire segment.

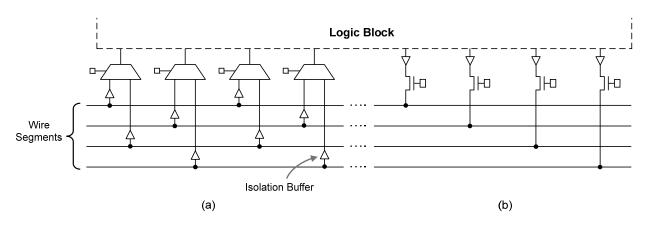

The final aspect in the architectural description of this FPGA is the connection block. The connection block house the individual connections from the routing tracks to the logic block output pins and the logic block input pins to the routing tracks. As shown in Fig. 2.7 (a), individual routing tracks connect to the inputs of a multiplexor whose output connects directly to a logic block input pin. The inputs and outputs are shown separately for clarity and simplicity. Notice in this example that each input connection multiplexor can select from 2 routing tracks in the channel. The selection of tracks is staggered to offer greater overall routing flexibility and reduce the amount of loading capacitance. In general, the proportion of tracks any input pin can connect to is denoted by  $F_{ci}$ . Additional buffers called *isolation buffers* are added to the input

connections to isolate the routing tracks from the capacitive effects of the input connections. Fig. 2.7 (a) shows how logic block output pins connect directly to the routing tracks using a driving buffer to propagate the output signal and a SRAM based pass transistor switch to control the connection. Here,  $F_{co}$  represents the proportion of tracks the output pin can connect to.

#### 2.1.2 Bidirectional Multi-bit Architecture

Fig. 2.8. Output connections using configuration memory sharing (CMS)

Prior research regarding an FPGA architecture optimized for datapath applications (DP-FPGA architecture) is described in [14]. The DP-FPGA study focused on designing heterogeneous blocks including a memory block, control block and a datapath block. The memory block could be configured to implement various types of memory architectures. The control and datapath blocks implemented non-datapath and datapath circuits respectively. The DP-FPGA architecture is the first study to make use of configuration memory sharing (CMS). As its name implies, configuration memory sharing involves sharing a single set of SRAM memory bits over multiple switch connections. Take for example the output connections in Fig. 2.7 (b) of the previous section. Fig. 2.8 shows how employing CMS on these output connections would reduce amount of SRAM bits required from 4 to 1 resulting in significant area savings. However,

Fig. 2.9. Multi-bit FPGA

the DP-FPGA study did not specify the architecture in detail or investigate the effectiveness of CMS utilization on the routing architecture.

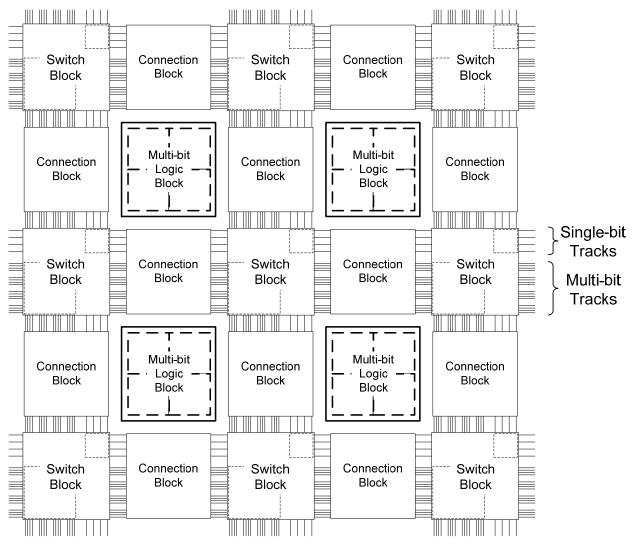

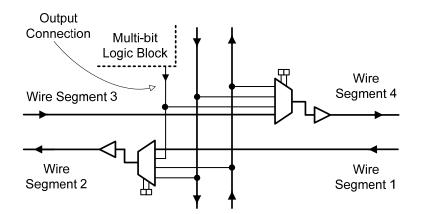

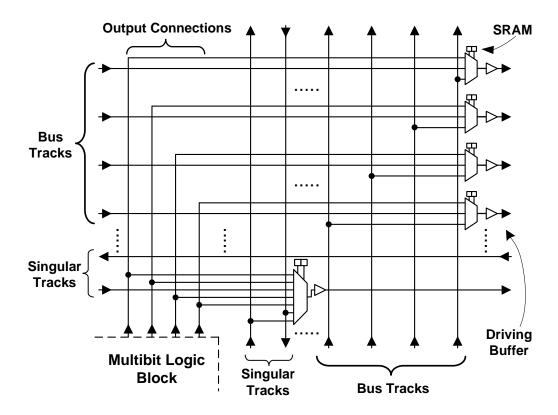

The *multi-bit* architecture, proposed and described in [21], is a continuation of the DP-FPGA work and is also based on the island style topology. Similar to the DP-FPGA architecture, the purpose of this architecture was to exploit the significant proportion of datapath signals in modern circuits to achieve overall FPGA area-efficiency. As Fig. 2.9 shows, the multi-bit architecture employs the same components described in the previous section (including logic

Fig. 2.10. Mapping of a 4-bit adder into a Multi-bit logic block

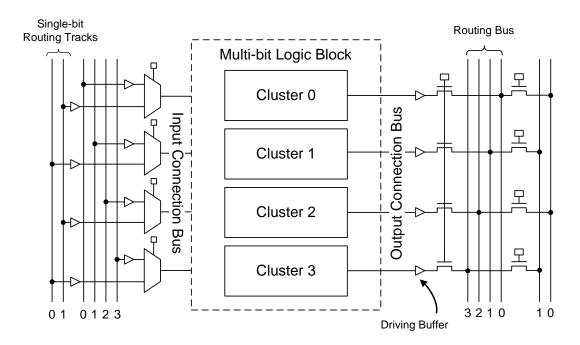

functions are somewhat different. The multi-bit architecture in Fig. 2.9 employs a special type of logic block called the multi-bit logic block which are connected to other multi-bit logic blocks using single bit routing tracks and groups of *routing buses* called multi-bit routing tracks.

#### 2.1.2.1 Multi-bit Logic Block

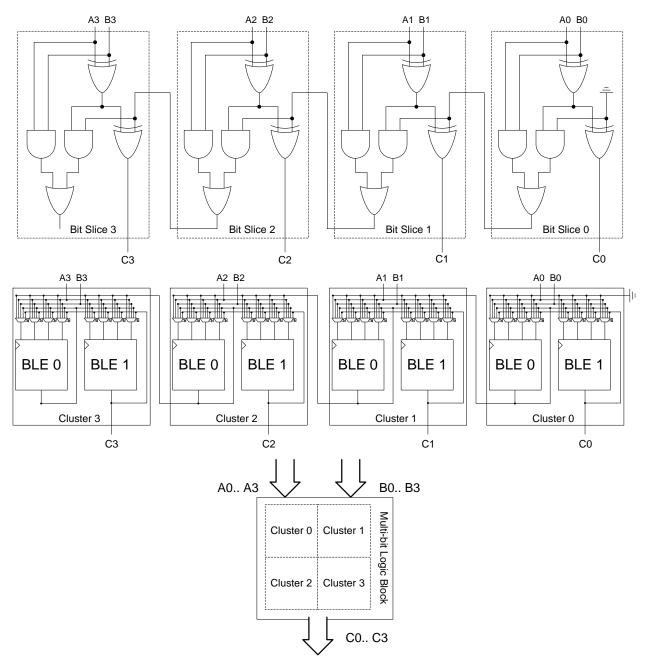

Recall in Section 2.1.1.1, how several BLEs can be grouped together using internal routing to form a logic cluster (or logic block). Similarly a multi-bit logic block involves grouping M logic clusters together to process M-bit computation, where M is known as the *granularity* of the architecture. Take for example, a 4-bit addition operation with inputs A0-A3, B0-B3 and the sum C0-C3. Fig. 2.10 shows how this addition operation can be partitioned into bit-slices, where each bit-slice encompasses a 2-bit adder with a carry signal feeding the next bit-slice. Assuming the logic in each bit-slice can fit 2 interconnected BLEs, these two BLEs form a logic cluster. The resulting 4 logic clusters form a multi-bit logic block with 2 4-bit wide *input connection buss* and 1 4-bit wide *output connection bus*. In general, the number of inputs and outputs are still represented by I and N respectively. Recall from Section 2.1.1.1, the number of logic block outputs reflects the exact number of BLEs the logic block contains. In the multi-bit architecture, N, actually represents the number of output buses, while the total number of output pins is  $I \times M$ .

#### 2.1.2.2 Multi-bit Routing

The routing network of the multi-bit architecture is similar in design to the bidirectional single-bit routing architecture described in Section 2.1.1.2. The difference lies in the addition of *M*-bit wide routing buses to the existing channels containing the *single-bit routing tracks* as described in Section 2.1.1.2. The individual tracks in a routing bus are known as *multi-bit routing tracks*. The multi-bit routing tracks transport the datapath oriented signals from one multi-bit logic block to another as a single unit. The single-bit routing tracks transport controls signals or any other single-bit signal throughout the FPGA. The amount of multi-bit routing

Fig. 2.11. Input and output connections of the connection block

tracks in a channel (the channel width) is represented by  $W_c$ , while the amount of single-bit routing tracks in a channel is defined as  $W_f$ .

A simplified version of the input and output connections of a multi-bit logic block is shown in Fig. 2.11 and shown separately for clarity. Each input pin of the multi-bit logic block is connected to a fixed number of single-bit tracks and multi-bit routing tracks. The proportion of single-bit tracks an input pin connects to is represented by  $F_{cif}$  while the number of routing buses that an input pin connects to is represented by  $F_{cic}$  [21]. Similarly the output pins are connected to a fixed proportion of single-bit tracks and routing buses represented by  $F_{cof}$  and  $F_{coc}$ respectively. While the single-bit tracks can follow any connection pattern, routing bus connectivity requires the input and output pins to be restricted to the specific bus index (or bit position) they represent. Take for example the output of cluster 0 in Fig. 2.11. Cluster output 0 is the 0<sup>th</sup> bit in the output connection bus; therefore, it may only connect to 0<sup>th</sup> track of the routing bus. Similarly, multi-bit logic block inputs must connect to routing buses with the same bus index.

The multi-bit switch block accommodates both single-bit switch connections and multi-bit switch connections. Within the switch block, each type of routing track is segregated from the other, meaning multi-bit tracks connect only to other multi-bit tracks and single-bit tracks connect only to other single-bit tracks. While this allows the flexibility to implement different switch block topologies for each routing track type, the disjoint switch topology [19] defines the switch arrangement for both multi-bit and single-bit switch connections. The single-bit tracks are connected together in the same manner as outlined in Section 2.1.1.2 using half and full switch block connections. Conversely the switches connecting each *M*-bit wide routing bus to another share a single set of configuration memory (CMS). Similar to the input and output connections, the multi-bit routing tracks in a bus must connect to other multi-bit tracks with the same index within a switch block.

#### 2.1.3 Single-bit Unidirectional Routing Architecture

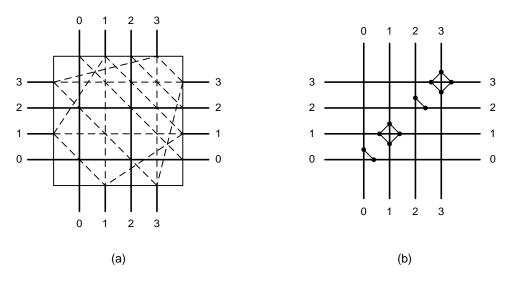

In both the bidirectional single-bit and multi-bit architectures, the bidirectional wire segments are connected together and driven using tri-state buffer switches inside a switch block (one for each direction). The study done in [5] demonstrates that 50% of these switches remain unused once the FPGA has been fully configured. Conversely, unidirectional wires only employ a single driver per direction per wire. This results in a much higher utilization of the programmable switches, especially if CAD tools can approximately match the amount of signals to the number of tracks in each direction. It is important to note that the number of tracks *W* inside a channel must be a multiple of 2. Given an FPGA tile with 1 track (2 wire segments connected using bidirectional switches); it can be observed that an equivalent tile with the same amount of

Fig. 2.12. Conventional switch block with unidirectional wires of length 2

unidirectional switches requires twice as many wires. The work in [5] shows that in order for unidirectional routing to be area efficient, the total number of routing tracks must be less than twice the amount of equivalent bidirectional tracks.

In this architecture, the programmable switches within the switch blocks (routing switches) are implemented using non-tristate drivers and multiplexors. Using non-tristate driver offers an advantage of greater area savings due to the removal of the SRAM based tri-state functionality. The multiplexor offers greater track connection flexibility within a switch block. The use of a multiplexor eliminates the need for full and half type connections as a multiplexor can switch

between wire segment midpoints and ends. As in both the general and multi-bit architecture, the conventional architecture employs the disjoint topology inside switch blocks. Fig. 2.12 illustrates switch block containing unidirectional wire segments of length 2 and associated programmable switches. The staggered routing is exemplified in this example as tracks 2, 3, 6 and 7 in both channels end at this switch block, while tracks 1, 2, 4 and 5 continue through. The arrows at the fringes of the switch block mark the directions of each track. The multiplexors in Fig. 2.12 show connections from the midpoints and endpoints of nearby wires with a single input line and black circles to indicate individual connections. The unconnected input line represents connections to logic block outputs which will be discussed next.

Fig. 2.13. Switch block connections for a horizontal channel

The connection blocks in the conventional architecture lack direct connections to tracks from logic block outputs, containing only input connections. Due to design restrictions, the outputs of multi-bit logic blocks can only connect to the multiplexors of wire segments that begin nearby. Fig. 2.13 shows a multiplexor base switch and its connectivity to a multi-bit logic output in a horizontal channel. The SRAM cells can be programmed to select between the multi-bit logic block output and any of the three track to track connections. The input connections are structured exactly as in the single-bit bidirectional architecture.

### 2.2 FPGA CAD Algorithms and Tools

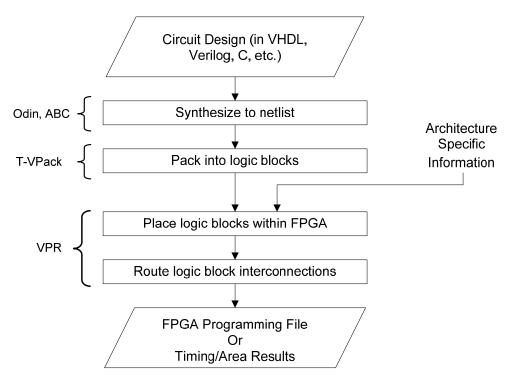

Fig. 2.14. FPGA CAD flow

In order to practically implement circuit designs on an FPGA, the use of CAD tools are necessary. CAD tools allow a designer to input a high-level description of a circuit which is then converted into a programming file or alternatively, in the case of VPR, a textual and graphical description of the FPGA implementation. The programming file specifies the state of every programmable switch and configuration bit on the FPGA. These CAD tools, both commercial and academic, follow a set of steps called a CAD flow as illustrated in Fig. 2.14. This section will first briefly describe the *synthesis*, *packing*, *placement* and *routing* elements of the CAD flow. A more in-depth discussion of the *routing* step, where the architectural changes of this research are made, will then be presented.

#### 2.2.1 Synthesis & Packing

Given a circuit, described in either a hardware description language or schematic form, the synthesis stage converts such a description into a netlist of simple gates (NAND, NOR, Inverter, etc.). The netlist of gates then undergoes a process of optimization, independent of any technology process, where the logic is reduced to a minimum or near-minimum amount of gates. This process of logic minimization must be completed within a reasonable amount of computing time. The new optimized netlist of gates is then technology-mapped into look-up tables and flip-flops [22] [23] [24]. If in the case of the VPR CAD flow, the circuit is described in Verilog hardware description language, the open-source tool Odin [25] can be used to initially synthesize the circuit into a basic netlist of gates. This netlist can then be optimized using the ABC [26] synthesis and verification tool.

The second step in the CAD flow, called packing, groups LUTs and flip-flops (up to a limit of N) into logic clusters. The packer must take into consideration pre-determined architectural parameters such as the maximum number of inputs, the maximum number of outputs and whether clock signals are needed (and how many distinct clock signals) to implement sequential logic. The packing operation attempts to minimize the amount of routing connections between logic blocks. In addition, the packing process attempts to pack as many highly connected LUTs into logic blocks (up to their limit N) therefore reducing the total number of total logic blocks required. Timing driven packing involves attempting to reduce the number of connections between logic clusters on the critical path in addition to the packing process described above. In the case of the VPR CAD flow, T-VPack is the stand alone packing tool described in [27] which can perform timing or non-timing driven packing.

#### 2.2.2 Placement & Routing

The placement and routing operations in Fig. 2.14 are performed by a single program – VPR and will be described in further detail in this section. Also illustrated in Fig. 2.14 are two necessary inputs to this process: 1) The packed and optimized logic block netlist from the previous step and 2) a file containing architectural specific information about the target FPGA – the architectural description file.

#### **VPR** Placement

The placement process of VPR is conducted using the simulated annealing algorithm [28]. This algorithm is derived from the annealing process in metallurgy wherein metals are heated and then slowly cooled to alter the materials' physical properties (improve strength, soften for cutting and shaping etc.). Initially the placer will randomly position all the logic blocks in the netlist to available locations on an FPGA. It will then move a randomly selected logic block either by swapping it with another logic block's physical location or moving it to an unoccupied spot to create a new placement. The move is then evaluated based on a *cost function* which measures the quality the new placement against the previous placement. The process is repeated multiple times in order to reach a final placement solution. After each iteration, a decision is made to either keep or reject each move based on the change in the cost before and after the move. If the cost is less after the move, it will always be accepted. Should the cost increase, the move may still be accepted even though the placement is worse in the hope that subsequent moves may yield a better placement result. This probability is modeled mathematically and a key parameter called the *temperature* determines how likely a move is accepted despite the cost increase the placement causes. Initially, the temperature is set very high allowing almost all moves to be accepted. The temperature is then gradually reduced at each subsequent move

allowing fewer bad moves to be accepted till at a temperature of zero, where only good moves are accepted. The rate at which the temperature is reduced and the number of moves attempt at each set temperature value is defined in the *annealing schedule*.VPR uses an adaptive annealing schedule, which adapts to a wide range of FPGA architectures, cost functions and circuit sizes [7] while consuming a reasonable amount of computation time.

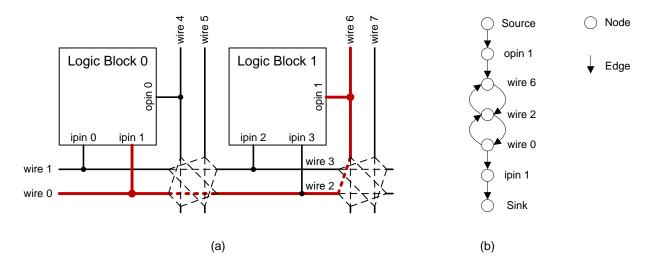

#### **VPR** Routing

The VPR router has the flexibility of implementing a variety of architectures through the use of directed graphs. A directed graph, or *routing-resource graph* (as it is know in VPR) [29], is generic and simple enough for any architecture to be represented. Given the architectural description file, an internal graph generator creates a detailed routing resource graph representation of the desired FPGA [7]. The architectural description file (described fully in [7]) contains parametric information of the architecture such as the number of logic block input pins (I), the switch block topology and  $F_c$  values for logic block outputs. The actual routing operation, graphical output and performance analysis all rely on the routing-resource graph. Should the need arise to use a new FPGA architecture, only the routing-resource graph requires

Fig. 2.15. Modelling (a) a connection between two output pins on (b) a directed graph

modification. This is particularly convenient since this research involves investigating the effects of unidirectional and multi-bit architectural features.

Inside the routing-resource graph, wires and logic block pins are represented by *nodes* while connections between two nodes (or switches) are represented by *edges*. Fig. 2.15 (a) illustrates a path originating from 'opin 1' of logic block 1 and terminating at 'ipin 1' of logic block 0, where the resources required to connect these two points are highlighted in red. Fig. 2.15 (b) shows the directed graph equivalent of the path in Fig. 2.15 (a). Recall in Section 2.1.1.1, the input and output pins of logic blocks are logically equivalent. This logical equivalence is represented in the routing-resource graph by having connections originating and terminating at common logical points called *sources* and *sinks* respectively. Accordingly, the pins 'opin 1' and 'ipin 1' are labeled as the source and sink respectively in Fig. 2.15 (b). Since Fig. 2.15 (a) depicts a bidirectional routing architecture, the connections between wire 6, wire 2 and wire 0 are drawn as pairs of directed edges in Fig. 2.15 (b).

VPR uses the negotiated congestion based method of the Pathfinder algorithm [29] with optimizations to better optimize delay. When searching for the best path for each net, conflicts will inevitably occur when choosing routing resources which can only be assigned to a single net. When a particular routing resource is temporarily assigned to several nets, it is called a *congested* routing resource. The Pathfinder algorithm executes multiple routing iterations to resolve this contention for routing resources. In the first routing iteration, each connection is routed on a minimum delay path and ignores routing congestion. In subsequent routing iterations, each net is ripped up and re-routed using a maze routing algorithm [30] until all occurrences of congestion are resolved. After each iteration, the costs of congested routing resources for routing resources are increased to give more timing-critical nets priority when multiple nets compete for

the same routing resources. These costs take into account the net delays (Elmore delay of each source to sink connection) and congestion of routing resources from all previous iterations.

#### 2.2.3 MB-FPGA CAD Flow

The MB-FPGA CAD flow is similar to the CAD flow described in Fig. 2.14 but also contains support for recognizing datapath components and preserving their regularity through the CAD process. The distinguished features of each step in the CAD flow are outlined as follows:

- The EMC (Enhanced Module Compaction) synthesis algorithm [9] attempts to optimize logic across bit-slices for area efficiency while retaining their regularity.

- The CNG (Coarse-Grain Node Graph) packing algorithm [10] packs identical LUTs and register elements (flip flops) from neighboring bitslices. The packer optimizes the packed clusters for area efficiency and delay of critical nets.

- The MB-FPGA Placer [31] is similar to the VPR placer described in Section 2.2.2 as it contains the same annealing schedule and cost functions. The MB-FPGA placer differs in that it moves blocks of logic (within a square grid) on two hierarchal levels: as bit-sized clusters and multi-bit sized logic blocks.

- The CGR (Coarse-Grain Resource) Routing Algorithm routes two different types of tracks (multi-bit and single-bit). The router compensates overused tracks by committing signals to under used tracks, even if it means routing single-bit signals on multi-bit tracks (or vice versa multi-bit wide signals on single-bit tracks). In doing so, the router balances the overall usage of all routing tracks.

This chapter has presented background information on basic FPGA architectural components along with a review of previous work on mult-bit architectures and unidirectional routing architectures. It is shown how the proposed features of both these architectures can improve routing area efficiency. The information on the VPR and MB-FPGA CAD flows will serve as a basis for the design of a unidirectional multi-bit compatible CAD tool for empirical evaluation.

# **Chapter 3 : Unidirectional Bus Connections**

This chapter defines the conventional unidirectional routing architecture and discusses unidirectional bus connections in detail. The theoretical area savings of an ideal architecture using unidirectional bus connections is compared to those of the conventional routing architecture. This serves as a motivation to empirically determine the actual performance of the unidirectional multi-bit architecture in Chapter 6.

### 3.1 The Conventional Routing Architecture

The conventional architecture employs the same multi-bit logic block of granularity M as discussed in Section 2.1.2.1. The choice of using a multi-bit logic block over the general logic block (consisting of a single cluster) is justifiable for two reasons: 1) Consider if both the unidirectional multi-bit architecture and the conventional architecture employ multi-bit logic blocks. Therefore the investigation can focus on the effect of the routing fabric on area-efficiency rather than a 2 dimensional problem involving variations in both routing and logic block design. 2) In addition to the studies in [11], [12], [13], [14], [15] and [21] which employ multi-bit logic block types, such as DSPs and multi-bit addressable memory blocks, to process multi-bit signals. Motivated by this trend, this work compares the efficiency of the conventional architecture against the unidirectional multi-bit routing architecture for connecting multi-bit logic blocks.

Unidirectional routing tracks and related switch block resources are employed in the conventional architecture with routing channels consisting of W unidirectional routing tracks. Recall from Section 2.1.3, W must always be an even number of tracks to accommodate signals travelling in both the forward and reverse directions. In this research, M=4, L=2, I=10 and N=4

are used because the previous work in [21] has shown this combination of values results in good area results. Since this architecture uses a multi-bit logic block, it is important to note that N and I actually represent the number of output buses and input buses of size M respectively. However since the conventional architecture does not include any routing bus tracks to specifically route datapath signals, all individual input and output bus connections are treated as fully independent one-bit wide input and output connections. The total number of input connections is  $\left[F_{ci} \times \frac{W}{2}\right] \times$ 2 where  $F_{ci}$  represents the fraction of routing tracks each input pin connects to. The total number of output connections is  $\left[F_{co} \times \frac{W}{2}\right] \times 2$  where  $F_{co}$  represents the fraction of routing tracks each output pin connects to. Recall from Section 2.1.3, the output connections can only be made to the routing switch multiplexors of wire segments that begin nearby. Also recall from Section 2.1.1.2, in order to create a tile-based FPGA design, the starting points of wire segments must be staggered and shifted in fixed intervals. These two factors determine the number of available routing tracks that an output pin can connect to. The number of wire segments beginning in switch blocks on either side of a logic block is represented by  $\frac{W}{L}$ . The parameters  $F_{ci}$  and  $F_{co}$  are set to 0.5 and 0.25 respectively and the disjoint switch block topology is used.

## 3.2 Unidirectional Routing Bus Connections and Their Advantages

In this research, the active area (the area occupied by transistors) is measured to estimate the total FPGA area including computational logic and routing resources. Specifically, this area is measured in terms of minimum-width transistor area and calculated using the following equation:

Area =

$$\sum_{\text{All Transistors}} \left( 0.5 + \frac{\text{Drive Strength of Current Transistor}}{2 \times \text{Drive Strength of Minimum Width Transistor}} \right)$$

While the previous work in [21] has confirmed the large impact of bidirectional single-bit routing resources on total FPGA area (previously discovered by [3]), no study has found the impact of unidirectional single-bit routing resources on total FPGA area. Therefore, Table 3.1 summarizes the routing resource area (input and switch block connections) and the total area of an FPGA tile (including the area of a single-bit logic block) employing unidirectional single-bit routing resources for increasing values of W.

| W   | $\mathbf{A}_{\mathrm{input}}$ | $\mathbf{A}_{\mathrm{sw.block}}$ | $\mathbf{A}_{\mathbf{routing}}$ | A <sub>FPGA</sub> | $\mathbf{A}_{\mathbf{routing}}/\mathbf{A}_{\mathbf{FPGA}}$ |

|-----|-------------------------------|----------------------------------|---------------------------------|-------------------|------------------------------------------------------------|

| 4   | 396                           | 262                              | 658                             | 8,507.72          | 7.73%                                                      |

| 8   | 873                           | 524                              | 1397                            | 9,246.96          | 15.11%                                                     |

| 12  | 1350                          | 845                              | 2195                            | 10,044.64         | 21.85%                                                     |

| 16  | 1587                          | 1049                             | 2635                            | 10,485.44         | 25.13%                                                     |

| 20  | 2064                          | 1369                             | 3433                            | 11,283.12         | 30.43%                                                     |

| 24  | 2301                          | 1573                             | 3874                            | 11,723.92         | 33.04%                                                     |

| 28  | 2538                          | 1894                             | 4432                            | 12,281.61         | 36.08%                                                     |

| 32  | 2775                          | 2098                             | 4872                            | 12,722.40         | 38.30%                                                     |

| 36  | 3252                          | 2418                             | 5670                            | 13,520.09         | 41.94%                                                     |

| 40  | 3489                          | 2622                             | 6111                            | 13,960.88         | 43.77%                                                     |

| 48  | 3963                          | 3146                             | 7109                            | 14,959.36         | 47.52%                                                     |

| 52  | 4200                          | 3467                             | 7667                            | 15,517.05         | 49.41%                                                     |

| 64  | 4911                          | 4195                             | 9106                            | 16,956.32         | 53.70%                                                     |

| 88  | 6574                          | 5768                             | 12342                           | 17,754.01         | 55.78%                                                     |

| 100 | 7285                          | 6613                             | 13898                           | 20,191.77         | 61.12%                                                     |

| 120 | 8470                          | 7866                             | 16336                           | 21,747.94         | 63.90%                                                     |

Table 3.1 Impact of Routing on Total FPGA Area

The transistor sizing of routing resources for all area calculations in Table 3.1 are based on the 90nm process specifications in [32]. The sizes of transistors within a logic block are determined by following the methodology described in [7]. Columns 2 and 3 list the input and switch

connection area (both of which are illustrated later in Fig. 3.2) while column 4 lists the total area of all routing resources. Column 5 lists the total FPGA area including that of the multi-bit logic block while the final column shows the percentage of total FPGA area that the routing resources occupy. It can be observed that the input connection area, the output connection area and the percentage of total area that routing resources occupy in Table 3.1 increase as a function of *W*. The routing resources consume between 8% and 20% of total FPGA area for small channel widths. For large channel widths (ie. Over W = 64 routing tracks), the programmable routing resources occupy a substantial amount (over 54%) of the total FPGA area. The bold rows in Table 3.1 represent a typical track count range (32 to 64) for circuits with the given architectural values where the routing resources consume from 38% to 54% of the total FPGA area. It is important to note that the contribution to area savings from unidirectional routing as described in [5] accounts for the lower proportional values of routing area results (Column 6) with respect to the results obtained from the bidirectional architecture in [21].

Fig. 3.1. Bit-slice partitioned datapath circuit

It is possible to alleviate some of this area by replacing conventional unidirectional tracks with multi-bit oriented unidirectional routing buses that employ multi-bit based connections to more efficiently transport multi-bit signals from a common source to a common destination. In order to clearly illustrate the advantages of multi-bit routing, we first consider mapping a generic datapath circuit onto a conventional FPGA tile. The circuit is segmented into 4 bit-slices in

Fig. 3.2. Bit-slice circuit implementation on a conventional FPGA tile

which each bit-slice has 4 inputs and 4 outputs as shown in Fig. 3.1. Assuming the computational logic of each bit-slice can fit within a single logic cluster, for M=4, a multi-bit logic block is used to house the 4 logic clusters containing the entire datapath circuit. Fig. 3.2 shows, at a minimum, a 16-bit wide routing channel is required to transport all the signals to and from the multi-bit logic block. Each of the white circles in Fig. 3.2 represent a routing switch where each switch includes a *X*:1 multiplexor and its associated driving buffer. *X* represents the amount of multiplexor input connections which consist of all the black circles on the associated track (line segment) and the track itself. These switches are arranged in accordance with the disjoint topology. The white squares represent input multiplexors of size *Y*:1 where *Y* equals the number of connections between tracks in a channel and a particular input pin (marked with an 'x'). This example assumes 50% connectivity of the inputs and 100% connectivity of the outputs wherever

possible ( $F_{ci} = 50\%$  and  $F_{co} = 100\%$ ). According to Fig. 3.2, there are 16 switch block connections and 16 input connections. Each switch block connection includes a 9:1 multiplexor while each input connection includes an 8:1 multiplexor. The multiplexors situated at the switch block each incorporate 4 output connections, 4 connections from adjacent tracks in the perpendicular channel and the track continuing straight through the multiplexor (hence 9 multiplexor inputs in total). While the bit-slices of Fig. 3.1 show a total of 16 input and output connections, Fig. 3.2 shows only 8 connections in total. The remaining 8 connections would be distributed among the other two sides of the multi-bit logic block (not pictured) and were also intentionally left out to preserve the clarity of the illustration.

Fig. 3.2 illustrates the two essential details of a practical design using one common tile layout as discussed in Section 2.1.1.2. The first being a staggered starting position of wires leaves tracks labeled A0-A3, B0-B3, C0-C3 and D0-D3 (in this example) without any switch block connections. These tracks do not begin on this tile and therefore do not have any switches associated with them to make connections. This leads to the next detail of requiring track shifts between pairs of 2L wires as shown at the bottom and right edges of Fig. 3.2. Specifically in this example, track shifts occur in groups of 4 wires. Additionally, in order to achieve a tile-based design with unidirectional wires, the channel width must be a multiple of 2L.

Alternatively Fig. 3.3 illustrates an architecture which replaces the routing tracks in each channel of Fig. 3.2 with 4 4-bit wide routing buses and groups the existing input and output connections into 4-bit wide input buses and output buses. The same multi-bit logic block of the previous example is used. Multi-bit based connection patterns are then used to connect the input/output connection buses and routing buses together. In particular, a bit in one bus can only be connected to a bit of the same bit position from another bus. Like the conventional tile of the

Fig. 3.3. Bit-slice circuit implementation on a FPGA tile with routing buses

previous example, this example assumes  $F_{ci} = 50\%$  and  $F_{co} = 100\%$ . Additionally, Fig. 3.3 illustrates a tile employing track shifts and staggered start positions of wires as seen in the previous example. This time, however, the staggering of wires occur in groups of M (or as buses) while the track shifts are made between groups of 2L buses (between a group of 4 buses in this example) as shown in Fig. 3.3. Notice how both the tiles in Fig. 3.2 and Fig. 3.3 require the same number of switches (white circles and white squares) and routing tracks to implement the circuit. Fig. 3.3 however requires smaller input and switch block multiplexors, specifically of size 2:1 and 6:1 respectively. This constitutes a 75% reduction in input multiplexor size and a 33% reduction in the switch block multiplexor size. This reduction occurs due to a much sparser

switch block and input connection pattern where bit positions in one bus only connect to the same bit positions in another bus.

Given the area results in Table 3.1 for a conventional tile, the same methodology is used to generate results for a purely routing bus based tile. Table 3.2 lists the active area of a conventional tile and that of a unidirectional routing bus-based tile for increasing values of W and  $W_{bus}$ , where is the number of equivalent *M*-bit wide routing buses. The area calculations use M=4, N=4, I=10, L=2,  $F_{ci} = .5$ ,  $F_{co} = .25$  and a disjoint switch topology. For the purpose of this

| Conventional |                  | Bus-based               |                  |                       |  |

|--------------|------------------|-------------------------|------------------|-----------------------|--|

| W            | A <sub>BIT</sub> | <b>W</b> <sub>BUS</sub> | A <sub>BUS</sub> | $A_{BUS}$ / $A_{BIT}$ |  |

| 8            | 9,246.96         | 2                       | 8,685.98         | 94%                   |  |