#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2003

### 10-GHz wide tuning-range linear voltagecontrolled oscillator

Sameh Soliman Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

#### **Recommended** Citation

Soliman, Sameh, "10-GHz wide tuning-range linear voltage-controlled oscillator" (2003). Theses and dissertations. Paper 194.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# 10-GHz Wide Tuning-Range Linear Voltage-Controlled Oscillator

Sameh Soliman B.Eng. Ryerson University Toronto, Ontario

Department of Electrical and Computer Engineering

Submitted in partial fulfillment of the requirements for the degree of Masters of Applied Science

> School of Graduate Studies RYERSON UNIVERSITY Toronto, Ontario

> > PROCEPTY OF RYERSON UNIVERSISY LIERARY

© Sameh Soliman 2003

#### UMI Number: EC52896

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC52896 Copyright 2008 by ProQuest LLC. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 E. Eisenhower Parkway PO Box 1346 Ann Arbor, MI 48106-1346

#### **Instructions on Borrowers**

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

als

or of

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

iii

#### Abstract

The current high-growth nature of digital communications demands higher speed serial communication circuits. Present day technologies barely manage to keep up with this demand, and new techniques are required to ensure that serial communication can continue to expand and grow.

The goal of this work is to optimize the performance of an essential building block of serial communication circuits, namely, the phase-locked loop (PLL), so that it can cope with today's high-speed communication. Due to its popularity, the optimization has targeted the charge-pump-based implementation of the phase-locked loop.

This goal is achieved by researching, designing, and evaluating high speed serial communication circuits. Research has involved an in-depth study of the state of the art in high-speed, serial communication circuits; high-speed, controlled oscillators; and CMOS technology.

An LC, voltage-controlled oscillator (VCO) is designed in 0.18-micron, mixedsignal, 6-metal-2-poly, CMOS process. A *novel* tuning technique is employed to tune its output frequency. Simulation results shows that it provides quadrature and differential outputs; operates with 10-GHz center frequency, 600-MHz tuning range centered around its center frequency, and phase noise of -95 dBc/Hz at 1-MHz offset from the fundamental harmonic of its output; and draws 10 mA of DC current from a single, 1.8-V power supply. Also, It exhibits a good linearity throughout its tuning range. The new tuning technique increases the tuning range of the VCO to 6% of its center frequency compared to the 1-to-2% typical value.

As its locking performance depends on the characteristic of the employed VCO and to demonstrate the effect of optimizing the tuning range of the VCO, a chargepump PLL is designed. Simulation results shows that the PLL acquisition range is 300 MHz compared to a maximum value of 100 MHz when a conventional LC VCO is employed. Also, as a measure of its tracking range, the maximum frequency slew rate of its input has improved by 40%.

iv

#### Acknowledgment

I would like to express my thanks and gratitude to my supervisor, Professor K. Raahemifar. This work would not have been possible without his continuous support and encouragement. I also would like to thank Professor F. Yuan, my co-supervisor, who has provided me with advice, boost, and encouragement.

e-

th

on

ck

an

эn

lal

he

rs;

d-

ne

<del>ک</del>ت-

n-

et

m

ng its

:0

;eis

:0

ЭW

I am thankful to the members of my defense committee, Professors S. Krishnan, M. Kassam, V. Geurkov, K. Raahemifar, and F. Yuan for their valuable comments.

I would also like to thank all my colleagues and friends for their support and useful discussions.

Special thanks to the system administration, Jason Naughton in particular.

# Contents

| 1 | 1 Introduction              |                                                   |    |  |  |

|---|-----------------------------|---------------------------------------------------|----|--|--|

|   | 1.1                         | The Necessity of Controlled Oscillators           | 1  |  |  |

|   | 1.2                         | The Necessity of GHz Oscillators                  | 2  |  |  |

|   | 1.3                         | The Necessity of Integrated Oscillators           | 3  |  |  |

|   | 1.4                         | Intended Application: Fiber-Optic receiver        | 4  |  |  |

|   | 1.5                         | Phase-Locked Loop: An Overview                    | 5  |  |  |

|   | 1.6                         | Thesis Contribution                               | 6  |  |  |

|   | 1.7                         | Thesis Outline                                    | 7  |  |  |

| 2 | Osc                         | illators: A Background                            | 8  |  |  |

|   | 2.1                         | Modeling of Oscillators                           | 8  |  |  |

|   | 2.2                         | Start-up Conditions                               | 9  |  |  |

|   | 2.3                         | Performance Parameters                            | 11 |  |  |

|   |                             | 2.3.1 Phase Noise                                 | 11 |  |  |

|   |                             | 2.3.2 Noise-Power Trade-off                       | 16 |  |  |

|   |                             | 2.3.3 Effect of Frequency scaling on Phase Noise  | 17 |  |  |

|   |                             | 2.3.4 Oscillator Pulling and Pushing              | 17 |  |  |

| 3 | Тор                         | ologies of Monolithic, High-Frequency, CMOS VCO's | 19 |  |  |

|   | 3.1                         | LC Oscillator                                     | 19 |  |  |

|   | 3.2                         | Ring Oscillator                                   | 22 |  |  |

|   | 3.3                         | Performance Metrics                               | 24 |  |  |

|   | 3.4                         | Topologies of High-Frequency VCO's                | 25 |  |  |

| 4 | The Proposed Circuit Design |                                                   |    |  |  |

|   | 4.1                         | The Voltage-Controlled Oscillator Circuit         | 28 |  |  |

|   | 4.2                         | The Core Circuit                                  | 29 |  |  |

|   |                             | 4.2.1 Waveform Analysis                           | 33 |  |  |

|   | 4.3                         | Monolithic Inductors: Design Guidelines           | 35 |  |  |

|   | 4.4                         | The Buffer Circuit                                | 38 |  |  |

|    |                                   | 4.4.1 Waveform Analysis                         | 39 |

|----|-----------------------------------|-------------------------------------------------|----|

|    | 4.5                               | The Bias Circuit                                | 41 |

|    | 4.6                               | Application Example: Phase-Locked Loop          | 41 |

|    |                                   | 4.6.1 Waveform Analysis                         | 43 |

| 5  | Con                               | clusions and Future Work                        | 48 |

|    | 5.1                               | Conclusions                                     | 48 |

|    | 5.2                               | Future Work                                     | 48 |

| Bi | bliog                             | graphy                                          | 50 |

| A  | The                               | Quality factor of a Resonant Circuit            | 54 |

| в  | 8 Narrowband Frequency Modulation |                                                 | 56 |

| С  | Gen                               | neration of a Small-Signal, Negative Resistance | 58 |

| D  | Pha                               | se-Locked Loop: A Background                    | 60 |

|    | D.1                               | Modeling the Building Blocks of the PLL         | 60 |

|    | D.2                               | The Linearized Model of the PLL                 | 62 |

|    | D.3                               | Lock Metrics                                    | 65 |

|    |                                   | D.3.1 Acquisition Range                         | 65 |

|    |                                   | D.3.2 Tracking Range                            | 65 |

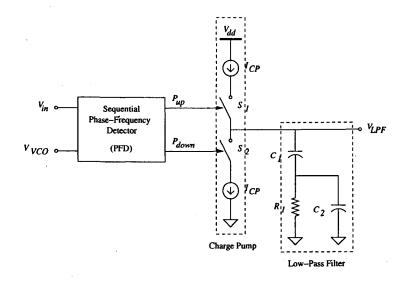

|    | D.4                               | Charge-Pump PLL                                 | 65 |

}

i

ś.

vii

# List of Figures

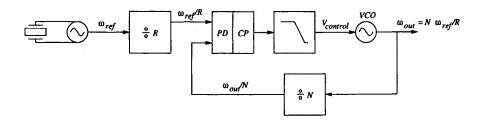

| 1.1        | A phase-locked loop consists of a voltage-controlled oscillator (VCO),<br>frequency divider, phase detector (PD), charge pump (CP) and lead-<br>lag filter. The VCO output frequency $\omega_{out}$ is set to a multiple or<br>sub-multiple of the reference frequency $\omega_{ref}$ depending on the divider |         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|            | ratios $N$ and $R$                                                                                                                                                                                                                                                                                             | 2       |

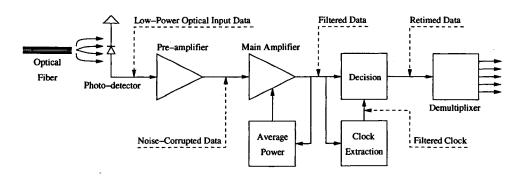

| 1.2        | Simplified block diagram of a fiber-optic receiver.                                                                                                                                                                                                                                                            | 4       |

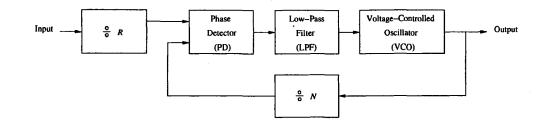

| 1.3        | The basic architecture of the PLL.                                                                                                                                                                                                                                                                             | 6       |

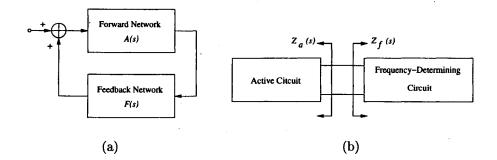

| 2.1        | (a) Feedback and (b) negative-resistance models of an oscillator                                                                                                                                                                                                                                               | 8       |

| 2.2        | Multi-oscillation phenomenon.                                                                                                                                                                                                                                                                                  | 11      |

| 2.3        | Noise in (a) signal path and (b) control path of a controlled-oscillator circuit.                                                                                                                                                                                                                              | 12      |

| 2.4        | Noise shaping in oscillator circuits.                                                                                                                                                                                                                                                                          | 12      |

| 2.5        | High-frequency multiplicative noise.                                                                                                                                                                                                                                                                           | 15      |

| 2.6        | Low-frequency multiplicative noise.                                                                                                                                                                                                                                                                            | 15      |

| 2.7        | Adding the outputs of $N$ identical oscillators. $\ldots$                                                                                                                                                                                                                                                      | 16      |

| 2.8        | Injection pulling of oscillators.                                                                                                                                                                                                                                                                              | 17      |

| 3.1        | The response of (a) an LC tank and (b) the tank in (a) in parallel with a resistor with a negative resistance $-R_p$ to a current impulse                                                                                                                                                                      | 20      |

| 3.2        | (a) A simple tuned stage; (b) the magnitude and phase of the impedance                                                                                                                                                                                                                                         |         |

| 3.3        | of an LC tank as a function of frequency                                                                                                                                                                                                                                                                       | 21      |

| 0.0        | output frequency.                                                                                                                                                                                                                                                                                              | 22      |

| 3.4        | The topology of a ring oscillator.                                                                                                                                                                                                                                                                             | 22      |

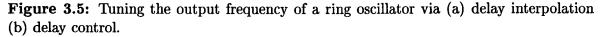

| <b>3.5</b> | Tuning the output frequency of a ring oscillator via (a) delay interpo-                                                                                                                                                                                                                                        |         |

|            | lation (b) delay control.                                                                                                                                                                                                                                                                                      | 23      |

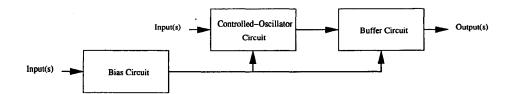

| 4.1        | Block diagram of a controlled oscillator.                                                                                                                                                                                                                                                                      | 29      |

| 4.2        | (a) Using varactor diodes to tune the output frequency of a differential                                                                                                                                                                                                                                       |         |

|            | tuned stage; (b) a variant of the circuit in (a).                                                                                                                                                                                                                                                              | 30      |

| 4.3        | The proposed technique (enclosed in the dashed box) to tune the out-                                                                                                                                                                                                                                           |         |

|            | put frequency of a differential tuned stage.                                                                                                                                                                                                                                                                   | 31      |

| 4.4        | (a) Parasitic capacitances of a MOSFET; (b) representing the capaci-                                                                                                                                                                                                                                           | <i></i> |

|            | tances in (a) with lumbed capacitances at the MOSFET terminals.                                                                                                                                                                                                                                                | 32      |

|   | 4.5  | Connecting two differential tuned stages to obtain in-phase and quadra-                                                               | 0.0       |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |      | ture, differential outputs.                                                                                                           | 33        |

|   | 4.6  | The transient and steady-state outputs of the core circuit.                                                                           | 34        |

|   | 4.7  | The frequency content of the output of the core circuit                                                                               | 34        |

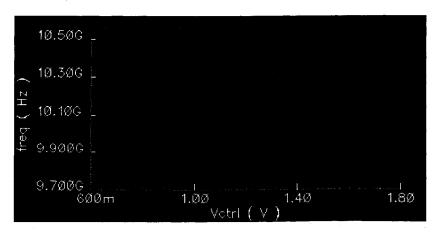

|   | 4.8  | The characteristic of the core circuit.                                                                                               | 34        |

|   | 4.9  | Equivalent energy model representing energy-storage and energy-loss                                                                   |           |

|   |      | mechanisms in a monolithic inductor.                                                                                                  | 35        |

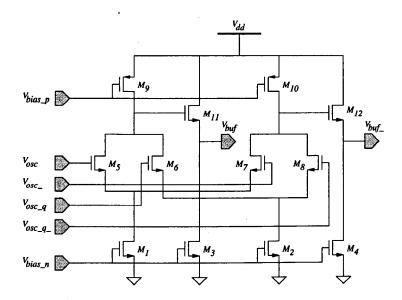

|   | 4.10 | Schematic diagram of the buffer circuit                                                                                               | 38        |

|   | 4.11 | The transient and steady-state outputs of the buffer circuit                                                                          | 39        |

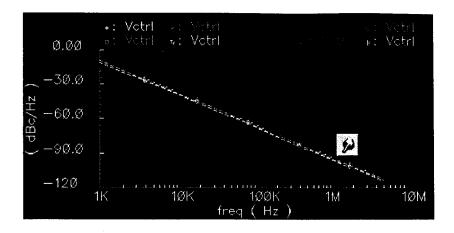

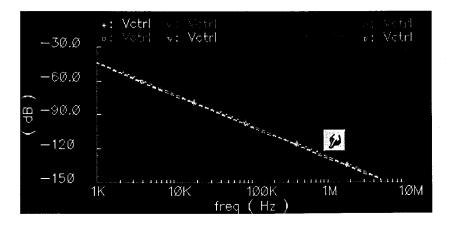

|   | 4.12 | Simulated phase noise relative to the fundamental harmonic of the                                                                     |           |

|   |      | buffer circuit's output for different values of $V_{ctrl}$                                                                            | 40        |

|   | 4.13 | Simulated output noise relative to the fundamental harmonic of the                                                                    |           |

|   |      | buffer circuit's output for different values of $V_{ctrl}$                                                                            | 40        |

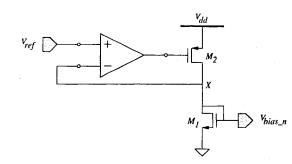

|   | 4.14 | Schematic diagram of the bias circuit                                                                                                 | 41        |

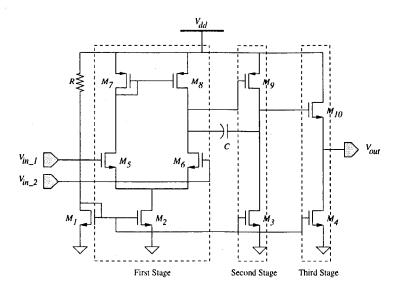

|   | 4.15 | Schematic diagram of the opamp.                                                                                                       | 42        |

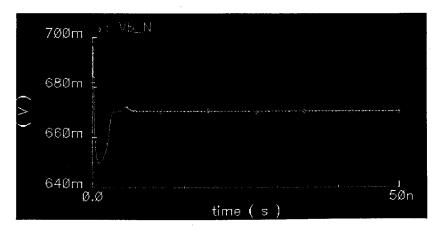

|   | 4.16 | The transient and stead-state outputs of the bias circuit                                                                             | 42        |

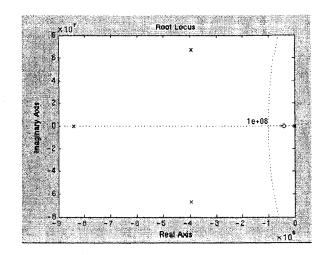

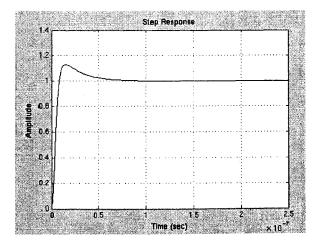

|   |      | The root locus of a third-order, charge-pump PLL.                                                                                     | 44        |

|   |      | The step response of a third-order, charge-pump PLL                                                                                   | 44        |

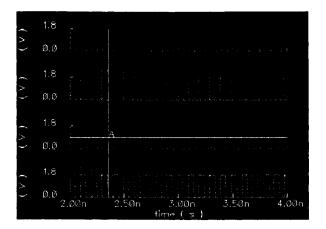

|   |      | The PFD signals for locked inputs.                                                                                                    | 44        |

|   |      | The PFD signals when the reference leads the VCO output.                                                                              | 45        |

|   |      | The PFD signals when the reference lags the VCO output.                                                                               | 45        |

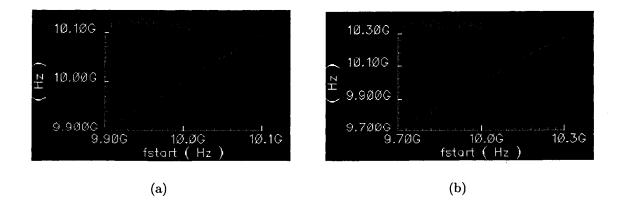

|   |      | The characteristic of a (a) 200-MHz, and (b) 600-MHz, tuning-range                                                                    |           |

|   |      | VCO                                                                                                                                   | 45        |

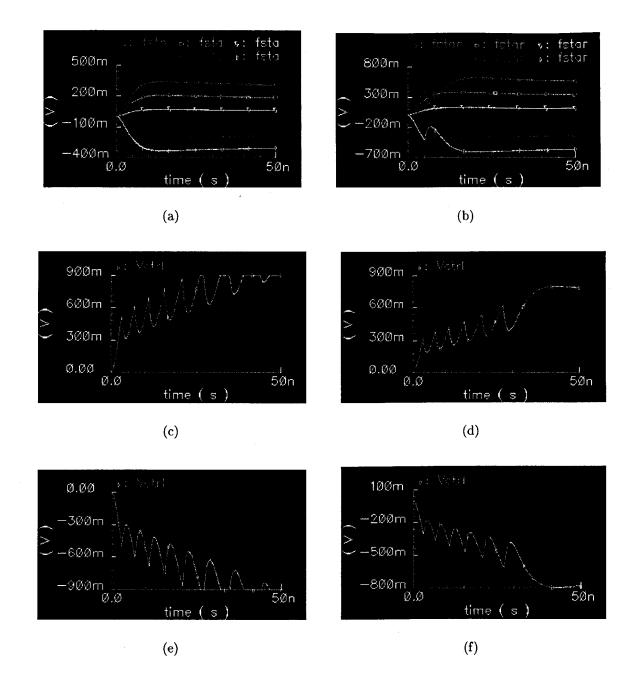

|   | 4.23 | The locking performance of a charge-pump PLL employing a 200-MHz, and 600-MHz, tuning-range VCO's: (a) and (b) within its acquisition |           |

|   |      | range; (c), (d), (e) and (f) outside its acquisition range                                                                            | 46        |

|   |      | range, $(c)$ , $(d)$ , $(c)$ and $(r)$ outside its acquisition range. $\ldots$ $\ldots$                                               | 40        |

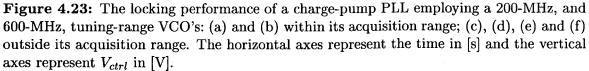

|   | A.1  | The magnitude of a resonant circuit's transfer function                                                                               | <b>54</b> |

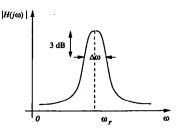

|   | A.2  | The phase of an oscillator's open-loop transfer function                                                                              | 55        |

|   | B.1  | Frequency modulating a carrier by a message signal                                                                                    | 56        |

|   | 01   | (a) Taralamentian a set a set in a sister a state of a labor                                                                          |           |

|   | C.1  | (a) Implementing a one-port, negative-resistance network by a cross-                                                                  |           |

|   |      | coupled pair of MOSFET's; (b) the small-signal equivalent of the cir-                                                                 |           |

|   |      | cuit in (a)                                                                                                                           | 58        |

| ε | D.1  | Block diagram of the PD.                                                                                                              | 60        |

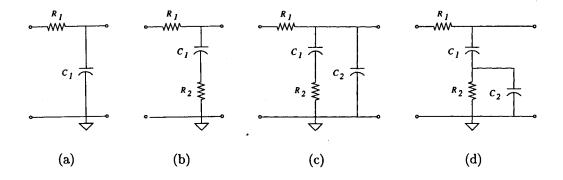

|   | D.2  | Common implementations of the LPF.                                                                                                    | 61        |

|   | D.3  | Block diagram of the VCO.                                                                                                             | 62        |

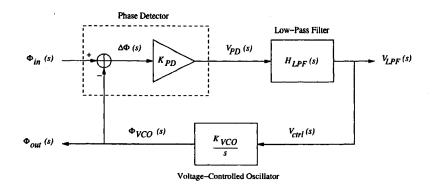

|   | D.4  | The linearized model of the PLL.                                                                                                      | 63        |

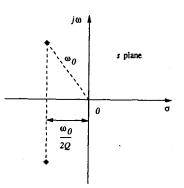

|   | D.5  | Definition of $\omega_0$ and $Q$ of a pair of complex-conjugate poles.                                                                | 64        |

|   |      | Block diagram of the charge-pump PFD.                                                                                                 | 66        |

|   |      | and the of the owned brank + F                                                                                                        | 00        |

|   |      |                                                                                                                                       |           |

$\frac{22}{22}$

Sold in the local data

### List of Tables

| 3.1 | Performance metrics of different techniques to implement a 10-GHz,<br>LC oscillator.                         | 27 |

|-----|--------------------------------------------------------------------------------------------------------------|----|

|     | Suppression of the first six harmonics of the oscillator's output<br>Parameter values of the charge-pump PLL |    |

| D.1 | Design formulas of a second-order, charge-pump PLL.                                                          | 67 |

# Chapter 1 Introduction

27

39 43

67

I this chapter, the motivation behind this thesis is presented, as well as a description of the intended application.

#### 1.1 The Necessity of Controlled Oscillators

Most electronic signal processing systems require frequency or time reference signals. To use the full capacity of communication channels, e.g., wireless, wired and optical channels, transmitters modulate the baseband message signal into different parts of the spectrum to exploit better propagation characteristics or to frequency multiplex several messages, and the receivers demodulate them. These operations require accurate frequency reference signals. Digital circuits and mixed mode circuits, e.g., analog-to-digital (A-to-D) and digital-to-analog (D-to-A) converters, pace and synchronize their operations using a clock signal as a time reference signal.

At the lower end of the spectrum, the stable properties of quartz crystals can be used as resonators to build very accurate fixed frequency or time reference signals. On the other hand, at higher frequencies (greater than few hundred MHz) the quality of the crystal resonators degrades due to physical and material-properties limitations. Many communication applications require programmable carrier frequencies and a multitude of crystals would be prohibitive due to the cost and board space. Indirect frequency synthesis techniques based on a phase-locked loop (PLL) [1] are preferred to generate programmable carrier frequencies. As shown in Figure 1.1 a less accurate oscillator whose frequency can be controlled with a control signal is embedded in

a feedback loop and its output frequency is locked to an accurate low frequency reference.

Figure 1.1: A phase-locked loop consists of a voltage-controlled oscillator (VCO), frequency divider, phase detector (PD), charge pump (CP) and lead-lag filter. The VCO output frequency  $\omega_{out}$  is set to a multiple or sub-multiple of the reference frequency  $\omega_{ref}$ depending on the divider ratios N and R.

In many data-communication applications, the data rate is accurately standardized. A local clock signal is derived from the incoming data signal with a clock recovery circuit to track small variations in the rate of the sender's clock and to align the phase of the local clock for optimal data recovery [2]. Another important application of controlled oscillators is the modulation or demodulation of frequency or angle modulated carriers. Open loop modulation and demodulation as well as closed loop schemes are very popular for portable wireless handsets [3].

Two main types of controlled oscillators exist: voltage-controlled oscillators (VCO's) with a voltage control signal and current-controlled oscillators (ICO's) with a current control signal. Although VCO's will be mainly referred to in the remainder of this thesis, most of the discussed concepts are equally applicable to ICO's.

#### **1.2** The Necessity of GHz Oscillators

Several evolutions demand the realization of VCO's with center frequencies in the GHz to several GHz range.

In the wireless arena, the better propagation characteristics and the larger available bandwidth in the 1 to 2 GHz range have allowed the standardization and exploitation of digital cellular phone systems worldwide. The fabrication of the wireless phone terminals triggered a large demand for high performance, GHz VCO's. At higher frequencies, around 2.5 GHz and 5 GHz, new wireless data applications, e.g., domestic short-range automation applications, cable replacement wireless links, etc., have spurred a strong interest and large markets.

With the constant shrinking of feature size in IC technologies and the increase of clock speeds we are very close to the widespread use of digital systems with clock speeds in the 1 GHz range. The distribution and synchronization of these GHz clocks is very challenging and will rely on on-chip PLL clock multipliers. Currently, these techniques are being used at clock frequencies of several hundred MHz [2]. These applications will drive the demand for GHz VCO's.

The same trend exists in data communications where widespread deployment of Gb/s data channels is fueled by the Internet growth and the convergence of data and voice communications. These systems rely on clock recovery architectures and also increase the demand for GHz VCO's.

#### **1.3** The Necessity of Integrated Oscillators

High-volume, IC markets are governed by price, package, performance and power consumption. IC integration reduces production cost since it allows for mass volume production. Integration of the analog components reduces the number of analog pins, hence, it allows for cheaper packaging solutions. However, integration increases the complexity of the part, hence, testing cost can become a limiting factor or the number of I/O pins can become large which are counterproductive for packaging cost reduction. For low-cost and large-volume production post-fabrication trimming is to be avoided. By integrating the VCO on the IC, complex automatic calibration techniques become feasible since there is an abundance of cheap active devices along with sophisticated computing power.

Performance is a key factor. In applications governed by standards, meeting the performance specifications is necessary; without standards compliance, price, package or power consumption is irrelevant. The benefit of integration for performance is less obvious when the analog components are combined with digital ones. The choice of IC technology is driven by the requirements of the majority of the components which are digital. Therefore, the use of special technology which enables better analog performance is unjustifiable due to its cost. Consequently, integration typically results in a somewhat lower performance for the VCO.

#### **1.4 Intended Application: Fiber-Optic receiver**

In recent years there has been a significant research effort in the area of high-speed electronics for communications. Higher speeds are required in order to take full advantage of the broadband capabilities of optical fibers. In particular integrated solutions are sought for practical systems to reduce cost and improve reliability. One of the target bit rates for integrated fiber optic receivers is 10 Gb/s, which is consistent with the SONET hierarchical specification [4]; practical transmission systems at these extremely high data rates will open the way to unexplored territory in networking. Each of these systems will require high-speed, low-cost interface electronics.

A simplified block diagram of a fiber-optic receiver is shown in Figure 1.2. It consists of a photo-detector at the front-end. The low-level signal from the photo-detector is then amplified by a low-noise pre-amplifier, followed by a main amplifier with automatic gain control. A clock extraction and data regeneration circuit recovers the timing information from the random data, and samples the data stream at the appropriate instant. Finally, a serial to parallel converter demultiplexes the re-timed serial data to a lower rate, where it can be processed by other circuitry.

Figure 1.2: Simplified block diagram of a fiber-optic receiver.

The photo-detector is implemented as a p - i - n diode or an avalanche photo-

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

$\tilde{\tau}_{ij} =$

detector (APD). When light pulses are focused onto it, it absorbs the light energy and generates electron-hole pairs. These electron-hole pairs are swept across the depletion region of the diode, resulting in a current that is proportional to the incident optical power.

To prevent additional processing from adding to the noise current, the low-level signal current from the photo-detector must be amplified. The pre-amplifier is used to convert this current into a voltage for subsequent processing. The sensitivity of the receiver and the signal-to-noise ratio are determined at this stage. Therefore, a very low-noise amplifier is required.

The main amplifier buffers the circuit from process variations and changes in signal strength, and it performs noise shaping. It must contain either a limiter, or an automatic-gain-control circuit to provide the proper signal level to the clockextraction and data-recovery circuit, regardless of the output power of the preamplifier circuit.

Typically, clock-extraction and data-recovery circuit is implemented as a PLL circuit. This approach requires a VCO be controlled by a suitably filtered error signal. Although the PLL has the desirable property of being self adjusting, complications due to non-linear frequency acquisition and tracking make the circuit difficult to design.

#### **1.5** Phase-Locked Loop: An Overview

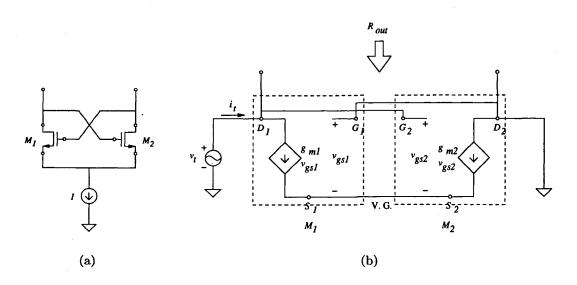

The basic architecture of the PLL is shown in Figure 1.3. The phase detector (PD) senses the phase difference between the input to the PLL and the output of the voltage-controlled oscillator  $(VCO)^1$ . The loop filter is a low-pass filter (LPF), hence, it averages the output of the PD. This average is used as a control input to the VCO. The VCO generates an output whose frequency is proportional to its control input.

5

<sup>&</sup>lt;sup>1</sup>In addition to sensing the phase difference between its inputs, some implementations allow the PD to sense the frequency difference between its inputs as well. Such implementations are referred to as phase and frequency detectors (PFD's).

Figure 1.3: The basic architecture of the PLL.

The PLL is locked if the output of the PD has a nearly constant average so that the output frequency of the VCO remains constant.

The frequency divider divides the frequency of its input by a specific factor or a range of factors. The basic architecture of Figure 1.3 utilizes two frequency dividers. They allow the PLL to lock to inputs or generate outputs of different frequencies<sup>2</sup>.

#### **1.6** Thesis Contribution

Optimizing the locking performance of the PLL at the 10 Gb/s data-rate relaxes other design trade-offs in the target application. Typically, the locking performance of the PLL is measured by its acquisition and tracking ranges. In the high-frequency region, PLL is usually implemented as a charge-pump PLL. For this implementation, the acquisition and tracking ranges depend on the characteristic of the employed VCO. More specifically, increasing the tuning range of the VCO increases the acquisition and tracking ranges of the charge-pump PLL which allows it to tolerate larger frequency and phase drifts in its input.

In this thesis, a novel approach to tune the output frequency of the conventional LC-oscillator topology is proposed. This approach improves the tuning range of the VCO, hence the acquisition and tracking ranges of the charge-pump PLL where it is employed. The improved VCO utilizes an LC topology and exhibits the following features:

• DC-current consumption of 10 mA from a single, 1.8-V power supply.

<sup>&</sup>lt;sup>2</sup>Depending on the application and the implementation of the frequency divider, the inputs or the outputs are usually separated by a fixed frequency step.

- Near-sinusoidal, in-phase and quadrature, differential outputs with a fundamental harmonic at 10 GHz.

- Tuning range of 600 MHz centered around the fundamental harmonic of its output.

- Phase noise of -95 dBc/Hz at 1-MHz offset from the fundamental harmonic of its output.

- Output noise of -130 dB at 1-MHz offset from the fundamental harmonic of its output.

The improvement in the locking performance of the charge-pump PLL is demonstrated via a system-level implementation and can be summarized as follows:

- The acquisition range of the charge-pump PLL increased to 300 MHz.

- As a measure of its tracking range, the maximum frequency slew rate of the input of the charge-pump PLL increased by 40%.

#### **1.7** Thesis Outline

This thesis consists of five chapters. Chapter 2 reviews the key design issues and performance parameters of oscillators. Chapter ?? reviews the theory behind the PLL and the system-level design of its charge-pump implementation. Chapter 3 reviews the common topologies used to implement monolithic, high-frequency, CMOS VCO's and presents a strategy for designing them. Chapter 4 describes the transistor-level design of a 10-GHz, wide-tuning-range, linear, CMOS VCO. Also, it presents the simulation results of the designed circuits. As an application example, the VCO is used as a building block in a charge-pump PLL and the improvement in its locking performance is presented via simulation results. Chapter 5 concludes this thesis and presents several future-work plans.

# Chapter 2 Oscillators: A Background

This chapter reviews the theory behind oscillators. Most of this theory is extensively covered in several text books [5, 6, 7, 8, 9].

#### 2.1 Modeling of Oscillators

Depending on the configuration and characteristic of the oscillator, it can be analyzed using one of two models: the feedback model or the negative-resistance model.

If the oscillator's circuit can be decomposed into a multi-port, forward network and a multi-port, feedback network, the feedback model, shown in Figure 2.1(a), is used.

Figure 2.1: (a) Feedback and (b) negative-resistance models of an oscillator.

The circuit in Figure 2.1(a) is characterized by its loop transfer function L(s), defined as the product of its forward and feedback transfer functions A(s) and F(s)

$$L(s) = A(s) F(s).$$

(2.1)

Its characteristic equation is given by

$$1 - L(s) = 0, (2.2)$$

from which its poles can be found.

On the other hand, if the oscillator's circuit can be separated into a one-port, active circuit and a one-port, frequency determining circuit, the negative-resistance model, shown in Figure 2.1(b), is used. The function of the active circuit is to produce a small-signal, negative resistance around the operating point of the oscillator and to couple with the frequency-determining circuit in defining the oscillation frequency. Usually, the frequency-determining circuit is a linear, time-invariant circuit and is signal independent.

In Figure 2.1(b), the active and frequency-determining circuits are characterized by the impedance quantities  $Z_a(s)$  and  $Z_f(s)$ , respectively. Alternatively, admittance quantities,  $Y_a(s)$  and  $Y_f(s)$ , may be used for the same purpose. The characteristic equation of the circuit is given by [10]

$$Z_a(s) + Z_f(s) = 0$$

or  $Y_a(s) + Y_f(s) = 0.$  (2.3)

#### 2.2 Start-up Conditions

As a basic requirement for producing a self-sustained, near-sinusoidal oscillation, an oscillator must have a pair of complex-conjugate poles in the right-half of the s plane (RHP)

$$p_{1,2} = \alpha \pm j\beta. \tag{2.4}$$

When excited by an arbitrary input, the RHP poles in Equation (2.4) give rise to a sinusoidal signal with an exponentially growing envelope

$$x(t) = K \exp(\alpha t) \cos(\beta t), \qquad (2.5)$$

where K is set by initial conditions. The growth of this signal is eventually limited by nonlinearities in the oscillator.

> PROPERTY OF RVERSON UNIVERSITY LILIUMY

For a feedback-oscillator circuit, the fulfillment of the following condition indicates that the circuit is unstable around its operating point.

$$\angle L(\omega_z) = 0 \quad \text{and} \quad |L(\omega_z)| \ge 1, \tag{2.6}$$

where  $\omega_z$  denotes the frequency at which the total phase shift through the forward and feedback networks is zero (or an integer multiple of  $\pm 360^{\circ}$ ).

For a negative-resistance-oscillator circuit, with the active and frequency-determining circuits characterized by the impedances  $Z_a = R_a + jX_a$  and  $Z_f = R_f + jX_f$ , respectively, the fulfillment of the following condition [10] indicates that the circuit is unstable about its operating point

$$R_a(\omega_x) + R_f(\omega_x) < 0 \quad \text{and} \quad X_a(\omega_x) + X_f(\omega_x) = 0, \tag{2.7}$$

where  $\omega_x$  denotes the frequency at which the total reactive component  $X_a + X_f$  is zero. The underlying assumption in condition (2.7) is that the current entering the active circuit in the steady state is near-sinusoidal.

Alternatively, if the voltage across the active circuit is near-sinusoidal in the steady state, the active and frequency-determining circuits should be modeled in terms of parallel admittances  $Y_a = G_a + jB_a$  and  $Y_f = G_f + jB_f$  where G and B denote the conductance and susceptance, respectively. The dual start-up condition in this case is

$$G_a(\omega_x) + G_f(\omega_x) < 0 \quad \text{and} \quad B_a(\omega_x) + B_f(\omega_x) = 0. \tag{2.8}$$

It is important to note that conditions (2.6), (2.7), and (2.8) have the following limitations

- Fulfilling any of these conditions does not always imply the existence of RHP poles [2].

- For controlled-oscillator circuits, varying the control signal of the circuit changes the location of its poles<sup>1</sup>. Because these conditions cannot predict the instability

10

<sup>&</sup>lt;sup>1</sup>This statement is not rigorous since linear concepts, e.g., poles and zeros, are difficult to apply to nonlinear circuits.

of the circuit throughout its tuning range, the existence of RHP poles throughout this range should be confirmed [2]. As a rule of thumb, these conditions are valid if they hold only at one frequency.

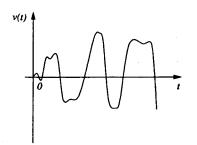

In the high-frequency region, the parasitic elements in the oscillator's circuit can give rise to a multi-oscillation phenomenon, in which more than one oscillation exist simultaneously in steady state. Due to the multiple oscillations, the net steady-state signal is severely distorted, as shown in Figure 2.2, and can cause unwanted spurious effects in many applications.

Figure 2.2: Multi-oscillation phenomenon.

The fulfillment of any of the conditions (2.6), (2.7), or (2.8) at more than one frequency indicates a potential multi-oscillation phenomenon and the existence of more than one pair of complex-conjugate poles in the RHP is a strong evidence on the existence of this phenomenon.

#### 2.3 **Performance Parameters**

Phase noise and frequency tuning range are the key performance parameters of highfrequency oscillators [11]. While the study of frequency tuning range of different oscillator circuits is deferred to Chapter 4, this section provides a detailed analysis of phase noise in oscillators.

#### 2.3.1 Phase Noise

Distinguished by the path into which the noise is injected, phase noise is generated primarily through two mechanisms. A controlled-oscillator circuit includes both a

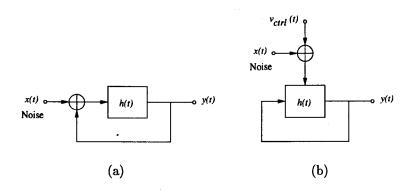

signal path and a control path. The phase noise observed at its output depends on how much the circuit rejects (or amplifies) noise in these paths. Shown in Figure. 2.3, the injected noise, x(t), in these paths gives rise to distinctly different effects [12, 13].

Figure 2.3: Noise in (a) signal path and (b) control path of a controlled-oscillator circuit.

#### Noise in Signal Path

In the steady state, representing the open-loop circuit in Figure 2.3(a) by a linear transfer function  $H_{ol}(j\omega)$ , its closed-loop transfer function is given by

$$H_{cl}(j\,\omega) = \frac{Y}{X}(j\,\omega) = \frac{H_{ol}(j\,\omega)}{1 - H_{ol}(j\,\omega)}.$$

(2.9)

The circuit oscillates at the frequency  $\omega = \omega_c$  if Equation (2.9) approaches infinity at this frequency. In the vicinity of this frequency, e.g.,  $\omega = \omega_c + \Delta \omega$ ,  $H_{ol}(j \omega)$  can be approximated by the first two terms of its Taylor expansion

$$H_{ol}(j\,\omega) \approx H_{ol}(j\,\omega_c) + \Delta\omega \,\frac{dH_{ol}(j\,\omega)}{d\omega}.$$

(2.10)

Since  $H_{ol}(j \omega_c) = 1$  and for most practical cases  $|\Delta \omega \, dH_{ol}(j \omega)/d\omega| \ll 1$ , Equation (2.9) can be reduced to

$$H_{cl}(j\omega) \approx \frac{-1}{\Delta\omega \frac{dH_{ol}(j\omega)}{d\omega}},$$

(2.11)

which implies, as shown in Figure 2.4, that the noise spectrum is shaped by

$$|H_{cl}(j\omega)|^2 = \frac{1}{(\Delta\omega)^2 \left|\frac{dH_{ol}(j\omega)}{d\omega}\right|^2}.$$

(2.12)

Figure 2.4: Noise shaping in oscillator circuits.

Expressing  $H_{ol}(j\omega)$  in the polar form  $H_{ol}(j\omega) = A(\omega) \exp[j\Phi(\omega)]$  and substituting for  $dH_{ol}(j\omega)/d\omega$ , Equation (2.12) can be written as

$$|H_{cl}(j\omega)|^2 = \frac{1}{(\Delta\omega)^2 \left[ \left( \frac{dA(\omega)}{d\omega} \right)^2 + \left( \frac{d\Phi(\omega)}{d\omega} \right)^2 \right]}.$$

(2.13)

Let the open-loop  $Q^2$  of the circuit, which is a measure of the opposition of the closed-loop circuit to variations in frequency, be defined by

$$Q = \frac{\omega_c}{2} \sqrt{\left(\frac{dA(\omega)}{d\omega}\right)^2 + \left(\frac{d\Phi(\omega)}{d\omega}\right)^2}.$$

(2.14)

Combining Equations (2.13) and (2.14) results in "Leeson's equation [12]"

$$|H_{cl}(j\,\omega)|^2 = \frac{1}{4Q^2} \,\left(\frac{\omega_c}{\Delta\omega}\right)^2,\tag{2.15}$$

which reveals the dependence of the output noise on the Q of the circuit, the center (or carrier) frequency, and the offset from the center frequency.

It is interesting to note that ring oscillators exhibit  $dA(\omega)/d\omega$  and  $d\Phi(\omega)/d\omega$  of the same order at resonance. Thus, phase-noise power of a ring oscillator is typically half the value given by Equation (2.15). On the other hand, LC oscillators exhibit  $dA(\omega)/d\omega = 0$  at resonance and Equation (2.14) reduces to the conventional definition of  $Q = \omega_c (d\Phi(\omega)/d\omega)/2$ .

Moreover, phase-noise power compared to carrier power depends on two other parameters: the noise generated by the devices in the circuit, that is, the magnitude of  $X(j\omega)$  and the amplitude of the oscillation. Deducing that phase-noise power

<sup>&</sup>lt;sup>2</sup>The definition of Q of a resonant circuit is reviewed in Appendix A.

of ring oscillators is lower than that of LC ones based on the comparison of their respective Q's may not be correct.

The above linear analysis does not consider the fact that oscillators usually experience amplitude limiting, i.e., nonlinearity, hence folding the noise components. To incorporate the effect of nonlinearity, two types of phase noise need to be identified.

First type is due to noise components that are directly added to the output of the oscillator as shown in Figure 2.4 and formulated by Equation (2.12). It is referred to as additive noise and is predicted by the above linear analysis. The accuracy of this prediction depends on the númber of stages in the oscillator and the portion of the oscillation period during which they operate linearly.

To identify the second type, consider a single-stage oscillator whose characteristic is expressed as  $v_{out}(t) = \alpha_1 v_{in}(t) + \alpha_2 v_{in}^2(t) + \alpha_3 v_{in}^3(t)$ . For an input consisting of the carrier and a noise component, e.g.,  $v_{in}(t) = A_c \cos(\omega_c t) + A_n \cos(\omega_n t)$ , the output of the oscillator exhibits the following important terms

$$v_{out1}(t) \propto \alpha_2 A_c A_n \cos[(\omega_c \pm \omega_n) t],$$

(2.16)

$$v_{out2}(t) \propto \alpha_3 A_c A_n^2 \cos[(\omega_c - 2\omega_n) t], \text{ and}$$

(2.17)

$$v_{out3}(t) \propto \alpha_3 A_c^2 A_n \cos[(2\omega_c - \omega_n) t].$$

(2.18)

If  $\omega_n$  is small,  $v_{out1}(t)$  appears in band. In a fully differential configuration  $\alpha_2 = 0$ , hence  $v_{out1}(t) = 0$ . Also,  $v_{out2}(t)$  is negligible because  $A_n \ll A_c$ , leaving  $v_{out3}(t)$  as the only significant cross-product.

This simplified one-stage analysis predicts the frequency of the output components, but not their magnitudes. When noise is injected into the oscillator, the magnitude of the observed response at  $\omega_n$  and  $2\omega_c - \omega_n$  depends on the noise shaping properties of the oscillator.

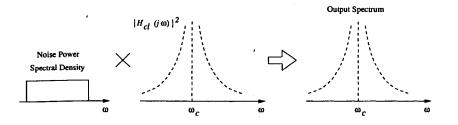

Since nonlinearity folds all the noise components below  $\omega_c$  to the region above it and vice versa, these components are referred to as high-frequency multiplicative noise and are important if they fall close to  $\omega_c$ . This phenomenon is illustrated in Figure 2.5.

Figure 2.5: High-frequency multiplicative noise.

It should be noted that for highly nonlinear oscillators, the Taylor expansion in Equation (2.10) may need to include higher order terms.

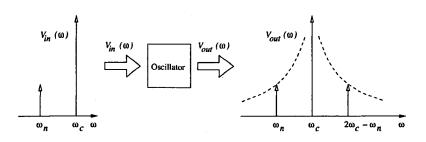

#### Noise in Control Path

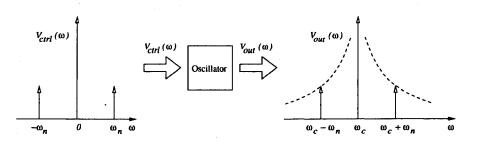

While noise injected into the signal path mixes with the carrier, noise injected into the control path affects the frequency of the oscillator's output by changing its physical properties. Viewed as analog frequency modulation (FM), this effect translates low-frequency noise components in the control path to the region around the carrier as illustrated in Figure 2.6. These components are referred to as low-frequency multiplicative noise.

Figure 2.6: Low-frequency multiplicative noise.

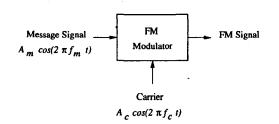

Representing the noise per unit bandwidth as a sinusoid  $A_n \cos(\omega_n t)$  with the same average power and using the narrowband FM approximation<sup>3</sup>

$$v_{out}(t) \approx A_c \cos(\omega_c t) + \frac{A_c A_n K_{osc}}{2 \omega_n} \left[ \cos(\omega_c + \omega_n) t - \cos(\omega_c - \omega_n) t \right], \qquad (2.19)$$

where  $K_{osc}$  is the controlled-oscillator gain. Thus, the noise power at  $\omega_c \pm \omega_n$  relative to the carrier power is equal to  $(A_n K_{osc}/2 \omega_n)^2$ . In practice,  $K_{osc}$  is proportional

<sup>&</sup>lt;sup>3</sup>The narrowband FM approximation is reviewed in Appendix B.

to the carrier frequency because for a given control-signal range, the tuning range must be constant percentage of the center frequency to compensate for process and temperature variations. The effect of this type of noise becomes more prominent as  $\omega_n$  decreases, making 1/f noise in the control path particularly detrimental.

It should be noted that low-frequency multiplicative noise arises from any source that can vary the frequency of the output of the oscillator.

The analyses in this section predict that the phase noise decreases indefinitely as the offset of  $\omega_n$  from  $\omega_c$  increases. In reality, it reaches a relatively flat floor since the oscillator does not shape the injected noise at high frequency offsets from the carrier.

#### 2.3.2 Noise-Power Trade-off

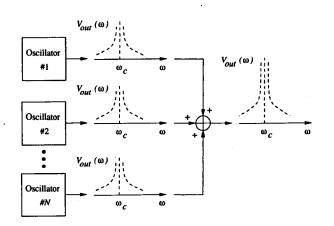

Oscillators, as other analog circuits, exhibit a trade-off between noise and power dissipation. As shown in Figure 2.7, if the outputs of N identical oscillators are added in phase, the carrier power is multiplied by  $N^2$ , whereas the noise power by N (assuming noise sources of different oscillators are uncorrelated).

Figure 2.7: Adding the outputs of N identical oscillators.

Thus, the phase noise power relative to the carrier power decreases by a factor N at the cost of a proportional increase in power dissipation.

#### 2.3.3 Effect of Frequency scaling on Phase Noise

Since frequency and phase are related by a linear operator, dividing frequency by a factor N is identical to dividing phase by the same factor. For a nominally periodic sinusoid,  $x(t) = A_c \cos[\omega_c t + \phi_n(t)]$ , where  $\phi_n(t)$  represents the phase noise, a frequency divider divides its total phase by N

$$x_{1/N}(t) = A_c \cos\left[\frac{\omega_c}{N}(t) + \frac{\omega_n}{N}(t)\right], \qquad (2.20)$$

where the phase noise contributed by the frequency divider is neglected.

This indicates that the magnitude of the phase noise at a given frequency offset from the carrier is divided by N. Thus, from narrowband FM approximation, the phase noise power is divided by  $N^2$ .

Similar reasoning shows that a frequency multiplier multiplies the magnitude of the phase noise by the same factor.

#### 2.3.4 Oscillator Pulling and Pushing

The analysis of phase noise in Section 2.3.1 assumed that the magnitude of the noise injected into the signal path is much less than that of the carrier, thereby arriving at a noise shaping function for oscillators.

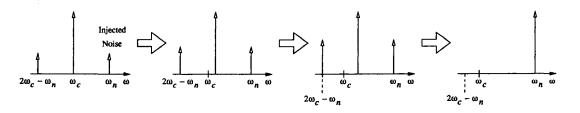

Close to the carrier, as the magnitude of the injected noise component becomes comparable to that of the carrier, the carrier frequency may shift toward the noise frequency and eventually locks to this frequency [14, 15]. Referred to as "injection pulling" this effect is shown in Figure 2.8.

Figure 2.8: Injection pulling of oscillators.

In general, oscillators exhibit a poor supply rejection. If the supply voltage varies, so do the frequency of oscillation. Referred to as "supply pushing" this effect is more

17

prominent in battery-powered (portable) applications. Owing to the finite output impedance of the battery, the supply voltage may vary by several hundred millivolts.

### Chapter 3

# Topologies of Monolithic, High-Frequency, CMOS VCO's

In general, oscillators can be categorized into two main categories: linear and nonlinear oscillators [26].

Linear oscillators generate a near-sinusoidal output. Their basic topology uses a frequency-tuning network, e.g., an LC tank, in a positive-feedback loop. Although they use a non-linear mechanism to limit the amplitude of the output, they are referred to as linear oscillators to distinguish them from the non-linear ones which can generate a near-sinusoidal output by waveform-shaping techniques.

Oscillators which generate square, triangular, etc. outputs are referred to as nonlinear oscillators. Two popular topologies in this category are relaxation and ring oscillators. While the former is a popular topology for bipolar oscillators, the latter is a popular one for CMOS oscillators.

In this chapter, the two main topologies of monolithic CMOS VCO's, namely, LC and ring topologies, are discussed. Also, following an overview of performance metrics of a controlled oscillator, the topologies of high-frequency VCO's are presented.

#### 3.1 LC Oscillator

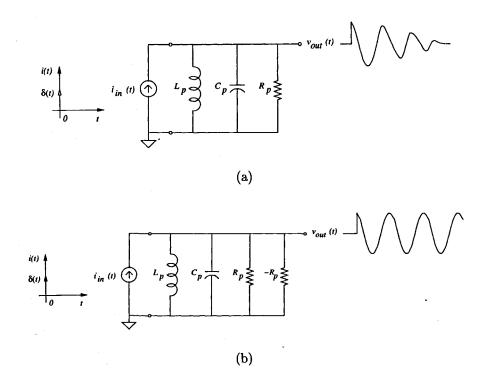

If a simple LC tank is stimulated by a current impulse, energy reciprocates between its capacitor and inductor in cycles. Every cycle, a portion of the reciprocating energy is lost in the form of heat in its resistor, hence, it responds with decaying oscillations as shown in Figure 3.1(a). If a resistor with a negative resistance  $-R_p$  is placed in parallel with the tank, its net resistance approaches infinity and it responds to the current impulse with indefinite oscillations as shown in Figure 3.1(b).

**Figure 3.1:** The response of (a) an LC tank and (b) the tank in (a) in parallel with a resistor with a negative resistance  $-R_p$  to a current impulse.

Thus, if a one-port network exhibiting negative resistance<sup>1</sup> is placed in parallel with an LC tank, the combination may oscillate.

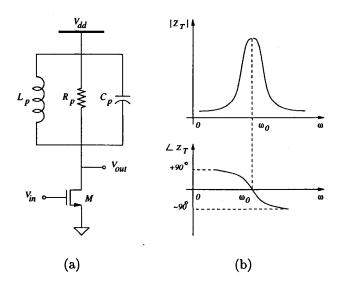

A simple *tuned* stage is shown in Figure 3.2 loaded with an LC tank. Also, the magnitude and phase of the impedance of the LC tank,  $Z_T$ , as a function of frequency are shown in the same figure.

At resonance,  $|Z_T| = R_p$  and  $\angle Z_T = 0$ . Thus, the magnitude of the gain of the tuned stage is  $R_p g_m$ , where  $g_m$  is the small-signal transconductance of the transistor M, and its phase is  $\pm 180^{\circ 2}$ .

<sup>&</sup>lt;sup>1</sup>The negative resistance is an incremental quantity. It indicates that if the applied voltage increases, the current drawn by the network decreases.

<sup>&</sup>lt;sup>2</sup>This phase is due to the low-frequency phase inversion of the common-source transistor M.

Figure 3.2: (a) A simple tuned stage; (b) the magnitude and phase of the impedance of an LC tank as a function of frequency.

An LC oscillator is a cascade of N tuned stages. For the cascade to start oscillating,  $(R_p g_m)^N \ge 1$  and its total phase shift<sup>3</sup> has to be zero. Thus, N has to be an even number.

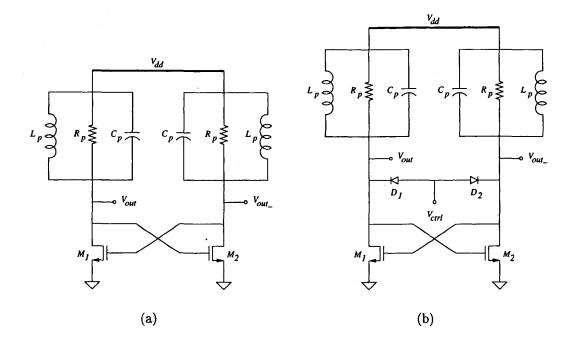

A differential tuned stage can be implemented by connecting two simple tuned stages as shown in Figure 3.3(a). Since the frequency of oscillation equals  $1/\sqrt{L_p C_p}$  [16], the output frequency of the LC oscillator can be tuned by varying the inductance or the capacitance of its tank. In monolithic implementations, it is difficult to vary the value of an inductor, hence, the common practice is to vary the value of the capacitance of the tank.

A reverse-biased p/n junction can serve as a voltage-dependent capacitor (also, referred to as a varactor). It can be used to vary the net capacitance of the LC tank as shown in Figure 3.3(b).

21

<sup>&</sup>lt;sup>3</sup>Total phase shift = frequency-independent or DC phase shift + frequency-dependent or AC phase shift.

22

Figure 3.3: (a) A differential tuned stage; (b) using varactor diodes to tune its output frequency.

#### 3.2 Ring Oscillator

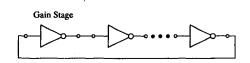

As shown in Figure 3.4, a ring oscillator is a cascade of N gain stages with a total DC phase shift of 180° in a feedback loop. If the total phase shift around the loop is zero at its unity loop gain, it starts to oscillate with a period of  $2N t_d$  where  $t_d$  is the delay of each gain stage with a fanout of one under these conditions.

Figure 3.4: The topology of a ring oscillator.

The common implementation of the gain stage is as a simple or differential-pairbased inverter. To achieve a DC phase shift of  $180^{\circ}$ , N must be an odd number when the simple inverter is used. On the other hand, N can be an even number when the differential-pair-based inverter is used. The required DC phase shift is achieved by swapping the outputs of one of the gain stages.

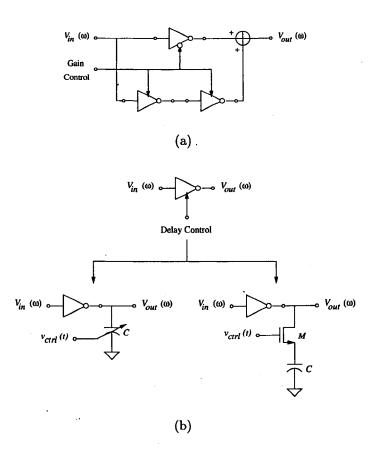

Tuning the output frequency is achieved by varying the effective number of gain stages or the delay of each one. Delay interpolation, shown in Figure 3.5(a), is the common implementation of the first technique where a fast signal path and a slow one are used in parallel. The total delay is varied by varying the gains, hence the delays, of both paths in complementary fashion.

Varying the delay of each gain stage can be achieved by varying its load capacitance or resistance. As shown in Figure 3.5(b), varying the load capacitance can be achieved by using a voltage-controlled capacitor or a fixed capacitor in series with a voltage-controlled resistor. The main limitations of this approach are the variation of the oscillator's gain and its output swing throughout its tuning range<sup>4</sup>. Moreover, it

<sup>&</sup>lt;sup>4</sup>These effects can be minimized by varying some other parameters of the gain stage [17].

is susceptible to common-mode noise as it uses single-ended control path.

Although varying the load resistance has the same limitations as changing its capacitance, this approach provides a large, relatively uniform frequency variation and lends itself to differential control [2].

#### **3.3** Performance Metrics

The performance of a controlled oscillator is described by the following metrics:

- *Center frequency*: it is the midpoint of the oscillator's tuning range and is mainly application dependent.

- Tuning range: it is the range between the minimum and maximum frequency of the oscillator's output and is mainly dictated by the application and the variation of the oscillator's center frequency with process and temperature. LC oscillators exhibit narrow tuning range compared to ring oscillators.

- Tuning sensitivity: it is the change in the output frequency of the oscillator per unit change in its control voltage and is frequently referred to as the oscillator's gain. To tune its output signal frequency, one of the oscillator's circuit parameters must be varied. Depending on the effect of this parameter, the oscillator's gain, hence its output swing, may vary considerably throughout its tuning range. LC oscillators exhibit less gain and output swing variation compared to ring oscillators.

- Characteristic linearity: if the oscillator is intended for frequency-synthesis applications, it may exhibit non-linear characteristic (its tuning range can be divided into regions throughout each of which the characteristic is linear). On the other hand, if the oscillator is intended for modulation or demodulation applications, its characteristic must exhibit high linearity. For such applications and as a measure of the linearity of the oscillator's characteristic, the variation of its gain throughout its tuning range must be minimum.

• Spectral purity: depending on the application, it can be specified in time domain as jitter or in frequency domain as phase noise.

• Noise rejection: when an oscillator share the same substrate with some digital circuit, its sensitivity to substrate and supply noise becomes prominent. Although it is not always possible, the common practice to minimize this sensitivity is to employ differential signal and control paths.

#### **3.4** Topologies of High-Frequency VCO's

Among the different performance metrics of a controlled oscillator, phase noise and tuning range are the most challenging to achieve specifically when operation in the high-frequency region is targeted. During the past few years several techniques to overcome these challenges were reported [18, 19, 20]. In this section a review of these techniques is presented.

The review targeted the recent publications on high-frequency VCO's. a representing examples of the available techniques to implement a 10-GHz VCO is presented.

In [18], a 10-GHz, LC VCO was designed in a 0.25-micron, CMOS process. It achieved a tuning range of 700 MHz. The measured phase noise at 400 kHz offset from the carrier was -101 dBc/Hz at the low end and -87 dB c/Hz at the high end of its tuning range. The circuit drew 2.4 mA from a 2-V power supply. PMOS varactors were used to achieve wide tuning range of the output frequency.

In [19], a 10-GHz, LC VCO was designed in a 0.13-micron, standard-digital, CMOS process. It achieved a tuning range of 3.7 GHz and a phase noise of -99 dBc/Hz at 1-MHz offset from the carrier. The core circuit consumed a 3.6 mW of DC power from a 1.2-V power supply.

Wide tuning range was achieved by using MOS, accumulation-mode varactors instead of the conventional reverse-biased p/n junction and MOS, depletion/inversion varactors.

In [20], a 10-GHz, CMOS, distributed, voltage-controlled oscillator (DVCO) was designed in a 0.35-micron, BiCMOS process. It achieved a tuning range of 1.2 GHz

and a phase noise of -103 dBc/Hz at 600 kHz offset from the carrier. The circuit drew 14 mA of DC current from a 2.5-V power supply.

Two techniques to tune the output frequency were described. The first was to introduce explicit varactors on the transmission lines. This technique suffered from a severe reduction in the output frequency due to the constant, zero-bias capacitance added to the transmission lines. Thus, canceling the advantage obtained by using a distributed topology, namely, higher operation frequency. Also, the quality factor of the varactors significantly degraded at higher frequencies which made them more undesirable.

The second technique was to change the round-trip time-delay by changing the length of the transmission lines. Although the physical length cannot be changed, the effective length can be varied. This effect was achieved via current steering technique.

From these examples, a strategy for designing VCO's in the 10-GHz frequency region (and above) can be obtained.

- In the 10-GHz frequency region and above, two main topologies were used to implement a VCO: LC-tank-based topology [18, 19] and distributed topology [20].

- Different processes were used to design the VCO, e.g., 0.25-micron, CMOS process in [18]; 0.13-micron, standard-digital, CMOS process in [19]; and 0.35-micron, BiCMOS process in [20].

- Supply voltage ranged from 1.2 V to 2.5 V.

- Phase noise was improved compared to the target-application requirements [19], namely, -90 dBc/Hz at 1-MHz offset from a 10-GHz carrier. For example, the phase noise at 400-kHz offset from the carrier ranged from -101 dBc/Hz at the low end to -87 dBc/Hz at the high end of the tuning range in [18]; a phase noise of -99 dBc/Hz was measured at 1-MHz offset from a carrier in [19]; and a phase noise of -103 dBc/Hz was measured at 600-kHz offset from the carrier in [20]. It should be noted that this improvement was achieved at the cost of increased power dissipation.

- The inadequacy of the conventional technique, namely, using reverse-biased p/n junctions, to achieve wide tuning range was reported [19, 20]. To achieve wide tuning range, an improved variant of it [19] or a new approach [20] was used.

- As a measure of power dissipation, the DC current drawn by the circuit ranged from 2.4 mA [18] to 14 mA [20].

In this thesis a 10-GHz VCO is designed in 0.18-micron, mixed-signal, 6-metal-2-poly, CMOS process. The designed VCO uses an LC topology to achieve superior phase-noise performance. The phase noise is -95 dBc/Hz at 1-MHz offset from the carrier. A novel tuning technique is used to increase its tuning range to 600 MHz compared to the achieved 200-MHz value when the conventional tuning technique is used. It draws 10 mA of DC current form a 1.8-V power supply. A comparison among the above techniques and the proposed one in this thesis is presented in Table 3.1.

| Source    | Supply<br>Voltage | Phase Noise                             | Tuning<br>Range | DC-Current<br>Consumption |

|-----------|-------------------|-----------------------------------------|-----------------|---------------------------|

| [18]      | 2 V               | -101 dBc/Hz @ 400-kHz                   | 700 MHz         | 2.4 mA                    |

| [19]      | 1.2 V             | -99 dBc/Hz @ 1-MHz                      | 3.7 GHz         | 3 mA                      |

| [20]      | $2.5 \mathrm{V}$  | -103 dBc/Hz @ 600-MHz                   | 1.2 GHz         | 14 mA                     |

| Proposed  |                   |                                         |                 |                           |

| Technique | 1.8 V             | $-95 \mathrm{ dBc/Hz} @ 1-\mathrm{MHz}$ | 600 MHz         | 10 mA                     |

Table 3.1: Performance metrics of different techniques to implement a 10-GHz, LC oscillator.

# Chapter 4 The Proposed Circuit Design

In this chapter, the detailed design of the proposed VCO is presented as well as one of its application examples.<sup>1</sup>

## 4.1 The Voltage-Controlled Oscillator Circuit

Integrating ring oscillators on a monolithic IC is easy, results in a compact design, and several order of magnitude tuning range is achievable [21]. Their main limitation is the poor spectral purity of the output specifically in the high-frequency region [7]. On the other hand, integrating LC oscillators is hard due to the lack of high-quality, passive inductors in standard IC technologies and their large size. Moreover, tuning range is limited by the non-controllable parasitics of the circuit and the supply voltage which continues to decrease as new IC technologies emerge. However, they exhibit a much higher frequency stability and spectral purity as they employ passive resonators.

As it was reported in [22], ring oscillators with active resistive loads designed and fabricated in 0.18-micorn, mixed-signal, 6-metal-2-poly, CMOS process did not operate in the 10-GHz frequency region. Satisfactory results were obtained by replacing the ring oscillator with an LC one [23]. Moreover, ring oscillators with active inductive loads [32], when designed in the same technology, failed to operate in the same frequency region.

Due to the increase of the data rates in the applications where oscillators represent an important building block, e.g., optical receivers, and the availability of high-quality,

<sup>&</sup>lt;sup>1</sup>The circuits described in this chapter were simulated using 0.18-micron technology in Cadence®.

passive inductors in the IC process used in this work, it was decided to use an LCoscillator topology. To overcome its main limitation, namely, narrow tuning range, a novel tuning approach was employed.

Typically, a controlled oscillator consists of a bias, a core circuit (or oscillator), and a buffer building blocks as shown in Figure 4.1. In the following sections, the transistor-level design and simulation results of each of these building blocks are presented.

Figure 4.1: Block diagram of a controlled oscillator.

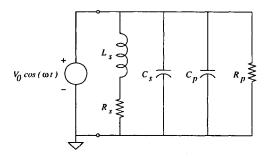

### 4.2 The Core Circuit

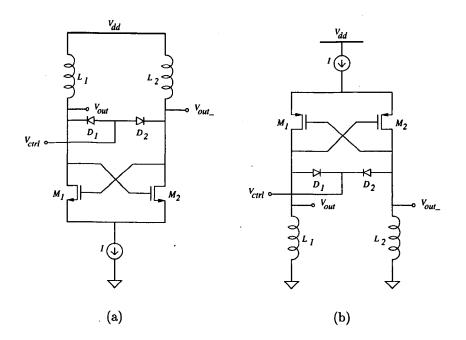

As shown in Figure 4.2(a), two reverse-biased diodes,  $D_1$  and  $D_2$ , are used as varactors to tune the output frequency of a differential tuned stage. To avoid forward-biasing the diodes significantly,  $V_{ctrl}$  must not exceed  $V_{out}$  or  $V_{out_-}$  by more than  $V_{cut-off}^2$ . Thus, if the amplitude of  $V_{out}$  or  $V_{out_-}$  is A,  $0 < V_{ctrl} < V_{dd} - A + V_{cut-off}$ , which indicates a trade-off between the output swing and the tuning range of this circuit.

Standard CMOS process offers two implementations of a diode. In the first, referred to as  $n^+/p$  diode, the *p*-substrate is used as the diode's anode and an  $n^+$  region as its cathode. In the second, referred to as  $p^+/n$  diode, a  $p^+$  region is used as the diode's anode and an *n*-well region as its cathode. Since the substrate is usually connected to ground, the first implementation cannot serve as a varactor. Using an *n*-well region in the second implementation pauses two problems. Its high resistivity creates a resistance in series with the reverse-biased diode which lowers the quality

<sup>&</sup>lt;sup>2</sup>It is assumed that the diode conducts a negligible current when it is forward-biased by  $V_{cut-off}$  [V].

Figure 4.2: (a) Using varactor diodes to tune the output frequency of a differential tuned stage; (b) a variant of the circuit in (a).

factor of its capacitance. Moreover, the n-well region exhibits a substantial parasitic capacitance to the substrate which increases the constant capacitance of the LC tank and limits its tuning range.

Surrounding the  $p^+$  region by an  $n^+$  ring decreases the series resistance of the diode as it reduces the resistance seen by the displacement current through the junction capacitance [27]. On the other hand, it increases the size of the *n*-well region which increases its parasitic capacitance to the substrate. This drawback can be eliminated by using the variant of the differential tuned stage shown in Figure 4.2(b). However, to obtain the same transconductance, the PMOS devices in this variant must be wider than their NMOS counter parts to account for their lower mobility. This degrades the constant capacitance of the LC tank.

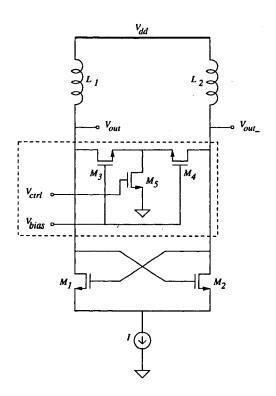

Despite these optimizations, the tuning range of the differential tuned stage remains limited by the supply voltage [27] which continues to decrease as new IC technologies emerge. This limitation can be minimized if a technique, that does not rely on varactors, to tuning the output frequency can be found. Figure 4.3 shows such a

technique<sup>3</sup>.

Figure 4.3: The proposed technique (enclosed in the dashed box) to tune the output frequency of a differential tuned stage.

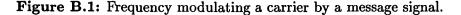

$M_1$  and  $M_2$  are cross coupled to provide a small-signal resistance of  $-2/g_{m1,2}^4$ where  $g_{m1,2}$  is the small-signal transconductance of any of them.  $M_3$ ,  $M_4$ , and  $M_5$ control the current flowing in differential tuned stage. Varying  $V_{ctrl}$  varies the current through  $M_5$ , hence the current drawn form nodes  $V_{out}$  and  $V_{out}$  by  $M_3$  and  $M_4$ .

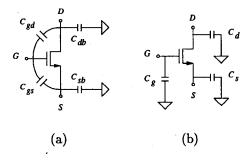

The LC tanks are formed by  $L_1$  and  $L_2$  and the parasitic capacitance at nodes  $V_{out}$  and  $V_{out_-}$ . For the tank formed by  $L_1$  and the parasitic capacitance at node  $V_{out}$ , each of its components contribute to its capacitance. While the contribution of  $L_1$  is constant, that of  $M_1$ ,  $M_2$  and  $M_3$  is controllable. Figure 4.4(a) shows the parasitic capacitances of a MOSFET. These capacitances can be represented by three lumbed capacitances at the drain, gate, and source terminals of the MOSFET as shown in Figure 4.4(b). Including the parasitic capacitances of each transistor in Figure 4.3,

<sup>&</sup>lt;sup>3</sup>Copyright © Sameh Soliman 2003. All rights reserved. Please, direct any concerns to the author at "ssoliman@ee.ryerson.ca".

<sup>&</sup>lt;sup>4</sup>The derivation of this expression is provided in Appendix C.

the controllable parasitic capacitance at node  $V_{out}$  composed of  $C_{d;M_1}$ ,  $C_{g;M_2}$ , and  $C_{d;M_3}$ .

Figure 4.4: (a) Parasitic capacitances of a MOSFET; (b) representing the capacitances in (a) with lumbed capacitances at the MOSFET terminals.

Varying the current of the differential tuned stage varies the parasitic capacitance of  $M_1$ ,  $M_2$  and  $M_3$ , and its output frequency consequently. Assuming that oscillation conditions are fulfilled, the upper bound of the tuning range is set by the supply voltage whereas its lower bound is set by the region of operation of  $M_5$ .

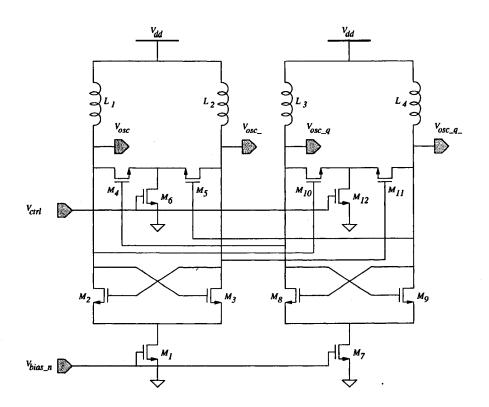

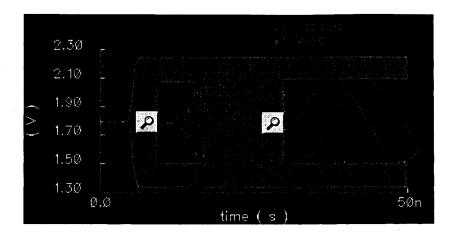

In-phase and quadrature, differential outputs can be obtained by connecting two differential tuned stages as shown in Figure 4.5. The transient and steady-state outputs of this configuration are shown in Figure 4.6. The steady-state output shows that the oscillator generates in-phase and quadrature, differential outputs.

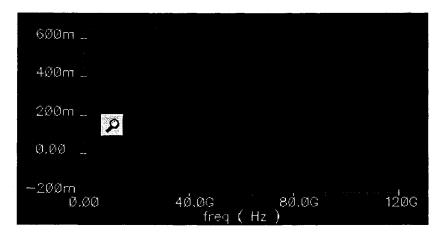

The frequency content of the core circuit's output is shown in Figure 4.7. It shows that it generates a near-sinusoidal output with a dominant harmonic at 10 GHz.

A practical LC tank resonates at a frequency given by [16]

$$\omega_c = \sqrt{\frac{1}{LC} - \left(\frac{R}{L}\right)^2}.$$

(4.1)

The magnitude of the impedance of the tank peaks at a frequency  $\omega_p$  higher than its resonance frequency  $\omega_c$ . That is, if the tank used to load a tuned stage in an LC oscillator, the output frequency of the oscillator can be tuned from  $\omega_c$  to  $\omega_p$ .

Typically, the tuning range of an LC oscillator is 1% to 2% of its center frequency [2]. The characteristic of the proposed LC oscillator is shown in Figure 4.8.

Figure 4.5: Connecting two differential tuned stages to obtain in-phase and quadrature, differential outputs.

It shows that the new tuning technique increased the tuning range of the oscillator to 6% of its center frequency. Also, it shows that the characteristic exhibits good linearity throughout the tuning range.

#### 4.2.1 Waveform Analysis

Referring to Figures 4.6 to 4.8, the following observations can be made:

- The waveforms in Figure 4.6 were magnified at two time instants: during the transient and steady state of the output. The magnified view during the steady state of the output the steady state of the output the the core circuit generates in-phase and quadrature, differential outputs.

- The waveform in Figure 4.7 was magnified to show that the core circuit generates a near-sinusoidal output with a dominant harmonic at 10 GHz.

- The waveform in Figure 4.8 shows that the output frequency can be tuned from

34

Figure 4.6: The transient and steady-state outputs of the core circuit. The horizontal axis represents the time in [s] and the vertical axis represents the output in [V].

Figure 4.7: The frequency content of the output of the core circuit. The horizontal axis represents the harmonic frequency in [Hz] and the vertical axis displays the harmonic amplitude.

Figure 4.8: The characteristic of the core circuit. The horizontal axis represents  $V_{ctrl}$  in [V] and the vertical axis represents the output frequency in [Hz].

9.7 GHz to 10.3 GHz by varying  $V_{ctrl}$  from 0.6 V to 1.7 V. Also, it shows that the characteristic exhibits good linearity throughout the tuning range.

### 4.3 Monolithic Inductors: Design Guidelines