# Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2011

# Reconfigurable platform for 3D-panoramic telepresence system for mobile applications

Artur Saakov Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Saakov, Artur, "Reconfigurable platform for 3D-panoramic telepresence system for mobile applications" (2011). *Theses and dissertations*. Paper 758.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# RECONFIGURABLE PLATFORM FOR 3D-PANORAMIC TELEPRESENCE SYSTEM FOR MOBILE APPLICATIONS

By

# **Artur Saakov**

B.A.Sc., Moscow State Institute of Radio Engineering, Electronics and Automation (Technical University), Russian Federation, 2007

A Thesis

presented to Ryerson University in partial fulfillment of the requirements for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2011

© Artur Saakov, 2011

# **Declaration of Authorship**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

# RECONFIGURABLE PLATFORM FOR 3D-PANORAMIC TELEPRESENCE SYSTEM FOR MOBILE APPLICATIONS

Artur Saakov Master of Applied Science Electrical and Computer Engineering Ryerson University 2011

# Abstract

The concept of telepresence allows human beings to interact with hazardous environments and situations without facing any actual risks. Examples include the nuclear industry, outer space and underwater operations, mining, bomb disposal and firefighting. Recent progress in digital system technology, especially in technology of reconfigurable logic devices (e.g. FPGA), allows the effective implementation of advanced embedded systems characterized by high-performance data processing and high-bandwidth communication. However, most of the existing telepresence systems do not benefit from these advancements. Therefore, the goal of this work was to develop a concept and architecture of the platform for the 3D-Pranoramic Telepresence System for mobile robotic applications based on reconfigurable logic devices. During the development process, two versions of the system were implemented. The first system focused on feasibility testing of major components of the proposed architecture. Based on the experimental results obtained on the first prototype of the system and their analyses, a set of recommendations were derived for an updated version of the system. These recommendations were incorporated into the implementation of the second and final version of the system.

**Keywords**: 3D Panoramic Telepresence, FPGA, multi-stream processing, reconfigurable computing, stereo vision.

## Acknowledgments

There are many people I would like to thank for making this thesis possible. Firstly, I would like to thank my supervising professor Dr. Lev Kirischian for providing his knowledge, immeasurable experience, support and guidance in all aspects of my M.A.Sc studies.

I would also like to express personal gratitude to Valeri Kirischian for his influence since the beginning of my studies here at Ryerson and for sharing his engineering experience which proved to be very practical and supportive throughout.

Thirdly, I would like to thank the Department of Electrical and Computer Engineering at Ryerson for their great facilities and numerous resources needed for my research, as well as the review committee for their participation.

Fourthly, appreciation goes out to Victor Dumitriu for providing advice and opinions at times needed the most.

Lastly, and most importantly, I would like to express profound gratification to my family for all of the unconditional support they gave me every step of the way; throughout all of my goals and achievements.

# **Table of Contents**

| 1. IN | TRODUCTION                                               | 1  |

|-------|----------------------------------------------------------|----|

| 1.1.  | Motivation                                               | 1  |

| 1.2.  | Objectives                                               | 3  |

| 1.3.  | Contributions                                            | 3  |

| 1.4.  | Thesis organization                                      | 5  |

| 2. CC | OMPREHENSIVE SURVEY OF TELEPRESENCE SYSTEMS FOR          |    |

| 3D-PA | NORAMIC MOBILE APPLICATIONS                              | 6  |

| 2.1.  | Introduction                                             | 6  |

| 2.2.  | Human Vision System Organization and Operation           | 10 |

| 2.3.  | Telepresence Systems in Hazardous Environments           | 13 |

| 2.4.  | Machine Vision Systems                                   | 14 |

| 2.5.  | Stereoscopic Display Systems                             | 20 |

| 2.6.  | Video Compression/Decompression Mechanisms and Standards | 26 |

| 2.7.  | Real-Time Video Processors                               | 35 |

| 2.8.  | Conclusion                                               | 39 |

| 3. AR | RCHITECTURE DEVELOPMENT OF RECONFIGURABLE PLATFORM FC    | R  |

| 3D-PA | NORAMIC TELEPRESENCE SYSTEM                              | 42 |

| 3.1.  | Introduction                                             | 42 |

| 3.2.  | Analysis of Operation Modes                              | 43 |

|    | 3.3. Sys | stem Architecture Organization                                   | 45      |

|----|----------|------------------------------------------------------------------|---------|

|    | 3.3.1.   | 3D-P Camera                                                      | 47      |

|    | 3.3.2.   | Video Compressor/Decompressor                                    | 49      |

|    | 3.3.3.   | Transceiver                                                      | 55      |

|    | 3.3.4.   | Display                                                          | 57      |

|    | 3.3.5.   | Transport Stream Combiner/Dispatcher                             | 59      |

|    | 3.3.6.   | Video Pre-Processor/Video Processor                              | 61      |

|    | 3.4. Co  | nclusion                                                         | 69      |

| 4. | IMPLE    | MENTATION OF THE PLATFOM FOR 3D-PANORAMIC TELEPF                 | RESENCE |

| SY | STEMS.   |                                                                  | 71      |

|    | 4.1. Int | roduction                                                        | 71      |

|    | 4.2. Sys | stem Design Implementation (stage 1)                             | 72      |

|    | 4.2.1.   | 4-Vision Subsystem                                               | 73      |

|    | 4.2.2.   | MARS Subsystem                                                   |         |

|    | 4.3. Sys | stem Design Implementation (stage 2)                             | 114     |

|    | 4.3.1.   | Selection of the Proposed Elements for the System Implementation | 115     |

|    | 4.3.2.   | System Hardware Architecture                                     | 120     |

|    | 4.4. Co  | nclusion                                                         |         |

| 5. | EXPER    | IMENTS AND RESULTS                                               | 124     |

| :  | 5.1. Int | roduction                                                        | 124     |

| 5.2.  | Experimental Setup                                                | 124 |

|-------|-------------------------------------------------------------------|-----|

| 5.3.  | Experimental Results Analysis                                     | 131 |

| 5.3   | S.1. Startup Time Analysis                                        | 131 |

| 5.3   | 3.2. Video Acquisition and Packet Transfer Time Analysis          | 134 |

| 5.3   | 3.3. Packet Reception and Frame Buffering Time Analysis           | 136 |

| 5.3   | Analysis of Bayer Color Decoding and RGB Pixels Output Timing     | 137 |

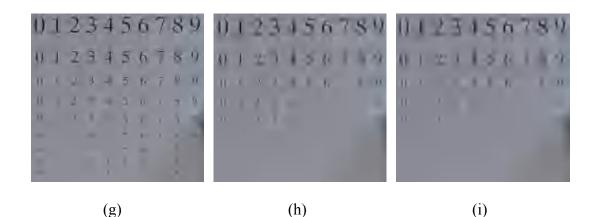

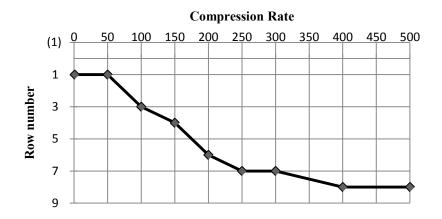

| 5.4.  | Compression Rate Analysis                                         | 140 |

| 5.5.  | Power Consumption Analysis                                        | 145 |

| 5.6.  | Utilization of Experimental Results in 4-Vision2 Subsystem Design | 147 |

| 5.7.  | Conclusion                                                        | 149 |

| 6. CO | ONCLUSION AND FUTURE WORK                                         | 151 |

| BI    | BLIOGRAPHY                                                        | 155 |

# List of Figures

| Figure 2.1: Human Eye Organization                                       | 11 |

|--------------------------------------------------------------------------|----|

| Figure 2.2: Human Visual Fields                                          | 12 |

| Figure 2.3: Stereo Vision Head System                                    | 15 |

| Figure 2.4: Stereo Vision Systems                                        | 16 |

| Figure 2.5: Pseudo-Stereo Vision System                                  | 17 |

| Figure 2.6: Line-Scan Sensor Rotation System                             | 18 |

| Figure 2.7: 2D Panoramic System Based on Panning Technique               | 18 |

| Figure 2.8: Multiple Camera Panoramic System                             | 19 |

| Figure 2.9: CCD Camera and Curved Mirror Panoramic System                | 20 |

| Figure 2.10: Rotating Mirror Architecture for Panoramic Vision           | 20 |

| Figure 2.11: Linear Polarizetion Scheme                                  | 22 |

| Figure 2.12: Circular Polarization Scheme                                | 23 |

| Figure 2.13: Autostereoscopic Displaying Schemes                         | 25 |

| Figure 2.14: MPEG GOP Sequence                                           | 29 |

| Figure 2.15: JPEG2000 Encoder Flow                                       | 34 |

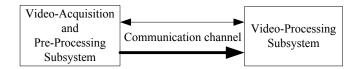

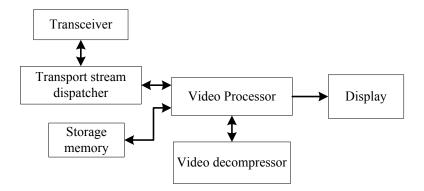

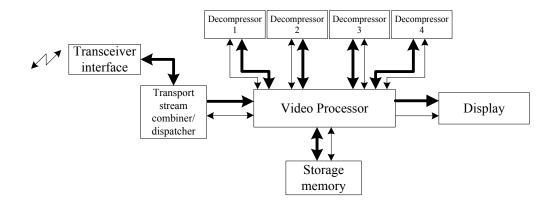

| Figure 3.1: Telepresence System Architecture                             | 45 |

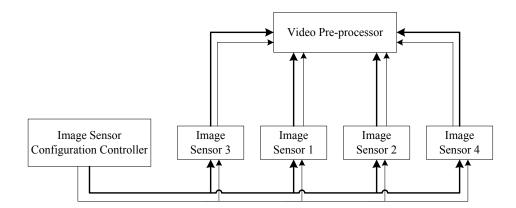

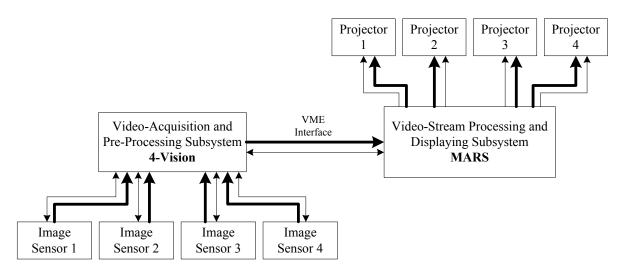

| Figure 3.2: Video-Acquisition and Pre-Processing Subsystem Block-Diagram | 46 |

| Figure 3.3: Video-Processing Subsystem Block-Diagram                     | 46 |

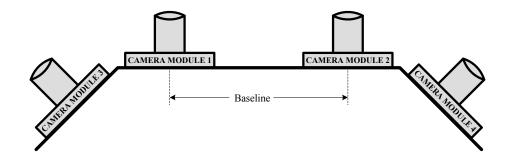

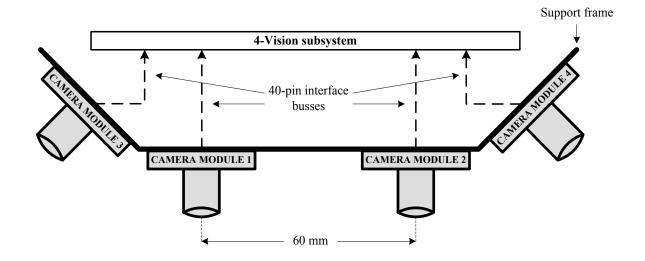

| Figure 3.4: Camera Modules Organization                                  | 48 |

| Figure 3.5: Image Sensor Configuration Controller Block-Diagram          | 49 |

| Figure 3.6: Resistance to Bit Errors of Various Compression Methods      |    |

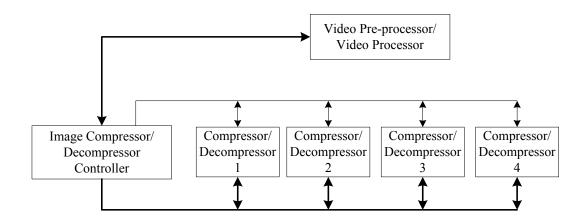

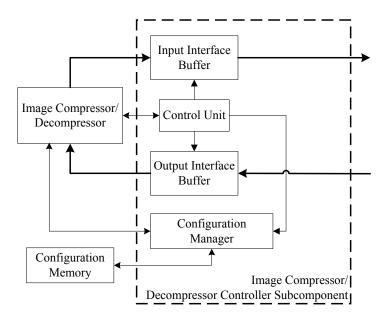

| Figure 3.7: Image Compressor/Decompressor Controller Block-Diagram       | 55 |

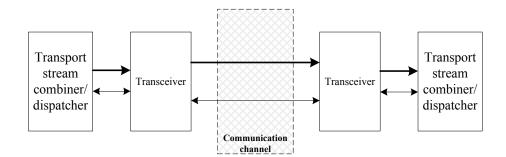

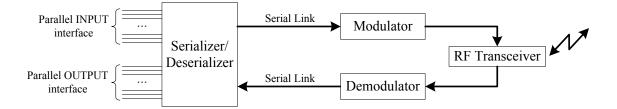

| Figure 3.8: Transceiver Block-Diagram                                    |    |

| Figure 3.9: Transceiver Operation Principles                                | 57       |

|-----------------------------------------------------------------------------|----------|

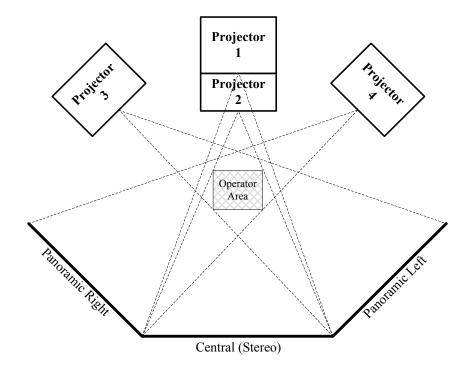

| Figure 3.10: Stereo-Panoramic Display                                       | 58       |

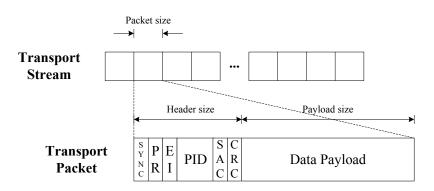

| Figure 3.11: Transport Stream Packet                                        | 59       |

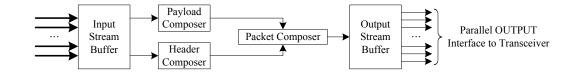

| Figure 3.12: Transport Stream Combiner Block-Diagram                        | 60       |

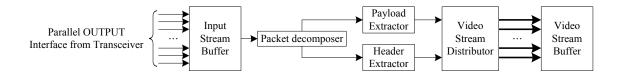

| Figure 3.13: Transport Stream Dispatcher Block-Diagram                      | 61       |

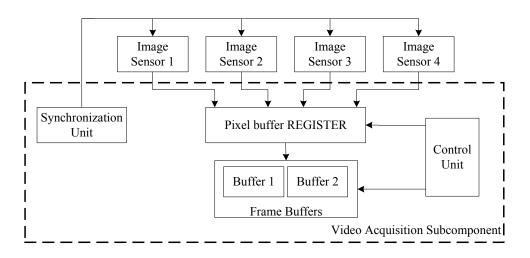

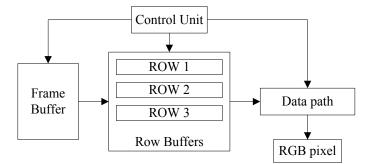

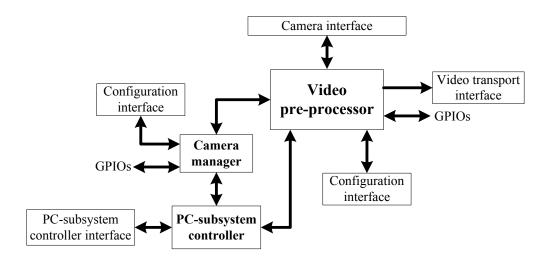

| Figure 3.14: Video Acquisition Subcomponent Block-Diagram                   | 62       |

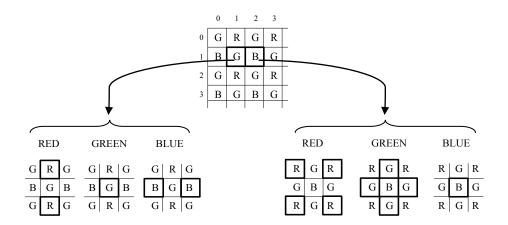

| Figure 3.15: Bayer Color Pattern                                            | 64       |

| Figure 3.16: Bilinear Interpolation Algorithm                               | 64       |

| Figure 3.17: Color Interpolation Subcomponent                               | 65       |

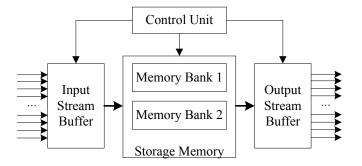

| Figure 3.18: Storage Memory Controller Subcomponent Block-Diagram           | 66       |

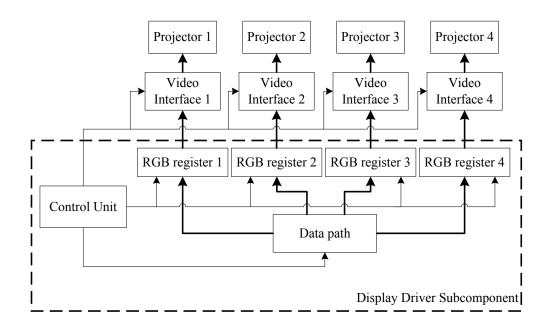

| Figure 3.19: Display Driver Subcomponent Block-Diagram                      | 67       |

| Figure 3.20: Image Compressor/Decompressor Controller Subcomponent Block-Di | agram 68 |

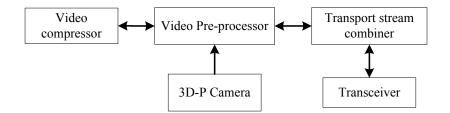

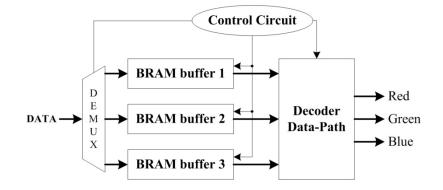

| Figure 4.1: Architecture of 3D-P Telepresence System                        | 72       |

| Figure 4.2: 3D-P Camera Organization                                        | 74       |

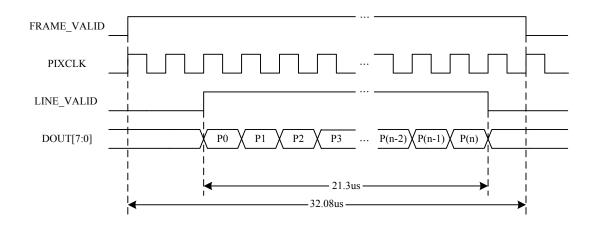

| Figure 4.3: Image Sensor General Timing Diagram                             | 78       |

| Figure 4.4: Camera Module Interface Connector                               | 79       |

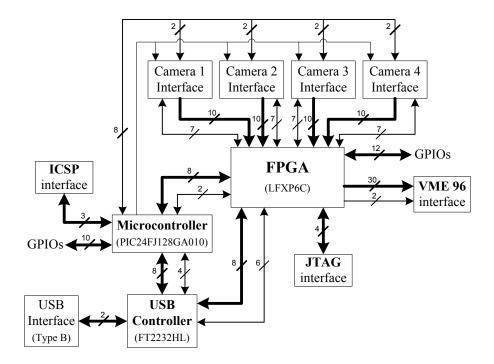

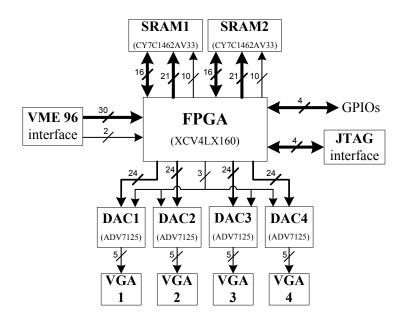

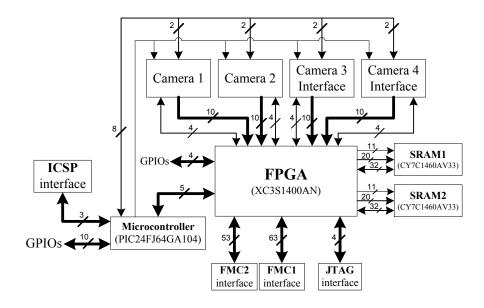

| Figure 4.5: 4-Vision Subsystem Hardware Architecture                        |          |

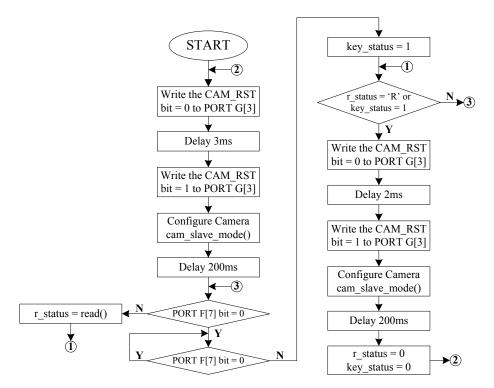

| Figure 4.6: FPGA Based Implementation Diagram                               |          |

| Figure 4.7: Microprocessor Based Implementation Flow Chart                  |          |

| Figure 4.8: Microprocessor Instruction Execution Process                    |          |

| Figure 4.9: 4-Vision Hardware Subsystem Architecture                        |          |

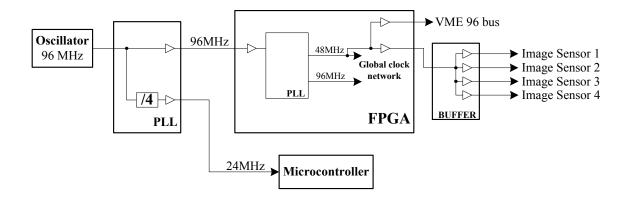

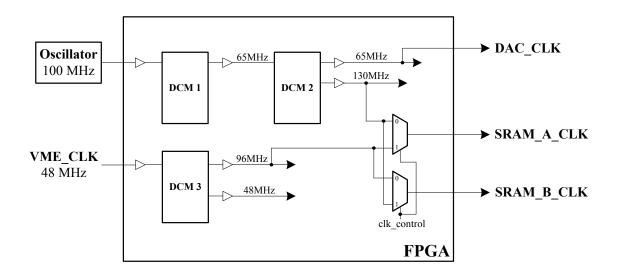

| Figure 4.10: 4-Vision Clock Distribution Scheme                             | 93       |

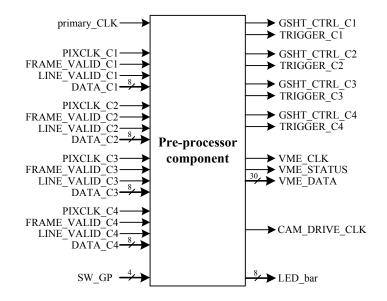

| Figure 4.11: Pre-Processor Component Symbol                                 | 94       |

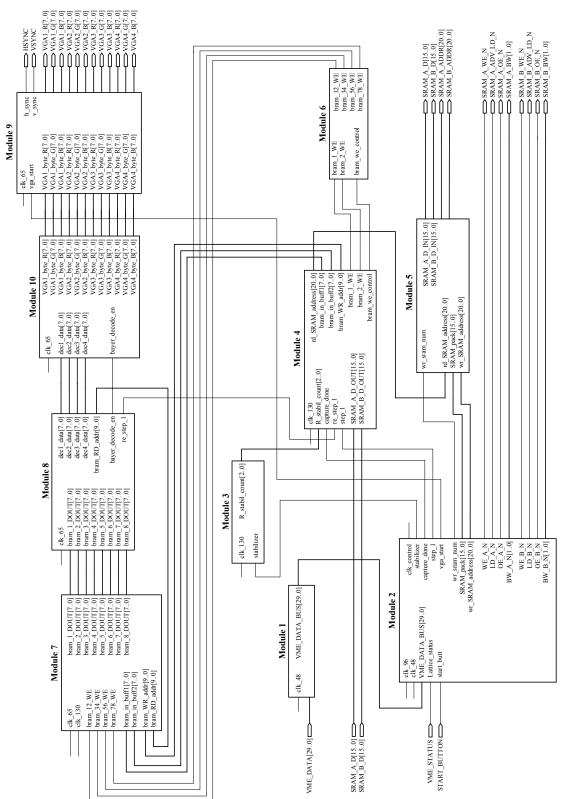

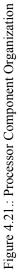

| Figure 4.12: Pre-Processor Component Organization                           |          |

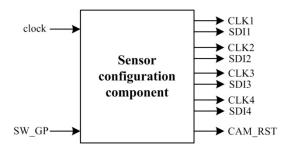

| Figure 4.13: 3D-P Camera Configuration Component Symbol                          |     |

|----------------------------------------------------------------------------------|-----|

| Figure 4.14: 3D-P Camera Configuration Component Operation Flow Chart            |     |

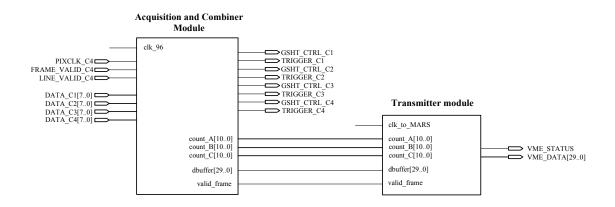

| Figure 4.15: MARS Hardware Subsystem Architecture                                |     |

| Figure 4.16: MARS Clock Distribution Scheme                                      |     |

| Figure 4.17: MARS Subsystem Data Flow                                            | 104 |

| Figure 4.18: Storage of Pixels in SRAM Memory                                    |     |

| Figure 4.19: XGA Timing Specification                                            |     |

| Figure 4.20: Processor Component Symbol                                          |     |

| Figure 4.21: Processor Component Organization                                    | 111 |

| Figure 4.22: Bayer Color Decoder Organization                                    | 113 |

| Figure 4.23: General Architecture of the Video-Acquisition and Pre-Processing So | -   |

| Figure 4.24: General Architecture of the Video-Steam Processing and Displaying   |     |

| Figure 4.25: 4-Vision Hardware Architecture                                      |     |

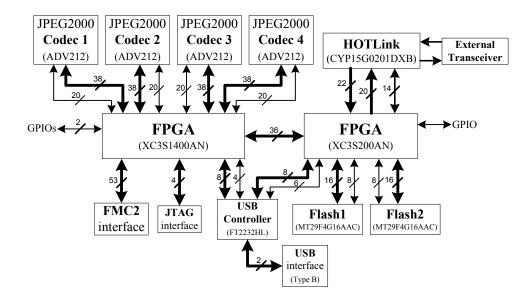

| Figure 4.26: 4V-J2C Hardware Architecture                                        |     |

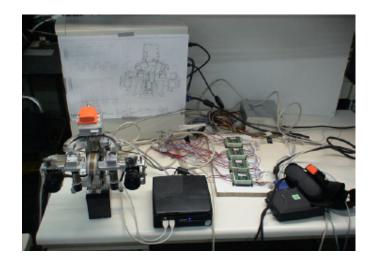

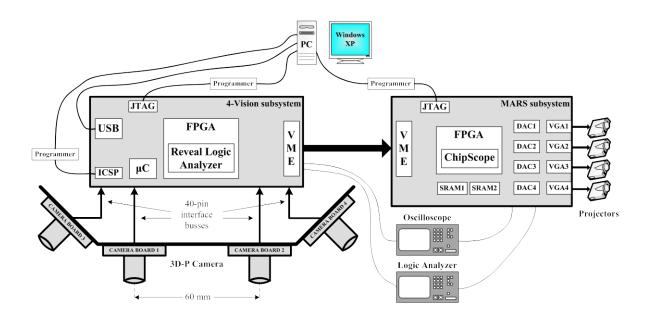

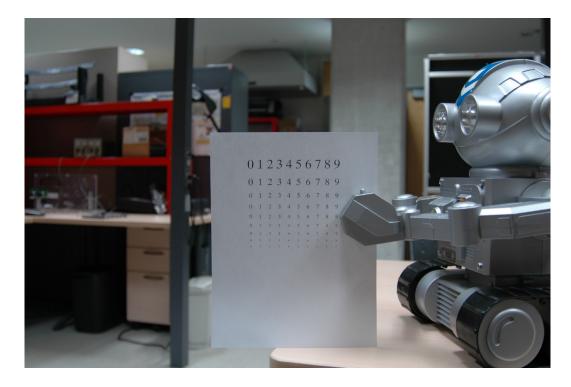

| Figure 5.1: Experimental Setup of 3D-Panoramic Telepresence System               |     |

| Figure 5.2: Image of the Experimental Setup                                      |     |

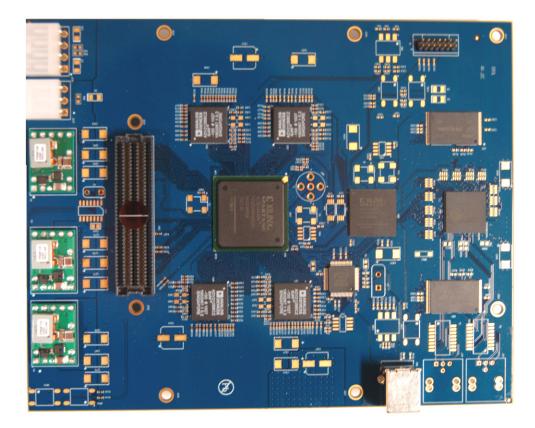

| Figure 5.3: Image of the 4-Vision Subsystem                                      |     |

| Figure 5.4: Image of the MARS Subsystem                                          |     |

| Figure 5.5: DC-DC Converters Startup Time                                        | 131 |

| Figure 5.6: 3D-P Camera Synchronous Operation                                    |     |

| Figure 5.7: 4-Vision Operation Timing Diagram                                    | 135 |

| Figure 5.8: Packet Reception and Frame Buffering Processes                       |     |

| Figure 5.9: Pixel Distribution to the Bayer Color Decoders                       |     |

| Figure 5.10: RGB Components Output to VGA                             | 139 |

|-----------------------------------------------------------------------|-----|

| Figure 5.11: Original Sample RAW Frame                                | 140 |

| Figure 5.12: Compression performance                                  | 142 |

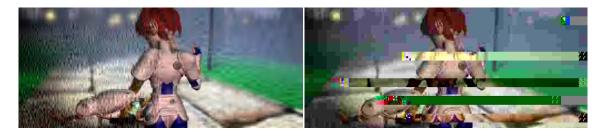

| Figure 5.13: Image Quality in Accordance to JPEG2000 Compression Rate | 143 |

| Figure 5.14: Image of the 4-Vision2 Subsystem                         | 148 |

| Figure 5.15: Image of 4V-J2C Subsystem                                | 149 |

# List of Tables

| Table 2.1: Machine Vision Systems Summary             | 40  |

|-------------------------------------------------------|-----|

| Table 3.1: Wireless Standards                         | 51  |

| Table 4.1: Image Sensor Signal Lines                  | 79  |

| Table 4.2: 4-Vision Subsystem Operational Frequencies | 92  |

| Table 4.3: Image Sensor Configuration Registers       | 99  |

| Table 4.4: MARS Subsystem Operational Frequencies     |     |

| Table 5.1: Startup Timing Summary                     |     |

| Table 5.2: Row Number to Font Size Correspondence     | 142 |

| Table 5.3: Power Consumption Chart                    | 146 |

# List of Acronyms

**3D-P** – 3D-Panoramic ALU – Arithmetic Logic Unit **ASD** – Autostereoscopic Display ASIC – Application-Specific Integrated Circuit **BER** – Bit Error Rate **BRAM** – Block Random Access Memory **CCD** – Charge-Coupled Device **CFA** – Color Filter Array **CMOS** – Complementary Metal Oxide Semiconductor **COFDM** – Coded Orthogonal Frequency Division Multiplexing **CPU** – Central Processing Unit **CR** – Compression Ratio CU – Control Unit **DCT** – Discrete Cosine Transform **DEMUX** – De-multiplexer **DF** – Data Fetch **DLP** – Data Level Parallelism **DSP** – Digital Signal Processor **DVB** – Digital Video Broadcasting **DWT** – Discrete Wavelet Transform **EBCOT** – Embedded Block Coding with Optimized Truncation **FMC** – FPGA Mezzanine Connector **FMO** – Flexible Macroblock Ordering FOV – Field of View **FPD** – Flat Panel Displays **FPGA** – Field-Programmable Gate Array FW – Firmware **GOP** – Groups of Pictures **GPU** – Graphics Processing Unit **HD** – High Definition HDL – Hardware Description Language HMD – Head Mounted Display **HQ** – High Quality HW – Hardware **ID** – Instruction Decode **IF** – Instruction Fetch ILP - Instruction-Level Parallelism ISO - International Organization for Standardization **IVT** – Interactive Virtual Telepresence **JPEG** – Joint Photographic Experts Group JTAG – Joint Test Action Group LC – Liquid Crystal

MARS – Multi-stream Adaptive Reconfigurable System

**MIMD** – Multiple Instruction Multiple Data

MPEG – Moving Picture Experts Group

MUX – Multiplexer

**OLED** – Organic Light Emitting Diode

**PC** – Personal Computer

PCB – Printed Circuit Board

**PIC** – Peripheral Interface Controller

PSVS – Pseudo-Stereo Vision System

**RCS** – Reconfigurable Computing System

**RF** – Radio Frequency

**RISC** – Reduced Instruction Set Computing

**ROI** – Region of Interest

RTL – Register Transfer Level

**SIMD** – Single Instruction Multiple Data

**SISD** – Single Instruction Single Data

**SoC** – System on Chip

SRAM – Synchronous Random Access Memory

SW – Software

**TDM** – Time Division Multiplexing

TFT-LCD – Thin Film Transistor Liquid Crystal Display

TLP – Thread-Level Parallelism

TVS – Telepresence Viewing System

**URV** – Underwater Robotic Vehicles

USB – Universal Serial Bus

#### 1. INTRODUCTION

#### 1.1. Motivation

In the last decade, increasing need for stereo-vision, stereo-panoramic and even semispherical stereo-vision systems has been dictated by a wide variety of scientific and industrial applications. The examples of these applications are: telepresence systems for remote robotic operations and unmanned vehicles, telemedicine and telesurgery systems, 3D HDTV and multimedia, video-gaming and professional simulators, various applications for autonomous robots and intelligent machine vision systems. Most of these applications require multi-modal high-performance operations when different video processing algorithms are active in different periods of time. As well, data-structure (e.g. video-frame structure, compressed transport stream formats etc.) may also change dynamically. The above aspects in turn required dynamic adaptation of the video processing system on variations of the workload. Therefore, dynamically reconfigurable platforms became one of the most promising ways for implementation of the above video processing systems.

On the other hand, the progress in technology of reconfigurable logic devices made possible cost-effective implementation of the entire video-processing systems in one chip. This allowed in turn a dramatic increase of system performance and reliability as well as, reduction of system cost and power consumption. Nowadays, Field Programmable Gate Array (FPGA) devices allow not only deploying the large System-on-Chip (SoC) in one FPGA but also dynamic re-configuration of the FPGA logic. This ability allows implementation of Dynamically Reconfigurable Systems on Chip (DRSoC) and thus, effective adaptation of the multi-modal multi-video-stream acquisition, processing and displaying systems on the basis of FPGA devices.

One of the most important applications for multi-modal and multi-video-stream processing systems is telepresence and teleoperation in environments where actual presence and operation is dangerous or even impossible for human beings. First of all, this is important for the remote monitoring and control of mobile systems working in harsh areas such as space, nuclear power plants, the ocean, underground pipelines, mining and many others. Another important application of this technology could be telemedicine and e-Health, where Immersive Interactive Virtual Telepresence (IVT) systems can be implemented effectively.

However, most of the existing video processing systems developed for the above applications are based on RISC processors or processors with vector processing accelerators (e.g. GPU: Graphic Processing Units). These processors are able to provide certain flexibility in adaptation to the variations of the workload but are limited in performance compared to Application Specific Integration Circuits (ASICs). On the other hand, ASICs can provide the highest performance but cannot change their functionality and thus, adapt to the variations in video-processing algorithms or data structure.

Therefore, the main goal for the presented work was the creation of effective highperformance multi-stream video-acquisition, processing and displaying platform on the basis of FPGA devices for immersive telepresence and teleoperation applications including prototyping, testing and analysis of performance parameters.

# 1.2. Objectives

The main objective of the work is to research and develop the reconfigurable platform for the immersive 3D-Panoramic (3D-P) Telepresence System for mobile applications.

This objective includes the following aspects:

- Extended literature search of existing approaches and methods used in designing of 3D-Panoramic vision systems;

- Develop an architecture of the reconfigurable multi-mode 3D-P Telepresence System;

- Design and implement the 3D-P Telepresence System;

- Analyze the experimental results associated with performance parameters of the considered class of telepresence systems and determine the set of recommendations for the design process.

## 1.3. Contributions

The following contributions were made during the period of the work:

- Extended literature search in the area of stereo, panoramic and stereo-panoramic telepresence systems was conducted. As a result, the analysis of the state-of-the-art for the class of the telepresence systems for mobile robotic applications was provided;

- The framework of the reconfigurable multi-mode 3D-P Telepresence System was developed including multi-stream acquisition, parallel video-processing and parallel

displaying subsystems. As a result, all levels of architecture including system level, on-board and on-chip levels were developed;

- The architecture of 3D-P Telepresence System was implemented in the first prototype. This implementation allowed for a collection of data of the system performance parameters. As a result, the analysis of system performance based on the obtained data was provided.

- Based on the performance analysis obtained from the first prototype, the set of recommendations for the design process of 3D-P Telepresence Systems for mobile applications was determined. The updated version of the system reflecting these recommendations was designed and prototyped.

The first system prototype was presented in the annual conference SVAR-2010: Space Vision and Advanced Robotics held at MDA Space Missions, Brampton, ON in June 2010. The presentation: "3D Panoramic Naturally Interactive Real-Time Telepresence System" [54] was awarded with the first prize for the best presentation and demo.

The updated system prototype was presented at the conference and exhibition "Discovery 11" held at Metro Toronto Convention Centre in May 2011.

#### 1.4. Thesis organization

The presented thesis is organized in six chapters. Chapter 1 summarizes motivation, objectives, contributions and thesis organization of this work. The observation of the telepresence systems application domain opens up in Chapter 2. The following material in this chapter presents the main aspects of the human vision system organization followed by observation of existing telepresence systems solutions for hazardous environments and observation of various systems and mechanisms used in the considered class of applications. Chapter 3 presents the proposed architecture of the adaptive 3D-P Telepresence System for mobile applications. Prior to the architecture description, the detailed analysis of operation modes required for various operation tasks is described in detail. Following the mode analysis, the system architecture partitioned on hardware, firmware and software components is presented. 3D-P Telepresence System architecture implementation is performed in Chapter 4. This chapter material covers the details associated with implementation of two versions of the system including hardware, firmware and software development. Chapter 5 contains information about the experimental setup, experimental results and their analyses. This chapter also presents the recommendations for the modifications of the system architecture for the next version of 3D-P Telepresence System and describes the updated system prototype as well. The final chapter of the thesis, Chapter 6, presents the summary of the research and development work performed for the project. Future development work is also outlined.

# 2. COMPREHENSIVE SURVEY OF TELEPRESENCE SYSTEMS FOR 3D-PANORAMIC MOBILE APPLICATIONS

#### 2.1. Introduction

The concept of telepresence system as well as the great importance of research in this domain was first underlined by Marvin Minsky in 1980 [1]. Since then, many attempts were made in order to create a system that would provide a sense of physical presence at a remote location to a human.

Visual information being an integral part of a human's ability to process sensory stimulus became a major motivation of using video information in telepresence systems. However, depending on particular telepresence application in addition to video information; audio and haptic might also be included.

Integration of visual system which can reproduce human vision in a remotely controlled mobile system made it possible to perform a wide range of tasks which were either dangerous for humans to be involved in or simply were impracticable. Tasks such as bomb disposal, demining operations, rescue operations, telesurgery, fire fighting, underwater operations and outer space operations can be grouped into three general categories of telepresence applications such as operation in hazardous environments, telemedicine and teleconferencing.

The teleconferencing exhibits a rapidly growing interest of such sectors of business, government, healthcare and education. This is due to economical and environmental reasons which can eliminate the need for transportation, thus saving time, money and energy. Teleconferencing can be described as a communication environment where multiple

geographically separated users are meeting together. A communication environment on each user site is realized by a video/audio-acquisition unit, processing unit, display unit and communication channel. Depending on a particular setup, different types of units as well as different numbers of them can be arranged to create a communication environment. The fact that teleconferencing does not assume any remote human operations resulted in majority of 2D implementations presented on the market. On the other hand, the majority of research is performed on 3D implementations.

Recent examples of commercial telepresence solutions such as Cisco's TelePresence [68] and HP's Visual Collaboration Studio [69] offer real-time High Definition (HD) video and High Quality (HQ) audio for the participants. However, both solutions do not produce stereoscopic views of the participants, thus, eliminating any immersive experience.

The research work performed by Feldmann et al. [2] presents real-time multi-camera 3D teleconferencing system. Each communication site is assumed to have two participants and two multi-view displays for remote parties. Data processing is performed on 5 PC clusters interconnected with high-bandwidth Infiniband network. The experimental results indicate that the system is capable to process 16 video streams in real-time 3D at 20fps.

Teleconferencing system proposed by Kauff et al. [3] is based on a concept of Augmented Reality (AR) which can be described as combination of real-world and computer generated Virtual Environment (VE). All conferees are captured by four video cameras and subsequently rendered such that they appear sitting around a shared virtual table. In order to realize such a system, a PCI-based multi-processor board was developed for PC terminals. The proposed setup from the author makes a seamless transition between the real and virtual world.

Another example of teleconferencing system is proposed by Sen Ma et al. [4]. The group developed panoramic a teleconferencing system based on the image mosaic principle. Two CMOS cameras are arranged to perform video acquisition. The Nios II embedded processor is programmed to perform image processing and consequent Ethernet transmission to a remote terminal. Experimental results indicate that the system satisfies the requirements for the teleconference situation.

The telemedicine applications can be divided on two types: remote medical consultations and remote surgeries [47]. The first aspect is quite similar to teleconferencing applications. As for remote surgeries, also called telesurgeries, it requires remote manipulations with a patient and with remote robotic equipment.

Telesurgery is developed to provide an access to advanced surgical care for patients irrespective of their geographical location [5], [48]. In a situation where a highly qualified surgeon is located in a different county than a patient, transfer time may result in added complications or even death. Therefore, to overcome this problem, Assisted Robotic Telepresence Surgery (ARTS) is being used. Robotic telemanipulators have statically positioned 2D or 3D vision system as well as different set of surgical tools integrated into a robotic system. A surgeon – teleoperator can perform local or remotely controlled robotic surgery while observing his manipulations via specialized monocular or binocular setup. Examples of telesurgery systems are "da Vinci" and "ZEUS". Both of them demonstrate enhanced operation precision thus allowing surgeons to perform more complex and fine grain operations [6].

Paper presented by Eadie et al. [49] describes types of successfully performed operations as well as provides an analysis of telepresence surgery. The consequences of a telepresence surgery experience lead to another application of telepresence systems in telemedicine called telementoring. It is used to perform real-time interactive hands-on experience transfer by an expert surgeon to novice surgeons located at the remote site. This is done by providing expert surgeon control over robotic platform in order to assist the remote mentor and, if necessary, take over and complete the task. The work presented by M. Anvari [7] describes a Canadian experience in telerobotic surgical operations performed between two hospitals separated 400 km away. Successful results of remotely completed 22 robotic assisted advanced laparoscopic surgeries demonstrate not only feasibility of such tasks but also provides an example of an effective solution for remote "on the job" training.

Despite of the number of successful results, current telesurgical technology experiences several major barriers. The first and most important barrier is the quality of communication lines. Because of the strict requirements for control and associated video information transmission, time delays are not acceptable. The second barrier is the cost of robotic platforms and associated maintenance cost.

The equipment used for teleconferencing and telemedicine can be considered as static in terms of placement and operation. Nevertheless, equipment used for hazardous environments requires mobile deployment of both a video-acquisition system as well as actuators for remote robotic manipulation. Moreover, since most of the hazardous tasks involve approaching an operational area, existence of panoramic-vision in addition to stereovision is required. All of that makes this class of telepresence systems not only the most complex and the most demandable, but also applicable to all other classes of telepresence. Therefore, the presented work will focus on the class of telepresence systems with regard to hazardous environments.

With this in mind, the following aspects should be analyzed before determination of the proposed system architecture:

- Human vision system organization and operation;

- Observation of existing implementations of telepresence systems for hazardous environments;

- Stereo and stereo-panoramic machine vision systems;

- Stereoscopic display systems;

- Video compression/decompression mechanisms and standards;

- Real-time video processors.

# 2.2. Human Vision System Organization and Operation

Each human eye acquires individual images of a visual scene from two slightly different perspectives. This difference is created because of an eye separation on about 60-80 mm and is referred to as a baseline. Several stages are involved in order to perceive (receive and process) an image by a human.

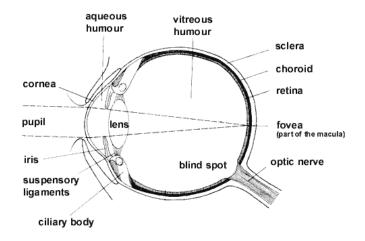

In the first stage, light rays entering the eye are bent and brought to focus as they pass through the cornea and lens. The iris, located after the cornea, controls the amount of light entering the eye through the pupil. By means of ciliary muscles, the shape of the lens can be changed in order to perform focus operation. Figure 2.1 below demonstrates the general organization of a human eye.

Figure 2.1: Human Eye Organization

In the next stage, a focused image is projected onto photosensitive receiver which is called the retina. The retina consists of two types of regions, central and peripheral. Both of these regions contain arrays of two types of cells, called rods containing approximately 100-120 million cells and cones, containing 6-7 million cells accordingly.

Cones are high-precision cells which manage color vision and detail. The highest concentration of cones can be found in macula's region called fovea. The fovea is the absolute center of vision and is specialized for visual acuity and object recognition. Cone cells dramatically reduce in number beginning from the fovea and up to both temporal and nasal directions. This results in poor visual acuity in peripheral region comparing to foveal vision (central vision).

Rod cells are insensitive to color and are more sensitive to light than cone cells, thus, they manage vision in low light conditions. They are generally dominant in the periphery of the retina and are used for night vision, motion detection, large objects detection and peripheral vision.

When the light contacts both rods and cones cells, a series of complex chemical reactions occur which in turn create electrical impulses in the optic nerve. These electrical impulses are consequently transmitted to the brain's visual cortex in order to perform image processing.

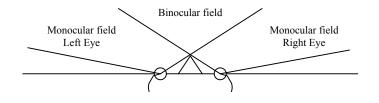

As it was mentioned before, because of eye horizontal separation, two images are received from slightly different perspectives. The angular difference between two images is called horizontal retinal disparity which is used by the brain to obtain depth information as well as object's spatial location [24]. The retinal visual field of an eye is about 120°. However, the intersection of visual fields from both eyes creates an actual stereoscopic (binocular) region of only about 50°, (see Figure 2.2). In this region, objects that are located within a 30 meter distance can only be perceived in 3D space by a human [9].

Figure 2.2: Human Visual Fields

An understanding of the above basic principles of human eye operation is very important, since they can be used as a reference for image processing algorithms implementation, as well as for hardware layout organization.

#### 2.3. Telepresence Systems in Hazardous Environments

As it was already mentioned, telepresence systems designed to operate in hazardous environments are the most complex and at the same time, the most demandable class of telepresence systems. The spectrum of related tasks include fire fighting, rescue operations, demining operations, underwater operations, outer space operations, bomb disposal etc. In order to prevent direct exposure of a human to such hazardous environments, a variety of systems are being developed [50]. The majority of them are based on a principle of teleoperator placement at a safe remote site equipped with an interactive environment that provides visual feedback and robotic control needed for remote system management. As a result, humans can effectively perform operation without any risk to their lives. An implementation example of such system is presented by Kron et al. [10]. They designed a bimanual haptic telepresence system in order to perform demining operations. Two-arm manipulator with touch and force feedback and the stereoscopic visual system needed for such an application-specific procedure as unscrewing and excluding the detonator were integrated to a quadruped walking robot. Performed experiments demonstrated that operator located 20 km apart from actual teleoperation site successfully completed demining task.

Underwater operations, particularly deep-water operations, are also related to the category of hazardous missions for a human. Periodical inspection and repair procedures of underwater structures such as pipelines, for example, have to be performed to make sure that structural safety and integrity is maintained. Thus, replacement of human divers with remotely controlled Underwater Robotic Vehicles (URV) is highly desirable. An example of such a system is presented by Iastrebov et al. [28]. The Telepresence Viewing System (TVS)

was designed by this research group and was integrated to URV. This enables remote operation from the base vessel providing a stereoscopic view of the scene.

In spite of a number of telepresence systems specifically designed to operate in hazardous environments, there are still a number of challenges related to most of them. For example, limited FOV (Field of View) of a robotic vision system, ineffectiveness of a remote robotic driving performance caused by lack of peripheral vision, poor video image quality and associated frame rate, and communication channel delays are all challenges. The analysis performed by Chen et al. [11] confirms that most of the factors stated above result in human performance degradation which in turn makes task completion questionable.

## 2.4. Machine Vision Systems

For several decades a number of machine vision systems have been developed. Depending on application, video-acquisition of a scene can be stereo, panoramic or a combination of stereo-panoramic. These acquisition methods can be classified into two categories: dioptric methods, where only refractive elements (e.g. lenses) are employed, and catadioptric methods, where reflective components (e.g. mirrors) are used in combination with refractive elements. Dioptric systems include single or multiple cameras attached to various lenses. Catadioptric systems include mirrors of different shapes (e.g. curved, planar) and a camera with attached optics.

The majority of stereo video-acquisition systems are based on a principle of human's binocular vision which was described in Section 2.2. However, the function of an eye's optic system and associated retina are fulfilled by optic lens (e.g. C-mount or CS-mount) mounted

on top of an image sensor (e.g. CMOS or CCD). Providing a separation between acquisition units, image processing tasks (e.g. stereo matching, disparity calculation, etc.) performed by the brain are realized by stream processors which are described in the Section 2.7.

An example of stereo vision system based on the previously mentioned principles and designed for remotely operated robot is provided in [12]. The proposed stereo vision head consists of two image sensors separately mounted on a frame and horizontally separated from each other, illustrated in Figure 2.3. Each image sensor provides resolution of  $640 \times 480$  pixels at maximum 30 fps. In order to compensate distortions caused by servo motors used to follow operator's HMD movements, stabilization sensors are being exploited. Image processing is performed by means of two PC clusters.

Figure 2.3: Stereo Vision Head System (courtesy to [12])

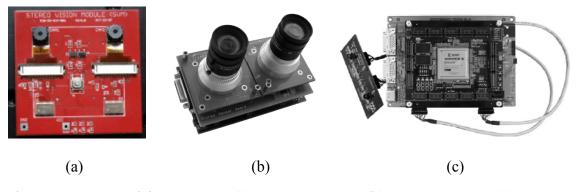

Other examples of stereo vision systems based on human vision are presented by Khaleghi et al. [13], by Jan Pohanka et al. [14] and by S. Jin et al. [15], Figure 2.4 (a), (b),

(c) accordingly. Each system, being application specific, introduces different baseline parameters. In order to simplify the camera calibration process and reduce computations associated with image rectification and disparity calculation, image sensors are placed on the same PCB. Image processing units selected for the first two systems are BlackFin DSPs. Third system has Virtex 4 FPGA, programmed to perform necessary computations.

Figure 2.4: Stereo Vision Systems: (a) courtesy to [13], (b) courtesy to [14], (c) courtesy to [13]

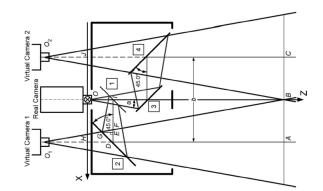

A completely different technique of designing stereo-vision systems is based on a singlecamera and a set of mirrors located in front of it. Recent work performed by Theodore P. Pachidis and John N. Lygouras [16] presents Pseudo-Stereo Vision System (PSVS) composed of a camera, a beam splitter and three statically positioned mirrors. As it can be noted from Figure 2.5, views acquired by mirrors 2 and 4 can be considered as if they were captured by two virtual cameras. Mirror 1 is a beam splitter which permits the reflection of 50% of the incident light from the 2<sup>nd</sup> mirror, whereas it permits through its body the other 50% of light coming from the 3<sup>rd</sup> mirror. As a result, the superposition of two views creates a stereoscopic image acquired by a single real camera.

Figure 2.5: Pseudo-Stereo Vision System (courtesy to [16])

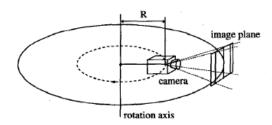

Panoramic and stereo-panoramic vision systems are also presented by a number of research groups. R. Petty et al. [17] presented a setup consisting of a pair of line-scan sensors mounted on a rotating platform. Each CCD line-scan sensor consists of a column of 1024-elements. During rotation, each one-dimensional sensor obtains two-dimensional perspective images of an object workspace (see Figure 2.6). This can be done with FOV of an image varied up to 360°. After the rotation of the sensors with respect to a static scene of an object of interest is completed, two overlapping fields of view define the stereoscopic region. For any object located within the stereoscopic region, disparity calculations may be performed.

Figure 2.6: Line-Scan Sensor Rotation System (courtesy to [17])

Similar to the previous system, an approach utilizing the panning technique (when a line scan-camera rotates up to a full view of 360° around a rotation axes) is presented by M. Barth and C. Barrows [18]. However, instead of a two line-scan sensors, one is used to provide a complete two-dimensional panoramic acquisition (see Figure 2.7).

Figure 2.7: 2D Panoramic System Based on Panning Technique (courtesy to [18])

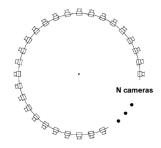

S. Tzavidas and A. Katsaggelos [23] proposed alternative implementation of a rotating camera method without moving parts. Instead of rotating a single or a pair of cameras,

multiples are mounted on rig with fixed geometry, as shown in Figure 2.8. As it can be seen, all cameras look outward from the center of the rig. A circular projection technique is employed in order to construct a stereo-panoramic video sequence.

Figure 2.8: Multiple Camera Panoramic System (courtesy to [23])

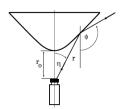

Another group of stationary panoramic vision systems use specially shaped mirror(s) combined with conventional camera(s). As a mirror reflects an image of the environment to a camera, it can be then converted to a panoramic perspective image. Depending on the shape of the mirror, which can be conical, hyperboloidal [19], spiral [20] etc., different transformation methods are required.

J.S. Chahl and M.V. Srinivasan [21] developed a technique for capturing panoramic images using a curved mirror and a conventional CCD camera providing extra-wide FOV, Figure 2.9. The shape of the mirror is such that a linear relationship exists between the angle of incidence of light onto the mirror surface and the angle of reflection onto the image sensor; in respect to the center of array.

Figure 2.9: CCD Camera and Curved Mirror Panoramic System (courtesy to [21])

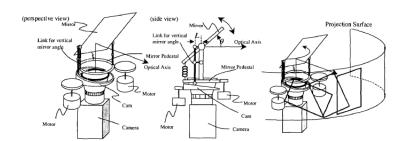

Setup presented by T.Nakao and A. Kshitani [22] is based on a stationary camera and 2axis mirror rotation mechanism as illustrated in Figure 2.10. Performing a 360° mirror rotation using set of motors, allows panoramic scene acquisition with a single stationary camera.

Figure 2.10: Rotating Mirror Architecture for Panoramic Vision (courtesy to [22])

# 2.5. Stereoscopic Display Systems

Over the years a number of 3D display techniques have emerged. Existing techniques can be divided into display systems requiring the user to wear eyeglasses for filtering or

displaying purposes and into systems where the user can observe a stereoscopic scene in a natural manner.

A very first stereoscopic display system was introduced in 1853 and it is still being used now. An example of such a system is color-multiplexed (anaglyph) display. It consists of anaglyph glasses and a pair of projector devices. The glasses have two different lens-filters which are chromatically opposite. For example, one of the commonly used color schemes can use a red filter to pass through only the red component of an image for the left eye and the second cyan filter to pass through only Blue and Green components of an image for the right eye. Both projectors have the same color filters as used for the glasses. The image pair is displayed overlapping, such that the left image contains only the red component and the right image contains only the cyan component. Portions of the image that are red will appear dark through the cyan filter. Therefore, each eye sees perspective as it is supposed to see which results in stereoscopic sensation.

Although anaglyph offers an affordable solution to create a good depth sensation, the quality of perceived colors is very poor. Moreover, despite the quick adaptation to stereoscopic view, after 15 minutes unpleasant aftereffect causes reduction of red-cyan perception of the real world.

Another example of stereoscopic display system requiring eyeglasses is the Polarized Display System. It is based on the same principle as anaglyph, however, instead of colored filters, polarized ones are used. The polarized filter is used to perform a conversion of a number electromagnetic waves emitted by a light source and represents an undefined polarization into a beam with defined polarization. The common types of polarization filters are linear and circular polarization filters.

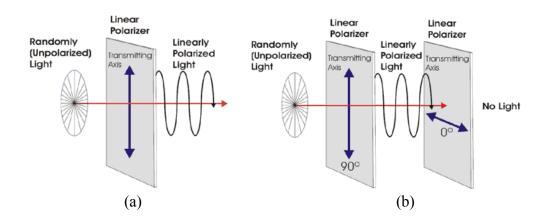

When an un-polarized light enters the linear polarizing filter, only electromagnetic waves oscillating in a singular orientation plane defined by a polarization degree (vertical or horizontal transmitting axis) can fully pass through, (see Figure 2.11 [a]). However, waves oscillating in a transmitting axis of 90° to one another are absorbed or reflected by the filter, thus producing near absolute blockage of light (see Figure 2.11 [b]). Finally, waves having both horizontal and vertical components will be partially transmitted.

Figure 2.11: Linear Polarization Scheme (courtesy to API [71])

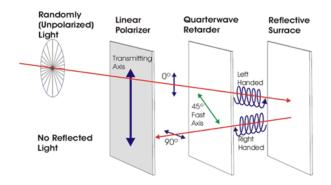

The circular polarizing filter represents the combination of a linear polarizer and a quarter wave retarder [71]. After the linear polarization is performed, light passes through the quarter wave retarder which retards the velocity of one of the polarization components (X or Y), one quarter of a wave out of phase from the other polarization component (see

Figure 2.12). Depending on which polarization component is retarded, one will have either a left handed or right handed circular polarizer. The left handed circular polarized light cannot pass through a right handed circular polarizer and vice versa. This occurs because of the reflected opposite handed circularly polarized light passing through the wave retarder, which becomes linearly polarized again, but 90° to its original orientation. Therefore light passing through a circular polarizer filter, reflecting off another surface, cannot pass back through the circular polarizer.

Figure 2.12: Circular Polarization Scheme (courtesy to API [71])

Circular polarization prevents the black-out effect and has a reduced "ghosting" effect compared to linear polarization. Despite better color rendering and lack of adaptation period comparing to anaglyph display, polarized stereo systems need a much stronger light source since polarized light loses at least 50% of its original intensity.

Shutter glasses are also related to the stereoscopic display class. In order to enable stereo viewing, shutter glasses are used in conjunction with a display screen. The shutter is made of

glass containing a Liquid Crystal (LC) layer. When the voltage is applied, the glass becomes dark, otherwise the glass is transparent. Thus, shutters are alternately opaque and transparent so that only one eye can see through the glasses at any given moment. The display system alternately presenting the right and left eye perspective images has to generate frames twice the frequency required for viewing. Thus, glasses being synchronized with the display let through only one image at a time for each eye enabling illusion of a three dimensional space.

Shutter glasses mostly eliminate "ghosting" which is a problem for two previously described setups. Moreover, unlike Red-Cyan color filter 3D glasses, LC shutter glasses provide 3D viewing in the full color spectrum. However, the constant shuttering might bother viewers who are very sensitive to low refresh rates (e.g. 60Hz) and cause flickering which can result in headaches. In addition, the majority of eyewear is designed so that peripheral vision, which is not shuttered, is completely covered to avoid viewing differences, thus creating the lack of peripheral perception.

Head Mounted Display (HMD) represents another existing solution of stereoscopic display class. HMDs can have a form of glasses or helmets worn on the head and consist of two small displays positioned near each users' eyes blocking out all external light or vision. They are commonly used in virtual reality applications and normally include a mechanism that follows the movement of the observer's head. Recent HMDs are realized by LCD or OLED technology. Being connected directly to a video source, displays present left and right images to the appropriate eyes providing a strong binocular disparity and 3D illusion. However, lower-priced HMD systems provide very narrow FOV while wide FOV which is

natural for humans, is only observed in HMDs priced over \$10,000 [70]. Examples of HMD devices used in telerobotics and telesurgical systems can be found in [26],[12] and [8].

Autostereoscopic Displays (ASDs) represent stereo displaying techniques which eliminates use of any type of eyewear or headgear needed for filtering or displaying visual information [27].

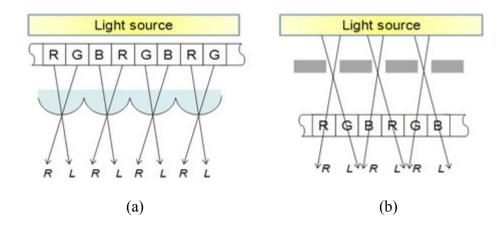

State-of-the-art systems are based on Flat Panel Displays (FPDs) equipped either with lenticular screens or parallax barriers to provide binocular disparity. In both cases, a pair of images for the left and right eye is cut in vertical strips. Then, vertical strips associated with the left and right viewpoints are interlaced and combined into one image. This interlaced image is then displayed on FPD.

Figure 2.13: Autostereoscopic Displaying Schemes

Lenticular lens represents an array of magnifying lenses such that when viewed from slightly different angles, different parts of images are magnified. Attaching a lenticular lens to the front of FPD screen magnifies parts of interlaced image that correspond to the left viewpoint and can only be seen by the left eye and vice versa, (see Figure 2.13 [a]). Such an acquisition process from two viewpoints creates 3D perception.

Parallax barrier is a fine column based grid of liquid crystals placed in between of TFT-LCD and associated backlight, (see Figure 2.13 [b]). By controlling the switching of the liquid crystal light emitting from the backlight, the interlaced image separates into two images. This causes different images to be seen by the right and left eyes, creating a sense of depth.

Both lenticular lens and parallax barrier technologies are heavily dependent on viewer location. Small deviation of view to either side causes a distortion of images. Thus, a very specific "sweet spot" for getting the 3D effect should be maintained. Moreover, because FPD resolution is divided between two images the overall horizontal screen resolution is reduced by a factor of two.

## 2.6. Video Compression/Decompression Mechanisms and Standards

As it was already mentioned in the beginning of this chapter, video information plays an essential role for applications such as telepresence. Besides that, the requirements for video quality and associated frame rate are very high. As a result, bandwidth of a communication channel required to transmit such HD data has also been in accordance to data rate. However this in most of the cases is not feasible. Therefore, compression mechanisms play an essential role for bit rate reduction of the digital video signal. The compression ratio can be described as a degree to which the encoder reduces the bit rate and equals:

compression ratio (CR) = decoded bit rate / encoded bit rate

Compression mode can be lossless or lossy. The lossless mode guarantees the exact recovery of the original data after compression and subsequent decompression. The lossy mode assumes that decompressed data would not be identical to the original.

Over the years a series of compression standards for still images such as JPEG, JPEG2000 as well for video sequences such as M-JPEG, M-JPEG2000, MPEG group including MPEG-1, MPEG-2, MPEG-4 and H.264 has been established. Prior to understanding MPEG standards, the JPEG standard is described since it is used as a building block for the complete MPEG group.

Joint Photographic Experts Group (JPEG), named after the committee that created it, is a worldwide ISO standard for compression of digital still images. The JPEG defines both controlled lossy and lossless compression based on Discrete Cosine Transform (DCT) compression algorithm. The basic JPEG encoder flow consists of four stages. At the first stage, the input image is divided into blocks of 8×8 pixels. The choice of the block size is specifically selected to reduce computation requirements related to larger blocks. On the next stage, a two-dimensional discrete cosine transformation (DCT) is performed for all 8×8 pixel block values. Following the transformation, blocks' coefficients are quantized. The quantization step size for each of the 64 DCT coefficients is specified in a quantization table, which remains the same for all blocks. In the next stage, in order to further reduce the amount of data represented in each block redundancy reduction is performed. As a result, the bit stream generated in this way, combined with signaling information such as quantization tables, resolution details, etc. shape a JPEG bit stream.

The corresponding decompression is performed by following all inverse procedures (i.e. redundancy reduction, quantization, DCT) and then putting 8x8 pixel blocks back together results in an output image construction.

When used in mid and high bit-rate applications, JPEG compressed pictures show no visual difference to the original uncompressed ones. On the other hand, applications with low bit-rate requirements involve greater quantization steps which results in artifacts appeared as "blockiness" due to 8×8 pixel block structure.

As it was already mentioned the JPEG standard was designed for a compression of only still images. On the other hand, in order to compress a video sequence, Motion-JPEG (M-JPEG) was offered. The concept of M-JPEG assumes that each video frame of an image sequence is coded as a separate JPEG image. Despite advantages of JPEG such as flexible CR and provided robustness with no dependency between the frames, M-JPEG was not adopted for several reasons. The first reason is the lack of a standard for M-JPEG meaning that there are considerable incompatibilities between the methods used by different manufacturers [29]. The second reason is that independent frame compression, without taking into consideration similarity between successive frames, makes no use of video compression techniques which results in a very low compression ratio.

In order to overcome shortcomings of M-JPEG, Moving Pictures Experts Group (MPEG) defined an algorithm for coding moving pictures based on work of JPEG. The main conceptual difference introduced in the group of MPEG standards is a consideration of similarities in consecutive video pictures which results in higher compression factors.

28

Therefore, the following paragraph will explain the general principle of video compression common for MPEG group and after, standard specific features will be described.

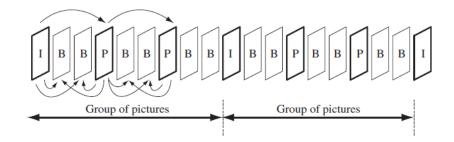

Each MPEG video sequence is divided into one or more groups of pictures (GOPs). Typical pattern of GOPs is represented in Figure 2.14. GOPs are defined by three types of pictures: I-, P- and B-pictures. In a sequence of picture frames, the start frame, called Intracoded picture (I-picture), is spatially encoded with no reference to other pictures using the JPEG engine. I-picture frame is used as a main reference for further frames and can be decoded without referencing to other pictures. This allows termination of transmission error propagation to the next frames. Since I-pictures are compressed using the JPEG standard, it provides only moderate compression.

Figure 2.14: MPEG GOP Sequence

The second type of pictures is Predictive-coded pictures (P-pictures). Pictures of this type are predicted from the preceding I- or P-pictures using the forward motion-compensated prediction mechanism. For that, a picture is broken down into macroblocks, which are the basic elements for motion estimation, and then the block-matching technique

is applied to the preceding picture. For example, a block-matching can be performed by shifting macroblock with a specific step (e.g. pixel, half of the pixel etc.) to all possible positions within a given search area. When a match is found, motion vector is generated, specifying the location of the best matching macroblock in the reference frame to be used for prediction picture. As a result, a set of motion vectors are generated and transmitted to the decoder in order to reconstruct the picture from the original reference. This allows achieve higher compression due to vector transmission instead of complete image parts as it is for I-pictures. However, because P-pictures serve as a reference for future P- and B-pictures prediction, errors occurring during transmission can propagate to the succeeding pictures and multiply over the time.

The bidirectional-predicted pictures (B-pictures) are coded using bidirectional motioncompensated prediction from both the past and future references of I- or P-pictures. The procedures involving macroblock-matching technique are the same as those described for Ppictures, however, the search is performed in past and future references as depicted by arrows in Figure 2.14. As a result, forward motion vector, which references to a best matching block in the previous picture, and a backward motion vector, which references to a best matching block in the following picture, is generated. By averaging between the past and the future blocks, motion-compensated prediction is formed. Therefore, B-pictures provide the highest compression in contrast to I- and P-pictures and do not propagate errors since they are not used as references.

In spite of better compression ratios of B-pictures, increasing the number of B-pictures reduces correlation between the previous and next I- or P-pictures. This results in quality

degradation as well in increase of computational complexity. Moreover, the search algorithm needed for prediction requires very large computational power. Because of the frame dependencies, errors in I- or P-pictures result in error multiplication for future predicted frames.

MPEG-1 is the first generation of digital compression standards for video and twochannel stereo audio applications. It was proposed based on the assumptions that acceptable video and audio quality can be obtained for a total bandwidth of about 1.5Mbps. The input resolution supported by MPEG-1 is optimized to operate at  $352 \times 240$  pixels at 30 fps, commonly referred as SIF (Source Input Format) video. However, the maximum supported resolution can be as high as  $4k \times 4k$  pixels at 60fps. MPEG-1 is also defined for progressive frames only; therefore, it has no direct support for interlaced video applications commonly used in broadcasting television applications.

The second phase of MPEG, named MPEG-2, appeared with demand for higher quality and higher resolution video applications operating at 4-15 Mbps. The MPEG-2 standard is heavily based on MPEG-1; however, numbers of improvements are introduced.

In order to cover a wide range of applications, MPEG-2 classified groups of profiles and levels (bitstream scalability, color space resolutions, frame resolutions, bit rates, sampling rates) are important for applications. Thus, seven distinct profiles are defined as simple, main, signal-to-noise ratio (SNR) scalable, spatially scalable, high, 4:2:2, and multiview. Within each profile four levels are defined as low (352×288 pxls and 30 fps), main (720×576 pxls and 30 fps), high-1440 (1440×1152 pxls and 60 fps), high (1920×1152 pxls

and 60 fps). Thus, all possible combinations of profiles and levels cover the most practical MPEG-2 applications. Moreover, MPEG-2 is suitable for coding not only the progressive video format but as well the interlaced video format commonly used in broadcasting television applications. Therefore, frame-based and field-based motion-compensated prediction and two corresponding DCT modes are developed.

MPEG-4 Part 2 and later developed MPEG-4 Part 10 (H.264/AVC) belong to the MPEG-4 standard.

MPEG-4 Part 2 [32] is based on coding techniques similar that of MPEG-1/MPEG-2, however it defines four types of coding tools: video object coding for the coding of natural and/or synthetic generated, rectangular or arbitrarily shaped Visual Objects (VOs), mesh object coding for the coding of visual objects represented with mesh structures, model-based coding for the coding of a synthetic representation and animation of the human face and body, and still texture coding for the wavelet coding of still textures. Similarly to MPEG-2, the MPEG-4 standard defines profiles; each of which targets a specific group of applications. The most commonly implemented profiles are Simple Profile (SP) and Advanced Simple Profile (ASP). SP targets low-complexity and low-delay applications such as mobile video communications, whereas the ASP provides higher coding performance and can be used in applications where video at higher bit rates is required.

Although H.264/AVC [33] is similar to preceding standards in the block-based video compression technique, it provides significantly higher compression capability due to several conceptual revisions and improvements.

Similarly to previous standards, pictures are partitioned into macroblocks, which are fundamental coding units. Also, each picture can be divided into a number of independently decodable slices, where each slice consists of one or more macroblocks. The slice type (e.g. I-slice, P-slice, B-slice) defines which prediction modes are available for the macroblocks. Within a single frame different types of slices can be presented. The concept of slice group, known as Flexible Macroblock Ordering (FMO) feature, provides loss/error robustness, enhanced Region of Interest (ROI) customization and low-delay construction of composited image scenes. Moreover, H.264/AVC is distinguished from its predecessors in a number of additional features. These features include spatial directional prediction; an advanced motion compensation model using variable block size prediction, quarter-sample accurate motion compensation, multiple reference picture prediction, and weighted prediction; an in-loop deblocking filter. Evaluation performed using H.264/AVC [30] standard show that coding yields bit rate savings at approximately half a bit rate used by MPEG-2 and approximately 35% over MPEG-4 Part 2 SP.

JPEG2000 standard [31] was created to address weaknesses of JPEG standard as well to provide a number of new features. The JPEG2000 standard is characterized by a maximum allowed image size to be  $(2^{32}-1) \times (2^{32}-1)$  and the maximum number of components in an image to be  $2^{14}$ , color component depth ranging from 1 to 38 bits, superior low bit-rate performance, continuous tone (grayscale and color) and bi-level (B/W) compression, lossy and lossless compression, robustness in the presence of bit errors, backward compatibility with JPEG and many more [34].

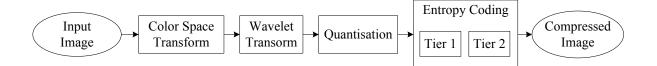

The typical JPEG2000 encoder system consists of several fundamental building blocks, as shown in Figure 2.15. These blocks include image pre-processing, Discrete Wavelet Transform (DWT), quantization and Embedded Block Coding with Optimized Truncation (EBCOT).

Image preprocessing is an optional step and consists of tiling (partitioning of image into a number of rectangular non-overlapping blocks), DC level shifting and multi-component transformation (reduction of the correlations among the multiple color components in a multicomponent image). After optional preprocessing step, DWT performs decomposition of each image tile into four sub-bands. On the next stage each sub-band is independently quantized by a quantization parameter. The quantized sub-bands are then divided into a number of smaller code-blocks of equal size.

Figure 2.15: JPEG2000 Encoder Flow

Following this, each code-block is passed to EBCOT engine consisting of Tier1 and Tier2. Tier1 performs entropy coding, while Tier2 generates the output bitstream.

The corresponding decoder architecture is similar to the encoder architectures with data flow in the reverse direction.

The results obtained by [35], [36], [37] indicate that JPEG2000 compression scheme outperforms the JPEG scheme in all aspects, thus, providing higher compression ratios and quality on both higher and lower bit-rate scenarios. The main drawback of the JPEG2000 standard compared to its predecessor is that the coding algorithm is much more complex and computationally intensive than that implemented in JPEG.

Similarly to the MJPEG system, the JPEG2000 standard defines file format as well instructions for coding motion sequences. The motion JPEG2000 represents an image sequence encoded using JPEG2000 coding algorithm for still pictures. Therefore, MJPEG2000 inherits all advantages of JPEG2000 and is aimed for applications where high-quality frame-based compression is needed.

## 2.7. Real-Time Video Processors

The class of applications requiring task execution under specific timing constraints is related to real-time system class. In specialized telepresence systems, real-time video stream processing involves manipulation with a great amount of continuously generated data. Therefore, in order to handle it four types of processing devices such as Central Processing Unit (CPU), Graphics Processing Unit (GPU), Application Specific Integrated Circuit (ASIC) and Reconfigurable Computing System (RCS) have been used.

CPU is a general-purpose processor related to a Single Instruction Single Data stream (SISD) uniprocessor category. The processor consists of three major components such as register set, Arithmetic Logic Unit (ALU) and Control Unit (CU). These components allow

for the execution of tasks consisting of the set of instructions stored in memory. In general, all instructions are executed in a sequential order. There are five stages per each instruction execution cycle such as Instruction Fetch (IF), Instruction Decode (ID), Data Fetch (DF), Instruction Execution (EX) and Store result (S). However, four out of five execution stages perform only service operations (IF, ID, DF, S). Therefore, in order to improve processor performance two basic techniques are used: clock frequency boosting and/or Instruction-Level Parallelism (ILP) [38].

There is another type of CPU which instead of one processor has multiples of them (e.g. two, four, and eight) interconnected and located on the same die. A Multiprocessor, also called multi-core Processor, has Multiple Instruction streams Multiple Data streams (MIMD) [38] architecture. In MIMD, each processor has its own control unit that issues instructions and operates on its own data. This allows operation on multiple threads in parallel which is called Thread-Level Parallelism (TLP) [38]. Due to such architecture it is possible to reduce not only overall task execution time but also to reduce operation frequency of the multiprocessor.

In contrast to general-purpose CPU, Graphical Processing Unit (GPU) architecture is specifically tailored for image processing algorithms which are computationally intensive and parallelizable. The fact that image processing tasks require similar calculations performed on quantities of data led to a Single Instruction stream Multiple Data stream (SIMD) [38] architecture. A modern GPU consists of a set of multiprocessors each of which consist of a set of processors with SIMD architecture. This allows execution of the same instruction for all multiprocessors but operation on different data at each clock cycle, thus exploiting the Data Level Parallelism (DLP) [38].

Despite GPU's dramatic performance increase in graphical applications, not all algorithms can be vectorized. Moreover, even making use of DLP, each individual processor still performs sequential instruction execution thus requiring higher clock rates for performance improvement. As a result, the increase of power consumption is unavoidable.

As opposed to general-purpose CPU and GPU processors, ASIC's internal architecture is specifically customized for a particular application and not for a general use. An ASIC engineer can create functional blocks with known electrical characteristics (e.g. propagation delay, capacitance and inductance, etc.), employ data parallelization, implement cache memory according to specification etc. Moreover, modern ASICs can include processors, memory blocks and other large building-blocks thus creating so-called System-on-a-Chip (SoC) architecture. All of this allows for the achievement of maximum performance possible for a particular application. Moreover, due to customizable architecture power consumption can also be decreased. However, for all those advantages there is a price to pay expressed in design complexity, associated cost, high cost per a unit when producing a small number of units and the longest time to market out of all possible implementation methods.

Field-Programmable Gate Array (FPGA) is a class of Reconfigurable Computing Systems (RCSs) devices that has performance close to an ASIC, but has a flexible architecture. By using Hardware Description Language (HDL) any design (e.g. DVB modulator, MPEG-4/H.264 decoder, DDR2 Controller, etc.) can be described on a Register Transfer Level (RTL), consequently synthesized and loaded to the FPGA's configuration memory. Unlike sequential processors, FPGAs can provide any level of parallelism thus maximizing throughout and minimizing power consumption by lowering operation frequency.

The basic architecture of FPGA consists of an array of configurable logic embedded into a configurable interconnected structure and surrounded by configurable I/O blocks [39]. In addition, modern FPGAs [40],[41],[42],[43] include other specialized elements such as memory blocks, DSPs, microprocessors etc. These specialized blocks perform more specific tasks than configurable logic, however they can also be configured in accordance with application needs. In case any modifications to the existing circuitry (e.g. communication standard) running on FPGA are necessary, the HDL code can be modified and reprogrammed again. This procedure can be performed as many times as necessary. All of this makes FPGA a versatile and useful device for high performance applications (e.g. video stream processing). Moreover, fast prototyping and as a result, shorter time-to-market, can be achieved due to reprogrammable architecture. However, high production cost of FPGAs makes them useful for only low volume products.

The performance comparison of CPU, GPU and FPGA for image processing applications is presented by Shuinchi Assano et al. [44]. The experimental results are suggesting that GPU has a potential for achieving almost the same performance as FPGA, but only for tasks involving independent pixel processing. As for more complicated algorithms which use shared data, GPU demonstrates very poor performance. In contrast, multi-core CPU performs much better for shared data processing. Another comparison of CPU and GPU processors performed by Nan Zhang et.al. [45] shows significant speedup achieved by GPU used for edge detection and filtering algorithms tested on various image resolutions.

The comparison of performance obtained with FPGA and GPU implementations of realtime stereo vision system is performed by Rathees Kalarot and John Morris [46]. The results reveal that despite a much slower system clock, FPGA implementation is superior due to extensive pipelining.

#### 2.8. Conclusion

The literature observation of existing telepresence systems oriented for various applications has shown that the class of the systems designed for hazardous environments is the most complicated for implementation. This is due to the following reasons: i) telepresence systems used for hazardous environments, in a general case, requires mobile deployment of both a video-acquisition system as well as actuators for remote robotic manipulation; ii) necessity of panoramic vision in addition to stereo-vision has to be provided for natural perception of the remote environment by a human-operator; iii) various modes of operation have to be supported in order to provide adaptation of the system to different operation tasks. The above reasons makes this class of telepresence systems the most complex and applicable to all other classes of telepresence systems (e.g. telemedicine, teleconferencing etc). Therefore, the presented work focuses on the class of telepresence systems in regards to hazardous environments.

To determine the potential architectural organization of telepresence system for the selected class of applications, the following aspects were analyzed: i) existing implementations of telepresence systems for hazardous environments; ii) organization of the human visual system; iii) existing machine vision systems; iv) stereoscopic display systems; v) real-time video processor solutions and vi) mechanisms of video compression and decompression.

Based on the performed observation and analysis, the following issues associated with the existing machine vision systems were determined: i) lack of peripheral vision; ii) utilization of electromechanical (moving) parts; iii) relatively low video quality performance including frame resolution and/or frame rate; iv) relatively high power consumption in case of CPU based implementations. The Table 2.1 summarizes the implementations details of existing machine vision systems.

| Literature source          | Stereo | Panoramic | Processor<br>type | Video-<br>acquisition<br>method | Video quality  |

|----------------------------|--------|-----------|-------------------|---------------------------------|----------------|

| Pohanka et al. [14]        | yes    | no        | FPGA & DSP        | Dioptric                        | n/a*           |

| Jin S. et al. [15]         | yes    | no        | FPGA              | Dioptric                        | 60fps          |

| Amanatiadis A. et al. [12] | yes    | no        | CPU               | Dioptric                        | 640x480, 30fps |

| Khaleghi et al. [13]       | yes    | no        | MCU & DSP         | Dioptric                        | 20fps          |

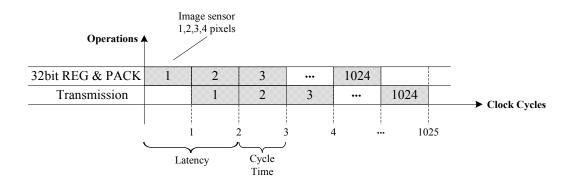

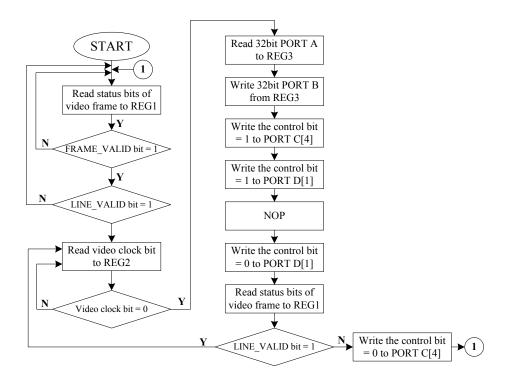

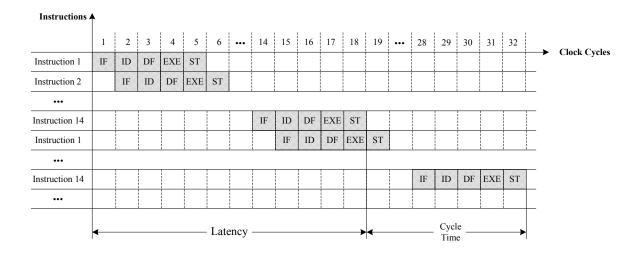

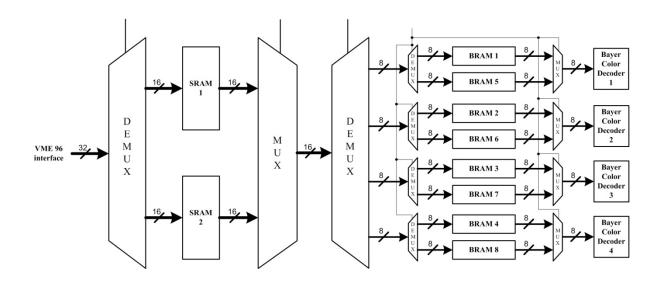

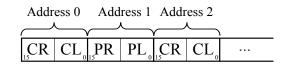

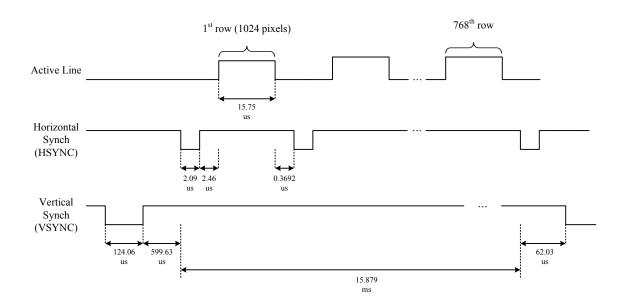

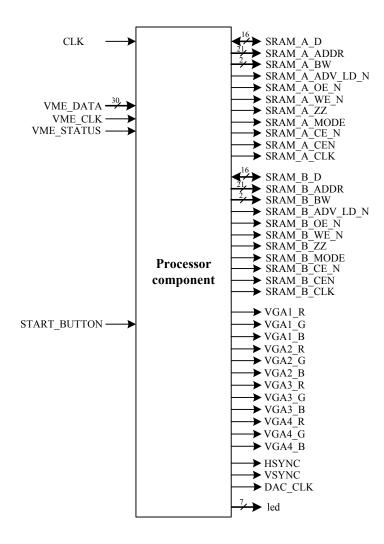

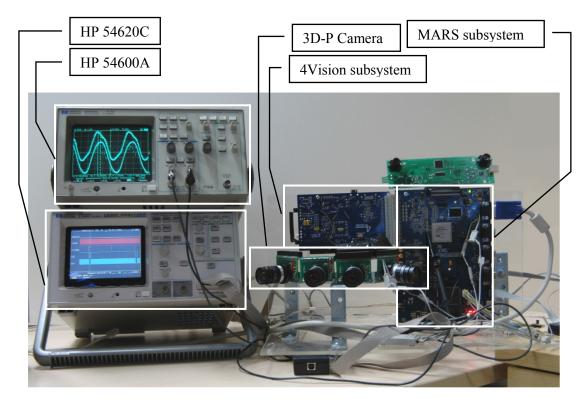

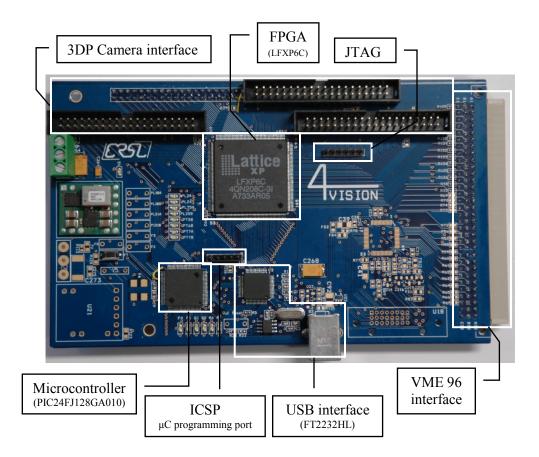

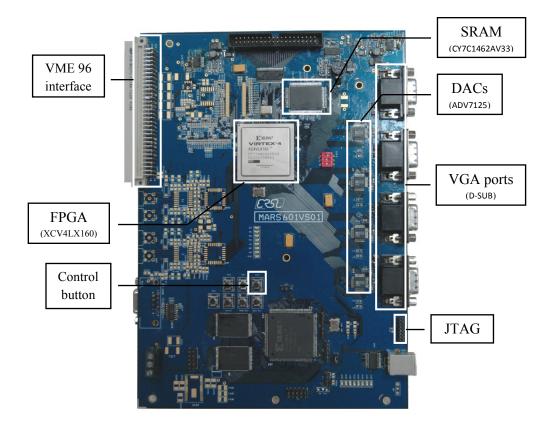

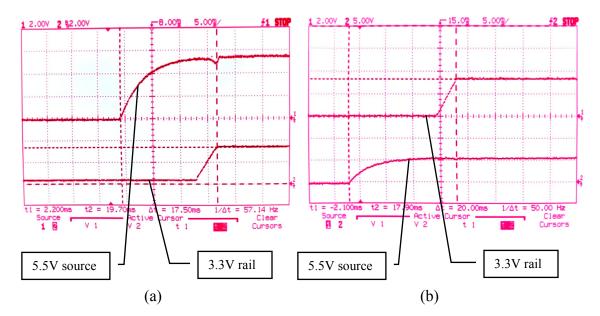

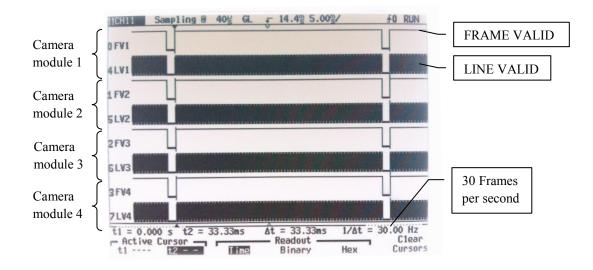

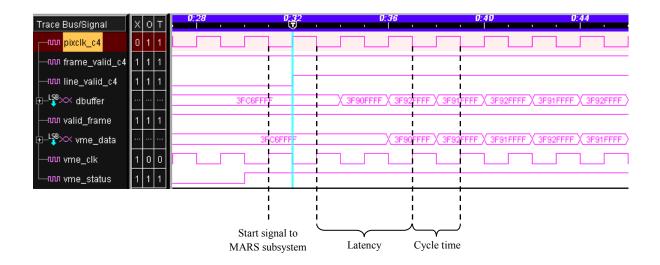

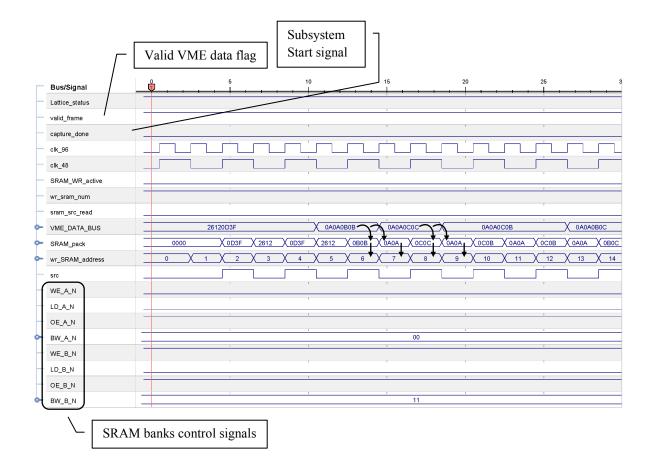

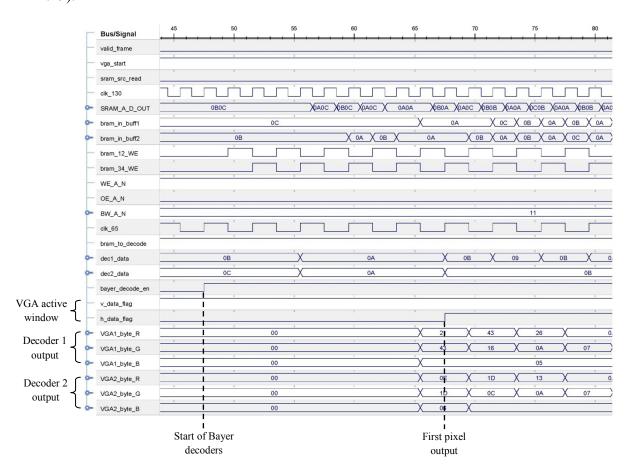

| Iastrebov et al. [28]      | yes    | no        | n/a <sup>*</sup>  | Dioptric                        | 800x600        |