### IC TESTING USING THERMAL IMAGE BASED ON INTELLIGENT CLASSIFICATION METHODS

by

Furat Al-Obaidy

MASc., University of Technology, Baghdad, Iraq, November 1999

BASc., University of Technology, Baghdad, Iraq, July 1996

A thesis

presented to Ryerson University

in partial fulfillment of the requirements for the degree of Master of Applied Science in the Program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2016

©Furat Al-Obaidy, 2016

### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for scholarly research.

I understand that my thesis may be made electronically available to the public.

#### Abstract

# IC Testing Using Thermal Image Based on Intelligent Classification Methods

Furat Al-Obaidy

Master of Applied Science, Electrical and Computer Engineering Ryerson University, Toronto, 2016

The goal of this thesis is to propose an algorithm which would can locate the defect IC on the PCB during their manufacturing phase based on a thermal image. A 3-dimensional PCB finite-element model is developed to estimate the temperature profile of stacked ICs. Image processing by noise removing and region of interest segmentation are applied. Two sets of feature extraction are presented; first-order histogram features and Gray Level Co-occurrence Matrix (GLCM) features. The Principle Component Analysis (PCA) method is applied to decrease the feature's extractions into smallest uncorrelated input. Three main intelligent techniques; Multilayer Perceptron (MLP), Support Vector Machine (SVM), and Adaptive Neuro-Fuzzy Inference System (ANFIS) are used to classify the thermal conditions of ICs into normal and faulty status.

On validation, the proposed approach applies to do thermal testing on Arduino UNO. The experimental evaluation is performed to detect the fault condition on the real time operating PCB.

#### ACKNOWLEDGEMENTS

First, I would like to gratefully and sincerely thank my advisor, Dr. F. Mohammadi, for her kindly instructions and help in this research. This work could not have been finished without her guidance, support, and time. Her belief in me throughout the difficult times during my research and my graduate studies is what keeps me motivated to this day.

I would also like to thank my thesis committee for generously offering their time, guidance and good will throughout the review of this document.

I would like to thank my friends, and all the members of the Ryerson Microsystems research group for their constructive guidance and suggestions as well as their consistent encouragement.

Last but not the least, I thank my wife and my family for everything I have today. They made me who I am today and sacrificed many of their own dreams so that my dreams could become reality. They provided every tool that I needed to succeed, and their constant encouragement made the completion of this degree possible.

#### **DEDICATION**

This thesis is dedicated to the memory of my father, mother, wife, and family,

For their endless love, support, and encouragement.

| <b>Table of</b> | Contents |

|-----------------|----------|

|-----------------|----------|

| Abstract                                                                      | iii  |

|-------------------------------------------------------------------------------|------|

| Acknowledgements                                                              | iv   |

| Dedication                                                                    | v    |

| List of Tables                                                                | viii |

| List of Figures                                                               | ix   |

| Chapter 1: Introduction                                                       | 1    |

| 1.1. Introduction                                                             | 1    |

| 1.2. Literature Review                                                        |      |

| 1.3. Thesis Objectives                                                        | 4    |

| 1.4. Thesis Layout                                                            | 5    |

| Chapter 2: Review of the Fault and Testing Techniques of Integrated Circuits  | 7    |

| 2.1. Introduction                                                             | 7    |

| 2.2. Fault, Defect, and Failure Relationship                                  | 7    |

| 2.3. VLSI Defects Types                                                       | 7    |

| 2.4. Fault Detection and Simulation                                           | 10   |

| 2.5. Digital PCB Testing Methods                                              | 10   |

| 2.5.1. Destructive Testing Methods                                            | 10   |

| 2.5.2. Non-destructive Testing Methods                                        | 11   |

| 2.6. Summary                                                                  | 13   |

| Chapter 3: Fundamentals of Thermal Testing                                    | 15   |

| 3.1. Introduction                                                             | 15   |

| 3.2. Infrared Thermography Principle                                          | 15   |

| 3.3. Principles of the Infrared Temperature Measurement                       | 17   |

| 3.4. Classification of Thermography Techniques                                | 19   |

| 3.4.1. Passive Thermography                                                   |      |

| 3.4.2. Active Thermography                                                    | 19   |

| 3.5. Thermography advantages and Limitations                                  |      |

| 3.6. Summary                                                                  |      |

| Chapter 4: Introduction to Intelligent Classification Models                  | 21   |

| 4.1. Introduction                                                             | 21   |

| 4.2. Artificial Neural Networks                                               | 21   |

| 4.2.1. The architecture of the MLP                                            | 23   |

| 4.2.2. The Training of the MLP                                                | 24   |

| 4.3. Support Vector Machine                                                   | 25   |

| 4.4. Adaptive Neuron-Fuzzy Inference System                                   | 26   |

| 4.5. Summary                                                                  | 29   |

| Chapter 5: Proposed Method for Fault Detection and Classification of the PCBs | 31   |

| 5.1. Introduction                                                             | 31   |

| 5.2. Proposal PCB Modeling                                                    | 33   |

| 5.2.1. Geometry Model Generation                                              | 34   |

| 5.2.2. Physical Materials and Thermal Parameters                              |      |

| 5.2.3. Mesh Generation                                                       | 37  |

|------------------------------------------------------------------------------|-----|

| 5.2.4. Simulation Results and Verification                                   |     |

| 5.3. Image Enhancement                                                       |     |

| 5.3.1. Image Denosing                                                        |     |

| 5.3.2. Image Segmentation for ROI                                            |     |

| 5.4. Feature Extraction                                                      |     |

| 5.4.1. Statistical Features Based First Order Histogram Statistical Analysis | 49  |

| 5.4.2. Statistical features based on Gray Level Co-occurrence Matrix         | 51  |

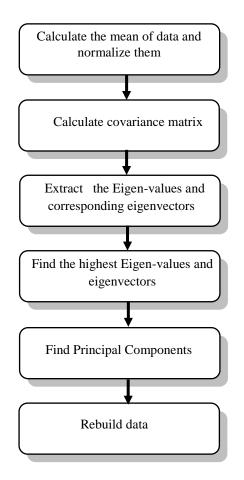

| 5.5. Principle Analysis Components                                           |     |

| 5.6. Classification Modules                                                  | 57  |

| 5.7. Results and Discussion                                                  |     |

| 5.7.1. Classification Results based on MLP                                   |     |

| 5.7.2. Classification Results based on ANFIS                                 |     |

| 5.8. Summary                                                                 | 69  |

| Chapter 6: Experimental Evaluation                                           |     |

| 6.1. Introduction                                                            |     |

| 6.2. Platform Setup                                                          |     |

| 6.2.1. Real- PCB Under Test                                                  |     |

| 6.2.2. FLIR Infrared Camera Unit                                             |     |

| 6.2.3. Data Acquisition System and Auxiliary Unit                            |     |

| 6.3. Experimental Setup                                                      |     |

| 6.4. Image capture and processing                                            |     |

| 6.5. Classification Results                                                  |     |

| 6.6. Summary                                                                 |     |

| Chapter 7: Conclusions and Future Work                                       |     |

| 7.1. Conclusions                                                             |     |

| 7.2. Summary of Contributions of this thesis                                 |     |

| 7.3. Future Work                                                             |     |

| References                                                                   | 93  |

| Glossary                                                                     | 100 |

### List of Tables

| Table 4.1: Arrangement of ANNs based on their functional characteristics   |    |

|----------------------------------------------------------------------------|----|

| Table 5.1: Geometry PCB Dimension                                          |    |

| Table 5.2: Thermal properties for the PCB                                  |    |

| Table 5.3: Mesh limits of detailed model                                   |    |

| Table 5.4: Comparison of SNR and PSNR values of different existing filters |    |

| Table 5.5: Distribution of conditions for entire samples                   |    |

| Table 5.6: Samples for the comparison results of MLP Training Functions    |    |

| Table 5.7: Samples for testing and output results of the Model             |    |

| Table 5.8: Summarized setting parameters for the MLP network               |    |

| Table 5.9: ANFIS parameters setting                                        |    |

| Table 5.10: Samples for testing and output results of the ANFIS Model.     |    |

| Table 5.11: SVM parameters setting                                         |    |

| Table 5.12. a: Comparative training results                                |    |

| Table 5.12.b: Comparative testing results                                  |    |

| Table 6.1: IR camera parameters set up                                     |    |

| Table 6.2. a: Comparison of training results                               |    |

| Table 6.2. b: Comparison of testing results                                | 88 |

### List of Figures

| Figure 2.1: a) Resistive Bridge Defect, b) Interconnect Defect                    |    |

|-----------------------------------------------------------------------------------|----|

| Figure 3.1: Infrared Thermography equipment                                       |    |

| Figure 3.2: Radiation received by the infrared camera                             |    |

| Figure 4.1: Architecture of a Multi-Layer Feed-Forward Network                    |    |

| Figure 4.2: Schematic diagram of an SVM classification                            |    |

| Figure 4.3: A basic ANFIS model with two input data and two member functions      |    |

| Figure 5.1: The main progress steps of the proposed algorithm                     |    |

| Figure 5.2: 3D layout of the PCB                                                  |    |

| Figure 5.3: Top and side views of the PCB                                         | 35 |

| Figure 5.4: Three dimensional views of the meshed PCB geometry                    | 38 |

| Figure 5.5: The simulation results for temperature distribution on the proposal   | 40 |

| PCB's surface                                                                     |    |

| Figure 5.6: Temperature variations vs Power dissipation                           |    |

| Figure 5.7: Comparative results of image denoising methods                        |    |

| Figure 5.8: Comparison of segmentation results for different methods              |    |

| Figure 5.9: Image cropping approach                                               |    |

| Figure 5.10: Image histogram representation for both color and gray thermal image |    |

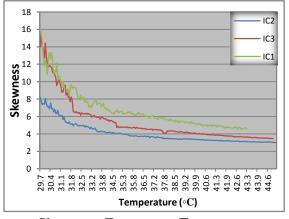

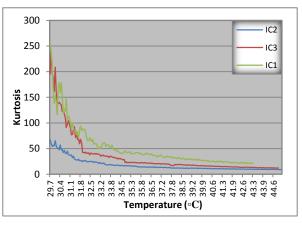

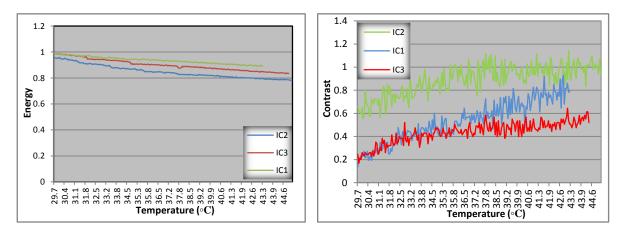

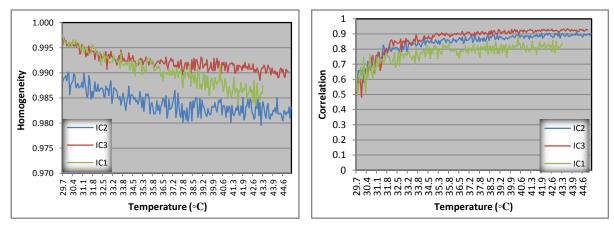

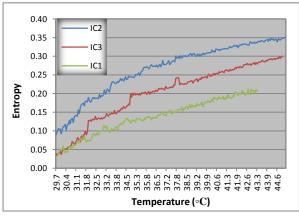

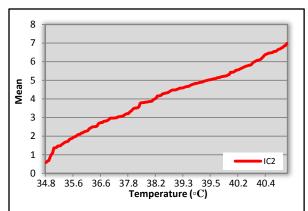

| Figure 5.11: Features changing plots versus temperature                           |    |

| Figure 5.12: Flow diagram of PCA algorithm                                        |    |

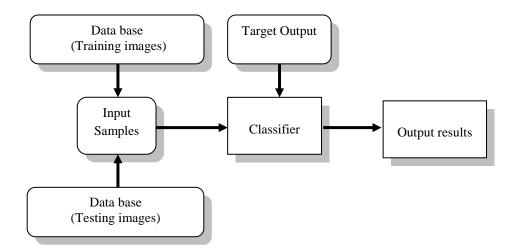

| Figure 5.13: Block diagram of the General Intelligent Classification steps        |    |

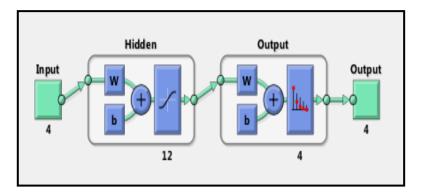

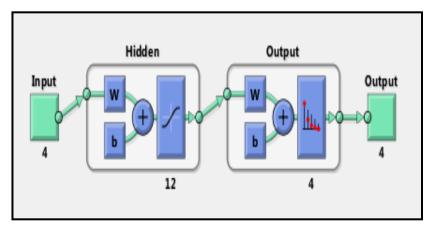

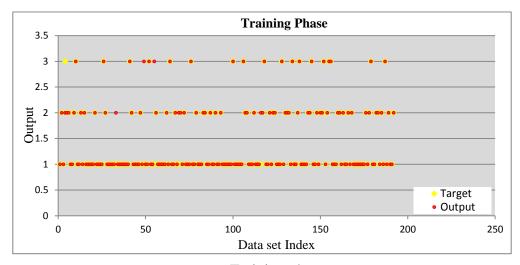

| Figure 5.14: The proposed neural network architecture layout                      |    |

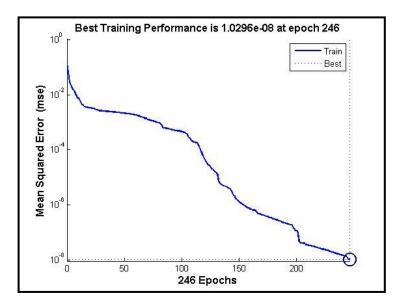

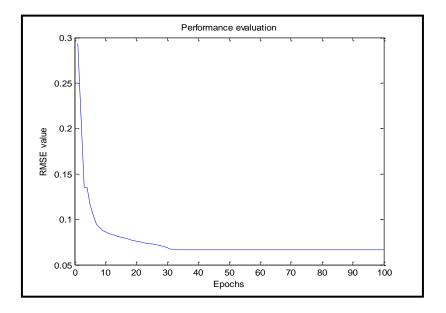

| Figure 5.15: The MLP network performance                                          |    |

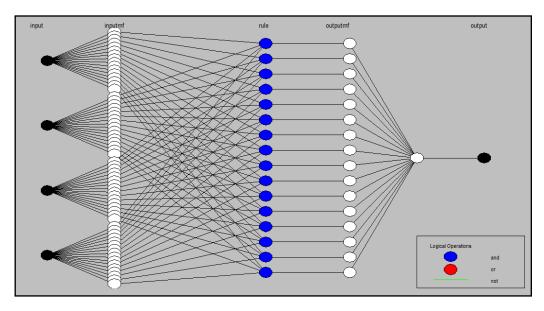

| Figure 5.16: ANFIS model structure                                                |    |

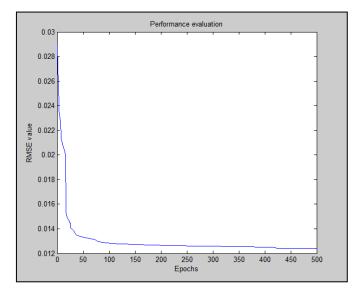

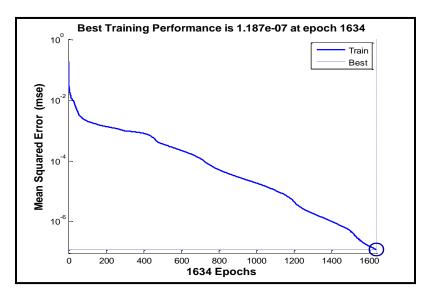

| Figure 5.17: The Performance Evaluation of ANFIS during training phase            |    |

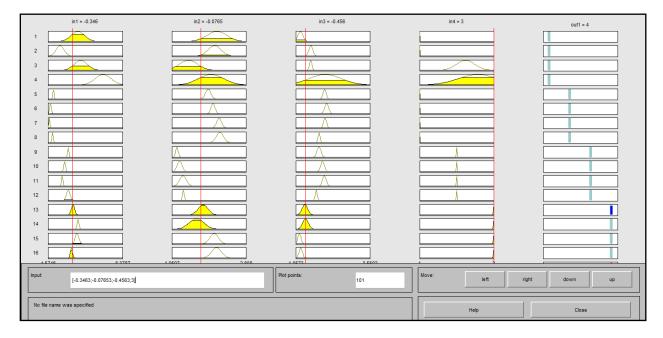

| Figure 5.18: The ANFIS Fuzzy rules of the classify network                        | 67 |

| Figure 5.19: The performance graph of the ANFIS Fault type classification model   |    |

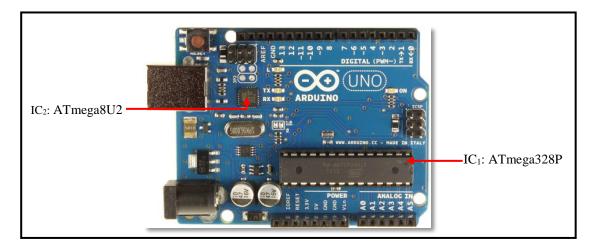

| Figure 6.1: Arduino UNO board                                                     |    |

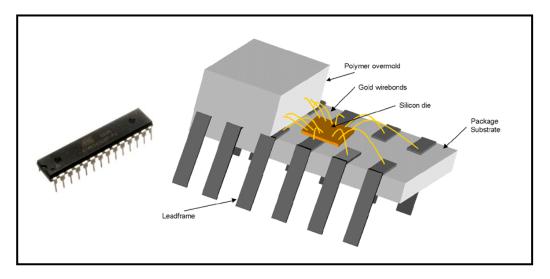

| Figure 6.2: ATmega328P IC configuration                                           |    |

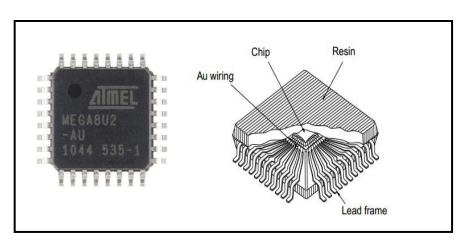

| Figure 6.3: ATmega8U2 IC configuration                                            |    |

| Figure 6.4: FLIR SC4000 camera                                           | 74 |

|--------------------------------------------------------------------------|----|

| Figure 6.5: Real PCB with IR capturing system                            |    |

| Figure 6.6: Thermal profile for UUT                                      | 78 |

| Figure 6.7: Samples of captured IR image for real PCB                    | 78 |

| Figure 6.8: Filtering image results                                      | 79 |

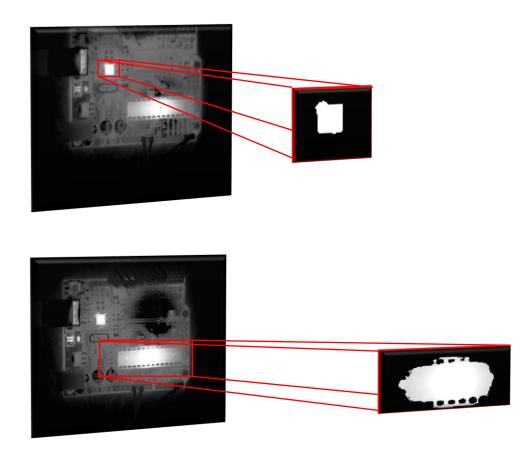

| Figure 6.9: Image segmentation (i.e. Otsu's method) and cropping results | 79 |

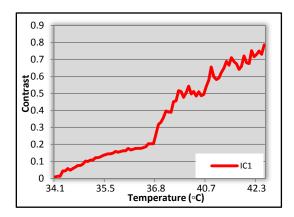

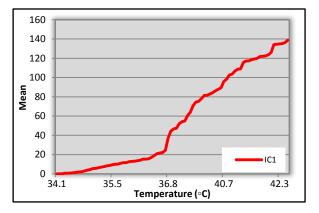

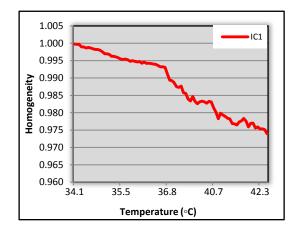

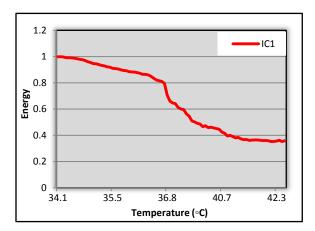

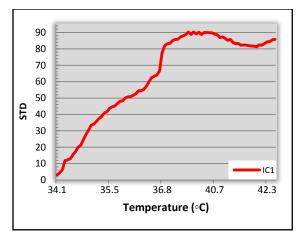

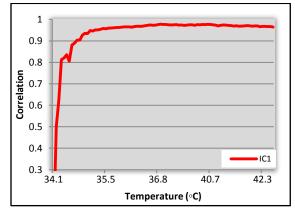

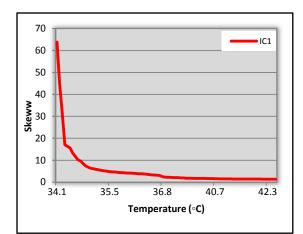

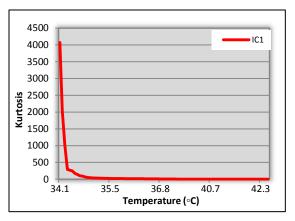

| Figure 6.10.a: Features changing plots versus temperature for IC1        |    |

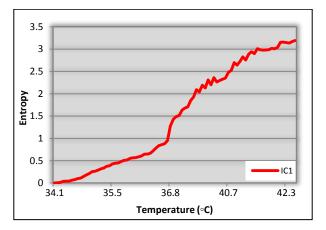

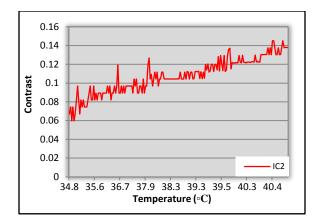

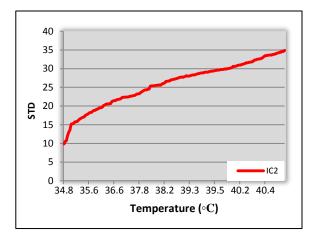

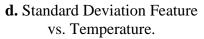

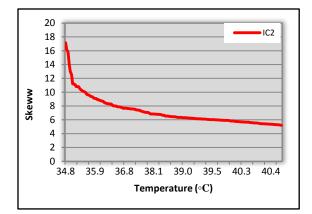

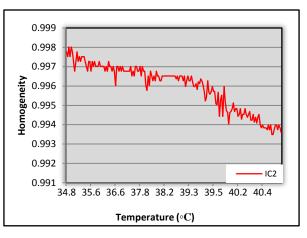

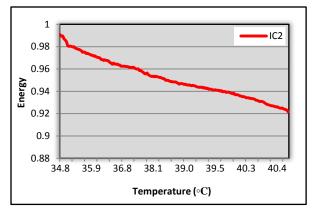

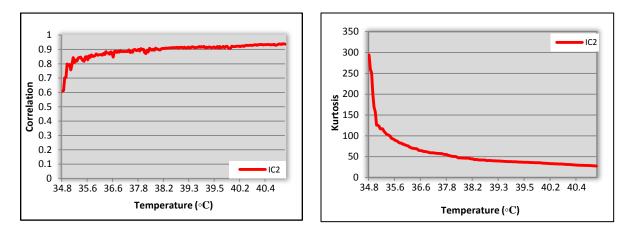

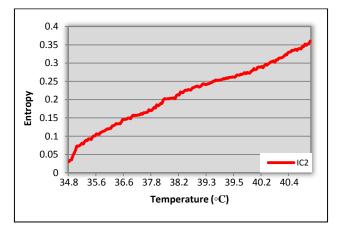

| Figure 6.10.b: Features changing plots versus temperature for IC2        |    |

| Figure 6.11: Proposed neural network architecture layout                 | 84 |

| Figure 6.12: Proposed neural network architecture layout                 |    |

| Figure 6.13: ANFIS structure                                             | 85 |

| Figure 6.14: RMSE response of ANFIS                                      | 85 |

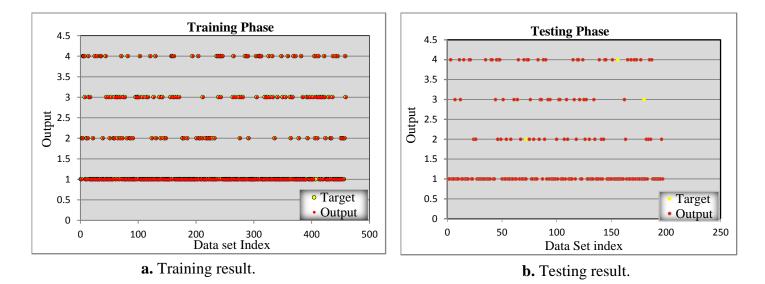

| Figure 6.15: Graphical classification output based on ANFIS              | 86 |

## **Chapter 1: Introduction**

#### **1.1. Introduction**

Technology scaling has enabled greater integration because of reduced transistor dimensions. The significant increase in complexity of Integrated Circuits (ICs), as the core of modern digital circuits, has substantially improved the semiconductor integration level production by generation. With technology scaling, the very large scale integrated (VLSI) circuits density has grown exponentially. This leads to increase the manufacturing defects in circuits.

This rapid technology scaling has resulted several reliability problems such as instance manufacturing defects, power dissipation limits and parametric variations. These threats can effect correct program execution which is the most significant aspect of any computer system. Therefore, testing of a digital circuit becomes imperative, particularly, in VLSI technologies [1].

In this context, testing techniques for digital circuits have to be improved and augmented to achieve quality levels as circuit density and area continue to grow. Traditional testing methods of digital circuits includes electronic test, visual inspection, signal analyzer and burn-in scheme. These methods are used for diagnosis and eliminate the defects and speed up weak component failures. However, problems with a short circuit, a faulty transistor, or a circuit that creates hotspot will stay invisible [2]. Therefore, the thermal testing methods are useful in the process of designing and testing of complex VLSI circuits.

The thermal testing method is one of the Non-Destructive Testing (NDT) techniques for

testing and showing hot spots on operating ICs, depending on the failure conditions such as shorts, over stressed or faulty components [2]. The primary benefits of NDT are to detect the flaws and defects of materials without changing or destroying their functionality and guarantee the safe operation of the system components. Infrared thermography method is a common thermal testing technique in NDT in which an external stimulus is used to heat the Unit Under Test (UUT) while an Infrared (IR) camera records the temperature. The shifting of the normal thermal dissipation pattern is a sign of fault occurrence. Infrared thermography testing technique is a consecutive approach involving thermal image enhancement, detection, main feature extraction, classification, decision making and determining whether the IC has a fault or not [2, 3].

#### **1.2. Literature Review**

A brief review about the Infrared thermography testing methods for PCB and electronic circuits is presented in the following sections:

**H. Moldovan, M. Marcu, and M. Vladutiu** [2], this work presents a testing method using infrared thermal signatures to detect and locate a fault in PCB. The proposed method is used to classify the ICs into three main categories (e.g. functional fault free, non-functional, faulty and less reliable). In this method, a stimuli vector applies to the PCB controllable inputs, and then a certain thermal response is observed for each IC on the PCB. The classification system uses an artificial neural network to classify the samples extracted from the IR image. The main drawback of this approach is the time and cost of solution achievement to get the thermal signature for every test vector applied to the primary inputs of the PCB.

J. Varghese, T. Singh, and S. Mohan [4], this work presents a method for thermal analysis of the PCB using MATLAB. Depending on loading condition of the PCB, two parameters are used for analysis the thermal image, the highest temperature and area of the highest temperature. Image segmentation algorithms are used based on short changes in the intensity. The histogram threshold approach is used for this study. The program compares each histogram and finds out the image with a maximum number of pixels of white or the worst-case image. But, this study is not recommended for the complex PCBs because the choice of selecting a region of interest should be improved by having been clustering based on segmentation methods.

**C. Wagh, and V. Baru [5],** presents detection of the faulty region on PCB by thermal image processing. In this research, the samples for thermal images of fault and fault free PCBs are experimentally obtained. The statistical analysis tool such as a Principal Component Thermography (PCT) technique is used to process the IR image sequences and increase the contrast of the processed data. Here, to reduce the amount of computations, the SVD technique based on the PCT is used. The euclidian distance is used for fault diagnosis and identification by comparing the features. The proposed method is conditional due to the excessive work of associate calculations.

**J. Jianliang, and Y. Jiang [6],** presents a fault diagnosis for component's location on the PCB. The authors worked on a template matching method to locate one specific circuit component. The main process includes thermal source identification, feature extraction, and thermal pattern recognition. Standard thermal images for PCBs are captured, and databases of the coordinate and characteristic values of the circuit components are built. Then a thermal image of the circuit under the test is matched with the feature template's images of every component pre-stored in the databases. The results show that thermal image drift can be reduced, but with an increase of accuracy, the time takes a higher computational complexity and a longer time.

**S. Huang, C., and K. Cheng** [7], in this study, present the analysis of PCBs for fault diagnosis by vector quantization. The feeding data to Hopfield neural network is used based on the code word. The code word is generated from the IR image. However, the main drawback of this study is that the mean values of the code words are nonlinearly distributed through the all codebooks, especially for small mean values.

Some other approaches have done on the temperature analysis of PCBs with different techniques of thermal imaging. Thermal analysis of PCBs has been done in [8]; in this paper, Finite -Element Model (FEM) via Galerkin approach applies to analyze the temperature behavior of PCBs for different width of copper and different amount of current. In addition, [9], describes another approach for analysis of thermal reliability of components on the PCBs, presented by ANSYS software to improve the reliability of the system. In [10], a qualitative based measurement of thermal anomalies has been done by detecting the feature point and region of interest with using the stable region algorithm and matching with euclidian distance.

#### **1.3.** Thesis Objectives

An intelligent testing technique should be able to detect ICs fault, extract features from the IR images, estimate the defective conditions, and do correct classification of the faults. For this purpose, the prime aim of this thesis is to detect the defective ICs on the PCBs by thermal image processing. To achieve this goal, the rigid testing method at each processing step is required to improve the efficiency of fault detection during the life time of an IC.

#### 1.4. Thesis Layout

#### Chapter 2

In Chapter 2, we describe a theoretical background of fault diagnosis, explain defects in digital circuits and describe the fault detection and simulation. Furthermore, the testing technique is reviewed in this chapter. Destructive and non-destructive testing methods will be explained, thoroughly, in this chapter.

#### Chapter 3

This chapter will cover the principle of infrared thermography technology and the fundamental of the infrared temperature measurements. Moreover, the classification of thermography technique, its advantages and disadvantages will be presented in this chapter.

#### Chapter 4

Chapters 4 will introduce the intelligent classification methods. A detailed review of the different classification techniques applied for detection and classification of occurred faults is explained in this chapter. Also, we demonstrate the related proposed architectures and the corresponding learning algorithms in this chapter.

#### Chapter 5

This chapter will cover the main contributions of this work. The proposed PCBs modeling steps will be explained in this chapter. This chapter also demonstrate our approach for

IR image processing and classification methods. The simulation results of our work are discussed in this context.

#### Chapter 6

This chapter will focus on the applied and implemented of the proposed method in the earlier chapters. The procedure of performing testing method, experimentally, will discuss in this chapter. Image capturing, processing, and feature extraction from the UUT of Arduino are illustrated. Experimental results are presented at the end.

#### Chapter 7

This chapter will present the conclusion, summary of the contributions of the thesis, and future works. Finally, the reference section will cover all the sources used in this endeavor.

# Chapter 2: Review of the Fault and Testing Techniques for Integrated Circuits

#### 2.1. Introduction

This chapter introduces the preliminaries helpful for the rest of this thesis. The fault, defect, and failure relationship are discussed in section 2.2. Defect types in VLSI circuits are described in section 2.3. The necessaries of fault detection and simulation process are briefly introduced in section 2.4. The PCB testing methods, including destructive and non-destructive test methods and their types, are discussed in section 2.5.

#### 2.2. Fault, Defect, and Failure Relationship

The defect is defined as the difference between the aimed design and the implemented hardware. If any component fails to do its duties, its output will be drastically changed. In this case, a component is said to have a fault. Fault is a representation of a physical defect reflecting a physical condition that causes a circuit to fail to do in a required way. A failure is defined as the inability of the component to perform its design role. A failure in a system is due to the incorrect design and specifications, defects during the manufacturing process, or due to the aging and environmental causes [11].

#### 2.3. VLSI Defect Types

In the past, the main sources of defects in VLSI circuits were opened, shorts and bridges circuits. This is expected to stay in complex circuits where the increasing number of PCB layers leads to a risk of open vias and metal bridges. Nowadays, in silicon technologies, shorts and

open due to the particles and spots, opens in vias and interconnection lines, silicidation problems, etc. are commonly seen. In addition, in this context, new technologies introduce new types of defects which we explain about them. These types of faults occurring in VLSI circuits can be arranged as follow:

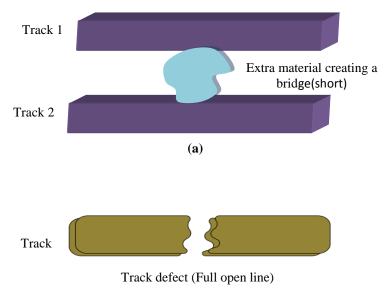

- 1. *Resistive Bridge Defects:* these defects happen when two or more distinct nodes of the circuit get connected due to a fault. Resistive bridge defects are one of the typical commonly of manufacturing defects. Figure 2.1.a, shows a bridge defect between two parallel interconnection lines [12].

- Resistive opens defects: defined as an imperfect resistor connected between two circuit nodes. A stuck-open defect is a special case of a resistive open in which the resistance value is large. These include open contacts, metallization open and open in diffusion [13, 14].

- 3. *Interconnect malfunctions:* a full open in an interconnection happens when the conductive material is fully broken. The main causes for the interconnecting open defects during the manufacturing process can be due to the several factors, such as chemical polishing process, metal filling, spots during the lithography, and lens imperfections. This defect is an interconnected line, shown in figure 2.1.b [12].

- 4. *Delay defect:* these faults cause the combinational delay of a circuit to exceed the clock period. Delay fault includes gate-delay fault, line-delay fault, and path-delay fault.

- 5. *Memory defects:* faults happened in memory sections are normally pattern sensitive, cell coupling, and single stuck-at faults in the address decoder logics.

8

Figure 2.1: a. Resistive Bridge Defect, b. Interconnect Defect.

- 6. *Parametric defects:* They refer to the difference between the actual and expected power or performance criteria for the component. For example, IC may function at a certain voltage, but not over the designed range.

- 7. *Temperature-dependent defects:* They occur when a connection between two circuit nodes has a conductance, high or low enough to be connected at the normal temperatures. This defect is environmentally sensitive, and appears only under certain environmental conditions. However, at high or low temperatures, the conductance decreases so much that the connection is disconnected [15].

- 8. Early-life Failures: Some individual ICs will fail early. These failures can be seen as manufacturing faults that are not manifesting as a defect just after the manufacturing. Defects and mistakes always cause early-life failures: material defects, design mistakes, errors in assembly, etc. This type cannot be detected by the manufacturing test that is performed at once after the fabrication process [15].

#### 2.4. Fault Detection and Simulation

Detection and locating of faults in a digital circuit or PCB, is known as the fault diagnosis. With VLSI technology scaling, fault diagnoses techniques are important to replace or discard the faulty component in the board. In addition, fault simulation is the process of simulating a circuit with a set of test patterns and a set of faults. The response of the circuit compares with the fault-free circuit. If the response does not match, the set of test patterns detects the fault [16].

#### **2.5. Digital PCB Testing Methods**

The aim of testing methods is the effective screening of manufactured circuits to detect the faults. Because of this work deals with thermography-related VLSI test methods, we focus on manufacturing test of PCBs that are produced by VLSI techniques [15]. Based on the variety of models on different levels of abstraction, several destructive and non-destructive test methods have been developed to perform the efficient and highly reliable testing procedures that detect the internal features or surface of the PCB components [17, 18].

#### **2.5.1. Destructive Testing Methods**

There are many conventional destructive testing techniques proposed so far that can check the VLSI circuits with some techniques such as logic, functional, delay and/or current testing such as Level Sensitive Scan Design (LSSD), scan path design, scan logic, random access scan, Built –In –Self Test (BIST) technique, the ad-hoc technique, partitioning technique, adding extra pin's techniques, and signature analysis technique. However, with developing the PCB

production technologies; these destructive testing methods are restricted obviously. At present, increasingly PCBs have a greater density and more electrical nodes. This PCBs need to avoid arranging many test points which make the performance testing method just test part of electrical nodes. The electrical performance testing method needs contact PCBs and probably damaged PCBs. This method needs a fixture for each PCBs, therefore the cost is high. It will be necessary to introduce new and efficient testing techniques to beat these difficulties [17, 19].

#### 2.5.2. Non-destructive Testing Methods

With Non-Destructive Testing (NDT) methods, we can detect, locate, measure, and test surface or internal layers of the components causing no damage or change the integrity of its properties. Thus, non-destructive testing can be done efficiently for the manufactured items.

Today, modern nondestructive tests are used in production fields to ensure product functionality and reliability. Several types of the NDT procedures are being used in the industry such; Acoustic Emission Testing (AET), Thermal or Infrared (IR) Testing, Ultrasonic Testing (UT), and Radiographic Testing (RT). Each of these techniques has its own advantages and disadvantages that mainly relate to the testing system cost, speed, accuracy, and safety. Following sections present the most often used NDT methods such as UT, RT, AE, and IR [20].

1. Ultrasonic Testing method: Ultra-high frequency wave is sent into the component to detect an internal structure of an element under the test. The main advantage of the ultrasonic testing technique is that it can seep into objects of high thicknesses and, therefore, the flaws can be distinguishable. The main disadvantage of it is that it

requires the materials which should be homogenous with uniform surface roughness. It requires a medium to transmit the waves from the transducer into the bulk, additionally, and ultrasound is a point inspection technique that can be timeconsuming for large areas.

- 2. *Radiography Testing:* In radiography, the sample shadow is generated using penetrating radiation rays, such as gamma or x-ray. Images are recorded using x-rays on the film called as radiograms. The recorded radiograms have different contrast levels depending on the flaws, thickness, densities, and the nature of its chemical composition. Radiograms require access from both sides of the sample being tested because it operates based on a transmission mode.

- **3.** *Acoustic Emission Testing;* Acoustic emission is the phenomenon of sound generation in materials when they are under stress. Most materials designed to withstand high-stress levels emit acoustic energy when stressed. Acoustic emission is used to non-intrusively monitor structural integrity and characterize the behavior of materials when they undergo deformation, fracture, or both. Unlike ultrasonic or radiography techniques, acoustic emission does not require external energy for inspection. Acoustic emission techniques have been used to monitor components and systems during processing, detecting and locating leaks, and testing pressurized vessels. One of the main problems with acoustic emission is that it produces large amounts of data that needs to be stored and retrieved for analysis.

4. Infrared Thermography Testing; Thermal testing, or infrared thermography testing, is used to measure the surface temperatures based on the infrared radiation which is emitted from the surface of an object as heat. The infrared radiation can be detected using thermal devices such as the infrared camera. The thermal image captured can be analyzed to retrieve information about the component subsurface thermal body, which is then used to understand its internal configuration. Such information helps in determining the presence or nature of defects in the body. In the recent years with the advancements in the infrared cameras and data processing codes, thermal imaging is a standalone technique for testing of several applications [20].

In the applications of VLSI testing techniques, the infrared thermography testing method has been occupied an important position in the predictive and preventive PCB failure. It has advantages of non-contact, less susceptible to electromagnetic interference, safety, and reliability. This technology can be diagnostic target instant visualization and verify thermal profile. In addition, the infrared thermography can test PCBs through its real running [21, 22].

#### 2.6. Summary

The fundamental of faults, defects, and failure relationship was reviewed in this chapter. The main kinds of faults occurring in VLSI chips were described. The benefit of working with the simulation process for fault detection in the VLSI circuits was defined. The difference between destructive and non-destructive testing methods for PCB was presented. Importance of using infrared thermography for VLSI circuit testing was illustrated. In brief, infrared thermography has various advantages like wide temperature range, usability with smaller areas, easy for understanding over other contactless methods. With progress in algorithms, infrared thermography technique can be used for a wide variety of application right from defect detection and analyzing of multi-layered PCBs to circuit design optimization.

### **Chapter 3: Fundamentals of Thermal Testing**

#### **3.1. Introduction**

Temperature is a physical parameter that has been used as a parametric test observable for ICs in different scenarios, while infrared thermography is a process of temperature measurement that detects the invisible infrared radiation and converts the energy from visible light into an electrical signal. The thermal imaging technique is a fully non-contact technique. Since images of components are difficult to physically access, thermal technique can scan them. Thermal testing methods can be defined as temperature measuring for the detection of structural defects in an IC [17].

This chapter will introduce how an infrared image can be generated and how it should be interpreted. The knowledge of how to interpret an infrared image will be important for the understanding of the rest of this thesis. Various fundamentals to clear the thermography idea will be discussed in this chapter.

#### **3.2. Infrared Thermography Principle**

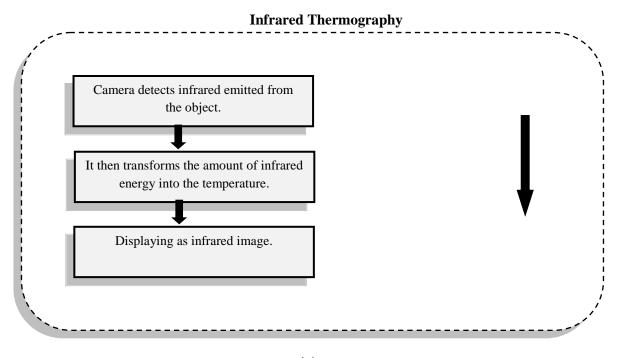

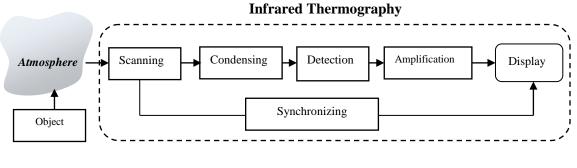

Infrared thermography is defined as an equipment which detects infrared energy emitted from an object, converts it to temperature, and displays the image of the temperature distribution. This equipment comprises the IR camera and the thermography processing unit. The camera includes the IR optics, IR sensor, unit for conversion of electrical into video signals, display, and memory card. Thermography processing unit is processor unit or a Personal Computer (PC) using special software, and they process data from the camera memory card. A main block diagram of measurement by infrared thermography equipment is shown in figure 3.1 [23]. For discussion about the main characteristics of infrared thermography equipment, we can say: it can be captured as a temperature distribution on a surface, and it can be measured from a distance without contacting an object. Besides that, a temperature can be measured in a real time.

**(b)**

Figure 3.1: Infrared Thermography equipment.

#### 3.3. Principles of the Infrared Temperature Measurement

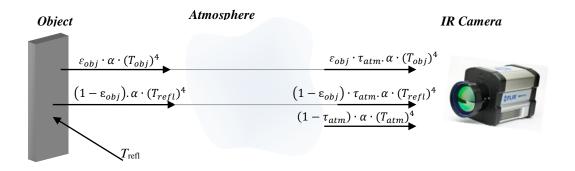

Infrared radiation is a part of the electro-magnetic spectrum, and it is radiated from the surface of the target object. The total power of infrared radiation ( $I_{tot}$ ) consists of three main parts: the emission from the main object ( $I_{obj}$ ), the emission from the surroundings ( $E_{refl}$ ) and the emission from the atmosphere ( $I_{atm}$ ). It can be expressed as the following equation. In addition, the process is shown in Figure 3.2.

$$I_{tot} = I_{obj} + I_{refl} + I_{atm}$$

(3.1)

Figure 3.2: Radiation received by the infrared camera [25].

The equation (3.1) can be rewritten at terms of three collected radiation power terms depending on the Stefan–Boltzmann law for a gray-body radiator as follows [24,25]:

• The emission of the target object  $(I_{obj})$ : It can be expressed as an equation (3.2). Where  $(\varepsilon_{obj})$  is the emittance of the object,  $(\tau_{atm})$  is the transmittance of the atmosphere,  $(\alpha)$  is the Boltzmann constant, and  $(T_{obj})$  is the temperature of a gray body.

$$I_{obj} = \varepsilon_{obj} \cdot \tau_{atm} \cdot \alpha \cdot (T_{obj})^4 \tag{3.2}$$

The reflection emission from surrounding (I<sub>refl</sub>): It can be written by equation (3.3). Where the term (1- ε<sub>obj</sub>) is the reflection of the object and (T<sub>refl</sub>) is the ambient temperature.

$$I_{refl} = \left(1 - \varepsilon_{obj}\right) \cdot \tau_{atm} \cdot \alpha \cdot (T_{refl})^4 \tag{3.3}$$

• The emission of the atmosphere ( $I_{atm}$ ): This term can be calculated using equation (3.4). Where (1 -  $\tau_{atm}$ ) is the emittance of the atmosphere, and ( $T_{atm}$ ) is the temperature of the atmosphere.

$$I_{atm} = (1 - \tau_{atm}) \cdot \alpha \cdot (T_{atm})^4 \tag{3.4}$$

Substituting Equations (3.2)– (3.4) in the main equation (3.1) to get the equation (3.5). The temperature variations of the target can be evaluated from the equation (3.6) [24, 25].

$$I_{tot} = \varepsilon_{obj} \cdot \tau_{atm} \cdot \propto (T_{obj})^4 + (1 - \varepsilon_{obj}) \cdot \tau_{atm} \cdot \propto (T_{refl})^4 + (1 - \tau_{atm}) \cdot \propto (3.5)$$

$$T_{obj} = \sqrt[4]{\frac{I_{tot} - (1 - \varepsilon_{obj}) \cdot \tau_{atm} \cdot \alpha \cdot (T_{refl})^4 + (1 - \tau_{atm}) \cdot \alpha \cdot (T_{atm})^4}{\varepsilon_{obj} \cdot \tau_{atm} \cdot \alpha}}$$

(3.6)

However, to calculate the correct temperature of the observed target from the IR radiation received by the camera, the properties of the target surface, the temperature of the surrounding objects, camera to the object distance, temperature and the humidity of air must be known. All these limits must be set as input data to the camera software [25].

#### 3.4. Classification of Thermography Techniques

According to the measurement methods and data processing, thermal imaging can be classified into two main categories depending on the sample excitation:

- **3.4.1.** *Passive Thermography:* the un-excited infrared radiation (natural emission) that is used to test the sample and detect any defect in its structure. In passive thermography, the temperature difference between a defect and its surroundings is used to distinguish it.

- **3.4.2.** *Active Thermography:* in active thermography an external source is used to excite the test sample thus creating temperature variation between the defective and non-defective areas within the test sample. This is accomplished in various manners as current flow and potential differences in the suspect board, then powered up and an infrared video system is used to generate an image representing the evolution of infrared radiation from the energized components on the board [25].

Active thermography is mostly used in NDT applications, where an exterior, test signal applies to the sample under test to detect any thermal contrast between areas under interest [24].

#### 3.5. Thermography advantages and Limitations

Every experimental method has the advantages and limitations. For thermography, we could say that the pros are [18]:

- Contactless technique: no physical contact, no interaction with a sample under test.

- Can inspect large parts in one test.

- Ability to test different materials and composites.

- Ability to diagnosis components of less accessibility.

- Can be used in real time applications such as during production cycles.

- Ease of numerical thermal modeling and easy to set up, use and keep on a production line.

The limitations of thermography are arranged:

- Depending on the heating source, duration of heating and location of samples.

- The capture duration must be studied depending on the material being tested.

- The performance of the infrared camera used has a major impact on the capture quality.

- Surroundings of the test sample can effect on the image capture.

- Need for a sample to heat uniformly.

#### 3.6. Summary

In this chapter, definition and principles of the infrared temperature measurement have been explained in details. Main steps of the temperature measuring by the IR camera with their mathematical relations have been provided, and then the classification of thermography techniques has been discussed. Differences between passive thermography and active thermography have been introduced. Finally, thermography advantages and limitations have been introduced.

# Chapter 4: Introduction to Intelligent Classification Models

#### 4.1. Introduction

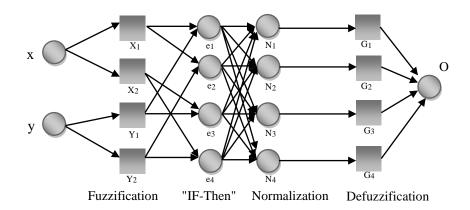

Classification process is used to train a classifier from a set of labeled data called training data set and to classify test set into one of the classes [26]. In this chapter, we review three main models based on intelligent classification techniques; MLP, SVM, and ANFIS. We describe their structures as well as the corresponding learning algorithms. This chapter will provide the readers with essential background information on intelligent classification techniques. We will apply the above three models in the classifying and detection the faults for the ICs, which will be discussed in the next chapters.

#### 4.2. Artificial Neural Networks

We consider a fault classification process using Artificial Neural Network (ANN). In this case, ANN has a remarkable ability to learn and get useful results from complicated and confused data that can be used to extract features. This characteristic of ANN gives an advantage over the conventional classification methods [27]. Neural networks have been used in connection with many different applications. In classification, typically a network will be asked to classify an input pattern as belonging to one of several different possible classes.

There are many different types of ANNs, each with its own advantages and limitations depending on the application. Selection and implementation of the network topology should be more desirable with selecting the smallest number of neuron nodes with an appropriate learning

algorithm. The purpose of learning algorithm is to minimize NNs structure by clipping unnecessary neurons. The main advantages of that can be reduced the cost of runtime and physical implementation. Table 4.1 briefs the main ANN structures used for typical applications such as classification purposes, image processing, pattern recognition, associative memory, optimization, function approximation, modeling, and control tasks [28].

| Application            | ANN Structure                      |

|------------------------|------------------------------------|

|                        |                                    |

| Classification         | MLP, Kohonen, RBF, ART, PNN        |

| Pattern Recognition    | MLP, Hopfield, Kohonen, PNN        |

| Associative Memory     | Hopfield, recurrent MLP, Kohonen   |

| Optimization           | Hopfield, ART                      |

| Function Approximation | MLFFN, CMAC, RBF                   |

| Modeling and Control   | MLP, recurrent MLP, CMAC, FLN, FPN |

| Image Processing       | CNN, Hopfield                      |

Table 4.1: Arrangement of ANNs based on their applications.

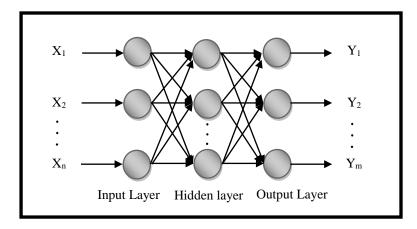

In this work, the network of choice for classification is a MLP with a back propagation learning algorithm for supervised classification (which includes a set of inputs and correct outputs are used to train the NN). A MLP is a feedforward artificial neural network model are characterized by the fact that the information starting from the input is only allowed to pass forward in the network to the output through a specified hidden layer, no feedback is allowed. The MLPs are popular due to their computational simplicity, flexibility, finite parameterization, stability, and smaller size for a problem as compared to other architectures [29].

#### 4.2.1. The Architecture of the MLP

The architecture of this class of network, besides having the input and the output layers, also has one or more intermediary layer or hidden layer [30]. The typical construction of MLP illustrated in figure 4.1. The general design considerations for a neural network includes determining the number of input and output nodes to be used, the number of hidden layers in the network and the number of hidden nodes used in each hidden layer. Typically, the number of state variables represents the number of input neurons, while the general classes of the state of the system decide the number of output neurons. To determine the number of hidden layer nodes, varying numbers of hidden layer are applied for obtaining satisfied results, initially; beginning with a small number of hidden nodes and gradually increasing this number with learning complexity occurs [28].

Figure 4.1: Architecture of a Multi-Layer Feed-Forward Network.

#### 4.2.2. The Training of the MLP

The objective of training an MLP is to produce the desired output (i.e. the target output) when a set of input is applied to the MLP. The proceeding of a neural network starts from the system activated by the input layer where the input data are weighted, and then neurons in the hidden layer perform a user chosen computation method and continue to activate all neurons to the end of this layer. Finally, the output layer determines which characteristics should be read [31, 32].

The MLPs are learned using various algorithms like Back Propagation (BP). Because of the BP network algorithm is simple, a small amount of calculation and parallel advantages. It's currently one of the most used and most mature neural network training algorithms. According to statistics, results, between 80%-90%, researchers are using the BP neural network model [22, 32]. But the limitations of this algorithm are that the traditional BP neural network model in the low learning rate, generalization ability is weak, easy to fall into local minima and the algorithm does not converge. The improved algorithms of traditional back propagation neural network conclude gradient descent Bp algorithms, Quasi-Newton Bp algorithms, and conjugate gradient Bp algorithms [32, 33]. After supervised learning of neurons is over, the trained networks are stored to be used in the algorithm. Whenever an image is taken as input to the algorithm, then simulated by the trained network and from the results; a percentage can be given to which diagnosis should be taken from the data set [22, 31].

#### 4.3. Support Vector Machine

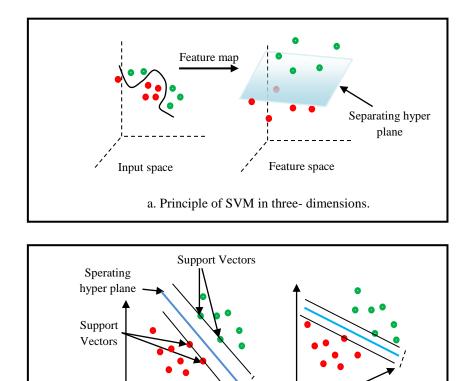

SVM is a group of learning algorithms primarily used for classification tasks on complicated data such as image classifications. In SVM is a single neural network neuron but without cost function or kernel function. This method has a few advantages such as its precision, the possibility of easy implementation and the speed in the training phase and the classification process. That is the reason for its wide use and one of the popular classification algorithms [34].

Generally, an SVM finds the best separating (maximal margin) hyper-plane between the multiple classes of training samples in the feature space, which leads to maximal generalization. It uses statistical learning theory to search for the regularized hypothesis that fits the available data well without over-fitting [34, 35].

SVM uses a supervised learning approach, which means it learns to classify untrained data based on a set of labeled training data. The initial set of training data is typically identified by domain experts and is used to build a model that can be applied to any other data outside the training set [35]. Internally, SVM manipulates data set to represent them as points in a high-dimensional space and then finds a hyper-plane (also called "the model") that optimally separates the two categories or more. As the example in figure 4.2.a, the data set is represented as points in three-dimensional space and the SVM algorithm finds the linear separator that divides the plot into two parts corresponding to two different classes.

On the other hand, it is said that one separator is better than another if it generalizes better, i.e. shows better performance on dataset outside of the training set. It turns out that the generalization quality of the plane is related to the distance between the plane and the data points that lay on the boundary of the two data classes. These data points are called "support vectors", and the SVM algorithm determines the plane that is as far from all support vectors as possible. In other words, SVM finds the separator with a maximum margin and is often called a "maximum margin classifier" as shown in figure 4.2.b [35].

Figure 4.2: Schematic diagram of a SVM classification.

#### 4.4. Adaptive Neuron-Fuzzy Inference System

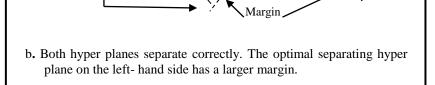

Adaptive Neuron-Fuzzy Inference System (ANFIS) is based on fuzzy logic modeling and uses the artificial neural network as the learning algorithm. Therefore, ANFIS is combined neural networks and fuzzy logic into a hybrid system, so that both can overcome their individual drawbacks as well as a benefit from each other's advantages [37]. The ANFIS has been proven as a classifier with high classification accuracy and fast turning speed for data clustering. ANFIS uses a hybrid algorithm that consists of a combination between BP and least-square estimation techniques. The techniques are implemented in an ANN as a learning algorithm that gives very fast convergence and more accurate in ANFIS target [36]. From the topology point of view as shown in figure 4.3, and the basic flow diagram of computations in ANFIS is illustrated in [38]. The ANFIS consists of five layers. The role of each layer is briefly presented as follows:

Figure 4.3: A basic ANFIS model with two inputs data and two member functions.

• In layer 1 (Fuzzification stage): the fuzzification algorithm is used to calculate the magnitude of the membership degree using the member function curve. The curve is performed by using the following equations.

$$x_{i}(x) = \frac{1}{1 + \left(\frac{x - c_{i}}{a_{i}}\right)^{2b_{i}}}$$

(4.1)

$$y_{i}(y) = \frac{1}{1 + \left(\frac{y - c_{i}}{a_{i}}\right)^{2b_{i}}}$$

(4.2)

Where,  $x_i(x)$  and  $y_i(y)$  are fuzzied values for each input data (x,y), where as  $a_i$ ,  $b_i$  and  $c_i$  are member function parameters.

• In layer 2 ("IF-THEN" stage): this stage receives the labeled data from the fuzzification stage and then evaluate the rules based on equations (4.3) to (4.6).

$$e_1 = X_1(x) \times Y_1(y)$$

(4.3)

$$e_2 = X_1(x) \times Y_2(y)$$

(4.4)

$$e_3 = X_2(x) \times Y_1(y)$$

(4.5)

$$e_4 = X_2(x) \times Y_2(y) \tag{4.6}$$

Where: e1, e2, e3 and e4 are real values for each 'IF-Then' rule.

• *In layer 3 (Normalization stage):* Next, the output signal from the stage of 'IF-THEN' rule will be an input signal to the normalization stage. In this stage, every signal is divided by the total of gaining signal as the following equation.

$$N_i = \frac{e_i}{e_T}$$

$i = 1, 2, 3, 4$  (4.7)

Where:  $e_T = e_1 + e_2 + e_3 + e_4$ .

• In layer 4 (Defuzzification stage); in this stage, the set data receive from pervious stage is defuzzified to give a crisp number. The membership functions of the output signal as following equation.

$$G_i = N_i(p_i x + q_i y + r_i)$$

$i = 1,2,3,4$  (4.8)

*Where pi, qi, and*  $r_i$ *: The Member function parameters.*

• *In layer 5* (Neuron addition stage); The last process in the ANFIS operation is called a neuron addition in which all defuzzification signals, G<sub>i</sub> are added together as shown below:

$$0 = \sum G_i \qquad i = 1, 2, 3, 4 \tag{4.9}$$

Finally, the dataset is classified as training data and testing data in ANFIS's learning process. The total error can be reduced by adjusting the variable membership function and epoch parameters. By selecting, an optimal epoch and several member functions, the performance will be improved accordingly [36].

#### 4.5. Summary

In this chapter, we reviewed three types of the classifier models for detection and the faulty element based on the IR image, which are; MLP, SVM, and ANFIS. These models are used to reduce the amount of training material needed to train a method by selecting the most informative features.

In the first section: we presented the concept of MLP model architecture and explained how to the improved the BP algorithms and to determine the optimal training algorithm and the number of hidden layers for MLP.

In the second section: the main concepts of SVM model have been briefly introduced. We explained the aim of using the SVM supervised method, by transforming the training data to multiple classes such that the new data set became more separable that of the original training data.

In Final section: we considered hybrid intelligent classification systems as an ANFIS. We reviewed an ANFIS model. This model is represented by a neural network with five layers: fuzzification, fuzzy rule, normalization, defuzzification, and neuron stage. In the ANFIS model, the combination between the least-squares estimator with the gradient descent method is used as a hybrid learning method.

# **Chapter 5: Proposed Method for Fault Detection and Classification of the PCBs**

### 5.1. Introduction

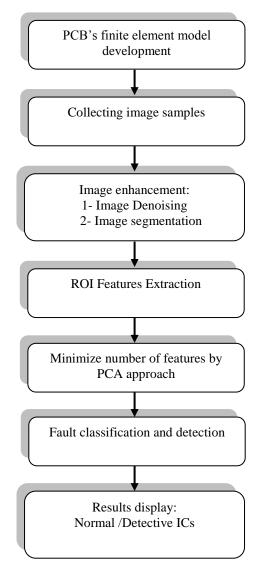

In this chapter, we propose a method for fault detection and classification of the PCBs. Main steps of the proposed algorithm in this chapter includes:

- 1. PCB's finite-element model development: A 3-dimensional PCB finite-element model to estimate the temperature profile of the stacked ICs is developed in this chapter. Procedures like entire thermal simulation, including, geometry generation, applied boundary conditions, solving governing equations, meshing, and post-processing are performed using finite-element method. Then the thermal profile of the developed model is verified with a thermal profile of *Atmel standard packages*.

- 2. Collecting image samples.

- 3. Image Enhancement: Proposing an image processing technique for the captured samples includes denoising, segmentation ROI and using the histogram algorithm to extract the image features is used in this chapter.

- ROI feature extraction: this chapter presents two sets of feature extraction from ROI; first order histogram features and GLCM features.

- 5. Minimize number of features: PCA is applied in our work to minimize the feature's extractions into a minimum uncorrelated variation.

- Fault classification and detection: To train the software for classification; MLP, SVM, and ANFIS techniques are used to classify the thermal image of ICs into two classes; normal condition and fault condition.

- 7. We use the capabilities of MATLAB to achieve the above steps.

Figure 5.1 shows an overview of the method undertaken in this work.

Figure 5.1: Main steps of the proposed algorithm.

#### 5.2. Proposed PCB Modeling

For the optimization of the infrared (IR) thermography, performance results are necessary to describe relevant thermo physical processes running on the object under study. In simple cases, it is possible to find an analytical solution of the problem, but in the real 3D complex objects, it is necessary to use the numerical solution of the Fourier's differential equation. One of the suitable methods is based on finite element models, FEMs. FEM is a numerical computation technique commonly used in the engineering design process [39]. The basic concept of this method is to divide the area of solution into smaller parts called finite-elements, connected at nodal points (mesh generation) and solution processes. The solution processes are known boundary conditions along with characteristic differential equations which depend on the physics of each layer [39]. Building a detailed finite-element model of the board-level package is difficult due to the complicated structure involved, such as the layer structure, through-holes, and signal wires. Obtaining the optimal size of the finite element model is necessary to build an equivalent PCB model with equivalent material properties [40].

Because of our work relates to simulate the temperature distribution of the PCB and study how the layouts of chip packages affect the temperature environment, the details of copper wire and other electronic circuits of the system are ignored. Therefore, the simplified model can reduce the time computing as well. systematic, the simulation process is paved with the following essential sections.

33

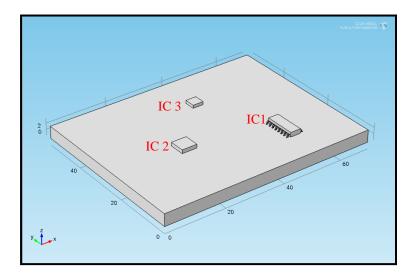

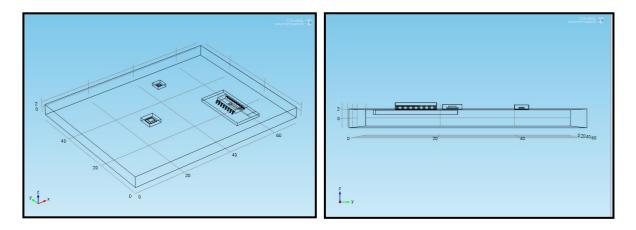

#### 5.2.1. Geometry Model Generation

The geometric model for the whole PCB with three main ICs is created. A PCB size is  $70 \times 55 \text{ mm}^2$  with 4 mm thickness. The geometry model and parameter sizes are shown in table 5.1 and figure 5.2[41].

| Component                                        |                              | $\begin{array}{c} \textbf{Dimensions} \\ (\Delta x \times \Delta y \times \Delta z) \text{ mm}^3 \end{array}$ |                   |         |             |

|--------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|---------|-------------|

|                                                  |                              |                                                                                                               | IC1               | IC2     | IC3         |

| Layout 1                                         | РСВ                          | 70×55×4                                                                                                       | -                 | -       | -           |

| Layout 2                                         | Air                          | 70×55×1.7                                                                                                     | -                 | -       | -           |

| Layout 3                                         | Die                          | -                                                                                                             | 2×2×0.1           | 2×2×0.3 | 1×1×0.15    |

| Layout 4                                         | Mold package                 | -                                                                                                             | 10×3.427×1        | 6×6×1   | 2.4×2.4×1   |

| Layout 5                                         | Bond wires and<br>lead frame | -                                                                                                             | (2.358+1.949×16)* | 3×3×0.2 | 1.5×1.5×0.1 |

| *: (Bond wire +lead frame $\times$ No. of pins). |                              |                                                                                                               |                   |         |             |

Table 5.1: Geometry PCB Dimension.

The first IC, IC1, is based on the simplified Plastic Dual Inline Package (PDIP) model. This is a rectangular shape package with two parallel rows of electrical connecting pins coming out of the two sides of the package. The basic geometric shape is imported from COMSOL library [42, 43].

Other ICs packages; IC2 and IC3 simulate a simplified geometry for a Quad Flat No lead (QFN). These systems have the same layout but different dimensions. This package is a surface mounted device and attached directly on the surface of the PCB [41]. In addition, it is assumed that there are no tiny differences in the heat conduction along the leads and pins of the ICs with the main body of the package. The 3D PCB Geometry and layout configuration are shown in figures 5.2 and 5.3.

Figure 5.2: 3D layout for the PCB.

Figure 5.3: Top and side views of the PCB.

# **5.2.2.** Physical Materials and Thermal Parameters

The next analysis process of FEM is defining layer types and material properties in the PCB modeling, depending on the *Atmel corporation* data sheet [39,44,45]. Basically, the 3D PCB model comprises five layers:

- First Physical Layer: Air convection layer applies to the top surface of the PCB.

- Second physical layer: The die element acts the silicon IC layer.

- Third physical layer: Bond wires and lead frame layer, with copper material layer.

- Fourth physical layer: Mold covers contact's material, bounding wires and dies element.

- **Fifth physical layer**: FR4 material (i.e. fiberglass in an epoxy resin) applies to make the PCB board.

| Layer<br>number | Definition                   | Thermal<br>Conductivity<br>(W/m.K) | Thermal<br>Capacity<br>(kJ/kg×K) |

|-----------------|------------------------------|------------------------------------|----------------------------------|

| 1               | Air                          | 0.03                               | 1                                |

| 2               | PCB (FR4)                    | 0.3                                | 1369                             |

| 3               | Die (Silicon)                | 163                                | 703                              |

| 4               | Bond wires and lead<br>frame | 400                                | 385                              |

| 5               | Mold                         | 0.163                              | 900                              |

Table 5.2: Thermal properties for the PCB.

The basic method to move heat away from the source can be explained using the following heat transfer equation:

$$Q = \nabla(-k\nabla T) = h \times (T_a - T_b)$$

(5.1)

where

Q: heat source  $(W/m^2)$ .

T<sub>a</sub> and T<sub>b</sub>: temperatures of PCB surface and the ambient temperature (°C).

k: thermal conductivity (W/m. K).

*h*: heat transfer coefficient (W/m<sup>2</sup>.K),  $h = (\frac{1}{R_{th} \times A})$ , where  $R_{th}$ ; is thermal resistance(°C/W), and *A*; is surface area of the package (m<sup>2</sup>).

The main properties of the layer materials listed in table 5.2, while the boundary conditions are:

- 1. The energy equilibrium through the upper side of the body is described by the equation (5.1).

- 2. Heat energy is exchanged between PCB and surroundings only through the upper side of the PCB.

- 3. The external air temperature is equal to  $T_b$ .

- 4. Assume air is covered the bottom space of IC1 between mold and PCB surface.

- 5. For the layers of ICs, heat flux is according to equation (5.1). The power dissipation of ICs groups is considered as a heat source with ambient temperature.

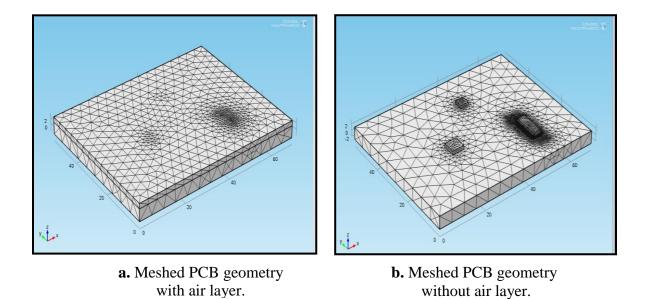

#### 5.2.3. Mesh Generation

Once the geometry is generated, it should be meshed into finite elements. To get a solution, FEM first discretizes the body being analyzed in a process meshing. This refers to dividing the known domain into many finite elements with points, or nodes, at each of its vertices. In each node, the physical equilibrium equation is defined and on the object's boundary, the boundary conditions are defined. In this way, the physical problem described by the partial differential equation is broken down into a linear system of equations [39]. The complex geometries always need more elements to represent than simple ones, and so, take a longer time to solve. It means the minimum number of elements is desirable by which an acceptable accuracy is achievable [39,41,44]. The final 3D revision of the meshed geometry of the proposed PCB can be seen in figure 5.4. This model has approximately 129599 tetrahedral and 25177 triangular elements. In addition, the meshing limits used in the PCB are listed in table 5.3.

Figure 5.4: Three dimension views of the meshed PCB geometry.

| Number of elements             | 129599                  |  |

|--------------------------------|-------------------------|--|

| Number of boundary elements    | 25177                   |  |

| Number of edge elements        | 1877                    |  |

| Number of Tetrahedral elements | 129599                  |  |

| Number of triangular elements  | 25177                   |  |

| Meshing volume                 | 21940.0 mm <sup>3</sup> |  |

Table 5.3: Mesh limits of detailed model.

# 5.2.4. Simulation Results and Verification

The performance of the simulation model is evaluated and verified by comparing its thermal performance to thermal profile of Atmel standard packages.

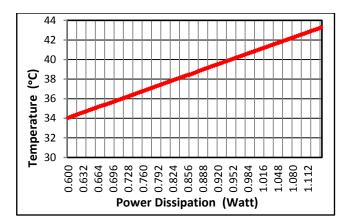

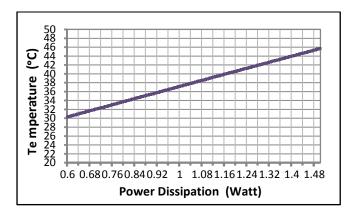

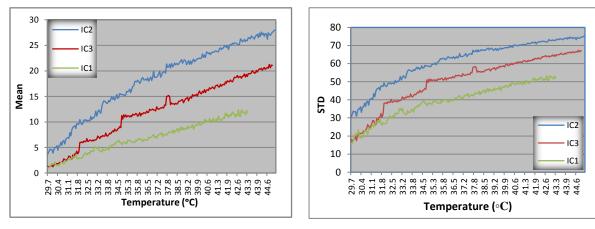

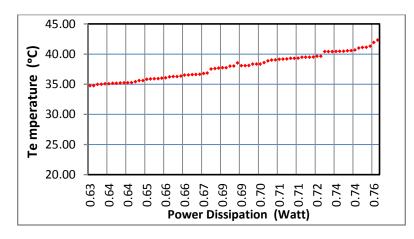

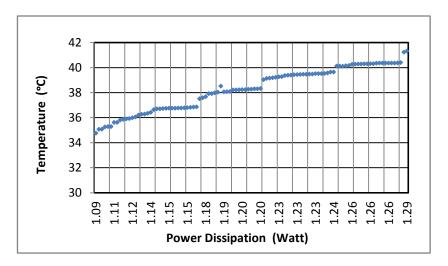

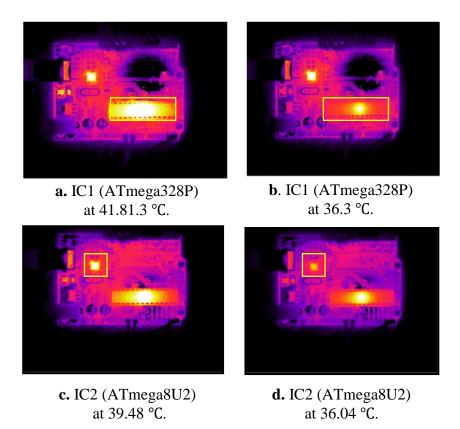

Thermal performance of a package is measured by the ability to dissipate the power required by the ICs into its surroundings. The electric power drawn by the PCB generates heat on the surface of the IC. This heat is conducted through the die to the surface and transferred to the surrounding air by convection. Each heat transfer step has a corresponding thermal resistance coefficient to the heat flow. Commonly used coefficients are  $R_{th(jA)}$  (junction to ambient air). The thermal performance can be characterized by equation (5.1). Based on Atmel data sheet [46], the average thermal resistance for IC1 (PDIP), and IC2 (QFN) model are 55 and 23 °C/W, respectively. With the same information for physical properties such as thermal conductivities and thermal capacities of the different layers of ICs as given in tables 5.1 and 5.2, the heat transfer coefficient of IC1 and IC2 can be got. Then, the power dissipation  $P_{dissp}$  curve versus temperature changes ( $T_a$ - $T_b$ ) provides thermal behavior for the developed model. Figure 5.5.a, shows the simulation results for power dissipation changed between 0.6W – 1.14W to get temperature range 34.055°C – 43.264°C, respectively, for IC1 model (PDIP).

Figure 5.5.b, shows power dissipation varied between 1W - 2.337W to get temperature range  $29.734^{\circ}C - 43.325^{\circ}C$  for IC2 (QFN) model. For IC3 (QFN) model, assuming the power dissipations swept between 0.6W - 1.5W to obtain the temperatures range between  $30.331^{\circ}C - 43.699^{\circ}C$  as illustrates in figure 5.5.c. Results for power dissipation versus temperature changes agreement with the thermal profile of Atmel packages that will present in experimental results. Consequently, simulation results from the thermal model provided good samples on the total temperature distribution that will use well in the classification approach.

a. Temperature variations vs. power dissipation for IC1 (PDIP) model.

b. Temperature variations vs. power dissipation for IC2 (QFN) model.

c. Temperature variations vs. power dissipation for IC2 (QFN) model.

Figure 5.5: Thermal profile for the developed model.

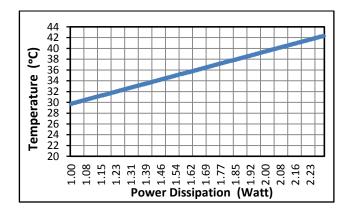

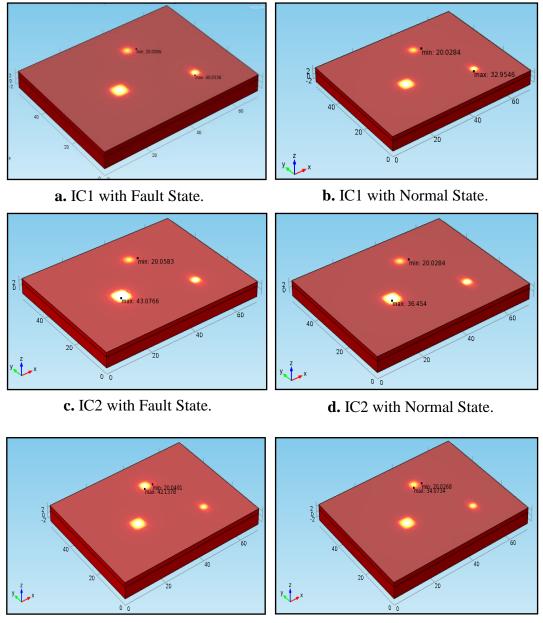

We have captured a series of about 656 thermal images, with a 260×420 image size under (.png) format, from the surface of the PCB. These samples at various thermal loading conditions depend on the thermal characteristics of ICs, as shown in figure 5.6.

e. IC3 with Fault State.

**f.** IC3 with Normal State.

Figure 5.6: The simulation results for temperature distribution on the PCB's surface.

#### **5.3. IR Image Enhancement**

The basic goal of image enhancement is to process the image so we can view and assess the visual information with greater clarity. Image enhancement, therefore, is rather subjective because it depends on the information the user is hoping to extract from the image. The removal of noise and the segmentation of images are main enhancement techniques [47].

#### **5.3.1. Image Denoising**

Processing the acquisition noise should be included to improve the visualization of defects. Therefore, noise filtering would be an important pre-processing technique to improve the contrast and achieve better estimation of the size of the defects [48].

Thermal image has the characteristics of high noise and low contrast. Noise sources include infrared camera system, electronic sensor, turbulence in the environments, etc. Main types of noise include Gaussian noise, sources shot noise, salt and pepper noise, and thermal noise. These noises result in image degradation which directly affect the accuracy of image segmentation and feature extraction. Therefore, denoising process is aimed to find a non-degraded image from the degraded or noisy image [49,50].

Two main types of noise, applied in this work to create different viewing of unclearly for the IR images, are:

- *Gaussian noise:* This noise appears in IR images from imaging equipment such as sensors, electronic circuit's noise, or amplifiers noise because of poor lighting and temperature rising.

- Salt and pepper noise: This noise called spike or impulse noise, because of this noise, dark and bright points or dots appear in the image. The heated faulty elements or dust pieces in the image equipment can cause this noise.

Test images are artificially corrupted by Gaussian noise plus salt and pepper noise with noise power density are 1%, and 0.1%, respectively, as described in [50]. To drop the confused noise, many algorithms have suggested based on linear and nonlinear filters and each algorithm has its advantages and limitations. We investigate on using seven common types such; the median filter, Wiener filter, Gaussian filter, the wavelet threshold method, simple digital filter and, block matching three-dimensional filter (BM3D) [51,52].

Simulation results show that the method based on above filters could work with noise and could preserve the details of the images as shown in Figure 5.7. Comparative performance of using the different filters is measured by two quantitative factors: signal-to-noise ratio (SNR) as in Equation (5.3) [53], and peak signal-to-noise ratio (PSNR) as Equation (5.2) [54]. These two factors use to decide which filter is suitable for using with the IR image as in table 5.4. In this comparison, the median filter is very effective for salt and pepper noise removing. Notably, experimental results presented, insists us to conclude that BM3D with median filters performed well results (as in figure 5.7.h). BM3D is the best choice of removing the Gaussian noise [52]. The Gaussian noise has been largely removed, but at the expense of a slight degradation in image quality.

$$PSNR_{dB} = 10 \log_{10} \left(\frac{255^2}{MSE}\right)$$

(5.2)

where:

MSE: is the mean square error between the original image and a distorted image.

$$SNR_{dB} = 10 \log_{10}(\frac{\mu}{\sigma}) \tag{5.3}$$

where:  $\mu$ : The mean image pixel intensity values and,  $\sigma$ : The standard deviation of the image pixel values.

**a.** The noisy Image (Gaussian + salt and pepper).

c. Using Gaussian filter.

e. Using Wavelet threshold filter (Soft type).

g. Using Wiener filter.

**b.** Using Median filter.

**d.** Using Simple Digital filter.

**f.** Using Wavelet threshold filter (Hard type).

h. Using BM3D with Median filter.

Figure 5.7: Comparison results for the image filtering methods.

| Filter Type                          | Parameter |          |  |

|--------------------------------------|-----------|----------|--|

| Filter Type                          | SNR(dB)   | PSNR(dB) |  |

| Simple Digital filter                | 4.628     | 20.590   |  |

| Gaussian filter                      | -0.392    | 15.569   |  |

| Wiener filter                        | 4.628     | 20.590   |  |

| Wavelet threshold filter (hard type) | 3.630     | 19.592   |  |

| Wavelet threshold filter (Soft type) | 4.477     | 20.439   |  |

| Median filter                        | 9.370     | 25.332   |  |

| BM3D filter                          | 5.868     | 21.830   |  |

| BM3D+Median filter                   | 12.982    | 28.944   |  |

Table 5.4: Comparison of SNR and PSNR values of different existing filters.

#### 5.3.2. Image Segmentation for ROI

The aim of image segmentation is separating a digital image into independent partitions or regions that are more significant to recognize the objects in an image. Segmentation occupies a very important role in image processing because so often the vital first step which must be successfully taken before next tasks such as feature extraction, and classification [55,56].

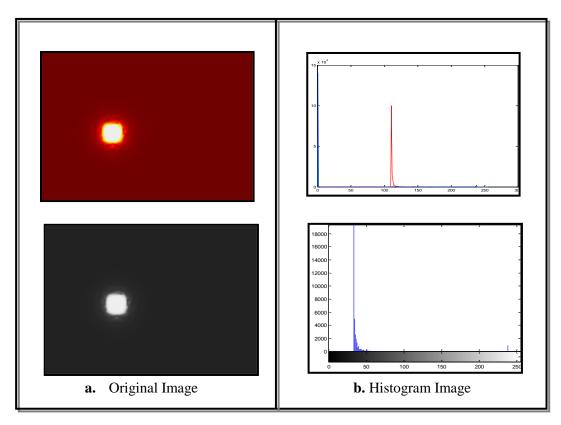

Through this stage, a thermal image of PCB is converted into a grayscale image, which carries the intensity information of the image. In the grayscale image, the faulty region shows more brightness than the normally repeated region in the equipment. The segmentation methods can be divided into threshold segmentation methods, region segmentation methods, edge detection methods and clustering segmentation methods. The result of image segmentation method depends on many factors such as intensity, region continuity, computation complexity, noise resistance, and accuracy [56].

One of the most widely used and convenient method is threshold segmentation technology [4]. This technology is based on a threshold value to turn a grayscale image into a binary image. The key of this technology is to select the threshold value. The reason for using this technology on ICs testing always has temperatures higher than the environment. By using a threshold method, the image of the main object can be separated from its background. However, threshold segmentation technology is useful and a common method for detecting defects in the thermal images [58].

In the threshold process; the heating abnormal in the PCB element's image can be detected by setting a certain threshold filtering [4], if the original image is G(x, y), the threshold image Z(a, b) is defined as follows equation.

$$Z(a,b) = \begin{cases} 1, & G(x,y) > T \\ 0, & G(x,y) < T \end{cases}$$

(5.4)

where: *T* is the threshold temperature.

Various algorithms are widely interested in the threshold thermal image; our work considers four main thresholding methods; iterative thresholding method, Fuzzy-C mean method, Sauvola method, and Otsu thresholding method.

To evaluate the practical performance of the proposed algorithm, the analysis of above segmentation methods and then compare the results of each algorithm is done. The result of the simulation showed that it greatly enhanced. Otsu thresholding works well with acceptable results for automated thresholding of the gray image, as shown in figure 5.8. In addition, Otsu thresholding method is used for the noisy image. The principle of Otsu method requires using the function gray-thresh which chooses the optimal threshold to minimize the interclass variance of the black and white pixels as explain in [57,59,60].

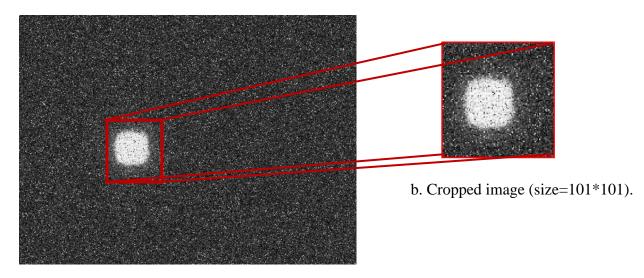

The cropping approach is used at this stage to find the ROI. This process leads to less complexity in the image processing and time because the selected region will minimize. The IC under test region is cropped by using the enclosing rectangle shape to enclose the segmented pattern in a compact window, and convert the selected area into another image. The width of ROI is adjusted accordingly such that all the thermal effect on the chip is preserved. Thus making the segmentation process easier, classification accuracy is higher and production cost, in long run, is reduced [61]. Figure 5.9 illustrates an example, with the using a cropping approach in the original image and the result of the cropped region of interest.

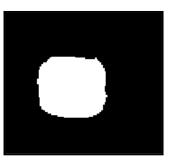

**a.** Noisy Image for IC1 (Salt and pepper + Gaussian) noise.

**c.** Iterative method.