### DESIGN TECHNIQUES FOR PASSIVE WIRELESS MICROSYSTEMS

Xiongliang Lai

Master of Science in Electrical Engineering, Utah, USA, August 2009 Master of Science in Mathematics, Kansas, USA, December 2004 Bachelor of Science in Telecommunication Engineering, Beijing, July, 2000

A dissertation submitted to the department of

Electrical and Computer Engineering

$\mathrm{in}$

the faculty of Engineering and Architectural Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Ryerson University

September 2013

Copyright © 2013 Xiongliang Lai All Rights Reserved

### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

#### ABSTRACT

Xiongliang Lai Doctor of Philosophy Electrical and Computer Engineering Ryerson University, Toronto, Canada, 2013

The unique advantage of harvesting power wirelessly has evolved passive wireless microsystems to a fast-growing high-impact technology. In this dissertation, several new design techniques are proposed for the increasingly stringent requirements of passive wireless microsystems. The absence of on-board batteries imposes ultralow power consumption of passive wireless microsystems. Recent research reveals that multi-voltage systems-on-achip dramatically reduce power consumption such that power-efficient on-chip voltage level shifters are critically needed. This dissertation proposes a novel set of voltage level shifters built upon diode-based clamper-rectifier configurations. The voltage level shifters are passively powered by incoming signals with no static current consumption and are able to shift the incoming signals bidirectionally to suit the different voltage domains. The shifting steps could be continuous and are not bounded by the discrete transistor thresholds and power rails. A second bottleneck of passive wireless microsystems is the wireless power-harvesting efficiency that limits the wireless communication distance and the on-chip circuitry complexity and functionality. This dissertation proposes a transformer-based impedance matching network that greatly improves the power transfer efficiency from the receiving antenna to the on-chip circuit loads. The transformer is also capable of automatically calibrating its input impedance to match to the antenna impedance by a novel low-power varactor current tuning technique. In passive wireless microsystems, data modulation scheme largely determines the power transmission efficiency and data communication speed. Exploiting the constant carrier envelop of FSK modulation, this dissertation proposes a dual-tank architecture for FSK receivers in passive wireless microsystems. The dual receiving tanks significantly improves the power conversion efficiency of on-chip AC-to-DC voltage multipliers by providing high-quality-factor resonating tank voltages at each of the alternating FSK carriers. High data transmission rate is also achieved by exploring the dual tanks in an all-digital and a voltage-level shifting FSK demodulators.

#### ACKNOWLEDGMENTS

The author graciously thanks his supervisor and mentor, Professor Fei Yuan, for his inspiration, technical and personal insight and unwavering support throughout this work. His enthusiasm, vision and experiences have been the greatest source and motivation to make possible the accomplishments herein.

The author also thanks other committee members, Prof. Gul N. Khan, Prof. Vadim Geurkov, Prof. Farrokh Sharifi, and Prof. Richard Horsey of York University for reviewing this dissertation.

I would like to acknowledge the members of Integrated Circuits and Systems Research Group at Ryerson University, Yushi Zhou, Alaa AL-Taee, and Shaul Peker for their helpful discussions, constructive suggestions, and invaluable technical inputs. Special acknowledgments go to former members of the research group, Dr. Dominic DiClemente, for his effort in establishing the wafer measurement facilities, and Tarek Khan for completing Cadence simulation environments.

My Ph.D. program was funded in part by Graduate Fellowships endowed by Ryerson University, the Ministry of Training, Colleges and Universities of Ontario, and the Natural Sciences and Engineering Research Council of Canada (NSERC). I remain grateful for these supports.

Finally, I would like to thank my family for all the love and support they have provided through the years.

# Table of Contents

| Li           | List of Tables xv    |        |                                        |      |  |

|--------------|----------------------|--------|----------------------------------------|------|--|

| Li           | List of Figures xvii |        |                                        |      |  |

| $\mathbf{A}$ | Abbreviations xxii   |        |                                        | xxii |  |

| 1            | Intr                 | oducti | ion                                    | 1    |  |

|              | 1.1                  | Backg  | round                                  | . 2  |  |

|              |                      | 1.1.1  | Architecture                           | . 2  |  |

|              |                      | 1.1.2  | Antenna                                | 4    |  |

|              |                      | 1.1.3  | Matching Network                       | 5    |  |

|              |                      | 1.1.4  | Rectification                          | 6    |  |

|              |                      | 1.1.5  | Modulation Backscatter/Load Modulation | 6    |  |

|              |                      | 1.1.6  | Demodulation                           | . 7  |  |

|              |                      | 1.1.7  | Industry Standard                      | . 8  |  |

|              | 1.2                  | Motiv  | ation and Objectives                   | 9    |  |

|              |                      | 1.2.1  | Voltage Level Shifters                 | 9    |  |

|              |                      | 1.2.2  | Impedance Matching                     | . 11 |  |

|              |                      | 1.2.3  | FSK Demodulator                        | 13   |  |

|              | 1.3                  | Contri | ibutions                               | . 14 |  |

|              |                      | 1.3.1  | Passive Voltage Level Shifters         | . 14 |  |

|          |     | 1.3.2   | High-Gain On-Chip Transformer Impedance Matching   | 15 |

|----------|-----|---------|----------------------------------------------------|----|

|          |     | 1.3.3   | Power-Efficient Dual-Tank FSK Demodulator          | 15 |

|          | 1.4 | Disser  | tation Organization                                | 16 |

|          | 1.5 | Chapt   | er Summary                                         | 16 |

| <b>2</b> | Pas | sive Vo | oltage Level Shifters                              | 17 |

|          | 2.1 | Basic   | Voltage Level Shifters                             | 18 |

|          | 2.2 | Voltag  | e Level Shifters with Current Compensation         | 20 |

|          | 2.3 | Voltag  | e Level Shifters with Variable Voltage Shift       | 25 |

|          |     | 2.3.1   | Cascaded Voltage Level Shifters                    | 25 |

|          |     | 2.3.2   | Superimposed Voltage Level Shifters                | 30 |

|          | 2.4 | Low-L   | eakage Voltage Level Shifters                      | 34 |

|          | 2.5 | Robus   | tness                                              | 37 |

|          |     | 2.5.1   | Process and Temperature Effect                     | 37 |

|          |     | 2.5.2   | Amplitude of Input                                 | 38 |

|          |     | 2.5.3   | Voltage Level Shifters with Native MOS Diodes      | 39 |

|          |     | 2.5.4   | Voltage Level Shifters with Bulk-Driven MOS Diodes | 40 |

|          |     | 2.5.5   | Speed                                              | 41 |

|          |     | 2.5.6   | Disturbances at Input                              | 42 |

|          |     | 2.5.7   | Distortion                                         | 43 |

|          |     | 2.5.8   | Loading Effect                                     | 44 |

|          |     | 2.5.9   | Driving Capability                                 | 45 |

|          |     | 2.5.10  | Sizing Capacitors                                  | 46 |

|          |     | 2.5.11  | Power Consumption                                  | 46 |

|          |     | 2.5.12  | ASK Demodulator                                    | 47 |

|   | 2.6 | Measurement Results                                              | 49  |

|---|-----|------------------------------------------------------------------|-----|

|   | 2.7 | Chapter Summary                                                  | 53  |

| 3 | Rer | note Calibration for Maximum Power Harvest                       | 55  |

|   | 3.1 | Transformer Impedance Tuning                                     | 57  |

|   |     | 3.1.1 Impedance Tuning                                           | 57  |

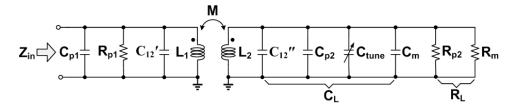

|   |     | 3.1.2 Equivalent Model of Transformer Impedance Matching Network | 61  |

|   |     | 3.1.3 Quality Factor and Voltage Gain                            | 62  |

|   | 3.2 | Transformer Matching Model                                       | 63  |

|   |     | 3.2.1 Impedance and Frequency Tuning                             | 66  |

|   | 3.3 | Current Tuning                                                   | 69  |

|   | 3.4 | Peak Detection and Self Tuning                                   | 72  |

|   | 3.5 | Measurement Results                                              | 74  |

|   | 3.6 | Chapter Summary                                                  | 77  |

| 4 | Dua | al-Tank FSK Demodulator                                          | 81  |

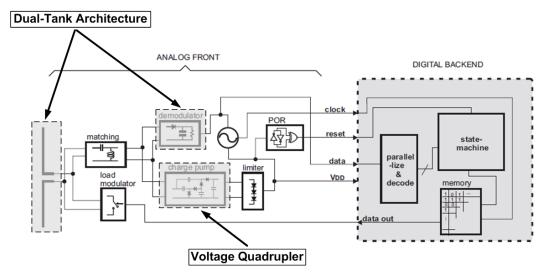

|   | 4.1 | Architecture of Dual-Tank FSK Demodulator                        | 82  |

|   | 4.2 | RF-to-DC Power Conversion and Voltage Multiplication             | 85  |

|   | 4.3 | Digtial FSK Demodulation                                         | 87  |

|   | 4.4 | Numerical Results                                                | 91  |

|   | 4.5 | FSK Demodulation by Voltage Level Shift                          | 92  |

|   | 4.6 | Chapter Summary                                                  | 97  |

| 5 | Cor | clusions and Future Work                                         | 99  |

|   | 5.1 | Conclusions                                                      | 99  |

|   | 5.2 | Future Work                                                      | 100 |

### Bibliography

## List of Tables

| 1.1 | RFID Standards                                                                                                                                                                                                                                                                                                                                                            | 8  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Comparison of the analytical results and simulation results of the voltage of clamping nodes of 3-stage cascaded negative voltage level shifters. Parameters of cascaded negative voltage level shifter 1 : $M_1 = 2$ , $M_2 = M_3 = 1$ , $N_1 = N_2 = N_3 = 1$ . Parameters of cascaded negative voltage level shifter 2 : $M_1 = M_2 = M_3 = 1$ , $N_1 = N_2 = N_3 = 1$ | 29 |

| 2.2 | Comparison of the analytical and simulation results of the voltage of clamping nodes of 3-stage cascaded positive voltage level shifters. Cascaded positive voltage level shifter 1 : $M_1 = 2$ , $M_2 = M_3 = 1$ , $N_1 = N_2 = N_3 = 1$ . Cascaded positive voltage level shifter 2 : $M_1 = M_2 = M_3 = 1$ , $N_1 = N_2 = N_3 = 1$ .                                   | 30 |

| 2.3 | Comparison of the analytical and simulation results of the voltage of clamping nodes of superimposed voltage level shifters with $V_{TH} = 0.5$ V used in calculation.                                                                                                                                                                                                    | 34 |

| 2.4 | Performance comparison of the voltage level shifter (Fig.2.15) and the low-<br>power voltage level shifter (Fig.2.16). $i_{leak1}$ and $i_{leak2}$ are the drain-bulk cur-<br>rents of M1b and M2b, respectively                                                                                                                                                          | 37 |

| 2.5 | Performance comparison of ASK demodulators for passive wireless microsystems.                                                                                                                                                                                                                                                                                             | 48 |

| 2.6 | Comparison of Voltage Level Shifters                                                                                                                                                                                                                                                                                                                                      | 53 |

| 3.1 | Parameters of hexagon step-up transformer.                                                                                                                                                                                                                                                                                                                                | 64 |

| 3.2 | Measured maximum output voltage of transformer network                                                                                                                                                                                                                                                                                                                    | 76 |

| 3.3 | Comparison of Impedance Matching Networks                                                                                                                                                                                                                                                                                                                                 | 79 |

| 4.1 | Comparison of Half-Wave Voltage Doublers.                                                                                                                                                                                                                                                                                                                                 | 92 |

| 4.2 | Comparison of Power Efficiency.                                                                                                                                                                                                                                                                                                                                           | 96 |

| 4.3 | Comparison of Performances of Published FSK Demodulators for Passive Mi- |    |

|-----|--------------------------------------------------------------------------|----|

|     | crosystems and This Work                                                 | 97 |

# List of Figures

| 1.1 | Basic structure of RF power microsystem.                                                                                                                                                           | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Architecture of a typical passive transponder device                                                                                                                                               | 3  |

| 1.3 | Popular antenna geometries for RFIDs and passive transponders. $\ldots$ . $\ldots$                                                                                                                 | 4  |

| 1.4 | (a), (b) and (c): Matching network topologies for RF power harvesting. (d) Transformer power matching circuit proposed in this dissertation.                                                       | 5  |

| 1.5 | Dickson charge-pump and Nakamotos dual half-wave rectifier widely used for RF signal rectification and voltage boost in transponders                                                               | 6  |

| 1.6 | Different matching network topologies for RF power harvesting. Transformer power matching circuit is proposed in this dissertation.                                                                | 7  |

| 2.1 | Contributions of the proposed voltage level shifters to a general passive wire-<br>less microsystem.                                                                                               | 18 |

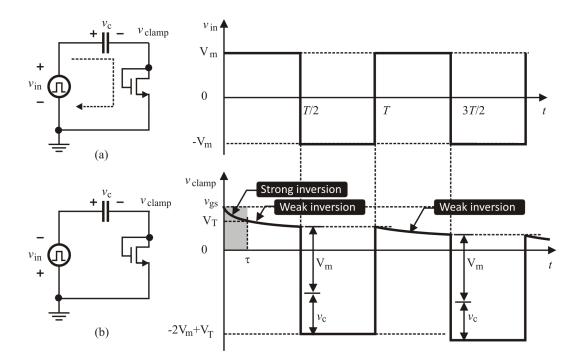

| 2.2 | Positive voltage double with ideal diodes. The voltage of the clamping node $v_{clamp}$ is a up-shifted version of the input.                                                                      | 19 |

| 2.3 | Single-stage negative voltage level shifter                                                                                                                                                        | 20 |

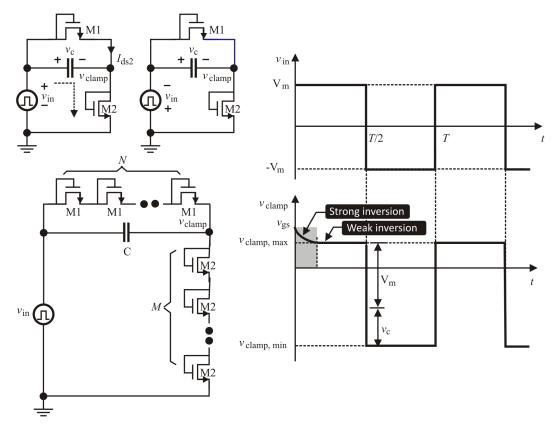

| 2.4 | Negative voltage level shifter with current compensation                                                                                                                                           | 22 |

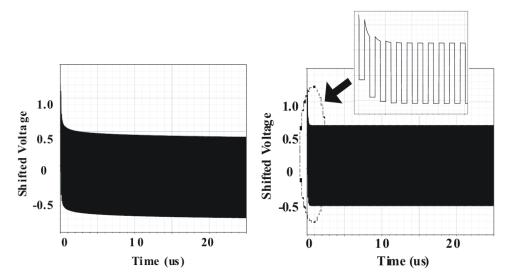

| 2.5 | Simulated voltage of the clamping node of a single-stage negative voltage level shifter without current compensation (Left) and with current compensation (Right).                                 | 24 |

| 2.6 | Simulated voltage of the clamping node of a single-stage negative voltage level shifter. Input is a 2.4 GHz 400 mV sinusoid. Left : Before voltage level shift. Right : After voltage level shift. | 24 |

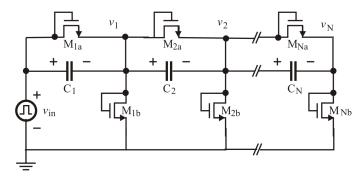

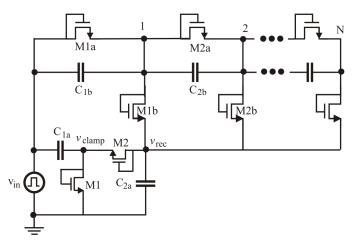

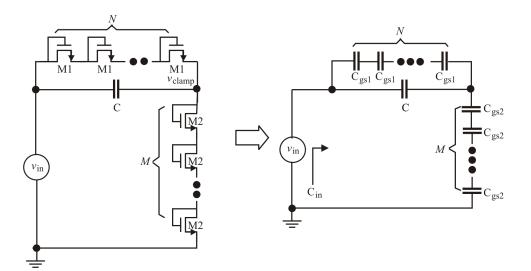

| 2.7 | Cascaded negative voltage level shifters.                                                                                                                                                          | 25 |

| 2.8 | Cascaded negative voltage level shifters with multiple diodes                                                                                                                                      | 28 |

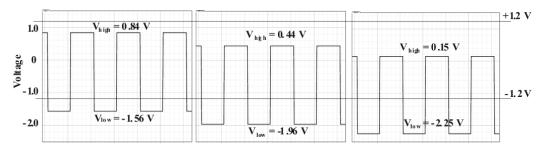

| 2.9  | Simulated voltage of clamping nodes of 3-stage cascaded negative voltage level shifter $(M_1 = 2, M_2 = M_3 = 1, N_1 = N_2 = N_3 = 1)$ .                                                                                                                                                                                                                                                    | 29 |

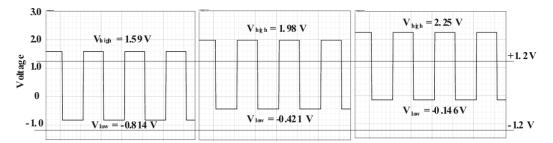

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

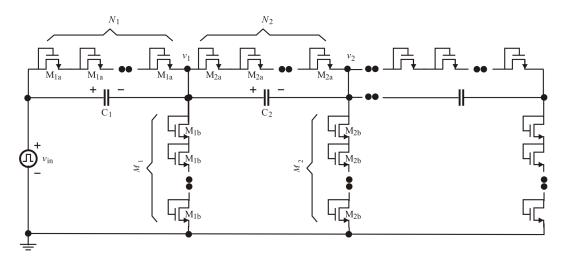

| 2.10 | Simulated voltage of clamping nodes of 3-stage cascaded positive voltage level shifter $(M_1 = 2, M_2 = M_3 = 1, N_1 = N_2 = N_3 = 1)$ .                                                                                                                                                                                                                                                    | 30 |

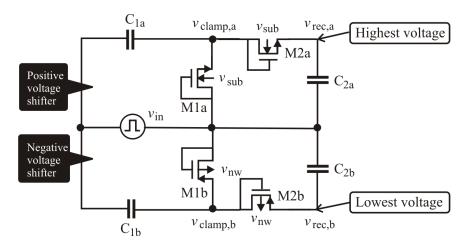

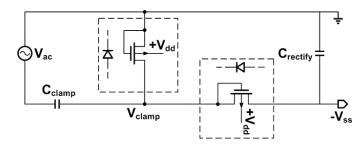

| 2.11 | Superimposed negative voltage level shifters. The voltage multiplication stage<br>is a voltage doubler. The number of current compensating diodes and that<br>of the clamping diodes per stage of the cascaded voltage level shifting level<br>shifter are one                                                                                                                              | 31 |

| 2.12 | Superimposed negative voltage level shifter with an arbitrary number of current compensating diodes and clamping diodes.                                                                                                                                                                                                                                                                    | 32 |

| 2.13 | Simulated voltage of clamping nodes of 3-stage cascaded positive voltage level shifter $(M_1 = 2, M_2 = M_3 = 1, N_1 = 3, N_2 = N_3 = 1)$ .                                                                                                                                                                                                                                                 | 33 |

| 2.14 | Simulated voltage of clamping nodes of 3-stage cascaded negative voltage level shifter $(M_1 = 2, M_2 = M_3 = 1, N_1 = 3, N_2 = N_3 = 1)$ .                                                                                                                                                                                                                                                 | 34 |

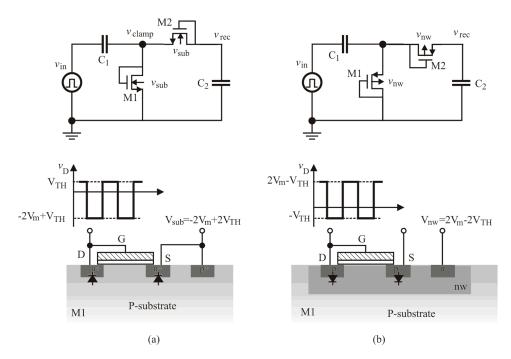

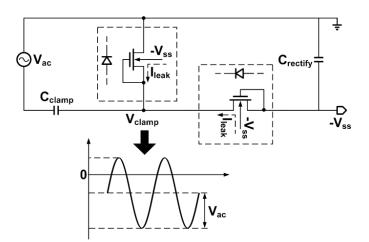

| 2.15 | (a) Negative voltage level shifter. (b) Positive voltage level shifter                                                                                                                                                                                                                                                                                                                      | 35 |

| 2.16 | Low-leakage voltage level shifter.                                                                                                                                                                                                                                                                                                                                                          | 36 |

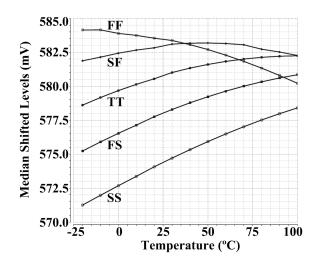

| 2.17 | Effect of process spread and temperature variation on output voltage of Fig.2.3. Legends : FF (fast NMOS/fast PMOS), SF (slow NMOS/fast PMOS), TT (typical NMOS/PMOS), FS (fast NMOS/slow PMOS), and SS (slow NMOS/slow PMOS)                                                                                                                                                               | 37 |

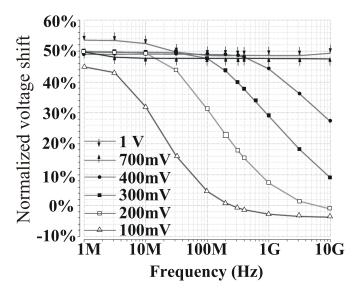

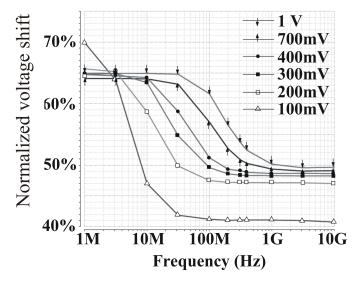

| 2.18 | Effect of the amplitude and frequency of the input of single-stage positive level shifter with regular MOS diodes. Circuit parameters : Clamping diode : W/L=1.6 $\mu$ m / 0.12 $\mu$ m; Compensating diode : W/L=0.32 $\mu$ m / 0.12 $\mu$ m. The clamping diode is made larger than the compensation diode to counteract the reversed leakage current and parasitics at high frequencies. | 39 |

| 2.19 | Effect of the amplitude and frequency of the input of single-stage positive level shifter with native MOS diodes. Circuit parameters : Clamping diode : W/L=15 $\mu$ m /3 $\mu$ m; Compensating diode : W/L=3 $\mu$ m / 3 $\mu$ m                                                                                                                                                           | 40 |

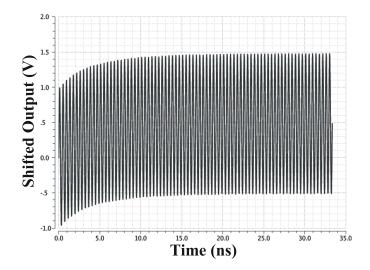

| 2.20 | Propagation delay of voltage level shifter in initial charge-up state                                                                                                                                                                                                                                                                                                                       | 41 |

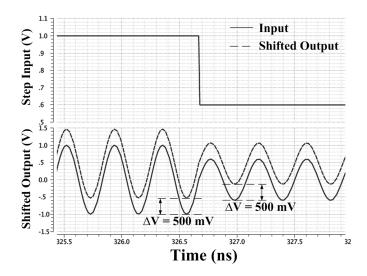

| 2.21 | Propagation delay of voltage level shifter in equilibrium state.                                                                                                                                                                                                                                                                                                                            | 42 |

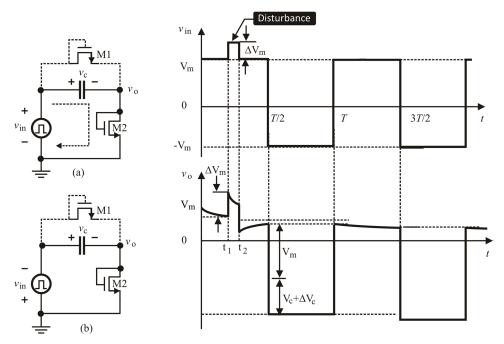

| 2.22 | Response of single-stage negative voltage shifter whose input has transient disturbances.                                                                                                                                                                                                                                                                                                   | 43 |

| 2.23 | Total harmonic distortion of the output of single-stage positive voltage level shifter to a 2.4 GHz sinusoidal input.                                                                                                                                                                                    | 44 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.24 | Capacitive loading effect of negative voltage level shifter                                                                                                                                                                                                                                              | 45 |

| 2.25 | Load capacity of voltage level shifters.                                                                                                                                                                                                                                                                 | 46 |

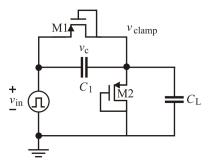

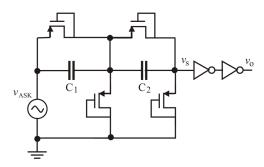

| 2.26 | ASK demodulator utilizing a 2-stage cascaded negative voltage level shifter. Circuit parameters : $C_1$ =500 fF, $C_2$ = 500 fF, and W/L = 1.6 $\mu$ m / 0.12 $\mu$ m.                                                                                                                                   | 47 |

| 2.27 | Response of ASK demodulator utilizing a 2-stage cascaded negative voltage level shifter. Top plot : Baseband data. Second plot : ASK carrier. Third plot : Output voltage of voltage level shifter $v_s$ . Bottom plot : Output of ASK demodulator $v_{clamp}$ .                                         | 48 |

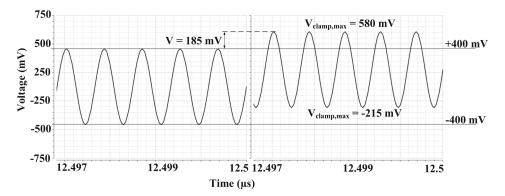

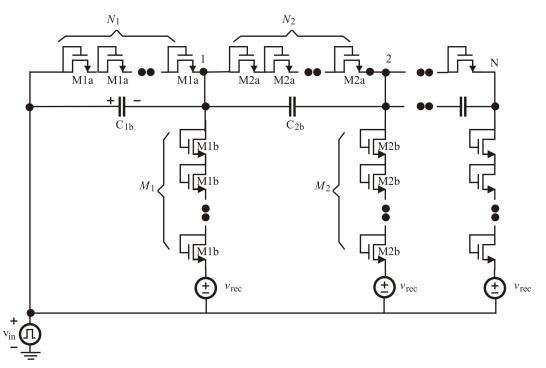

| 2.28 | Single stage positive voltage level shifter with $M_1 = N_1 = 1$ , $W_{1a}/L_{1a} = 30 \ \mu \text{m} / 0.56 \ \mu \text{m}$ , $W_{1b}/L_{1b} = 6 \ \mu \text{m} / 0.56 \ \mu \text{m}$ and $C_{clamp} = 1 \text{ pF.}$                                                                                  | 49 |

| 2.29 | 2-stage cascaded negative voltage level shifter with $M_1 = N_1 = 1$ , $M_2 = N_2 = 1$ , $W_{1a}/L_{1a} = W_{1b}/L_{1b} = 3.2 \ \mu\text{m} \ / \ 0.12 \ \mu\text{m}$ , $W_{2a}/L_{2a} = W_{2b}/L_{2b} = 1.6 \ \mu\text{m} \ / \ 0.12 \ \mu\text{m}$ , and $C_{clamp1} = C_{clamp2} = 1.23 \ \text{pF.}$ | 50 |

| 2.30 | Calculation of voltage level shifts                                                                                                                                                                                                                                                                      | 51 |

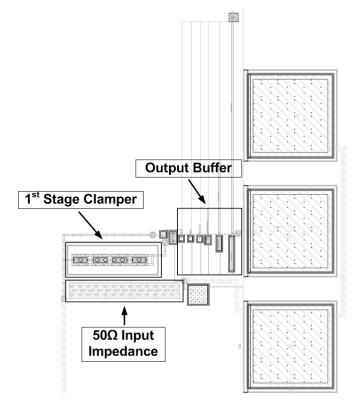

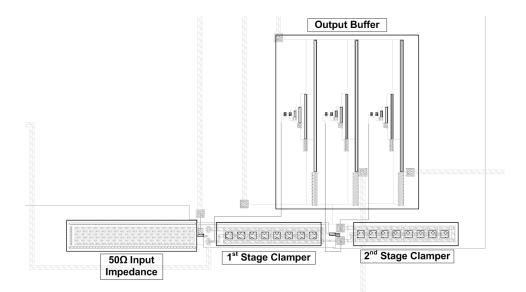

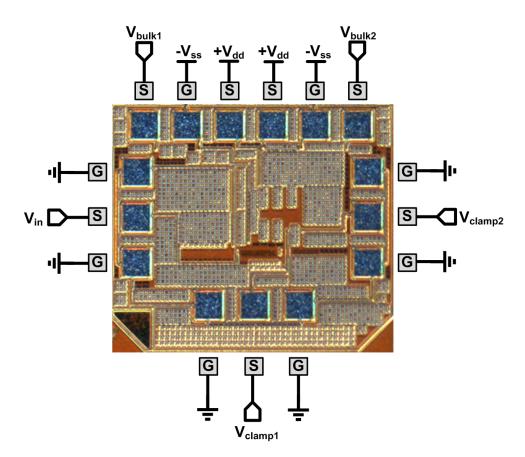

| 2.31 | Micrograph of the cascaded negative voltage level shifter of Fig.2.29                                                                                                                                                                                                                                    | 52 |

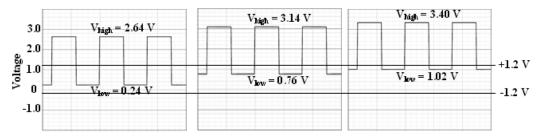

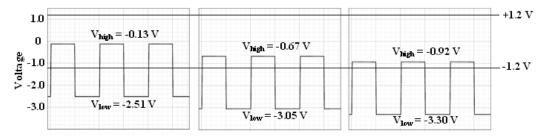

| 2.32 | Measurement results on the $1^{st}$ stage of the cascaded voltage level shifter in Fig.2.29                                                                                                                                                                                                              | 53 |

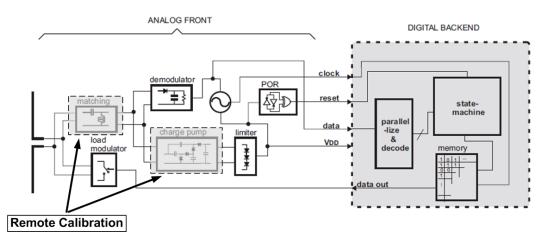

| 3.1  | Contributions of the proposed remote calibration technique in a general pas-<br>sive wireless microsystem.                                                                                                                                                                                               | 56 |

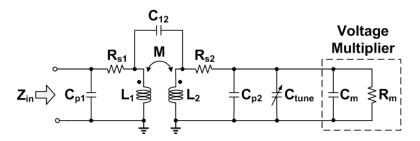

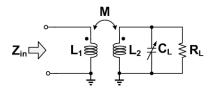

| 3.2  | Proposed tunable step-up transformer impedance matching network                                                                                                                                                                                                                                          | 57 |

| 3.3  | Tunable transformer impedance matching network.                                                                                                                                                                                                                                                          | 58 |

| 3.4  | Simplified tunable transformer impedance matching network                                                                                                                                                                                                                                                | 58 |

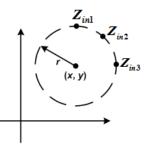

| 3.5  | Impedance matching circle determined by tuning capacitors                                                                                                                                                                                                                                                | 59 |

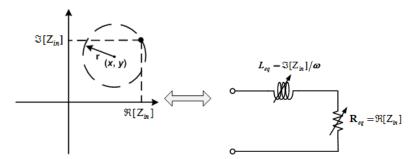

| 3.6  | L-R equivalent circuit of transformer impedance matching network                                                                                                                                                                                                                                         | 61 |

| 3.7  | Variable $L - R$ model for impedance matching                                                                                                                                                                                                                                                            | 62 |

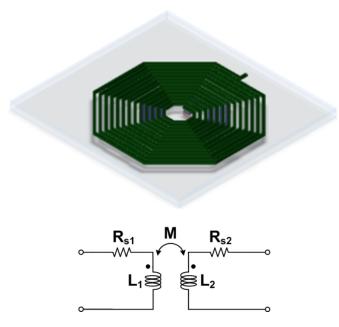

| 3.8  | Top: Layout of step-up transformer. Bottom: equivalent circuit.                                                                                                                                                                                                                                          | 63 |

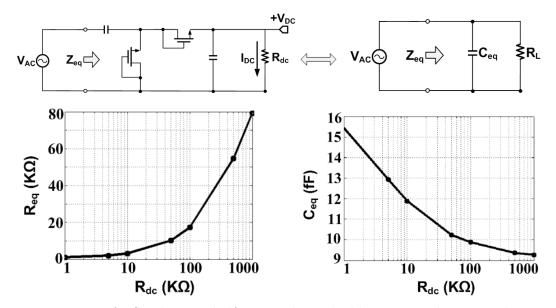

| 3.9  | Top Left: Single-stage half-wave voltage doubler. Top Right: Equivalent circuit. Bottom Left: Simulated input resistance. Bottom Right: Simulated input capacitance                                                                                                                                                                                                                                                                                                                                            | 65 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

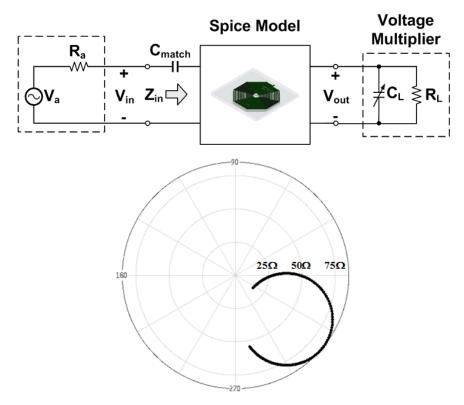

| 3.10 | Top: Series capacitor-transformer network. Bottom: Input impedance. $C_L$ is varied from 10 pF to 200 pF                                                                                                                                                                                                                                                                                                                                                                                                       | 65 |

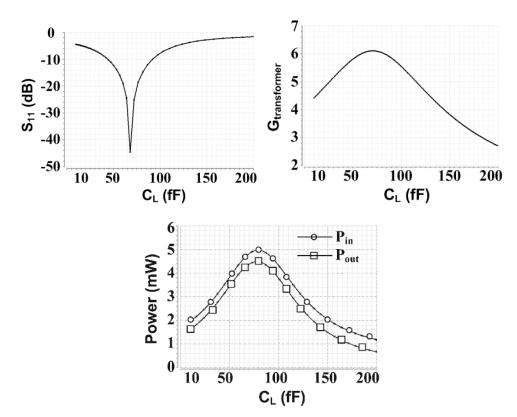

| 3.11 | Top Left: $S_{11}$ at the input port of capacitor-transformer network. Top Right:<br>Voltage gain. Bottom: Power transfer.                                                                                                                                                                                                                                                                                                                                                                                     | 66 |

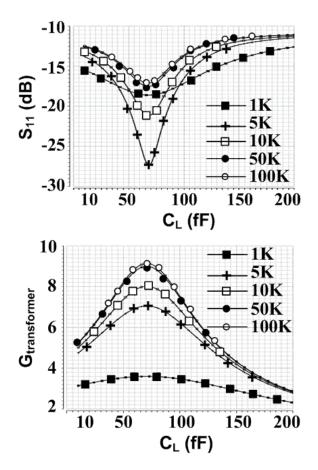

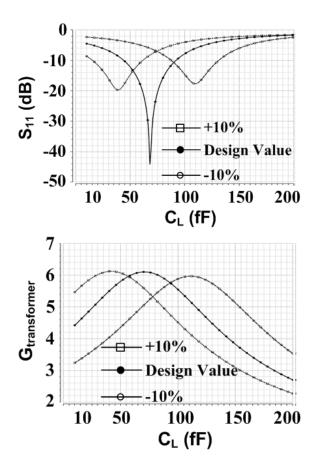

| 3.12 | Loading effect. Top : $s_{11}$ . Bottom : Voltage gain                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68 |

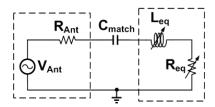

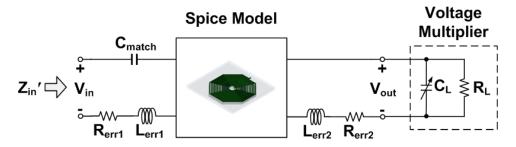

| 3.13 | Test bench.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68 |

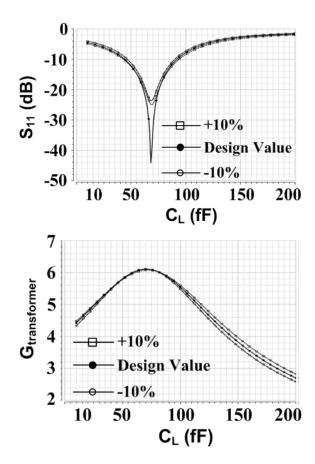

| 3.14 | Effect of primary winding error. Top : $s_{11}$ . Bottom: Voltage gain                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69 |

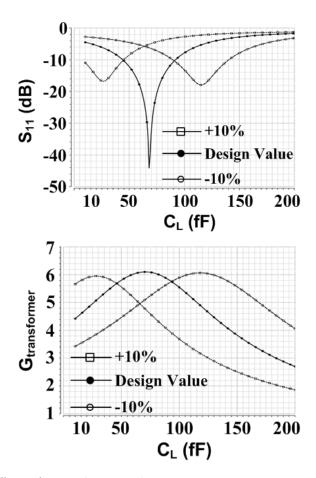

| 3.15 | Effect of secondary winding error. Top : $s_{11}$ . Bottom: Voltage gain                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70 |

| 3.16 | $s_{11}$ and $G_t$ due to frequency error                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71 |

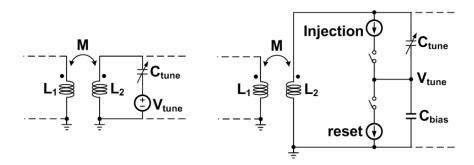

| 3.17 | Voltage-mode varactor tuning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

| 3.18 | Current-mode varactor tuning. The injection pump is composed of eight series-connected PMOS transistors of dimensions $W/L = 0.5 \ \mu m \ / \ 0.4 \ \mu m$ . The reset pump is a NMOS transistor of dimension $W/L = 5 \ \mu m \ / \ 0.4 \ \mu m$ . The capacitance of the varactor of dimension $W/L = 6 \ \mu m \ / \ 2 \ \mu m$ can be varied from 26.4 fF at -0.5 V to 70.7 fF at 3.3 V. The biasing capacitor is 6 pF.                                                                                   | 72 |

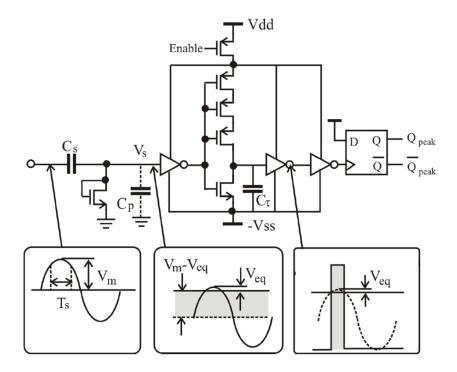

| 3.19 | Peak detection by negative signal level shift.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73 |

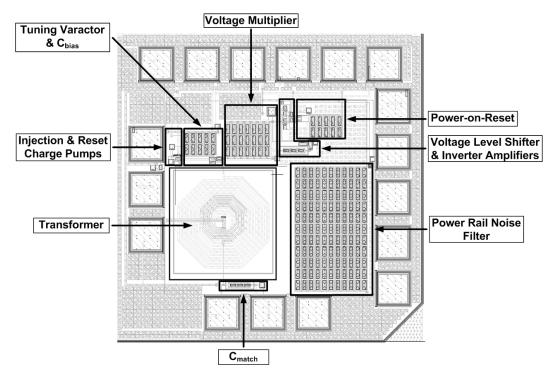

| 3.20 | Layout of transformer matching network                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75 |

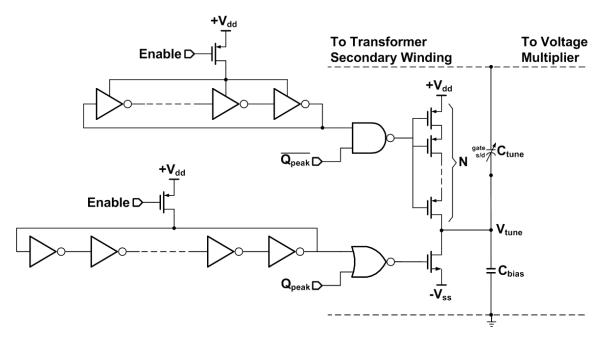

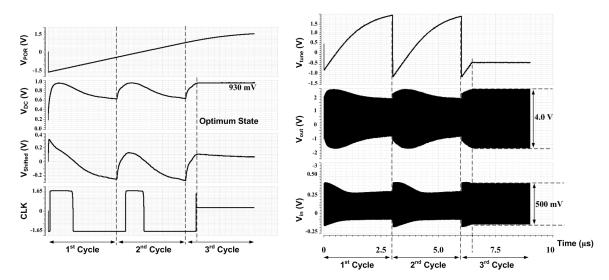

| 3.21 | Post-layout simulation results. Input : 2.4 GHz 500 mV <sub>pp</sub> sinusoid input.<br>Injection clock period : 1 MHz. Reset clock period : 1 KHz. POR clock period<br>: 100 Hz. $C_{clamp}$ =5 pF. zero- $V_T$ MOSFET : $W/L = 6 \ \mu m \ / \ 0.56 \ \mu m. \ V_{dd}$ =1.65<br>V and $V_{ss}$ =-1.65 V. $V_{DC}$ : Output voltage of voltage multiplier. $V_{shifted}$ :<br>Output voltage of voltage level shifter. $V_{in}$ : Input voltage of transformer.<br>$V_{out}$ : Output voltage of transformer. | 76 |

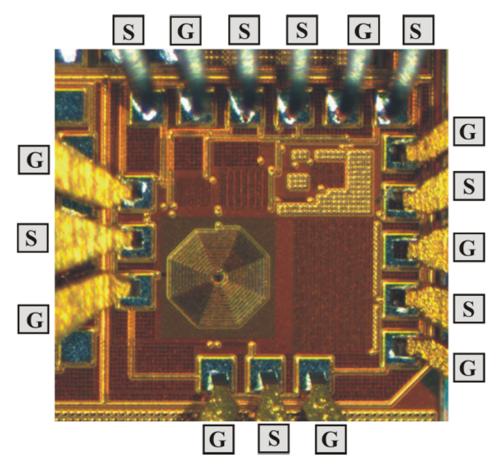

| 3.22 | Die micrograph of transformer matching network with probes in place for<br>on-wafer measurement                                                                                                                                                                                                                                                                                                                                                                                                                | 77 |

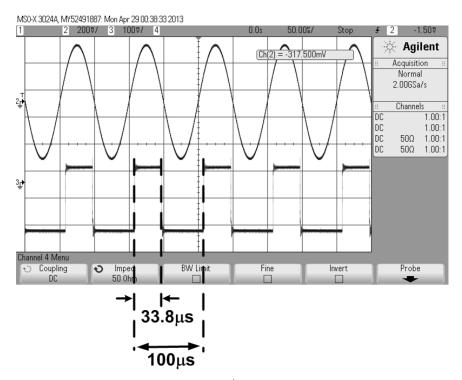

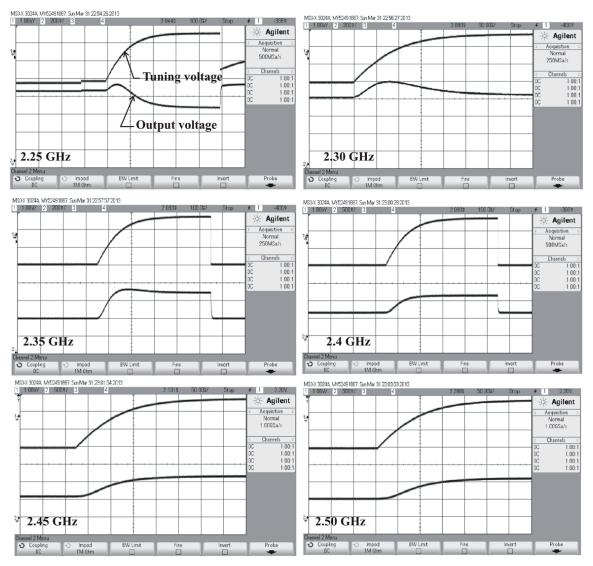

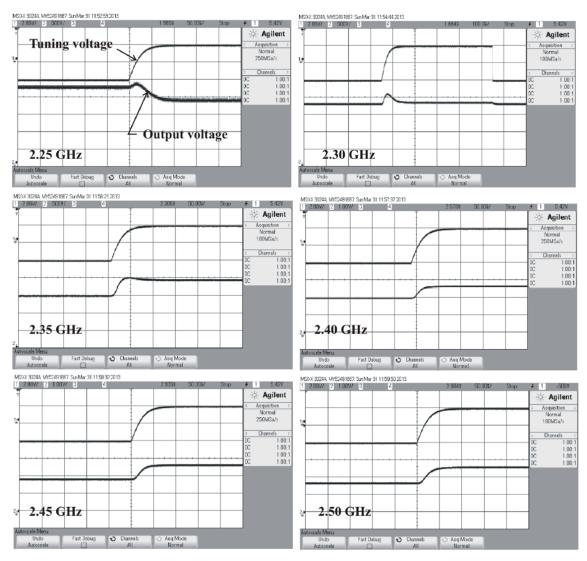

| 3.23 | Screen capture of tuning voltage $V_{tune}$ and output voltage of voltage multiplier<br>with 10 K $\Omega$ load. The maximum voltage gain is 7.35. Due to the limited<br>tuning range of the implemented varactor, the peak of $V_{DC}$ does not change<br>when frequency exceeds 2.4 GHz.                                                                                                                                                                                                                     | 78 |

| 3.24 | Screen capture of tuning voltage $V_{tune}$ and output voltage of voltage multiplier<br>with 1 M $\Omega$ load. The maximum voltage gain is 14.7. Due to the limited tuning<br>range of the implemented varactor, the peak of $V_{DC}$ does not change when<br>frequency exceeds 2.4 GHz.                                                                                                                                                                                                        | 79 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Contributions of the proposed dual-tank FSK architecture to a general passive wireless microsystem.                                                                                                                                                                                                                                                                                                                                                                                              | 83 |

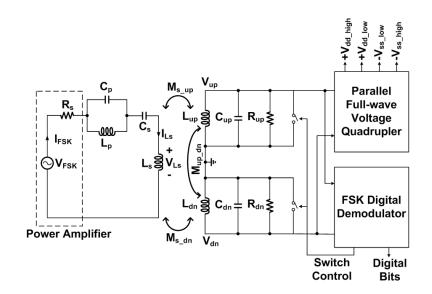

| 4.2  | Proposed dual-tank FSK demodulator                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83 |

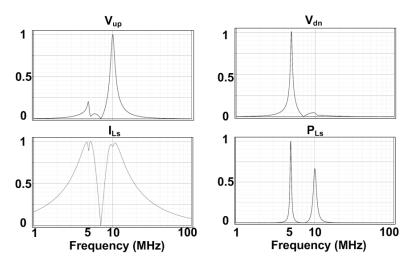

| 4.3  | Normalized frequency and power responses of dual-tank analog front-end. $I_{L_s}$ and $P_{L_s}$ are the current and power of the transmitter series inductor $L_s$ . FSK carrier frequencies: $f_{low} = 5$ MHz and $f_{high} = 10$ MHz.                                                                                                                                                                                                                                                         | 84 |

| 4.4  | Conventional NFET half-wave voltage doubler                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85 |

| 4.5  | Proposed PFET half-wave voltage doubler                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86 |

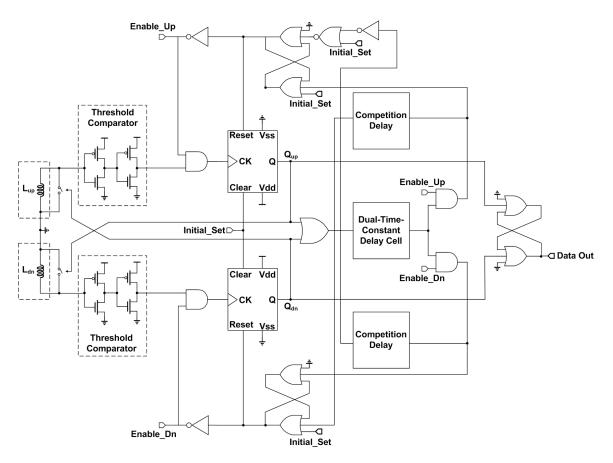

| 4.6  | Proposed full-wave voltage quadrupler.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86 |

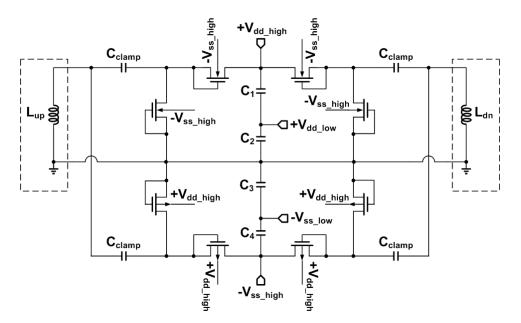

| 4.7  | FSK demodulator designed for the proposed dual-tank architecture                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88 |

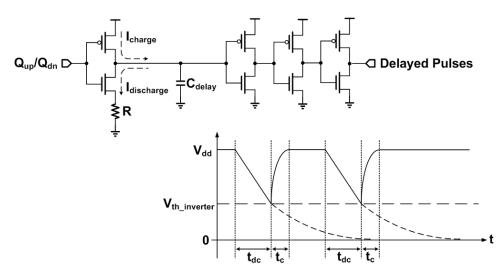

| 4.8  | Dual time constant delay cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89 |

| 4.9  | Triple-well complementary CMOS switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 89 |

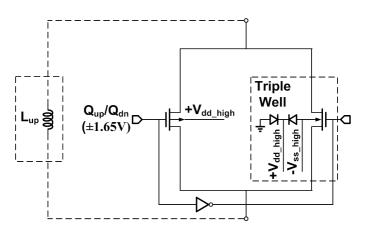

| 4.10 | Low-power voltage shifter and dual-supply step-up inverter amplifier. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                   | 90 |

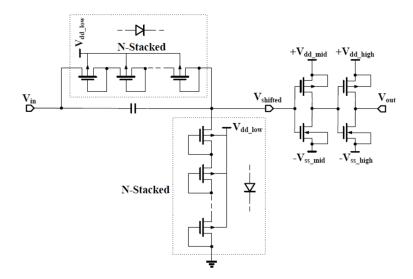

| 4.11 | Half-wave voltage doubler implemented in PFETs and NFETs. Circuit parameters: $V_{ac}=4$ V, $C_{clamp1} = C_{clamp2} = 10$ nF, $C_{rec1} = C_{rec2} = 10$ nF and $R_{load1} = R_{load2} = 10$ K $\Omega$ , $(W/L)_{NFET} = 20$ :1 and $(W/L)_{PFET} = 50$ :1                                                                                                                                                                                                                                     | 91 |

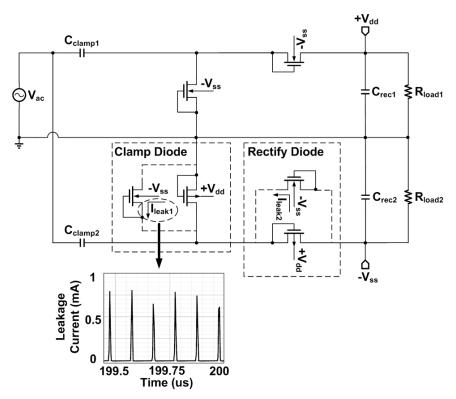

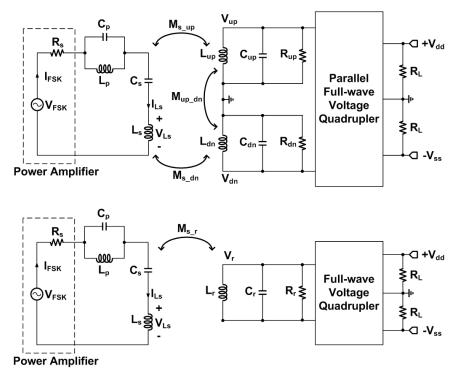

| 4.12 | Top - Dual-tank full-wave voltage quadrupler. Bottom - Single-tank full-<br>wave voltage quadrupler. Circuit parameters: $f_{low}=5$ MHz, $f_{high}=10$ MHz,<br>$M_{s\_up}=0.1, M_{s\_dn}=0.1, M_{up\_dn}=0.1, L_P=500$ nH, $C_P=1$ nF, $L_s=1 \mu$ H, $C_s=500$<br>pF, $L_{up}=2.5 \mu$ H, $C_{up}=101$ pF, $R_{up}=1.5$ K $\Omega$ , $L_{dn}=2.5 \mu$ H, $C_{dn}=404$ pF, $R_{dn}=2$<br>K $\Omega$ , $M_{s\_r}=0.1, L_r=2.5 \mu$ H, $C_r=404$ pF, $R_r=2$ K $\Omega$ , and $R_L=10$ K $\Omega$ | 93 |

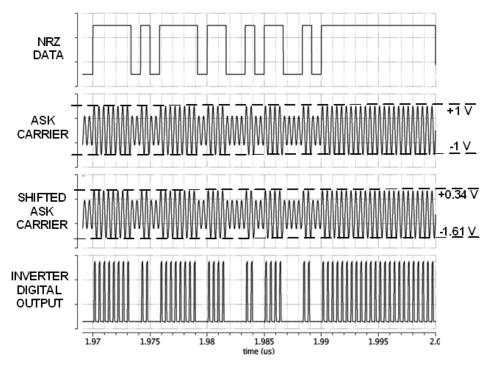

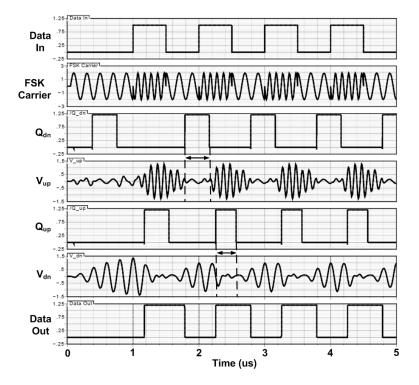

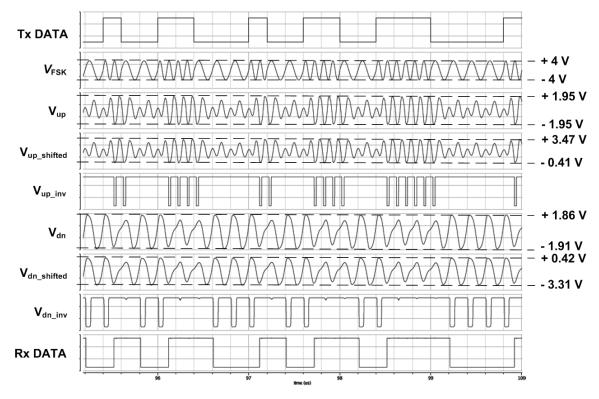

| 4.13 | Simulated waveforms of dual-tank FSK demodulator                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94 |

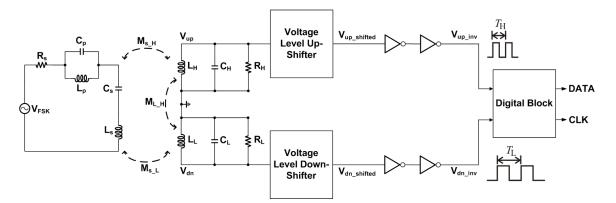

| 4.14 | Dual-tank FSK demodulation utilizing voltage level shifters                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94 |

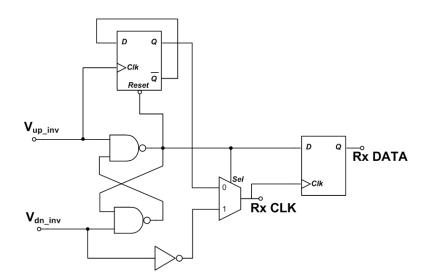

| 4.15 | Logic circuit implementation of the digital block in Fig.4.14                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95 |

| 4.16 | Response of FSK demodulation utilizing voltage level shifters                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96 |

# Abbreviations

| AC                              | Alternating Current                                                                                                                                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                             | Analog-to-Digital Converter                                                                                                                        |

| ADS                             | Advanced Design Systems                                                                                                                            |

| AM                              | Amplitude Modulation                                                                                                                               |

| ASK                             | Amplitude-Shift Keying                                                                                                                             |

| BSIM                            | Berkeley Short-channel IGFET Model                                                                                                                 |

| CAD                             | Computer-Aided Design                                                                                                                              |

| CMOS                            | Complementary Metal-Oxide Semiconductor                                                                                                            |

| dBm                             | Decidel with respect to 1 Milliwatt                                                                                                                |

|                                 |                                                                                                                                                    |

| DC                              | Direct Current                                                                                                                                     |

| DC<br>EEPROM                    | Direct Current<br>Electrically Erasable Programmable Read-Only Memory                                                                              |

|                                 |                                                                                                                                                    |

| EEPROM                          | Electrically Erasable Programmable Read-Only Memory                                                                                                |

| EEPROM<br>EM                    | Electrically Erasable Programmable Read-Only Memory<br>Electromagnetic                                                                             |

| EEPROM<br>EM<br>EPC             | Electrically Erasable Programmable Read-Only Memory<br>Electromagnetic<br>Electronic Product Code                                                  |

| EEPROM<br>EM<br>EPC<br>FF       | Electromagnetic<br>Electronic Product Code<br>Fast(NMOS)-Fast(PMOS)                                                                                |

| EEPROM<br>EM<br>EPC<br>FF<br>FM | Electrically Erasable Programmable Read-Only Memory<br>Electromagnetic<br>Electronic Product Code<br>Fast(NMOS)-Fast(PMOS)<br>Frequency Modulation |

| IBM    | International Business Machines                 |

|--------|-------------------------------------------------|

| IGFET  | Insulated-Gate Field-Effect Transistor          |

| ISM    | Industrial Scientific Medical                   |

| ISO    | International Organization for Standardization  |

| LC     | Inductor-Capacitor                              |

| LO     | Local Oscillator                                |

| Mbps   | Mega Bit Per Second                             |

| MHz    | Mega Hertz                                      |

| MIM    | Metal-Insulator-Metal                           |

| MOSFET | MetalOxideSemiconductor Field-Effect Transistor |

| NMOS   | N-type Metal-Oxide-Semiconductor                |

| NRZ    | Non-Return-to-Zero                              |

| PLL    | Phase-Locked Loop                               |

| PMOS   | P-type Metal-Oxide-Semiconductor                |

| POR    | Power-ON Reset                                  |

| PSK    | Phase-Shift Keying                              |

| PVT    | Process Voltage Temperature                     |

| reltol | relative tolerance                              |

| RF     | Radio Frequency                                 |

| RFID   | Radio Frequency Identification                  |

| RLC    | Resistor-Inductor-Capacitor                     |

| SF     | Slow(NMOS)-Fast(PMOS)                           |

| SS     | Slow(NMOS)- $Slow(PMOS)$                        |

- THD Total Harmonic Distortion

- TT Typical(NMOS)-Typical(PMOS)

- *UHF* Ultra High Frequency

- VCO Voltage-Controlled Oscillator

## Chapter 1

### Introduction

RF powered microsystems, also known as passive transponders, are critically needed in many applications such as automated payment systems, irretrievable pressure sensors in cement structures, and remote tracking devices. They have also found emerging applications in implantable electronics [1, 2, 3, 4, 5, 6], retinal prosthetic device [7], neuromuscular stimulation [8], wireless environmental monitoring [9], RFID [10], and medical endoscopy [11, 12], to name a few. Its most recent evolution involves passive transponders harvesting RF energy from ambient or dedicated sources such as mobile telephones, handheld radios, mobile base stations, and television/radio broadcast stations [13, 14]. The great advantage of a passive transponder is not having a power supply on-board. This enables it to operate indefinitely without requiring a battery exchange or recharge. Moreover, not having a power source attached to them, the transponders can be manufactured in very small sizes, free of connectors, cables and battery access panels, making them attractive for producing consumer electronics such as e-book readers and headsets, and ASIC sensors for implantable discrete wireless nodes and RFID tracking tags.

In this chapter, we first introduce some of the basic background information of wireless passive microsystems in Section 1.1. We then discuss some of the current design issues in passaive microsytems in Section 1.2 for our motivations and objectives. Section 1.3 presents the contributions of this dissertation. The organization of the dissertation is briefly described in Section 1.5. The chapter is summarized in Section 1.5.

### 1.1 Background

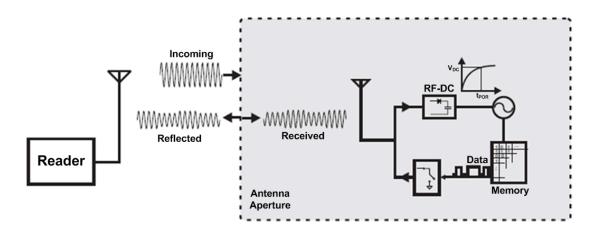

RF powered microsystems originate from the idea of wireless power transmission (WPT) which was proposed by Tesla early in 1899 [1]. In 1964, Brown et al. successfully demonstrated a working concept of a microwave-powered helicopter [2]. Recent research discovered that low-power wireless passive transponders can be powered by ambient RF energy such as mobile base stations, mobile phones, WiFi, Bluetooth and ZigBee [15, 16]. Wireless passive microsystems mainly operate by means of coupling through electric or magnetic fields. Inductive coupling of the magnetic field has been widely employed over short ranges with high efficiency using resonance magnetic coupling [2]. The second type, so-called rectenna, most often combines a rectifier and an antenna, coupling the power via electric field. The mix of magnetic and electric field couplings to form RF wave propagation for wireless passive microsystem enables a smaller scale integration of functionalities over longer operating distances. An RF powered transponder is a small wireless system that communicates with a nearby station called the reader. An illustration of the basic structure of an RF power microsystem comprising of a reader and a transponder is shown in Fig.1.1. The reader provides the transponder with power and initial information through a wireless channel. The reader-transponder communication protocol always starts with a relatively long power-up period during which the storage capacitor of the transponder is charged to an operational level [1]. At this point, the reader may send a data request which will be acknowledged by the transponder should the requested data be available. The transponder data are usually sensor readings or identification codes. These data are processed by the reader to gain the knowledge of the transponder's environment or identify subjects carrying the device.

#### 1.1.1 Architecture

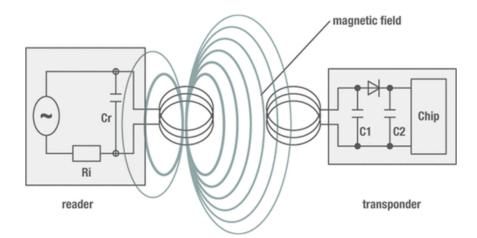

The architecture of an RF powered transponder has two majors layers: (1) an RF front and (2) baseband data units. The baseband circuits provide processing, generation and/or storage of baseband data or any combination of the three. These units may include EEPROMs for the storage of long ID codes, ADCs for quantizing sensor readings or even microprocessors that provide basic data/signal processing at the transponder. Fig.1.2 is the

Figure 1.1: Basic structure of RF power microsystem.

block diagram of a generic transponder architecture. All these blocks will have very stringent power constraints in an RF powered microsystem. Design for lower power consumption remains the top challenge. The study of baseband circuits, however, is beyond the scope of this dissertation and will not be discussed here.

Figure 1.2: Architecture of a typical passive transponder device.

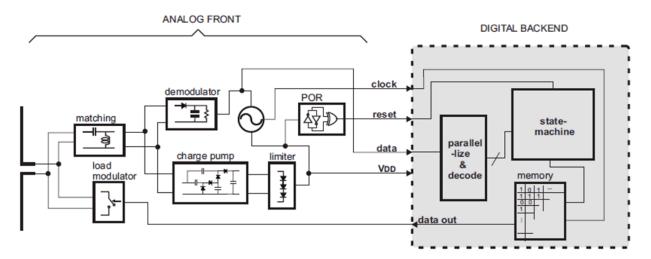

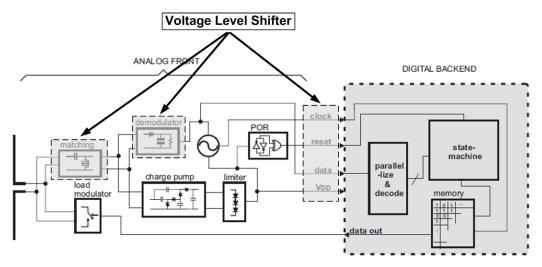

The RF front is responsible for the supply of power to the chip, and the wireless data interface with the reader. Major RF front components are an antenna, a matching network, a RF-to-DC converter, a modulator and a demodulator. The matching network and RF-DC conversion block are some times together referred to as the RF power harvester. Each block will be briefly described here, and a more detailed presentation will be given in the following chapters.

#### 1.1.2 Antenna

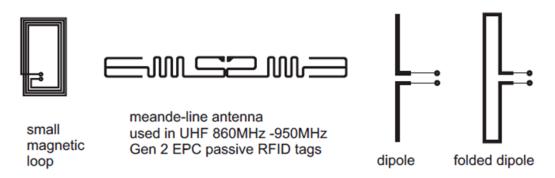

The antenna supplies the chip with power by gathering the electromagnetic wave emitted by the reader. It also receives the envelope of data modulated by the reader on the same carrier that provides the power. The shape and dimensions of the antenna are determined by the carrier wavelength, channel bandwidth and polarization of the EM field. For example, lower frequency (near-field) transponders often use magnetic coils whereas dipole, folded-dipole and meander-line antennas are popular configurations in UHF and microwave transponders. A small loop antenna is also popular geometry especially when the dimension of the antenna is required to be significantly smaller than the wavelength. Another advantage of the small loop antenna is its large inductive reactance which could be used to create a passive voltage gain in the received signal for better power harvest. Fig.1.3 shows different antennas used in passive transponders.

Figure 1.3: Popular antenna geometries for RFIDs and passive transponders.

#### 1.1.3 Matching Network

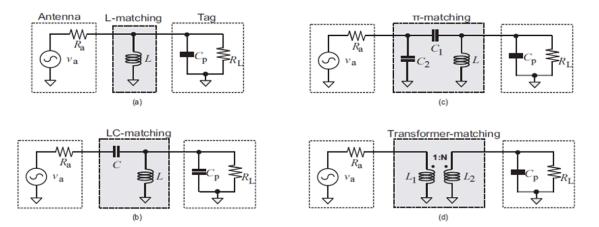

Regardless of the configuration, the impedance of the antenna has to be matched to input impedance of the chip to ensure the maximum transfer of power. This is accomplished by using a power matching block, which is a network of inductors and capacitors. Since these elements have purely imaginary impedances, ideally the power matching network does not dissipate power. However, due to the conductive loss of the inductor traces, the efficiency of the matching network becomes a challenging issue especially in on-chip matching where, in addition to the conductive loss, a significant portion of the available power is consumed in the substrate. The loss of energy in the substrate is mainly due to the Eddie currents caused by the coupling of electric and magnetic fields into the substrate. Another powermatching issue is the variation of the chip impedance under different loading conditions and the proximity of the reader. Power matching will be further discussed in Chapter 3. Fig.1.4 shows topologies of some popular matching networks. Fig.1.4 (a), (b) and (c) are widely used in transponders [10, 17, 18] while Fig.1.4 (d) is proposed in this dissertation for on-chip RF power matching in transponders.

**Figure 1.4:** (a), (b) and (c): Matching network topologies for RF power harvesting. (d) Transformer power matching circuit proposed in this dissertation.

#### 1.1.4 Rectification

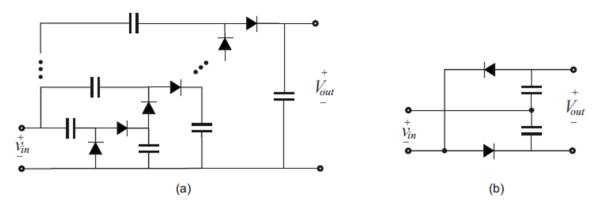

RF-to-DC conversion is implemented using rectifiers or voltage multipliers. At higher frequencies, however, due to a smaller antenna aperture, the signal at the transponder is weak. Most transponders operating at these frequencies use special rectifying charge-pump circuits to boost the voltage of the signal. Such architectures are called voltage multipliers. The DC output of a voltage multiplier is normally higher than the peak of the AC voltage applied. The main challenge in the design of voltage multipliers is the conversion efficiency which is typically less than 30% in most reported designs. In fact, efficiencies higher than 15% can only be achieved by the use of non-standard features such as Shockley diodes or silicon-on-insulator technologies [19, 10, 20]. Fig.1.5 shows two of the charge-pump topologies that are widely used in passive transponders [20, 21].

**Figure 1.5:** Dickson charge-pump and Nakamotos dual half-wave rectifier widely used for RF signal rectification and voltage boost in transponders.

#### 1.1.5 Modulation Backscatter/Load Modulation

In passive wireless microsystems, the absence of a power source makes the transmission of signals from the transponder challenging. Most designs do not allocate any DC power for RF transmission. Instead, they utilize a phenomenon called backscattering or backscatter modulation. Backscatter in antennas is similar to the reflection phenomenon in radars. Here, a portion of the received signal is reflected from the antenna back to the reader. The amount of the power reflected and the delay of the reflected wave are determined by the input impedance seen between the two terminals of the receiver antenna. Therefore, by modulating the termination impedance (or load) of the antenna, the reflected wave is modulated. Load modulation eases the power constraint of the design. In fact, by using this method along with other low-power design techniques, some of the recent UHF and microwave transponders have been able to lower the overall power consumption to a few microwatte, whereby increasing the operational range to over 12 meters while keeping the readers transmission powers within ISM bands regulations [20, 10]. Fig.1.6 shows the principle of backscattering in passive transponders.

**Figure 1.6:** Different matching network topologies for RF power harvesting. Transformer power matching circuit is proposed in this dissertation.

#### 1.1.6 Demodulation

As shown in Fig.1.2, the demodulator is located in parallel with the RF-DC conversion block, and draws a small fraction of the total RF current flowing into the chip. Due to power limitations, demodulation is usually done incoherently using an envelope detector followed by gain and signal quantizing circuits. Since the received signal must be large enough to power the device, envelope detection is well feasible in most cases.

#### 1.1.7 Industry Standard

| Band            | Regulation          | Range   | Data Speed       | Standards        |

|-----------------|---------------------|---------|------------------|------------------|

| 120-150 KHz     | Unregulated         | 10 cm   | Low              | ISO 11784        |

|                 | (LF Band)           |         |                  | ISO/IEC 18000-2A |

|                 |                     |         |                  | ISO/IEC 18000-2B |

| 13.56 MHz       | ISM Band            | 1 m     | Low to Moderate  | ISO/IEC 14443    |

|                 | (HF Band)           |         |                  | ISO/IEC 15693    |

|                 |                     |         |                  | ISO/IEC 18000-3  |

| 433 MHz         | ISM Band for        | 1-100 m | Moderate         | ISO 18000-7      |

|                 | Short Range Devices |         |                  | ISO 18000-7      |

|                 | (UHF Band)          |         |                  | ISO 18000-7      |

| 865-868 MHz     | ISM Band            | 1-2 m   | Moderate to High | ISO 18000-6A     |

| (Europe)        | (UHF Band)          |         |                  | ISO 18000-6A     |

| 902-928 MHz     |                     |         |                  | ISO 18000-6B     |

| (North America) |                     |         |                  | ISO 18000-6C     |

|                 |                     |         |                  | Class 0          |

|                 |                     |         |                  | Class 1          |

|                 |                     |         |                  | Class 1 Gen 2    |

| 2.45-5.80 GHz   | ISM band            | 1-2 m   | High             | ISO 18000-4      |

| (Microwave)     | (SHF Band)          |         |                  | ISO/IEC 24730-2  |

#### Table 1.1: RFID Standards

The fast evolution of wireless passive microsystems prompts national and international committees to set standards for its vastly diverse applications. Due to the continuously emerging technologies for new passive devices and systems, only a portion of the applications have been standardized in industries, especially for RFID applications. A number of organizations have set standards for RFID, including the International Organization for Standardization (ISO) and EPCglobal, etc. One of the early popular ISO RFID standards, known as ISO 15693, addresses contactless integrated circuit devices, which are used in security access and payment systems. ISO later developed a new series of standards, known as ISO 18000 family, to address how tags and readers communicate in a number of item identification applications. For example, ISO 18000 part 3, identifies 13.56 MHz as the frequency for tag-reader communication in its industrial and medical applications. Table 1.1 briefly summarizes some of the most popular RFID standards with its frequency bands, where the ISM bands are internationally reserved for industrial, scientific and medical purposes other than communications. The particular frequencies of the circuits proposed in this dissertation are ISM-HF band at 13.56 MHz and SHF-microwave band at 2.45 GHz.

### **1.2** Motivation and Objectives

Despite the numerous advantages of wirelessly powered passive microsystems, challenges in such systems must be overcome for the advantages to be feasible. These include the challenges of an efficient RF-power-receiving small antenna mentioned in Section 1.1.2, efficient matching networks for variations of input power and output loading impedances mentioned in Section 1.1.3, superior RF-to-DC power conversion efficiency mentioned in Section 1.1.4, novel low-power modulation/demodulation circuitries mentioned in Section 1.1.5 and 1.1.6, and optimization of wireless passive microsystem architectures.

#### 1.2.1 Voltage Level Shifters

Due to the very limited power received in passive microsystems, each block in the architecture of a passive microsystem in Fig.1.2 has to be optimized for full functional operation with low-power consumption. In this dissertation, a family of low-power passive voltage level shifters will be proposed in Chapter 2. By properly configuring the proposed voltage level shifters, the demodulator block in Fig.1.2 can be implemented for low-power ASK and FSK wireless demodulation schemes. The proposed voltage level shifter can also be applied in the matching network block in Fig.1.2 for auto-calibration of the matching network to achieve the maximum power harvest. We will see such an auto-calibration peak amplitude detection technique by voltage level shifting in Chapter 3. Furthermore, to lower power consumption in passive wireless microsystems, devices in non-critical portion of these systems often operate in a sub-threshold mode with a reduced supply voltage while other blocks such as electronically erasable programmable read-only memories operate in a super-threshold mode with a higher supply voltage [22, 23, 10]. Voltage level shifters that provide

proper voltage signals to bridge sub-threshold and super-threshold blocks are needed [24, 25]. Voltage level shifters are commonly implemented in the following topologies: (1) Half-Latch Topology: a half-latch topology is to take the advantage of its simple configuration subsequently a small propagation delay. These voltage level shifters, however, suffer from a long propagation delay, large pull-down NMOS transistors, and an excessive short-circuit current. The low current driving ability of half-latch voltage level shifters can be mitigated by replacing the pull-up PMOS latch with a current mirror, however, at the cost of excessive static power consumption [26]. (2) Bootstrapping Technique: Bootstrapping technique reduces the power consumption of half-latch voltage level shifters by driving pull-up PMOS and pull-down NMOS with separate low-swing signals [27]. Among the bootstrapping techniques, the voltage level shifter proposed by Kwon and Min improves speed and lowers power consumption by employing an auxiliary level shifter [28]. (3) Subthreshold-Superthreshold Conversion: Ltkemeier and Rckert proposed a Wilson current mirror based voltage level shifter for subthreshid-to-superthreshold signaling [29]. The energy-efficient subthreshold voltage level shifter proposed by Wooters et al. used low- $V_{TH}$  transistors to interface with the low- $V_{DD}$  circuitry feeding the voltage level shifters so as to boost the current-driving ability [30]. (4) Gate Coupling Technique: Baek *et al.* proposed a power efficient up-converter by coupling the gate of protection transistors to the input capacitively [31]. (5) Multi- $V_{TH}$ Transistor Topology: The voltage level shifter by Hasanbegovic and Aunet utilizes multi- $V_{TH}$ transistors with low- $V_{TH}$  transistors placed in locations where speed is critical and high- $V_{TH}$ transistors placed in locations where leakage current is essential [32].

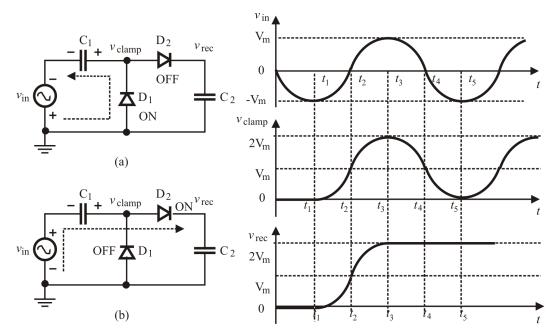

The preceding voltage level shifters only provide digital signaling and cannot provide continuous voltage level shifting. Although source followers, common-source, common-gate configurations or circuits alike are handy choices for shifting the median value of analog signals, their usefulness in low-power applications is largely hindered by the following factors: (1) the excessive static power consumption, (2) the minimum amount of the voltage shift that these voltage shifters can provide is typically lower-bounded by the gate-source voltage of MOSFETs in saturation, and (3) the maximum amount of the voltage shift that these voltage shifters can provide is upper and lower bounded by the voltages of the power rails, further limiting their applications in systems such as passive wireless microsystems where the output of the power harvesters of these systems is typically much higher than the amplitude of the received radio-frequency signals.

In this dissertation, we will propose a different kind of voltage level shifters built upon the rectifying characteristics of diode-based voltage multipliers. We will demonstrate that these voltage level shifters are capable of removing the drawbacks of the aforementioned voltage level shifters.

### 1.2.2 Impedance Matching

Passive microsystems are not equipped with internal batteries. Their operating power has to be harvested wirelessly. Illustrated in Fig.1.2, the power harvesting module includes an antenna, a matching network and a charge-pump voltage multiplier. The matching network needs to be optimized for the maximum power transfer from the antenna to the voltage multiplier. The voltage multiplier ideally requires the input voltage magnitude as large as possible for efficient AC-DC conversion. The efficiency of power harvest determines the maximum distance over which reliable links between base stations and microsystems can be established, the complexity subsequently the functionalities of microsystems, and the minimum amount of time required to harvest a sufficient amount of power. The efficiency of radio-frequency power harvest is mainly determined by three key factors listed as follows: (1) Efficiency of Antenna: The higher efficiency of the antenna induces a larger voltage in the antenna. The voltage generated by an antenna is determined by the type and dimensions of the antenna, both of which are usually set by applications. (2) Efficiency of Voltage Multiplier: An effective approach to improve the efficiency of voltage multipliers is to maximize the input voltage fed into the voltage multipliers from the antenna [33]. The loss of the power conversion efficiency of voltage multipliers is due to the voltage drop of the rectifying devices [18, 21, 19]. It can be improved by increasing the amplitude of the input voltage or using low-threshold rectifying devices, such as Shockley diode and zero- $V_T$ MOSFETs [20]. (3) Accuracy of Impedance Matching Network: The voltage at the input of voltage multipliers can be boosted using a resonant tank inserted between the antenna and the voltage multiplier that resonates at the carrier frequency [10, 34, 17, 35, 36]. To maximize the input voltage, in [33], an inductive matching technique is proposed to shunt the input of a voltage multiplier with a parallel inductor for a resonant LC tank utilizing the equivalent input capacitance of the voltage multiplier. A further boost of the input voltage across the voltage multiplier is obtained by applying a LC matching network at the input of the voltage multiplier [17, 35, 36]. The effectiveness of resonating LC tanks is severely affected by the low quality factor of on-chip spiral inductors. Also, if a varactor is employed to provide frequency tuning, the resistive loss of the varactor will also have a detrimental effect on the quality factor of the tank. The performance of the LC matching network, in particular, the voltage gain, can be largely improved by replacing the spiral inductor with a step-up spiral transformer [37]. (4) Optimum Loading of Impedance Matching Network: Instead of finding the optimum matching network, [38] analyzed the optimum load that yields the maximum possible power efficiency under arbitrary input impedance conditions. For the step-up spiral transformer introduced in [37], the large turn ratio and the wide spiral of the primary winding yield a large quality factor and a large voltage gain. Since the load of the voltage multiplier varies with applications, the input impedance of the transformer matching network with a voltage multiplier load at its secondary winding will also vary, giving rise to an impedance mismatch between the antenna and the transformer subsequently the loss of energy transferred from the antenna to the transformer. In addition, process-spread also gives rise to errors in the inductances, parasitic capacitances and resistances of the transformer, resulting in process-spread induced drift of the input impedance and resonant frequency of the transformer matching network. The former affects the amount of power transmitted from the antenna to the transformer while the latter impacts the output voltage of the transformer especially when the quality factor of the transformer is high. It is highly desirable that the parameters of the transformer matching network can be tuned such that it will not only provide a matching impedance to the antenna to maximize energy transfer from the antenna to the transformer, but also resonate at the desired frequency, i.e., the carrier frequency, to maximize the voltage of the secondary winding of the transformer.

This dissertation proposes a transformer impedance matching and frequency tuning technique for high-efficiency power harvest of passive wireless microsystems. The proposed method utilizes a step-up transformer inserted between the antenna and voltage multiplier to perform both impedance transformation for power matching and voltage amplification for improving the efficiency of the voltage multipliers.

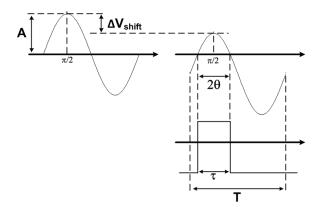

### 1.2.3 FSK Demodulator

There are different modulation techniques for wireless passive microsystems, among which ASK has been the most popular one due to its simple implementation subsequently low power consumption. FSK modulation has been recently used in passive wireless microsystems for its constant-envelope modulation scheme. When FSK is used to encode the data transmitted from a base station to a passive wireless microsystem, the drawback of fluctuating power transmission encountered in ASK is eliminated. Since baseband data are represented by the frequency rather than the amplitude of the carrier, the effects of noise and disturbances on data transmission are also reduced. Another unique characteristic of FSK is its ability to transmit data at a high data rate owing to the fact that the demodulation of a FSK-modulated signal does not need to extract the envelope of the carrier using a low-pass filter with a large time constant. This is particularly important for biomedical implants as not only is the data rate of these microsystems such as cochlear implants and visual prosthesis implants high, the carrier frequency of these implants is typically 13.56 MHz due to the high degree of the absorption of electromagnetic waves by human bodies at high frequencies.