## DESIGN AND IMPLEMENTATION OF PORTABLE AND CONFIGURABLE RISC PROCESSOR ARCHITECTURE

by

Volodymyr Sergeyev, B.Eng, Odessa Polytechnic University, 1987

A project presented to Ryerson University in partial fulfillment of the requirement for the degree of Master of Engineering in the Program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2010 © Volodymyr Sergeyev 2010

#### PROPERTY OF RYERSON UNIVERSITY LIBRARY

## **Author's Declaration**

I hereby declare that I am the sole author of this project.

2

I authorize Ryerson University to lend this project to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this project by photocopying or by other means, in total or in part at the request of other institutions or individuals for the purpose of scholarly research.

. .

-

## **Instructions on Borrowers**

•

5

Ryerson University requires the signatures of all persons using or photocopying this project. Please sign below, and give address and date.

| Name | Signature | Address | Date |

|------|-----------|---------|------|

|      |           |         |      |

|      |           | •       |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           | -       |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         | -    |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

#### DESIGN AND IMPLEMENTATION OF PORTABLE AND CONFIGURABLE RISC PROCESSOR ARCHITECTURE

Volodymyr Sergeyev Master of Engineering Department of Electrical and Computer Engineering Ryerson University, Toronto, 2010

#### Abstract

This project presents the configurable microprocessor design based on the MIPS architecture. The level of configurability includes a choice of the pipelined or unpipelined architecture, number of pipeline stages, data path bit-width, instruction subsetting, program and data memory size. The microprocessor design flow is supported by the set of standard and custom software tools. The wide spectrum of the microprocessor configurations provides an opportunity to optimize hardware for the specific application. The HDL design of the microprocessor is independent of the hardware platform. The portability of the design was verified on the competitive FPGA platforms and ASIC. The selected microprocessor configuration running the test application was successfully implemented and verified on the FPGA development board. The obtained implementation results were compared to the existing commercial and research microprocessors and critical advantages of the presented design were outlined.

### Acknowledgments

It is a pleasure to thank those who made this project possible. I want to convey my deepest gratitude to my supervisor Dr. Adnan Kabbani whose assistance, encouragement and expertise significantly contributed to this work. Through the duration of project-writing period, he provided inspiration, guidance, and good advice. Work under his supervision gave me an invaluable experience.

I would like to thank the many people who have taught me during my graduate studies. I am especially grateful to professors Reza Sedaghat, Fei Yuan, Gul Khan, Vadim Geurkov, and Lev Kirischian. Their devotion, professional attitude, and teaching skills had a remarkable influence on the completion of my studies.

I wish to thank the Department of Electrical and Computer Engineering for providing research resources and technical facilities required for completion of this project. My special thanks to Jason Naughton whose knowledge and technical expertise helped me efficiently use the department resources.

Most of all I owe my thanks to my family for their patience, support, and understanding during my graduate study. Especially, I am grateful to my wife Iryna whose encouragement and endless love helped me finish this work.

vii

# Contents

i.

| 1 | INT | RODUC   | CTION                               | 1   |

|---|-----|---------|-------------------------------------|-----|

|   | 1.1 | Motiva  | ation                               | 1   |

|   | 1.2 | Object  | tives and Contributions             | 3   |

|   | 1.3 | Projec  | t Organization                      | 4   |

| 2 | BAC | KGRO    | UND                                 | 5   |

|   | 2.1 | Introd  | uction                              | 5   |

|   | 2.2 |         | MIPS Processor Architecture         |     |

|   | 2.3 |         | y Related Work                      |     |

|   |     | 2.3.1   | •                                   |     |

|   |     | 2.3.2   | Configurable Processors             |     |

|   | 2.4 |         | ary                                 |     |

| 3 | CON | FICUR   | ABLE PROCESSOR PROPOSED DESIGN      | 20  |

| • | 3.1 |         | ath Components                      |     |

|   | 2.1 | 3.1.1   | •                                   |     |

|   |     | 3.1.2   | Register File                       |     |

|   |     | 3.1.3   | Instruction Memory                  |     |

|   |     | 3.1.4   | Data Memory                         |     |

|   |     | 3.1.5   | Program Counter                     |     |

|   |     | 3.1.6   | Sign Extension                      | 27  |

|   | 3.2 | Contro  | ol Unit Design                      | 27  |

|   | 3.3 | Pipelii | ned Architecture Design             |     |

|   |     | 3.3.1   | Five Stages Pipelined Processor     | 29  |

|   |     | 3.3.2   | Four Stages Pipelined Processor     | .31 |

|   | 3.4 | Unpip   | elined Architecture Design          | 33  |

|   |     | 3.4.1   | One-Cycle Processor                 | 33  |

|   |     | 3.4.2   | Multi-Cycle Processor               | .35 |

|   | 3.5 | Config  | guration Control                    | .37 |

|   | 3.6 | Config  | gurable Features                    |     |

|   |     | 3.6.1   | Data Path Width Parameterization    |     |

|   |     | 3.6.2   | Instructions Set Parameterization   |     |

|   |     | 3.6.3   | Data Memory Parameterization        |     |

|   |     | 3.6.4   | Instruction Memory Parameterization |     |

|   |     | 3.6.5   | I/O Memory Parameterization         |     |

|   |     | 3.6.6   | FPGA Optimization                   | .40 |

|   | 3.7 | Input/Output Interface                    | 42  |

|---|-----|-------------------------------------------|-----|

|   | 3.8 | Configuration GUI                         | 43  |

|   | 3.9 | Summary                                   | 45  |

| 4 | IMP | LEMENTATION                               | .46 |

|   | 4.1 | Hardware Components and Development Tools | 46  |

|   | 4.2 | Design and Implementation Flow            | 47  |

|   | 4.3 | FPGA Implementation                       | 50  |

|   |     | 4.3.1 Project Files                       | 50  |

|   |     | 4.3.2 Architecture                        | 53  |

|   |     | 4.3.3 BRAM Optimization                   | 54  |

|   |     | 4.3.4 Timing Constraints                  | 54  |

|   |     | 4.3.5 Xilinx Platform Implementation      | 55  |

|   |     | 4.3.6 Altera Platform Implementation      | 57  |

|   | 4.4 | ASIC Implementation                       | 59  |

|   | 4.5 | Demo Platform Design and Implementation   | 61  |

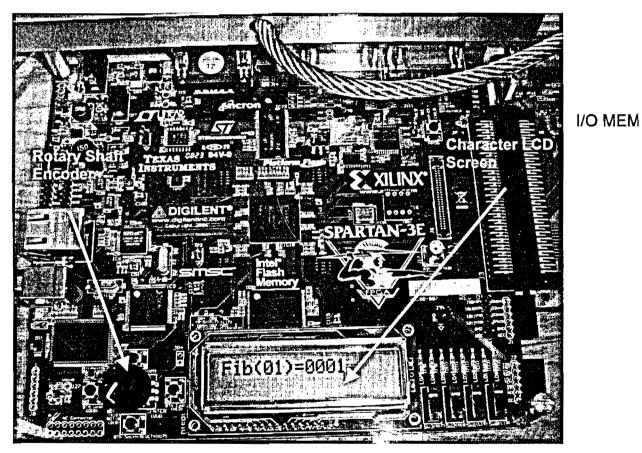

|   |     | 4.5.1 Hardware Platform Description       | 61  |

|   |     | 4.5.2 Processor Core Configuration        | 63  |

|   |     | 4.5.3 Demo Platform Interface Design      | 64  |

|   |     | 4.5.4 Software/Hardware Co-Design         | 64  |

|   |     | 4.5.5 Demo Design Implementation          | 65  |

|   | 4.6 | Summary                                   | 66  |

| 5 | DES | IGN VERIFICATION                          | .67 |

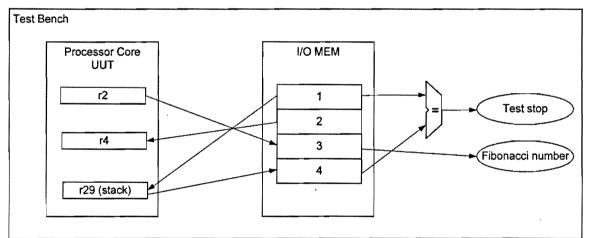

|   | 5.1 | Testbench Design                          | 68  |

|   |     | 5.1.1 Fibonacci Number Test Program       |     |

|   |     | 5.1.2 Verilog Testbench                   |     |

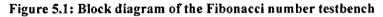

|   | 5.2 | Pipelined Architecture Verification       |     |

|   | 5.3 | Multi-Cycle Design Verification           |     |

|   | 5.4 | One-Cycle Design Verification             |     |

|   | 5.5 | Demo Platform Design Verification         |     |

|   | 5.6 | Summary                                   | 77  |

| 6 |     | ULT ANALYSIS                              |     |

|   |     | Xilinx FPGA Implementation Evaluation     |     |

|   | 6.2 | Altera FPGA Implementation Evaluation     |     |

|   | 6.3 | ASIC Implementation Evaluation            | 83  |

|   | 6.4 | Evaluation Against Existing Solutions     |     |

|   | 6.5 | Summary                                   | 86  |

| 7 | CON | CLUSION AND FUTURE WORK                   |     |

|   | 7.1 | Conclusion                                |     |

|   | 7.2 | Future Work                               | 88  |

| A | DEN | IO DESIGN PROGRAM CODE                    | .90 |

| B | PRO | CESSOR CONFIGURATION FILE                 | .95 |

|   |     | B.1 Base Configuration File Template      | 95  |

|    | B.2 Automatically Generated Part of Configuration File                                                            |     |

|----|-------------------------------------------------------------------------------------------------------------------|-----|

| С  | IMPLEMENTATION REPORTS         C.1 Xilinx Summary Reports         C.2 BRAM Utilization Reports                    |     |

| D  | TSMC 0.18 μM PROCESS IMPLEMENTATION                                                                               | 112 |

| E  | DEMO DESIGN CONSTRAINTS AND REPORT                                                                                | 114 |

| F  | FIBONACCI TEST PROGRAM                                                                                            | 118 |

| G  | CONFIGURABLE PROCESSOR VERIFICATION         G.1       Verification Reports         G.2       Simulation Waveforms |     |

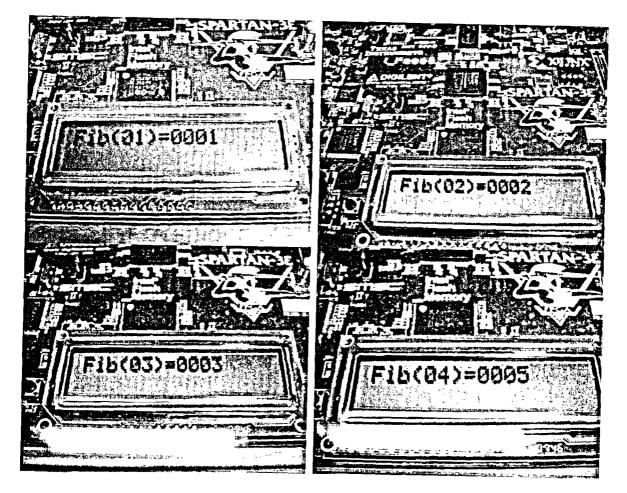

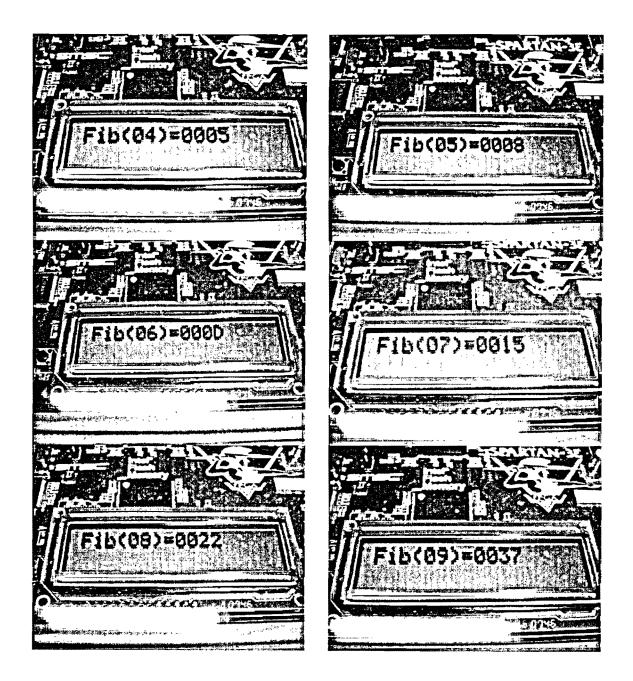

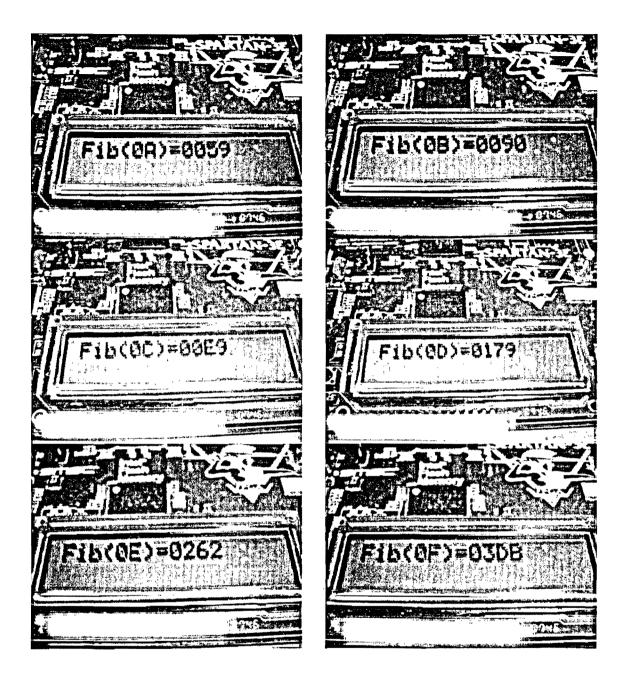

| H  | IMAGES OF DEMO DESIGN EXAMPLE                                                                                     | 125 |

| I  | ALTERA FPGA IMPLEMENTION                                                                                          | 130 |

| BI | BLIOGRAPHY                                                                                                        | 133 |

•

,

•

.,

. ~ Ŧ : -

•

# List of Tables

4

-

| Table 2.1. MIPS instruction format                                                                   |

|------------------------------------------------------------------------------------------------------|

| Table 2.2. MIPS instruction set                                                                      |

| Table 2.3: MicroBlaze Processor v7.2 Performance Levels    15                                        |

| Table 2.4. Nios II different version features                                                        |

| Table 3.1: Supported ALU operations                                                                  |

| Table 3.2: ALU signals                                                                               |

| Table 3.3: Data memory signals    25                                                                 |

| Table 3.4: Set of configuration features available for the processor core       38                   |

| Table 4.1: Implementation and development tools    46                                                |

| Table 4.2: MIPS_DLX project files description                                                        |

| Table 4.3: MIPS interface signals    53                                                              |

| Table 4.4: Clock period timing constraints (ns)    55                                                |

| Table 4.5: Maximum clock speed (MHz) of the processor configurations implemented in                  |

| Xilinx FPGA                                                                                          |

| Table 4.6: Xilinx FPGA resources (LUTs) used for the implementation of the different                 |

| processor configurations                                                                             |

| Table 4.7: Implementation results of 512-bit 5-stages pipelined processor configuration 57           |

| Table 4.8: Maximum clock speed (MHz) of the processor implemented in Altera FPGA58                   |

| Table 4.9: Altera FPGA resources (ALMs) used for the implementation of the different                 |

| processor configurations                                                                             |

| Table 4.10: Maximum clock speed (MHz) of the processor configurations implemented using              |

| 0.18 µm technology process                                                                           |

| Table 4.11: Total cell area ( $\mu m^2$ ) occupied by the processor configurations implemented using |

| 0.18 μm technology process                                                                           |

| Table 4.12: Mapping of the Demo design signals in I/O memory address space                           |

| Table 5.1: Verification matrix for the processor configurations set                                  |

| Table 5.2: Mapping of testbench in I/O memory address space    71                                    |

| Table 5.3: Data hazards handled by forwarding and stalling in the pipelined architectures74          |

| Table 5.4: FSM action description                                                                    |

| Table 6.1: Configurable MIPS processor variants vs. Altera Nios II/s/e       85                      |

| Table 6.2: Configurable MIPS processor vs. Xilinx Microblaze and Leon3                               |

. 4

•

# List of Figures

| Figure 2.1. Block diagram of the multi-cycled MIPS processor                                     | 10 |

|--------------------------------------------------------------------------------------------------|----|

| Figure 2.2. Block diagram of the pipelined MIPS processor                                        | 10 |

| Figure 3.1: Processor ALU symbol                                                                 | 22 |

| Figure 3.2: Register file symbol                                                                 |    |

| Figure 3.3: Regfile Read-First block diagram                                                     |    |

| Figure 3.4: Regfile Write-First block diagram                                                    |    |

| Figure 3.5: Regfile Write-First mode timing diagram                                              |    |

| Figure 3.6: Regfile Read-First mode timing diagram                                               |    |

| Figure 3.7: Instruction memory symbol                                                            |    |

| Figure 3.8: Data memory symbol                                                                   |    |

| Figure 3.9: Data memory read/write timing diagram                                                |    |

| Figure 3.10: Program counter symbol                                                              |    |

| Figure 3.11: Program counter timing diagram                                                      |    |

| Figure 3.12: Sign Extension symbol                                                               |    |

| Figure 3.13: Block diagram of five stages pipelined processor                                    |    |

| Figure 3.14: Block diagram of four stages pipelined processor                                    |    |

| Figure 3.15: One-cycle processor architecture                                                    |    |

| Figure 3.16: Multi-cycle processor architecture                                                  |    |

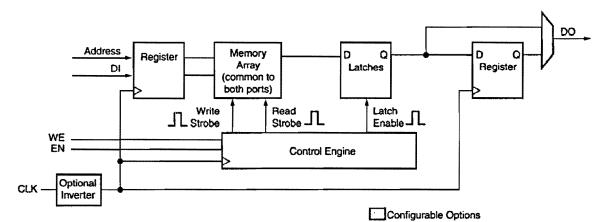

| Figure 3.17: BRAM logic diagram                                                                  | 40 |

| Figure 3.18: BRAM optimization for five stages architecture                                      | 41 |

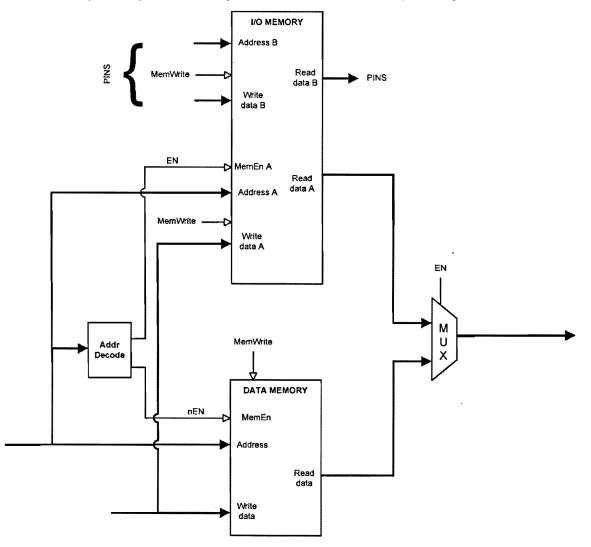

| Figure 3.19: Block diagram of the input/output interface organization                            |    |

| Figure 3.20: Configuration GUI wizard screenshot                                                 | 44 |

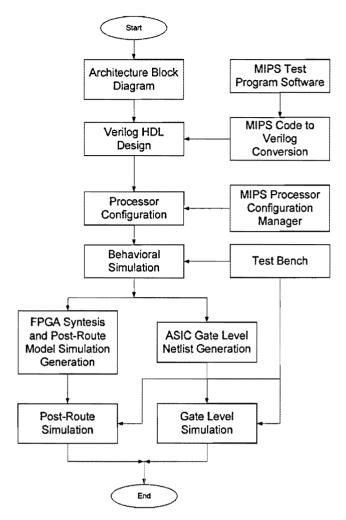

| Figure 4.1: The configurable MIPS processor design flow                                          |    |

| Figure 4.2: Format of the pseudo code inserted in the instruction memory module by the           |    |

| proposed custom conversion tool                                                                  |    |

| Figure 4.3 : MIPS_DLX project modules hierarchy.                                                 | 51 |

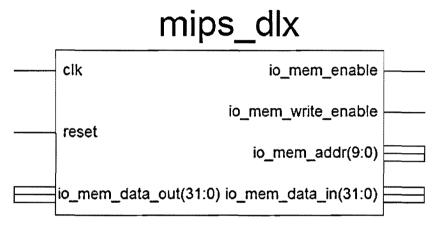

| Figure 4.4: 32-bit MIPS processor module                                                         | 53 |

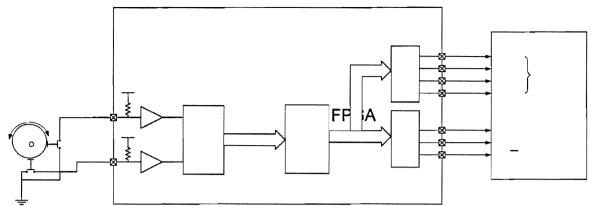

| Figure 4.5: Demo platform block diagram                                                          | 62 |

| Figure 4.6: Spartan-3E startup kit FPGA board                                                    | 62 |

| Figure 5.1: Block diagram of the Fibonacci number testbench                                      | 71 |

| Figure 5.2: Forwarding WB→EX and MEM→ EX in the pipelined architecture (ModelSin                 | n  |

| waveform)                                                                                        |    |

| Figure 5.3: Stalling and forwarding MEM $\rightarrow$ ID in the pipelined architecture (ModelSim |    |

| waveform)                                                                                        | 73 |

| Figure 5.4: Waveform of the multi-cycle architecture simulation                                  | 75 |

|                                                                                                  |    |

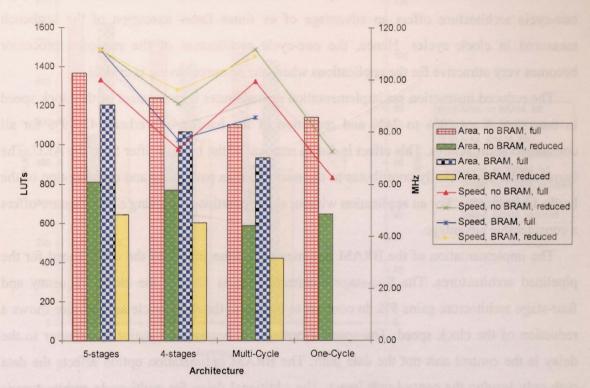

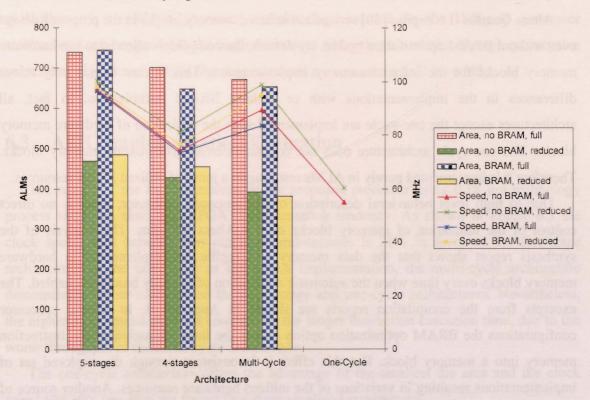

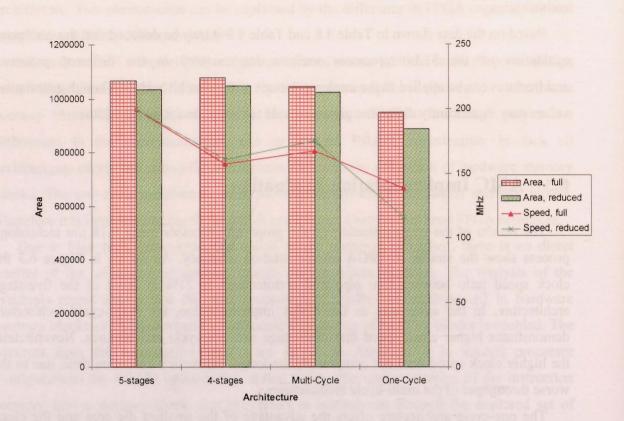

| Figure 6.1: Evaluation chart of the architecture variants of 32-bit processor implemented in Xilinx FPGA                      |

|-------------------------------------------------------------------------------------------------------------------------------|

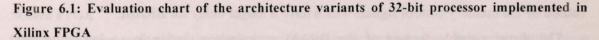

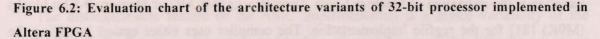

| Figure 6.2: Evaluation chart of the architecture variants of 32-bit processor implemented in Altera FPGA                      |

| Figure 6.3: Evaluation chart of the architecture variants of 32-bit processor implemented<br>using 0.18 µm technology process |

| Figure G.1: Post-route simulation waveforms of the 32-bit configuration of multi-cycle architecture                           |

| Figure G.2: Post-route simulation waveforms of the 32-bit configuration of one-cycle architecture                             |

| Figure G.3: Post-route simulation waveforms of the 32-bit configuration of four-stage architecture                            |

| Figure G.4: Post-route simulation waveforms of the 32-bit configuration of five-stage architecture                            |

-

# List of Abbreviations

-

-

| ASIC | Application Specific Integrated Circuit                                  |

|------|--------------------------------------------------------------------------|

| ASIP | Application Specific Instruction set Processor                           |

| ASP  | Application Specific Processor                                           |

| FPGA | Field Programmable Gate Array                                            |

| FPU  | Floating Point Unit                                                      |

| GUI  | Graphic User Interface                                                   |

| IDE  | Integrated Development Environment                                       |

| ISE  | Integrated Software Environment                                          |

| LE   | Logic Element                                                            |

| LUT  | Look-Up Table                                                            |

| M9K  | Memory 9-Kbit Block                                                      |

| MIPS | Microprocessor without Interlocking Pipe Stages                          |

| MLAB | Memory Logic Array Block                                                 |

| MMU  | Memory Management Unit                                                   |

| RAW  | Read After Write                                                         |

| RISC | Reduced Instruction Set Computer                                         |

| ROM  | Read Only Memory                                                         |

| TLB  | Translation Look-aside Buffer                                            |

| UUT  | Unit Under Test                                                          |

| VHDL | Very High Speed Integrated Circuit (VHSIC) Hardware Description Language |

| WAR  | Write After Read                                                         |

|      |                                                                          |

WAW Write After Write

-• .

## Chapter 1

## Introduction

#### 1.1 Motivation

The contemporary microprocessor market offers a vast variety of chips for new designs. The right choice of a microprocessor to fit for a specific application is a challenging task nowadays. Utilization of a configurable processor can facilitate this problem. A hardware designer can choose the configuration of a microprocessor which precisely matches design requirements. The advantage of FPGA configurable computing has brought the idea of implementing a general-purpose microprocessor on an FPGA chip [1]. This concept along with the growing demands for customization of the processor and its peripherals inspires FPGA vendors to include microprocessors in FPGA architecture. Manufacturers offer this feature in a form of hard or soft core. More then 32% of hardware developers use embedded FPGA microprocessors in their designs [2]. Configurable hard microprocessors also follow this trend. Customizable microprocessors form Tensilica, ARC and Improv for ASIC implementation offer a broad range of microprocessor optional features. Designers can choose the instruction set architecture to suit the application requirements. The microprocessor data path and pipeline structure are also customizable in order to meet the design constrains. In the ladder of the microprocessor solutions the configurable microprocessors occupy a niche in the middle between implementation on the dedicated hardware and the software running on general-purpose microprocessors [3]. Most of commercially available solutions for configurable microprocessors are oriented on the particular technology. A designer has to choose the target technology up-front. It may be a choice of FPGA from different manufacturers or technology process. But since the design is implemented and verified on a

chosen target platform it becomes very difficult to migrate the design to a different platform. The common situation is when a verified, proven design is to be upgraded due to additional new requirements or obsolescence of the target chip. Another challenge is the verification of an ASIC implemented microprocessor on FPGA platform. Design seamless transition from FPGA to ASIC is normally offered within technologies provided by the same manufacturer (e.g. Altera Stratix to HardCopy [4]).

Beside of the problems related to a market-oriented engineering, the configurable processor architecture with a versatile set of configuration features offers the fine grain optimization of hardware resources required the specific application. The combination of the possible processor configurations creates the exploration space which provides the opportunity for the research on decision making in the selection of the specific configuration features. Moreover, the flexibility of the configurable and portable design provides an opportunity to obtain the architecture with features not available in general purpose processor architectures.

The motivation of this project is to develop a configurable microprocessor architecture independent of the target technology. This architecture facilitates the optimization of the microprocessor architecture for a specific user application. The choice of the microprocessor architecture is provided by the set of user selectable features.

The application set of the proposed microprocessor architecture may include the following:

- The applications where operation with non-standard data bitwidth (256+) is required

- The applications with limited number of the allocated hardware resources

- The algorithm intensive low speed applications where implementation of Finite State Machine (FSM) is very complicated.

- The prototyping applications where the portability of the design is critical

The terms processor and microprocessor are used in this project to identify the same object, since in modern technical literature the term microprocessor is frequently contracted to just a processor.

2

## 1.2 Objectives and Contributions

The focus of this project is to develop, implement, and verify a portable configurable RISC processor architecture. The following goals are to be achieved in this project:

- To develop a processor architecture configurable for a user specification by selection of required features provided in the design.

- To implement configurable RISC processor using Verilog HDL [5] as independent module suitable for integration as a processor core in the processor-based digital systems.

- 3) To develop GUI that facilitates the choice of features for the processor configuration.

- 4) To select and implement a testbench for verification of generated processor configurations.

- 5) To generate a set of the distinguished processor configurations.

- 6) To verify the set of generated processor configurations.

- 7) To verify the portability of the design by implementing the set of processor configurations on several FPGA and ASIC platforms.

- 8) To implement one processor configuration in hardware using FPGA development board.

- 9) To test and verify the demo application on the FPGA development board.

The following contributions were made into the development of the Portable and Configurable RISC Processor Architecture project:

- 1) The development of the specific tool for the conversion of the compiled software code into Verilog HDL.

- 2) The conduction of the literature review on the configurable processor systems.

- The development of the specific design flow for the configuration and implementation of the proposed processor architecture

- 4) The development of the Configuration Manager, the GUI-based tool for the facilitating the right choice of the configuration options of the proposed processor architecture

- 5) The development and implementation of the Verilog description of portable and configurable processor design based on the MIPS processor architecture.

- 6) The development and implementation of the demonstration example implementing the proposed processor design as a part of the Fibonacci number computation and visualization system.

- The utilization of the proposed processor configuration framework as an educational platform for the processor organization teaching courses.

### **1.3** Project Organization

The rest section of the project is organized as follows:

Chapter 2 provides a background on the processor architecture and reviews related research studies.

Chapter 3 describes the design of the proposed configurable processor. The chapter shows implementation of configurable features for different processor architectures. The development of support software tools is also covered in this chapter.

Chapter 4 describes synthesis and implementation of the processor core on different hardware platforms i.e. FPGA and ASIC. Various combinations of configurable features and processor architectures implemented on different platforms create an exploration space. The chapter shows the subset of variants in that space. The included demo design illustrates a practical utilization of the processor core.

Chapter 5 describes the verification methods used to prove the functionality of the design on behavioral and hardware levels. The development of the testbenches and their properties are discussed and analyzed.

Chapter 6 analyzes results of the processor implementation on different platforms. Implementation of the processor variants are compared and evaluated.

Chapter 7 summarizes the conducted work and accomplishments of this project.

## Chapter 2

## Background

### 2.1 Introduction

In this chapter the relevant background in the processor architecture is presented. The chapter focuses on the description of MIPS RISC processor which is adopted as a base architecture for this project. The following sections review the research development in the area related to the project theme. The state-of-art of research and commercial configurable processors is outlined and analyzed in order to determine a niche taken by the presented project in a domain of available solutions.

### 2.2 Basic MIPS Processor Architecture

J. L. Hennessy et al. designed MIPS (Microprocessor without Interlocking Pipe Stages) in 1981. It was a result of their research of the processor architecture optimization for pipelining. The MIPS architecture proposed in [6] was used as a teaching example in their classical academic textbook [7] about the processor architecture design. Nowadays MIPS is widely used for the educational purposes [8].

Further development of MIPS architecture brought a row of the revisions of this architecture MIPS-I, MIPS-II, MIPS-III, MIPS-IV, MIPS32, MIPS64 [9]. The major market of the latest MIPS processor is embedded applications. They are implemented in numerous Cisco and Linksys routers, ADSL modems, Sony PlayStation 2, Sony Playstation Portable and many handheld computers[10] [11].

The choice of the MIPS processor architecture as a template for the configurable processor design in this project is justified by following reasons. The MIPS pipeline structure and organization is very well studied and described [12][13]. The MIPS microprocessor becomes very popular for academic purposes. Many researchers implemented [14][15] and enhanced it [16][17]. Therefore, the modification of the existing simple MIPS to a

5

configurable architecture is easier than modification of a sparely specified commercial processor. As any processor with unique instruction set, MIPS requires a custom software compiler. In order to complete the set of development tools for the MIPS, several open-source compilers and simulators have been developed [18][19]. Utilization to the open source software tools facilitates the development of the configurable processor.

The classic pipelined or unpipelined MIPS is a 32-bit RISC processor. The instruction set has 32-bit width for all instructions. Load/store MIPS Instruction Set Architecture (ISA) contains register file, which consists from 32 registers 32 bits long each. Two of them are assigned as special purposes registers. Register 0 is read-only and carries 0 values. It is used as a zero operand eliminating necessity to keep zero value in memory. Register 31 is used by special jump instructions to store return address. These instructions are used for calls and returns from subroutines. MIPS program counter has a width of 32 bit similar to the data path. The potential MIPS address space is up to 2 GB.

MIPS instructions are divided into three types *R-type*, *I-type* and *J-type*. The instruction format is shown in Table 2.1. R-type defines instructions operating with registers only. The instruction contains addresses of two operand registers *Rs* and *Rt*, address of the destination register *Rd* for result storing and the code of the executed operation. The I-type instruction also contains *Rs* and *Rd* but instead of the second source register it carries the 16-bit constant value *immediate*. This constant is used as an operand in arithmetic operations and as an address offset in load/store operations. J-type instructions represent *jumps* which change the program counter with 26-bit *address* enclosed in the instruction.

The instruction opcode has 6-bits width with possible opportunity of 64 basic operations. This instruction spare space allows adding of extended instructions such as FPU support. The simplified instruction set of MIPS processor is shown in Table 2.2. The basic set includes only two branch, four jump, and two memory instructions. Other instructions are arithmetical.

The supported data types are 8-bit bytes, 16-bit half words, and 32-bit words for integer data. Bytes and half words are loaded into 32-bit in two ways: extra bits are filled with sign extension or with zeros. After the load transaction they are processed as 32-bit integer operands.

#### Table 2.1. MIPS instruction format

•

| Format |     | Bits |    |    |         |              |    |    |     |    |     |     |

|--------|-----|------|----|----|---------|--------------|----|----|-----|----|-----|-----|

|        | 31  | 26   | 25 | 21 | 20      | 16           | 15 | 11 | 10  | 6  | 5   | 0   |

| R-type | opc | ode  | F  | ۲s |         | Rt           |    | Rd | sha | mt | fur | nct |

| I-type | opc | ode  | F  | ۲s |         | Rt immediate |    |    |     |    |     |     |

| J-type | opc | ode  |    |    | address |              |    |    |     |    |     |     |

#### Table 2.2. MIPS instruction set

•

| Instr. | Description                    | Format | Opcode/    | Operation (Verilog-style coding)                         |

|--------|--------------------------------|--------|------------|----------------------------------------------------------|

|        |                                |        | Func (hex) |                                                          |

| add    | Add                            | R      | 0/20       | R[rd]=R[rs]+R[rt]                                        |

| addi   | Add Immediate                  | I      | 8          | R[rt]=R[rs]+SignExtImm                                   |

| addiu  | Add Imm.<br>Unsigned           | I      | 9          | R[rt]=R[rs]+SignExtImm                                   |

| addu   | Add Unsigned                   | R      | 0/21       | R[rd]=R[rs]+R[rt]                                        |

| sub    | Subtract                       | R      | 0/22       | R[rd]=R[rs]-R[rt]                                        |

| subu   | Subtract<br>Unsigned           | R      | 0/23       | R[rd]=R[rs]-R[rt]                                        |

| and    | And                            | R      | 0/24       | R[rd]=R[rs]&R[rt]                                        |

| andi   | And Immediate                  | I      | c          | R[rt]=R[rs]&ZeroExtImm                                   |

| nor    | Nor                            | R      | 0/27       | R[rd] = (R[rs]]R[rt])                                    |

| or     | Or                             | R      | 0/25       | R[rd]=R[rs] R[rt]                                        |

| ori    | Or Immediate                   | I      | d          | R[rt]=R[rs] ZeroExtImm                                   |

| xor    | Xor                            | R      | 0/26       | R[rd]=R[rs]^R[rt]                                        |

| xori   | Xor Immediate                  | I      | e          | R[rt]=R[rs]^ZeroExtImm                                   |

| sll    | Shift Left<br>Logical          | R      | 0/00       | R[rd]=R[rt]< <shamt< td=""></shamt<>                     |

| srl    | Shift Right<br>Logical         | R      | 0/02       | R[rd]=R[rt]>>shamt                                       |

| sra    | Shift Right<br>Arithmetic      | R      | 0/03       | R[rd]=R[rt]>>>shamt                                      |

| sllv   | Shift Left<br>Logical Var.     | R      | 0/04       | R[rd]=R[rt]< <r[rs]< td=""></r[rs]<>                     |

| srlv   | Shift Right<br>Logical Var.    | R      | 0/06       | R[rd]=R[rt]>>R[rs]                                       |

| srav   | Shift Right<br>Arithmetic Var. | R      | 0/07       | R[rd]=R[rt]>>>R[rs]                                      |

| slt    | Set Less Than                  | R      | 0/2a       | R[rd] = (R[rs] < R[rt])?1:0                              |

| slti   | Set Less Than<br>Imm.          | I      | a          | R[rt]=(R[rs] <signextimm)?1:0< td=""></signextimm)?1:0<> |

| sltiu  | Set Less Than<br>Imm. Unsign.  | I      | b          | R[rt]=(R[rs] <signextimm)?1:0< td=""></signextimm)?1:0<> |

| sltu   | Set Less Than<br>Unsigned      | R      | 0/2b       | R[rd]=(R[rs] <r[rt])?1:0< td=""></r[rt])?1:0<>           |

| beq    | Branch On                      | I      | 4          | if(R[rs]==R[rt]) PC=PC+4+BranchAddr                      |

|      | Equal         |   |      |                                     |

|------|---------------|---|------|-------------------------------------|

| bne  | Branch On Not | 1 | 5    | if(R[rs]!=R[rt]) PC=PC+4+BranchAddr |

|      | Equal         |   |      |                                     |

| j    | Jump          | J | 2    | PC=JumpAddr                         |

| jal  | Jump And Link | J | 3    | R[31]=PC+8; PC=JumpAddr             |

| jr   | Jump Register | R | 0/08 | PC=R[rs]                            |

| jalr | Jump And Link | R | 0/09 | R[31]=PC+8; PC=R[rs]                |

|      | Register      |   |      |                                     |

| lui  | Load Upper    | Ι | f    | R[rt]={imm,16'b0}                   |

|      | Imm.          |   |      |                                     |

| lw   | Load Word     | I | 23   | R[rt]=M[R[rs]+SignExtImm]           |

| sw   | Store Word    | Ι | 2b   | M[R[rs]+SignExtImm]=R[rt]           |

SignExtImm =  $\{16\{immediate[15]\}, immediate\}$  – extension of the immediate operand with the sign bit;

ZeroExtImm =  $\{16\{1b'0\}, immediate\}$  - extension of the immediate operand with "0" bit; BranchAddr =  $\{14\{immediate[15]\}, immediate, 2'b0\}$  - extension of the immediate operand with the sign bit and multiplication by 4;

JumpAddr = {PC[31:28], address, 2'b0 } – concatenation of the immediate operand with four MSBs of program counter and multiplication by 4;

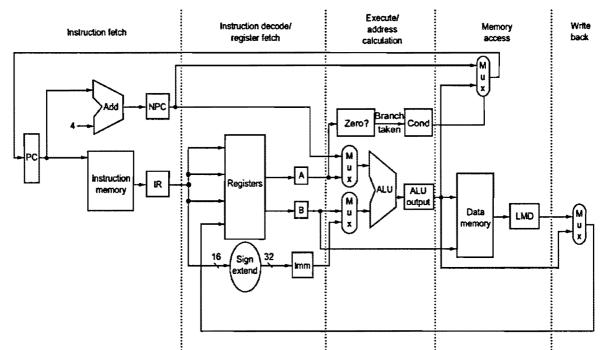

The ISA architecture of MIPS defines the organization of the processor data path. The simplified 5-cycle implementation without pipeline is shown in Figure 2.1. The following actions are performed during each cycle:

```

1. Instruction fetch cycle (IF):

IR \leftarrow \text{Mem}[PC]

NPC \leftarrow PC + 4

2. Instruction decode/register fetch cycle (ID):

A ← Regs[IR6..10];

B ← Regs[IR11..15];

Imm ← ((IR16)16##IR16..31

3. Execution/effective address cycle (EX):

ALUOutput \leftarrow A + Imm;

or

ALUOutput \leftarrow A func B;

or

ALUOutput ← A op Imm;

or

ALUOutput ← NPC + Imm;

Cond \leftarrow (A op 0)

4. Memory access/branch completion cycle (MEM):

LMD ← Mem[ALUOutput]

or

```

```

Mem[ALUOutput] ← B;

if (cond) PC ← ALUOutput

5. Write-back cycle (WB):

Regs[IR16..20] ← ALUOutput;

Regs[IR11..15] ← ALUOutput;

Regs[IR11..15] ← LMD;

```

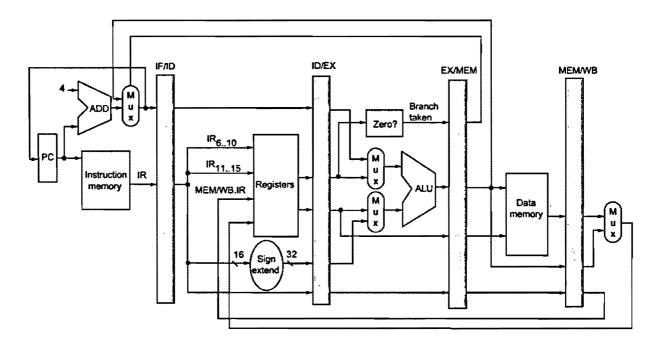

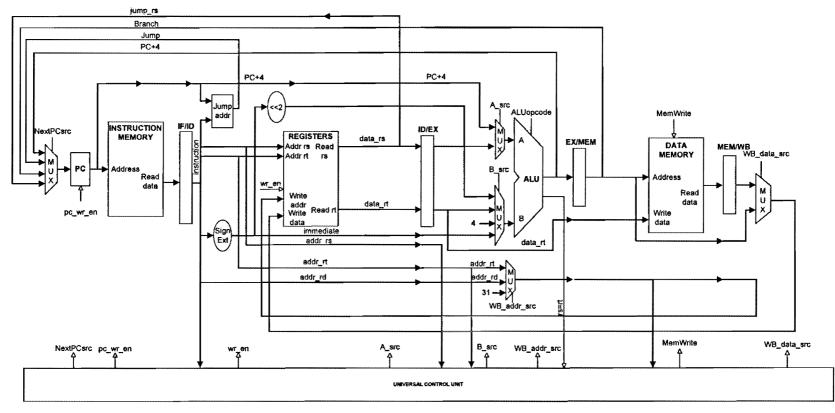

The design of MIPS is refined for pipelining. The multi-cycle version of the MIPS can be smoothly augmented with a pipeline. In a pipelined architecture all instructions are executed in the same number of cycles. This organization allows one instruction per cycle throughput. The block diagram of the pipelined MIPS processor is shown in Figure 2.2. The standard MIPS processor incorporates 5-stages pipeline. A drawback of pipelining is hazards. The most common type of hazard is the data hazard. The data hazard is a situation when a fetched instruction reads the same operand as one of preceding instructions writes. If the preceding instruction still propagates through the pipeline, the fetched instruction may read a wrong value. This data hazard is called Read-After-Write (RAW). There are two ways to handle data hazard – stalling and forwarding. Stalling means an artificial insertion of NOP instruction in the pipeline. The processor stalls the pipeline until a hazard is over. This technique results in wasting of processor clock cycles. Whereas, the forwarding does not have that disadvantage. Forwarding uses the pipeline property when the result of the instruction is available in one of pipeline stages but not written yet in a register. An additional hardware supports forwarding of the result to the stage to another stage where it is required. Another type of hazard, the control hazard is caused by branch instructions. The next fetched instruction after a branch may not be executed due to a result of branching. This would cause the pipeline to flash its contents and to stall. As a result the processor's speed slows down which is called the branch penalty. There are many methods to reduce the branch penalty. The simplest is a delay slot. It is efficient when delay penalty is one clock cycle. An execution algorithm of the processor with delay slot presumes that a next instruction after the branch is executed regardless of the branching result, whether the branch is taken or not. The compiler has to reorder the instructions and put in the delay slot an instruction which is to be executed despite a result of the branch instruction.

Figure 2.1. Block diagram of the multi-cycled MIPS processor.

Figure 2.2. Block diagram of the pipelined MIPS processor

#### 2.3 Closely Related Work

Two major approaches to automatic processor synthesis can be distinguished nowadays. One of them is template-based configurable processors. This methodology is mostly exploited by commercial products. The other one generates Application Specific Instruction set Processor (ASIP) based on Architecture Description Language (ADL) – a specific language developed for a processor architecture description.

#### 2.3.1 Architecture Description Languages

Originally ADL was developed as a high level of abstraction description language for modeling processor's architectures. VHDL and Verilog languages do not completely suit for this purpose due to their orientation toward the hardware implementation.

Several ADLs were created in attempt to find the best way for processor architectural exploration and evaluation. One of them is nML which has been developed at TU Berlin [20]. This language is intended for automatic generation of the software tools for an explored processor architecture. In order to obtain a complete processor design, the developer has to create the separate ADL model and HDL description of the processor. It has limited ability to handle invalid instructions and can not describe architectures with parallel instructions [21]. A lack of the hardware generation feature in nML has been recently amended in its enhanced version Sim-nML [22]. A synthesizable Verilog description can be obtained with Structural Sim-HS tool included in Sim-nML. Generation of the processor RTL description from Sim-nML specification has been successfully tested with specifications of the microcontroller Motorola 68HC11 and microprocessor Intel 8085. Performance of the synthesized architecture has not been estimated.

Similar to nML, ISDL architecture description language was developed by MIT LCS [23]. ISDL is instruction set specific language, specifically oriented toward Very Long Instruction Word (VLIW) processor architectures. However, multi-cycle and multi-word instructions are not fully supported by ISDL. GENSIM system software automatically generates Instruction Level Simulator (ISL) specific to the developed architecture. The ISL is capable to simulate cycle-accurate and bit-true execution of the program. The achieved speed-up of such simulation compared to the simulation of the Verilog model is 34x [24]. Lately, HGEN tool has been developed in order to automatically generate Verilog RTL model from ISDL description [25].

The language EXPRESSION [26] is capable to describe correctly multi-cycle and multiword architectures. A characteristic feature of EXPRESSION is the partition of the design flow into two phases. Evaluation and exploration of the chosen architecture is performed in Exploration Phase. This phase is supported by Exploration Simulator and Exploration Compiler automatically generated by the software itself. The compiler and simulator allow rapid comparative estimation and simulation of candidate processor architectures. A chosen solution is finally adjusted in Refinement Phase. The software toolkit generates an optimized Instruction Level Parallelism (ILP) compiler and a cycle-accurate simulator from EXPRESSION description. Using these tools the developer may perform detailed processor evaluation and verification of memory hierarchy (e. g. cache, TLB). The link to RTL synthesis is provided by the HDLGen tool [27][28] which generates the VHDL model from the EXPRESSION description. In order to test results, the automatically synthesized DLX processor [29] has been compared to its hand-written version. Despite 20-40% worse results in terms of speed, power consumption, and area, it is shown that the design time is an order of magnitude less. The paper, however, do not compare the development efforts for the processors with reported degraded performance designed manually and automatically.

One of the most prominent and widely used ADL is Language for Instruction-Set Architectures (LISA) [30]. Due to its C-like syntax, LISA is very attractive for architect designers who are beginners in utilization of ADL for ASIP development. The structure of LISA allows a designer to specify details sufficient for automatic generation of the software tools set containing compiler, assembler, linker, and simulator. These tools are used in the stage of exploration of the developed processor architecture. During this phase a designer can tune and verify designed processor by changing the ADL description. Repetition of the development environment [31][32]. LISA description contains enough architectural information for generating a synthesizable HDL model.

The advantage of architectural exploration using LISA description inspired founders to develop the integrated LISA Processor Design Platform (LPDP) [33]. Efficiency of the LPDP has been evaluated on the example of ICORE processor. This ASIP processor is oriented

toward FFT realization, sampling-clock synchronization for interpolation and carrier frequency offset calculation. The handwritten version of ICORE has been compared with the automatically generated version. The generated ICORE shows the same clock speed, 1% area overhead, and 15% more power consumption. Design efforts for LPDP ICORE are approximately one month and a week vs. three months for the original handwritten version.

LPDP has apparent advantage of a fully developed and integrated system for ASIP design. The convenient user interface and support of different operational systems [34] distinguishes it from general research projects, where the integrated environment accelerates the exploration of various processor architectures. Performance of the LPDP generated processors can compete with commercial handwritten versions. However, the necessity of manual development of a processor data path diminishes the advantages of this system.

The advantages of utilizing LISA ADL have been recognized by many researchers. LISA has been used as a base ADL for numerous research projects focused on ASIP development [35][36][37]. High level of LISA development has stimulated its implementation in a commercial processor generation system. LISA 2.0 is used by CoWare company in CoWare Processor Designer [38]. This platform is dedicated for design and optimization of ASIP. LISA 2.0 architectural description was used to generate a full set of processor software tools and the RTL description in Verilog, VHDL, and SystemC. This commercial processor development system lately has been used in several ASIP research projects [39][40] for rapid processor architecture exploration.

#### 2.3.2 Configurable Processors

The concept of flexible microprocessor architecture is exploited by many authors. Two major approaches can be distinguished: *configurable* and *reconfigurable* processors [41][42]. The term configurable presumes customization before manufacturing. Whereas, the reconfigurable processor implies configurability after manufacturing. Runtime dynamic changing of the configuration is a powerful feature of the reconfigurable architecture. This approach offers reuse of the same silicon design by multiple applications without additional manufacturing cost. Examples of the reconfigurable microprocessors are shown in [43][44]. These designs represent multiple computing units connected by a sophisticated reconfigurable network. Narrow reconfiguration ability is implemented in the computing units as well. Due

to implementation of the described processors using technology process, their flexibility is limited.

Configurable processors became very popular last decade. They can be divided into soft and hard-processors. Hard processors are intended for Application-Specific Integrated Circuit (ASIC) implementation. Xtensa LX3 offered by Tensilica [45] is an example of commercial configurable processors. This is 32-bit RISC ISA processor that allows the designer to perform the configuration by choosing predefined options from the menus. The following main groups of features can be added and tuned for Xtensa LX3:

- Execution Unit and ISA Options (multipliers, DSP engines, FPU, custom instructions, etc.)

- Interface Options (DMA, FIFO, GPIOs, interrupts, debug port, etc.)

- Memory Subsystem Options (caches, memory management unit (MMU), parity, cache organization, etc.)

The chosen configuration of the processor is automatically processed by Xtensa Processor Generator software. The complete solution is represented by the RTL description and EDA scripts. The example of the configurability of Xtensa processor is demonstrated in implementation of the multi- standard video decoder [46]. Two different processor configurations are used to create the stream processor and pixel processor. Each processor is enhanced with specific video instructions. The optimized ISA architecture of the processors allows video decoding in the software only.

A similar set of configurable features is proposed by the ARC for the ARC 600 Core and ARC 700 Core processor families [47][48]. ARChitect Processor Configurator [49] extends the processor design with Single Instruction Multiple Data (SIMD) instructions, integrated coprocessor instructions, compound instructions and many others. More than 20,000 preconfigured options can be selected by the developer.

The explicit benefit of these processor systems is that their template-base synthesis does not require an extensive knowledge of the processor architecture. A developer can obtain fully functional ASIP from a specification with very high level of abstraction. Rapid automatic synthesis allows fast evaluation of several solutions and optimization of the final ASIP. Flexibility of the template-based processor architecture is limited by the set of the predefined options which is not always suitable for research projects. Along with commercial configurable products numerous research projects show interesting results in this field. Advantages of the implementation of Dolby Digital (AC-3) decoder with the hard configurable processor are shown in [50]. The paper convincingly proves that utilization of the configurable processor tuned for the specific audio application increases performance of the processor and reduces the required size of the die.

Very fast growth of the FPGA performance and density accompanied with sophisticated development tools has made FPGA devices very attractive for the implementation of a processor architecture. Reprogrammable nature of FPGA determines the definition of the processor implemented in FPGA as a soft processor. Therefore, it is not a surprise that the most well-known configurable soft processors are offered by major FPGA vendors Xilinx and Altera. Xilinx promotes 32-bit RISC soft-processor Microblaze [51] with configurable peripherals. It has limited configurable abilities for the core structure. This soft processor is proposed as alternative to the hard-processor core PowerPC 440 [52] implemented in the Xilinx Vertex-5 FXT FPGA family. Table 2.3 shows the performance of the MicroBlaze processor for different FPGA families.

| Architecture | Performance    | Maximum Clock          | Maximum Dhrystone 2.1 |

|--------------|----------------|------------------------|-----------------------|

|              |                | Frequency              | Performance           |

| 5-Stage      | 1.19 DMIPs/MHz | 235 MHz in Virtex®-5   | 280 DMIPS             |

| Pipeline     |                | FXT                    |                       |

| 3-Stage      | 0.95 DMIPs/MHz | 106 MHz in Spartan®-3A | 100 DMIPS             |

| Pipeline     |                | DSP                    |                       |

Table 2.3: MicroBlaze Processor v7.2 Performance Levels

Along with high-end Microblaze processor Xilinx developed Picoblaze 8-bit Picoblaze soft processor [53] with no options for the configurability. Source code is open for evaluation and modification. The HDL model is offered on very low gate level description. Picoblaze can be implemented only on Xilinx FPGA platform. It became very popular due to its simplicity, free distribution, and availability of software tools. Popularity of Picoblaze inspired Bleyer [54] to develop Pacoblaze – a behavioral version of Picoblaze. This model incorporates maximum level of parameterization. The high level definition file represents a wizard for implementation of the possible versions of Pacoblaze. Low level definitions files comprise a hierarchical ladder, which an experienced user can employ for configuration of a

custom version of the Pacoblaze architecture. Using Verilog optional compilation the author has created the specific configuration language, which supports a variety of custom configurations.

Xilinx major competitor Altera offers Nios II – second generation of Altera's soft processors [55]. It is 32-bit RISC general purpose processor with 32-bit width instruction set similar to MIPS. Altera offers Nios II in three different configurations: economy (e), standard (s) and fast (f). Table 2.4 outlines specific features of each configuration. All versions allow adding up to 256 custom instructions. The choice of the required configuration is supported by SOPC Builder software. The resulting configuration is generated in a form of FPGA programming file.

| Processor Version |             | Nios II/e | Nios II/s | Nios/f   |

|-------------------|-------------|-----------|-----------|----------|

|                   | DMIPS/MHz   | 0.16      | 0.75      | 1.17     |

| Performance       | Max DMIPS   | 28        | 120       | 200      |

|                   | Clock (MHz) | 150       | 135       | 135      |

| Area              | LEs         | 600       | 1300      | 1800     |

| Pipeline          |             | unpiped   | 5         | 6        |

| Branch            | Prediction  | -         | static    | dynamic  |

| ALU               | Multiplier  | -         | 3-cycle   | 1-cycle  |

|                   | Divider     | -         | -         | optional |

|                   | Shifter     | serial    | 3-cycle   | 1-cycle  |

Table 2.4. Nios II different version features.

The idea of modification of the commercially successful soft processors lies in the basis of UT Nios soft processor [56]. It is an attempt to use a different approach of configurability of the Altera Nios II. In contrast to original Nios II, UT Nios has optional 16/32-bit data path width and reduced 16-bit instruction word width. Instruction set supports five custom instructions. The register file has a configurable size with 32 visible registers window. There is an option of integer multiplication. Benchmark evaluation shows insignificant 1% average and 56% for particular applications speed-up. UT Nios requires 31% more FPGA resources than Altera Nois II.

Another attempt to use Altera Nios II architecture for the research project is UTMT II [57]. The design exploits the multithread processor architecture using different UTMT II

configurations with multiprocessor core structure. Despite the poorer performance then Altera Nios II, an advantage of the 45% area saving has been reported.

Four stages pipeline is used in UWindsor Nios II (UWN2) [58], another Altera Nios II compatible soft processor. The parameterization of the UWN2 is limited to 10 options. The best achieved area saving is 47%, while the clock speed is 7% worse than Nios II.

The success of commercial soft processors does not discourage numerous researchers to develop other configurable soft processor architectures. The example of a very well developed and tested configurable processor is LEON3 [59]. This 32-bit processor core is designed as synthesizable VHDL model compatible with SPRC V8 architecture. The open source design offers many configurable options for the optimization. The portability of the design is verified for Altera and Xilinx FPGA platforms on multiple development boards. The LEON3 is also suitable for ASIC implementation. The best achievable clock speed is 140 MHz for FPGA platform and 650 MHz for ASIC. The hardware design is supported by a set of software development tools including simulator, compiler, linker, Newlib embedded C-library, Eclipse based IDE, etc.

The general purpose traditional processor architecture is focused on the execution of different applications of the same hardware. While most of embedded processors run only one specific application. The Application Specific Instruction-set Processor (ASIP) incorporates an idea of optimization of the processor architecture according to a running task. This approach significantly improves performance and speed of the processor. Due to a high cost of implementation of ASIP in ASIC devices, the usage of FPGA for ASIP becomes very attractive. The design of video-processor [60] demonstrates the implementation of ASIP in FPGA. The targeted Altera Nios II/f processor core is augmented with the custom hardware for block manipulation. The efficient data reuse achieves three order of magnitude acceleration compared to software implementation.

2

Instruction Set Extensions (ISE) is another approach to optimization of ASIP architecture. The design of the E-ASIP (ETRI-Application Specific Instruction Processor) for the CAVLC of H.264/AVC decoder [61] uses this technique. In order to improve the processor performance for the specific function, the instruction set is extended with additional special purpose instructions. The number of basic instructions is reduced down to the minimum set required for the functionality. Exploration of the different aspects of processor configurability is performed in the SIxD application-specific soft processor [62]. The processor incorporates several configurable options, such as length and width of the data space, custom branching and shifting instructions, ability to choose subset of instructions and the choice of SIMD mode. The design has been successfully tested with MPEG-7 Motion Activity Descriptors application.

Aside from the traditional RISC ISA architecture stands CUSTARD (CUStomizable Threaded Architecture) - a customizable threaded FPGA soft processor [63]. The available configurable features include data path width, number of threads, threading type, custom instructions, custom memory blocks, forwarding, and register file parameterization. The design is supported by the custom C-compiler developed by the authors. Reported evaluation results show a significant 2.41x average speed-up of the single-treaded CUSTARD with custom instructions compared to Xilinx Microblaze. The disadvantage of the considered processor is a twice larger area overhead.

The versatility of configurable processors shows the necessity of the performance evaluation for different configurations. Such estimation has been fulfilled using Softprocessor Rapid Exploration Environment (SPREE) [64]. This system is able to generate RTL description of the soft processor from the high level architecture description. The SPREE base configurable core is similar to MIPS and Altera Nios II processors. The textual description of the processor data path and ISA are used as an input for SPREE. Multiple generated processors were benchmarked and compared with all three versions of Atera Nios II e/s/f. The best variants show the same or better performance than Nios II. For example, 80- MHz three-stage pipelined processor generated by SPREE is 9% smaller and 11% faster than Nios II/s. The study examines the influence of different processor architectural features on the performance. The impact of the following options is investigated: shifter implementation, multiplication support, pipeline depth, pipeline organization, forwarding, application-specific architecture customization, and ISA subsetting. The optimized processors achieve improvement of the performance per area 24.5% on average. Saving of the power and area is obtained 25% on average.

# 2.4 Summary

In this chapter, the main concept of RISC processor architecture is presented. The MIPS processor specification and architecture are described. The related configurable solutions in the form of soft and hard processors are studied and analyzed. The complementary software tools are outlined and examined for the reviewed processors.

# Chapter 3

# **Configurable Processor Proposed Design**

This chapter describes the structural components of a configurable processor design and high level design of the processor data path. It also illustrates the design of the processor's control unit.

The data path design of the configurable MIPS processor is organized in the following sequence:

- 5-stages pipelined architecture

- 4-stage pipelined architecture

- Multi-cycle unpipelined architecture

- One-cycle unpiplined architecture

The methodology of the design of configurable processor architecture in this project differs from the classical approach described in [12]. The classical approach does not presume the configurability of the described processor architecture. The evolution from the simplified form to the more complex is chosen for the educational purpose in order to facilitate understanding. Instead of this approach, here the most complicated design is taken as an initial and gradually modified to reach the simplest. The most complicated design contains the majority of the components present in other architectures, therefore it is logical to use this design for the transformation into other architectures.

The 5-stage architecture is the most advanced and complicated design with maximum hardware overhead. All other architectures are derivatives from the initial 5-stage pipelined architecture. The configuration options control transformation of the initial design toward other three architectures. The major structural components are shared in all data path architectures. Components pertained only to a specific architecture included as options controlled by the configuration engine.

Since the control unit design highly depends on the data path realization, the control unit design has limited configurability. The control unit is unique for each of the four types of

architectures. The choice of the appropriate control unit is also supported by the configuration engine.

# 3.1 Datapath Components

# 3.1.1 ALU

In order to support MIPS instruction set, ALU is designed to have the capability of performing operations with two input operands A, B. Table 3.1 shows the correspondence between ALU operations and supported MIPS instructions.

Table 3.1: Supported ALU operations

| ALU Operation                                                    | MIPS Instructions              |

|------------------------------------------------------------------|--------------------------------|

| Addition (result = A+B)                                          | add, addu, addi, addiu, lw, sw |

| Subtraction (result = A-B)                                       | sub, subu                      |

| Logical conjunction (result = A and B)                           | and, andi                      |

| Logical disjunction (result = A or B)                            | or, ori                        |

| Logical disjunction with negation (result = A nor B)             | nor                            |

| Logical exclusive or (result = A xor B)                          | xor, xori                      |

| Pass operand (result = A)                                        | jr                             |

| Load immediate to upper word (result = $B \ll 16$ ) <sup>1</sup> | lui                            |

| Logical right shift                                              | srl, srlv                      |

| Logical left shift                                               | sll, sllv                      |

| Arithmetic right shift                                           | sra, srav                      |

| Compare result to 0                                              | beq, bne                       |

| Set less than                                                    | slt, slti, sltu, sltui         |

<sup>1</sup> Shift for 16-bits applies only for classic MIPS instruction set. In general, this parameter is configurable in the design.

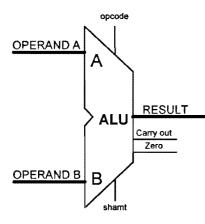

The symbol for ALU is shown in Figure 3.1. The list of the ALU signals and their description are shown in Table 3.2.

Figure 3.1: Processor ALU symbol

| Table 3.2: ALU signals |     |                                               |                                                         |  |

|------------------------|-----|-----------------------------------------------|---------------------------------------------------------|--|

| Signals                | Dir | Bitwidth                                      | Description                                             |  |

| OPERAND A              | In  | Data path                                     | First arithmetic/logic operand.                         |  |

| OPERAND B              | In  | Data path                                     | Second arithmetic/logic operand                         |  |

| RESULT                 | Out | Data path                                     | Result of arithmetic/logic opration                     |  |

| opcode                 | In  | 3 or 4 bits. Depend on<br>the instruction set | Code of the executed operation                          |  |

| shamt                  | In  | Configurable; 5 bits by default               | Shift amount. The number of bits to shift the operand B |  |

| Carry_out              | Out | 1 bit                                         | Carry out of the arithmetic operations                  |  |

| Zero                   | Out | 1 bit                                         | Produces "1" when result is equal 0                     |  |

The ALU module has a configurable bit-width and subset of operations. Support for shift commands and "Set Less Than" commands is optional and may be excluded from the design to reduce hardware overhead.

The ALU is an asynchronous device and consists of the combinational logic only.

### 3.1.2 Register File

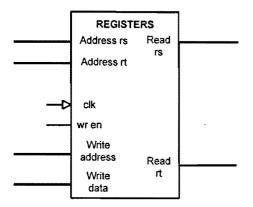

The register file design consists of 32 registers with configurable bit-width. The register with address 0 does not have memory elements. It comprises hardwired 0's. The register file symbol is shown in Figure 3.2.

#### Figure 3.2: Register file symbol

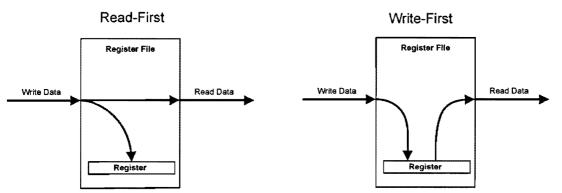

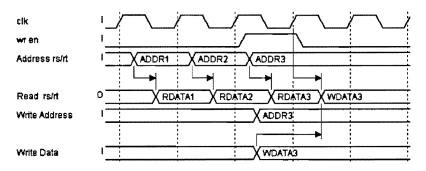

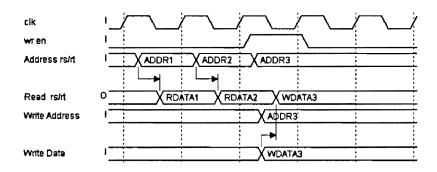

The register file module works simultaneously in write and read modes. It asynchronously produces data on two output ports from two registers which addresses are set on the corresponding address inputs. It also synchronously writes data from the *Write data* input port to the register which address is set on the *Write address* input. Writing is controlled by *wr en* signal. In order to support configurability, two writing modes are implemented: Read-First Mode and Write-First Mode. The Figure 3.3 and Figure 3.4 show the difference between these two modes. The writing mode defines the order of access in case of simultaneous read-write access to the same register. In Read-First Mode the data set on the write port immediately appears on the corresponding read output port and is written to the register later. In Write-First Mode data is written to the register on the first clock edge and only after that the data is set on the read output port. The writing mode is a configurable feature of the register file module. The timing diagrams demonstrating the difference of Read-First and Write-First modes are shown in Figure 3.5 and Figure 3.6.

Figure 3.3: Regfile Read-First block diagram

Figure 3.4: Regfile Write-First block diagram

Figure 3.5: Regfile Write-First mode timing diagram

Figure 3.6: Regfile Read-First mode timing diagram

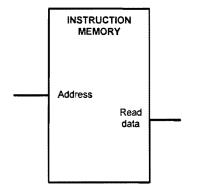

### 3.1.3 Instruction Memory

The instruction memory module is designed as an asynchronous static memory. The size and bit-width are configurable features of this module. The instruction memory has read-only access. The symbol of the instruction memory is shown in Figure 3.7. The design of the module provides the opportunity to use it as the built-in instruction memory in the microcontroller type of applications. The module also can be used as a prototype of the L1 cache design in the advanced processor applications.

Figure 3.7: Instruction memory symbol

# 3.1.4 Data Memory

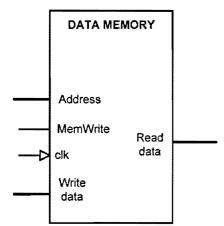

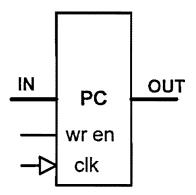

The data memory module has an asynchronous read access and synchronous write access. The writing access is enabled by *MemWrite* signal. The symbol of the data memory is shown in Figure 3.8. Due to MIPS load-store architecture, simultaneous read-write access to the same memory address in not possible. Table 3.3 shows the input/output signals of the data memory module. The timing diagram describing the read/write data memory access is shown in Figure 3.9. The size and bit-width are configurable features of this module. Similar to the instruction memory, the data memory module can used in microcontroller style applications and as a prototype of the L1 cache design.

Figure 3.8: Data memory symbol

| Table 3.3: Data memo | ry | signals |

|----------------------|----|---------|

|----------------------|----|---------|

| Signals    | Dir | Bitwidth  | Description                       |

|------------|-----|-----------|-----------------------------------|

| clk        | In  | 1bit      | Processor clock                   |

| Address    | In  | Data path | Memory address                    |

| Write data | In  | Data path | Data to be written in the memory  |

| MemWrite   | In  | 1bit      | "1" enables writing to the memory |

| Read data  | Out | Data path | Data read from the memory         |

Figure 3.9: Data memory read/write timing diagram

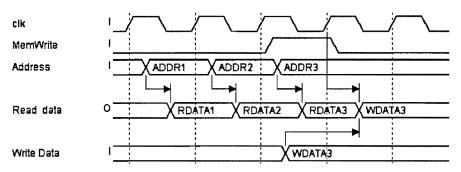

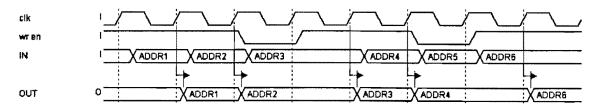

### 3.1.5 Program Counter

The program counter shown in Figure 3.10 is a register with a write enable (*wr en*) input. It holds the current instruction address. The bit-width of the program counter is configurable and depends on the size of the instruction memory. The program counter module does not have a built-in counting capability. An external adder is required for implementing the counting function. The functionality of the program counter is illustrated by the timing diagram shown in Figure 3.11.

Figure 3.10: Program counter symbol

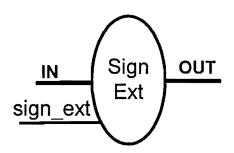

#### 3.1.6 Sign Extension

In order to support I-type of commands, MIPS architecture requires extension of the 16bit immediate operand to the bit-width of the processor datapath. In most cases it means filling the extra bits with the sign bit of the immediate operand. For commands *andi, ori, xori* it requires filling the extra bits with 0s.

The sign extension module has a configurable bit-width depending on the processor datapath bit-width. The extension mode is controlled by the input port *sign\_ext*. The module is asynchronous and contains only the combinational logic.

Figure 3.12: Sign Extension symbol

### 3.2 Control Unit Design

The control unit module contains all logic required for producing control signals for configurable architectures. The control unit design is different for all four architectures. Due to the significant variations of the processor architectures, a unified configurable design of the control unit is not feasible. Each control module comprises a unique design specific to the chosen processor architecture. The control unit is connected to the data path trough the unified interface. It consists of the same set of input and output signals. This set contains a maximum possible number of the control signals pertained to the most complicated processor configuration. Therefore instantiation of the specific control module in the chosen processor design is a call of the corresponding name of the module.

Due to redundancy in the connection interface, not all interface signals are used in the control unit design. They are just not connected to internal parts of the control unit. This does not introduce a problem since they are ignored by the synthesis tool.

All control units support the same set of instructions. The way they are decoded and handled differs in control units for different architectures. The distinguishable feature of the control module for the pipelined architectures is an internal pipelining of control signals. This internal pipelining corresponds to the pipelining of the data path. Detection and handling of all type of hazards native for a pipelined architecture occur in the control unit.

# 3.3 Pipelined Architecture Design

The design of the pipelined architecture follows the concept described in [12]. It exploits the Instruction Level Parallelism (ILP) when all stages of the processor execute different instructions simultaneously.

Configuration options for pipelined processor architecture in this project consider two architectures: five stages and four stages. The maximum number of stages can be identified as follows:

- Instruction Fetch (IF)

- Instruction Decode(ID)

- Execute (EX)

- Memory Access (MEM)

- Write Back (WB)

The designed architecture implements the following features of the pipelined MIPS processor organization:

- Branch delay slot

- Data hazards handling

- Control hazards handling

- Forwarding

In the pipelined architecture one instruction is issued every clock cycle. Therefore in the ideal situation, the throughput of the processor is equal to the clock speed. However, hazards cause the throughput to be reduced. The implementation of the branch delay slot reduces the penalty for control hazards but requires explicit support in the compiler. The data hazards are handled by forwarding and pipeline stalling. Read After Write (RAW) is the only type of data

hazard possible in the proposed pipelined architecture. The Write After Read (WAR) and Write After Write (WAW) hazards are not possible in the designed processor.

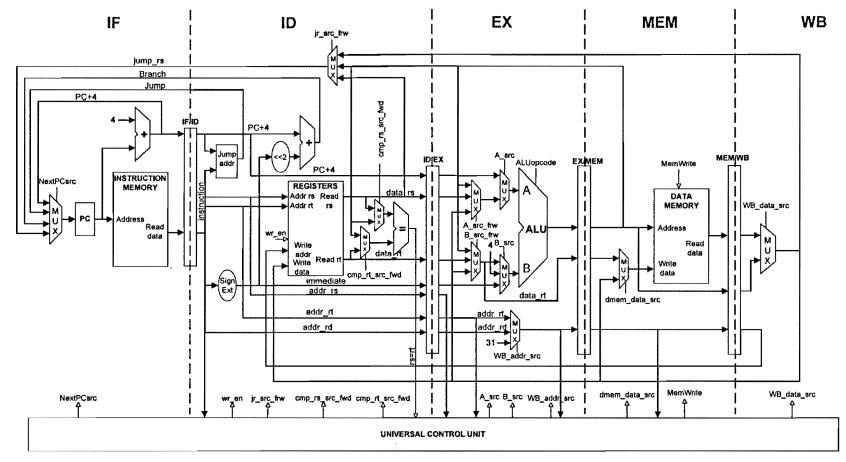

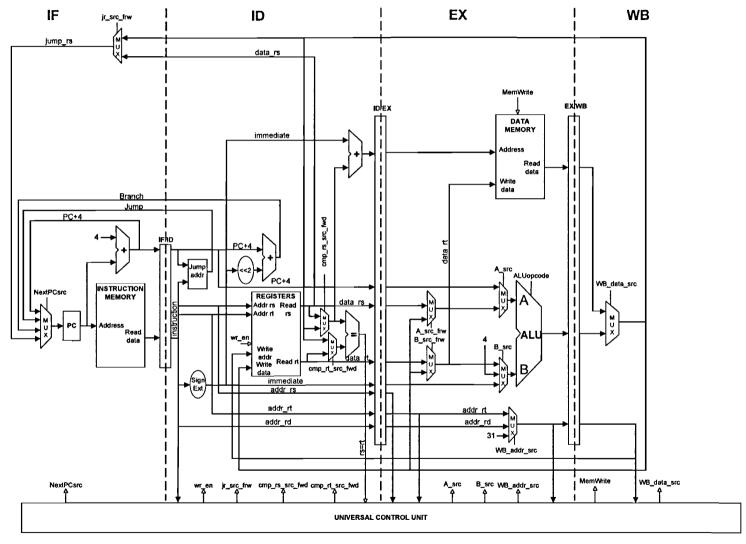

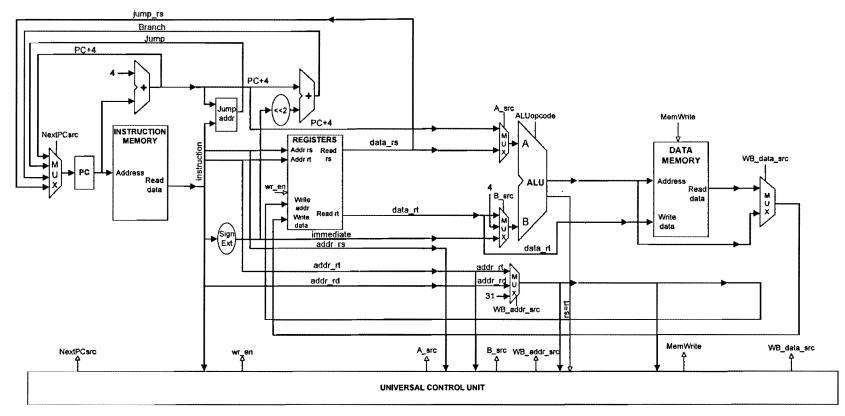

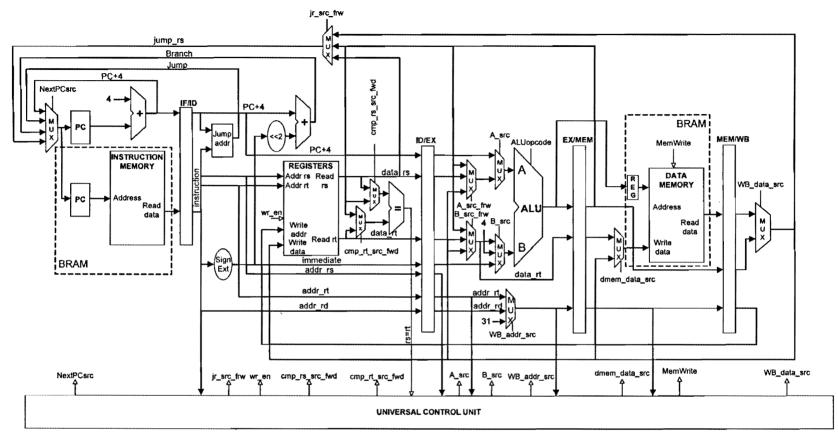

#### 3.3.1 Five Stages Pipelined Processor

The block diagram of the processor with five pipeline stages is shown in Figure 3.13. The IF stage contains program counter, instruction memory, instruction address adder and multiplexer which selects the source of the next instruction address. An issued instruction is decoded in ID stage and analyzed in the control unit. Selection of the address source of the next instruction is controlled by signals from the control unit. In case of a sequenced order of execution, the address is increased by a number of bytes in the instruction word. Though this number is a configurable option, on practice 4 bytes organization is chosen. It allows a standard instruction set and compiler to be used. In case of a taken branch or jump instruction, the next instruction address is calculated in ID stage. Since *jr* instruction uses a register for the jump address, it may introduce a data hazard. The forwarding from EX, MEM, and WB stages is used to reduce or avoid a stalling penalty for data hazards. The ID stage includes Register File, adder for the taken branch address calculation, sign extension module, and comparator for the branch decision. Implementation of a separate comparator rather than using the ALU on EX stage reduces the branch hazard penalty down to one cycle. That penalty is covered by the branch delay slot technique. A drawback of this approach is a hardware overhead required for the extra comparator and forwarding multiplexers.

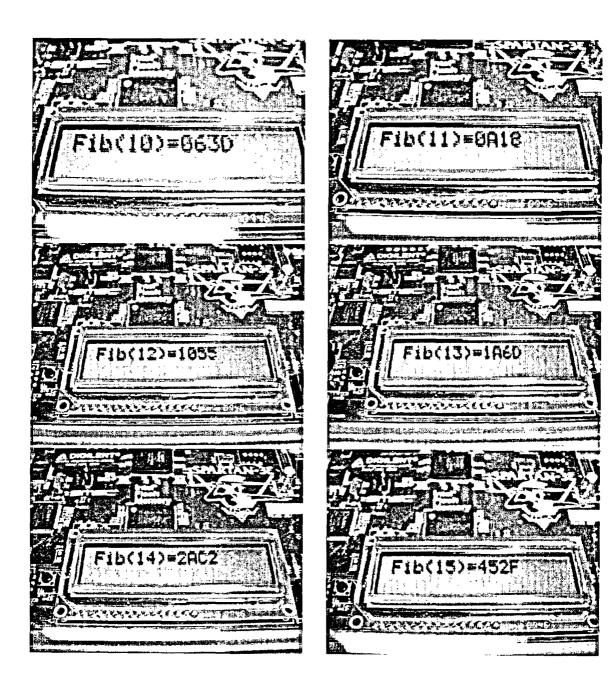

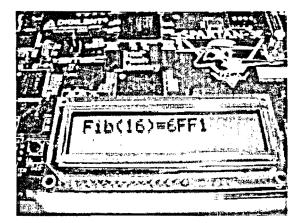

ID stage multiplexers support forwarding from EX, MEM, and WB stages. The jump address is obtained by combining lower bits from instruction and PC higher bits.