# A NEW PHASE-LOCKED LOOP WITH ACTIVE INDUCTOR RING OSCILLATOR

Mohamad El-Hage B.Eng, Ryerson University, Toronto, Ontario, Canada, 2002

> Submitted in partial fulfillment of the requirements for the degree of Master of Applied Science

Department of Electrical and Computer Engineering Ryerson University Toronto, Ontario, Canada

September, 2004

PROPERTY OF RYERSON UNIVERSITY LIBRARY

©MOHAMAD EL-HAGE, 2004

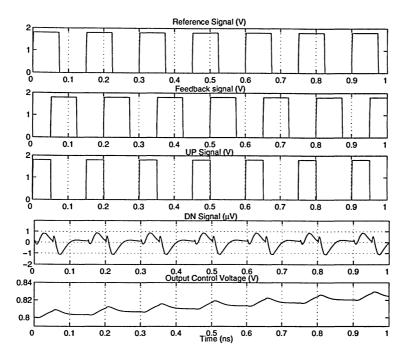

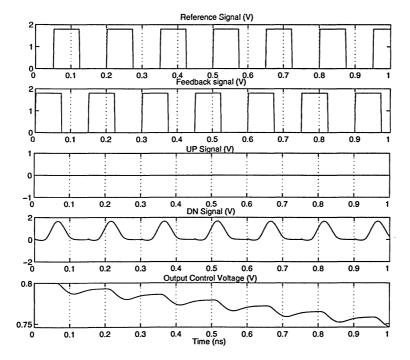

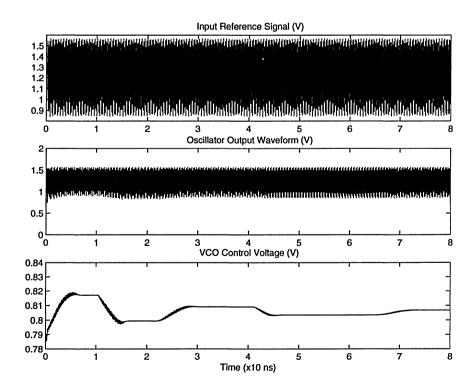

UMI Number: EC53459

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC53459

Copyright 2009 by ProQuest LLC

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Date September 30-2004

Signature

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Date September 30-2004

Signature

## Borrower's Page

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

A New Phase-Locked Loop With Active Inductor Ring Oscillator

Master of Applied Science, 2004

Mohamad El-Hage

Department of Electrical and Computer Engineering

Ryerson University

#### Abstract

Many of today's applications require that a phase-locked loop (PLL) operate at high speeds, while maintaining reasonable phase noise and jitter performance. Voltage-controlled oscillators (VCO) are important building blocks in PLLs. More importantly, the VCO is the major contributor of phase noise in a PLL. The noisy environment, mainly due to the switching noise generated by the digital portion of these systems, imposes stringent constraints on the design of VCOs, especially phase noise or timing jitter. The switching noise originated in the digital portion of the systems are coupled to the supply and ground rails of the VCO of PLLs. Another important block of a PLL is the charge-pump, a block that is responsible for generating the control voltage to be applied to the VCO. The stability or fluctuation of the control voltage, can severely affect the phase noise performance of the VCO.

The research in this thesis, centered on (i) the design considerations of CMOS charge-pumps, (ii) the timing jitter of the delay-cells of low-voltage CMOS ring-VCOs, and (iii) the design of a high-speed ring oscillator.

A PLL was designed using a new active inductor 6.3-GHz ring oscillator, with a tuning range of  $\pm 15\%$  was designed in  $0.18\mu m$  CMOS technology. The ring oscillator employed active inductor loads that resulted in an improvement of about 42% in oscillation frequency when compared to the conventional resistor loaded ring oscillator.

### Acknowledgment

I would like to thank first and foremost, my advisor Dr. Fei Yuan, for his support, guidance, and constant stream of fresh ideas through out my research made this work possible. I profoundly appreciate his enthusiasm and close interaction that inspires my exploration of integrated circuits. Moreover, I feel privileged to have had the freedom he has given me while conducting my research.

I thank all of the students in the Analog and Mixed Signal group at Ryerson University ,Jean Jiang in particular, for the numerous technical discussions that helped my research in many ways.

I am extremely indebted to Jason Naughton for the CADENCE lab support.

I would like to thank Dr. Kaamran Raahemifar, Dr. Lev Kirischian and the defense chair Dr. M. Zeytinoglu at Ryerson University for their participation in my defense.

Special thanks go to Oksana Evseeva for her gracious support and countless sacrifices that have allowed me to complete this work.

## Dedication

I dedicate this work to my parents Khodre and Fairouz El-Hage for the support and endless encouragement they have given me.

# Contents

| 1 | Inti | roduction                                | 1  |

|---|------|------------------------------------------|----|

|   | 1.1  | Motivation                               | 1  |

|   | 1.2  | Contribution                             | 2  |

|   | 1.3  | Thesis Organization                      | 3  |

| 2 | Pha  | ase-Locked Loops                         | 4  |

|   | 2.1  | Basic Topology and Function              | 4  |

|   |      | 2.1.1 Phase Detectors                    | 5  |

|   |      | 2.1.2 Voltage Controlled Oscillators     | 5  |

|   |      | 2.1.3 PLL Operating Regions              | 6  |

|   | 2.2  | Loop Dynamics                            | 8  |

|   | 2.3  | Critical Parameters                      | C  |

|   |      | 2.3.1 Static Phase Error                 | .( |

|   |      | 2.3.2 Tracking Range                     | 2  |

|   |      | 2.3.3 Acquisition Range                  | 3  |

|   |      | 2.3.4 Acquisition Time                   | 5  |

|   |      | 2.3.5 Aided Acquisition                  | 6  |

|   |      | 2.3.6 Phase Noise and Jitter             | 7  |

|   | 2.4  | Charge Pump Phase-Locked Loop CP-PLL     | 8  |

|   |      | 2.4.1 Stability                          | 0  |

|   |      | 2.4.2 Dynamics                           | 0  |

| 3 | Pha  | se-Frequency Detectors 2                 | 3  |

|   | 3.1  | Functionality and Performance Evaluators | 3  |

|   | 3.2  | Design Techniques                        | 4  |

|   |      | 3.2.1 Phase Detectors                    | 5  |

|   |      | 3.2.2 Phase-Frequency Detectors PFD      | 8  |

|   | 3.3  | Conclusions                              | 4  |

| 4 | Cha  | rge Pumps 3                              | 5  |

|   | 4.1  | Functionality                            |    |

|   | 4.2  | Non-ideal Effects                        | _  |

|   |      | 4 2 1 Mismatches 3                       |    |

|          |          | 4.2.2 Switch Induced Errors                                          |

|----------|----------|----------------------------------------------------------------------|

|          | •        | 4.2.3 Charge Sharing (OFF⇒ ON)                                       |

|          | 4.3      | Basic Charge Pumps                                                   |

|          |          | 4.3.1 Switch-at-Drain                                                |

|          |          | 4.3.2 Switch-at-Gate                                                 |

|          |          | 4.3.3 Switch-at-Source                                               |

|          | 4.4      | Current-Steering Charge-Pumps                                        |

|          | 4.5      | Differential Current-Steering Charge Pumps                           |

|          | 4.6      | Miscellaneous Charge Pumps                                           |

|          |          | 4.6.1 Charge-Pump with Active Amplifier                              |

|          |          | 4.6.2 Charge-Pump with Error Amplifier                               |

|          |          | 4.6.3 Charge-Pump with Complementary Switches                        |

|          |          | 4.6.4 Charge-Pump with AC Coupling transistors                       |

|          |          | 4.6.5 High-Speed Charge-Pump                                         |

|          |          | 4.6.6 Fully Balanced Charge-Pump                                     |

|          |          | 4.6.7 Charge Amplifier Charge-Pump                                   |

|          | 4.7      | Conclusion                                                           |

| 5        | <b>A</b> | alvsis of Supply Noise Sensitivity of VCO Delay Cells 56             |

| <b>o</b> | 5.1      | Alysis of Supply Noise Sensitivity of VCO Delay Cells  Noise Sources |

|          | 5.1      | 5.1.1 Device Noise                                                   |

|          |          | 5.1.2 Supply Noise                                                   |

|          | 5.2      | Design Considerations                                                |

|          | 0.2      | 5.2.1 Single-ended and Differential Configurations                   |

|          |          | 5.2.2 Linearity of Load                                              |

|          |          | 5.2.3 Voltage Swing                                                  |

|          | 5.3      | Simulation Results                                                   |

|          | 5.4      | Conclusions                                                          |

|          | 0.1      |                                                                      |

| 6        | Nev      | v Active Inductor VCO Delay Cell 71                                  |

|          | 6.1      | Oscillation Frequency Estimation                                     |

|          | 6.2      | Oscillation Frequency of RC Ring Oscillator                          |

|          | 6.3      | Active Inductor Loads                                                |

|          | 6.4      | Delay Cells with Active Inductor Loads                               |

|          | 6.5      | Comparative Speed Analysis                                           |

|          | 6.6      | Simulation                                                           |

|          | 6.7      | Conclusions                                                          |

| 7        | Pha      | se-Locked Loop Design 85                                             |

| •        | 7.1      | Design Procedure                                                     |

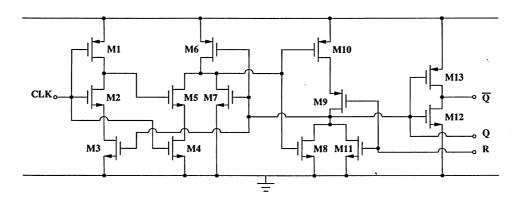

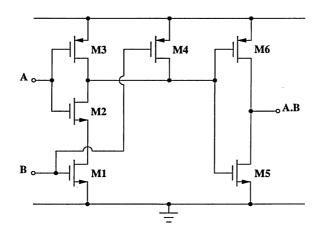

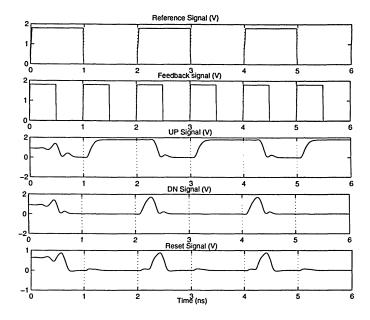

|          | 7.2      | Phase-Frequency Detector                                             |

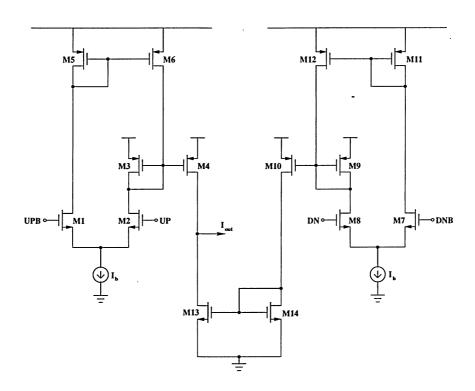

|          | 7.3      | Charge-Pump                                                          |

|          | 7.4      | Simulation Results                                                   |

|          |          |                                                                      |

| 8  | Con                                          | aclusions       | 95  |

|----|----------------------------------------------|-----------------|-----|

|    | 8.1                                          | Conclusions     | 95  |

|    | 8.2                                          | Future Research | 96  |

| Bi | bliog                                        | graphy          | 98  |

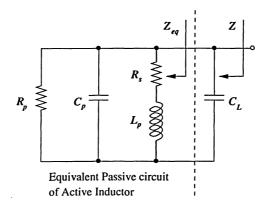

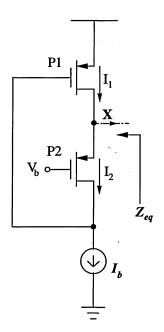

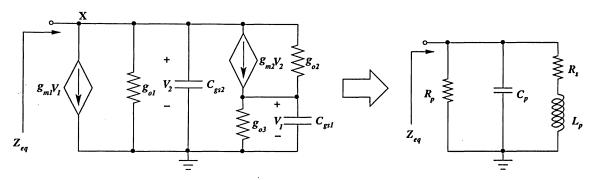

| A  | A Active Inductor and its equivalent circuit |                 |     |

| Vi | ta                                           |                 | 107 |

# List of Figures

| 2.1  | Basic phase-locked loop                                                         | 4  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Characteristic of an ideal phase detector                                       | 5  |

| 2.3  | PLL Regions of Operations                                                       | 7  |

| 2.4  | Simple low pass filter                                                          | 9  |

| 2.5  | Loop filter with an added zero                                                  | 11 |

| 2.6  | Acquisition of lock in frequency domain                                         | 13 |

| 2.7  | Acquisition of lock in time domain                                              | 15 |

| 2.8  | (L) Jitter in a periodic signal, and (R) Frequency spectrum of a signal with    |    |

|      | Phase noise                                                                     | 17 |

| 2.9  | Charge-pump phase-locked loop                                                   | 19 |

| 3.1  | Gilbert cell PD and characteristic                                              | 25 |

| 3.2  | XOR characteristic                                                              | 26 |

| 3.3  | SR-latch PD and characteristic                                                  | 27 |

| 3.4  | Sample-and-hold PD                                                              | 28 |

| 3.5  | Sample-and-hold PD schematic                                                    | 28 |

| 3.6  | PFD state diagram                                                               | 29 |

| 3.7  | 2-XOR PFD                                                                       | 30 |

| 3.8  | D-Flipflop PFD, and characteristic                                              | 31 |

| 3.9  | Dead-zone                                                                       | 32 |

| 3.10 | Dead-zone characteristic                                                        | 33 |

| 3.11 | Dead-zone free PFD                                                              | 33 |

| 4.1  | Conceptual representation of a charge pump                                      | 36 |

| 4.2  | (L) Current mismatch, and (R) Pulse-width mismatch                              | 38 |

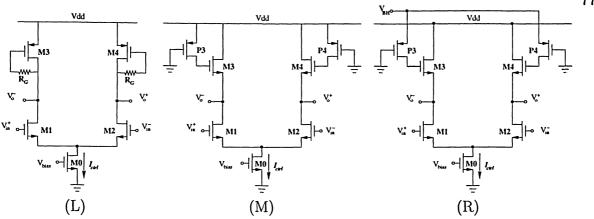

| 4.3  | (L)Switch at Drain CP, (M)Switch at Gate CP, and (R)Switch at Source CP.        | 42 |

| 4.4  | Charge sharing comparison                                                       | 44 |

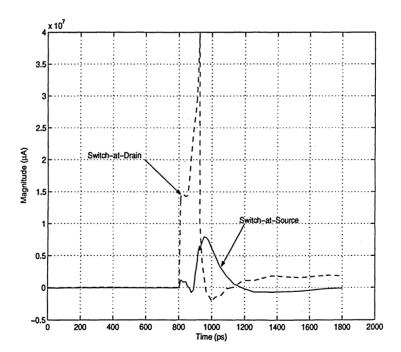

| 4.5  | Charge injection comparison                                                     | 44 |

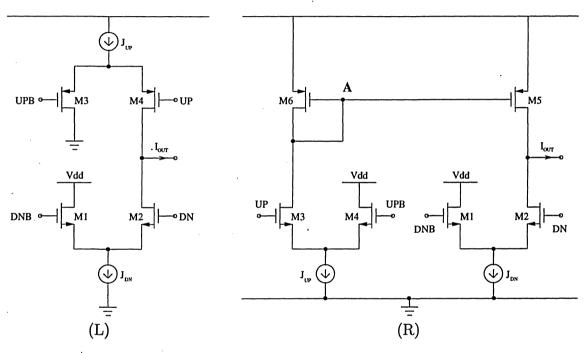

| 4.6  | (L) Conventional current-steering CP, and (R) NMOS switch only CP               | 45 |

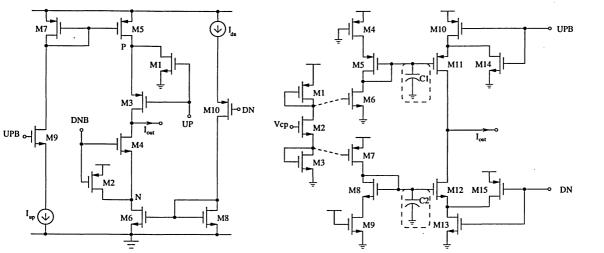

| 4.7  | (L) Chang's CP, (M) Current reuse, and (R) Current reuse and positive feedback. | 46 |

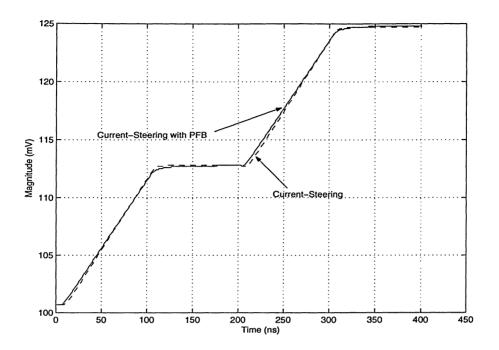

| 4.8  | Charge up of current-steering CPs                                               | 47 |

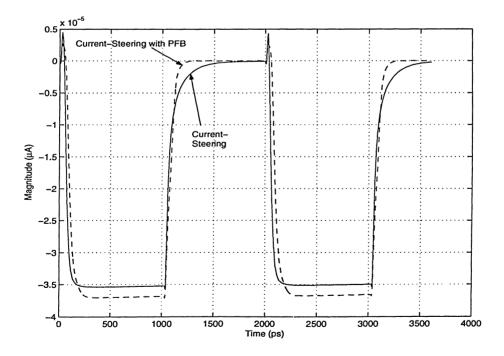

| 4.9  | Output current of current-steering CPs                                          | 47 |

| 4.10 | Differential current-steering CP                                                | 48 |

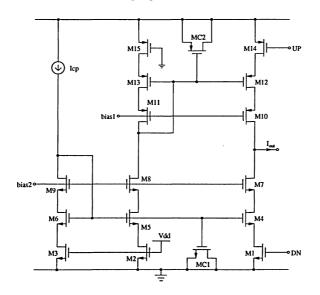

| 4.11 | Self-biased differential current-steering CP                                    | 49 |

|------|---------------------------------------------------------------------------------|----|

| 4.12 | Charge-pump with active amplifier                                               | 50 |

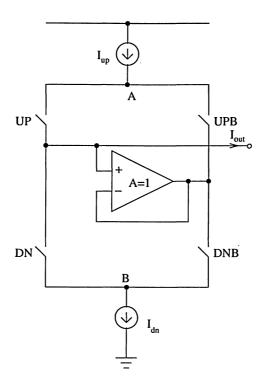

| 4.13 | Charge-pump with error amplifier                                                | 51 |

| 4.14 | (R)Improved switch at drain CP, and (R)Improved switch at source CP             | 52 |

| 4.15 | Charge-pump with AC coupling transistors                                        | 52 |

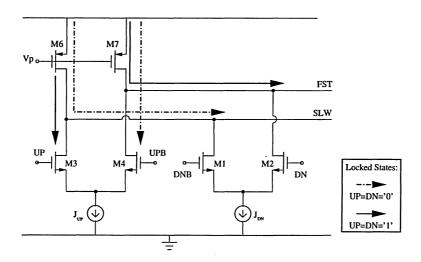

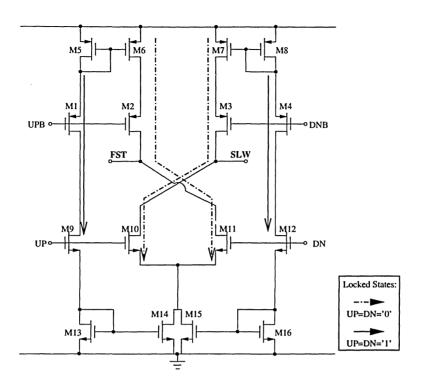

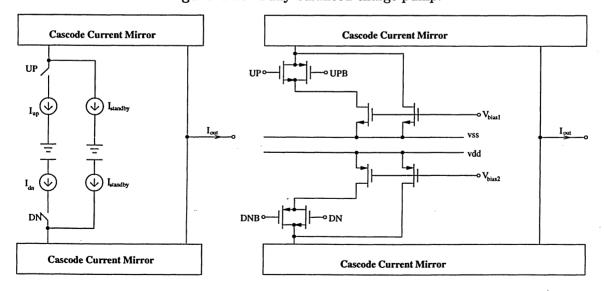

| 4.16 | High-speed charge-pump                                                          | 53 |

| 4.17 | Fully balanced charge-pump                                                      | 54 |

| 4.18 | Charge amplifier charge-pump                                                    | 54 |

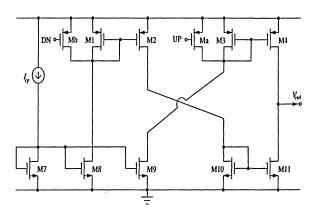

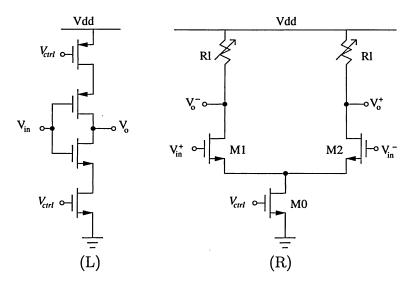

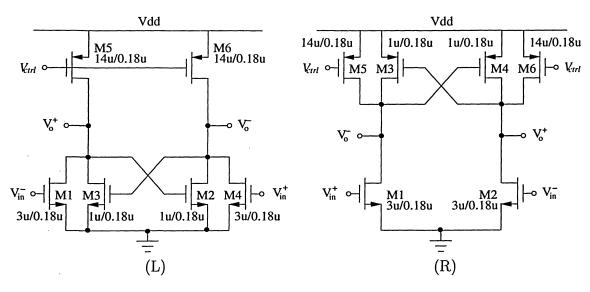

| 5.1  | Delay cells: (L) Single-Ended, and (R) Differential                             | 60 |

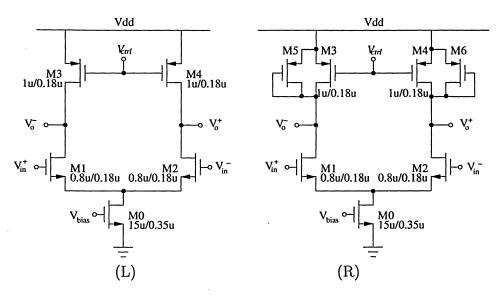

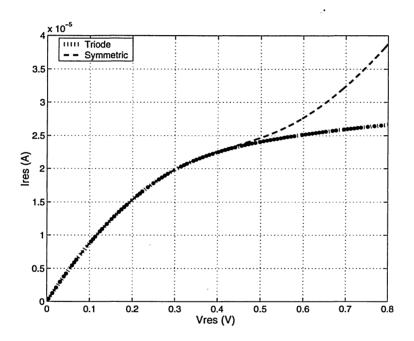

| 5.2  | Delay Cells: (L) Triode or Current source load, and (R) Symmetric load          | 61 |

| 5.3  | IV characteristic of symmetric loads                                            | 62 |

| 5.4  | Cross-coupled delay cells: (L) P-Latch, and (R) N-Latch                         | 63 |

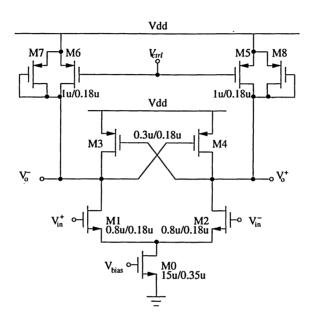

| 5.5  | Cross-coupled delay cell with symmetric loads                                   | 64 |

| 5.6  | Cross-coupled delay cells: (L) without skewed delay, and (R) with skewed delay. | 65 |

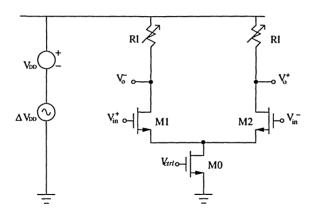

| 5.7  | Supply Sensitivity test of a differential delay cell                            | 67 |

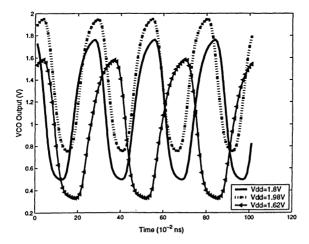

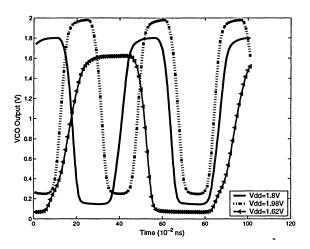

| 5.8  | VCO output: Symmetric Load                                                      | 67 |

| 5.9  | VCO output: Cross-coupled N-Latch                                               | 68 |

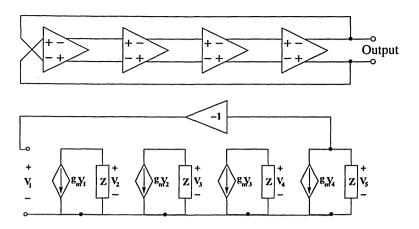

| 6.1  | Ring oscillator and its linear model                                            | 73 |

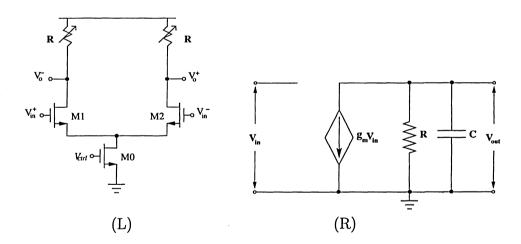

| 6.2  | (L)Differential Delay cell, and (R) Small signal model of cell                  | 73 |

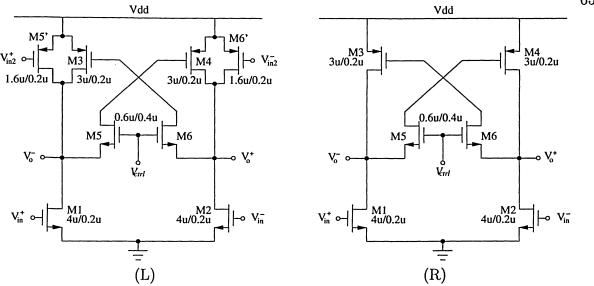

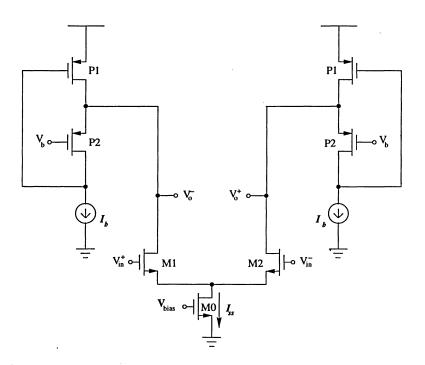

| 6.3  | Inductive load delay cells: (L) PMOS, (M) NMOS, and (R) NMOS-low voltage.       | 77 |

| 6.4  | Proposed differential delay cell with active inductive loads                    | 78 |

| 6.5  | Load impedance of delay cell employing active inductors                         | 79 |

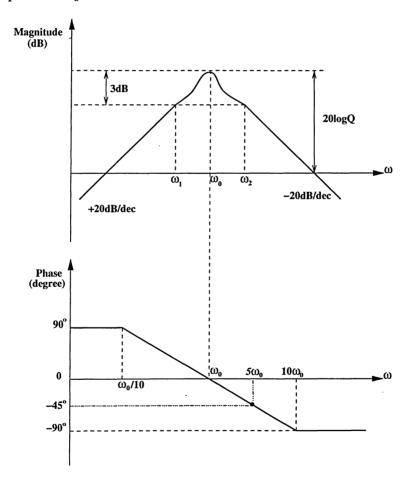

| 6.6  | $s^2 + \frac{1}{C}s + \omega_0^2$                                               | 81 |

| 6.7  |                                                                                 | 83 |

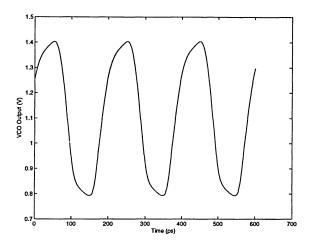

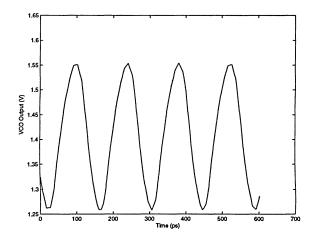

| 6.8  | Proposed VCO output waveform at 7 GHz                                           | 83 |

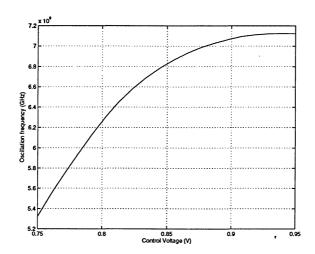

| 6.9  | Simulated frequency tuning characteristic of the proposed VCO                   | 84 |

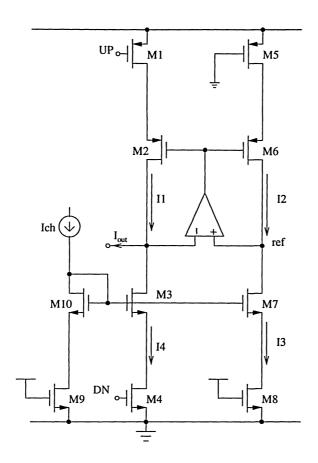

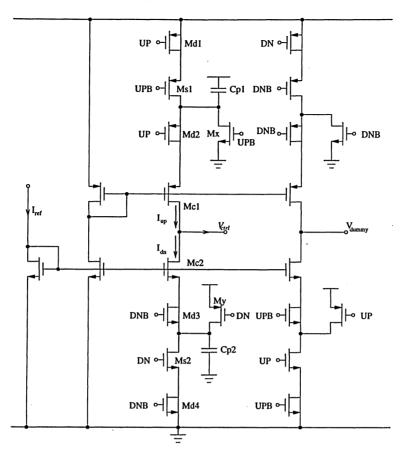

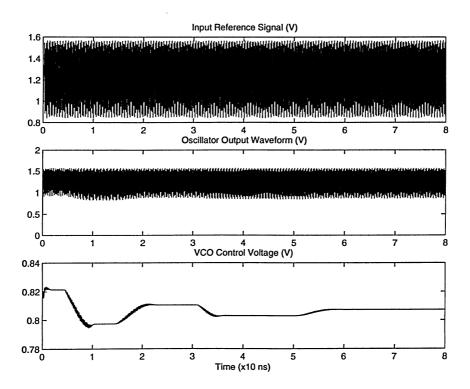

| 7.1  |                                                                                 | 87 |

| 7.2  | <b>.</b>                                                                        | 88 |

| 7.3  |                                                                                 | 88 |

| 7.4  |                                                                                 | 89 |

| 7.5  |                                                                                 | 90 |

| 7.6  |                                                                                 | 91 |

| 7.7  |                                                                                 | 91 |

| 7.8  | 1 0 1                                                                           | 92 |

| 7.9  | 0                                                                               | 93 |

|      |                                                                                 | 93 |

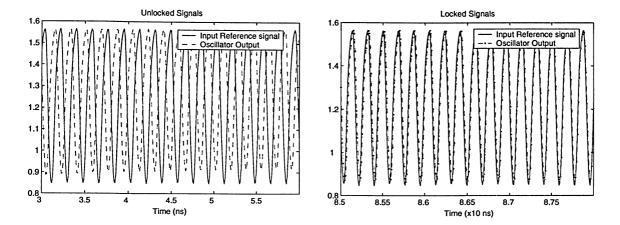

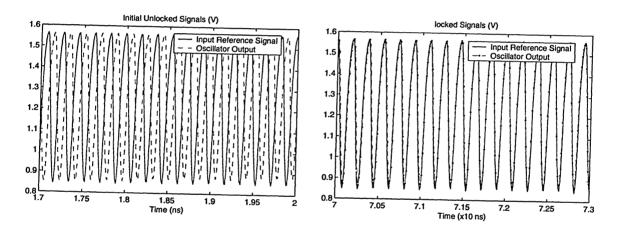

| 7.11 | Reference and feedback signals before and after lock                            | 94 |

| A.1  |                                                                                 | 04 |

| A.2  | Small signal equivalent circuit of Active inductor                              | 05 |

# List of Tables

| 4.1 | Charge Pump Functionality                                                       | 37 |

|-----|---------------------------------------------------------------------------------|----|

| 5.1 | Rise time of delay cells and its normalized worst-case sensitivity              | 68 |

| 5.2 | Fall time of delay cells and its normalized worst-case sensitivity              | 69 |

| 5.3 | Average delay of delay cells and its normalized worst-case sensitivity          | 69 |

| 5.4 | Oscillation frequency of delay cells and its normalized worst-case sensitivity. | 70 |

# Chapter 1

## Introduction

#### 1.1 Motivation

Phase locked loops (PLLs) are used in almost every communication system. Some of their uses include recovering clock and data signals, performing frequency-phase modulation and demodulation and recovering the carrier from satellite transmission signals and frequency synthesis.

The demand for high speed, wide bandwidth communication systems has led to advancements in both wireless and fiber-optic systems. To ensure economic viability, the entire semiconductor industry has been pushing for the implementation of a low-cost, low power, high-speed fully integrated receiver-on-chip.

To achieve the goal of a fully integrated receiver on-chip, where analog and digital blocks co-exist on the same substrate, the PLL has to operate at high speeds, while maintaining reasonable phase noise and jitter performance. Voltage-controlled oscillators (VCOs) are important building blocks of PLLs. More importantly, the VCO is the major contributor of phase noise of PLLs. Another important block of a PLL is the charge-pump, a block that is responsible for generating the control voltage to be applied to the VCO. The stability or fluctuation of the control voltage, can severely affect the phase noise performance of the VCO. In addition, the noisy environment, mainly due to the switching noise generated by

the digital portion of these systems, imposes stringent constraints on the design of VCOs, especially on phase noise or timing jitter. The switching noise originated in the digital portion of the systems is coupled to the supply and ground rails of the VCO of PLLs.

The research of this thesis, is centered on (i) the design considerations of CMOS charge-pumps, (ii) the timing jitter of the delay-cells of low-voltage CMOS ring-VCOs, and (iii) the design of a high-speed ring oscillator.

I chose phase locked loop because it is an excellent research topic, as it covers many disciplines of electrical engineering such as communication theory, control theory, signal analysis, noise characterization, microelectronic transistor design, digital circuit design and non-linear circuit analysis.

#### 1.2 Contribution

The contributions made in this thesis are three-fold:

- A comprehensive review of the architectures of CMOS charge pumps and an in-depth comparison of their characteristics such as speed, minimum supply voltage, mismatchinduced errors, charge injection and clock feed-through induced errors, and noise rejection is presented.

- 2. A comparative study of the architecture and timing jitter of the delay-cells of low-voltage CMOS ring-VCOs. Design considerations, such as noise, single-ended versus differential configurations, linearity and symmetry of load, and the output voltage swing of delay cells were examined in detail. The worst-case sensitivity of the delay time of the delay cells and that of the oscillation frequency of corresponding ring-VCO were analyzed and simulation results are presented.

- 3. A new delay cell utilizing inductive loads to enhance the oscillation frequency of a four-

stage ring oscillator was proposed. Both theoretical analysis and simulation results are presented. The new delay cell improves the oscillation frequency by 42%.

### 1.3 Thesis Organization

This thesis is organized as follows:

- Chapter 2 introduces the PLL system theory, challenges and trade-offs that lie in the design of PLLs.

- Chapter 3 presents the performance metrics of phase-frequency detectors and examines their different architectures.

- Chapter 4 examines both the architectures and design considerations of CMOS charge pumps for phase-locked loops.

- Chapter 5 presents a comparative study of the architecture and timing jitter of the delay-cells of low-voltage CMOS ring-VCOs. Design considerations, such as noise, single-ended versus differential configuration, linearity and symmetry of load, and the output voltage swing of delay cells are examined in detail. The worst-case sensitivity of the delay time of the delay cells and that of the oscillation frequency of corresponding ring-VCO are presented.

- Chapter 6 details the design of a new delay cell used in a 4-stage ring oscillator. A comprehensive analytical analysis of the oscillating speed of ring VCOs is provided. Simulation results are presented to verify the speed improvement.

- Chapter 7 details the design of a charge-pump PLL that employs the proposed delay cell. System level design, transistor level design and simulation results are presented.

- Chapter 8 concludes the thesis and presents several research areas to be explored in the future.

# Chapter 2

# Phase-Locked Loops

This chapter introduces the PLL system theory, challenges and trade-offs that lie in designing a PLL. In Section 2.1, the PLL is introduced and its function and operating regions are defined. The PLL's loop dynamics are formulated in Section 2.2. Critical parameters of PLLs are defined in Section 2.3. Section 2.4 presents the loop dynamics and stability analysis of a charge-pump PLL.

### 2.1 Basic Topology and Function

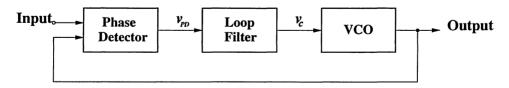

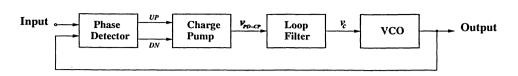

A phase-locked loop is a feedback control circuit that synchronizes the frequency of the oscillator's output with that of a reference signal. A simple PLL utilizes three basic blocks: a phase detector (PD), a loop filter (LPF), and a voltage controlled oscillator (VCO), as shown in Figure 2.1 [3].

Figure 2.1: Basic phase-locked loop.

A phase detector compares the phase difference between the input reference signal and the oscillator output. The PD generates an output voltage  $v_{PD}$  proportional to the phase

difference between the two signals. A loop filter is a low-pass filter that filters out the high frequency components of  $v_{PD}$  to produce  $v_c$ , which is the control voltage of the VCO. The control voltage  $v_c$  determines the frequency of the output voltage of the VCO.

#### 2.1.1 Phase Detectors

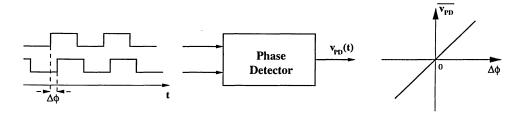

An ideal phase detector produces an output signal whose DC value is linearly proportional to the phase difference of the two input signals[2]:

$$\overline{v_{PD}} = K_{PD} \Delta \phi, \tag{2.1}$$

where  $K_{PD}$  is the gain of the phase detector, and  $\Delta \phi$  is the phase difference between the two input signals, as shown in Figure 2.2.

Figure 2.2: Characteristic of an ideal phase detector.

The phase detector input-output characteristic should ideally be linear, non-periodic, and monotonic for a wide range of phase difference values. In reality, the gain or slope  $K_{PD}$  of the characteristic is not constant and may depend on either the amplitude or duty-cycle of the input signals. Chapter 3 will further evaluate the design considerations of PDs, the different architectures, their advantages and limitations.

#### 2.1.2 Voltage Controlled Oscillators

An ideal voltage controlled oscillator produces an output signal whose frequency  $\omega_{out}$  is a function of the control voltage  $v_c[1]$ :

$$\omega_{out} = \omega_{FR} + K_{VCO}v_c, \tag{2.2}$$

where  $\omega_{FR}$  is the free-running frequency of the VCO and  $K_{VCO}$  is the gain of the VCO. The relations between time, phase, and frequency provide us with an expression of the output voltage of the VCO:

$$y(t) = A\cos(\omega_{FR}t + K_{VCO}\int_{-\infty}^{t} v_c dt).$$

(2.3)

The VCO is considered a linear time-invariant system whose output of concern is the output excess phase. Equation (2.3) provides us the input  $(v_c)$  - output  $(\phi_{out})$  relationship as:

$$\phi_{out}(t) = K_{VCO} \int v_c dt, \qquad (2.4)$$

from which we obtain the input-output transfer function:

$$\frac{\Phi_{out}(s)}{V_c(s)} = \frac{K_{VCO}}{s}.$$

(2.5)

It is important to know that  $v_c$  in itself does not determine the phase at the output, but the frequency. A change in  $v_c$  will lead to either an increase or decrease in the output frequency  $\omega_{out}$  and consequently the output will either accumulate or dissipate phase faster thereby reducing phase-error. In essence, the initial conditions of the VCO and the system response determine the phase.

#### 2.1.3 PLL Operating Regions

In this section we define the lock conditions, locked states, and the regions of operation of PLLs. Note that the behavior of PLLs in an unlocked state is not important. What is important is whether the PLL enters lock and how it acquires lock.

For PLLs to achieve *lock*, both frequency acquisition and phase acquisition must be attained. Frequency acquisition is defined as having equal input and output frequencies [1]. This condition is extremely important for applications such as frequency synthesis that is intolerant to frequency inaccuracies. Phase acquisition is defined as having the phase error settle to a constant value, not necessarily zero, with respect to time. In the case where frequency

acquisition is met, but phase acquisition is not, the loop must continue the transient, temporarily loosing frequency acquisition until both lock conditions are met.

In the locked state, all signals within the phase-locked loop will be in a steady state [1]. The phase detector will generate an output whose average DC value is proportional to the phase difference, and the VCO will oscillate at a frequency equal to the input frequency with a phase difference  $\Delta \phi$ .

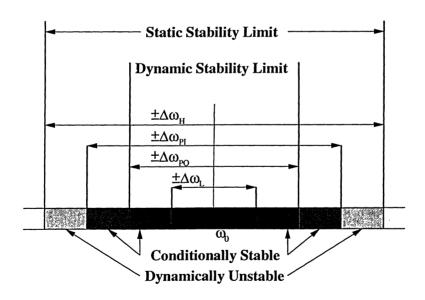

The PLL's operation can be dissected to four different regions. In the case when the output signal is not *locked* in frequency and phase with the input signal, the PLL is said to be in a dynamic state. Alternatively, the PLL is said to be in a static state when the output signal is locked with only the frequency of the input reference signal. The four regions of operation are shown in Figure 2.3 [3] as *hold range*, *pull-in range*, *pull-out range*, and *lock range*.

Figure 2.3: PLL Regions of Operations.

Hold range: The hold range  $\Delta \omega_H$  is the frequency range over which the PLL can maintain phase tracking without falling out of lock.

Pull-in range: The pull-in range  $\Delta\omega_{PI}$ , also known as capture/acquisition range<sup>1</sup>, describes the frequency range of the input signal over which the PLL can acquire lock. The process of acquiring lock within the pull-in range maybe a slow process. However, if the input reference frequency is within the narrower lock range, then the process of acquiring lock will be faster.

Lock range: The lock range  $\Delta\omega_L$ , also known as the tracking range<sup>2</sup>, is the input frequency range over which the PLL can acquire lock without cycle slips. i.e. within a single beat.

Pull-out range: The pull-out range  $\Delta\omega_{PO}$  determines the dynamic limit for stable operation. In other words, it determines the maximum value of the frequency step that can be applied at the input without causing the PLL to unlock. Assuming the PLL is in lock, if a frequency step that exceeds the pull-out range is applied to the input, the PLL will not be able to track and will fall out of lock.

### 2.2 Loop Dynamics

While the transient response of a phase-locked loop is a nonlinear process that is difficult to formulate, a linear approximation is useful in understanding the PLL's behavior and design tradeoffs. In this section, the transfer function of the PLL is derived and its static and dynamic behaviors are analyzed [2].

Using the linear model, the open loop transfer function of the PLL is given by:

$$H_o(s) = \frac{\Phi_{out}(s)}{\Phi_{in}(s)} = K_{PD}G_{LPF}(s)\frac{K_{VCO}}{s},$$

(2.6)

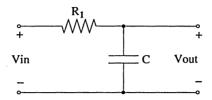

where  $G_{LPF}$  is the transfer function of the loop filter. Assuming the loop filter in use is a simple RC low pass filter, the transfer function will have the following form:

<sup>&</sup>lt;sup>1</sup>We will avoid using the deceptive term *capture range*, since it is used as an alternative for lock range in some texts and pull-in range in others.

<sup>&</sup>lt;sup>2</sup>When frequency detection is a property of the phase detector, tracking range becomes equal to acquisition range (Chapter 3).

$$G_{LPF}(s) = \frac{1}{1 + \frac{s}{\omega_{LPF}}} = \frac{1}{1 + sR_1C}.$$

(2.7)

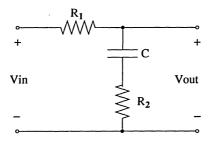

Figure 2.4: Simple low pass filter.

Thus the closed loop transfer function is simplified to

$$H_c(s) = \frac{H_o(s)}{1 + H_o(s)} = \frac{K_{PD}G_{LPF}(s)K_{VCO}}{s + K_{PD}G_{LPF}(s)K_{VCO}} = \frac{K_{PD}K_{VCO}}{\frac{s^2}{\omega_{LPF}} + s + K_{PD}K_{VCO}}.$$

(2.8)

The derived closed loop transfer function indicates that the PLL is a second order system with the loop gain  $K = K_{PD}K_{VCO}$  and two poles, one contributed from the LPF and the other from the VCO. From control theory, we recognize the form of the close loop transfer function as:

$$H(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2},\tag{2.9}$$

where  $\omega_n$  is the natural frequency, and  $\zeta$  is the damping factor.

By comparing (2.8) and (2.9), we obtain

$$\omega_n = \sqrt{\omega_{LPF}K}, \qquad (2.10)$$

$$\zeta = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K}}. (2.11)$$

For a flat frequency response, the optimum value for damping factor  $\zeta$  is equal to  $\frac{\sqrt{2}}{2}$ . This value dictates a relationship between the LPF's cut-off frequency  $\omega_{LPF}$  and the loop gain K:  $K = \frac{\omega_{LPF}}{2}$ . This relationship puts a constraint on choosing K and  $\omega_{LPF}$  independently in the design of a PLL.

### 2.3 Critical Parameters

In this section, we define the performance criteria of PLLs. They are static phase-error, tracking range, acquisition range, and acquisition time [1, 3, 5].

#### 2.3.1 Static Phase Error

Even-though the PLL operates on excess phase  $\phi_{out}$ , its phase error<sup>3</sup> final settling  $(t \to \infty \equiv s \to 0)$  value and its response to frequency variations is of interest. The phase error transfer function is obtained from:

$$H_e(s) = \frac{\Phi_e(s)}{\Phi_{in}(s)} = 1 - H(s) = \frac{s^2 + 2\zeta\omega_n s}{s^2 + 2\zeta\omega_n s + \omega_n^2}.$$

(2.12)

With the current configuration where, a single pole loop filter is used, Equations (2.9) and (2.12) indicate that a *static* phase shift at the input is transferred to the output unchanged (as  $s \to 0$ ,  $H(s) \to 1$  and  $H_e(s) \to 0$ ). On the other hand, a rapid variation of the phase of the input (*dynamic* phase shift) will lead to a small variation in the phase of the output.

Given that a phase shift is due to a change in frequency, it is worthwhile to analytically see the effect of an input step frequency  $\Delta \omega u(t)$  to the output phase error, where u(t) is the unit step function. The phase error is calculated as follows<sup>4</sup>:

$$\Phi_e(s) = H_e(s)\Phi_{in}(s) \tag{2.13}$$

$$= \frac{s^2 + 2\zeta\omega_n s}{s^2 + 2\zeta\omega_n s + \omega_n^2} \frac{\Delta\omega}{s^2}, \tag{2.14}$$

and its final settling value is:

$$\lim_{t \to \infty} \Phi_e = \lim_{s \to 0} s \Phi_e(s), \tag{2.15}$$

<sup>&</sup>lt;sup>3</sup>In case where the PLL is designed to lock onto a non-zero phase difference ( $\Delta \phi = constant \neq 0$ ), then  $\phi_e \neq \Delta \phi$ .

<sup>&</sup>lt;sup>4</sup>The Laplace transform of the frequency step equals  $\Delta \omega/s$ , therefore the input phase would be its derivative  $\Delta \omega/s^2$ .

$$= \Delta \omega \frac{2\zeta}{\omega_n}, \tag{2.16}$$

$$= \frac{\Delta\omega}{K}.\tag{2.17}$$

The above calculations conclude that static frequency variations at the input will manifest themselves as static phase shifts attenuated by a factor K at the output. It is obvious that in order to minimize the phase error, a high loop gain K is needed. However, Equation (2.11) indicates that a tradeoff has to be made between  $\zeta$  that determines the settling behavior (see Section 2.3.4),  $\omega_{LPF}$  that determines the cutoff frequency of the loop filter, and K that determines the phase error, and width of the acquisition range (see Section 2.3.3).

To allow for a larger gain independent of  $\omega_{LPF}$  and without sacrificing the settling time, a zero (resistor  $R_2$ ) added to the LPF would modify the loop filter transfer function to

Figure 2.5: Loop filter with an added zero.

$$G_{LPF}(s) = \frac{sR_2Cs + 1}{s(R_1 + R_2)C + 1}. (2.18)$$

A similar calculation to those presented before will yield a closed loop transfer function

$$H(s) = \frac{K\omega_{LPF}(\frac{s}{\omega_z} + 1)}{s^2 + \omega_{LPF}(\frac{K}{\omega_z} + 1)s + K\omega_{LPF}},$$

(2.19)

where,

$$\omega_z = \frac{1}{R_2 C},\tag{2.20}$$

$$\omega_z = \frac{1}{R_2 C},$$

(2.20)

$$\omega_{LPF} = \frac{1}{(R_1 + R_2)C},$$

(2.21)

and the damping factor  $\zeta$

$$\zeta = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K}} (\frac{K}{\omega_z} + 1), \qquad \omega_z > \omega_{LPF}.$$

(2.22)

Using the same optimal  $\zeta$  value introduced before, the reader can similarly calculate the gain K as  $32\omega_{LPF}$ , a much larger gain compared to  $K = \frac{\omega_{LPF}}{2}$ . However, a disadvantage of adding a zero to the loop filter is the decrease in the attenuation of high frequency signals. A possible solution would be to add another pole far from the zero in the form of a capacitor at the output. The downside of the additional pole is the degradation of the settling time, due to the change in the optimum damping factor.

#### 2.3.2 Tracking Range

As explained earlier, the tracking range is defined as the input frequency range over which the PLL can acquire lock without cycle slips(static tracking) i.e. within a single beat [3].

Assuming that the loop filter's components are linear, for the PLL to track, the three characteristic curves (i)  $\phi_e$  vs.  $\omega_{in}$ , (ii)  $\overline{v_{PD}}$  vs.  $\phi_e$ , and (iii)  $\omega_{out}$  vs.  $v_c$  must vary monotonically. In other words, the edge of the tracking range is determined by the slope/gain of each of the characteristic curves. The point at which any of the slopes approach zero or change sign defines the edge of the tracking range. While, the tracking range depends greatly on the type of phase detector used (see Chapter 3), for simplicity, we will assume that the phase detector is a simple analog multiplier. The gain  $K_{PD}$  of an analog multiplier, changes sign for input phase differences  $\Delta \phi$  greater than  $\frac{\pi}{2}$ . Voltage controlled oscillators, on the other hand, have a limited frequency range, beyond which the gain  $K_{VCO}$  drops sharply. To lock within a single beat, the VCO output frequency can not vary by more than:

$$\Delta\omega_L = K_{PD} K_{VCO} \sin\left(\frac{\pi}{2}\right). \tag{2.23}$$

Because the tracking range refers to the deviation from the center free running frequency, the tracking range is half of the lock range.

#### 2.3.3 Acquisition Range

In the case where a PLL acquires lock within a number of cycle slips or beats, the PLL is said to be in the *dynamic tracking* mode or within the acquisition range. In this section, we will determine the maximum input frequency range over which the PLL can acquire lock. We will present the process of acquiring lock in both frequency and time domains [1].

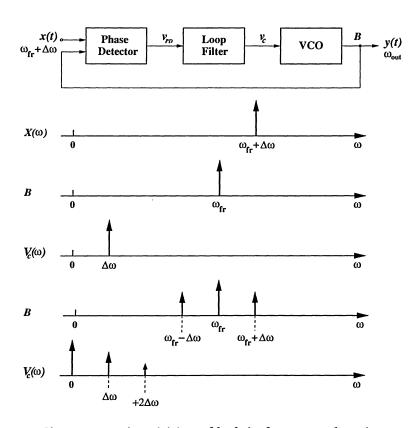

Figure 2.6: Acquisition of lock in frequency domain.

Frequency domain: Assuming that the phase detector is a simple analog multiplier, we will plot the frequency spectra (Figure 2.6) of the signals around the loop to illustrate the process of acquiring lock. With the assumption that the initial conditions of the loop filter are zero, the VCO output frequency should be  $\omega_{out} = \omega_{fr}$ . A frequency step  $\Delta \omega$  is applied at the input to give  $\omega_{in} = \omega_{fr} + \Delta \omega$ . It can be shown analytically that the VCO output voltage will be [1]:

$$y(t) \approx A \cos \omega_{fr} t - \frac{K_{VCO}}{\Delta \omega} A_m \sin \omega_{fr} t \sin (\Delta \omega t),$$

(2.24)

where A is the amplitude of the output voltage, and  $A_m$  is the amplitude of the modulated control voltage. The spectra of the modulated signal has sidebands at  $\omega_{fr} \pm \Delta \omega$ , the phase detector multiplies the sidebands with the input frequency, resulting in a DC component at the control voltage. This DC component will grow over a number of cycles adjusting the VCO frequency until lock. From our analysis, we observe that the acquisition range is a function of: (1) the attenuation of the loop filter components at  $\Delta \omega$  and (2) the feedback strength of the DC component. In other words, the acquisition range is a function of the loop gain at  $\Delta \omega$ . Simple type-I <sup>5</sup> PLLs mentioned so far, experience a fading loop gain at larger frequency differences.

Time domain: Assuming the same initial conditions mentioned above, in this section we illustrate the process of lock in the time domain. During the first cycle, where the feedback in the loop has not yet affected the response, the output of the combined analog phase detector and loop filter  $v_c$  is a sinusoid with a frequency equal to  $\Delta \omega = \omega_{in} - \omega_{out} = \omega_{in} - \omega_{fr}$ . Moreover, the frequency of the VCO increases and decreases with  $v_c$ . The implication is that  $\Delta \omega_{max}$  refers to positive peak of the sinusoid and  $\Delta \omega_{min}$  refers to the negative peak.

Without the feedback signal, the sinusoidal signal is periodic and symmetric with an average DC value of zero. To acquire lock, the DC value of  $v_c$  must move the frequency of the VCO in the direction of the reference input frequency. Fortunately, the feedback signal once introduced, has a time-varying frequency due to frequency modulation at the VCO. If the output frequency is modulated in the positive direction, the frequency difference decreases and the sinusoid will have longer positive cycles as shown in Figure 2.7. Consequently  $v_c$  will have a larger positive DC component that will allow the PLL to lock.

<sup>&</sup>lt;sup>5</sup>Type-I refers to the order of the PLL, more specifically the number of poles in the loop filter, in this case being one

Figure 2.7: Acquisition of lock in time domain.

We can conclude that the proximity of  $\omega_{in}$  to  $\omega_{out}$  will determine whether the loop will acquire lock within one beat or several beats. The number of cycle slips needed for lock is a function of the initial conditions of the loop filter and VCO [3]. The analytical estimation of the acquisition range is [3]:

$$\Delta\omega_{acq} = K_{PD}K_{VCO} \mid G_{LPF}(j\Delta\omega) \mid . \tag{2.25}$$

#### 2.3.4 Acquisition Time

The terms acquisition time and settling time are often mistakenly interchanged. The difference stems from the operating region of PLLs. While in the lock-tracking range, the time needed for a PLL to lock within a defined phase-error is referred to as the lock-in or settling time. For a second order PLL ( $\zeta < 1$ ), the step response is given by [1]:

$$y(t) = \left[1 + \frac{1}{\sqrt{1-\zeta^2}}e^{-\zeta\omega_n t}\sin(\omega_n\sqrt{1-\zeta^2} - \psi\right]u(t), \tag{2.26}$$

where  $\psi = \sin^{-1} \sqrt{1 - \zeta^2}$ . The settling time can be derived form (2.26):

$$t_{settle} = \frac{1}{\zeta \omega_n} = \frac{2}{\omega_{LPF}}. (2.27)$$

Clearly, there is a trade-off to be made between stability and ripple noise on the control voltage  $v_c$ . To minimize the ripple in the control voltage, the cut-off frequency of the loop filter has to be decreased. The drawback of decreasing  $\omega_{LPF}$  is stability degradation in the form of a prolonged settling time.

Acquisition time on the other hand, refers to the acquisition operating range of the PLL, and so defines the time needed for the PLL to acquire lock given a certain frequency difference. The acquisition time for a linear type-I PLL is given by [3]:

$$t_{acq} = \frac{\pi^2 \Delta \omega_0^2}{16 \zeta \omega_n^3}.$$

(2.28)

#### 2.3.5 Aided Acquisition

For a PLL employing a simple one-pole loop filter, designed for an optimum damping factor of  $\zeta = \frac{\sqrt{2}}{2}$ , Equation 2.25 will conclude an acquisition range of  $\Delta \omega_{acq} = 0.5\omega_{LPF}$ , a rather small range. Due to jitter and sideband suppression requirements, minimize the ripple on the control voltage  $v_c$ , increasing  $\omega_{LPF}$  is not feasible. Moreover, the loop gain fades as the input output frequency deviation increases. For the reasons mentioned, PLLs often employ a frequency detector to aid in the acquisition of frequency. The frequency detector will produce a DC voltage proportional to the frequency difference  $\omega_{in} - \omega_{out}$ . The concept is simple, for large frequency differences, the VCO will be driven by the DC of the frequency detector, and for small frequency differences, the VCO will be driven by the DC of the phase detector. With the addition of frequency acquisition, the loop gain is now constant and independent of the value of  $\omega_{in} - \omega_{out}$ , this can substantially increase the acquisition range to a limit set by the tuning range of the VCO (see Chapter 3).

#### 2.3.6 Phase Noise and Jitter

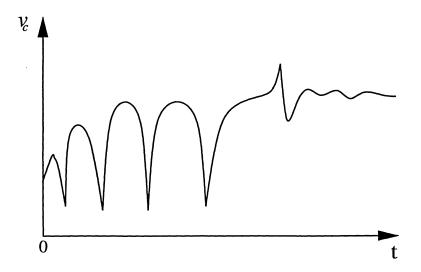

One of the more important design considerations of phase locked loops is phase noise or jitter. An ideal periodic signal has a frequency spectra with an impulse at the fundamental frequency, in addition to energy impulses at DC and the harmonic frequencies of the fundamental frequency. Timing jitter is the resultant of varying zero crossings in the time domain (see Figure 2.8(L)). In the frequency domain, these variations result in energy skirts (see Figure 2.8(R)) known as phase noise [1, 3, 12].

Figure 2.8: (L) Jitter in a periodic signal, and (R) Frequency spectrum of a signal with Phase noise.

Phase noise is defined as the ratio of the power of the sideband noise  $P_{SB}$  in a 1Hz bandwidth at a given offset frequency  $\Delta \omega$  to the carrier power  $P_c$ :

$$L\{\Delta\omega\} = 10\log_{10}\frac{P_{SB}(\omega_0 + \Delta\omega, 1HzBW)}{P_c}.$$

(2.29)

Phase noise in the frequency domain in specified in dBc/Hz at a given frequency offset  $\Delta\omega$ , and translates into jitter specified by its peak-to-peak time value (picoseconds) in the time domain. While all PLL blocks contribute to the overall phase noise, we will only present the more dominant noise sources, input referred phase noise, and VCO generated phase noise. In both cases, we assume that the phase noise is a random component of the excess phase that the PLL operates on.

Input Phase Noise: The input-output phase transfer function given in (2.9), indicates that for a constant input excess phase or a slowly varying input phase with respect to time, H(s) is approximately equal to unity and consequently the output follows the input. As the input phase noise  $\phi_{in}(t)$  varies at higher rates, the output phase depreciates to zero and the PLL fails to track. The input phase noise transfer function, obviously has a low pass characteristic. In order to reduce the input refereed phase noise, the PLL loop bandwidth must be reduced. The consequences of reducing the loop bandwidth are, a reduction in lock speed, a limited capture range, and a degradation in stability.

VCO Phase Noise: The phase noise generated by the VCO  $\phi_{VCO}$  is modelled as an input signal. Assuming the VCO phase noise is uncorrelated to the input phase noise  $\phi_{in}(t)$ , then the VCO phase noise transfer function is:

$$\frac{\Phi_{out}(s)}{\Phi_{VCO}(s)} = \frac{s(s + \omega_{LPF})}{s^2 + 2\zeta\omega_n s + \omega_n^2}.$$

(2.30)

The VCO phase noise transfer function has a high pass characteristic, and in order to reduce the VCO-referred phase noise, a PLL with a wide loop bandwidth is preferred. Clearly, a tradeoff has to be made regarding the width of the PLL bandwidth and its effect on the noise contribution from the input and the VCO. The application will dictate the loop bandwidth. The VCO phase noise is caused by several sources: up-converted 1/f noise of the transistors, ripple in the control voltage, and power supply voltage fluctuations among other things. Chapter 5 will elaborate more.

### 2.4 Charge Pump Phase-Locked Loop CP-PLL

The charge-pump phase locked loop (CP-PLL) shown in Figure 2.9 is preferable to the conventional PLL for the following reasons:

• The CP-PLLs pull-in range is limited only by the VCO's tuning range [3].

Figure 2.9: Charge-pump phase-locked loop.

- The CP-PLL locks to a phase error of zero, even if the reference input frequency is not equal to the center free-running frequency of the VCO, as was the case in the simple PLL [1].

- The CP-PLL displays more immunity to power supply variations [4].

- The CP-PLL does not experience charge decay as compared to the conventional PLL. This is because, in the simple PLL, charge is applied to the loop filter capacitor at every phase comparison, and between the phase comparison, the charge across the capacitor decays. With a charge pump in place, decay is minimized [2].

The CP-PLL, also referred to as the classical digital PLL uses the charge pump at the output of the phase-frequency detector. Only in this case, the phase-frequency detector produces two control signals UP and DN as opposed to one. The control signals will determine how much error current is applied to the loop filter. The charging and discharging of the loop filter will determine the value of the control voltage.

The combined response of a charge pump-phase frequency detector to a static phase difference is a linear ramp. In other words, the transfer function of the charge-pump and phase frequency detector combined, contains a pole at the origin and can be represented as:

$$H(s)_{PFD-CP} = \frac{K_{PD}}{s}. (2.31)$$

Clearly, with the addition of the charge-pump and all its advantages, the stability and dynamics of the PLL have changed. In the following sections, we analyze the stability and dynamics of CP-PLL [1, 12].

#### 2.4.1 Stability

To ensure that the CP-PLL is a stable system, care must be taken in the design of the loop filter. With solely a capacitor as the loop filter, the new PLL transfer function can be easily computed as:

$$H_c(s) = \frac{K_{PFD}K_{VCO}}{s^2 + K_{PFD}K_{VCO}}. (2.32)$$

The above transfer function has two imaginary poles, rendering the system unstable. An added zero in the form of a resistor in series with the capacitor of the loop filter can help stabilize the system. The disadvantage of adding a resistor, is an increase in ripple at the control voltage. This ripple can be suppressed by a second capacitor  $C_2$  in parallel with the  $R-C_1$  combination.  $C_2$  should be chosen in the order of one-tenth of  $C_1$ , so that the system can still be analyzed as a second order system.

#### 2.4.2 Dynamics

Assuming that the loop is experiencing a phase difference of  $\Delta \phi = \phi_{in} - \phi_{out}$ , the charge pump will produce an average current equal to:

$$I_{ave} = \frac{I\Delta\phi}{2\pi},\tag{2.33}$$

and the loop filter will produce a control voltage:

$$V_c(s) = \frac{I\Delta\phi}{2\pi} (R + \frac{1}{sC_p}). \tag{2.34}$$

Consequently, the VCO output phase will be equal to:

$$\Phi_{out}(s) = V_c(s) \frac{K_{VCO}}{s}.$$

(2.35)

The closed loop transfer function, can easily be computed to:

$$H(s) = \frac{\Phi_{out}(s)}{\Delta\Phi(s)} = \frac{\frac{I}{2\pi C_p} (RC_p s + 1) K_{VCO}}{s^2 + \frac{I}{2\pi} K_{VCO} Rs + \frac{I}{2\pi C_p} K_{VCO}},$$

(2.36)

that has the form:

$$H(s) = \frac{K\omega_p(\frac{s}{\omega_z} + 1)}{s^2 + \omega_p(\frac{K}{\omega_z} + 1)s + K\omega_p},$$

(2.37)

from which we can calculate:

$$\omega_n = \sqrt{\frac{I}{2\pi C_p}} K_{VCO},$$

$$= \sqrt{K\omega_p},$$

$$\zeta = \frac{R}{2} \sqrt{\frac{IC_p}{2\pi}} K_{VCO}.$$

(2.38)

We can also repeat the calculations seen in Section 2.3.4, to calculate

$$t_{settle} = \frac{2}{\zeta \omega_n},$$

$$= \frac{8\pi}{RIK_{VCO}}.$$

(2.40)

With the dynamics computed, we note the following observations:

- High frequency applications require high loop bandwidth, which is proportional to the natural frequency  $\omega_n$ . Using the conventional PLL,  $\omega_n$  could only be increased by increasing  $\omega_{LPF}$  (see Equation 2.11), which is undesirable for low noise applications (see Section 2.3.6). In a CP-PLL,  $\omega_n$  can be increased through the charge pump current I or VCO gain  $K_{VCO}$  as shown in (2.39).

- By comparing (2.27) and (2.40), we notice that with the CP-PLL design,  $t_{settle}$  is independent of the loop filter capacitor.

- The dynamic analysis of the simple PLL is based on the assumption that the system is a linear system. This assumption holds true on condition that the input reference frequency be much greater than the loop bandwidth. When the condition does not hold, discrete time analysis should be used. Since the loop bandwidth is directly proportional to the natural frequency  $\omega_n$ , discrete time analysis leads to the stability

$$\omega_n^2 < \frac{\omega_{in}^2}{\pi (RC_1 \omega_{in} + \pi)},\tag{2.41}$$

which puts a limit on the value of the resistor R. On the other hand, in the CP-PLL configuration,  $\omega_n$  is independent of R, which eases the design constraint.

## Chapter 3

# **Phase-Frequency Detectors**

The dynamics of the PLL described in Chapter 2, conclude that the performance of the PLL -Tracking Range, Acquisition Range, Loop Gain, and Transient Response- depends on the properties of the PD in-use. Section 3.1 defines the performance evaluators of the PFD. This is followed by Section 3.2 that examines the different design techniques of phase detectors, phase-frequency detectors, and the dead-zone concept.

### 3.1 Functionality and Performance Evaluators

An ideal phase detector produces an output signal whose DC value is linearly proportional to the phase difference of the two input signals. The phase detector input-output characteristic should ideally be linear, non-periodic, and monotonic for a large range of phase difference  $\Delta \phi$ . In reality, the gain or slope  $K_{PD}$  of the characteristic is not constant and may depend on either the amplitude or duty-cycle of the input signals. The performance evaluators of a phase detector are illustrated below [1, 2, 3, 8].

Tracking Range: We can recall that the edge of the tracking range of a PLL is defined as:  $\frac{\Delta\omega_L}{2}$ , where  $\Delta\omega_L = K_{PD}K_{VCO}\sin\frac{\pi}{2}$ . Therefore, we have to ensure that the PD characteristic is monotone for a large phase difference  $\Delta\phi$ .

Acquisition Range: The acquisition range was defined as:  $\Delta \omega_{acq} = K_{PD}K_{VCO} \mid G_{LPF}(j\Delta\omega) \mid$ , the gain of the PD,  $K_{PD}$  is constant and independent of the amplitude and duty-cycle of the input signals. Moreover, the phase detector's ability to detect input signals of different frequencies can greatly enhance the acquisition range, and remove its dependance on the gain  $K_{PD}$  and loop-filter frequency  $\omega_{LPF}$ .

Lock Condition: Ideally, in the locked state the phase detector's output is zero, the chargepump is no longer switching, and the control voltage is fixed. In practice, the phase detector's output is not zero, and can create unwanted switching activity at the charge-pump which increase the jitter and ripple on the control voltage  $V_c$ .

Sensitivity to input data pattern: PDs usually require that the input data have a minimum timing content. Long strings of ones and zeros could result in high VCO output jitter, due to the activity introduced to the control voltage  $V_c$ , even while in lock.

Lock Speed: Lock speed is an evaluation parameter of PLLs, but the choice of PD can greatly affect the time needed for a PLL to lock, given a phase difference. For example, digital PDs operate at slow speeds and require sufficient time for the outputs to stabilize, they suffer from long Lock time. Analog PDs are more suitable for high-speed applications, but are slightly more complex.

# 3.2 Design Techniques

Phase detectors can be categorized into: (i) Combinational PDs, (ii) XOR PDs, and (iii) Edge-triggered PDs [8]. In the following section, we will examine PDs that are widely used, and highlight their advantages, disadvantages, and performance limitations.

#### 3.2.1 Phase Detectors

#### Gilbert Cell PD

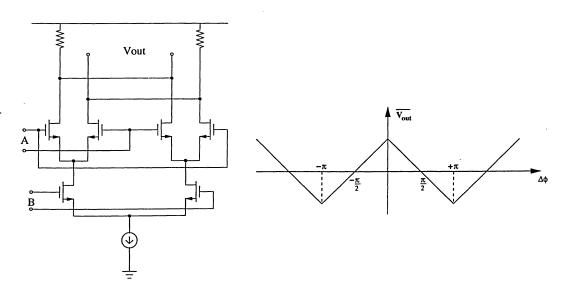

The schematic and transfer characteristics of the Gilbert cell based PD is shown in Figure 3.1 [1]. When the inputs of the cell are of small amplitude, the cell behaves as an analog multiplier, whose output is determined by

$$\overline{V_{out}} = \frac{\alpha AB}{2} \cos(\Delta \phi), \tag{3.1}$$

where  $\alpha$  is a factor due to the multiplier, A and B are the amplitudes of the input signals. Although this implementation is characterized as having a high operating speed, its input-output characteristic is nonlinear, sinusoidal and periodic. For phase differences near 90°, the relationship is approximately linear. While the characteristic of the cell in Figure 3.1 indicates that it has a limited tracking range of 90°. Within the range, the PD's gain is a function of the amplitude of the input signals. Moreover, the cell suffers from high statistic power consumption, and can not detect frequency errors.

Figure 3.1: Gilbert cell PD and characteristic.

#### XOR PD

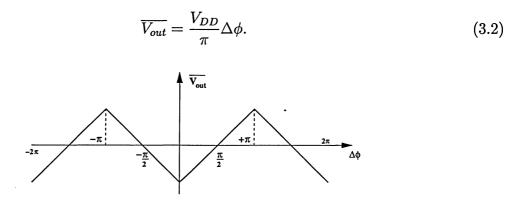

When the inputs of the cell shown in Figure 3.1 are of large amplitude, the cell behaves as a XOR gate or a digital multiplier [1], whose output is determined by the following equation:

Figure 3.2: XOR characteristic.

As compared with the Gilbert cell PD, the tracking range has been improved to  $(0^{\circ} \sim 180^{\circ})$  as shown in Figure 3.2, and the gain is no longer dependant of the amplitude of the input signals. A drawback of this circuit is the output's dependance on the duty-cycle of the inputs; i.e. when the phase difference between the inputs varies from 90°, the output duty-cycle will no longer be 50%, resulting in an output DC value proportional to  $\Delta \phi$ . This manifests itself as a static phase error in the PLL.

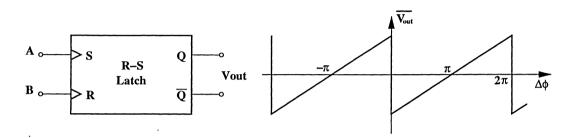

#### SR-Latch PD

The SR-Latch [12], is an edge-triggered 2-state PD. The rising edge of A drives Q to '1' and the rising edge of B resets Q to '0'. Hence, the differential output changes sign for every consecutive rising edges of the inputs. Inherently, the input and output frequencies are the same.

The advantages of the SR-latch are: (1) Monotonic Acquisition range of  $\pm 180^{\circ}$ , and (2) a DC output independent of the duty-cycle of the inputs as shown in Figure 3.3. The drawbacks of this cell are: (1) For applications that require frequency multiplication/synthesis, equal

input and output frequencies is undesirable, (2) In cases where one of the input frequencies is an integer multiple of the other, the SR-latch generates a nonzero DC output. As a result, PLLs employing an SR-Latch may lock onto a higher harmonic, and (3) the SR-latch provides only two output states, giving rise to significant ripple on the control line in the locked condition and hence producing greater jitter at the VCO output.

Figure 3.3: SR-latch PD and characteristic.

#### Sample-and-Hold PD

Linear PDs are characterized as having linear input-output characteristics, with minimal activity at the charge-pump after lock. Their drawback was in generating pulse-widths equal to a fraction of the clock period at high speeds. Digital PDs, on the other hand, employed simple flip-flops for the maximum speed, but provided only two output states creating significant ripple on the control line in the locked condition and hence producing greater jitter at the VCO output. The sample-and-hold PD proposed in [7], attempted to overcome these limitations.

The master-slave sample-and-hold (S&H) circuit is equivalent to an analog D-flipflop whereby each data transition samples the value of the VCO output as shown in Figure 3.4. The advantages of this topology are: (1) the master-slave configuration avoids a transparent path between  $D_{in}$  and  $V_{out}$  producing a voltage linearly proportional to phase difference for most of the period, and (2) the path with large switching transients operates at the data rate and not the VCO rate, minimizing the activity on the control voltage.

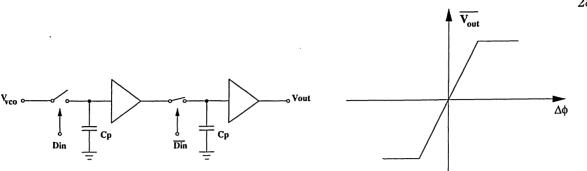

Figure 3.4: Sample-and-hold PD.

Figure 3.5: Sample-and-hold PD schematic.

An implementation of the S&H circuit is shown in Figure 3.5. The master and slave circuits are differential pairs whose tail current and load turn off simultaneously; storing the value of the VCO output on the parasitic capacitances  $C_{P1}$  to  $C_{P4}$ . The control circuit is implemented in PMOS transistors to allow for low-voltage operation.

The drawbacks of this circuit are: (1) limited acquisition range of  $\pm 50^{\circ}$  [7], (2) sensitivity to the input data pattern, and (3) the speed is limited by the current steering circuit.

# 3.2.2 Phase-Frequency Detectors PFD

The main drawback of phase-detectors is their periodic transfer characteristic, which implies that phase-shifts of  $2\pi$  cannot be distinguished. When the frequencies of the two input

signals are different, phase will accumulate, the output of PDs becomes unpredictable, depending on how far the loop is away from the lock state, acquisition time can suffer greatly if one of the PDs mentioned is used. A solution to extend the acquisition/tracking range and the lock speed of PLLs is to use phase-frequency detectors (PFDs) [1, 2, 12].

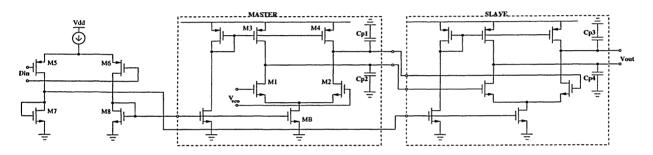

Phase-frequency detectors are able to sense phase as well as frequency differences when the loop is not locked. When in lock they behave as a PD, outputting a signal that is linearly proportional to the phase difference of the two input signals. In order to detect frequency differences, PFDs must contain memory, compared to the memoryless PDs. One possible solution is to implement PFDs as an edge-triggered sequential machine, as shown in Figure 3.6.

Figure 3.6: PFD state diagram.

The PFD functions as follows:

- $\omega_A < \omega_B$ : PFD produces positive pulses at  $Q_A$ , while  $Q_B$  remains at zero.

- $\omega_A > \omega_B$ : PFD produces positive pulses at  $Q_B$ , while  $Q_A$  remains at zero.

- $\omega_A = \omega_B$ : PFD produces positive pulses at either  $Q_A$  or  $Q_B$  with a width proportional to the phase-difference between the two input signals.

Ideally,  $Q_A$  and  $Q_B$  are never high at the same time since they control the charging and discharging of the CP. Consequently, the three logical states are as seen in Figure 3.6. Assuming the circuit is rising-edge triggered, and we start in State 0, a transition on A takes it to State I, another transition on B takes it to State O and so on... Two possible implementations of the PFD are presented.

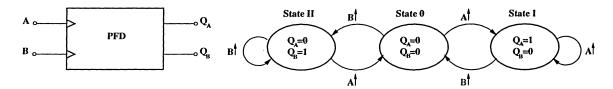

#### Two-XOR PFD

The Two-XOR PFD is used in conjunction with a 4 stage ring VCO generating eight differential clock signals *CLK1* through *CLK4* spaced by 45°. The Data\_Lead signal is the resultant of XORing the CLK1 and CLK3 signals and hence is a periodic signal that acts as a charge-down signal, while the Data\_Lag signal is the non-periodic signal, resultant of XORing the CLK1 and Data signals and acts as the charge-up signal. Figure 3.7 illustrates the operation of the Two-XOR PFD [6].

Figure 3.7: 2-XOR PFD.

The PFD achieves locked state when the signals *Data* and *CLK3* are phase-aligned as shown in Figure 3.7. The Data\_Lead and Data\_Lag signal transitions occur at the same time and the control voltage stays at the same level.

In the case of the input data is faster than CLK3, then the 'High' state of the lag signal is shorter than that of the lead signal, the CP discharges and the clock period becomes shorter to track the input. The opposite happens when the input data is slower than CLK3.

An example of frequency correction occurs when the frequency of the input data is faster than the clock, then the surplus part of the lead signal discharges current, so the clock can track the data.

The advantages of the Two-XOR PFD are its ease of implementation, its large acquisition range, and high lock speed. However, when it comes to long string of ones and zeros, the

#### D- Flipflop PFD

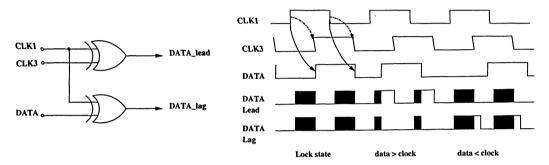

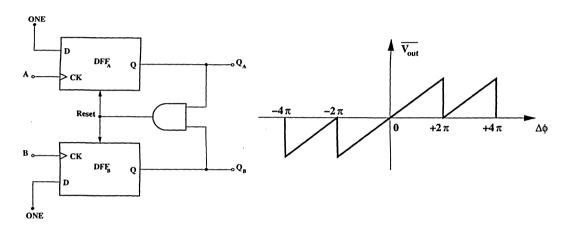

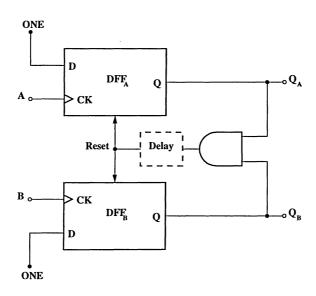

Another implementation of the PFD is shown in Figure 3.8 [9]. The PFD employs two edge-triggered resettable D-Flip-flops and an AND gate. The data inputs of the DFF are connected to logic 'ONE' with the clock inputs being the input signals A and B.

Figure 3.8: D-Flipflop PFD, and characteristic.

The PFD functions as follows: Starting in State 0 ( $Q_A=Q_B=0$ ), a transition on A causes  $Q_A$  to go 'HIGH', further transitions on A will have no effect on  $Q_A$ . A transition on B, will cause  $Q_B$  to go 'HIGH', activating the AND gate and resetting both DFF. It is important to note the non-periodic behavior of the transfer characteristic for the PFD shown in Figure 3.8, when the phase difference is too large, the PFD enters the FD mode.

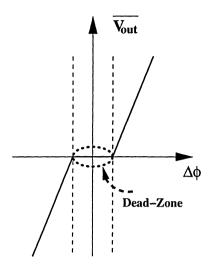

Since the PFD detects phase and frequency differences, it is characterized as having a wide Acquisition range, high lock speed, an output independent of input signal duty-cycle, and a constant gain over a phase error of  $\pm 360^{\circ}$  as shown in Figure 3.8. Its drawbacks include: (1) output jitter due to the meta-stability during lock condition, and (2) Dead-Zone due to the delay associated with the DFF and AND gate to be explained in the following section.

#### Dead-Zone

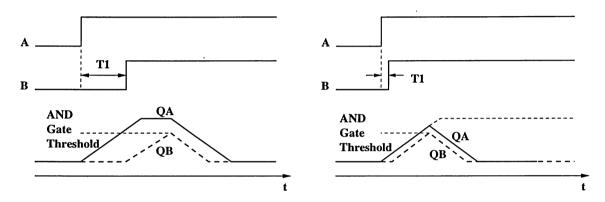

The dead-zone problem occurs, when a PFD is used in conjunction with a Charge-Pump (CP). The delay associated with the DFF and AND gate compared to that of the charging of the capacitor at the CP switches, will determine whether the system is in the dead-zone region or not [1, 2].

Figure 3.9: Dead-zone.

The dead-zone problem is better understood in conjunction with Figure 3.9. In the figure to the left, the phase difference between the two input signals A and B is large enough for the signals  $Q_A$  and  $Q_B$  to reach full logic levels of 'ONE'. In other words, there is enough time for the signal  $Q_A$  to charge the capacitor  $C_P$ . In the figure to the right, the time or phase-difference between the two input signals is too small, and the PFD resets before signal  $Q_A$  reaches a full logic level. In essence the CP switch fails to turn on for an ill-defined length of time. For such small phase differences, the gain of the PFD drops drastically as shown in Figure 3.10.

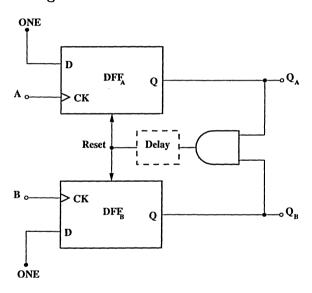

If the phase difference is within the dead-zone, the PLL will fail to correct itself and the deadzone will manifest itself as peak-peak jitter at the output. To avoid the dead-zone, a short delay is inserted between the output of the AND gate and the reset pins of the DFF

Figure 3.10: Dead-zone characteristic.

Figure 3.11: Dead-zone free PFD.

as shown in Figure 3.11 [10]. The delay for the reset signal must be long enough to allow for the full switching of the UP and DN pulses and CP switches. Caution should be exercised when choosing the length of the pulse as not to limit the operating frequency of the PFD to:

$$f_{max} = \frac{1}{2\Delta T}. (3.3)$$

1

# 3.3 Conclusions

The architectures and design considerations of CMOS phase-frequency detectors for phase-locked loops have been presented. Basic PDs have simple configurations, however, they suffer from slow lock speed, narrow acquisition range, periodic input-output transfer characteristic and non-monotonic gain. PFDs have complex configurations but provide high locking speed, wide tracking range, linear, monotonic and non-periodic input-output transfer characteristic. However they suffer from the 'dead-zone' problem.

# Chapter 4

# Charge Pumps

Phase-locked loops play a critical role in mixed analog-digital systems, such as clock distribution networks and frequency synthesizers [1]. The noisy environment of these systems, mainly caused by the digital portion, imposes challenges on the design of phase-locked loops. Charge pumps that convert digital outputs from phase-frequency detectors into analog control signals for local oscillators are an essential component of phase-locked loops.

In Chapter 2, we explained the benefits of using a CP-PLL over a basic PLL. What concerns us in this chapter is the performance criteria of the charge-pumps and their effect on the performance of phase-locked loops. In clock and data recovery (CDR) applications, the maximum data bandwidth achievable is determined by the clock skew between the internal and external clocks. Clock skew is mainly determined by the non-idealities of charge pumps. Similarly, in frequency synthesis applications, phase-noise can be minimized by increasing the PLL's loop-bandwidth, hence the need for a high-speed CP. Moreover, charge pumps are the dominant block of a phase-locked loop that determines the level of unwanted FM modulation which gives rise to reference spur [13].

Many architectures of charge pumps have emerged recently. A comprehensive review of the architectures of CMOS charge pumps and an in-depth comparison of their characteristics such as, speed, minimum supply voltage, mismatch-induced errors, charge injection and clock

feed-through induced errors, and noise rejection, is presented in this chapter. Section 4.1 introduces the concept of a charge-pump and it's importance to a PLL. Section 4.2 elaborates on the performance evaluators as well as the non-idealities of a charge-pump. Section 4.3 analyzes the basic charge-pump configurations. The more advanced current-steering and differential current-steering charge-pumps are analyzed in Sections 4.4 and 4.5. Miscellaneous charge-pumps are presented in Section 4.6 and the chapter is summarized in Section 4.7.

# 4.1 Functionality

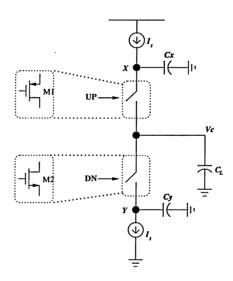

A CP consists of two switched current sources driving the loop filter, as shown in Figure 4.1. Ideal switching is realized by a three-state phase-frequency detector. The UP and DN signals are non-overlapping.

Figure 4.1: Conceptual representation of a charge pump.

Depending on which switch is activated, the CP will either charge or discharge the load capacitor according to Table 4.1. The third state is known as the locked state in which both switches are open and the voltage across the load capacitor remains unchanged.

**Table 4.1:** Charge Pump Functionality.

| UP   | DN   | Output State $V_c$ |

|------|------|--------------------|

| High | Low  | Charge             |

| Low  | High | Discharge          |

| Low  | Low  | Locked             |

In reality, MOS transistors implementing these switches suffer from device mismatches and current-leakage that give rise to clock-skew and reference spurs in the output of the PLL.

These non-ideal effects are explained in greater detail in the following section.

# 4.2 Non-ideal Effects

As mentioned before, device mismatches and current-leakage result in a phase error that translates into timing jitter or modulation at the VCO output. These errors are analyzed below.

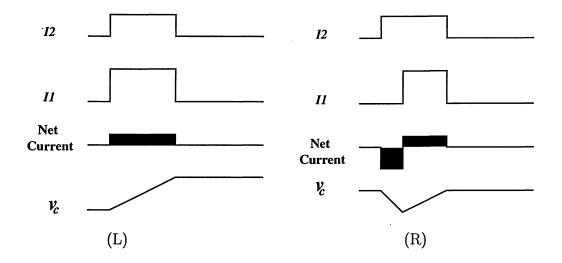

#### 4.2.1 Mismatches

#### Current Mismatch

The current sources I1 and I2 in the CP are essentially transistors biased in the saturation region. Non-idealities in the current mirrors or biased transistors causes static current mismatches between the two transistors. The difference between the charging and discharging currents causes a change or ripple in the control voltage  $V_c$  at each phase comparison as shown in Figure 4.2 (L).

The current mismatch and consequent ripple voltage translates to a phase-error defined as:

$$\phi_{\epsilon} = 2\pi \frac{\Delta t_{on}}{T_{ref}} \frac{\Delta i}{I} , \qquad [rad]$$

(4.1)

Figure 4.2: (L) Current mismatch, and (R) Pulse-width mismatch.

where  $T_{ref}$  is the reference clock period, I is the charge-pump current,  $\Delta i$  is the current mismatch assumed to be greater than zero and  $\Delta t_{on}$  is the turn on time of the PFD. It is important to note that to avoid the dead zone,  $\Delta t_{on}$  has a minimum limit.

For a third order PLL, the phase-error  $\phi_{\epsilon}$  translates to a reference spur  $P_r$  (noise) [13]:

$$P_r = 20 \log(\frac{1}{\sqrt{2}} \frac{f_{BW}}{f_{ref}} N \phi_{\epsilon}) - 20 \log(\frac{f_{ref}}{f_{p1}}), \qquad [dBc]$$

(4.2)

where N is the division value,  $f_{BW}$  is the loop bandwidth,  $f_{ref}$  is the reference clock frequency and  $f_{p1}$  is the frequency of the pole in the loop filter.

Moreover, due to the inhibited low output impedance property of short-channel Mosfets [12], dynamic current mismatch occurs, where the current mismatch  $\Delta i$  varies with  $V_c$ . To counter this error, the PLL locks with a finite phase error as shown in Figure 4.2(R) such that the average current per cycle is zero.

#### Timing Mismatch

The UP signal in Figure 4.1 must be active-low, hence the need for an inverter between the PFD and the charge pump (CP). The timing mismatch that is a resultant of the delay introduced by the inverter produces a phase error and a consequent spur that equals [13]:

$$P_{r} = 20 \log(\frac{f_{BW}}{f_{ref}} N \frac{(2\pi)^{2}}{\sqrt{2}} \frac{\Delta t_{on}}{T_{ref}} \frac{\Delta t_{d}}{T_{ref}}) - 20 \log(\frac{f_{ref}}{f_{p1}}), \qquad [dBc]$$

(4.3)

where  $\Delta t_d$ , the inverter delay is much less than  $\Delta t_{on}$ .

A simple solution to the delay problem is to insert a complementary pass gate before the DN signal to equalize the delay [1].

#### 4.2.2 Switch Induced Errors

# Charge Injection (ON $\Rightarrow$ OFF)

Charge injection occurs when a switch moves from an ON state to an OFF state. When a MOS switch is ON, it operates in the triode region. During that time it holds mobile charges in its channel. Upon turning OFF, the charge must flow out of the channel and into the drain and source.

For the DN switch depicted in Figure 4.1, the total charge it holds in an ON state is:

$$Q_{on} = -WLC_{ox}(V_{DN} - V_{tn} - V_Y), \qquad (4.4)$$

where W, L,  $C_{ox}$ , are the width, length, and oxide capacitance of the DN switch.  $V_{DN}$ ,  $V_{tn}$ , and  $V_Y$  are voltage of the DN signal, the threshold voltage of the DN switch, and the voltage at node Y.

When turned OFF, a portion of this charge will flow back to  $V_Y$ , while the rest, a fraction K will flow into the load capacitance  $C_L$ . The fraction K is the charge injection error. The

voltage-error at the output due to charge injection is calculated by:

$$\Delta V'_{out} = \frac{\Delta Q_{on}}{C_L} = \frac{-KWLC_{ox}(V_{DN} - V_{tn} - V_Y)}{C_L}.$$

[V] (4.5)

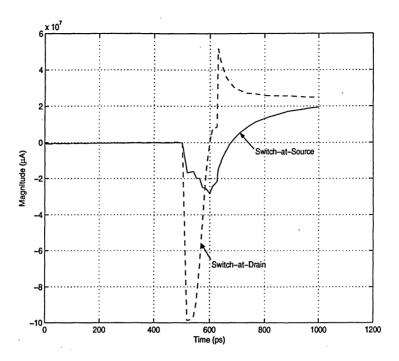

Clearly, charge injection introduces a non-linear signal dependent error at the output voltage  $(V_{tn})$  has a non-linear relationship with  $V_Y$ ). It was shown in [14] that if a MOS transistor is turned OFF while in saturation, all the channel charge flows into the source, leaving the drain terminal unaffected (K=0). As a result, charge injection is avoided. As we shall see later on, positioning the switch relative to the current-sources will determine the severity of charge-injection.

#### Clock Feedthrough

Clock feedthrough is due to the overlap parasitic capacitances  $C_{ov}$ . The error occurs when the fast rise and fall edges of a clock signal at the gate is coupled into the output node via the gate-to-source and gate-to-drain overlap capacitances, causing a sufficient rise of the signal level above the supply voltage. This rise in signal level could forward bias the junction diodes resulting in a electron injection into the substrate that can potentially lead to faulty operation, if it is conducted by a nearby high-impedance node [14][26]. It is important to note that clock feedthrough error is signal independent and manifests itself as an offset voltage  $\Delta V''_{out}$  that is calculated according to:

$$\Delta V_{out}'' = \frac{-C_{para}(V_{DD} - V_{SS})}{C_{para} + C_L}, \qquad [V]$$

$$(4.6)$$

where  $C_{para}$  is the parasitic capacitances,  $V_{DD}$  and  $V_{SS}$  are the high and low voltage levels of the clock.

## 4.2.3 Charge Sharing (OFF⇒ ON)

Charge sharing occurs when switches in a CP move from an OFF state to an ON state. While the input of the CP is the output of a three-state PFD, where-by the UP and DN switches of the CP can not be ON simultaneously, charge-sharing is the accumulative effect of output voltage non-compliance due to each switch moving from the OFF to ON state. Charge sharing is the resultant of the finite drain capacitances  $C_Y$  and  $C_X$  of the charging and discharging currents respectively.

The process is best explained in conjunction with Figure 4.1. When the switches are OFF, the voltage at node X and Y are  $V_{dd}$  and ground, respectively. The output node  $V_c$  is floating. When the switches are turned ON, the voltage at node X will decrease and that on node Y will increase, resulting in charge sharing between  $C_L$ ,  $C_X$ , and  $C_Y$ , which causes a deviation in the output voltage  $V_c$ .

It is important to note, that even if the voltage drop across the two switches is equal,  $I_1$  and  $I_2$  are equal and in-phase and the parasitics at node X and Y are equal, this will not avoid charge-sharing. To see why, let us consider the case where  $V_c$  is high (larger than the equilibrium midpoint voltage  $V_{dd}/2$ ) when the switches are OFF. Turning ON the switches will lead to a voltage fluctuation at node Y that is much larger than the fluctuation at node X, this difference in voltage change must be supplied from  $C_L$  resulting in charge-sharing.

The effect of charge or current leakage can be mathematically computed. Eq. 7.5 conveys the phase-offset due to charge-sharing and Eq. 7.6 gives the consequent reference spur in a third-order PLL [20].

$$\phi_{\epsilon} = 2\pi \frac{I_{leak}}{I_{cp}}, \qquad [rad] \tag{4.7}$$

$$P_r = 20 \log(\frac{1}{\sqrt{2}} \frac{f_{BW}}{f_{ref}} N \phi_{\epsilon}) - 20 \log(\frac{f_{ref}}{f_{p1}}).$$

[dBc] (4.8)

In later sections, it will become clear that by moving the position of the switches away from the output node, the effect of charge-sharing can be minimized. To better understand how the structure of a charge-pump can affect the performance due to the non-ideal effects mentioned prior, the following sections will present the basic charge-pumps, current-steering charge-pumps, and differential charge-pumps.

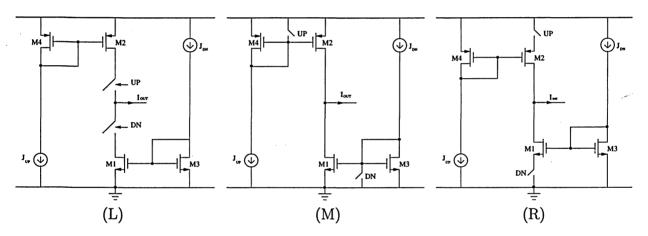

# 4.3 Basic Charge Pumps

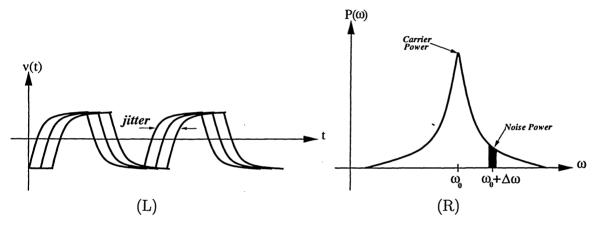

Figure 4.3 presents three single ended charge-pumps, differing only in the location of the switches. From Left to Right, each CP will be analyzed, its defects explained, setting the stage to explain the advantages of using the more advanced CP's.

Figure 4.3: (L)Switch at Drain CP, (M)Switch at Gate CP, and (R)Switch at Source CP.