#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2011

# Current-mode techniques for UWB frequency synthesizers

Dominic DiClemente *Ryerson University*

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

DiClemente, Dominic, "Current-mode techniques for UWB frequency synthesizers" (2011). Theses and dissertations. Paper 878.

This Dissertation is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# CURRENT-MODE TECHNIQUES FOR UWB FREQUENCY SYNTHESIZERS

by

Dominic DiClemente Bachelor of Engineering, Ryerson University, 2005

A dissertation presented to Ryerson University in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY in the Program of ELECTRICAL AND COMPUTER ENGINEERING

> Toronto, Ontario, Canada 2011 © Dominic DiClemente 2011

I hereby declare that I am the sole author of this dissertation.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the pupose of scholarly research.

Dominic DiClemente

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other

means, in total or in part, at the request of other institutions or individuals for the pupose of scholarly research.

Dominic DiClemente

# Abstract

#### Dominic DiClemente

Current-Mode Techniques for UWB Frequency Synthesizers Doctor of Philosophy, Electrical and Computer Engineering, Ryerson University, 2011

This thesis deals with current-mode techniques for ultra-wide band applications.

An overview of ultra-wide band (UWB) wireless communications is presented. Two standards for UWB data communications, namely direct-synthesis UWB (DS-UWB) and Multi-band orthogonal frequency division multiplexing (MB-OFDM) UWB are presented. MB-OFDM UWB devices must hop among 14 UWB channels within 9.5 ns, imposing stringent constraints on design of frequency synthesizers. A review of the state-of-the-art frequency synthesizers for MB-OFDM UWB applications is provided.

Current-mode phase-locked loops with active inductors and active transformers employed in both loop filters and voltage-controlled oscillators are proposed and their performance is analyzed. Current-mode phase-locked loops decouple the PLL dynamic range from the scaling down of the supply voltage.

An active-inductor VCO with both coarse and fine frequency adjustment, a hybrid VCO with a step-down passive transformer loaded with an active inductor, and a hybrid VCO with a step-up passive transformer loaded with a varactor are proposed and their performances are analyzed. These VCOs obtain wide frequency tuning ranges without relying on

switched back networks.

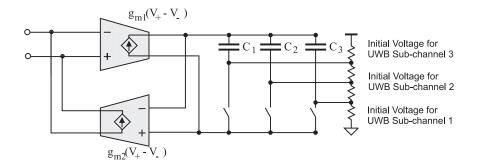

To meet the timing constraint of UWB frequency synthesizers, Current-mode techniques are further developed for UWB frequency synthesizers. An active inductor with a bank of switched capacitors is proposed to provide fast locking. The bank of switched capacitors eliminates the frequency acquisition locking time of the frequency synthesizer, allowing 9.5 ns phase locking time.

The proposed current-mode phase-locked loops, active-inductors oscillators and hybrid oscillators were designed and implemented in TSMC-0.18 $\mu m$  and IBM-0.13 $\mu m$  CMOS technologies.

# Acknowledgments

First and foremost I would like to thank my advisor Dr. Fei Yuan for his guidance and inspiration during my tenure at Ryerson. His professionalism and enthusiasm during our weekly meetings always spurred me on to improve my work and provide inspiration to my research. I would also like to thank him for providing me with the freedom and atmosphere that allowed me to flourish and to take many tangents in my studies.

I also thank Dr. Raahemifar for providing an unequaled enthusiasm for teaching and education during my undergraduate studies and Professor Mike Kassam for providing me with an opportunity to grow and mature as an educator.

I am also indebted to support staff Jason Naughton, Dan Giannitelli and Jim Koch. They had always been a source of last minute technical support, all too often being called upon to solve software problems with looming deadlines. Their light hearted attitudes and expertise have always been reassuring during panicked moments.

I would also like to take the opportunity to thank my fellow students in the MCS group and other students who shared ENG313 lab with us. A special thank goes to Adrian Tang who has always been a wealth of knowledge and uncontainable energy, Nima Soltani, for being a valuable friend during long hours in the lab, and Tarek Khan, for his correspondence with CMC and MOSIS, as well as being a friend and valued colleague.

Most importantly, I thank my family, their love and support provided me the opportunity to continue my education for as long as I wanted.

# Contents

| Ab | Abstract |                                               |    |  |  |

|----|----------|-----------------------------------------------|----|--|--|

| Ac | know     | ledgments                                     | v  |  |  |

| 1  | Intro    | oduction                                      | 1  |  |  |

|    | 1.1      | Ultra Wide-Band                               | 1  |  |  |

|    | 1.2      | Objectives                                    | 7  |  |  |

|    | 1.3      | Contributions                                 | 7  |  |  |

|    | 1.4      | Thesis Organization                           | 9  |  |  |

| 2  | Freq     | uency Synthesizers for Ultra WideBand devices | 11 |  |  |

|    | 2.1      | Multi-Band OFDM UWB                           | 12 |  |  |

|    | 2.2      | Lock Time and Bandwidth Requirements of UWB   | 16 |  |  |

|    | 2.3      | Delay-Locked Loop Frequency Synthesizer       | 18 |  |  |

|    | 2.4      | Miller Divider Based Frequency Synthesizer    | 19 |  |  |

|    | 2.5      | Direct Synthesis Frequency Synthesizers       | 21 |  |  |

|    | 2.6      | Performance Comparison                        | 23 |  |  |

|    | 2.7      | Chapter Summary                               | 24 |  |  |

| 3  | Cur      | rent-Mode Phase Locked Loops                  | 27 |  |  |

|    | 3.1      | Low-Voltage Voltage-Mode PLLs                 | 29 |  |  |

|   | 3.2               | Current-Mode Filtering                                                                 |                                                    |                                                                                                                        |

|---|-------------------|----------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                   | 3.2.1                                                                                  | Current-Mode Loop Filter                           | 31                                                                                                                     |

|   |                   | 3.2.2                                                                                  | Gyrator-C Floating Active Inductors                | 33                                                                                                                     |

|   | 3.3               | Curren                                                                                 | t-Controlled Oscillator                            | 35                                                                                                                     |

|   |                   | 3.3.1                                                                                  | Replica Bias for Active Inductor VCOs              | 36                                                                                                                     |

|   | 3.4               | Loop I                                                                                 | Dynamics of Active-Inductor based Current-Mode PLL | 39                                                                                                                     |

|   |                   | 3.4.1                                                                                  | Type I Current-Mode PLLs                           | 40                                                                                                                     |

|   |                   | 3.4.2                                                                                  | Type II Current-Mode PLLs                          | 41                                                                                                                     |

|   |                   | 3.4.3                                                                                  | Non-ideal Cases                                    | 42                                                                                                                     |

|   | 3.5               | Phase                                                                                  | Noise of Current-Mode Active Inductor PLLs         | 44                                                                                                                     |

|   | 3.6               | Simula                                                                                 | ation Results of Active-Inductor Current-mode PLL  | 45                                                                                                                     |

|   | 3.7               | Chapte                                                                                 | er Summary                                         | 49                                                                                                                     |

|   |                   |                                                                                        |                                                    |                                                                                                                        |

| 4 | Cur               | rent-Ma                                                                                | de Phase Locked Loons with Active Transformers     | 51                                                                                                                     |

| 4 |                   |                                                                                        | ode Phase Locked Loops with Active Transformers    | <b>51</b>                                                                                                              |

| 4 | <b>Cur</b><br>4.1 | Curren                                                                                 | t-Mode Filtering                                   | 51                                                                                                                     |

| 4 |                   | Curren<br>4.1.1                                                                        | t-Mode Filtering                                   | 51<br>51                                                                                                               |

| 4 |                   | Curren<br>4.1.1                                                                        | t-Mode Filtering                                   | 51<br>51                                                                                                               |

| 4 | 4.1               | Curren<br>4.1.1                                                                        | t-Mode Filtering                                   | 51<br>51<br>53                                                                                                         |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS                                                                | t-Mode Filtering                                   | 51<br>51<br>53<br>53                                                                                                   |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS<br>4.2.1                                                       | t-Mode Filtering                                   | 51<br>51<br>53<br>53<br>54                                                                                             |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS<br>4.2.1<br>4.2.2                                              | t-Mode Filtering                                   | 51<br>51<br>53<br>53<br>54<br>55                                                                                       |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS<br>4.2.1<br>4.2.2<br>4.2.3                                     | t-Mode Filtering                                   | 51<br>51<br>53<br>53<br>54<br>55<br>56                                                                                 |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                            | t-Mode Filtering                                   | 51<br>51<br>53<br>53<br>54<br>55<br>56                                                                                 |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                   | at-Mode Filtering                                  | 51<br>51<br>53<br>53<br>54<br>55<br>56<br>58                                                                           |

| 4 | 4.1               | Curren<br>4.1.1<br>CMOS<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7 | t-Mode Filtering                                   | <ul> <li>51</li> <li>51</li> <li>53</li> <li>53</li> <li>54</li> <li>55</li> <li>56</li> <li>58</li> <li>59</li> </ul> |

|    | 4.5   | Simulation Results of Active-Transformer Current-Mode PLL | 64  |

|----|-------|-----------------------------------------------------------|-----|

|    | 4.6   | Chapter Summary                                           | 65  |

| 5  | Wid   | le-Band VCOs for Frequency Synthesizers                   | 68  |

|    | 5.1   | Wide-band VCOs                                            | 69  |

|    | 5.2   | Active-Inductor Ultra Wide-band VCO                       | 71  |

|    | 5.3   | Wide-Band Hybrid VCO with Active-Inductor Load            | 79  |

|    | 5.4   | Wide-Band Hybrid VCO with Varactor Load                   | 86  |

|    | 5.5   | Performance Comparison                                    | 94  |

|    | 5.6   | Chapter Summary                                           | 97  |

| 6  | UW    | B Current-Mode Frequency Synthesizer                      | 99  |

|    | 6.1   | Quick Hopping for UWB Frequency Synthesizer               | 100 |

|    | 6.2   | Wide-Band VCO                                             | 103 |

|    | 6.3   | Bang-Bang Phase Detector                                  | 104 |

|    | 6.4   | Injection locked Oscillator for Frequency Division        | 105 |

|    | 6.5   | Simulation Results                                        | 107 |

|    | 6.6   | Chapter Summary                                           | 109 |

| 7  | Con   | clusions                                                  | 111 |

|    | 7.1   | Thesis Summary                                            | 111 |

|    | 7.2   | FUTURE RESEARCH                                           | 113 |

| Aŗ | opend | lix A                                                     |     |

|    | Publ  | lications                                                 | 114 |

| Aŗ | opend | lix B                                                     |     |

|    | Glos  | ssary                                                     | 116 |

#### Bibliography

118

# **List of Tables**

| 1.1 | Parameters of commercially available wireless networks [2]                    | 2   |

|-----|-------------------------------------------------------------------------------|-----|

| 2.1 | Subcarriers of MB-OFDM UWB.                                                   | 13  |

| 2.2 | Data-rates of MB-OFDM.                                                        | 13  |

| 2.3 | Time-Frequency Codes for a Group 1 MB-OFDM hopping sequence                   | 14  |

| 2.4 | Comparison of state-of-the-art UWB frequency synthesizers                     | 25  |

| 3.1 | Effect of $V_{DD}$ fluctuation on the inductance of active inductors with and |     |

|     | without replica biasing.                                                      | 40  |

| 3.2 | Corner analysis results of the PLL (post-layout)                              | 49  |

| 5.1 | Comparison of wide band VCOs                                                  | 98  |

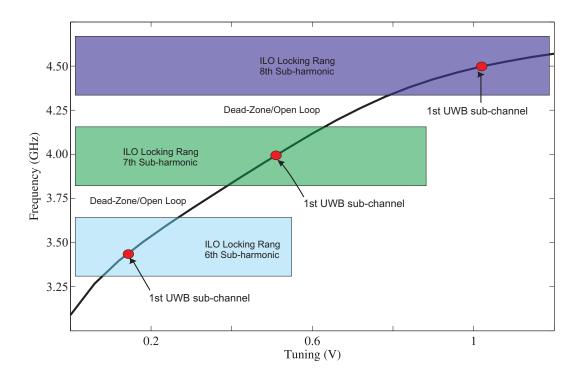

| 6.1 | Locking range of ILO harmonics                                                | 107 |

| 6.2 | Comparison of state-of-the-art UWB frequency synthesizers                     | 10  |

# **List of Figures**

| 1.1 | An example of an UWB wireless personal area network                       | 4  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Spectral allocations showing the proposed UWB and existing narrow-band    |    |

|     | interferers                                                               | 5  |

| 1.3 | FCC specified spectral mask for indoor UWB commercial devices, severely   |    |

|     | limiting the output spectrum outside of 3.7-10.3 GHz                      | 6  |

| 2.1 | Time-frequency kernel example code used for multiple user access as well  |    |

|     | as high channel efficiency.                                               | 15 |

| 2.2 | DLL based frequency synthesizer [14]                                      | 18 |

| 2.3 | Architecture of [15] showing a fixed synthesizer and modified Miller fre- |    |

|     | quency divider.                                                           | 20 |

| 2.4 | Miller frequency divider.                                                 | 20 |

| 2.5 | Modified Miller divider [15]                                              | 21 |

| 2.6 | UWB receiver using multiple RF paths tuned to each of their respective    |    |

|     | bands [26]                                                                | 22 |

| 2.7 | MB-OFDM frequency synthesizer based on direct synthesis [28]              | 23 |

| 2.8 | The output spectrum of [22] showing spurs                                 | 24 |

| 3.1 | Configuration of type II voltage-mode PLLs                                | 27 |

| 3.2 | Configuration of current-mode phase-locked loops.                         | 28 |

| 3.3  | Configuration of a supply regulated PLL.                                                                                                                   | 29 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4  | Configuration of a supply regulated VCO.                                                                                                                   | 30 |

| 3.5  | Configuration of a differentially tuned PLL.                                                                                                               | 31 |

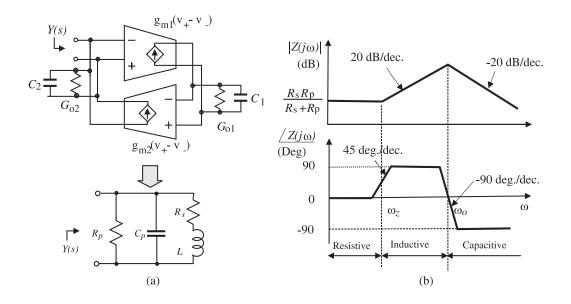

| 3.6  | Characteristics of current-mode loop filter                                                                                                                | 32 |

| 3.7  | (a) Configuration of floating gyrator-C active inductors. $G_{o1}$ and $C_1$ are                                                                           |    |

|      | the output conductance of transconductor 1 and the input capacitance of                                                                                    |    |

|      | transconductor 2, respectively. (b) Bodé plots of gyrator-C active inductors.                                                                              | 34 |

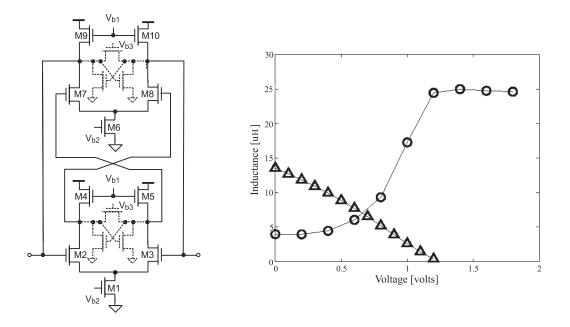

| 3.8  | Fully differential gyrator-C active inductor circuit. Circuit parameters :                                                                                 |    |

|      | $W_{1,6} = 5\mu m$ , $W_{2,3,7,8} = 0.5\mu m$ , $W_{4,5} = 100\mu m$ , and $W_{9,10} = 0.5\mu m$ .                                                         |    |

|      | $L=0.18 \mu m$ for all transistors. $\bigcirc$ - Dependency of the inductance of the                                                                       |    |

|      | floating active inductor on the biasing voltage $V_{b2}$ at 3 GHz. $\triangle$ - Large-                                                                    |    |

|      | signal behavior of the floating active inductor at 3 GHz                                                                                                   | 35 |

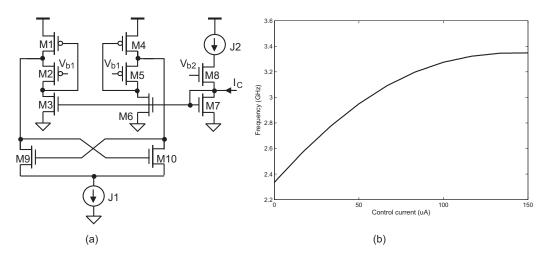

| 3.9  | (a) Current-controlled oscillator with current reuse active inductors. Circuit                                                                             |    |

|      | parameters : $W_1 = 10 \mu \text{m}$ , $W_2 = 3 \mu \text{m}$ , $W_{3\sim 4} = 10 \mu \text{m}$ , $W_{5\sim 6} = 5 \mu \text{m}$ , $W_7 = 10 \mu \text{m}$ |    |

|      | $5\mu$ m, $I_b = 1$ mA, $I_{b2} = 100\mu$ A, $V_b = 1$ V, $V_{b2} = 0.2$ V. (b) Frequency tuning                                                           |    |

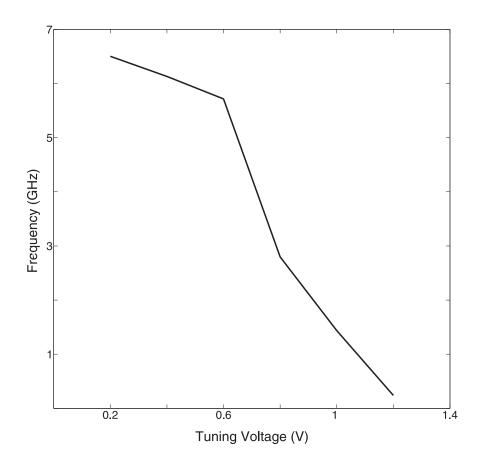

|      | range of the current-controlled oscillator                                                                                                                 | 36 |

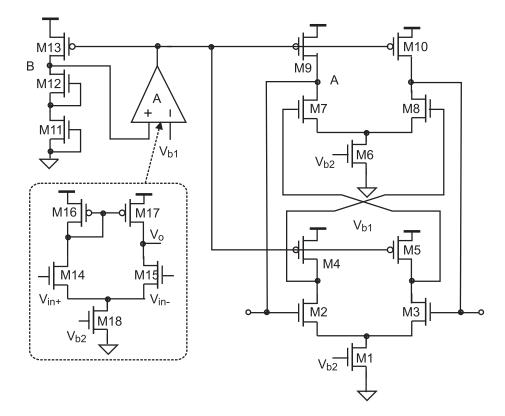

| 3.10 | Fully differential gyrator-C active inductor with replica biasing.                                                                                         | 37 |

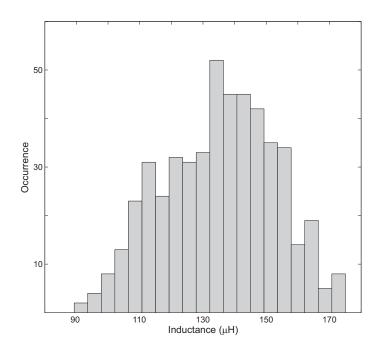

| 3.11 | Distribution of the inductance of the active inductor without replica biasing                                                                              |    |

|      | due to process variations (500 samples in Monte Carlo simulation) $\ldots$                                                                                 | 38 |

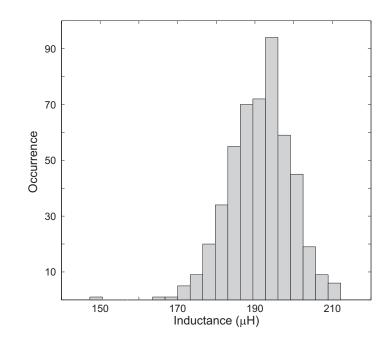

| 3.12 | 2 Distribution of the inductance of the active inductor with replica biasing                                                                               |    |

|      | due to process variations (500 samples in Monte Carlo simulation)                                                                                          | 39 |

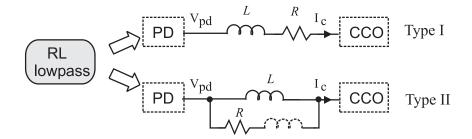

| 3.13 | Current-mode filters for type I and type II current-mode PLLs                                                                                              | 40 |

| 3.14 | Phase diagram for type I current-mode PLLs.                                                                                                                | 41 |

| 3.15 | Phase diagram for type II current-mode PLLs                                                                                                                | 41 |

| 3.16 | Phase diagram for type II current-mode PLLs with additional inductor                                                                                       | 42 |

| 3.17 | Phase noise analysis of Type I current-mode PLLs in the lock state                                                                                         | 44 |

|      |                                                                                                                                                            |    |

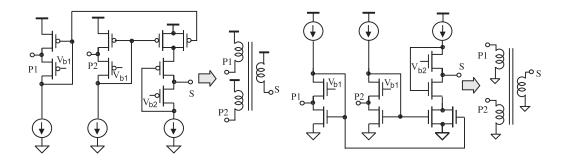

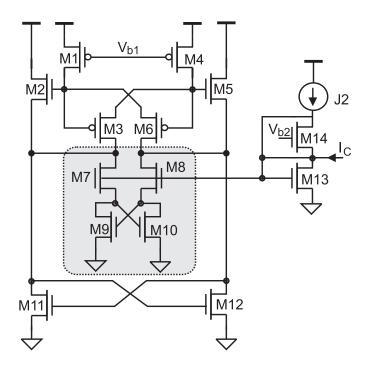

| Simplified schematic of the proposed current-mode PLL                                  | 45                                      |

|----------------------------------------------------------------------------------------|-----------------------------------------|

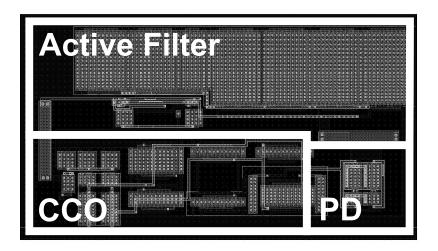

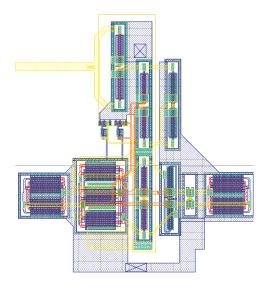

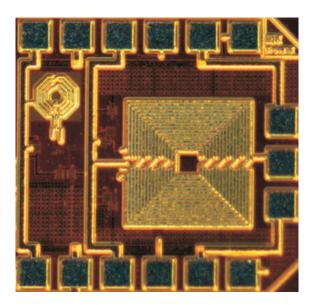

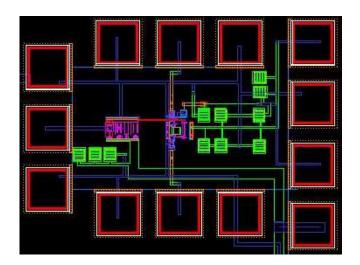

| Layout of the proposed current-mode PLL.                                               | 46                                      |

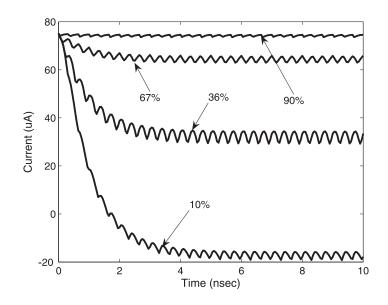

| Dependence of the output current of current-mode loop filter on the duty               |                                         |

| cycle of the input voltage (post-layout).                                              | 46                                      |

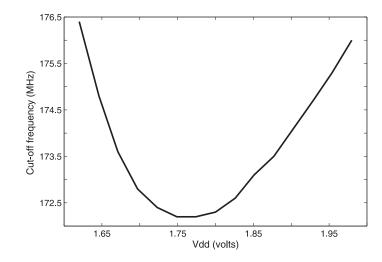

| Effect of the fluctuation of supply voltage on the cut-off frequency of the            |                                         |

| current-mode loop filter (post-layout).                                                | 47                                      |

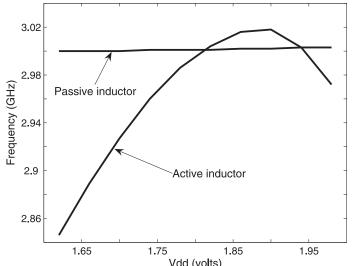

| Effect of the fluctuation of the supply voltage on the oscillation frequency           |                                         |

| of CCO (post-layout).                                                                  | 48                                      |

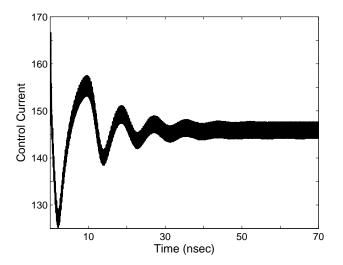

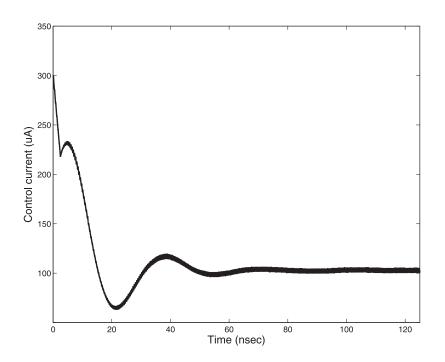

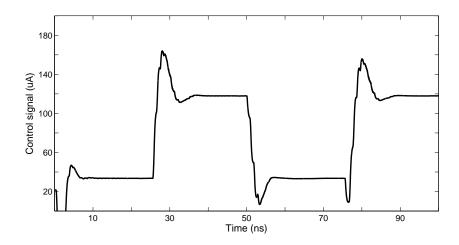

| Control current of the proposed current-mode PLL (post-layout)                         | 48                                      |

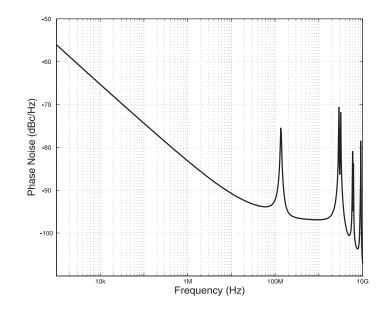

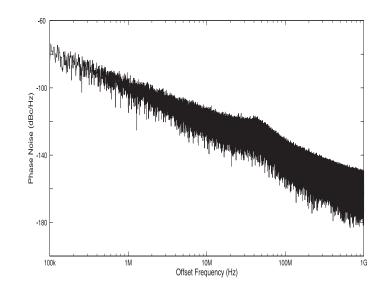

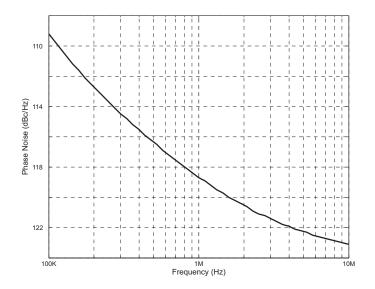

| Simulated Phase noise of the proposed current-mode PLL (post-layout)                   | 49                                      |

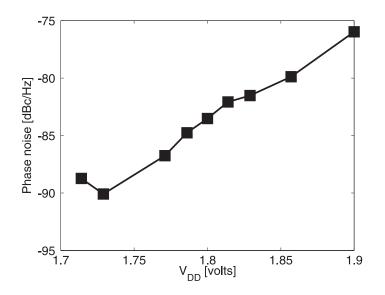

| Effect of $V_{DD}$ fluctuation on the phase noise of the proposed current-mode         |                                         |

| PLL at 1MHz frequency offset (post-layout).                                            | 50                                      |

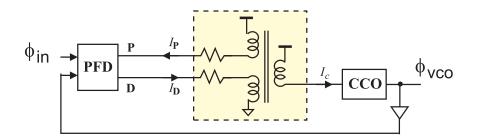

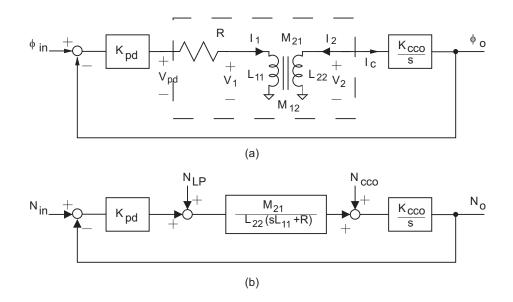

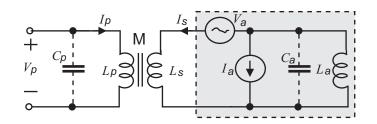

| Configuration of current-mode phase-locked loops using transformer filter-             |                                         |

|                                                                                        | 52                                      |

|                                                                                        |                                         |

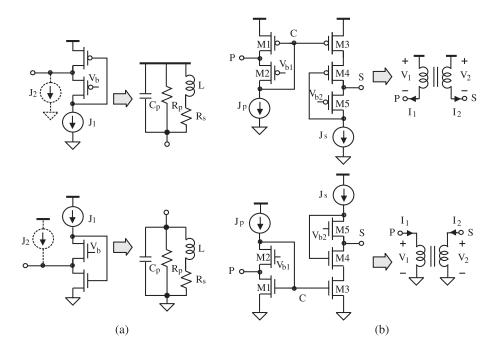

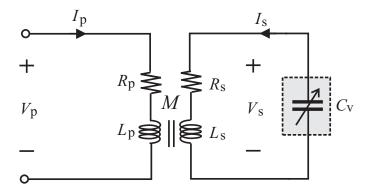

|                                                                                        | 55                                      |

|                                                                                        | E 1                                     |

|                                                                                        | 54                                      |

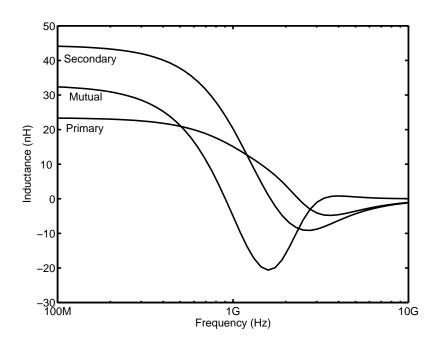

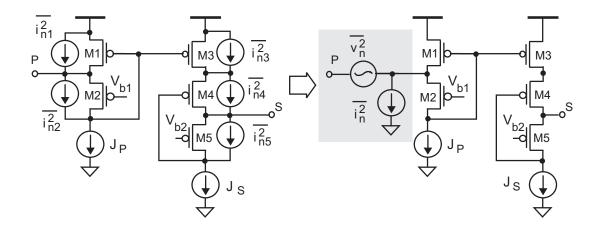

|                                                                                        |                                         |

| tual inductance from the primary winding to the secondary winding of the               |                                         |

| active transformer. Circuit parameters : $W = 50 \mu m$ , $L = 0.18 \mu m$ for all     |                                         |

| transistors, $J_p, J_s = 150 \mu A$ , $V_{b1} = 0.8$ V, and $V_{b2} = 0.2$ V           | 56                                      |

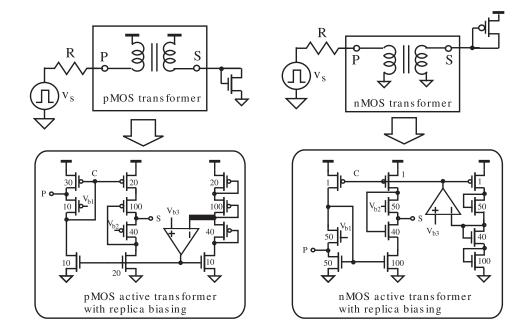

| Current-mode loop filter. pMOS active transformer: $V_{b1} = 1.2$ V, $V_{b2} = 1.2$    |                                         |

| V, $V_{b3} = 1.3$ V. nMOS active transformer: $V_{b1} = 0.7$ V, $V_{b2} = 0.7$ V,      |                                         |

| $V_{b3} = 0.5$ V. $R = 6k\Omega$ . $L = 0.18\mu$ m for all transistors. The numbers in |                                         |

| the figures are transistor width.                                                      | 57                                      |

|                                                                                        | Layout of the proposed current-mode PLL |

| 4.6  | Simulated dependence of the output current of active-transformer loop filter |    |

|------|------------------------------------------------------------------------------|----|

|      | on the duty cycle of the input voltage                                       | 58 |

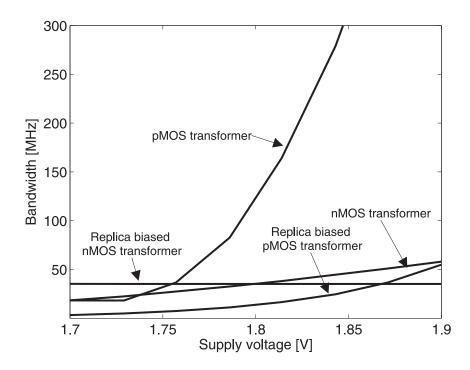

| 4.7  | Simulated sensitivity of the bandwidth of active-transformer loop filter to  |    |

|      | supply voltage.                                                              | 59 |

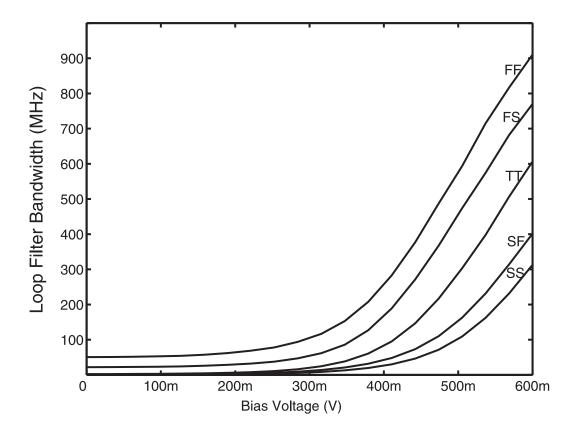

| 4.8  | The dependence of loop filter bandwidth on replica bias reference voltage    |    |

|      | at process corners and in nominal conditions.                                | 60 |

| 4.9  | Noise equivalent circuit of active transformer.                              | 61 |

| 4.10 | Active transformers with multiple windings                                   | 62 |

| 4.11 | Block diagram with noise sources of the PLL in lock state                    | 62 |

| 4.12 | Layout of the PLL.                                                           | 65 |

| 4.13 | Simulated control current of the PLL (post-layout).                          | 66 |

| 4.14 | Simulated phase noise of the PLL                                             | 67 |

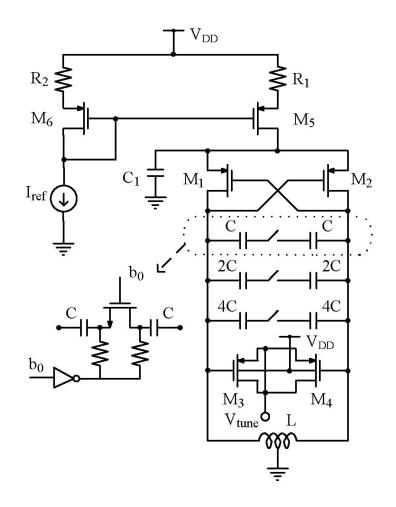

| 5.1  | Schematic of a wide-band VCO using a switched capacitor bank [66]            | 70 |

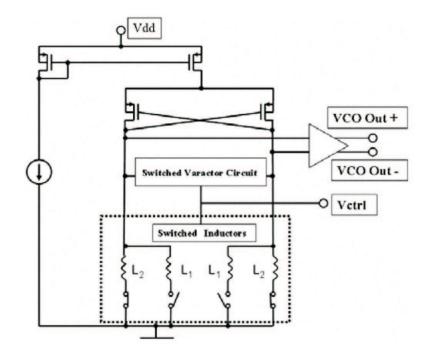

| 5.2  | Schematic of a wide-band VCO using a switched inductor bank [68]             |    |

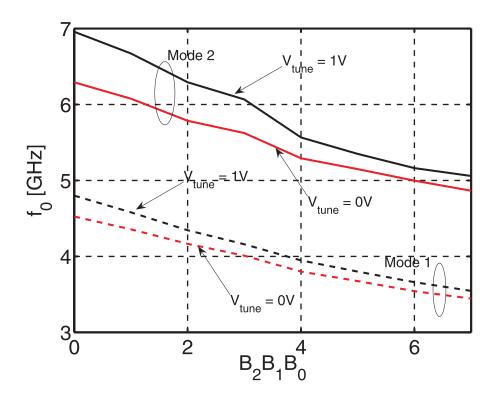

| 5.3  | VCO tuning curves of a 1-bit switched capacitor bank [69]                    |    |

| 5.4  | Schematic of Lu <i>at. al</i> active inductor VCO                            |    |

| 5.5  | Schematic of the proposed ultra wide-band VCO with dual tuning mecha-        |    |

|      | nisms.                                                                       | 74 |

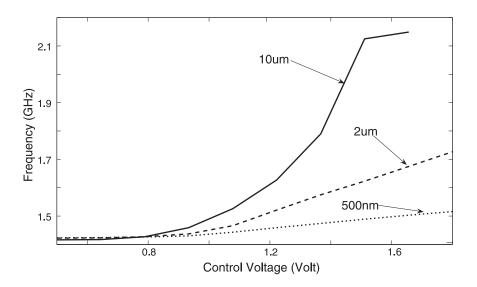

| 5.6  | Dependence of the oscillation frequency of VCO on $V_{b1}$                   |    |

| 5.7  | Dependence of the oscillation frequency of VCO on $V_{b2}$                   |    |

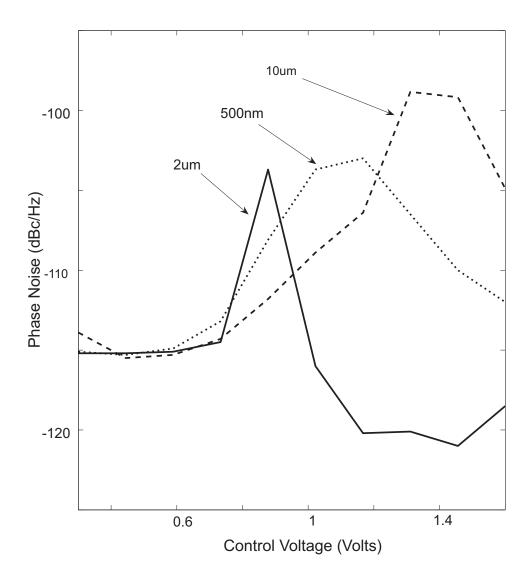

| 5.8  | Dependence of the phase noise of VCO on $V_{b2}$ and nMOS size               |    |

| 5.9  | Layout of VCO.                                                               | 78 |

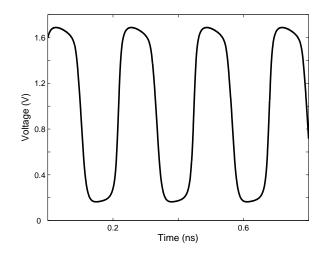

| 5.10 | Waveform of the output voltage of VCO                                        | 78 |

|      | Simulated phase noise of VCO                                                 | 79 |

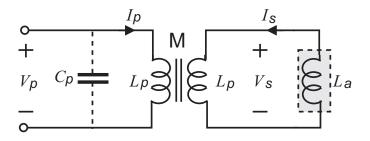

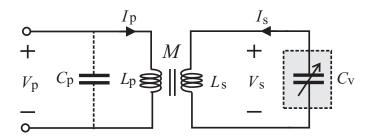

|      | Ideal transformer loaded with an active inductor.                            | 80 |

| 5.13 | Noise analysis of noiseless passive transformer loaded with a noisy active                                |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | inductor                                                                                                  | 82 |

| 5.14 | Quality factor analysis of passive transformer loaded with an active inductor.                            | 84 |

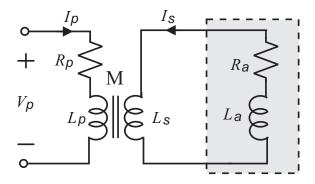

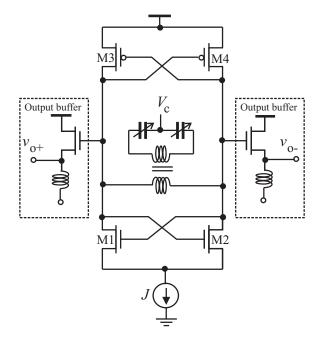

| 5.15 | (a) Proposed VCO. (b) Spiral inductor VCO. (c) Active inductor VCO                                        | 85 |

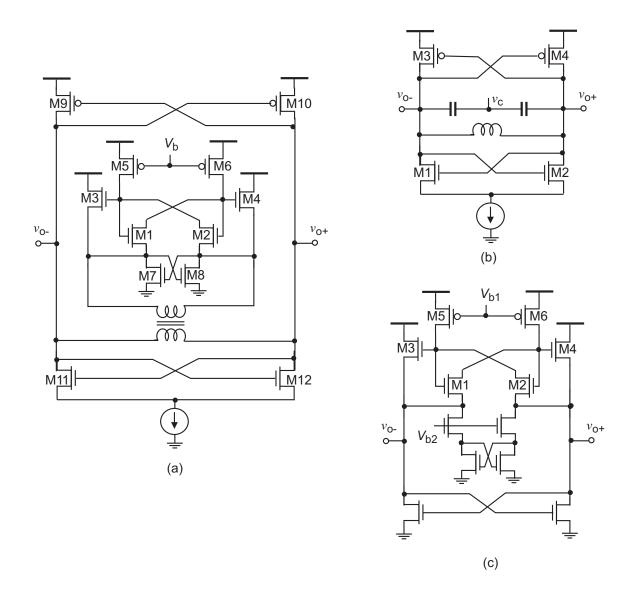

| 5.16 | Simulated frequency tuning of proposed VCO.                                                               | 86 |

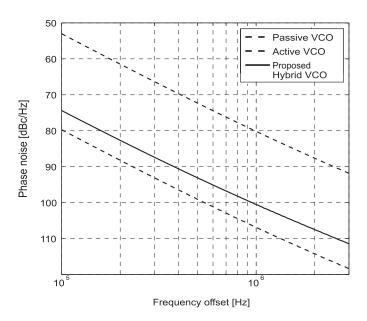

| 5.17 | Simulated phase noise of spiral inductor VCO, active inductor VCO, and                                    |    |

|      | proposed VCO (labeled Hybrid VCO)                                                                         | 87 |

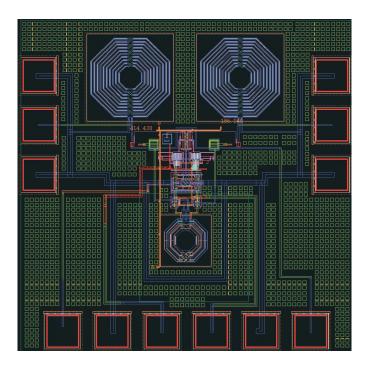

| 5.18 | Layout of proposed VCO                                                                                    | 88 |

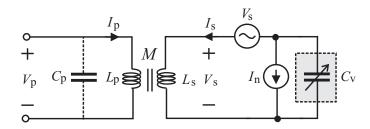

| 5.19 | Ideal transformer loaded with a varactor.                                                                 | 90 |

| 5.20 | Noise analysis of noiseless passive transformer loaded with a noisy sec-                                  |    |

|      | ondary circuit.                                                                                           | 91 |

| 5.21 | Quality factor analysis of transformer loaded with varactor                                               | 92 |

| 5.22 | Schematic of transformer VCO with reflected capacitance frequency tun-                                    |    |

|      | ing. Circuit parameters : $W_{1,2} = 60 \mu \text{m}$ , $W_{3,4} = 80 \mu \text{m}$ , tail current source |    |

|      | : nMOS transistor with $W = 250 \mu \text{m} L = 2 \mu \text{m}$ , V=1V. The buffer is a                  |    |

|      | differential pair with a balun load, the nMOS transistors are the same size                               |    |

|      | as the core ones, and the balun is 9.8 nH. Varactor : $L = 2\mu m$ , $W = 64\mu m$ .                      | 93 |

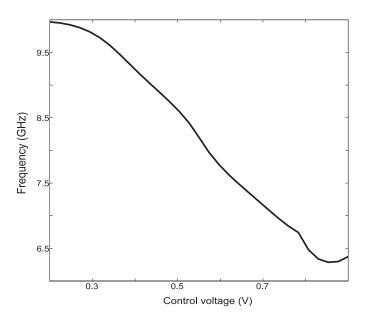

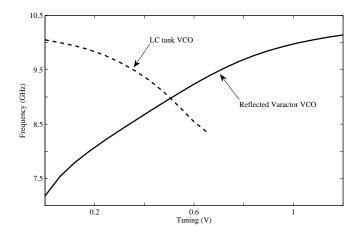

| 5.23 | Simulated frequency tuning of VCO with varactor loading the secondary                                     |    |

|      | and primary windings.                                                                                     | 94 |

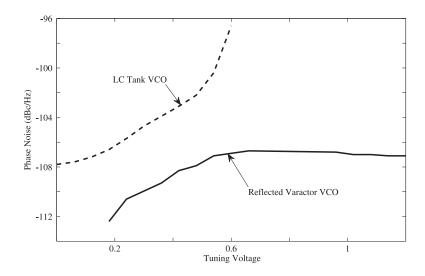

| 5.24 | Phase noise of VCO with varactor loading the secondary and primary wind-                                  |    |

|      | ings                                                                                                      | 95 |

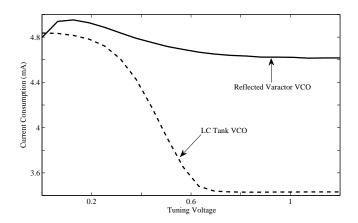

| 5.25 | Power consumption of VCO with varactor loading the secondary and pri-                                     |    |

|      | mary windings.                                                                                            | 95 |

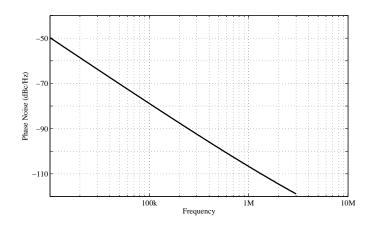

| 5.26 | Phase noise plot of the proposed VCO                                                                      | 96 |

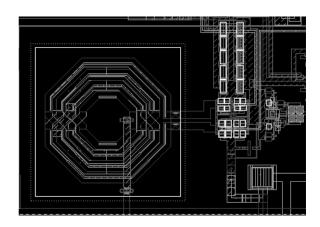

| 5.27 | Layout of proposed VCO                                                                                    | 96 |

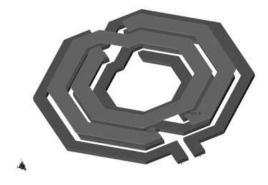

| 5.28 | Configuration of the transformer used in the hybrid VCO                                                   | 97 |

| 5.29 | Die photo of the transformer used in the hybrid VCO                                                       |

|------|-----------------------------------------------------------------------------------------------------------|

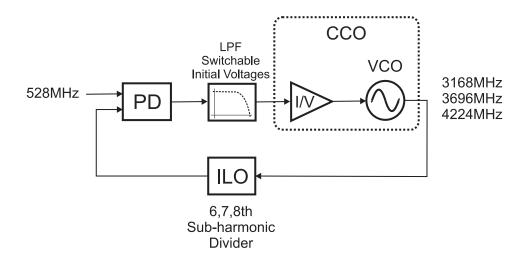

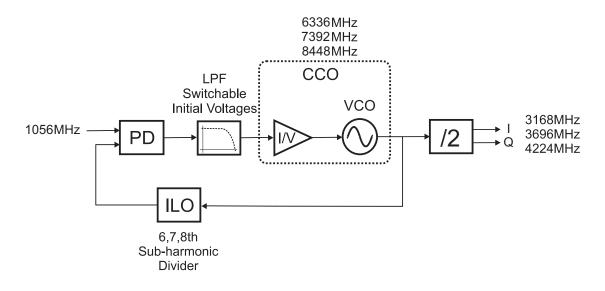

| 6.1  | Architecture of a frequency synthesizer utilizing the quick hopping scheme. 100                           |

| 6.2  | Schematic of proposed Mixer for frequency translation                                                     |

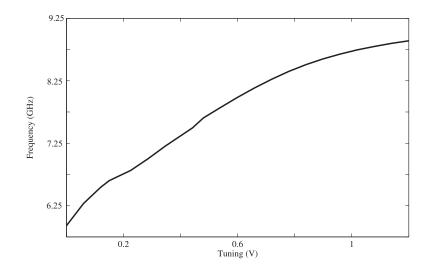

| 6.3  | CCO tuning curve showing the UWB sub-channels including the locking                                       |

|      | range of the ILO                                                                                          |

| 6.4  | Final topology of the current-mode UWB frequency synthesizer 103                                          |

| 6.5  | Schematic of transformer VCO with reflected capacitance frequency tun-                                    |

|      | ing. Circuit parameters : $W_{1,2} = 60 \mu \text{m}$ , $W_{3,4} = 80 \mu \text{m}$ , tail current source |

|      | : nMOS transistor with $W = 250 \mu \text{m}$ $L = 2 \mu \text{m}$ , V=1V. The buffer is a                |

|      | differential pair with a balun load, the nMOS transistors are the same size                               |

|      | as the core ones, and the balun is 9.8 nH. Varactor : $L = 2\mu m$ , $W = 64\mu m$ . 104                  |

| 6.6  | Simulated frequency tuning of VCO with varactor loading the secondary                                     |

|      | and primary windings                                                                                      |

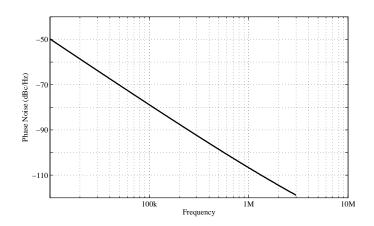

| 6.7  | Phase noise plot of the Wide-Band Hybrid VCO with Varactor Load 105                                       |

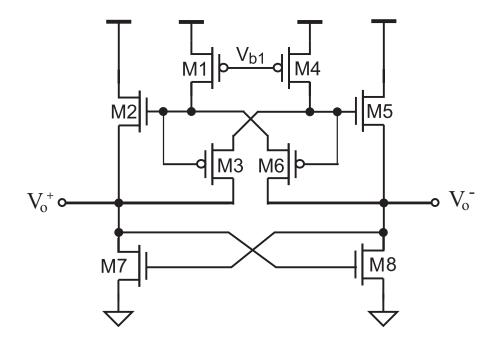

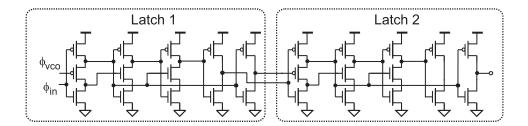

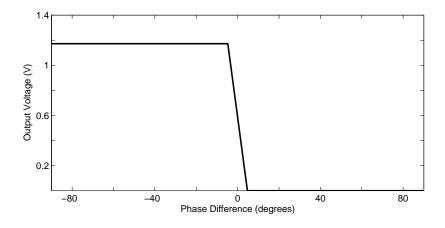

| 6.8  | Schematic of bang-bang phase detector                                                                     |

| 6.9  | Output voltage of Bang-Bang phase detector                                                                |

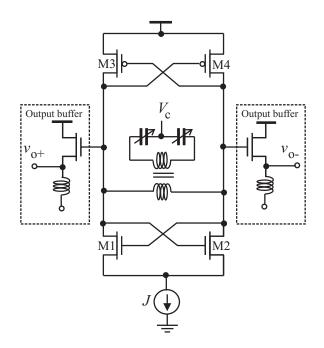

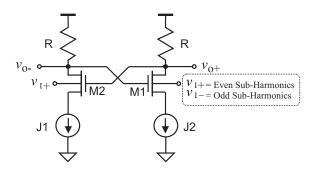

| 6.10 | Schematic of proposed ILO                                                                                 |

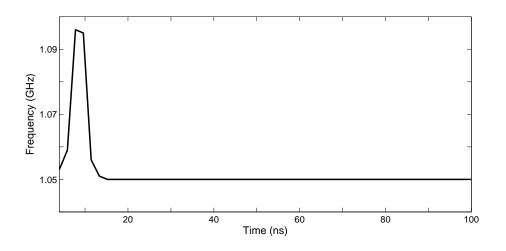

| 6.11 | Locking transient of ILO                                                                                  |

| 6.12 | Layout of proposed ILO                                                                                    |

| 6.13 | Locking characteristics of the proposed UWB Current-mode frequency syn-                                   |

|      | thesizer                                                                                                  |

# Chapter 1

# Introduction

With the explosive growth of the popularity in the unlicensed 2.4 GHz Industrial, Scientific and Medical (ISM) band, the demand for wireless connectivity in electronic devices is ever increasing. High quality multimedia require high data rates in addition to a better Quality of Service (QoS). When the Federal Communications Commission (FCC) created the ISM band they allocated 80 MHz centered at 2.4 GHz allowing for data rates up to 100 Mb/s. The continuous demand for better video and audio quality requires higher data rates than the ISM band can provide. With the advent of digital televisions on the horizon, existing wireless standards become inadequate for the required data rate of 25 to 935 Mb/s [1]. Current wireless standards cannot support the data rates of real-time high-definition videos due to limited bandwidth. Table 1.1 tabulates existing wireless standards and their data rate parameters.

## 1.1 Ultra Wide-Band

The maximum capacity of a channel is defined by the Shannon-Hartley theorem,

| Protocol | Frequency | Data Rate | Throughput | Range |

|----------|-----------|-----------|------------|-------|

|          | (GHz)     | (Mb/s)    | (Mb/s)     | (m)   |

| 802.11a  | 5         | 54        | 23         | 35    |

| 802.11b  | 2.4       | 11        | 4.3        | 38    |

| 802.11g  | 2.4       | 25.8      | 19         | 38    |

| 802.11n  | 2.4/5     | 54        | 74         | 70    |

| 802.11y  | 3.7       | 54        | 23         | 50    |

Table 1.1: Parameters of commercially available wireless networks [2].

$$C = W \log_2(1 + SNR), \tag{1.1}$$

where C is the theoretical channel capacity limit, W is the bandwidth of the channel, and SNR is the signal-to-noise ratio of the channel. To increase the channel capacity two options exist. The first is to increase SNR, but this is limited by the noise of electronic circuits and propagation media. The second option is to increase the channel bandwidth.

In 2002, the FCC approved the operation of certain types of wireless devices utilizing ultra wide-band technologies for commercial use. Ultra wide-band systems differ from traditional narrow-band systems by employing low-power high-bandwidth signals in place of high-power low-bandwidth signals. The reduction in the signal power reduces the SNR, but the channel capacity is increased due to the substantial bandwidth increase.

The first transmission of an ultra wide-band signal was in fact the first wireless transmission and dates back to Marconi in 1890 with a spark gap generator. The spark gap generator produces a very narrow pulse that has a very large bandwidth due to the timefrequency duality (a narrow pulse in the time domain translates to a large bandwidth in the frequency domain). Ultra wide-band systems continued to be developed in radar systems where narrow pulses allow for the accurate distance measurement of aircrafts. Ultra wide-band systems also found use in military communications due to the difficulty in the detection and reception of very narrow pulses. Meanwhile narrow-band systems prospered in the commercial market due to their lower cost and ease of implementation. With the narrow bandwidth used in traditional systems the data rates were severely limited. This gave rise to a renewed interest in ultra wide-band technology for commercial applications. The FCC proposed the largest frequency allocation spanning from 3.1 GHz to 10.6 GHz to be called 802.15.3 UWB. The applications of UWB include [3]:

- Wireless Personal Area Networks (WPANs) Wireless personal area networks allow the high-speed transmission of signals up to a maximum distance of two meters. An example of WPAN is shown in Fig.1.1, consisting of a multi-media system that allows HDTV signals to be shared between cable/sat set top boxes, HD ready televisions, audio systems, Blu-ray DVD players, and personal computers all without wires.

- Sensor Networks The desired characteristics of any UWB device are a low fabrication cost, low complexity and low power consumption. With these three attributes it is advantageous to create an array of transceivers that allow for accurate positioning. A transducer or other sensors can be included in the transceiver to allow for an array of measurements to be taken. An example of an UWB sensor network is the tracking of participants in an endurance race, which allows automatic time tracking and remote heart beat monitoring of participants.

- Imaging Systems Similar to sensor networks the ultra short pulses that define the UWB can be used for imaging due to a large penetration depth at UWB wavelengths.

Figure 1.1: An example of an UWB wireless personal area network.

Imaging systems can allow rescuers at the scene of a natural disaster to locate victims without wasting time to dig or endanger the rescuers themselves.

• Vehicular Radar Systems - A leading cause of death in North America is car collisions. By using UWB devices as an automated radar warning system a warning tone can be emitted whenever a car or an object approaches the vehicle alerting or applying the breaks automatically.

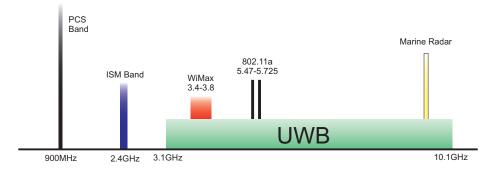

UWB was the first frequency allocation to span over existing wireless standards. The proposed frequency spectrum of UWB and the existing standards are shown in Fig. 1.2. Since the existing standards cannot be changed, the FCC placed stringent restrictions on UWB devices. Any UWB "device may not cause harmful interference, and must accept

Figure 1.2: Spectral allocations showing the proposed UWB and existing narrow-band interferers.

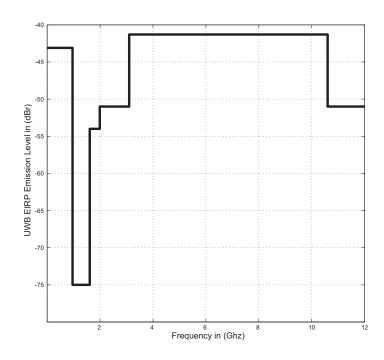

any interference received, including interference that may cause undesired operation."<sup>1</sup> A harmful interference is defined as "interference that ... seriously degrade, obstruct or repeatedly interrupts a radio communication service."<sup>2</sup> To ensure that UWB devices do not interfere with existing networks under any circumstance UWB devices have severely limited power to transmit. The spectral mask defined by the FFC is shown in Fig. 1.3 [4]. Outside of the UWB spectrum the power must not be greater than -75 dBm/MHz. The small signal power of the GPS signal places perhaps the most stringent power restriction on UWB devices in this spectrum. GPS is a network consisting of many satellites used to send time signals to receivers for accurate positioning. The attenuation caused by traveling through the atmosphere results in small signal power that is easily corrupted by other devices.

The UWB spectral mask allows for power transmission of -41.3 dBm/MHz in-band, this low power spectrum ensures that it will not cause interference to existing narrow-band systems sharing part of the same spectrum (In-band interferers). In-band interferers can

<sup>&</sup>lt;sup>1</sup>FCC 47 C.F.R. Sec 15.5(b).

<sup>&</sup>lt;sup>2</sup>FCC 47 C.F.R. 1.907, Sec 2.1.

Figure 1.3: FCC specified spectral mask for indoor UWB commercial devices, severely limiting the output spectrum outside of 3.7-10.3 GHz.

cause interference in UWB devices due to their large signal that may saturate amplifiers and other RF components. As a comparison, cellphones operate at transmission power of +30 dBm/MHz, which is ten million times greater than that of UWB signals. The small signal power of UWB will mean a very low SNR ratio. Recalling from the Shannon-Hartley capacity theorem, a low SNR can be compensated by large bandwidth to maintain the same channel capacity. Out-of-band interference can also cause interference even though they do not share the same spectrum. This is due to the common practice of using non-linear power amplifiers that create harmonic components inside the UWB spectrum [5].

#### 1.2 Objectives

The objective of this thesis is to develop current-mode techniques and circuits for application in ultra wideband. The current-mode techniques will be applied to PLLs and frequency synthesizers to combat the following challanges:

- Integrability: The proposed current-mode techniques should have less reliance on on-chip passive components. On-chip passive components add additional masking layers and expense. Passive components also have high tolerances which require digitally assisted analog blocks.

- Wide frequency Tuning range: VCOs should have a frequency tuning range over 30% without relying on switched bank networks. With a large frequency tuning range the current-mode frequency synthesizer can be applied to new wireless standards that rely on spread spectrum techniques or multi-standard radios.

- Quick Hopping: The MB-OFDM UWB quick channel hopping scheme has a 9.5 ns guard time. This short quard time makes it impractical to use integer frequency synthesizers, because it would require a closed loop bandwidth of several gigahertz. The proposed current-mode frequency synthesizer should be able to lock in under 9.5 ns without resorting to direct frequency synthesis.

### **1.3** Contributions

In this thesis, several current-mode techniques for wideband applications are proposed, and implemented to conform to the objectives stated above. The major contributions of this thesis are:

- Current-mode phase-locked loop The proposed current-mode phase-locked loop decouples control signal dynamic range from the scaling of the supply voltage of CMOS technologies. In voltage-mode PLLs the dynamic range of the control signal is limited to the supply voltage, a reduction in the dynamic range will require a higher VCO gain. The increased VCO gain will result in a higher tolerance and increased noise response.

- Active Inductor and active transformer current-mode filtering The inductance required for current-mode PLLs makes passive on-chip spiral inductors impractical, requiring active circuits to mimic inductance. Active inductors and active transformers previously used for bandwidth enhancement are used for current-mode filters.

- Wideband Oscillators This thesis will propose three wideband oscillators. The three oscillators are capable of frequency tuning ranges of over 30% without using switched bank networks. Without relying on switched bank networks, along with the complexity and problems associated with a discontinuous frequency tuning curve are avoided.

- Quick hopping scheme The 9.5 ns locking time of the MB-OFDM UWB channel hopping scheme makes it impossible to use traditional PLL based frequency synthesizers. This thesis proposes using a deterministic frequency hopping scheme to allow a PLL to lock in the required time. The quick hopping scheme eliminates the frequency acquisition time required by PLL based frequency synthesizers. By only requiring a phase lock the proposed frequency synthesizer is able to lock frequency and phase in the required time.

#### **1.4 Thesis Organization**

- **Chapter 2** (Frequency Synthesizers for Ultra WideBand devices) provides a brief introduction to Multiple-Band OFDM UWB devices. The locking time challenges of MB-OFDM UWB frequency synthesizers are explored. State-of-the-art UWB frequency synthesizers including a DLL based frequency synthesizer, a modified miller frequency divider and direct synthesis are introduced. Performance comparison of published MB-OFDM frequency synthesizers is included at the end of the chapter.

- **Chapter 3** (**Current-Mode Phase Locked Loops**) introduces modern techniques for battling the problem of supply scaling in voltage-mode PLLs. Current-mode filtering will be used to replace voltage-mode filtering. The inductance of the current-mode filter will be implemented using active inductors. A detailed analysis of active inductors will follow. Closed-loop expressions for current-mode PLLs are derived. The phase noise of current-mode PLLs is investigated. The simulation results of an active inductor based current-mode PLL are provided.

- Chapter 4 (Current-Mode Phase Locked Loops with Transformers): introduces the concept of current-mode filtering using transformers. The inductance of the transformer will be implemented using active inductors. A detailed analysis of the winding inductance, mutual inductance, noise, and multiple windings is provided in the chapter. Closed-loop expressions for the active transformer based current-mode PLLs are derived. The phase noise of current-mode PLLs is also investigated. The simulation results of the transformer current-mode are presented.

- **Chapter 5** (**Wide-Band VCOs for Frequency Synthesizers**) starts with a brief introduction to the existing wide band VCOs that utilize switched banks to increase the frequency tuning range. This chapter introduces three new wideband VCOs that do not

use switched networks. An active inductor that provides large frequency tuning range is investigated. A hybrid oscillator that utilizes the superior phase noise performance of a passive transformer and the wide frequency tuning range of an active inductor is developed. A modified hybrid oscillator that uses the impedance scaling property of a passive transformer to increase the frequency tuning range of varactors is created. A comparison of the three presented wide band oscillators and existing wide band oscillators that use switched banks is provided.

- **Chapter 6** (**Current-Mode Frequency Synthesizer UWB**) introduces a current-mode frequency synthesizer for MB-OFDM UWB. A quick hopping scheme that will enable the frequency synthesizer to hop within 9.5 ns is developed. The frequency synthesizer will utilize an ILO as the frequency divider. By forcing the CCO's oscillation frequency to the different regions of the frequency tuning curve the ILO will lock to different UWB channels. Simulation results and a comparison to existing UWB frequency synthesizers are provided.

- **Chapter 7** (**Conclusions**) Summarizes the contributions of this research and suggests the future directions of research on wideband devices.

# Chapter 2

# Frequency Synthesizers for Ultra WideBand devices

This chapter starts with a brief introduction of Multiple-Band OFDM UWB. Section 2 describes the locking time challenges of MB-OFDM UWB frequency synthesizers. Section 3 introduces DLL based frequency synthesizer for UWB devices. Section 4 introduces a modified miller frequency divider used as an UWB frequency synthesizer. Section 5 introduces direct synthesis, including both parallel synthesis and single side-band mixing. Section 6 is a performance comparison of published MB-OFDM frequency synthesizers. The chapter is concluded in Section 7.

Two proposals for the adoption of an UWB standard were presented in [6] [7]. The first is called Direct Sequencing Ultra Wide-band (DS-UWB) and uses classical ultra wideband techniques. DS-UWB is a carrier-less modulation scheme. Unlike traditional narrow-band wireless standards that modulate a base-band signal by a carrier, the base-band is applied to shaped pulses. Time and frequency have an inversely proportional nature, i.e. the narrower a pulse in the time domain the larger the bandwidth it will occupy in the frequency domain. By taking the advantage of UWB's large bandwidth the resulting pulses are ultra narrow in width, allowing for a high data-rate. The pulses can be modulated using traditional modulation techniques such as pulse position modulation or pulse amplitude modulation. DS-UWB devices have the advantage of simple RF front ends due to the absence of a carrier. Synchronization, however, is difficult due to the requirement of near perfect phase alignment with the receiver's correlators.

The second proposal is called Multi-Band Orthogonal Frequency Division Multiplexing Ultra WideBand (MB-OFDM UWB). An ultra wide-band signal is defined as a signal with fractional bandwidth greater than 0.2. Fractional bandwidth is defined as [8]

Fractional Bandwidth =

$$\frac{F_H - F_L}{\frac{F_H + F_L}{2}}$$

, (2.1)

where  $F_H$  and  $F_L$  are the upper and lower boundaries of the frequency range over which 90% of the signal energy is contained, respectively. An UWB fractional bandwidth of 0.2 translates into a bandwidth of 500 MHz. Instead of trying to utilize the entire UWB band for a single device, MB-OFDM UWB divides the UWB band into 14 bands with equal channel width of 528 MHz. MB-OFDM UWB uses more traditional wireless techniques to effectively combat multipathing.

#### 2.1 Multi-Band OFDM UWB

Multi-Band OFDM UWB consists of 14 bands, each has 528 MHz bandwidth. Each band has 128 OFDM subcarriers. The characteristics of 128 subcarriers are shown in Table. 2.1. Only 100 of the 128 carriers are used to carry data. 12 of the subcarriers are called pilots and used for synchronization and channel estimation. An additional 10 subcarriers are used as guard carriers. The guard carriers are used on either sides of the data carrying subcarriers

| Number of data subcarriers       | 100       |

|----------------------------------|-----------|

| Number of defined pilot carriers | 12        |

| Number of guard carriers         | 10        |

| Null subcarriers                 | 6         |

| Number of total subcarriers used | 122       |

| Subcarrier frequency spacing     | 4.125 MHz |

| IFFT/FFT period                  | 242.42 ns |

Table 2.1: Subcarriers of MB-OFDM UWB.

to prevent ICI with other UWB devices. The null carriers are used beside the guard carriers and used to relax the filter requirements. A subcarrier frequency spacing of 4.125 MHz is used. An IFFT/FFT sampling period of 242.42 ns ensures subcarrier orthogonality. Table. 2.2 shows the data rates of MB-OFDM.

Table 2.2: Data-rates of MB-OFDM.

| Data Rate | Modulation | Code  | Conjugate | Time      | Coded Bits |

|-----------|------------|-------|-----------|-----------|------------|

| (Mb/s)    | Scheme     | Rate  |           | Spreading | Per Symbol |

| 53.3      | QPSK       | 1/3   | Yes       | 2         | 100        |

| 80        | QPSK       | 1/2   | Yes       | 2         | 100        |

| 110       | QPSK       | 11/32 | No        | 2         | 200        |

| 160       | QPSK       | 1/2   | No        | 2         | 200        |

| 200       | QPSK       | 5/8   | No        | 2         | 200        |

| 320       | QPSK       | 1/2   | No        | 1         | 200        |

| 400       | QPSK       | 5/8   | No        | 1         | 200        |

| 480       | QPSK       | 3/4   | No        | 1         | 200        |

The code rate is the convolutional encoder rate that introduces memory into the system to allow for error detection and correction. At lower data rates the last 50 subcarriers are the conjugate of the upper 50 subcarriers. The use of conjugate subcarriers introduces redundancy that allows for error correction by sending the same bits sequence twice in every OFDM frame. The use of conjugate rather than a simple duplication of the base-band data results in an output signal having no imaginary component. An output signal without an imaginary component reduces the hardware requirement of the transmitter, as only a Q path is required.

Table 2.3: Time-Frequency Codes for a Group 1 MB-OFDM hopping sequence.

| TFC | Hopping Sequence |

|-----|------------------|

| 1   | 1, 2, 3, 1, 2, 3 |

| 2   | 1, 3, 2, 1, 3, 2 |

| 3   | 1, 1, 2, 2, 3, 3 |

| 4   | 1, 1, 3, 3, 2, 2 |

| 5   | 1, 2, 1, 2, 1, 2 |

| 6   | 1, 1, 1, 2, 2, 2 |

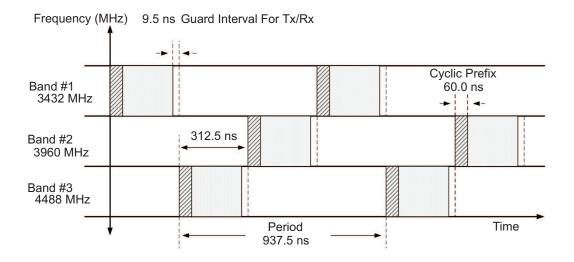

To provide multi-user access and channel diversity an UWB device will hop among multiple channels. Since each mode is composed of 3 channels, a pico-net of UWB devices will hop around using one of the Time Frequency Codes (TFC) shown in Table. 2.3, allowing for three UWB devices to co-exist in the same space. Fig. 2.1 shows an example of an UWB device hopping around using the first TFC code from the Table. 2.3. There is a 9.5 ns interval between hopping from one channel to another during which the transmitter and receiver must be ready to send and receive MB-OFDM signals. After the guard interval there is a 60 ns cycle prefix and finally a 312.5 ns ODFM signal consisting of 128 subcarriers.

Due to the ultra wide-band nature of the signals present in MB-OFDM UWB devices

Figure 2.1: Time-frequency kernel example code used for multiple user access as well as high channel efficiency.

there are unique design challenges that are not encountered in traditional narrow-band wireless systems [9]. Traditionally, phase noise, which is a measure of signal purity is the most important design parameter for frequency synthesizers. With the tight spacing between channels the spectrum of the carrier outside of the channel bandwidth must be sufficiently attenuated. A less important design constraint is the settling time, the time required to hop from one frequency to another.

The design constraints of MB-OFDM UWB frequency synthesizers are different from those of frequency synthesizers for narrow-band RF systems. Due to the wide bandwidth of each channel (subcarrier generation is done in the digital domain), phase noise requirement is greatly relaxed. Phase noise requirement for a MB-OFDM UWB frequency synthesizer is only -105 dBc/Hz (plateau) while typical phase noise of narrow-band synthesizers is below -110 dBc/Hz at 1 MHz offset. Unlike traditional phase noise measurements that

specify the phase noise at some offset from the carrier such as 100 KHz or 1 MHz, UWB phase noise requirement is based on a plateau. This is because phase noise has a flat profile within the loop bandwidth, and MB-OFDM UWB has a large loop bandwidth. The cutoff point of a phase noise plot where the phase noise is no longer corrected by the closed loop is equal to the closed loop bandwidth of the PLL. A wide bandwidth is required for UWB synthesizers in order to have a short lock time

#### 2.2 Lock Time and Bandwidth Requirements of UWB

MB-OFDM UWB uses spread spectrum by means of an ultra-fast frequency hopping scheme [10][11][12]. In MB-OFDM UWB there is only a 9.5 ns guard period in which the transmitter/receiver must quit transmitting in one channel and be ready to begin transmission in another. The 9.5 ns guard period places a strict constraint on the synthesizer. The setting time, which is the time required for the synthesizer to hop to one frequency, is governed by the synthesizer's 2nd order closed loop expression and is given by [13]

$$T_s = -\frac{\ln(\text{tolerance})}{\zeta \omega_n},\tag{2.2}$$

where  $\zeta$  is the damping factor,  $\omega_n$  is the loop bandwidth, and tolerance is the allowed steady-state error. If we assume a 1% tolerance, a damping ratio  $\frac{2}{\sqrt{2}}$ , and a loop bandwidth 50 MHz, the required settling time is at least 100 ns. Eq.(2.2) shows that an increase in the loop bandwidth will decrease the settling time. One may wonder whether it is possible to increase the bandwidth until the synthesizer meets the settling time requirement. Unfortunately there is an upper limit on the bandwidth of the synthesizer that will limit the settling time to well above what is required by MB-OFDM UWB. This limit is due to a 528 MHz channel spacing mandating a maximum loop bandwidth of 52.8 MHz. Frequency synthesizers are almost exclusively composed of charge-pump type-II PLLs that use a frequency/phase detector for a quick phase and frequency acquisition. Due to the sampling nature of the frequency/phase detector the system becomes unstable if the loop bandwidth approaches the reference frequency. Garder defined the upper limit of stability [13]

$$K\tau_2 = \frac{(\omega_c \tau_2)^2}{\pi (1 + \frac{\omega_c \tau_2}{\pi} \frac{1-a}{1+a} \frac{b-1}{b})}$$

(2.3)

where  $a = exp(\frac{-2\pi b}{\omega_c \tau_2})$ ,  $\omega_c$  is the reference frequency of the synthesizer, b is the ratio of the pole frequency to that of the zero frequency, and  $\tau_2$  is the time constant of the stabilizing zero added by the resistor of the loop filter. With  $K = \frac{\omega_c}{10}$  the gain margin is 10 dB, resulting in a minimally stable closed-loop response of the PLL. With the reference frequency of the UWB synthesizer being 528 MHz (a 528 MHz reference frequency was chosen to allow for an integer frequency synthesizer to be used), the upper limit of the loop bandwidth is approximately 50 MHz.

The inability of narrow-band frequency synthesizers to lock in 9.5 ns sparks the search for new techniques, which include:

- A delay-locked loop with an edge combiner [14] Instead of using a high-frequency oscillator to generate the output signal, a low frequency DLL is used and the outputs of the individual delay cells are summed by an edge combiner. By selecting how many delay cells are used in the feedback loop, the desired frequency multiplication factor can be obtained.

- A high frequency PLL with a frequency divider at the output [15] By having a fixed frequency synthesizer with a programmable frequency divider, multiple output frequencies can be generated. The synthesizer only needs to lock to the fixed frequency at power-up, resulting in fast locking.

• Direct synthesis utilizes the frequency translation function of single side band mixing [16] [17] [18] [19] [20] [21] [22] [23] [24]. By multiplying multiple fixed frequency synthesizers the sum or difference of their output frequencies is generated. By having one of the fixed frequency synthesizers set to the middle carrier of mode-1 and the second fixed frequency synthesizer set to 528 MHz, we can generate all 3 of the mode-1 carriers. Because the fixed frequency synthesizers only need to achieve frequency and phase lock at the power-up the channel hopping of a direct synthesis frequency synthesizer has a short lock time.

## 2.3 Delay-Locked Loop Frequency Synthesizer

Figure 2.2: DLL based frequency synthesizer [14].

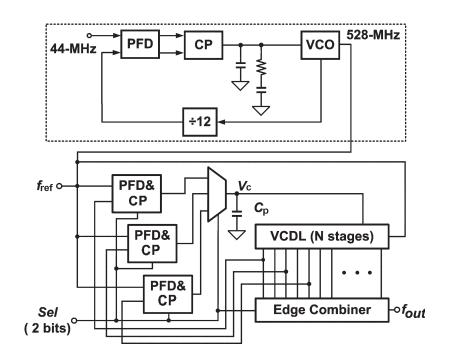

The basic DLL frequency synthesizer is shown in Fig. 2.2. It consists of a phase detector, a charge pump, a loop filter, delay line, and edge combiner. In the place of the voltage controlled oscillator in a PLL, a DLL uses a voltage controlled delay line driven by a reference oscillator. The DLL is a first-order system, yet still capable of fast locking. The short locking time makes DLL-based frequency synthesizers attractive for MB-OFDM UWB.

No frequency multiplication occurs in the loop of a DLL because the frequency of the reference oscillator is fixed and the delay line cannot alter the frequency of the signal. The multiplication of the reference frequency is obtained by using an edge combiner. When the DLL is locked the reference oscillator and the output of the delay line are shifted by 180 degrees. The 180 degree phase shift is equally divided among the delay cells of the delay line. Each delay cell has a phase shift of  $\frac{\pi}{N}$ , where N is the number delay cells in the delay line. When the edges of the delay cell of the DLL are combined the resulting frequency is multiplied by a factor of N. Mismatches in the delay times and layouts of the delay cells and edge combiner will cause spurs in the output spectrum and can cause ISI.

#### 2.4 Miller Divider Based Frequency Synthesizer

The reason classical frequency synthesizers cannot lock in 9.5 ns guard period is due to a finite closed-loop bandwidth. As described previously, the closed-loop bandwidth is limited to a 10<sup>th</sup> of the reference oscillator's frequency. Instead of having frequency hopping occurring inside the closed loop of the PLL, the frequency divider can be placed outside the loop therefore not requiring the PLL to re-acquire phase and frequency lock during channel hopping [25]. A classical PLL locks to a fixed frequency at the start-up. It is followed by a programmable frequency divider [15]. The architecture of the frequency synthesizer is

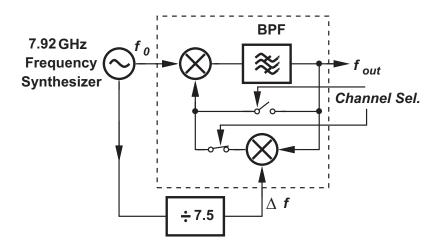

Figure 2.3: Architecture of [15] showing a fixed synthesizer and modified Miller frequency divider.

shown in Fig. 2.3. It consists of a fixed frequency synthesizer producing a 7.92 GHz reference signal, which is used to drive a divided-by-7.5 frequency divider and a programmable Miller frequency divider.

Figure 2.4: Miller frequency divider.

Miller frequency divider shown in Fig. 2.4 consists of a mixer and a bandpass filter. The mixer mixes the output of the reference oscillator with its own output. The output of the mixer is given by

Figure 2.5: Modified Miller divider [15].

$$f_o - f_{out} = f_{out}, \quad f_{out} = \frac{f_o}{2}.$$

(2.4)

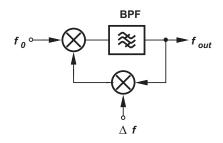

Eq.(2.4) shows that once the Miller divider has reached an equilibrium state, its output will be half the reference frequency. The modified Miller frequency divider presented in [15] is shown in Fig. 2.5. The feedback mixer modifies (2.4) into

$$f_o - (f_{out} \pm \Delta f) = f_{out}, \quad f_{out} = \frac{f_o}{2} \pm \frac{\Delta f}{2}.$$

(2.5)

By using the modified Miller frequency divider in the architecture presented in [15] the first 3 channels of UWB can be synthesized. The modification to the Miller frequency divider that allowed the additional 2 UWB channels also resulted in spurs in the output spectrum.

## 2.5 Direct Synthesis Frequency Synthesizers

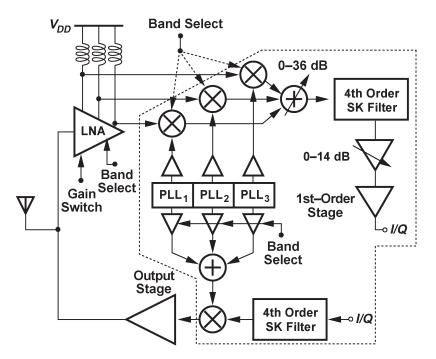

The most common method for generating carrier signals of MB-OFDM is direct synthesis [16] [17] [18] [19] [20] [21] [22] [23] [24]. Direct synthesis modifies the output of a fixed frequency synthesizer but doesn't require a carrier twice that of the desired output

frequency. Direct synthesis falls into two categories: (i) Parallel synthesis shown in Fig. 2.6 [26] [27], and (ii) single side band mixing. For parallel synthesis no locking is required by using a separate RF path for all the required channels. The drawback of this architecture is the high silicon area and power consumption. The need for a synthesizer and a mixer in every channel is difficult for mandatory mode-1 devices and impractical for a UWB with all 14 channels.

Figure 2.6: UWB receiver using multiple RF paths tuned to each of their respective bands [26].

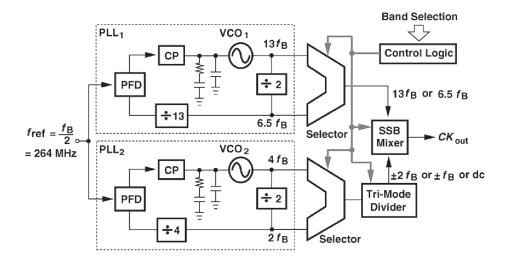

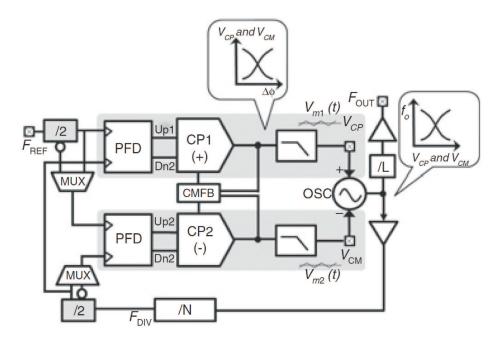

A more common architecture for direct synthesis is by means of single side band (SSB) mixing. By using a SSB mixer a high frequency carrier can be frequency translated by the channel frequency offset of 528 MHz. An example of a SSB mixer-based frequency synthesizer is shown in Fig. 2.7.

Figure 2.7: MB-OFDM frequency synthesizer based on direct synthesis [28].

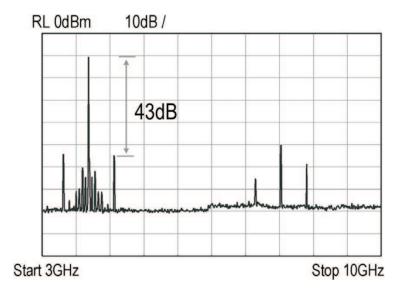

While SSB allows for the creation of all 14 channels of MB-OFDM with settling time well under 1 ns, SSB mixers create sidebands located at the center of the adjacent channels that might cause ISI. These spurs are due to the non-linearities of the SSB mixer, and I/Q mismatch from the oscillators. An example of the generated spurs is shown in Fig. 2.8.

### 2.6 Performance Comparison

Table. 2.4 compares the performance of published MB-OFDM UWB frequency synthesizers. Several trends are observed:

- Most of the frequency synthesizers are fabricated on low cost CMOS processes, with 0.18  $\mu m$  CMOS the most widely used.

- All of the MB-OFDM UWB frequency synthesizers suffer from the generation of spurs, with the largest spurs occurring directly ontop of adjacent channels. These

Figure 2.8: The output spectrum of [22] showing spurs

spurs are due to the open-loop architectures being used to generate the UWB carrier with lock time under 9.5 ns. These spurs will reduce the sensitivity of the receiver.

• MB-OFDM UWB frequency synthesizes have an average power consumption of 11.2 mW per channel. These power consumption figures are a result the necessity of multiple PLLs and SSB mixers, both require large power consumption for proper performance.

## 2.7 Chapter Summary

An overview of UWB for wireless communications has been presented. The two standards for UWB transmission namely DS-UWB and MB-OFDM have been discussed. DS-UWB uses the direct modulation of narrow pulses to represent the base-band data. It is difficult

| Ref. | Technology  | Lock | Spur  | Phase    | Total | Power    |

|------|-------------|------|-------|----------|-------|----------|

|      |             | time | Level | Noise    | Power | per Band |

|      |             | [ns] | [dBc] | [dBc/Hz] | [mW]  | [mW]     |

| [14] | 0.18um CMOS | 8    | -35   | -120     | 54    | 18       |

| [15] | 0.18um CMOS | 4    | -25   | -109     | 47    | 15.6     |

| [25] | 90nm CMOS   | 9    | -32   | -120     | 55    | 3.9      |

| [16] | 0.18um CMOS | 2    | -40   |          | 65    | 16.25    |

| [17] | 0.18um CMOS | 1    | -37   | -103     | 48    | 6.85     |

| [19] | 0.18um CMOS | 2.4  | -20   |          | 34    | 11.3     |

| [21] | 0.18um CMOS | 2    | -26   | -98      | 68    | 22.6     |

| [29] | 0.18um SiGe | 3    | -40   | -130     | 88    | 12.6     |

| [28] | 0.18um CMOS | 1    | -37   | -110     |       |          |

| [22] | 65nm CMOS   | 6    | -43   | -128     | 43    | 4.8      |

| [23] | 0.18um CMOS | 3    | -30   |          | 45    | 3.2      |

| [24] | 0.18um CMOS | 3    | -33   | -98      | 117   | 8.3      |

Table 2.4: Comparison of state-of-the-art UWB frequency synthesizers.

to synchronize the transmitter and receiver. MB-OFDM uses more traditional narrow-band techniques by sub-dividing the ultra wide-band into small bands of bandwidth 528 MHz. MB-OFDM uses orthogonal frequency division multiplexing for high channel efficiency.

A state-of-the-art review of existing MB-OFDM UWB frequency synthesizers has been presented. MB-OFDM places a greater constraint on lock time and less constraint on phase noise. We have shown that the lock time is the greatest challenge for MB-OFDM UWB frequency synthesizers. A guard time of 9.5 ns requires loop bandwidth larger than that set by the stability of PLL based frequency synthesizers. The common approaches to perform frequency synthesis for MB-OFDM UWB have been investigated.

The first approach is DLL based frequency synthesis. A DLL is incapable of frequency multiplication, with the addition of an edge combiner, frequency multiplication can be performed. By controlling the number of the delay cells in the delay line a programmable DLL based frequency synthesizer can be created. Low-frequency DLLs are able to establish a very quick lock because only phase lock is required. DLL frequency synthesizers generate spurs due to mismatching in the delay cells and edge combiner.

The second approach is the fixed frequency synthesizer with a programmable frequency divider. By having the programmable frequency divider at the output of the VCO and not in the VCO feedback loop phase and frequency lock only needs to be established during power-up. The modification of the miller frequency divider also results in spurs at the output of the divider.

The third and also most common frequency synthesis for MB-OFDM UWB is direct synthesis. There are two approaches for direct synthesis, namely parallel synthesis and SSB mixing. Parallel synthesis requires the generation of all UWB channels using multiple frequency synthesizers, resulting in a large silicon area and high power consumption. SSB mixing is the most common approach for MB-OFDM frequency synthesis. It suffers from spur generation due to the use of SSB mixing of multiple fixed frequency synthesizers.

It is evident that existing MB-OFDM UWB frequency synthesizers suffer from the generation of spurs due to the use of open loop architectures. Direct synthesis frequency synthesizers suffer from high power consumption due to the use of multiple frequency synthesizers and single side band mixers.

## Chapter 3

## **Current-Mode Phase Locked Loops**

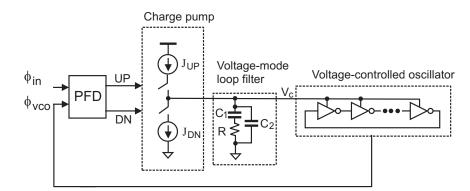

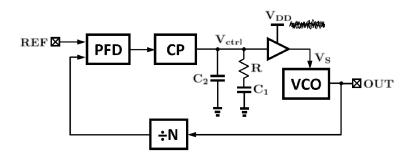

Figure 3.1: Configuration of type II voltage-mode PLLs.

A typical configuration of conventional type II PLLs is shown in Fig. 3.1. We shall term these PLLs voltage-mode PLLs as the oscillation frequency of the oscillator is voltage-controlled. Many new topologies of and design techniques for voltage-mode PLL, such as supply-regulated PLLs [30], PLLs with dual-slope phase-frequency detectors [31], PLLs

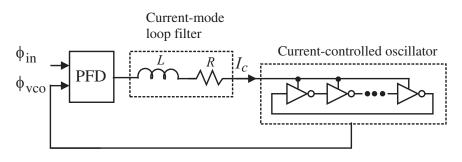

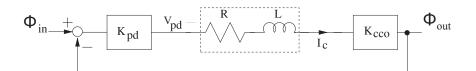

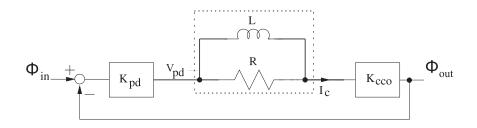

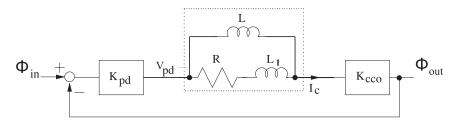

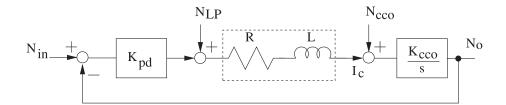

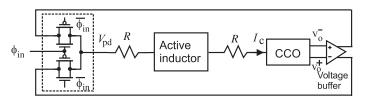

with frequency tracing circuits [32], [33], PLLs with adaptive loop dynamics for fast locking [34], a half-duty sampled feed-forward loop filter for reference spur suppression [35], calibrated phase/frequency detectors [36], and glitch-free charge pumps [37], to name a few, emerged. One of the main drawbacks of voltage-mode PLLs is the limited dynamic range of the control voltage. The current-mode PLLs proposed in this chapter and shown in Fig. 3.2 replaces the conventional voltage-mode RC loop filter with a current-mode RL loop filter. Using current as a control signal the dynamic range of the control signal is no longer limited by the supply voltage. The magnitude of the control signal is not limited by the output of the active inductor gyrators.

Figure 3.2: Configuration of current-mode phase-locked loops.

Section 1 of this chapter introduces modern techniques for battling the problem of supply scaling in voltage-mode PLLs. Section 2 introduces the concept of current-mode filtering that will be used to replace voltage-mode filtering. The inductance of the current-mode filter will be implemented using active inductors. A detailed analysis of active inductors will follow. Current-controlled oscillators are studied in Section 3. Section 4 develops closed-loop expressions for current-mode PLLs. The phase noise of current-mode PLLs is investigated in Section 5. Section 6 provides the simulation results of an active inductor based current-mode PLL. The chapter is summarized in Section 7.

### 3.1 Low-Voltage Voltage-Mode PLLs

The different scaling factors of the supply and threshold voltages reduces the control voltage range. The noise present on the control signal remains unchanged. To compensate for the drop of supply voltage, VCO sensitivity has to increase in order to maintain the same frequency tuning range. The increase in VCO gain makes the VCO more susceptible to noise. Two techniques for combating the reduction of the dynamic range of the control signal are supply regulated PLLs [38, 39, 40, 41, 42, 43] and differentially tuned PLLs [44, 45, 46, 47].

Figure 3.3: Configuration of a supply regulated PLL.

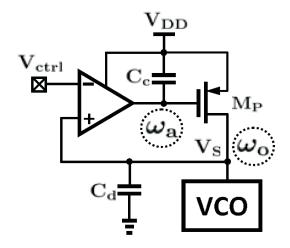

A supply regulated PLL is shown in Fig. 3.3. The VCO's supply voltage is a buffered replica of the control signal. By using the control signal as the VCO's supply voltage the VCO is decoupled from the noisy VDD of the system. Using a regulator to supply the VCO limits the topology of the VCO to ring oscillators. One of the challanges in the design of a supply regulated PLL is highlighted in Fig. 3.4. The regulator consists of an op-amp and a large pMOS  $M_p$ . A large decoupling capacitor  $C_d$  is usually added to filter the VDD of the VCO. The addition of the decoupling capacitor and large pMOS creates two poles  $\omega_a$  and  $\omega_o$ . Both poles  $\omega_a$  and  $\omega_o$  must be an order of magnitude higher than the loop bandwidth of

the PLL. If the bandwidth of the regulator is not sufficiently higher than the loop bandwidth they will degrade the phase margin. To have  $\omega_o$  higher than the loop bandwidth and still effectively filter the VDD of the VCO. an op-amp is required.

Figure 3.4: Configuration of a supply regulated VCO.

A differentially tuned PLL is shown in Fig. 3.5. The differentially tuned PLL uses a differential control signal. By having a differential control signal the dynamic range is effectively doubled. To generate the differential control signal the PLL must have two PFDs and two charge pumps, and a differential loop filter, doubling power and silicon consumption. Having two charge pumps also creates a problem of matching, a mismatch between the two charge pumps generates considerable spurs in differentially tuned PLLs. Another challenge with a differentially tuned PLL is that the VCO must be differentially tuned, requiring a unique VCO topology.

Supply regulated PLLs are not suitable for UWB frequency synthesizers due to power consumption. The large loop bandwidth of a UWB frequency synthesizer will require a high powered op-amp with an output pole of tens of gigahertz. Differentially tuned PLLs

Figure 3.5: Configuration of a differentially tuned PLL.

are also not suitable for UWB frequency synthesizers. This chapter explores current-mode techniques for frequency synthesizers.

## 3.2 Current-Mode Filtering

#### 3.2.1 Current-Mode Loop Filter

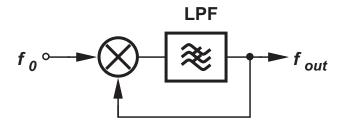

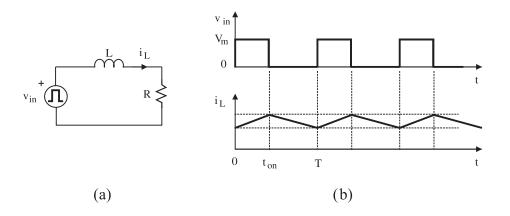

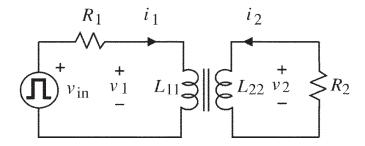

Current-mode filtering is widely used in power electronics for dc-dc conversion where a constant output current is required. Current-mode filtering differs fundamentally from voltage-mode filtering where sustaining a constant output voltage is the objective. A typical current-mode low-pass filter consists of an inductor and a resistor in series, as shown in Fig. 3.6. Let the input voltage source  $v_{in}(t)$  be a square-wave generator with amplitude  $V_m$  and duty cycle  $t_{on}/T$ , where T is the period and  $t_{on}$  is the ON time. The inductor current is given by

$$i_{L}(t) = \begin{cases} \frac{V_{m}}{R}(1 - e^{-t/\tau}) + i_{L}(0^{-})e^{-t/\tau}, & 0 \le t \le t_{on}, \\ i_{L}(t_{on}^{-})e^{-(t-t_{on})/\tau}, & t_{on} \le t \le T, \end{cases}$$

(3.1)

where  $\tau = \frac{L}{R}$  is the time constant,  $i_L(0^-)$  and  $i_L(t_{on}^-)$  are the initial current of the inductor at t = 0 and  $t = t_{on}$ , respectively. If  $\tau$  is sufficiently large, we have  $e^{-\frac{t}{\tau}} \approx 1 - \frac{t}{\tau}$  and (3.1) is simplified to

$$i_{L}(t) \approx \begin{cases} \frac{V_{m}}{R} \frac{t}{\tau} + i_{L}(0^{-})(1 - \frac{t}{\tau}), & 0 \le t \le t_{on}, \\ i_{L}(t_{on}^{-})(1 - \frac{t - t_{on}}{\tau}), & t_{on} \le t \le T. \end{cases}$$

(3.2)

Figure 3.6: Characteristics of current-mode loop filter.

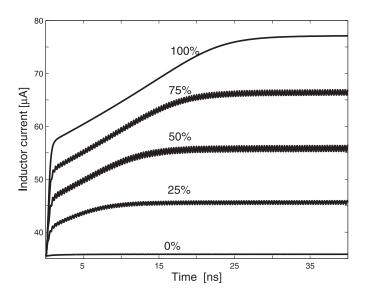

For fixed  $V_m$ , the dc component of the inductor current is a function of the duty cycle.