# OPTIMIZED SWITCH-LEVEL SOFT ERROR DETECTION BASED ON ADVANCED SWITCH-LEVEL MODELS

by

#### Jalal Mohammad Chikhe

Maîtrise de science de la modélisation, de l'information et des systèmes Mention Électronique, électrotechnique, automatique et systèmes University of Paul Sabatier, Toulouse, France, 2007

A project report

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Engineering

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2010

©Jalal Mohammad Chikhe 2010

PROPERTY OF RYERSON UNIVERSITY LIBRARY

#### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this project or dissertation. I authorize Ryerson University to lend this project or dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this project or dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

#### **ABSTRACT**

#### Project Title:

Optimized switch-level soft error detection based on advanced switch-level models

Project submitted by:

#### Jalal Mohammad Chikhe

Optimization Problems Research and Applications Laboratory (OPR-AL)

Master of Engineering, Ryerson University, 2010

Project Directed by:

Dr. Reza Sedaghat

Due to the reduction of transistor size, modern circuits are becoming more sensitive to soft errors. The development of new techniques and algorithms targeting soft error detection are important as they allow designers to evaluate the weakness of the circuits at an early stage of the design. This project presents an optimized implementation of soft error detection simulator targeting combinational circuits. The developed simulator uses advanced switch level models allowing the injection of soft errors caused by single event-transient pulses with magnitudes lesser than the logic threshold. The ISCAS'85 benchmark circuits are used for the simulations. The transients can be injected at drain, gate, or inputs of a logic gate. This gives clear indication of the importance of transient injection location on the fault coverage. Furthermore, an algorithm is designed and implemented in this work to increase the performance of the simulator. This optimized version of the simulator achieved an average speed-up of 310 compared to the non-algorithm based version of the simulator.

#### **ACKNOWLEDGEMENT**

At first I would like express my gratitude to Dr Sedaghat for his advice, guidance and patience. I am grateful to have him as a mentor because his support helped me progress in my research. Being part of Optimization Problems Research and Applications Laboratory (OPR-AL) was one a most creative and energetic experience. I would like to thank the members of the (OP-RAL) for making me very comfortable when joining the team and for offering their help and support.

I dedicate this project to my parents. Their love and encouragement helped me through this journey.

# TABLE OF CONTENTS

| Abstract      |                                                                | iV         |

|---------------|----------------------------------------------------------------|------------|

| Acknowledg    | ement                                                          | V          |

| Table of Co   | tents                                                          | / <b>i</b> |

| List of Table | si                                                             | X          |

| List of Figur | esxi                                                           | i          |

| Nomenclatu    | exi                                                            | V          |

| Chapter 1     | Introduction                                                   | 1          |

| 1.1.          | Background1                                                    |            |

| 1.2.          | Motivation 3                                                   |            |

| 1.3.          | Summary of Contribution                                        |            |

| 1.4.          | Project Organization 4                                         |            |

|               |                                                                |            |

| Chapter 2     | Main Functions of the Simulator                                | 5          |

| 2.1           | Verilog Strength and Logic Levels                              |            |

| 2.2           | Switch-Level Functions                                         |            |

|               | <b>2.2.1.</b> funC Function                                    |            |

|               | <b>2.2.2.</b> funN Function                                    |            |

|               | <b>2.2.3.</b> funP Function                                    |            |

|               | 2.2.4. Capacitance Functionality                               |            |

|               | 2.2.5. Example of Transient Injection at Drain of a Switch     |            |

|               | Applied to NAND2 Gate                                          |            |

| Chapter 3     | Fundamental Architecture and Data Structure of the Simulator 1 | 5          |

| 3.1           | Programming Language                                           |            |

| 3.2           | Simulation Environment                                         |            |

|               | 3.2.1. Data Input                                              |            |

|               | 3.2.2. Simulator Flow Diagram                                  |            |

|               | 3.2.3. Data Output                                             |            |

|         |      | 3.2.4.     | Processing              | Module         | * * * * * * * * * * * * * * * * * * * * |                                         | 23 |

|---------|------|------------|-------------------------|----------------|-----------------------------------------|-----------------------------------------|----|

|         | 3.3. | Data Struc | cture of Net            | list Gate-Lo   | evel (netlist_g                         | )                                       | 24 |

|         | 3.4. | Processing | g and Storin            | g Arrays of    | Gate-Level                              |                                         | 26 |

|         | 3.5. | Data Struc | cture of Net            | list Switch-   | Level (netlist                          | _s)                                     | 28 |

|         |      | 3.5.1.     | Coding Ar               | chitecture o   | f netlist_s                             |                                         | 28 |

|         |      | 3.5.2.     | NOT Gate                |                |                                         |                                         | 29 |

|         |      | 3.5.3.     | BUFFER                  | Gate           | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | 32 |

|         |      | 3.5.4.     | NAND2 –                 | AND2 Gate      | s                                       | ***************                         | 33 |

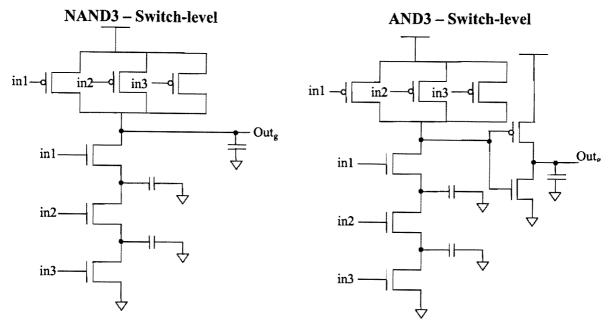

|         |      | 3.5.5.     | NAND3 –                 | AND3 Gate      | s                                       |                                         | 36 |

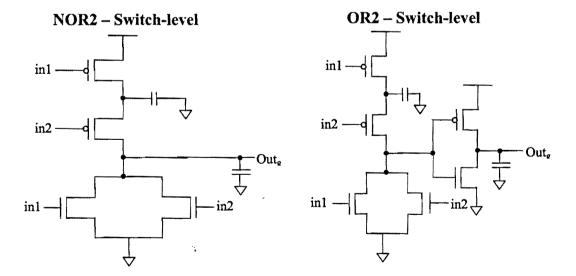

|         |      | 3.4.6.     | NOR2 – O                | R2 Gates       | ***********                             |                                         | 38 |

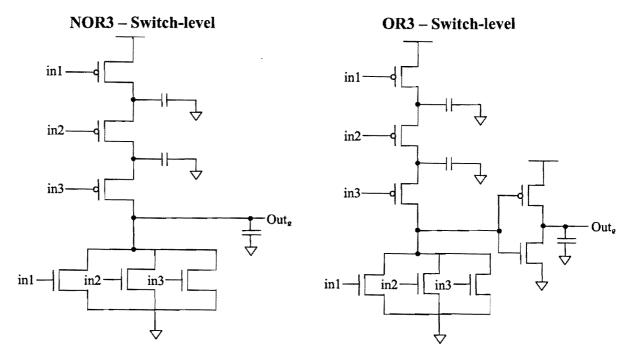

|         |      | 3.4.7.     | NOR3 – O                | R3 Gates       | ******************                      | ********                                | 40 |

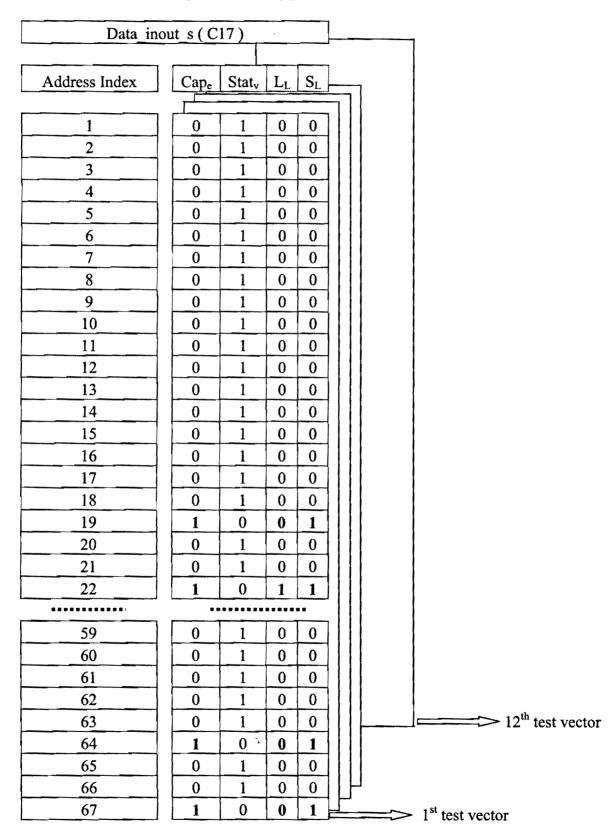

|         |      | 3.5.8.     | Data Struc              | ture Switch    | -Level of C17                           | Circuit                                 | 43 |

|         | 3.6. | Processing | g and Storin            | ig Arrays of   | Switch-Leve                             | 1                                       | 46 |

|         |      |            |                         |                |                                         |                                         |    |

| Chapter | 4    | Detail     | ed Represe              | ntation of Si  | mV <sub>1</sub> Simulat                 | or                                      | 48 |

|         | 4.1. | Flow Diag  | ram of Sim              | V <sub>1</sub> | ******                                  | • • • • • • • • • • • • • • • •         | 48 |

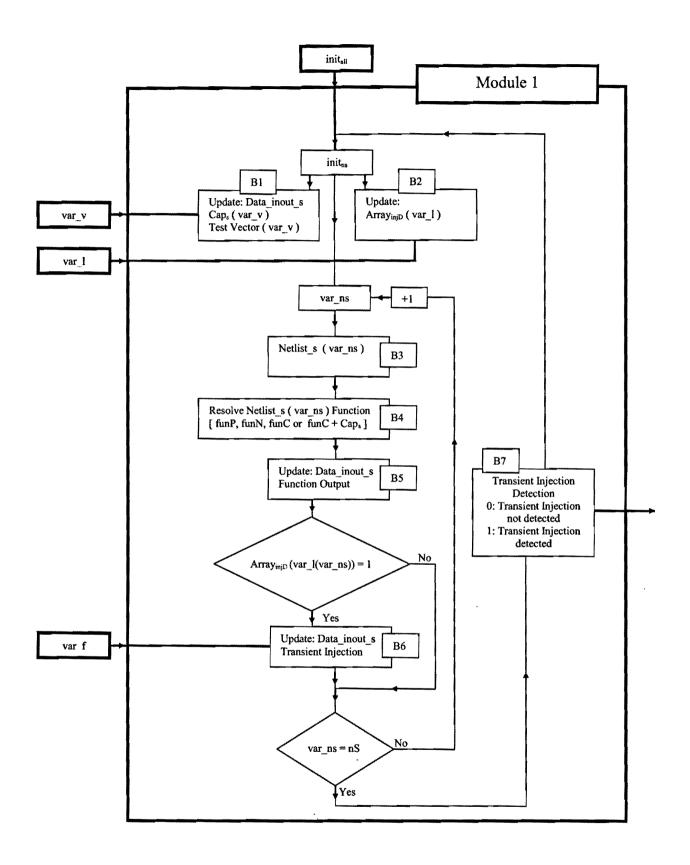

|         | 4.2. | Flow Diag  | ram of Moo              | dule 1         | ••••                                    | • • • • • • • • • • • • • • • • • • • • | 52 |

|         |      |            |                         |                |                                         |                                         |    |

| Chapter | 5    | Detail     | ed Represe              | ntation of Si  | imV2 Simulat                            | or                                      | 57 |

|         | 5.1. | Gate-Leve  | l Resolution            | n Function.    |                                         |                                         | 57 |

|         | 5.3. | Switch-Le  | vel Data In             | put Organiz    | ation                                   |                                         | 63 |

|         | 5.3. | Concept o  | f the Algori            | thm Used in    | ı SimV <sub>1</sub> Simu                | lator                                   | 63 |

|         |      | 5.3.1.     | 1st Solution            | n Based on     | C17 Circuit E                           | Example                                 | 67 |

|         |      | 5.3.2.     | 2 <sup>nd</sup> Solutio | n Based on     | C17 Circuit l                           | Example                                 | 69 |

|         |      | 5.3.3.     | 3 <sup>rd</sup> Solutio | n Based on     | C17 Circuit I                           | Example                                 | 70 |

|         |      | 5.3.4.     | 4 <sup>th</sup> Solutio | n Based on     | C17 Circuit I                           | Example                                 | 71 |

| Chapter | 6    | Exper      | imental Re              | sults          | ••••••                                  |                                         | 75 |

|         | 6.1. | Overview   | of the Simu             | lation Appl    | ied Data                                |                                         | 75 |

|         |      | 6.1.1.     | Benchmarl               | ks             |                                         | • • • • • • • • • • • • • • • • • • • • | 75 |

|         |      | 6.1.2.     | Informatio              | n on the Ap    | plied Data                              | •••••                                   | 77 |

| 6.2.         | Fault Coverage Due to Transient Injection at Different                      |      |

|--------------|-----------------------------------------------------------------------------|------|

| •            | Location types                                                              |      |

|              | 6.2.1. Injection at Gate of a Switch                                        |      |

|              | 6.2.2. Injection at Drain of a Switch                                       |      |

|              | 6.6.3. Injection at Inputs of a Logic Gate                                  |      |

| 6.3.         | Fault Coverage Versus Applied Test Vectors                                  |      |

| 6.4.         | Timing Results                                                              |      |

|              | 6.6.1. Matlab Profile of SimV <sub>1</sub> and SimV <sub>2</sub> Simulators |      |

|              | 6.6.2. Timing Results of SimV <sub>1</sub> Simulator                        |      |

|              | 6.6.3. Timing Results of SimV <sub>2</sub> Simulator                        |      |

|              | 6.6.4. Performance Study of the Developed the Simulators 93                 |      |

| Chapter 7    | Conclusion                                                                  | . 96 |

| Publications | 3                                                                           | . 98 |

| Ribliograph  | V                                                                           | . 90 |

# LIST OF TABLES

| Table 1: Verilog coding representation of logic and strength levels and their decimal         |       |

|-----------------------------------------------------------------------------------------------|-------|

| Representation                                                                                | 7     |

| Table 2: map_det of C17 circuit                                                               | 2     |

| Table 3: map_detATV of C17 circuit                                                            | 2:    |

| Table 4: Coding of the gate types                                                             | 2:    |

| Table 5: Data structure of C17 netlist gate-level (netlist_g) before and after net reorganisa | ation |

|                                                                                               | 2     |

| Table 5(a): Data structure of C17 netlis gate-level before net reorganisation                 | 2     |

| Table 5(b): Data structure of C17 netlist gate-level after net reorganisation                 | 20    |

| Table 6: The main storing and indexing arrays needed to process C17 circuit gate-level        | 2′    |

| Table 7: Coding of the switch-level functions                                                 | 2     |

| Table 8: Coding and data structure of switch-level NOT gate                                   | 32    |

| Table 9: Coding and data structure of switch-level BUFFER gate                                | 33    |

| Table 10: Data structure of switch-level NAND2 and AND2 gates                                 | 3     |

| Table 11: Coded data of switch-level NAND2 and AND2 gates                                     | 3     |

| Table 12: Data structure of switch-level NAND3 and AND3 gates                                 | 3     |

| Table 13: Coded data of switch-level NAND3 and AND3 gates                                     | 3′    |

| Table 14: Data structure of switch-level NOR2 and OR2 gates                                   | 3     |

| Table 15: Coded data of switch-level NOR2 and OR2 gates                                       | 40    |

| Table 16: Data structure of switch-level NOR3 and OR3 gates                                   | 4     |

| Table 17: Coded data of switch-level NOR3 and OR3 gates                                       | 4     |

| Table 18. Data structure of netlist switch level of C17 circuit                               | 1     |

| Table 19: Array of the storing processed data of C17 circuit switch-level                                       |

|-----------------------------------------------------------------------------------------------------------------|

| Table 20: Architecture of Array <sub>injD</sub> drain location array applied to NAND3                           |

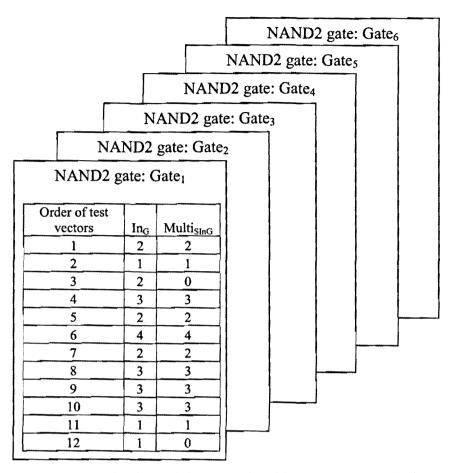

| Table 21: Example of gate-level resolution function applied to NAND2 gate: Gate <sub>1</sub> of C17             |

| circuit covering the effect of the flipping bit of the output of the logic gate on the                          |

| circuit for a set of 12 test vectors                                                                            |

| Table 22: Data structure of collected data gate-level based on the resolution function applied to               |

| C17 circuit                                                                                                     |

| Table 23: Structure of the collected data of NOT gate applied to SimV <sub>1</sub> * simulator 65               |

| Table 24: Example of how the algorithm applied to SimV <sub>2</sub> simulator builds the solution maps          |

| map_det and map_detATV for C17 circuit                                                                          |

| Table 25: map_det and map_detATV maps for C17 circuit74                                                         |

| Table 26: Detailed logic gate information of ISCAS'85 benchmark circuits                                        |

| Table 27: Information on ISCAS'85 benchmark circuits                                                            |

| Table 28: Simulation results for injection at gate of a switch for C5315 circuit                                |

| Table 29: Simulation results of F <sub>cov</sub> for transient injection at gate of a switch for ISCAS'85       |

| benchmark circuits                                                                                              |

| Table 30: Simulation results for transient injection at drain of a switch for C5315 circuit 82                  |

| Table 31: Simulation results of F <sub>cov</sub> for transient injection at drain of a switch for ISCAS'85      |

| benchmark circuits                                                                                              |

| Table 32: Simulation results for transient injection at inputs of a logic for C5315 circuit 84                  |

| Table 33: Simulation results of F <sub>cov</sub> for transient injection at inputs of a logic gate for ISCAS'85 |

| benchmark circuits                                                                                              |

| Table 34: Timing results extracted from SimV <sub>1</sub> simulator based on transient injection at           | drain     |

|---------------------------------------------------------------------------------------------------------------|-----------|

| of a switch                                                                                                   | 89        |

| Table 35: Timing results extracted from SimV <sub>2</sub> simulator                                           | 91        |

| Table 36: Performance and speedup of SimV <sub>2</sub> versus SimV <sub>1</sub> based on all applied test vec | ctors and |

| based on transient injection at drain of a switch                                                             | 94        |

| Table 37: Performance and speedup of SimV <sub>2</sub> versus SimV <sub>1</sub> based on one test vector and  | d based   |

| on transient injection at drain of a switch                                                                   | 95        |

## LIST OF FIGURES

| Figure 1: Strength levels versus Voltage levels adapted from [16]                       | 8      |

|-----------------------------------------------------------------------------------------|--------|

| Figure 2: Flow Diagram of funC Function                                                 | 10     |

| Figure 3: Flow Diagram of funN Function                                                 | 11     |

| Figure 4: Flow Diagram of funP Function                                                 | 12     |

| Figure 5: Example of NAND2 gate in switch-level                                         | 13     |

| Figure 6: Example of NAND2 gate in switch-level where the transient "11111" is injected | at the |

| drain of P1: PMOS                                                                       | 14     |

| Figure 7: Flow diagram of the simulation environment                                    | 17     |

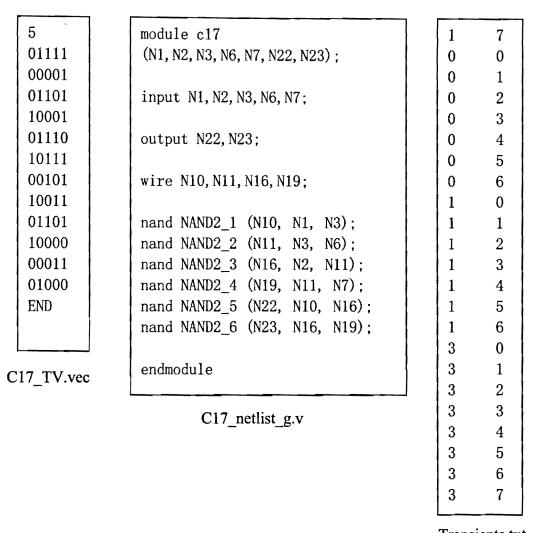

| Figure 8: The simulator data input for C17 Circuit                                      | 18     |

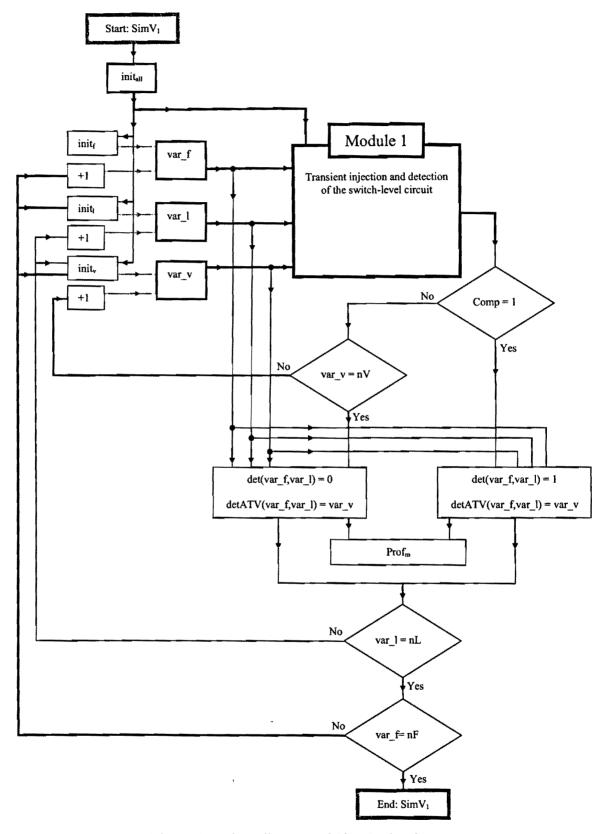

| Figure 9: Flow diagram of the Simulator                                                 | 20     |

| Figure 10: C17 Circuit before and after net reorganisation                              | 24     |

| Figure 10(a): C17 Circuit - Before net reorganisation                                   | 24     |

| Figure 10(b): C17 Circuit - After net reorganisation                                    | 24     |

| Figure 11: How the function code "4" processes the data                                 | 29     |

| Figure 12: Switch-Level of BUFFER and NOT                                               | 31     |

| Figure 13: Switch-Level of NAND2 and AND2                                               | 35     |

| Figure 14: Switch-Level of NAND3 and AND3                                               | 38     |

| Figure 15: Switch-Level of NOR2 and OR2                                                 | 39     |

| Figure 16: Switch-Level of NOR3 and OR3                                                 | 43     |

| Figure 17: Flow diagram of SimV <sub>1</sub> simulator                                  | 51     |

| Figure 18: Flow diagram of the transient injection and detection Module 1               | 55     |

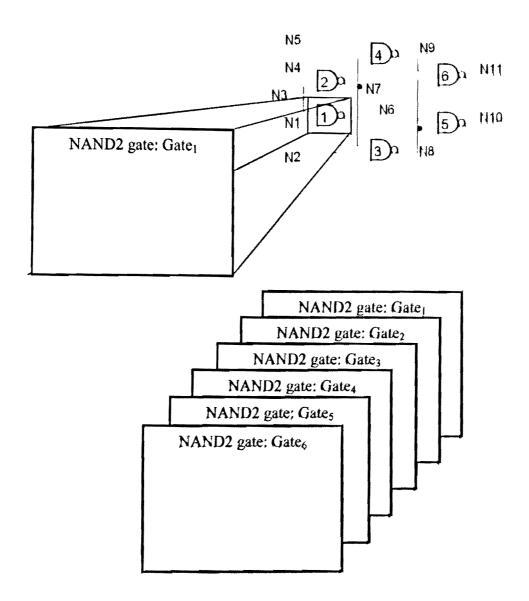

| Figure 19: Structure of the 3D array of gate-level resolution function applied to C17 circuit 62           |

|------------------------------------------------------------------------------------------------------------|

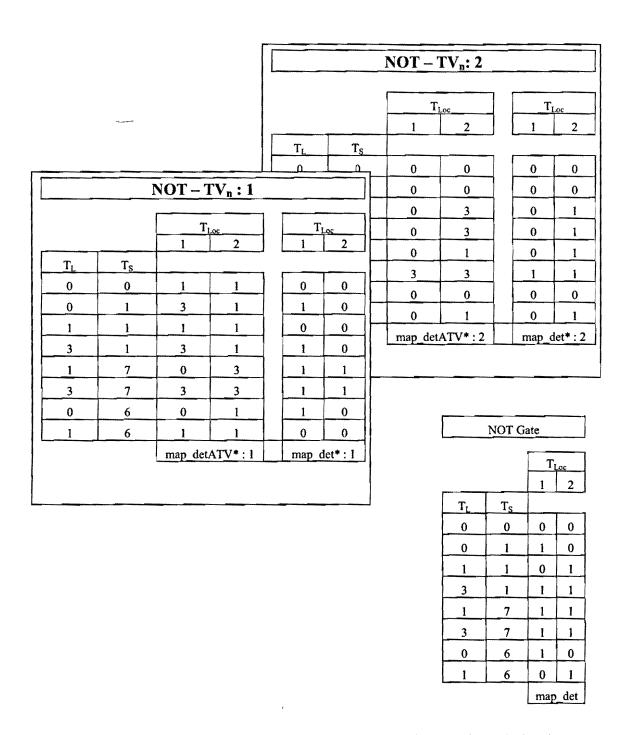

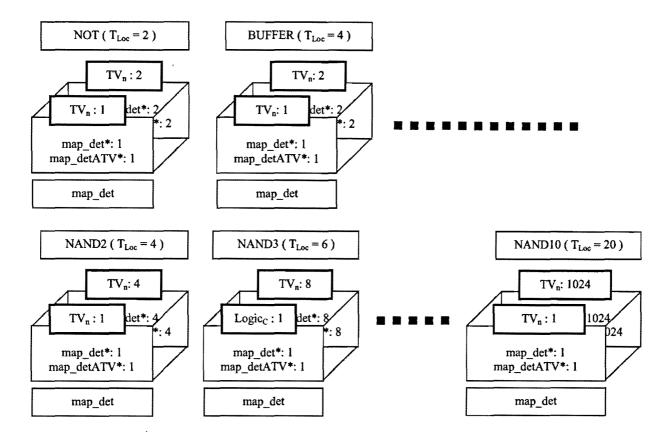

| Figure 20: Data structure of some logic gates extracted from SimV <sub>1</sub> * simulator                 |

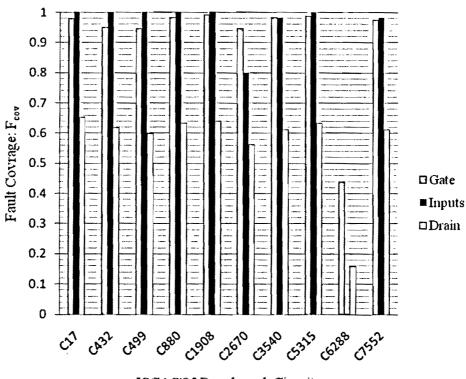

| Figure 21: F <sub>cov</sub> for gate, drain of a switch and inputs of a logic gate for ISCAS'85 benchmarks |

| circuits85                                                                                                 |

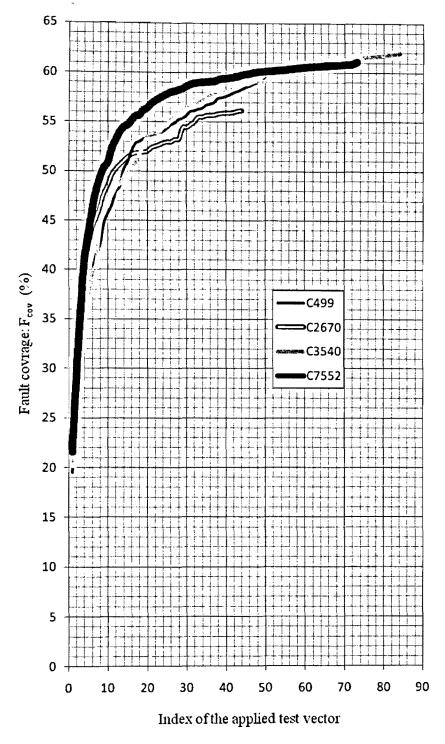

| Figure 22: Plot of $F_{cov}$ based on transient injection at drain of a switch versus applied test vectors |

| for C499, C2670, C3515 and C7552 benchmarks circuits                                                       |

| Figure 23: Matlab Profile Display showing the execution time of SimV <sub>1</sub> functions                |

| Figure 24: Matlab Profile Display showing the execution time of SimV <sub>2</sub> functions                |

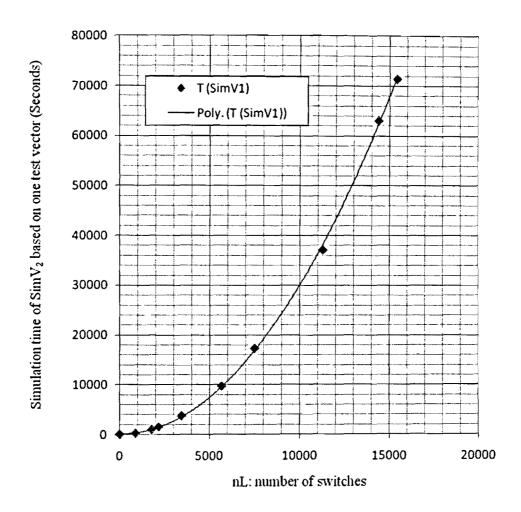

| Figure 25: SimV <sub>1</sub> Simulation time for ISCAS'85 benchmark circuits based on transient injection  |

| at drain of a switch90                                                                                     |

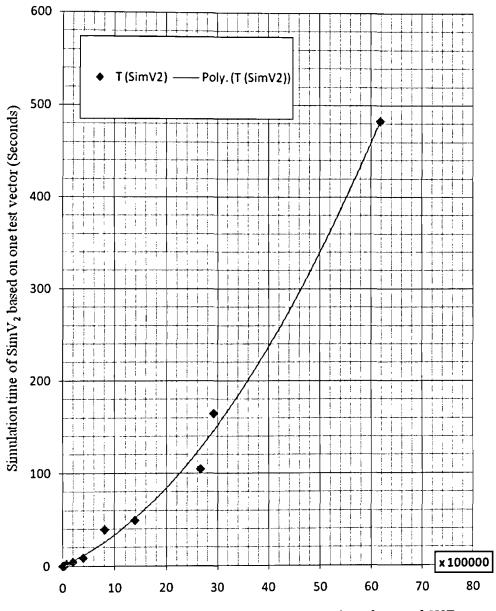

| Figure 26: SimV <sub>2</sub> Simulation execution time for ISCAS'85 benchmark circuits                     |

## **NOMENCLATURE**

| SET                       | Single-Event Transient                                          |

|---------------------------|-----------------------------------------------------------------|

| SEE                       | Single-Event Effects                                            |

| CUT                       | Circuit Under Test                                              |

| SimV <sub>1</sub>         | Non-algorithm based soft error detection simulator              |

| SimV <sub>2</sub>         | Algorithm based soft error detection simulator (Optimized       |

|                           | Simulator)                                                      |

| funC                      | The function resolving the connection node                      |

| funN                      | The function representing the NMOS switch                       |

| funP                      | The function representing the PMOS switch                       |

| Signal1 <sub>L</sub>      | Logic code of incident signal 1 (Same topology for Signal 2)    |

| Signal1 <sub>S</sub>      | Strength code of incident signal 1 (Same topology for Signal 2) |

| OutC                      | State code of output of funC                                    |

| OutCs                     | Strength code of funC output                                    |

| OutC <sub>L</sub>         | Logic code of funC output                                       |

| Drain <sub>L</sub>        | Logic code of the signal at drain                               |

| <b>Drain</b> <sub>S</sub> | Strength code of the signal at drain                            |

| Gate <sub>L</sub>         | Logic code of the signal at gate                                |

| Gates                     | Strength code of the signal at gate of a switch                 |

| SourceL                   | Logic code of the signal at source of a switch                  |

| Sources                   | Strength code of the signal at source of a switch               |

| Org <sub>m</sub>    | Reorganizing, coding and parsing program of data inputs                       |

|---------------------|-------------------------------------------------------------------------------|

| SimV <sub>1</sub> * | SimV <sub>1</sub> simulator applied to all the logic gate types independently |

| Prof <sub>m</sub>   | Profiling maps generated by SimV <sub>1</sub> or SimV <sub>2</sub>            |

| Prof <sub>m</sub> * | The 3D profiling maps generated by SimV <sub>1</sub> *                        |

| map_det             | The 2D Profiling map of fault detection                                       |

| map_detATV          | The 2D Profiling map of the record of test vectors achieving                  |

|                     | transient detection                                                           |

| T <sub>Loc</sub>    | Transient location                                                            |

| T <sub>L</sub>      | Transient logic code                                                          |

| $T_{S}$             | Transient strength code                                                       |

| netlist_g           | Array based netlist gate-level                                                |

| Data_in_g           | Array of the addresses of the primary inputs                                  |

| Data_out_g          | Array of the addresses of the primary outputs                                 |

| Data_inout_g        | Storage array of the values of the connection links of CUT                    |

| Stat <sub>v</sub>   | Status of the content of the corresponding address (i.e. 0 or 1)              |

| netlist_s           | Array based netlist switch-level                                              |

| Cap <sub>v</sub>    | Capacitance value at the node                                                 |

| Cap <sub>s</sub>    | Updated capacitance value at the node                                         |

| Add <sub>inc1</sub> | Incrementation start address of a logic gate of CUT (i.e. used to             |

|                     | determine the address of VDD and GND).                                        |

| Add <sub>inc2</sub> | The remainder address incrementation of a logic gate of CUT                   |

|                     | without VDD and GND address                                                   |

| Outg                | Output of a gate .                                                            |

| Inca                | The first incrementation address of the links of the switch-level      |

|---------------------|------------------------------------------------------------------------|

|                     | data structure                                                         |

| Addeg               | The last address of the last link corresponding to the previous logic  |

|                     | gate                                                                   |

| Data_inout_s        | Storage array of the values of the connection links of CUT switch-     |

|                     | level                                                                  |

| Cape                | The capacitance value exists for 1 and does not exist for 0 value      |

| Ls                  | Strength code of a link                                                |

| $L_L$               | Logic code of a link                                                   |

| var_f               | Variable of injected transient types                                   |

| nF                  | The maximum number of injected transient types                         |

| var_l               | Variable of locations of transient injection                           |

| nL                  | The maximum number locations of transient injection                    |

| var_v               | Variable of index of the used test vector                              |

| nV                  | The maximum number of applied test vectors                             |

| Init <sub>f</sub>   | Initializes var_f to 1.                                                |

| Init <sub>l</sub>   | Initializes var_1 to 1.                                                |

| Init <sub>v</sub>   | Initializes var_v to 1.                                                |

| init <sub>all</sub> | Initialzes init <sub>f</sub> , init <sub>l</sub> and init <sub>v</sub> |

| det(var_f,var_l)    | Coefficients of map_det                                                |

| detATV(var_f,var_l) | Coefficients of map_detATV                                             |

| Comp                | The results of comparing faulty and non-faulty CUT                     |

| init <sub>ns</sub>  | Initializes var_ns, block B1 and B2 of Module 1 of SimV <sub>1</sub>   |

| Array <sub>injD</sub> | The 2D array of transient injection locations of drain location array |

|-----------------------|-----------------------------------------------------------------------|

| var_ns                | Variable representing the row indexes of netlist_s                    |

| nS                    | The maximum number of rows in netlist_s                               |

| Logice                | Array of gate-level resolution function used in SimV <sub>2</sub>     |

| $In_G$                | Decimal representation of logic combination + 1                       |

| Out <sub>G</sub>      | Logic value at the output of the logic gate                           |

| Out <sub>GF</sub>     | Flipped bit of logic value at the output of the logic gate            |

| Stat <sub>po</sub>    | Status of the primary output due to Out <sub>GF</sub>                 |

| Multi <sub>SInG</sub> | Multiplication of In <sub>G</sub> by Stat <sub>po</sub>               |

| ng                    | Number of logic gates in CUT                                          |

| $ m N_{pg}$           | Number of progressive logic gates in CUT                              |

| TV <sub>n</sub>       | The index of applied test vector similar to var_v                     |

| map_det*              | The 3D Profiling map of fault detection for a switch-level logic      |

|                       | gates                                                                 |

| map_detATV*           | The 3D Profiling map of the record of the output of a switch-level    |

|                       | logic gate                                                            |

| n <sub>T.d</sub>      | Total number of injected transients based on test vectors             |

|                       | elimination                                                           |

| n <sub>T.all</sub>    | Total number of injected transients without test vectors elimination  |

| F <sub>cov</sub>      | The fault coverage or soft error coverage                             |

| nL <sub>d</sub>       | The number of transient injection locations corresponding to          |

|                       | detection                                                             |

| T(Parameter)          | Execution time of the parameter number                                |

| T <sub>cycle</sub>           | Execution time to run the simulator for one transient injection and             |  |  |

|------------------------------|---------------------------------------------------------------------------------|--|--|

|                              | at one transient injection location and for one test vector                     |  |  |

| T(RF <sub>Gate-level</sub> ) | The simulation execution time of the resolution function gate-level             |  |  |

| T(P <sub>Algorithm</sub> )   | T(P <sub>Algorithm</sub> ) The simulation execution time to apply the algorithm |  |  |

#### Chapter 1

#### Introduction

## 1.1. Background

As the dimension of transistors are reduced to nanometre scale, modern integrated circuits have the advantage of operating at low power and can achieve high speed characteristics, thus they are becoming more sensitive to external radiation [1]. This work focuses on soft errors in combinational circuits caused by single-event transients (SETs) which belong to Single-Event Effects (SEEs) category. When a vulnerable node within a combinational logic is hit by a cosmic particle, the produced disturbance might propagate to the primary output of the circuit [2]. This can create a soft error if the faulty output data are latched. The developed simulator in this work assumes that the faulty output data are always latched. Furthermore, this work does not apply to sequential circuits; it is mainly developed for combinational circuits. Moreover, due to the reduction of technology scaling, the internal electrical masking and latching-window masking are diminishing as modern digital circuits operate at a higher clock frequency compared to their predecessor. Due to the susceptibility of modern digital circuits to SETs, the research trend has shifted toward SETs in combinational logic.

The developed simulator for soft error detection in this work, operates by injecting a fault at certain location of the circuit under test (CUT), applies a set of test vector at the primary inputs of CUT and by comparing the faulty and non-faulty primary outputs of CUT, the simulator can determine whether there is a fault detection or not. There are different levels of abstraction that can be used for soft error detection including gate-level, electrical-level and switch-level. Gatelevel soft error detection models are bit-flip based [3] [4] and the inputs of a logic gate are used as transient injection location [4] [5]. These models can't mimic the complex analog behavior of the transient propagation as the internal nodes of CUT can't be accessed [6]. As a result the simulators based on these models can be very fast and less reliable in terms of accuracy. The simulators for soft error detection based on electrical-level are reliable in terms of accuracy and very time consuming in terms of simulation speed but not feasible for complex digital circuits. There are examples of electrical-level simulators of soft error detection in the literature such as [7]. Switch-level soft error simulation based models can be a tradeoff between gate-level abstraction and electrical-level abstraction. Switch-level can model important characteristics in MOS circuits such as charge sharing and variation in driven strengths [8] [9]. The switch-level models used in this work are based on Verilog strength and logic levels and are provided by Verilog Hardware Descriptor Language Reference Manual [10]. These models can imitate important phenomena of electrical-level such as variations in driven strengths due to different voltage levels induced by SETs and the effect of the storage strength of the node capacitance. These switch-level models were previously used in different work such as in [11] where static faults are injected at gate of a switch.

## 1.2. Motivation

Due to progress in technology, modern circuits are becoming more sensitive to soft errors. The use of simulation based soft error detection is important as it allows detection of design weakness at early stage of the design. The use of switch-level models for soft error detection simulation is an alternative to electrical-level and gate-level models. Simulation soft error detection based on switch-level models can overcome the speed limitation and feasibility of complex digital circuits of electrical-level models and the accuracy limitation of gate-level models. Several soft error simulators using various techniques are available in the literature such as [12] [13]. The developed simulator in this work uses Verilog strength and logic levels models to simulate transient injection in combinational circuits. The developed simulator is array based and is programmed in Matlab scripting language. Furthermore, an algorithm is developed to significantly speed up the simulation process when compared to the non-algorithm based simulator based on the same switch-level models.

#### 1.3. Summary of Contribution

The objective of this project is to present a soft error switch-level based simulator. This simulator has the ability to inject SETs of different strengths at different locations of a combinational circuit. The contribution to the project is summarized as following:

- Coding the main switch-level functions that allow modeling of CUT. These functions use

models based on Verilog strength and logic levels [10] allowing the injection of transients of

different logic levels and strength levels. These transients are classified in 23 types.

- Parsing the netlist gate-level of CUT expressed in Verilog into data structure gate-level.

- Parsing the data structure gate-level of CUT into switch-level data structure.

- The developed simulator can inject the transients at different location types such as drain, gate or inputs of a logic gate. The soft error coverage (or fault coverage) can be determined for any of these location types. This feature of the simulator shows the effect of the transient injection location type on the soft error coverage.

- The results of the simulation are stored in arrays called the profiling maps. These maps allow

the determination of the status of the transient injection location versus the injected transient

type and the test vector used to detect the corresponding transient.

- The created profiling maps are used to build statistical results based on the used test vectors.

The progress of the fault coverage due to injected transients can be plotted against the order of the applied test vectors allowing the evaluation of the efficiency of the applied test vectors.

- Development of an algorithm allowing the design of new soft error detection simulator SimV<sub>2</sub>. This simulator achieved a significant speed-up compared to SimV<sub>1</sub> non-algorithm based developed in this work as well

- Timing equations are determined based on run time of the developed simulators  $SimV_1$  and  $SimV_2$

- Analytical study is conducted based on the experimental results of fault coverage and simulation run time.

## 1.4. Project Organization

The remainder of the chapters is organized as follows: Chapter 2 discusses the main switch-level models implemented in this work. Chapter 3 explains the coding of CUT in gate-level and switch-level data structures and provides a large view of the simulation environment. Chapter 4 describes the architecture of the non-algorithm based simulator SimV<sub>1</sub>. Chapter 5 explains how

the developed algorithm is applied to  $SimV_2$  simulator and describes its architecture. Chapter 6 presents the results of the experiments extracted from  $SimV_1$  and  $SimV_2$  simulators. Chapter 7 presents the conclusion of this work followed by a cited publication and references.

## Chapter 2

#### Main Functions of the Simulator

## 2.1. Verilog Strength and Logic Levels

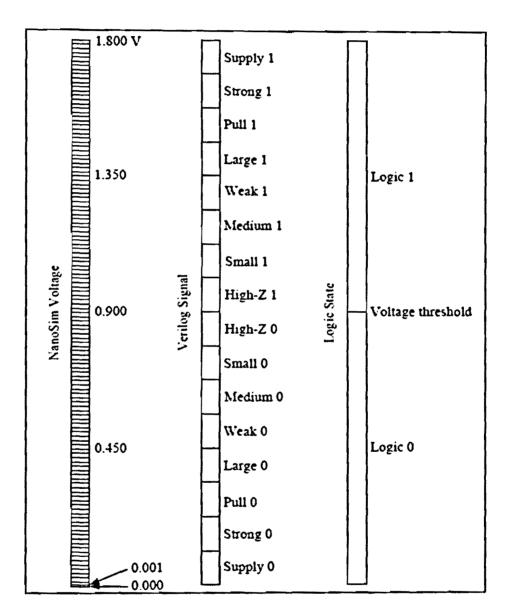

The switch-level soft error models in this work use the Verilog strength and logic levels [10]. Table 1 [14] shows how the logic levels and strength levels are structured and coded. There are 3 logic levels 0, 1, U, called respectively logic 0, logic 1, and unknown. These logic levels are associated with 7 levels of strength varying from small to supply. The 2-bit logic code represents the logic level and the 3-bit strength code represents the strength level. The state code combines the logic level and strength level codes and they are coded in 5-bit. This represents the state of the signals of the switch-level models. Logic levels Z and X have special significance. The logic code xx means that the logic of the signal has no significance as the strength level is below small strength level, thus the state codes associated to Z and X are respectively 00000 and 10000 representing "High Impedance" and the OFF state of CMOS switch. In addition, table 1 shows the decimal representation of the logic and strength codes. This representation is used for the simulation program.

Table 1: Verilog coding representation of logic and strength levels and their decimal representation

| Logic<br>Level | Verilog<br>Strength Level | Logic<br>Code | Strength<br>Code | State code |

|----------------|---------------------------|---------------|------------------|------------|

| 0              | Supply                    | 00            | 111              | 00111      |

| 0              | Strong                    | 00            | 110              | 00110      |

| 0              | Pull                      | 00            | 101              | 00101      |

| 0              | Large                     | 00            | 100              | 00100      |

| 0              | Weak                      | 00            | 011              | 00011      |

| 0              | Medium                    | 00            | 010              | 00010      |

| 0              | Small                     | 00            | 001              | 00001      |

| 1              | Supply                    | 01            | 111              | 01111      |

| 1              | Strong                    | 01            | 110              | 01110      |

| 1              | Pull                      | 01            | 101              | 01101      |

| 1              | Large                     | 01            | 100              | 01100      |

| 1              | Weak                      | 01            | 011              | 01011      |

| 1              | Medium                    | 01            | 010              | 01010      |

| 1              | Small                     | 01            | 001              | 01001      |

| Ü              | Supply                    | 11            | 111              | 11111      |

| U              | Strong                    | 11            | 110              | 11110      |

| U              | Pull                      | 11            | 101              | 11101      |

| U              | Large                     | 11            | 100              | 11100      |

| U              | Weak                      | 11            | 011              | 11011      |

| U              | Medium                    | 11            | 010              | 11010      |

| U              | Small                     | 11            | 001              | 11001      |

| Z              | High Z                    | xx            | 000              | 00000      |

| Х              | Don't care                | xx            | 000              | 10000      |

| Decimal Re | Decimal Representation |  |  |  |  |

|------------|------------------------|--|--|--|--|

| Logic      | Strength               |  |  |  |  |

| Code       | Code                   |  |  |  |  |

| 0          | 7                      |  |  |  |  |

| 0          | _6                     |  |  |  |  |

| 0          | 5                      |  |  |  |  |

| 0          | 4                      |  |  |  |  |

| 0          | 3                      |  |  |  |  |

| 0          | 2                      |  |  |  |  |

| 0          | 11                     |  |  |  |  |

| 1          | 7                      |  |  |  |  |

| 1          | 6                      |  |  |  |  |

| 1          | 5_                     |  |  |  |  |

| 1          | 4                      |  |  |  |  |

| 1          | 3                      |  |  |  |  |

| 1          | 2                      |  |  |  |  |

| 1          | _1                     |  |  |  |  |

| 3          | 7                      |  |  |  |  |

| 3          | 6                      |  |  |  |  |

| 3          | 5                      |  |  |  |  |

| 3          | 4                      |  |  |  |  |

| 3          | 3                      |  |  |  |  |

| 3          | _2                     |  |  |  |  |

| 3          | 11                     |  |  |  |  |

| 0          | _0                     |  |  |  |  |

| 2          | 0                      |  |  |  |  |

Voltage levels and strength levels of signals are related as shown in figure 1. There is a direct relationship between voltage levels and strength levels for 1.8 V supply voltage [16]. Switch-level strength-based models using Verilog logic and strength levels were previously used in

different works such as [11] where static faults are injected at gate of a switch. Similar switch-level models are used to study the delay introduced by resistive faults [14]. These switch-level models were used for soft error detection for the first time in the cited publication [15].

Figure 1: Strength levels versus Voltage levels adapted from [16].

#### 2.2. Switch-Level Functions

The signals processed by the switch-level models are based on 5-bit coding representing the state code which combines the logic and strength levels as shown in Table 1. In the absence of transients, the strength code of all signals are assumed to be at Supply strength level "111". The switch-level models in this work are based on Verilog signal resolution rules described as follows:

- When a switch is OFF, the signal at drain of a switch takes the state code "10000" and hence this signal does not participate in resolving the output at the connection node.

- When a switch is ON, the signal at drain of a switch will take the state code of the signal at the source of this switch.

- When the signal at gate of a switch has a logic code unknown (i.e. U) or state code of high

impedance, then the state code of the signal at drain of this switch will be "11111" which is

the unknown logic code and supply strength code.

#### 2.2.1. funC Function

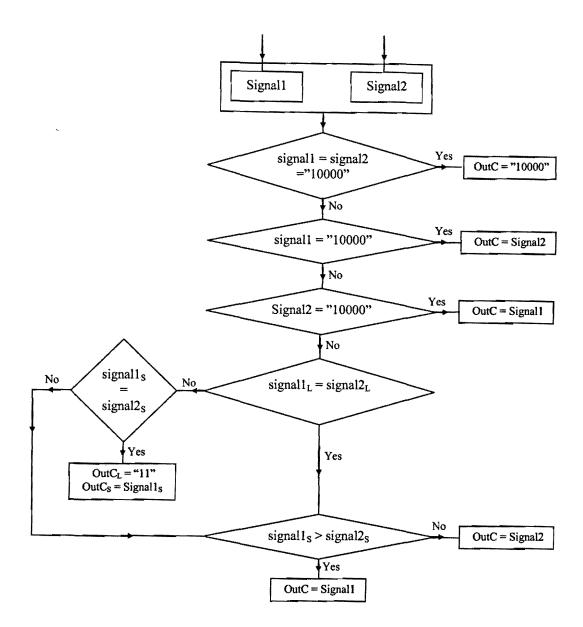

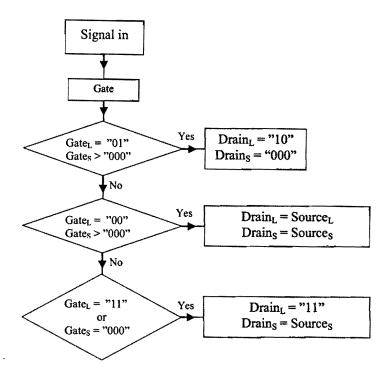

The flow diagram shown in Figure 2 describes the functionality of the connection node. This function resolves the output of the connection node for two incident signals presented at this node, Signal1 and Signal2. Signal1<sub>L</sub> and Signal2<sub>L</sub> represent respectively the logic code of the incident signals 1 and 2 at the node. Signal1<sub>S</sub> and Signal2<sub>S</sub> represent respectively the strength code of the incident signals 1 and 2 at the node. OutC represents the output of funC. OutC<sub>L</sub> and OutC<sub>S</sub> represent respectively the logic and strength codes of funC output.

Figure 2: Flow Diagram of funC Function

OutC<sub>L</sub>: Logic code of funC output; OutC<sub>S</sub>: Strength code of funC output; Signal1<sub>L</sub>, Signal2<sub>L</sub>: Logic code of the incident signals 1 and 2 at the node Signal1<sub>S</sub>, Signal2<sub>S</sub>: strength code of the incident signals 1 and 2 at the node

#### 2.2.2. funN Function

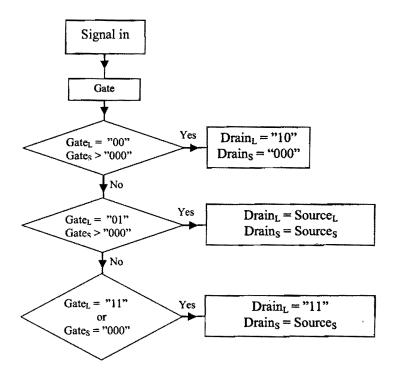

This function is modeled based on Verilog rules described earlier. The flow diagram shown in Figure 3 describes the functionality of funN which represents the NMOS switch. Drain<sub>L</sub> and

Drain<sub>s</sub> represent respectively, the logic and strength code of the signal at drain. Gate<sub>L</sub> and Gate<sub>s</sub> represent respectively the logic and strength code of the signal at gate. Source<sub>L</sub> and Source<sub>s</sub> represent respectively the logic and strength code of the signal at source

Figure 3: Flow Diagram of funN Function

Gate<sub>L</sub>, Drain<sub>L</sub>, Source<sub>L</sub>: Logic code of signals at gate, drain and source respectively Gate<sub>S</sub>, Drain<sub>S</sub>, Source<sub>S</sub>: Strength code of signals at gate, drain and source respectively

### 2.2.3. funP Function

Similarly, funP function is modeled based on Verilog rules described earlier. The flow diagram shown in Figure 4 describes the functionality of funP which represents the PMOS switch.

Figure 4: Flow Diagram of funP Function

Gate<sub>L</sub>, Drain<sub>L</sub>, Source<sub>L</sub>: Logic code of signals at gate, drain and source respectively. Gate<sub>S</sub>, Drain<sub>S</sub>, Source<sub>S</sub>: Strength code of signals at gate, drain and source respectively.

## 2.2.4. Capacitance Functionality

Due to technology scaling and the shrinking size of transistors, the charge of capacitance values are weak [10]. The modeled capacitance in this work takes the strength code "001" (i.e. strength level "small"). The logic value of a capacitance takes the logic value of the output of the resolved connection node.

## 2.2.5. Example of Transient Injection at Drain of a

### Switch Applied to NAND2 gate

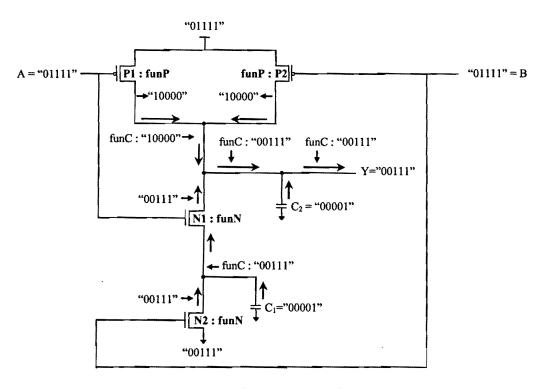

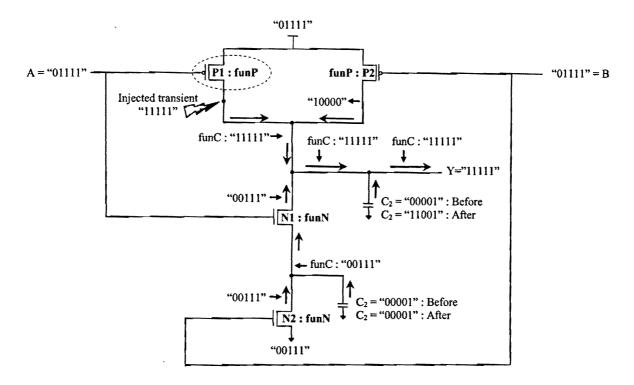

Figure 5 shows NAND2 gate translated in switch-level. The main functions used to resolve the output Y of NAND2 gate are funP, funN and funC. The capacitance values C<sub>1</sub> and C<sub>2</sub> are updated after applying funC at the node.

Figure 5: Example of NAND2 gate in switch-level

Figure 6 shows the same example of NAND2 gate when a transient "11111" is injected at the drain of P1: PMOS switch. This transient injection results in soft error as the resolved output Y of the NAND2 gate changes to "11111". This example shows how the capacitance values are updated. According to the capacitance functionality, the capacitance strength code is "001" and its logic takes the logic of the resolved connection node. The "Before" transient injection and

"After" transient injection values of  $C_1$  and  $C_2$  show an example of how these capacitances update their values.

Figure 6: Example of NAND2 gate in switch-level where the transient "11111" is injected at the drain of P1: PMOS

## Chapter 3

#### Fundamental Architecture and Data Structure of the

#### **Simulator**

This chapter explains in details the architecture and the data structure of the simulation environment. The simulator is array based and a coding structure is used to code CUT in gate and switch-level. Examples are provided along this chapter to clarify the idea of how the data structures are coded.

#### 3.1. Programming Language

All the programs developed in this work are coded in Matlab using m-file format. A large amount of data is processed through the simulation and the use of an optimized programming language is important. Matlab scripting language is a combination of different languages offering simple, efficient and optimized functions targeting array based applications and offers different tools such as the Profile option. This tool allows the user to optimize the code as it offers a detailed execution time report for the full program line by line. This option along other tools, help improve the speed of the developed program.

#### 3.2. Simulation Environment

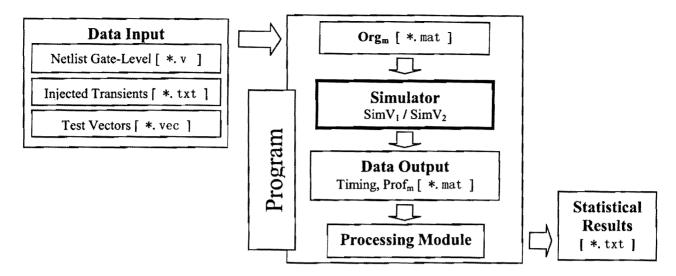

The flow diagram in Figure 7 presents a large view of the simulation environment. There are three stages for the simulation and can be classified as follows:

- Data Input: Contains the files representing CUT, the test vectors and the injected transient types. The test vectors in this work are based on compaction algorithm [18] and are design for gate-level circuits. These test vectors are used for the first time on the switch-level models used in this work for the purpose of soft error simulation. There are different formats and are loaded into the simulator (i.e. Block Program). A detailed explanation of the content of these files is provided in section 3.2.1.

- **Program**: Represents the processing part of the simulation environment and is coded entirely in Matlab scripting language. Different sections are dedicated for this block.

- Statistical Results: Represents the different results extracted from the simulation. These detailed results are used to conduct statistical study on the performance of the simulator, test vectors and the effect of transient injection location type on the fault coverage. Chapter 6 is based on these results.

Figure 7: Flow diagram of the simulation environment

### 3.2.1. Data Input

The different file formats shown in figure 8 target the C17 benchmark circuit. Any other combinational circuit can be loaded into the simulator similarly as long as its format is expressed in the same manner as the C17 sample. These files are as follows:

- C17\_TV.vec: Represents the test pattern for the C17 circuit. Number 5 indicates the number of inputs of the circuit. The notation END indicates the end of the test vectors. This data is accessed line by line where the most significant bit is devoted to the first input of the circuit. Every bit of the data input is expressed in decimal and represent the logic level. The strength level is assumed to be "111" which is 7 in decimal. The inputs of CUT are then formatted in a logic and strength level format.

- C17\_netlist\_g.v: Represents the netlist gate-level of C17 circuit expressed in Verilog format.

Any circuit can be loaded into the simulator in the same format.

• Transients.txt: Represents the decimal format of the transient types injected into CUT. The logic and strength levels are represented respectively by the column on the left and right.

Transients.txt

Figure 8: The simulator data input for C17 Circuit

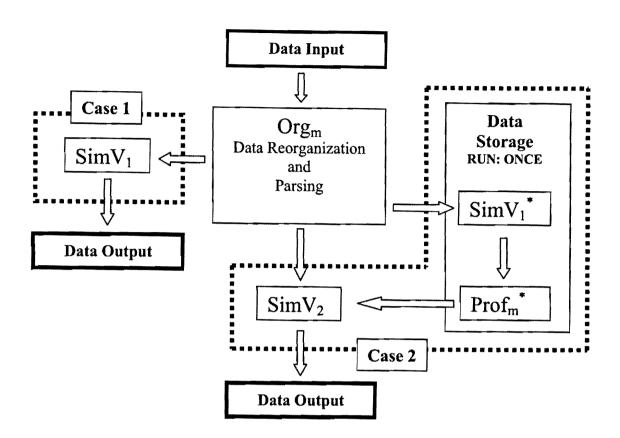

#### 3.2.2. Simulator Flow Diagram

The flow diagram in figure 9 shows a highlight of the simulation architecture. There are two developed simulators in this work; SimV<sub>1</sub> and SimV<sub>2</sub>. Chapter 4 and 5 provide respectively,

detailed explanation on SimV<sub>1</sub> and SimV<sub>2</sub>. The various blocks of this flow diagram are as follows:

- Data Input: Explained in section 3.2.1.

- Org<sub>m</sub>: Reorganizes, parses and codes the data input. Sections 3.3, 3.4, 3.5 and 3.6 provide

detailed explanations of how these data structures are coded.

- Case1: Represents SimV<sub>1</sub> non algorithm based version of the simulator.

- Case2: Represents SimV<sub>2</sub> algorithm based version of the simulator. The block titled "Data Storage RUN: ONCE" processes all the logic gate types (i.e. AND2, NAND2, etc) independently by running SimV<sub>1</sub>\* simulator on these gates. Exhaustive test vectors are applied for the simulation and the results are stored in 3D profiling maps (i.e. Prof<sub>m</sub>\*) in a \*.mat format file. Detailed explanation of Prof<sub>m</sub>\*, SimV<sub>2</sub> and SimV<sub>1</sub>\* is provided in chapter 5. The block "Data Storage RUN: ONCE" will run only one time and generates a \*.mat file that is used for any circuit simulated by SimV<sub>2</sub>, thus its run time is not part of the simulation time.

- Data Output: Provides the results of the simulation in profiling maps arrays Prof<sub>m</sub> and the simulation execution time (i.e. Timing). Section 3.2.3 is dedicated to the structure of the profiling maps Prof<sub>m</sub>.

Figure 9: Flow diagram of the Simulator

## 3.2.3. Data Output

The data output of the simulators are stored in 2D arrays and are called profiling maps "Prof<sub>m</sub>" due to the way these arrays store the results of the simulation. The C17 circuit profiling maps are used as example of the data output. Table 2 shows the profiling map map\_det representing the fault detection due to transient injection at a drain of a switch. This table is organized as follows:

- T<sub>Loc</sub>: Represents the location of drain or gate as transient injection location for C17 circuit.

There are 24 drains or gates in C17 circuit where the transient can be injected.

- T<sub>L</sub>: Represents the transient logic code expressed in decimal

#### • T<sub>S</sub>: Represents the transient strength code expressed in decimal

The values in table 2 are either 1 or 0 representing respectively, detection or non-detection of the transient injection. For example:

[Transient location: " $T_{Loc} = 5$ ", Transient value: " $T_L$ : $T_S$ " = "1:7", Results = (1)]

Explanation: The corresponding injected transient is detected at location (5).

Table 2: map\_det of C17 circuit

|         |       |                  |   |   |   |   |    |   | _ |   | •         |    |    |    |    |

|---------|-------|------------------|---|---|---|---|----|---|---|---|-----------|----|----|----|----|

|         |       | $T_{\text{Loc}}$ | 1 | 2 | 3 | 4 | 5  | 6 | 7 | 8 | ********* | 21 | 22 | 23 | 24 |

| $T_{L}$ | $T_S$ |                  |   |   |   |   |    |   |   |   |           |    |    |    |    |

| 1       | 7     | 1                | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

| 0       | 0     | ]                | 0 | 1 | 0 | 0 | 0  | 1 | 0 | 0 |           | 0  | 1  | 0  | 0  |

| 0       | 1     |                  | 1 | 1 | 0 | 0 | 1  | 1 | 0 | 0 |           | 1  | 1  | 0  | 0  |

| 0       | 2     | 1                | 1 | 1 | 0 | 0 | 1  | 1 | 0 | 0 |           | 1  | 1  | 0  | 0  |

| 0       | 3     | 1                | 1 | 1 | 0 | 0 | 1  | 1 | 0 | 0 |           | 1  | 1  | 0  | 0  |

| 0       | 4     |                  | 1 | 1 | 0 | 0 | 1  | 1 | 0 | 0 |           | 1  | 1  | 0  | 0  |

| 0       | 5     | 1                | 1 | 1 | 0 | 0 | 1  | 1 | 0 | 0 |           | 1  | 1  | 0  | 0  |

| 0       | 6     | 1                | 1 | 1 | 0 | 0 | 1  | 1 | 0 | 0 |           | 1  | 1  | 0  | 0  |

| 1       | 0     |                  | 0 | 1 | 0 | 0 | 0  | 1 | 0 | 0 |           | 0  | 1  | 0  | 0  |

| 1       | 1     | 1                | 0 | 1 | 1 | 1 | 0  | 1 | 1 | 1 |           | 0  | 1  | 1  | 1  |

| 1       | 2     | 1                | 0 | 0 | 1 | 1 | 0  | 0 | 1 | 1 |           | 0  | 0  | 1  | 1  |

| 1       | 3     | 1                | 0 | 0 | 1 | 1 | 0  | 0 | 1 | 1 |           | 0  | 0  | 1  | 1  |

| 1       | 4     |                  | 0 | 0 | 1 | 1 | 0  | 0 | 1 | 1 |           | 0  | 0  | 1  | 1  |

| 1       | 5     |                  | 0 | 0 | 1 | 1 | 0  | 0 | 1 | 1 |           | 0  | 0  | 1  | 1  |

| 1       | 6     | 1                | 0 | 0 | 1 | 1 | 0  | 0 | 1 | 1 |           | 0  | 0  | 1  | 1  |

| 3       | 0     | 1                | 0 | 1 | 0 | 0 | 0  | 1 | 0 | 0 |           | 0  | 1  | 0  | 0  |

| 3       | 1     |                  | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

| 3       | 2     |                  | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

| 3       | 3     | 1                | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

| 3       | 4     |                  | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 | ********  | 1  | 1  | 1  | 1  |

| 3       | 5     | 1                | 1 | 1 | 1 | 1 | -1 | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

| 3       | 6     | 1                | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

| 3       | 7     | 1                | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |           | 1  | 1  | 1  | 1  |

Table 3 shows map\_detATV profiling map. This array is organized similarly to map\_det array. The results in this table represent the index of the test vector used to detect the injected transient in case of detection. For example:

- [ Transient location: " $T_{Loc} = 5$ ", Transient value: " $T_L:T_S$ " = "0:1", Results = (8) ] Explanation: The  $8^{th}$  test vector detects the injected transient "0:1" at location (5).

- [ Transient location: "T<sub>Loc</sub> = 1", Transient value: "T<sub>L</sub>:T<sub>S</sub>" = "0:0", Results = (12)] Explanation: All the 12 test vectors are used and the injected transient "0:0" at location (1) is not detected. map\_det shows (0) as results indicating a non detection of transient injection at this location.

The sum of all the values of map\_detATV represents the number of times the circuit is simulated in other terms; this is called the total number of transients.

The sum of all the values of map\_det represents the number of detected faults. The number of coefficient of map\_det array is called the number of injected faults. The soft error coverage is evaluated based on (EQ-3-1) equation:

Soft Error Coverage (%) =

$$\frac{Number\ of\ detected\ faults}{Number\ of\ injected\ faults}$$

· 100 (EQ - 3 - 1)

Table 3: map\_detATV of C17 circuit

|         |           |   |    |    |    |    |    |    |    |    | }        |    |    |    | 1  |

|---------|-----------|---|----|----|----|----|----|----|----|----|----------|----|----|----|----|

|         | $T_{Loc}$ | : | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |          | 21 | 22 | 23 | 24 |

| $T_{L}$ | $T_S$     |   |    |    |    |    |    |    |    |    |          |    |    |    |    |

| 1       | 7         |   | 1  | 1  | 4  | 1  | 2  | 2  | 1  | 1  |          | 2  | 2  | 1  | 1  |

| 0       | 0         |   | 12 | 4  | 12 | 12 | 12 | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 0       | 1         |   | 1  | 4  | 12 | 12 | 8  | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 0       | 2         |   | 1  | 4  | 12 | 12 | 8  | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 0       | 3         |   | 1  | 4  | 12 | 12 | 8  | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 0       | 4         |   | 1  | 4  | 12 | 12 | 8  | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 0       | 5         |   | 1  | 4  | 12 | 12 | 8  | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 0       | 6         |   | 1  | 4  | 12 | 12 | 8  | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 1       | 0         |   | 12 | 4  | 12 | 12 | 12 | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 1       | 1         |   | 12 | 4  | 6  | 6  | 12 | 3  | 1  | 1  |          | 12 | 2  | 1  | 1  |

| 1       | 2         |   | 12 | 12 | 6  | 6  | 12 | 12 | 1  | 1  |          | 12 | 12 | 1  | 1  |

| 1       | 3         |   | 12 | 12 | 6  | 6  | 12 | 12 | 1  | 1  |          | 12 | 12 | 1  | 1  |

| 1       | 4         |   | 12 | 12 | 6  | 6  | 12 | 12 | 1  | 1  |          | 12 | 12 | 1  | 1  |

| 1       | 5         |   | 12 | 12 | 6  | 6  | 12 | 12 | 1  | 1  |          | 12 | 12 | 1  | 1  |

| 1       | 6         |   | 12 | 12 | 6  | 6  | 12 | 12 | 1  | 1  |          | 12 | 12 | 1  | 1  |

| 3       | 0         |   | 12 | 4  | 12 | 12 | 12 | 3  | 12 | 12 |          | 12 | 2  | 12 | 12 |

| 3       | 1         |   | 1  | 4  | 6  | 6  | 8  | 3  | _1 | 1  |          | 12 | 2  | 1  | 1  |

| 3       | 2         |   | 1  | 4  | 6  | 6  | 8  | 3  | 1  | 1  |          | 12 | 2  | 1  | 1  |

| 3       | 3         |   | 1  | 4  | 6  | 6  | 8  | 3  | 1  | 1  |          | 12 | 2  | 1  | 1  |

| 3       | 4         |   | 1  | 4  | 6  | 6  | 8  | 3  | 1  | 1  | ******** | 12 | 2  | 1  | 1  |

| 3       | 5         |   | 1  | 4  | 6  | 6  | 8  | 3  | 1  | 1  |          | 12 | 2  | 1  | 1  |

| 3       | 6         |   | 1  | 4  | 6  | 6  | 8  | 3  | 1  | 1  |          | 12 | 2  | 1  | 1  |

| 3       | 7         |   | 1  | 1  | 4  | 1  | 1  | 1  | 1_ | 1  |          | 1  | 1  | 1  | 1  |

# 3.2.4. Processing Module

This block processes the profiling maps; map\_det and map\_detATV in order to calculate the soft error coverage and other statistical results. This module provides the Statistical Results mentioned in figure 7. All the results in chapter 6 are provided by this module.

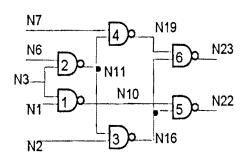

# 3.3. Data Structure of Netlist Gate-Level (netlist\_g)

This section explains the data structure and the coding architecture of gate-level netlist of CUT. The schematic of C17 circuit shown in figure 10(a) translates the Verilog netlist gate-level (i.e. input file of the simulator). Every logic gate is coded accordingly to table 4. Based on these codes, the first column of table 5(a) is code (11) representing a NAND2 gate and the second column represents the address of the output. Section 3.4 explains in detail how these addresses are used. Columns in1 to in10, are the addresses of the inputs of the logic gates. An address "0", indicates that the corresponding input does not exist. This structure is the main idea behind the simulation. Any combinational circuit can be parsed into this structure. There are 10 possible inputs indicating that this simulator can handle circuits built with up to 10 logic gates. Table 4 shows the different gate types and their corresponding codes.

Figure 10(a): C17 Circuit Before net reorganisation

Figure 10(b): C17 Circuit After net reorganisation

Figure 10: C17 Circuit before and after net reorganisation

Based on the information of Table 5(a), the maximum number of addresses in this 2D array is 23. The block Org<sub>m</sub> mentioned in section 3.2.2. reorganizes these addresses in a way that their numbers will be minimized when there are gaps between these numbers. Figure 10(b) and Table 5(b) show the results of the addresses reorganization. The maximum number of addresses after

reorganization is 11. This operation is useful as it reduces the size of the storage array and resulting in maximizing the speed of the simulation. The storage array Data\_inout\_g as shown in table 6, its size depends on the number of nets in the circuit and as the index of the number of the nets is reduced, the size of the storage array is reduced. Section 3.4. explains in detail the structure of this storage array.

Table 4: Coding of the gate types

| Gate   | Gate | Gate  | Gate |

|--------|------|-------|------|

| Type   | Code | Type  | Code |

|        |      |       | ·    |

| BUFFER | 1    | AND10 | 21   |

| NOT    | _ 2  | AND9  | _22  |

|        |      | AND8  | 23   |

| NAND10 | 3    | AND7  | 24   |

| NAND9  | 4    | AND6  | 25   |

| NAND8  | 5    | AND5  | 26   |

| NAND7  | 6    | AND4  | 27   |

| NAND6  | 7    | AND3  | 28   |

| NAND5  | 8    | AND2  | 29   |

| NAND4  | 9    |       |      |

| NAND3  | 10   | OR10  | 30   |

| NAND2  | 11   | OR9   | 31   |

|        |      | OR8   | 32   |

| NOR10  | 12   | OR7   | 33   |

| NOR9   | 13   | OR6   | 34   |

| NOR8   | 14   | OR5   | 35   |

| NOR7   | 15   | OR4   | 36   |

| NOR6   | 16   | OR3   | 37   |

| NOR5   | 17   | OR2   | 38   |

| NOR4   | 18   |       |      |

| NOR3   | 19   | XOR2  | 39   |

| NOR2   | 20   | -     | -    |

Table 5: Data structure of C17 netlist gate-level (netlist\_g) before and after net reorganisation

Table 5(a): Data structure of C17 netlis gate-level before net reorganisation

| Gate Type | Output | inl | in2 | in3 | in4 | in5 | in6 | in7 | in8 | in9 | in10 |

|-----------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 11        | 10     | _1  | 3   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | _11    | 3   | 6   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | 16     | 2   | 11  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | 19     | 11  | 7   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | 22     | 10  | 16  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | 23     | 16  | 19  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

Table 5(b): Data structure of C17 netlist gate-level after net reorganisation

| Gate Type | Output | in1 | in2 | in3 | in4 | in5 | in6 | in7 | in8 | in9 | in10 |

|-----------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 11        | 6      | 1   | 3   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | 7      | 3   | 4   | 0   | _0  | 0   | 0   | 0   | 0   | 0   | 0    |

| 11        | 8      | 2   | 7   | 0   | 0   | 0   | 0   | _ 0 | 0   | 0   | 0    |

| 11        | 9      | 7   | 5   | 0   | 0   | 0   | 0   | 0   | _0  | _0  | 0    |

| 11        | 10     | 6   | 8   | 0   | 0   | 0   | _0  | 0   | _0  | 0   | 0    |

| 11        | 11     | 8   | 9   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

# 3.4. Processing and Storing Arrays of Gate-Level

This section explains how a circuit is processed and its primary output is resolved. Table 6 shows the following:

- Data\_in\_g: Contains the addresses of the primary inputs of C17 circuit

- Data\_out\_g: Contains the addresses of the primary output of C17 circuit

- Data\_inout\_g: Contains the resolved values of every net of the circuit. Address Index is the address of input or output of any logic gate as shown in Table 5(b). L<sub>L</sub> and L<sub>S</sub> represent

respectively the logic and strength codes of CUT connection links. Stat<sub>v</sub> represents the status of the content of the corresponding address. "Stat<sub>v</sub> = 1" indicates that the value corresponding to this address is not resolved and similarly, when "Stat<sub>v</sub> = 0", this indicates that the value corresponding to this address is resolved. The values of the address index from 1 to 5 represents the addresses of the primary inputs as shown in Data\_in\_g and the  $L_L$  and  $L_S$  corresponding to these values are the first applied test vectors "0111" as shown in figure 8 and consequently the corresponding Stat<sub>v</sub> values are filled by zeros.

This is the main idea of how the data is stored when processing the gate-level data structure. When a CUT is entirely processed and the primary outputs of the circuit are resolved all the values of Staty become "0".

Table 6: The main storing and indexing arrays needed to process C17 circuit gate-level

| ·         |            | Data_inou     | ıt g              | · · · · · · · · · · · · · · · · · · · |    |

|-----------|------------|---------------|-------------------|---------------------------------------|----|

| Data_in_g | Data_out_g | Address Index | Stat <sub>v</sub> | L <sub>L</sub>                        | Ls |

| 1         | 10         | 11            | _0                | 0                                     | 7  |

| 2         | 11         | 2             | 0                 | 1                                     | 7  |

| 3         |            | 3             | 0                 | 1                                     | 7  |

| 4         |            | 4             | 0                 | 1                                     | 7  |

| 5         |            | 5             | 0                 | 1                                     | 7  |

|           |            | 6             | 1                 | 0                                     | 0  |

|           |            | 7             | 1                 | 0                                     | 0  |

|           |            | 8             | 1                 | 0                                     | 0  |

|           | ¥          | 9             | 1                 | 0                                     | 0  |

|           |            | 10            | 1                 | 0                                     | 0  |

|           |            | 11            | 1                 | 0                                     | 0  |

# 3.5. Data Structure of Netlist Switch-Level (netlist\_s)

# 3.5.1 Coding Architecture of netlist\_s

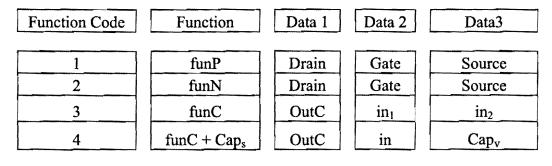

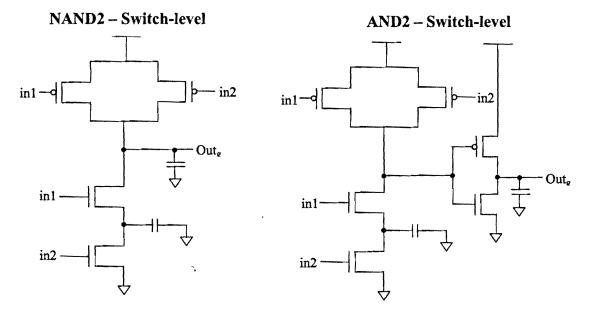

The main idea of the coding structure of netlist switch-level is similar to the coding structure of netlist gate-level. The switch-level of CUT is composed of funP, funN and funC representing respectively the switches P, N and the function of the connection node. These functions were previously explained in chapter 2. The capacitance is represented by Cap<sub>v</sub> (i.e. Capacitance value) and Cap<sub>s</sub> represents the updated capacitance value at the node. Table 7 uses these notations and is organized as follows:

- Function Code: Represents the codes of the functions in column two.

- Function: Represents the main functions of the switch level funN, funP, funC and (funC + Caps). Function (funC + Caps) performs two operations as follows:

- o 1<sup>st</sup> operation: Resolves the connection node by applying funC on the input (in) and the previous value of the capacitance Cap<sub>v</sub> (i.e. Capacitance value). The resolved output is represented by OutC.

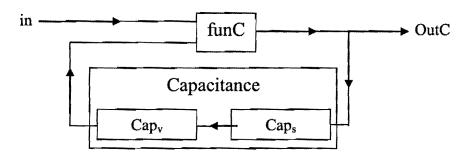

- o **2<sup>nd</sup> operation**: Updates the capacitance value Cap<sub>v</sub> by Cap<sub>s</sub> (i.e. Capacitance store) value. The functionality of Cap<sub>s</sub> is based on the explanation provided on the capacitance in section 2.2.4. Figure 11 shows a flow diagram of (funC + Cap<sub>s</sub>) function where OutC is resolved by funC and the Cap<sub>v</sub> is updated by Cap<sub>s</sub>

- Data 1: Represents the output of the function (i.e Drain for funP and funN)

- Data 2, 3: Represents the inputs of the functions (i.e. the inputs funP, funN and funC).

Table 7: Coding of the switch-level functions

Figure 11: How the function code "4" processes the data

A structure based on this coding architecture is created for every single logic gate of table 4 (i.e. Gates type). Org<sub>m</sub> block shown previously will build a switch-level netlist based on these structures for any combinational circuit. The following sections of this chapter focus on providing detailed information on the logic gates switch-level coding structure.

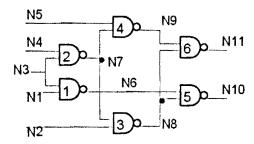

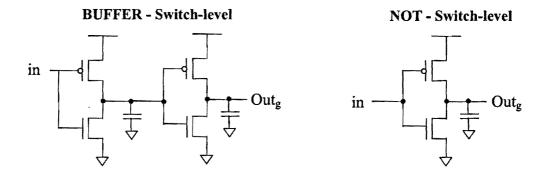

#### **3.5.2. NOT Gate**

Figure 12 shows the switch-level of NOT gate. Table 8 shows the coding and data structure of switch-level NOT gate. The main concept is to affect addresses to the links created for the switch-level (i.e. D(Drain), G(Gate), S(Source), OutC,  $Cap_v$ , VDD and GND). These links represent the basic elements of the switch-level structure. The equation (EQ - 3 - 2) evaluates the incrementation start address for a logic gate.

$$Add_{incl} = [Number of input(s) of the logic gate + 1]$$

(EQ - 3 - 2)

Add<sub>inc1</sub> represents the incrementation start address. The NOT gate shown in table 8 represents the organization of the data structure and the results of the coding of these structures. The numbers of "Coded Data" represent the addresses for Data1, Data2 and Data3. The "Function" column is similar to the structure created for gate-level and it is used to identify the operators. (i.e. funN, funP, funC and (funC + Caps)). The "Coded Data" and "Data structure" are organized as follows:

- (in) and (Out<sub>g</sub>) represent respectively the input and output of NOT gate. The addresses (1) and (2) are respectively allocated to these elements.

- VDD and GND (i.e. Supply and ground) get respectively the addresses (3) and (4) as the incrementation of the addresses starts from  $Add_{inc1} = 2$ . The remainder incrementation of the addresses of the links of the switch-level of this logic gate will start from  $Add_{inc2}$  as shown in (EQ 3 3).  $Add_{inc2}$  represents the starting incermentation address for the remainder elements of this logic gate.

$$Add_{inc2} = Add_{inc1} + 2 = 4$$

(EQ - 3 - 3)

- The remainder elements of this table are coded as follows:

- o D[1], D[2]: Represents respectively the drains of P and N switches numbered by order of priority access. The order is important because of the dependency of the switches to resolve the output of the logic gate. As the program processes the information in sequence, it is important to have these functions in certain order for coherent results when resolving the output of the logic gate.

- OutC [1]: Represents the output of funC function and it resolves the incident signals

D[1] and D[2].

- o Cap<sub>v</sub>: The capacitance value at the node.

- The Asterix sign followed by a number (i.e. \* number) has a particular meaning as it helps construct the addresses order. For example the notation (\*1 D[1]) indicates that the corresponding elements are increasingly numbered at these locations. The repeating elements in the table will simply keep their numbers. Once these numbers are completed, they will be assigned to the coded data table (i.e. [(\* number) + Add<sub>inc2</sub>]) starting from top to bottom and left to right. Based upon this data structure table, the program will be able to build the "Coded Data" table.

Figure 12: Switch-Level of BUFFER and NOT

Table 8: Coding and data structure of switch-level NOT gate

| ,     |                         | NOT - Switc | h-level   |                         |           |       |

|-------|-------------------------|-------------|-----------|-------------------------|-----------|-------|

| Index | Function                | Data 1      | Data 2    | Data3                   |           |       |

| 1     | funP                    | *1 D[1]     | in        | VDD                     | 7.0       |       |

| 2     | funN                    | *2 D[2]     | in        | GND                     | ří        |       |

| 3     | funC                    | *3 OutC[1]  | 1 D [1]   | 2 D [2]                 | Structure | Data  |

| 4     | funC + Cap <sub>s</sub> | Outg        | 3 OutC[1] | *4 Cap <sub>v</sub> [1] | re        |       |

|       | p                       |             |           |                         |           |       |

| 1     | 1                       | 5           | 1         | 3                       | İ         |       |

| 2     | 2                       | 6           | 1         | 4                       | Da        | C     |