# A NOVEL PREDICTIVE CONTROL STRATEGY FOR NEUTRAL-POINT CLAMPED CONVERTER WITH HARMONIC SPECTRUM SHAPING

By

# Jaksa Rubinic

B.Sc, University of Novi Sad, Novi Sad, Serbia, 2010M.Sc, University of Novi Sad, Novi Sad, Serbia, 2011

A thesis presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Applied Science in the Program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2016

© Jaksa Rubinic, 2016

# **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

# A Novel Predictive Control Strategy for Neutral-Point Clamped Converter with Harmonic Spectrum Shaping

Jaksa Rubinic

Master of Applied Science Electrical and Computer Engineering Ryerson University, Toronto, 2016

# Abstract

This thesis proposes a new predictive control strategy to achieve fixed-switching frequency operation for a neutral-point clamped (NPC) inverter. The classical fixed-sampling frequency finite control-set model predictive control (FSF-FCS-MPC) operates with variable switching frequency, and thus produces spread-spectrum in an output current. The classical method also suffers from high computational complexity as the number of converter voltage levels increases. To overcome these issues, a high performance variable sampling frequency finite control-set model predictive control (VSF-FCS-MPC) strategy is proposed to control the power converters.

The proposed control technique combines the advantages of space vector modulation (SVM) with a newly introduced mechanics to determine the appropriate sampling frequency. With these features the major requirements such as balancing of DC-link capacitor voltages, switching frequency minimization and common-mode voltage mitigation have been achieved with simultaneous elimination of even-order and inter-harmonics in the load current harmonic spectrum. The VSF-FCS-MPC strategy for current control with decoupled active/reactive power regulation of grid-connected multilevel converter was also analyzed.

Moreover, a novel DC-link voltage balancing technique is presented which eliminates the need for balancing the capacitor voltages through cost function, and thus alleviates the weighting factor design. An introduction of SVM highly reduces the calculation time by considering only

adjacent vectors, rendering FCS-MPC more suitable for implementation with multi-level converters with a number of voltage levels higher than three.

Finally, the proposed control technique has been validated through simulation and experimental verification and a detailed comparison of VSF-FCS-MPC with FSF-FCS-MPC and SVM is presented.

# Contents

| Author's Declaration                                                 | ii              |

|----------------------------------------------------------------------|-----------------|

| Abstract                                                             | iii             |

| List of Figures                                                      | viii            |

| CHAPTER 1 - INTRODUCTION                                             | 1               |

| 1.1 Introduction                                                     | 1               |

| 1.2 Converter Topologies                                             | 3               |

| 1.2.1 Two-Level Voltage Source Converter                             | 4               |

| 1.2.2 Three-Level NPC VSC                                            | 5               |

| 1.2.3 Four-Level Diode Clamped VSC                                   | 7               |

| 1.2.4 AFE NPC Rectifier                                              | 8               |

| 1.3 Current Control Methods for the Converters                       | 9               |

| 1.3.1 Linear Control with PWM or SVM                                 | 10              |

| 1.3.1.1 Pulse Width Modulation                                       | 10              |

| 1.3.1.2 Linear Control with Space Vector Modulation                  | 10              |

| 1.3.2 Hysteresis Current Control                                     | 13              |

| 1.4 Control Requirements                                             | 14              |

| 1.5 Motivation for the Research                                      | 15              |

| 1.6 Organization of the Thesis                                       | 16              |

| CHAPTER 2 - MODEL PREDICTIVE CONTROL                                 | 17              |

| 2.1 Introduction                                                     | 17              |

| 2.2 Predictive Control in Power Electronic                           | 18              |

| 2.2.1 Predictive Control Types                                       | 19              |

| 2.2.2 Control Requirements and Challenges for Three-Level Converters | 20              |

| 2.3 The Concept of FCS-MPC                                           | 21              |

| 2.3.1 FSC-MSC Operating Principle                                    | 22              |

| 2.3.2 Controller Design                                              | 25              |

| 2.3.3 Current FCS-MPC of a 2L-VSI                                    | 27              |

| 2.4 Applications of Model Predictive Control and Challenges          | 29              |

| 2.5 Summary                                                          |                 |

| CHAPTER 3 - VARIABLE SAMPLING FREQUECNY MODEL PREDICTIVE CONT        | ר <b>ROL</b> 31 |

| 3.1 Introduction                                                     | 31              |

| 3.2 Virtual System Simulator Model for Harmonic Spectrum Shaping     |                 |

| 3.2.1 Vector Selection Using SVM                                     |                 |

| 3.2.2 Auxiliary MPC and Virtual Load Current Calculation                   |    |

|----------------------------------------------------------------------------|----|

| 3.2.3 Load Current Verification                                            |    |

| 3.2.4 Sampling Frequency Shifter and Constrains                            | 40 |

| 3.2.5 Capacitor Voltage Balancing using P/N/O States                       | 41 |

| 3.3 Inverter – Side Predictive Control with Load Current Spectrum Shaping  | 43 |

| 3.3.1 Mathematical Model of NPC Inverter                                   | 45 |

| 3.3.2 Discrete-Time Model for Prediction                                   | 46 |

| 3.3.3 Cost Function Evaluation                                             | 47 |

| 3.3.4 Capacitor Voltage Balancing                                          |    |

| 3.3.5 Common-mode Voltage Reduction                                        |    |

| 3.3.6 Simulation Results with High Power Inverter                          |    |

| 3.3.6.1 Steady-state and transient characteristics                         |    |

| 3.3.6.2 P/N/O Voltage Balancing                                            |    |

| 3.3.6.3 Common-mode Voltage Elimination                                    | 53 |

| 3.4 Rectifier – Side Predictive Control with Grid Current Spectrum Shaping | 54 |

| 3.4.1 Mathematical Model of NPC AFE Rectifier                              | 56 |

| 3.4.2 Discrete-time Model of NPC AFE Rectifier                             | 57 |

| 3.4.3 Rectifier Simulation Results                                         | 57 |

| 3.5 Switching Frequency Targeting versus Number of Samples                 | 58 |

| 3.6 Summary                                                                | 60 |

| CHAPTER 4 - DSP IMPLEMENTATION AND EXPERIMENTAL VERIFICATION               |    |

| 4.1 Introduction                                                           | 61 |

| 4.2 Inverter Simulation Results with Low Power                             | 61 |

| 4.3 DSP Implementation                                                     | 65 |

| 4.3.1 Delay Compensation                                                   | 66 |

| 4.4 Experimental Results and Analysis                                      | 67 |

| 4.5 Summary                                                                | 74 |

| CHAPTER 5 - CONCLUSION                                                     | 75 |

| 5.1 Technical Challenges and Work Contributions                            | 75 |

| 5.1.1 Technical Challenges with Model Predictive Control                   | 75 |

| 5.1.2 Work Contributions                                                   | 76 |

| APPENDIX                                                                   | 78 |

| Discretization methods                                                     | 78 |

| Approximate solution using numerical integration                           |    |

|     | Exact solution                                                       | . 80 |

|-----|----------------------------------------------------------------------|------|

|     | Reference following                                                  | .81  |

|     | Delay compensation                                                   | .81  |

|     | Calculation of future reference using Lagrange extrapolation         | . 82 |

|     | Calculation of future references using vector angel compensation     | .83  |

|     | Weighting Factors Adjustment for cost functions with secondary terms | . 84 |

| REF | FERENCES                                                             | .86  |

# List of Figures

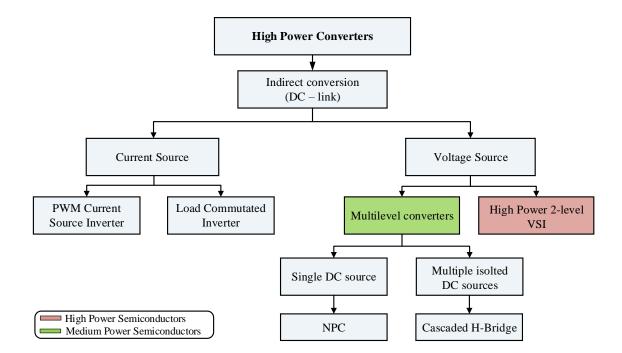

| Figure 1 - High power converter classification                                               | 3  |

|----------------------------------------------------------------------------------------------|----|

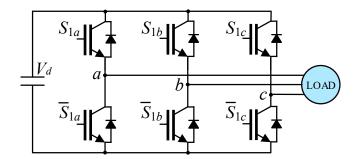

| Figure 2 - Two-level voltage source converter                                                | 5  |

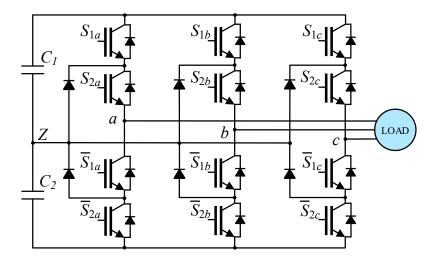

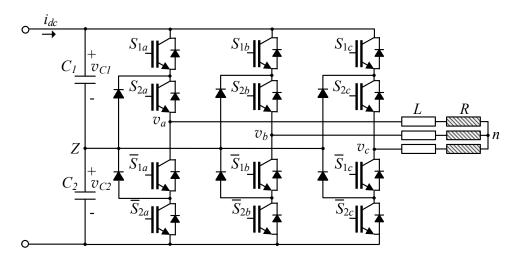

| Figure 3 - Three-level neutral-point clamped voltage source converter                        | 6  |

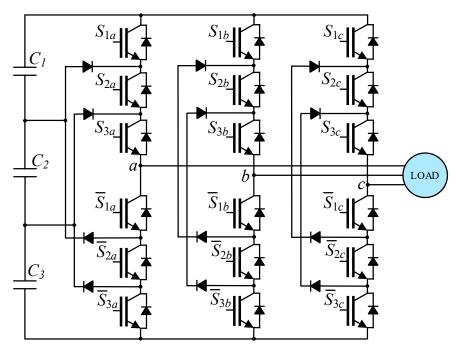

| Figure 4 - Four-level voltage source converter                                               | 7  |

| Figure 5 - NPC AFE rectifier                                                                 | 9  |

| Figure 6 - Pulse width modulator for a three-phase inverter                                  | 10 |

| Figure 7 - Principles of space vector modulation                                             | 12 |

| Figure 8 - Classical control scheme using SVM                                                | 12 |

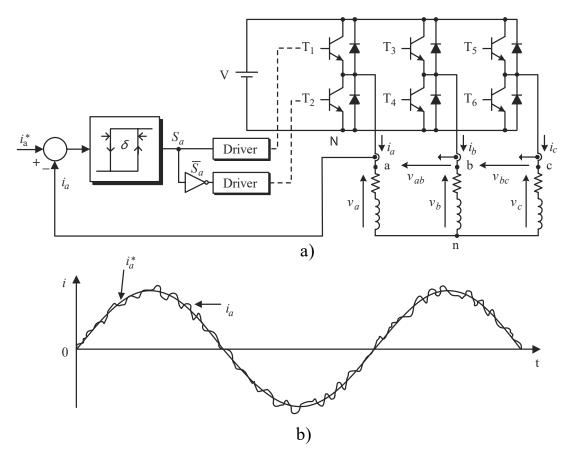

| Figure 9 - Hysteresis current control for a three-phase inverter                             | 13 |

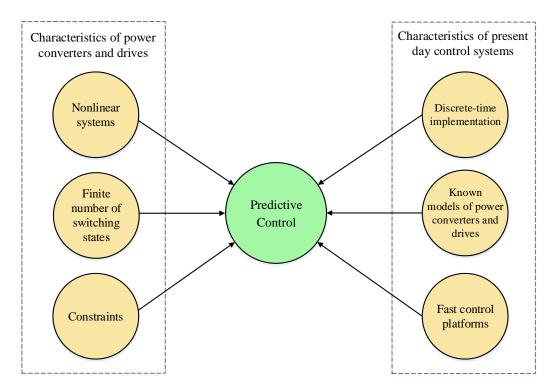

| Figure 10 - Characteristics of predictive control                                            | 18 |

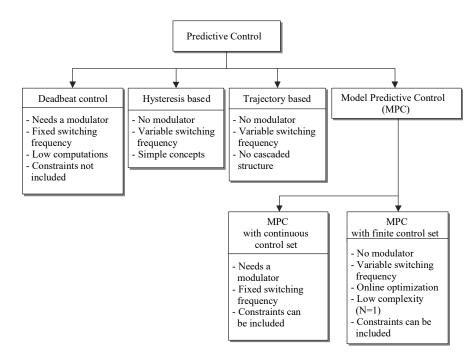

| Figure 11 - Classification of predictive control                                             | 19 |

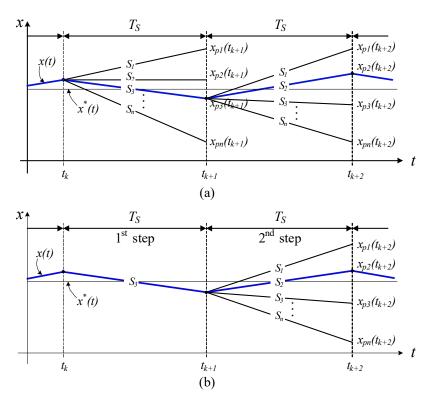

| Figure 12 - FCS-MPC operating principle: (a) ideal theoretical case (b) implementation case  | 23 |

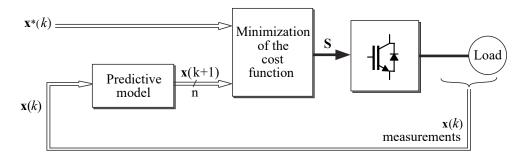

| Figure 13 - FSC-MPC generic control diagram                                                  | 24 |

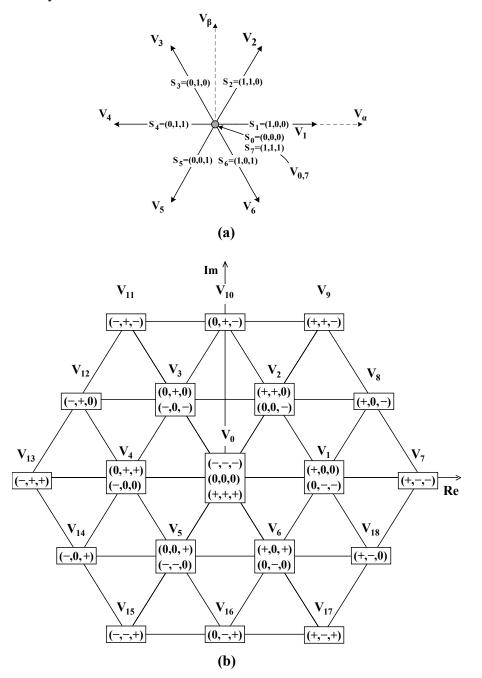

| Figure 14 - Voltage vectors generated by a) two level converter, b) three-level converter    | 26 |

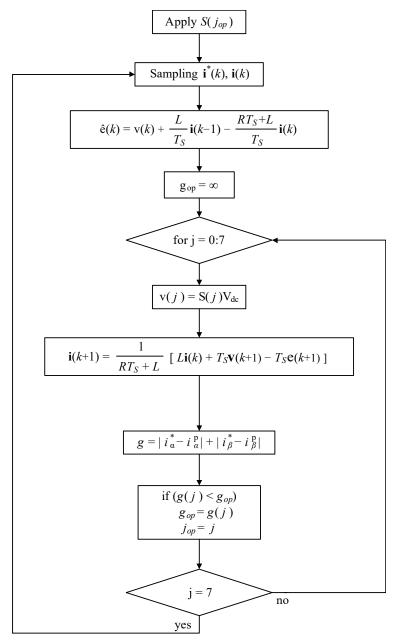

| Figure 15 - Flow diagram of implemented control algorithm                                    | 28 |

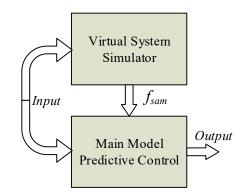

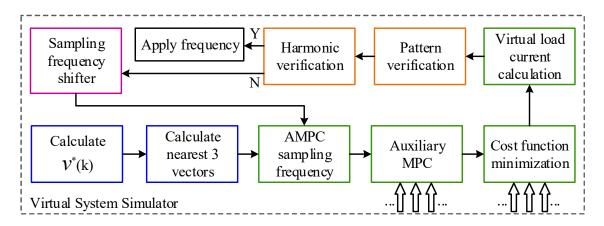

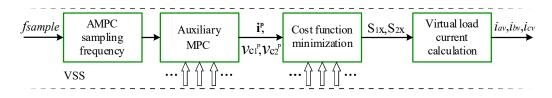

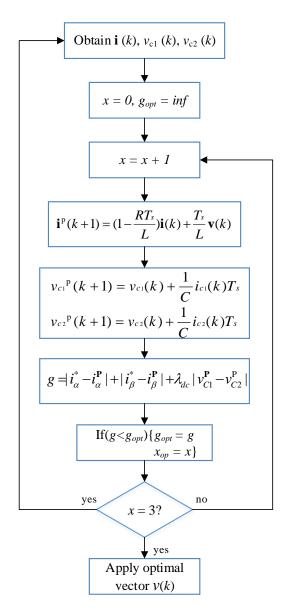

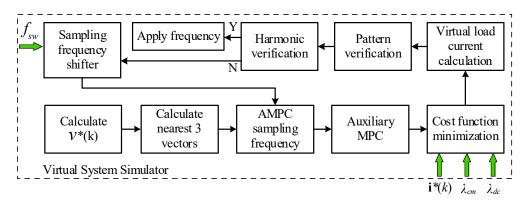

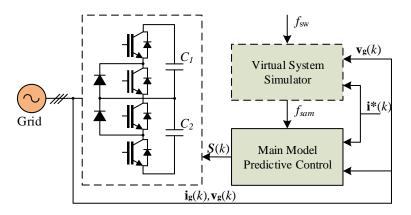

| Figure 16 - General concept of MPC with VSS                                                  | 33 |

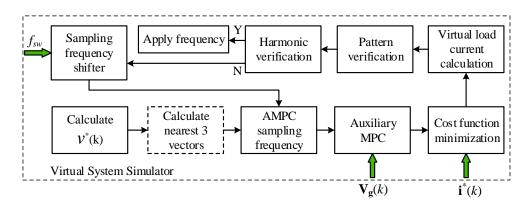

| Figure 17 - Model of Virtual System Simulator                                                | 33 |

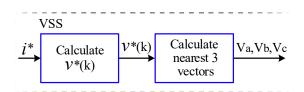

| Figure 18 - VSS module for reference calculation and nearest vector selection                | 34 |

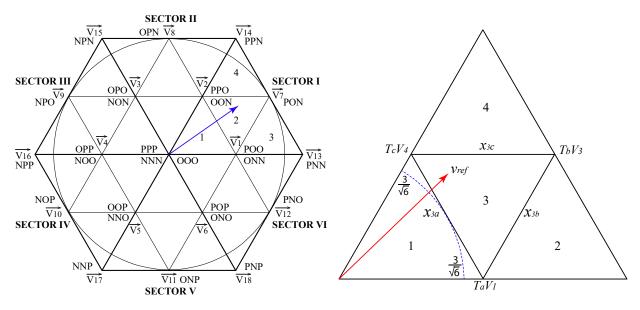

| Figure 19 - Two-level SVM: a) Division of sectors and regions, b) Regions 1 to 4 in Sector I | 35 |

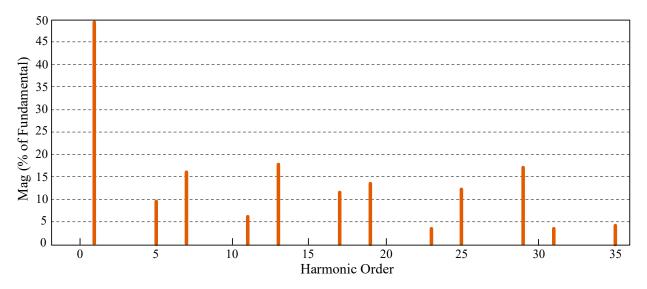

| Figure 20 - General current spectrum with SVM                                                | 36 |

| Figure 21 - VSS module for virtual load current generation                                   | 37 |

| Figure 22 - Auxiliary MPC flow diagram for the NPC inverter                                  |    |

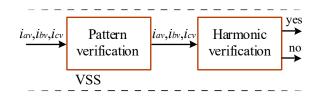

| Figure 23 - VSS module for virtual load current verification                                 | 40 |

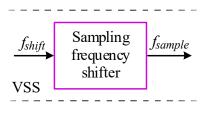

| Figure 24 - VSS module for sampling frequency control                                        | 40 |

| Figure 25 - P/N/O state sorting                                                              | 42 |

| Figure 26 - P/N/O states arranged by the cost function                                       | 42 |

| Figure 27 - P/N/O states arranged using an external algorithm                                | 43 |

| Figure 28 - Inverter side control, VSS with MPC                                              | 44 |

| Figure 29 - Internal VSS structure for inverter                                              | 44 |

| Figure 30 - NPC inverter circuit                                                             | 46 |

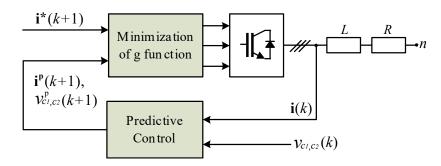

| Figure 31 - Predictive current control method for the NPC inverter                           | 47 |

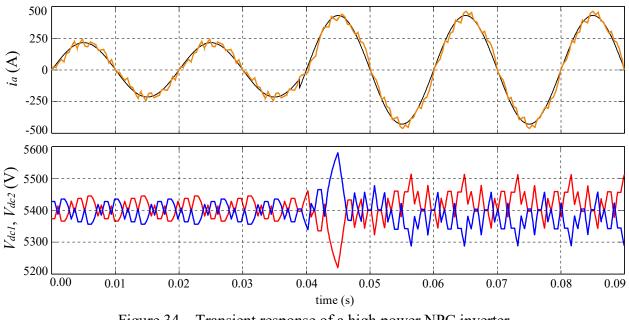

| Figure 34 - Transient response of a high power NPC inverter                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------|

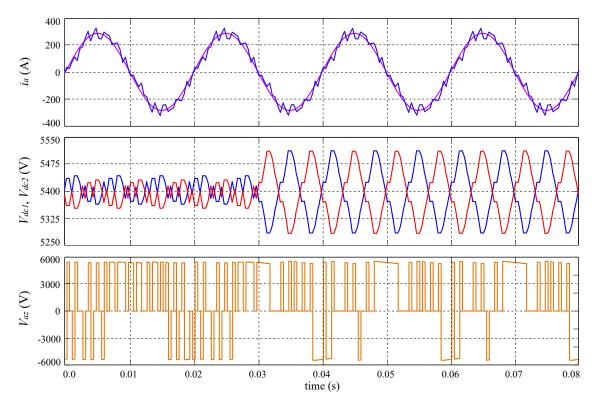

| Figure 35 - DC-link voltage balancing by switching from auto $\lambda dc$ balancing to P/N/O                                |

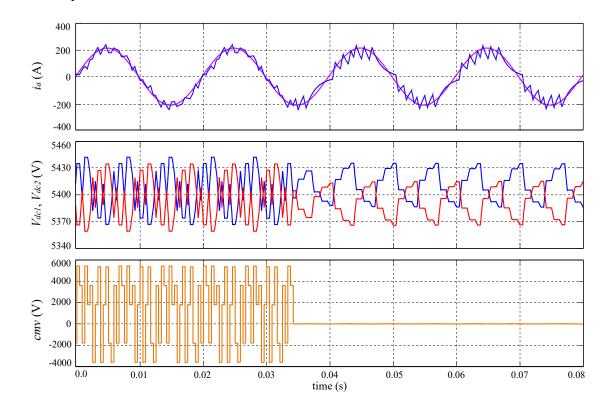

| Figure 36 - Common-mode voltage elimination through cost function minimization                                              |

| Figure 37 - Rectifier side control, VSS with MPC55                                                                          |

| Figure 38 - Internal VSS structure for rectifier55                                                                          |

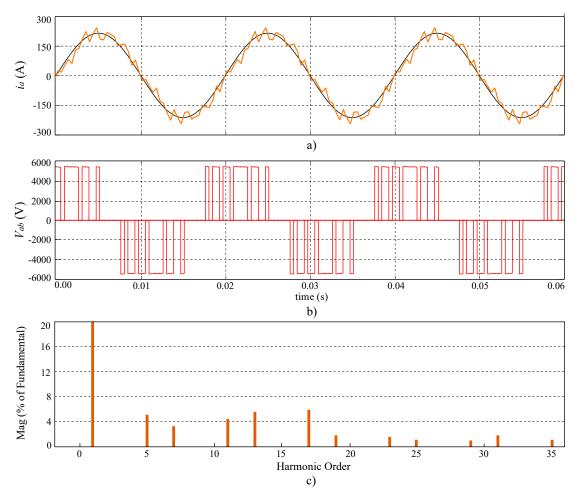

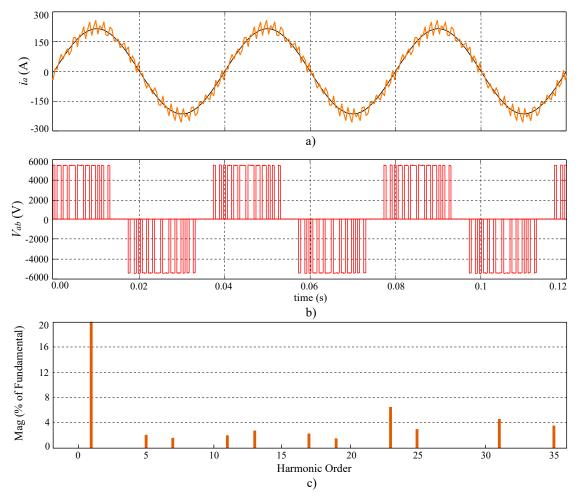

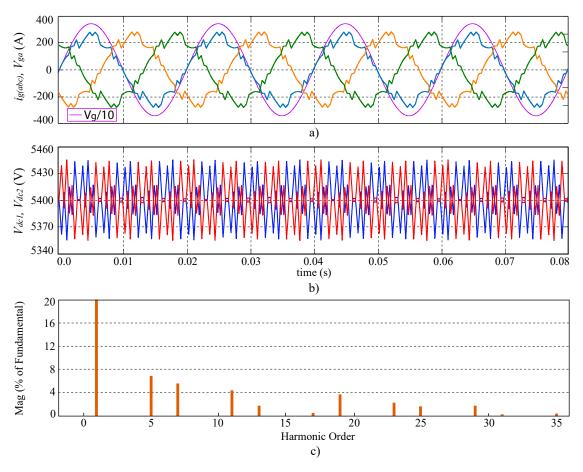

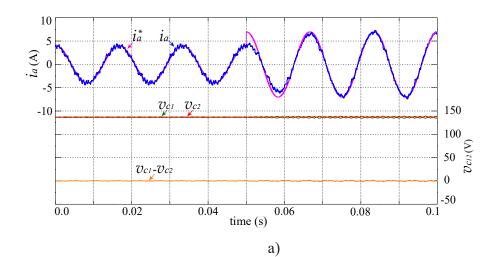

| Figure 39 - Rectifier operation: a) grid currents, b) DC-link capacitor voltages, c) harmonic spectrum 58                   |

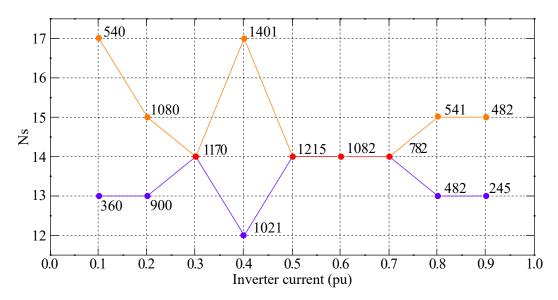

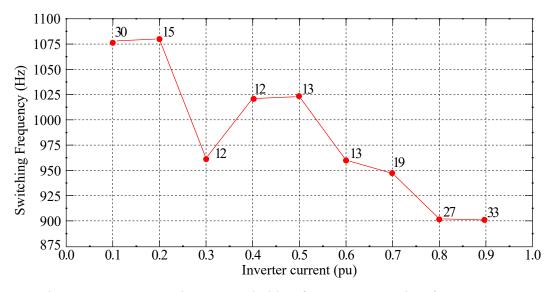

| Figure 40 - $N_s$ versus inverter switching frequency targeting $N_s = 14$                                                  |

| Figure 41 - $N_s$ versus inverter switching frequency targeting $f_{sw} = 1000$ Hz                                          |

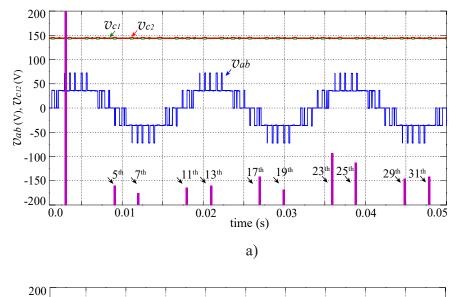

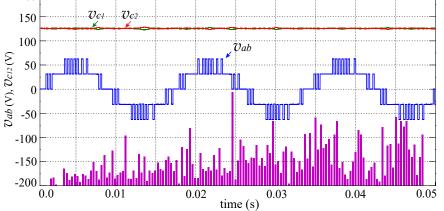

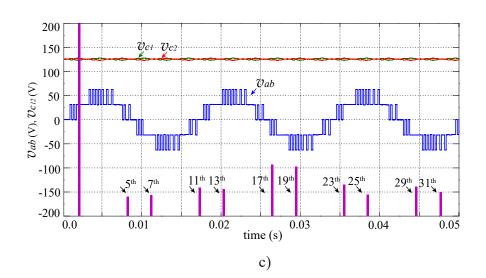

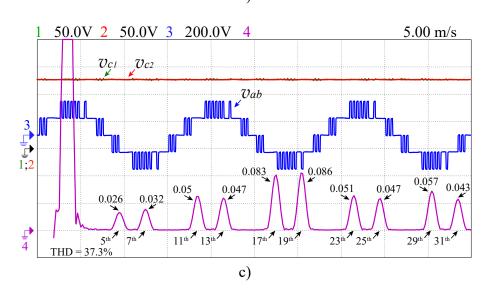

| Figure 42 - Steady-state comparison of line-to-line voltages: a) SVM; b) FSF-MPC; c) VSF-MPC62                              |

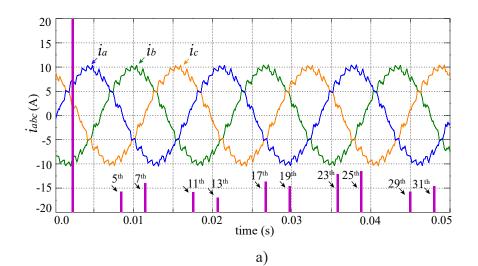

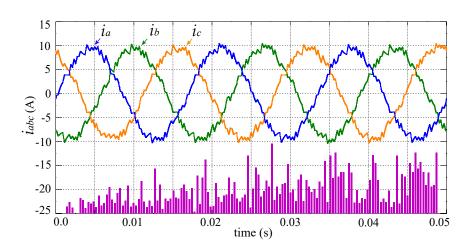

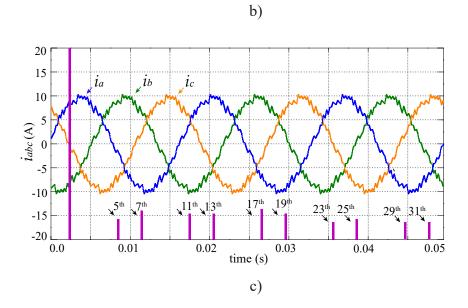

| Figure 43 - Steady-state comparison of 3-phase currents: a) SVM; b) FSF-MPC; c) VSF-MPC63                                   |

| Figure 44 - Transient response comparison: a) SVM; b) FSF-MPC; c) VSF-MPC64                                                 |

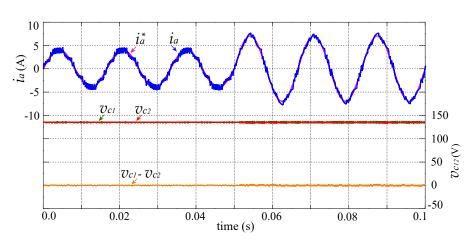

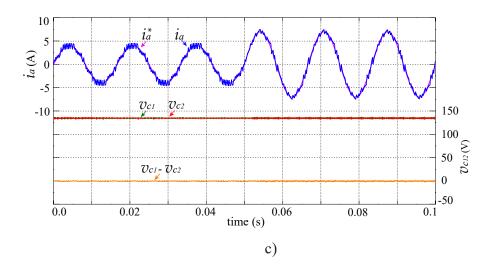

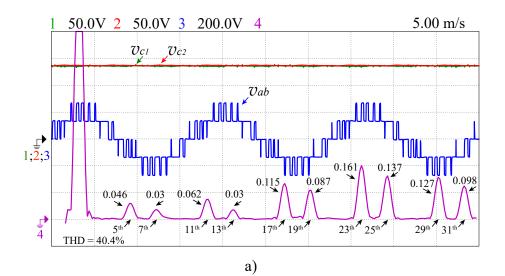

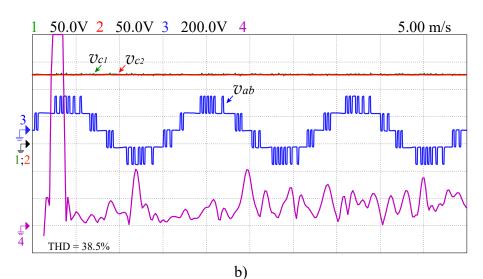

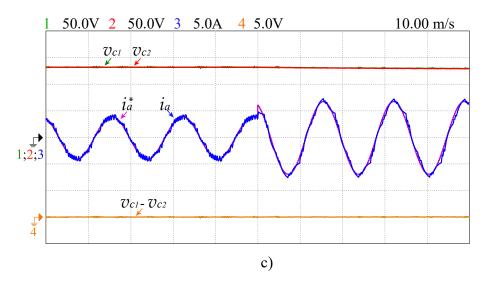

| Figure 45 - Steady-state comparison of line-to-line voltages: a) SVM; b) FSF-MPC; c) VSF-MPC68                              |

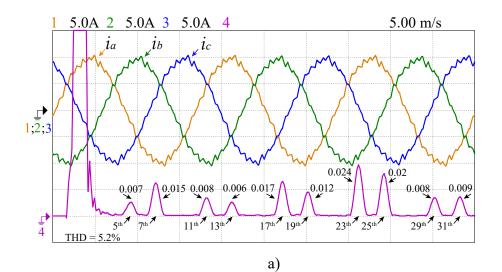

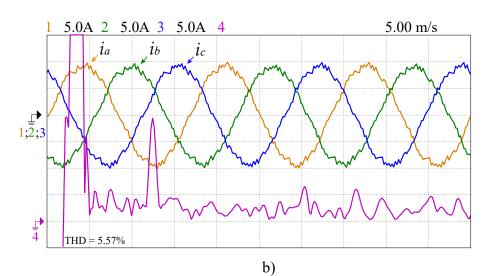

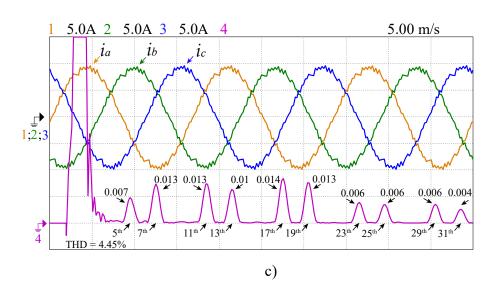

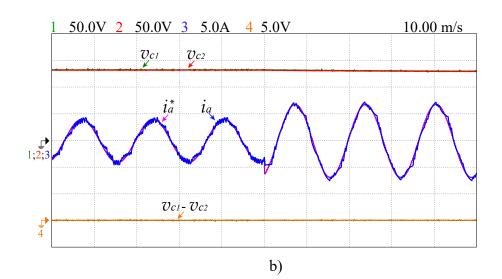

| Figure 46 - Steady-state comparison of 3-phase currents: a) SVM; b) FSF-MPC; c) VSF-MPC69                                   |

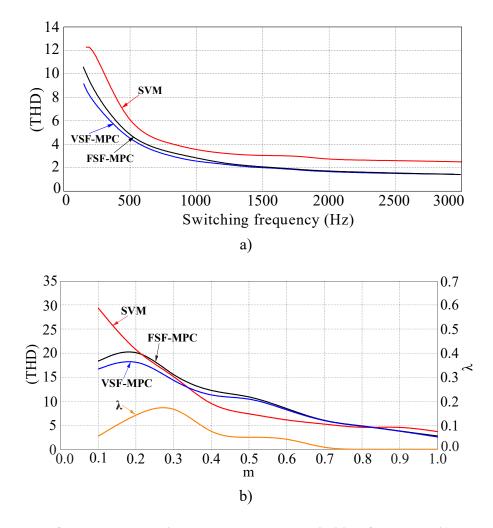

| Figure 47 - Performance comparison: a) THD versus switch. freq.; b) THD versus modulation index71                           |

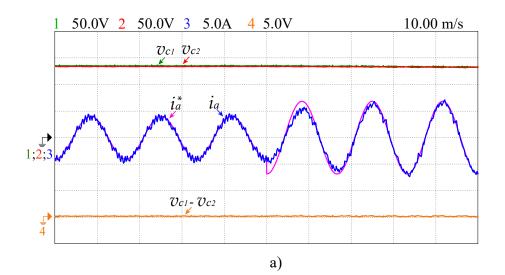

| Figure 48 - Transient response comparison: a) SVM; b) FSF-MPC; c) VSF-MPC73                                                 |

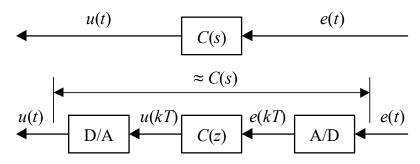

| Figure 49 - Approximating Continuous-Time Controller78                                                                      |

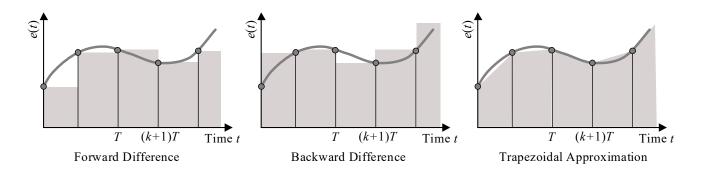

| Figure 50 - Different Types of Integral Approximations79                                                                    |

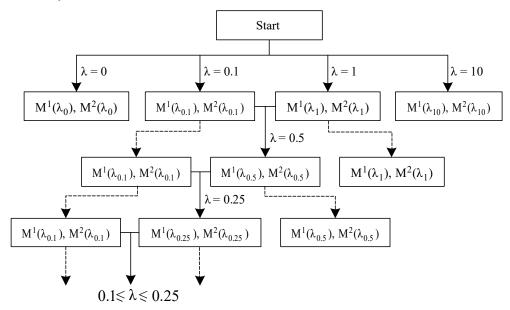

| Figure 51 - Branch and bound algorithm to reduce the number of simulations required to obtain<br>suitable weighting factors |

# **1.1 Introduction**

The field of high-power converters has been one of the most active areas in research and development of power electronics in the last few decades. Several industrial processes have increased their power-level needs, driven mainly by economies of scale (production levels and efficiency), triggering the development of new power semiconductors, converter topologies, and control methods. The development of high-power converters started in the mid- 1980s when 4500-V gate-turn-off (GTO) thyristors became commercially available. The GTO was the standard for high power applications until the advent of insulated-gate bipolar transistors (IGBTs) and gate-commutated thyristors (GCTs) in the late 1990s [1], [2]. These switching devices are now extensively used in high-power converters and drives due to their superior switching characteristics, reduced power losses, ease of gate control, and snubberless operation. High-power converters have found widespread applications in industry. They can be used for pipeline pumps in the petrochemical industry or water pumping stations, fans in the cement industry, grid integration of renewable-energy sources, reactive-power compensation, and other applications.

The most important requirements for these converters are: high efficiency, overload capability, high reliability and operation in harsh environments. The converters can be generally classified into a few significant families: Cycloconverters (CCV), Current Source Converters (CSC) and Voltage Source Converters (VSC). All of these families have shown important advances in design, performance and control strategies. The VSI converts the DC voltage to a three-phase AC voltage with adjustable magnitude and frequency whereas the CSC converts the DC current to an adjustable three-phase AC current. Mostly used topologies in the industry include three-phase VSI topologies, consisting of a conventional two-level converter, a three-level and four-level neutral-point clamped converter, a seven-level cascaded H-bridge converter and a four-level flying-capacitor converter [3-11]. Either IGBT or GCT can operate in these converters as a switching device.

The control of power converters is one of the most elaborate fields in power electronics due to its pivotal importance for proper operation of converters. Properly designed control mechanisms may increase reliability, efficiency and the overall robustness of an entire system. More often, various issues in the operation of power converters can be solved through judicious control optimization rather than using more complex and expensive hardware solutions. The control of power converters is a topic undergoing intense study and is constantly evolving according to technological developments in power quality standards, control requirements, grid code requirements, semiconductor devices, control platforms, etc.

During the 1960s, analog control platforms based on operational amplifiers and passive components were developed to control the firing angles of thyristors in order for an output voltage to be controlled [12]. A few years later, fully controllable device named IGBT has been developed [3], improving power converters and requesting more complex control systems. The converters in the past used analog control circuits, where a single-phase pulse width modulator or hysteresis controller generates the gating signals. Analog control platforms present several drawbacks such as a large number of components, reduced system reliability and poor computational capability to name a few [13]. To achieve high performance operation, digital control techniques were developed during the 1970s which involved powerful calculations, complex strategies and mathintensive algorithms. Introduction of digital signal processors (DSPs) has created the basis for the implementation of digital control techniques. The digital control platforms evolved rapidly and revolutionized the industrial control area by allowing the user to develop sophisticated control algorithms. A few examples of modern real-time (RT) digital control platforms include: microcontrollers, DSP, and field programmable gate array (FPGA). These platforms have been used widely in the control of various power electronic converters and they feature low cost, more reliability and high computational power [13-19].

Highly exploited and very well studied control techniques include the hysteresis and linear controllers. Over the years they have become widely accepted by the power electronics industry. More recent and advanced control techniques include sliding-mode, intelligent and predictive control techniques. The predictive control uses the system model to predict the future responses of a plant. These predictions are then used to generate the optimal control action. This control philosophy emerged during the 1970s for the process control which are normally very slow in nature. The application of predictive control in power electronics is a rather recent topic due to the

fast processing time required to control the electric variables. With the evolution in DSPs, a wide range of predictive controllers have been developed which includes deadbeat and hysteresis-based predictive control, trajectory-based predictive control, and model-based predictive control.

# **1.2 Converter Topologies**

The design of power converters is faced with a number of challenges that relate to topologies and control as well as power semiconductor switching devices. One of the major requirements is to produce high quality waveforms and this is particularly important in a grid connected operation to reduce the device switching impact. In inverters and rectifiers, the waveforms are affected by the following factors: 1) the topology used; 2) the application; 3) the control algorithm; 4) the size of the filter; and 5) the choice of switching frequency [3, 20, 21]. Based on a method of achieving variable output in terms of magnitude and frequency the high-power converters can be classified into two main categories: direct AC–AC converters and indirect AC-DC-AC converters. The latter group introduces a link between two converters which can be of voltage or current nature. Both groups with their representatives have certain advantages and disadvantages, which should be taken into account when selecting the topology for a given application. The general classification of high power converters is provided in Figure 1.

Figure 1 - High power converter classification

At low voltage, a single topology that still dominates the market is the voltage-source twolevel converter. However, at medium and high voltages the situation is completely different. Multilevel converter technology started with the introduction of the multilevel stepped waveform concept with a series-connected H-bridge, which is also known as cascaded H-Bridge converter, in the late 1960s [22]. This was closely followed by low-power development of an FC topology the same year [23]. Finally, in the late 1970s, the diode-clamped converter (DCC) [24] was first introduced. The DCC concept evolved into the three-level NPC (3L-NPC) converter we know today as it was proposed in [8, 25] and can be considered as the first real multilevel power converter for medium-voltage applications.

Multi-level converters provide a wide range of advantages over two-level topology such as better waveform quality, lower *dv/dt* operation, reduced switch stress levels and many more. They are finding increased attention in industry and academia as one of the preferred choices of electronic power conversion for high-power applications. They have successfully made their way into the industry and therefore can be considered a mature and proven technology. Although it is an enabling and already proven technology, multilevel converters present a great deal of challenges, and even more importantly, they offer such a wide range of possibilities that their research and development is still growing in depth and width. Researchers all over the world are contributing to further improve energy efficiency, reliability, power density, simplicity, and cost of multilevel converters, and broaden their application field as they become more attractive and competitive than classic topologies.

#### 1.2.1 Two-Level Voltage Source Converter

The primary function of a voltage source converter is to convert a fixed DC voltage to a three-phase AC voltage with variable magnitude and frequency. The two-level VSI is the main building block for AC-DC and AC-DC-AC converter systems for low- and medium-power applications. The two-level topology presented in Figure 2 is one of the most commonly used topologies in the industry.

The converter is composed of an array of six switching devices, typically IGBTs and a capacitor as a DC-link. The presence of these active switches along with a proper control scheme, allows the generation of sinusoidal currents at the input side, a fully adjustable power factor and a bidirectional power flow. Both carrier based pulse-width modulation (PWM) and space vector

modulation can be applied to generate the switching patterns for the 2L-VSC [3]. In addition, variable switching frequency methods as table or prediction based methods can also be used [12].

Figure 2 – Two-level voltage source converter

As its name suggests this converter generates a binary pulse train, alternating between 0 and  $V_d$ , while the line-to-line voltage presents a three-level waveform. This impacts the total harmonic distortion (THD) of the input current, as larger active/passive filters or higher switching frequencies are needed in order to meet the limits imposed by the grid code. Even though the main features of this converter are its simplicity, modularity and low number of power components, they suffer from unwanted traits such as high dv/dt, static and dynamic voltage sharing and common-mode voltage (CMV). Some of these problems are solved with the invention of multilevel topologies. However, these topologies require a higher number of power devices, which increases the complexity of the design.

#### **Multilevel Voltage Source Converters**

Another option for a VSI system to accommodate the voltage requirements of a high-power application is to utilize a multilevel voltage synthesis strategy. Conceptually, the multilevel VSC configurations can be divided into:

- Diode-clamped multilevel VSC,

- H-bridge-based multilevel VSC,

- Capacitor-clamped multilevel VSC.

#### 1.2.2 Three-Level NPC VSC

These types of converters employing clamping diodes and cascaded DC capacitors to produce AC voltage waveforms with multiple levels can be generally configured as a three-, four-,

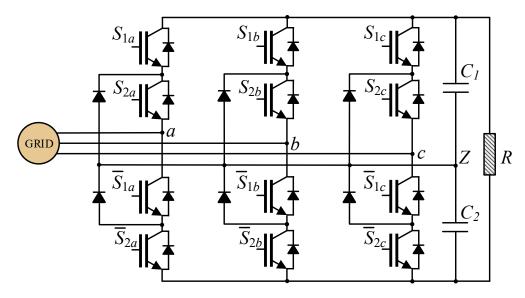

or five-level topology, but only the three-level converter, often known as the neutral-point clamped converter has found a wide application in high-power medium-voltage drives [7,8]. The schematic of the NPC converter is presented in Figure 3.

Compared to a two-level converter with a direct series connection of devices the NPC VSC features two additional diodes per phase leg. These diodes link the midpoint of the "indirect series connection" of the main switches to the neutral point of the converter. This allows the connection of the phase output to the converter neutral point and enables the three-level characteristic of the topology. There are 27 switch states, whereas the two-level converter allows eight switch states not comprising a "0" state. Hence, the clearly superior output voltage quality is the most distinct advantage over the two-level converter. The three-level converter compared to a two-level VSC of the same rating can achieve reduced dv/dt and THD in its AC output voltages, lower switching losses, reduced switch stress levels and it does not have dynamic voltage sharing problem.

Figure 3 - Three-level neutral-point clamped voltage source converter

One main technical requirement for proper operation of the NPC converter is to maintain the voltages of its DC-bus capacitors at their prescribed (usually equal) levels and to prevent voltage drifts during the steady-state and dynamic regimes. Conceptually, there are two approaches to deal with the DC capacitor voltage drift phenomenon. The first approach is to utilize an auxiliary power circuitry. The auxiliary circuitry can be a set of independent power supplies for capacitors, or it can be a dedicated electronic converter that injects current into the capacitors and regulates their voltages. The approach is, however, not appealing for power systems applications due to its cost and complexity. The second approach to equalize the voltages of the DC-side capacitors of a NPC

converter is to enhance the converter control strategy and, to modify the switching patterns of the switches such that the capacitor voltages are regulated at their corresponding desired values. Another drawback of this topology is an increased number of components and complicated PWM switching pattern.

#### **1.2.3 Four-Level Diode Clamped VSC**

Four-Level NPC converter is an extension of the three-level NPC converter which means it carries similar features. The number of components is increased to 6 switches and 6 diodes per leg. The clamping diodes withstand different reverse voltages and thus a series connection of two diodes is necessary.

Figure 4 – Four-level voltage source converter

The DC-link voltage is divided between 3 capacitors connected in series forming two neutral point voltages that need to be balanced. The balancing techniques are similar to those used with the 3-level converter. The converter is presented in Figure 4. In the topology, only three switches conduct at any time and the switch pairs  $(S_{1X}, \overline{S_{1X}}), (S_{1X}, \overline{S_{1X}})$  operate in a complementary manner. A total of 37 voltage vectors with 64 switching combinations are available for the converter. The main advantage of this converter is an increased switching frequency, which leads to a better power

quality or grid code compliance in case of grid connection. The converter can also be operated at higher voltage levels without connecting the switching devices in series.

A brief summary of the number of power components required in most common multilevel topologies versus the 2-level VSC is presented in Table I.

|                                               | 2L-VSC     | 3L-NPC VSC  | 3L-FLC VSC  | 4L-FLC VSC  | 5L-CHB VSC  |

|-----------------------------------------------|------------|-------------|-------------|-------------|-------------|

| Number of IGBTs                               | 6 x 6.5 kV | 12 x 3.3 kV | 12 x 3.3 kV | 18 x 2.5 kV | 24 x 1.7 kV |

| Number of diodes                              | 6          | 18          | 12          | 18          | 24          |

| Number of flying capacitors                   | -          | -           | 3           | 6           | -           |

| Number of LC filter<br>capacitors / inductors | -          | 3/3         | 3/3         | 3/3         | 3/3         |

| Total component count                         | 23         | 36          | 33          | 48          | 54          |

Table I – Comparison of required power components

#### **1.2.4 AFE NPC Rectifier**

Rectifiers are by far the most widely used converters in power electronics. The transformation from alternating current to direct current performed by rectifiers is used in a large variety of applications (from small power up to several megawatts). There are three distinct types of rectifiers, the first of which is the diode rectifier. The main advantages of the diode rectifier are its simplicity and extremely low cost.

The disadvantages and limitations of the three-phase diode rectifier are that:

- it does not offer the possibility to control the power flow,

- it generates high harmonics at the input current, especially when it supplies a capacitive load,

- it does not allow regeneration of power.

The second topology of importance is the thyristor rectifier which introduces the possibility of control of power flow by changing the angle of the gate pulses  $\alpha$  for the thyristors. Through angle  $\alpha$  control, it is possible to change the mean value of the load voltage, regulating the control of power delivered to the load. Thyristor rectifiers have in general the same advantages and limitations as the diode rectifiers. An additional negative feature is that an increase in the value of  $\alpha$  increases the phase

displacement of the input current with respect to the source AC voltage, increasing the amount of fundamental reactive power. An advantage of thyristor rectifiers is that, in operating with  $\alpha > 90$ , they can regenerate power from the DC load to the power supply.

Figure 5 - NPC AFE rectifier

The third important rectifier topology includes power transistors with antiparallel diodes as the main power switches. This rectifier operates with high switching frequency and is also known as an active front-end (AFE) rectifier. A three-level NPC AFE rectifier is presented in Figure 5. It carries all the same features as the NPC converter, as it shares the 3-level topology, except for the power flow which is inverse. The AFE rectifier overcomes all the problems and limitations of the diode and thyristor rectifiers. Its main features are:

- 1. Controlled DC voltage.

- 2. Controlled input currents with sinusoidal waveform (reduced harmonics).

- 3. Operation with high power factor.

- 4. Full regenerative operation.

## **1.3 Current Control Methods for the Converters**

One of the most studied topics in power converters control is a current control, for which there are two classical control methods that have been extensively studied over the last few decades: namely, linear control using pulse width modulation and hysteresis control [21, 26, 27].

#### 1.3.1 Linear Control with PWM or SVM

Considering a modulator stage for the generation of control signals for the power switches of the converter allows one to linearize the nonlinear converter. In this way, any linear controller can be used. The most common choice being used is the proportional–integral (PI) controller.

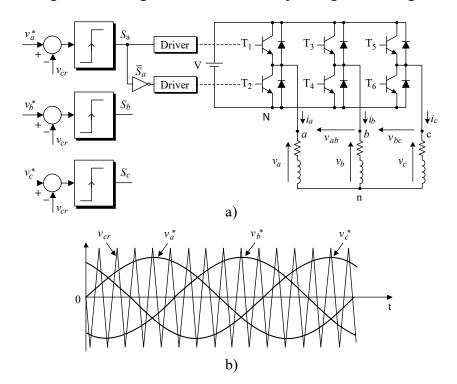

#### 1.3.1.1 Pulse Width Modulation

In a pulse width modulator, the reference voltage is compared to a triangular carrier signal and the output of the comparator is used to drive the inverter switches. A sinusoidal reference voltage is compared to the triangular carrier signal generating a pulsed voltage waveform at the output of the inverter. The fundamental component of this voltage is proportional to the reference voltage. In a three-phase inverter, the reference voltage of each phase is compared to the triangular waveform, generating the switching states for each corresponding inverter leg, as in Figure 6.

Figure 6 – Pulse width modulator for a three-phase inverter

#### **1.3.1.2 Linear Control with Space Vector Modulation**

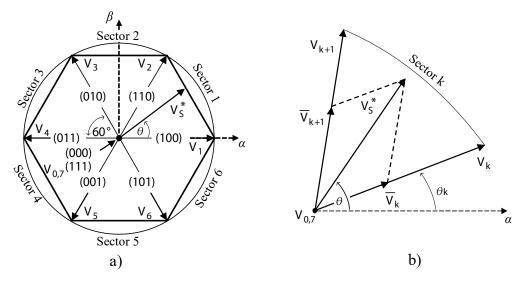

A variation of PWM is called space vector modulation, in which the application times of the voltage vectors of the converter are calculated from the reference vector. It is based on the vector representation of the three-phase voltages, defined as

$$\mathbf{v} = \frac{2}{3}(v_{aN} + \mathbf{a}v_{bN} + \mathbf{a}^2 v_{cN}) \tag{1}$$

where  $v_{aN}$ ,  $v_{bN}$  and  $v_{cN}$  are the phase-to-neutral voltages of the inverter and  $\mathbf{a} = e^{j2\pi/3}$ . The output voltages of the inverter depend on the switching state of each phase and the DC-link voltage,  $v_{xN} = S_x V_{dc}$ , with  $x = \{a, b, c\}$ . Then, taking into account the combinations of the switching states of each phase, the three-phase inverter generates the voltage vectors listed in Table II.

| $\frac{14010 \text{ II}}{S_a}$ | $Switching stat}{S_b}$ | S <sub>c</sub> | Voltage vector V                                                     |

|--------------------------------|------------------------|----------------|----------------------------------------------------------------------|

| 0                              | 0                      | 0              | $\mathbf{V}_0 = 0$                                                   |

| 1                              | 0                      | 0              | $\mathbf{V}_1 = \frac{2}{3} V_{dc}$                                  |

| 1                              | 1                      | 0              | $\mathbf{V}_2 = \frac{1}{3}  V_{dc}  + j \frac{\sqrt{3}}{3}  V_{dc}$ |

| 0                              | 1                      | 0              | $\mathbf{V}_{3} = -\frac{1}{3} V_{dc} + j \frac{\sqrt{3}}{3} V_{dc}$ |

| 0                              | 1                      | 1              | $\mathbf{V}_4 = -\frac{2}{3} V_{dc}$                                 |

| 0                              | 0                      | 1              | $\mathbf{V}_{5} = -\frac{1}{3} V_{dc} - j \frac{\sqrt{3}}{3} V_{dc}$ |

| 1                              | 0                      | 1              | $\mathbf{V}_{6} = \frac{1}{3} V_{dc} - j \frac{\sqrt{3}}{3} V_{dc}$  |

| 1                              | 1                      | 1              | $\mathbf{V}_7 = 0$                                                   |

Table II - Switching states and voltage vectors

Considering the voltage vectors generated by the inverter, the  $\alpha - \beta$  plane is divided into six sectors, as shown in Figure 7(a). In this way, a given reference voltage vector  $\mathbf{v}^*$ , located at a generic sector k (Figure 7b), can be synthesized using the adjacent vectors  $\mathbf{V}_k$ ,  $\mathbf{V}_{k+1}$  and  $\mathbf{V}_0$ , applied during  $t_k$ ,  $t_{k+1}$  and  $t_0$ , respectively. This can be summarized with the following equations:

$$\mathbf{v}^* = \frac{1}{T} (\mathbf{V}_k T_k + \mathbf{V}_{k+1} T_{k+1} + \mathbf{V}_0 T_0)$$

(2)

$$T = t_k + t_{k+1} + t_0 \tag{3}$$

where *T* is the carrier period and  $t_k/T$ ,  $t_{k+1}/T$  and  $t_0/T$  are the duty cycles of their respective vectors. Using trigonometric relations the application time for each vector can be calculated, resulting in

$$t_k = \frac{3T|\boldsymbol{v}^*|}{2V_{dc}} (\cos(\theta - \theta_k) - \frac{\sin(\theta - \theta_k)}{\sqrt{3}})$$

(4)

$$t_{k+1} = \frac{3T|v^*|}{V_{dc}} \frac{\sin(\theta - \theta_k)}{\sqrt{3}}$$

(5)

$$t_0 = T - t_k - t_{k+1} \tag{6}$$

where  $\theta$  is the angle of the reference vector  $\mathbf{v}^*$  and  $\theta_k$  is the angle of vector  $\mathbf{V}_{k}$ .

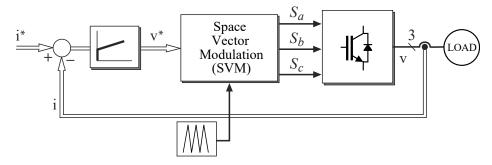

A classical current control scheme using SVM is shown in Figure 8. Here, the error between the reference and the measured load current is processed by a PI controller to generate the reference load voltages.

Figure 7 – Principles of space vector modulation. (a) Voltage vectors and sector definition, (b) Generation of the reference vector in a generic sector

Figure 8 - Classical control scheme using SVM

With this method, constant switching frequency, fixed by the carrier, is obtained. The performance of this control scheme depends on the design of the controller parameters and on the frequency of the reference current.

Although the PI controller assures zero steady state error for continuous reference, it can present a noticeable error for sinusoidal references. This error increases with the frequency of the reference current and may become unacceptable for certain applications [27]. To overcome the problem of the PI controller with sinusoidal references, the standard solution is to modify the original scheme considering a coordinate transformation to a rotating reference frame in which the reference currents are constant values.

#### **1.3.2 Hysteresis Current Control**

The basic idea of hysteresis current control is to keep the current inside the hysteresis band by changing the switching state of the converter each time the current reaches the boundary. Figure 9(a) shows the hysteresis control scheme for a three-phase inverter.

Figure 9 – Hysteresis current control for a three-phase inverter

Here, the current error is used as the input of the comparator and if the current error is higher than the upper limit  $\delta/2$ , the power switch  $T_1$  is turned on and  $T_2$  is turned off. The opposite switching states are generated if the error is lower than  $-\delta/2$ . It can be observed in Figure 9(b) that with this simple strategy the load current  $i_L$  follows the waveform of the reference current  $i_L^*$  very well, which in this case is sinusoidal. For a three-phase inverter, measured load currents of each phase are compared to the corresponding references using hysteresis comparators. Each comparator determines the switching state of the respective inverter leg ( $S_a$ ,  $S_b$  and  $S_c$ ) such that the load currents are forced to remain within the hysteresis band. Due to the interaction between the phases, the current error is not strictly limited to the value of the hysteresis band.

This method is conceptually simple and the implementation does not require complex circuits or processors. The performance of the hysteresis controller is good, with a fast dynamic response. The switching frequency changes according to variations in the hysteresis width, load parameters, and operating conditions. This is one of the major drawbacks of hysteresis control, since variable switching frequency can cause resonance problems. In addition, the switching losses restrict the application of hysteresis control to lower power levels [27]. Several modifications have been proposed in order to control the switching frequency of the hysteresis controller. When implemented in a digital control platform, a very high sampling frequency is required in order to keep the controlled variables within the hysteresis band all the time.

### **1.4 Control Requirements**

Traditionally, control requirements were mainly associated with the dynamic performance and stability of the system. Currently, industry requires more demanding technical specifications and constraints, and in many cases it is subject to regulations and codes. Many of these requirements enforce operating limits and conditions that cannot be dealt with by the hardware only, but also need to be addressed by the control system. This shift in trend has driven the development of more advanced control methods. The design of an industrial power electronic systems can be seen as an optimization problem where several objectives must be fulfilled at the same time. Among these requirements, constraints, and control challenges, the following are especially important:

- provide the smallest possible error in the controlled variables, with fast dynamics for reference following and disturbance rejection;

- operate the power switches in such a way that switching losses are minimized. This requirement leads to increased efficiency and better utilization of the semiconductor devices;

- power converters are switched systems that inherently generate harmonic content. Usually this harmonic content is measured as THD. Many power converter systems have limitations and restrictions on the harmonic content introduced by the modulation stage. These limits are usually specified in standards that can change from one country to another;

- the electromagnetic compatibility (EMC) of the system must be considered, according to defined standards and regulations;

- in many systems, common-mode voltages must be minimized due to the harmful effects that they can produce. These voltages induce leakage currents that reduce the safety and lifetime of some systems;

- good performance for a wide range of operating conditions. Due to the nonlinear nature of power converters, this is difficult to achieve when the controller has been adjusted for a single operating point of the linearized system model;

- some converter topologies have their own inherent restrictions and constraints such as forbidden switching states, voltage balance issues, power unbalances, mitigation of resonances, and many other specific requirements.

### **1.5 Motivation for the Research**

Considering the trends in control of power converters it can be seen that predictive control is making a significant impact in research field as well as in the market. Among predictive techniques, deadbeat control and MPC stand out due to their good properties. An implementation of MPC for power converters can be difficult due to the large number of calculations. A solution is found in FCS-MPC, which takes into account only the finite number of possible switching states, and can be easily implemented using standard control hardware. The FCS-MPC has so far been successfully implemented on various converters and rectifiers, uninterruptible power supplies, active filters and motor control. Some of the dominant features of FCS-MPC, such as simple and convenient algorithm for digital implementation, absence of linear controllers and the ability to easily include different control objectives make its research potential constantly growing. Despite of this good features, the FCS-MPC has two main drawbacks which make its application in industrial power converters difficult. The FCS-MPC needs a high sampling frequency to achieve high performance and, a large number of calculations required for high-level converters combined with an extended prediction horizon could make implementation impossible. Another significant issue of FCS-MPC is a nonconstant switching frequency producing widespread spectrum frequencies of generated currents and voltages. This fact leads to necessity for large passive filters, increasing the weight, volume and cost of power converters.

This thesis aims to investigate and solve some of the current issues associated with FCS-MPC. Variable sampling frequency model predictive control has been proposed to achieve spectrumshaping for the NPC converter. The proposed control technique simultaneously considers load current control, balancing of DC-link capacitor voltages, mitigation of common-mode voltage, elimination of even-order and inter-harmonics in the load current harmonic spectrum, and fixedswitching frequency operation. The challenges associated with weighting factor design are also addressed. Through simulation and experimental verification on a low-power NPC converter, it has been demonstrated that the proposed method preserves high dynamic performance nature of MPC, and predefined harmonic spectrum characteristic of space vector modulation.

## 1.6 Organization of the Thesis

The thesis is divided into five chapters. Chapter 1 provides a brief introduction to power converter topologies and most established control techniques in industry. This section also provides the motivation for the research in field of model predictive control. Chapter 2 presents detailed analysis of MPC, its operating principles, application and current issues. Chapter 3 is the main body of the thesis which presents a theoretical background with proposed solutions to the addressed issues in MPC presented in Chapter 2. Simulation results are also provided in this chapter. Chapter 4 presents experimental results and analysis along with DSP implementation of variable sampling frequency. Chapter 5 makes an overview of main contributions of this work and provides conclusions.

# **2.1 Introduction**

Considering the increasing demands in performance and efficiency of power converters, the development of new control schemes must take into account the real nature of these kinds of systems. Power converters and especially drives are nonlinear systems of a hybrid nature, including linear and nonlinear parts and a finite number of switching devices. The input signals for power electronic devices are discrete signals that command the turn-on and turn-off transitions of each device. Several constraints and restrictions need to be considered by the control, some of which are inherent to the system, like the maximum output voltage of the converter, while others are imposed for security reasons, like current limitations to protect the converter and its loads.

All the characteristics of power converters, as well as the characteristics of the control platforms, converge in a natural way to the application of model predictive control. The main characteristic of MPC is to use a model of the system to predict future behavior of the controlled variables. The main body of the model predictive control is the cost function. In case of a finite number of switching states, minimization of the cost function through multiple iterations produces the optimal actuation for the switches. MPC may easily consider numerous control objectives, just by inclusion of appropriate terms into the cost function. In such a way, the design of the controller becomes alleviated. Combined with modern digital processors it became prosperous control technique with ever growing potential.

This chapter extends the discussion on control methods to one of newly introduced control strategies in power electronics, model predictive control. Different classes of predictive control algorithms, operating principles, algorithms, block diagrams, advantages and flexibility, as well as challenges are discussed in this chapter. It further provides an example of the design process for current control of two-level converter with necessary discretization steps. Digital implementation as well as defining appropriate prediction horizon are also discussed. Finally, up-to-date challenges in MPC are presented. This chapter builds the foundations for the research which is focused on solving problems in predictive control applied to multi-level VSC.

### **2.2 Predictive Control in Power Electronic**

Nowadays, practically all control strategies are implemented in digital control platforms running at discrete time steps. Design of any control system must take into account the model of the plant for adjusting the controller parameters, which in the case of power converters is well known. Control platforms offer an increasing computational capability thus more calculation-demanding control algorithms are feasible today.

As described before, due to the nature of predictive control, various constraints and objectives could be easily implemented. Along with the known mathematical models of the converters and considering the finite number of switching states, predictive control has stand up as a mighty alternative to classical control methods. The main features converging toward predictive control are summarized in Figure 10, which highlights the characteristics that lead to simple control schemes for the control of power converters and drives.

Figure 10 - Characteristics of predictive control

Predictive control includes a wide class of controllers that have found rather recent application in power converters. It avoids the cascaded structure, which is typically used in a linear control scheme, obtaining fast transient responses. Nonlinearities of a system can be included in the model, thus avoiding the need to linearize the model for a given operating point and improving the operation of the system for all conditions. It is also possible to include restrictions to some variables when designing the controller.

#### 2.2.1 Predictive Control Types

The classification of different predictive control methods is shown in Figure 11. The main feature of predictive control is to use the model of the system in order to predict future values of controlled variables. This information is used by the controller to obtain the optimal actuation, according to a predefined optimization criterion. The optimization criterion in the hysteresis-based predictive control is to keep the controlled variable within the boundaries of a hysteresis area, while in the trajectory based control the variables are forced to follow a predefined trajectory.

Figure 11 – Classification of predictive control

One of the earlier predictive controllers used in power converters, so-called dead-beat control, eliminates the classic linear controller by using a predictive model of the system. This model is used to calculate the required reference voltage in order to reach the desired reference value for a certain variable (usually the current). The predicted reference voltage is later generated by the converter via a modulation stage. This scheme has been applied for current control of inverters [28]–[34], rectifiers [35, 36], active filters [37, 38], and uninterruptible power supplies (UPSs) [39, 40].

Another approach emerged called model predictive control, in which a model of the system is considered in order to predict the future behavior of the variables. MPC is based on a minimization of the cost function which may include different control objectives and constraints. Using discretized equations, it is possible to predict the future value of the controlled variables, obtaining the future control actions.

The difference between these groups of controllers is that deadbeat control and MPC with continuous control set need a modulator, in order to generate the required voltage. This will result in having a fixed switching frequency. The other controllers directly generate the switching signals for the converter, do not need a modulator, and present a variable switching frequency.

MPC has several advantages, such as easy inclusion of nonlinearities and constraints. This scheme has few applications in power converter control due to high amount of calculations needed to solve the optimization problem online, which is incompatible with small sampling times used in converter control. One solution in order to reduce the calculation time is to solve the optimization problem offline, as presented in [41], where MPC is implemented as a search tree and the calculation time is reduced, making it possible to use the MPC in drive control. Another solution is the use of Generalized Predictive Control (GPC) [42], where the optimization is solved analytically, obtaining a linear controller. Nevertheless, with GPC, it is very difficult to include system constraints and nonlinearities.

Another approach to implement MPC for power converters takes advantage of the inherent discrete nature of power converters. Since power converters have a finite number of switching states, the MPC optimization problem can be simplified and reduced to the prediction of the system behavior only for those possible switching states. Then, each prediction is used to evaluate a cost function (also known as quality or decision function), and consequently, the state with minimum cost is selected and generated. This approach is known as a finite control set MPC since possible control actions (switching states) are finite. This method is also known as finite alphabet MPC or simply as predictive control, and it has been successfully applied to a wide range of power converters [12].

#### 2.2.2 Control Requirements and Challenges for Three-Level Converters

Multilevel converters are recognized as among the most suitable and efficient candidates to be used in high-power, medium-voltage industrial applications. They can synthesize near sinusoidal voltages while increasing the number of levels, leading to good power quality and smaller output filters. In addition, higher levels of MV operation can be achieved without connecting the switching devices in series. The most popular and well-known multi-level topologies are flying capacitor, cascaded H-bridge and diode-clamped converters. By using clamping diodes to divide the DC-link voltage among several capacitors, different configurations, ranging from three-level to m-level diode-clamped converters can be obtained.

Multi-level diode-clamped converters are suitable for many industrial applications such as: STATCOM, train traction, ship propulsion, regenerative conveyors, wind and photovoltaic energy systems, and general MV motor drive applications (pumps, fans, etc.) In these applications, current control is one of the most important issues and it has been widely studied in literature.

DC-link capacitor voltage balancing is one of the main issues in diode-clamped converters. Especially when the number of levels increases, the switching actions in three-level converters lead to an imbalance among the DC-link capacitor voltages. Usually, redundant switching states are used for proper balancing. Another important challenge for diode-clamped converters is the operation at low switching frequency in order to minimize the switching losses and to allow proper heat dissipation. This requirement can be accomplished with the PWM and SVM techniques by simply changing the carrier frequency. Unfortunately, low order harmonics are produced by the PWM and SVM techniques when operated below 1 kHz leading to poor output current quality. One more critical issue is that fast switching actions of the semiconductor devices cause high dv/dt in the converter output voltages and this leads to higher common-mode voltage. The common-mode voltage through improvements in PWM/SVM techniques is a cost effective and attractive solution. However, the complexity of the SVM increases with the number of converter levels.

The finite control-set model predictive control takes over the functions of linear regulators and SVM/PWM modulators. To accomplish the aforementioned control requirements, they can be described in a single cost function and the importance of each term can be weighted by using assigned coefficients. This leads to fast and convenient implementation on digital processors.

# 2.3 The Concept of FCS-MPC

The common elements of FSC-MPC are: 1) using a model of the system to predict the future behavior of the variables (until a predefined horizon in time), 2) and selection of optimal actuations

by minimizing a cost function for a finite number of states. This structure has several important advantages:

- ✤ concepts are intuitive and easy to understand;

- ✤ it can be applied to a great variety of systems;

- the multivariable case can be easily considered;

- ✤ dead times can be compensated;

- ✤ easy inclusion of nonlinearities in the model;

- ✤ simple treatment of constraints;

- the resulting controller is easy to implement;

- this methodology is suitable for the inclusion of modifications and extensions depending on specific applications.

However, there are certain disadvantages that are stated below:

- ✤ larger amount of calculations for high-level converters;

- the quality of the model has a direct influence of the quality of the resulting controller;

- ✤ variable switching frequency caused by absence of a modulator.

The quality of the model has a direct influence on the quality of the resulting controller. If parameters of the system change with time, some adaptation or estimation algorithm must be considered.

#### 2.3.1 FSC-MSC Operating Principle

The control problem for power converters can be defined as determining of an appropriate control action S(t) (usually the gate signals of the converter) that will drive a generic system variable x(t) as close as possible to a desired reference value  $x^*(t)$ . Consider the qualitative behavior of x(t) and its regularly sampled value  $x(t_k)$  over a sample period  $T_s$  for a system with a finite number of control actions n, as shown in Figure 12(a), where measurements, computations, and control actions are performed instantly (i.e., ideal case). Since the control actions or control set is finite in number  $S_i$  with  $i = 1, \ldots, n$ , they can be evaluated together with the measured value  $x(t_k)$ , based on a prediction function  $f_p$ , to predict all possible system transitions  $x_{pi}(t_{k+1}) = f_p\{x(t_k), S_i\}$ , for  $i = 1, \ldots, n$ .

This prediction function is directly derived from the discrete model and parameters of the system. To determine which of the control actions is to be selected, a decision or cost function  $f_g$  predictions can be defined, usually dependent on the desired reference value and the prediction  $g_i = f_g\{x^*(t_{k+1}), x_i(t_{k+1})\}$  for i = 1, ..., n. Note that a future reference value is needed  $x^*(t_{k+1})$ , which can be assumed to be equal to the actual value  $x^*(t_k)$ , since  $T_s$  is sufficiently small compared with the dynamic behavior of the system, and thus, the reference can be considered constant over  $T_s$ . If needed for highly dynamic systems, the future reference value  $x^*(t_{k+1})$  can be estimated via appropriate extrapolation methods. A typical example for  $f_g$  would be the absolute error between the predictions and the reference  $g_i = |x^*(t_{k+1}) - x_{pi}(t_{k+1})|$ . The evaluation of the cost function with n predictions leads to n different costs. Naturally, control action leading to the minimum cost (min $\{g_i\}$ , for i = 1, ..., n) is selected to control the system.

Figure 12 – FCS-MPC operating principle: (a) ideal theoretical case (b) implementation case

Based on the example shown in Figure 12(a), the predicted value  $x_{p3}(t_{k+1})$  is the closest to the reference  $x^*(t_{k+1})$ , hence,  $S_3$  is selected and applied at  $t = t_k$ . Following the same criterion,  $S_2$  is selected and applied in  $t = t_{k+1}$ . However, the ideal theoretical case in which the variables can be measured, predicted, and controlled instantly in  $t = t_k$  is not feasible in real-time applications.

Nevertheless, this problem can be overcome if a two-step-ahead prediction is considered, as shown in Figure 12(b), in which the control action to be applied in the following sample time  $S(t_{k+1})$  is determined. This way, a complete sample period  $T_s$  is available to perform the algorithm.

Naturally, the sample period  $T_s$  has to be greater than the measurement, computation, and actuation times added together. Assume that on a sample time  $t_k$ , a measurement  $x(t_k)$  is made and the previously computed control action  $S(t_k)$  is applied. With this information and the system model, a first prediction can be made to obtain the future value  $x(t_{k+1})$  (this is the first step prediction).

Now, from the predicted value  $x_p(t_{k+1})$ , the FCS-MPC algorithm is performed for *n* possible control actions, leading to one optimal selection  $S(t_{k+1})$  (this is second step prediction). Both predictions are performed during the first sample period, and then, at  $t = t_{k+1}$ , the optimal selected control action  $S(t_{k+1})$  is applied, while  $x(t_{k+1})$  is measured to perform the algorithm again. As shown in the example in Figure 12(b), there is only one prediction for the first step, given by the applied control action  $S(t_k) = S_3$  determined in the previous execution of the algorithm, while  $S(t_{k+1}) = S_2$  is selected from *n* predictions for the second step.

Figure 13 – FSC-MPC generic control diagram

A simplified control block diagram for the real-time implementation of FCS-MPC is shown in Figure 13, considering a generic system variable x(t). It is worth mentioning that this control method is not limited to a single variable; on the contrary, multiple variables, system constraints, perturbations, saturations, and, basically, every characteristic that can be mathematically modeled and measured can be included in the predictive model and cost function. This is the basis of a great flexibility and control potential that can be achieved with FCS-MPC. Moreover, the fact that power converters have a reduced and limited number of switching states (or control set) makes this method feasible for implementation with presently available microprocessing resources. Since only a discrete model of the system is necessary, rather than approximated linear models (together with control system design theory and modulation algorithms), a simpler and more direct design and implementation of the controller are achieved.

#### **2.3.2 Controller Design**

In the design stage of FCS-MPC for the control of a power converter, the following steps are identified:

- modeling of the power converter with identifying all possible switching states and its relation to the input or output voltages or currents,

- defining a cost function that represents the desired behavior of the system,

- obtaining discrete-time models for prediction of the future behavior of the variables to be controlled.

When modeling a converter, the basic element is the power switch, which can be an IGBT, a thyristor, a gate turn-off thyristor (GTO), or others. The simplest model of these power switches considers an ideal switch with only two states: on and off. Therefore, the total number of switching states of a power converter is equal to the number of different combinations of two switching states of each switch. However, some combinations are not possible, for example, those combinations that short-circuit the DC-link. As a general rule, the number of possible switching states N is

$$N = x^{\mathcal{Y}} \tag{7}$$

where x is the number of possible states of each leg of the converter, and y is the number of phases (or legs) of the converter. In this way a three-phase, two-level converter has  $N = 2^3 = 8$  possible switching states, a three-phase, three-level converter has  $N = 3^3 = 27$  switching states, and a five-phase, two-level converter has  $N = 2^5 = 32$  switching states. In some multilevel topologies the number of switching states of the converter can be very high, as in a three-phase, nine-level cascaded H-bridge converter, where the number of switching states is more than 16 million.

Another aspect of converter model is the relation between the switching states and the voltage levels, in the case of single-phase converters, or voltage vectors, in the case of three-phase or multiphase converters. For current source converters, the possible switching states are related to current vectors instead of voltage vectors. It can be found that, in several cases, two or more switching states generate the same voltage vector.

For example, in a three-phase, two-level converter, the eight switching states generate seven different voltage vectors, with two switching states generating the zero vector. In a three-phase, three-level converter there is a major redundancy, with 27 switching states generating 19 different voltage vectors. Figure 14 depicts the relation between switching states and voltage vectors for two different converter topologies. In some other topologies, the method of calculating possible switching states may be different.

Figure 14 – Voltage vectors generated by a) two level converter, b) three-level converter

Each application imposes several control requirements on the systems such as: current control, torque control, power control, low switching frequency, etc. These requirements can be expressed as a cost function to be minimized. The most basic cost function measures the error between a reference and a predicted variable, for example, load current error, power error, torque error, etc. However, one of the advantages of the predictive control methods is the possibility to control different types of variables and include restrictions in the cost function. In order to deal with different units and magnitudes of the controlled variables, each term in the cost function is multiplied by a weighting factor that can be used to adjust the importance of each term.

When building a model for prediction, the controlled variables must be considered in order to get discrete-time models that can be used for prediction of these variables. It is also important to define which variables are measured and which ones are not measured, because in some cases variables that are required for the predictive model are not measured and some kind of estimation will be needed. To get a discrete-time model it is necessary to use some discretization methods. For first-order systems it is simple to approximate the derivatives using the Euler forward method, i.e., using

$$\frac{dx}{dt} \approx \frac{x(k+1) - x(k)}{T_s} \tag{8}$$

where  $T_s$  is the sampling time. However, when the order of the system is higher, the discrete-time model obtained using the Euler method is not precise because the error introduced by Euler's method for higher order systems is significant. For these higher order systems, an exact discretization must be used.

#### 2.3.3 Current FCS-MPC of a 2L-VSI

The FCS-MPC current control problem can be easily derived from the generic operating principle analyzed in this section. The variable x(t) would be the current  $i_s$ ; the control action S(t) represents the switching states ( $S_i$ , with i = 0, ..., 7) of the converter. The predictive model corresponds to the discrete time model of the load, with Euler approximation of the current derivative, which leads to

$$i_{sp}\{S_i\} = \frac{Li_s(t_k) + T_s V_i(t_{k+1})}{RT_s + L}$$

(9)

$$V_i(t_{k+1}) = \frac{2}{3} V_{dc}(S_i[1 \ a \ a^2]^T)$$

(10)

where  $\mathbf{i}_s(t_k)$  is the measured current and  $\mathbf{v}_{i}(t_{k+1})$  is the voltage vector generated by the switching states S<sub>i</sub>, with i = 0, ..., 7. Additionally, note that  $\mathbf{i}_{ps} = i_{\alpha p} + ji_{\beta p}$ . Finally, the cost function that needs to be minimized is

$$g_i(t_k) = |i_{\alpha}^* - i_{\alpha p} \{S_i\}| + |i_{\beta}^* - i_{\beta p} \{S_i\}|$$

(11)

The corresponding simplified block diagram of the current FCS-MPC is shown in Figure 15 as a flow diagram.

Figure 15 – Flow diagram of implemented control algorithm

The FCS-MPC does not force a commutation in each sample period. Hence, the average switching frequency is variable, leading to a spread current spectrum. As shown in the flow diagram, this current control is performed in the following steps:

- 1. the value of reference current is obtained and the load current is measured;

- the model of the system is used to predict the value of the load current in the next sampling interval for each voltage vector;

- 3. the quality function *g* evaluates the error between reference and predicted currents in the next sampling interval. The voltage that minimizes the current error is selected and applied to the load.

As shown in the diagram, the minimization of the quality function can be implemented as cyclical prediction for each voltage vector, evaluating the quality function, and storing the minimum value and the index value of the corresponding switching state.

## 2.4 Applications of Model Predictive Control and Challenges

For power conversion systems in the megawatt range, device average switching frequencies over 1 kHz are considered inconvenient. In fact most common switching frequencies are found around 500 Hz for IGBT and IGCT based converters. The use of lower switching frequencies introduces a mayor trade-off between efficiency and high dynamic performance, and has been a challenge in power electronics for decades.

Model predictive control is a powerful control strategy that uses the model of the system to pre-calculate the behavior of the system for a predefined horizon in the future. The standard implementation of predictive current control calculates the voltage required by the load to get the desired current. Then this voltage is applied using pulse width modulation. This scheme has been used for the control of single-phase and three-phase inverters, inverters with output LCL filter, rectifiers and active filters, and uninterruptible power supplies. This concept has also been used for torque control of induction machine. It is also possible to calculate the duty cycles for the converter instead of the voltages. Some works have been presented using this scheme for current control in a three-phase inverter and a matrix converter, flux and torque control of an induction machine [43], and direct power control in an active front end rectifier [44].

It is also possible to include and control different variables using a single cost function. For instance, while the current is controlled, at the same time, the cost function minimizes the switching

frequency and balances the DC-link voltages in a neutral point clamped converter. This approach is easily extended to the drives, where the entire system can be easily modelled including nonlinearities. The fact is that the versatility and universality of MPC approach delivers great potential for a wide range of application and an ever growing research potential.

In all applications the switching states are changed at equidistant time instants. However, lack of modulation stage leads to a variable switching frequency producing spread voltage spectrum over a range of frequencies. This is certainly one of the most significant issues in MPC which reduces its potential for practical implementation. As discussed above, high number of converter voltage levels generates many possible switching states. Due to extensive calculation required, real-time implementation of MPC for high-level converters becomes troublesome. Moreover, weighting factor design faces significant problems as an optimized procedure has not been presented up-to-date. The work in Chapter 3 presents solutions to some of the problems stated.

### 2.5 Summary

In this chapter state-of-the-art converter control techniques are reviewed followed by the discussion of various classes of predictive control techniques. The operating principle of FCS-MPC is discussed for ideal and implementation cases. The implementation of current control strategy has been discussed for 2-level converter through a flow diagram. Furthermore, the applications of model predictive control and technical challenges are also presented.

The strategy introduced in this chapter leverages the discrete nature of power converters and microprocessors. The predictive control has proven to be effective with a good dynamic response and compares well with the classical methods. The use of linear and nonlinear controllers is avoided. In addition, it is not necessary to include any type of modulator. The high calculation power of today's existing DSPs makes this method attractive to control power converters. Even though the method might be simple in case of 2-level converter, the control algorithm might become difficult to implement for some multilevel converters due to the extensive number of calculations.

The results and analysis show that predictive control is a strong tool with a conceptually different approach that opens up new possibilities for power converters control, especially in the field of multi-level converter based systems.

# CHAPTER 3 VARIABLE SAMPLING FREQUECNY MODEL PREDICTIVE CONTROL

### **3.1 Introduction**

As discussed in a previous chapter, various control strategies can be used to control rectifiers and inverters. One of the newest control methods with numerous advantages over classical control is certainly model predictive control. As many of control objectives could be simultaneously considered and easily implemented without the need for a cascaded control, MPC becomes promising solution to control the converters in the future.

Spread spectrum and variable switching frequency is a well-known problem with model predictive control that still has not been fully solved. The work in [45] proposes preliminary study on using a discrete Fourier transform (DFT) in the cost function to solve this issue. The authors in [46] presented a frequency weighted cost function to shape the harmonic spectrum. The addition of secondary control objectives to cost function reduces the relative importance of primary control objective, i.e., load current control. As a result, the quality (total harmonic distortion) of the load current deteriorates. The variable switching frequency nature with these two works is still unanswered. In [47] the authors incorporate duty-cycle calculation into cost function which determines the time each vector will be applied for. This method is able to concentrate the spectrum around certain frequency. However, the authors use a very high inverter switching frequency. It is not clear how the method performs if the switching frequency was lower. Furthermore, the experimental results are not provided to support theoretical analysis. The work in [48] proposes selective harmonic elimination for predictive control. This concept fixes the switching frequency but only mitigates certain harmonics in the spectrum. The current waveform is not half-wave symmetrical and some low-order triplen harmonics are still present.

This work aims to solve the challenges associated with the FCS-MPC such as spread spectrum and variable switching frequency by introducing variable sampling frequency concept. This method uses an auxiliary algorithm to calculate the number of sampling points to be used in the main predictive control algorithm. This approach combines the working principles of the FCS-MPC and space vector modulation to achieve high dynamic performance as in FCS-MPC and fixed switching frequency operation as in SVM.

In this chapter a variable sampling frequency model predictive control is presented for the elimination of even-order harmonics and spectrum shaping. The proposed strategy was verified with the NPC converter, since it presents more challenges compared to a standard two-level converter. Multiple objectives are considered at the same time, such as: load current control, balancing of the DC-link capacitor voltages, common-mode voltage mitigation and elimination of even-order harmonics in the load current harmonic spectrum. The corresponding simulation results are presented for both NPC rectifier and inverter configurations.

### 3.2 Virtual System Simulator Model for Harmonic Spectrum Shaping

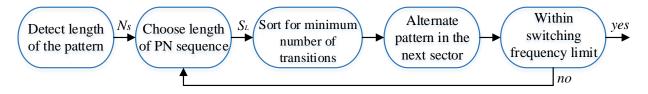

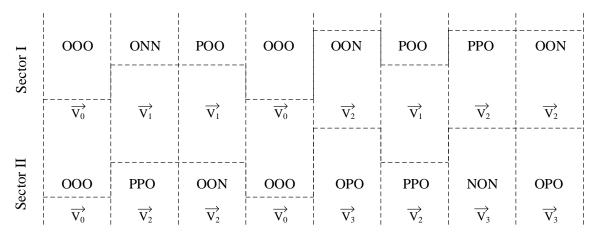

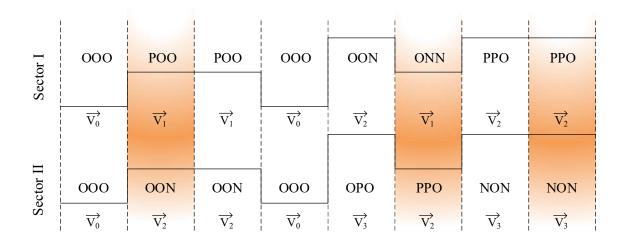

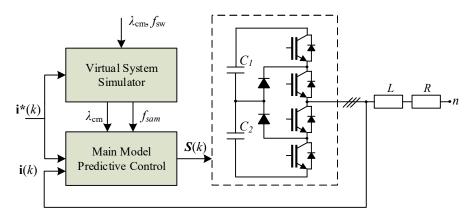

The very well-known characteristic of FCS-MPC is that a switching pattern does not exists as the control does not use a modulator. This issue leads to a variable switching frequency. Due to unsynchronized sampling between the measurements and output fundamental frequency, the chosen states (voltage vectors) vary from the selected switching states in the preceding cycle. The resulting switching does not fit into a pattern, leading to a spectrum with spread frequencies, containing integer and non-integer multiples of the fundamental frequency.