#### APPLICATION MAPPING AND NOC CONFIGURATION USING HYBRID PARTICLE SWARM OPTIMIZATION

by

Muhammad Obaidullah

B.Sc. Electrical Engineering, Abu Dhabi University, U.A.E, 2014

A thesis presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2017

© Muhammad Obaidullah, 2017

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public

#### **Application Mapping and NoC Configuration**

#### **Using Hybrid Particle Swarm Optimization**

Master of Applied Science, 2017 Muhammad Obaidullah Electrical and Computer Engineering Ryerson University

#### Abstract

Network-on-Chip (NoC) has been proposed as an interconnection framework for connecting large number of cores for a System-on-Chip (SoC). Assuming a mesh-based NoC, we investigate application mapping and NoC configuration optimization using a hybrid optimization scheme. Out technique, Hybrid Discrete Particle Swarm Optimization (HDPSO), combines Tabu-search, communication volume based core swapping, and swarm intelligence. We employ a Tabu-list to discourage swarm particles to re-visit the explored search space and propose an alternative route towards the intended movement direction. In each iteration of swarm, a sub-swarm containing configuration solutions (sub-particles) searches for optimal configuration for the parent particle (mapping solution). Optimization goals include minimum average communication latency, power, area, credit loop latency, and maximum average link duty factor. The proposed technique is tested for well-known multimedia application core graphs and several large synthetic cores-graphs. It was found that on average our hybrid scheme generates high quality NoC mapping and configuration solutions when compared to some existing stochastic optimization techniques.

#### Acknowledgements

Foremost, I would like to express my sincere gratitude to my supervisor Dr. Gul N. Khan. His guidance helped me during the time of research and writing of this thesis. It was fantastic to have the opportunity to work with such a supporting, cheering, and experienced person. He paved my way throughout my study and helped me make crucial decisions in my academic life. He consistently allowed my work to be my own work, but steered me in the right direction whenever he thought I needed it. I could not have imagined having a better advisor and mentor for my MASc study. It has been a period of intense learning for me, not only in the scientific arena, but also on a personal level.

A very special gratitude goes to Ryerson University, Faculty of Engineering & Architectural Science (FEAS), and Ontario Graduate Scholarship (OGS) for helping and providing the funding for the work.

I would also like to thank my siblings: Mamuna, Abdur Rab, Fatima, and Aisha, who have provided me moral and emotional support in my life. I am grateful to my father Rashid Manzur, for supporting me spiritually throughout writing this thesis and my life in general. I am also grateful to my other family members and friends who have supported me along the way.

Last but not the least, I would like to thank my life-coach, my mother Kausar Rashid. She was always there for me. She taught me never to give up. No matter how hard the journey became, she encouraged me to try harder and keep moving forward.

Thanks for all your encouragement! This would not have been possible without you.

Muhammad Obaidullah

Dedicated to

my mother

Kausar Rashid

## **Table of Contents**

| Author's Dec  | larationii                          |

|---------------|-------------------------------------|

| Abstract      | iii                                 |

| Acknowledge   | ements iv                           |

| Dedication    | V                                   |

| List of Table | s xi                                |

| List of Figur | es xii                              |

| Chapter 1 In  | troduction1                         |

| 1.1           | Motivation4                         |

| 1.2           | Objectives & Contributions          |

| 1.3           | Thesis Structure                    |

| Chapter 2 O   | verview7                            |

| 2.1           | NoC Topologies7                     |

| 2.2           | NoC Packet Structure                |

|               | 2.2.1 Flow Control Unit (flit)      |

|               | 2.2.2 Physical Transfer Unit (phit) |

| 2.3           | Flow Control                        |

|               | 2.3.1 STALL-GO Flow Control         |

|               | 2.3.2 T-Error Flow Control          |

|     | 2.3.3  | ACK/NACK Flow Control                            | 14 |

|-----|--------|--------------------------------------------------|----|

|     | 2.3.4  | Credit-based Flow Control                        | 15 |

| 2.4 | Routir | ng Mechanisms                                    | 15 |

|     | 2.4.1  | Starvation                                       | 15 |

|     | 2.4.2  | Dead-locks                                       | 16 |

|     | 2.4.3  | Live-locks                                       | 16 |

|     | 2.4.4  | Deterministic Routing                            | 16 |

|     |        | 2.4.4.1 Dimension ordered routing (X-Y) or (Y-X) | 16 |

|     |        | 2.4.4.2 Destination-Tag Routing                  | 17 |

|     | 2.4.5  | Oblivious Routing                                | 18 |

|     | 2.4.6  | Adaptive Routing                                 | 19 |

|     |        | 2.4.6.1 Load Balanced Adaptive Routing           | 19 |

|     |        | 2.4.6.2 Fully Adaptive Routing                   | 19 |

|     |        | 2.4.6.3 Minimal Adaptive Routing                 | 20 |

| 2.5 | NoC r  | outer micro-architecture                         | 20 |

|     | 2.5.1  | Crossbar                                         | 21 |

|     | 2.5.2  | Input port                                       | 21 |

|     | 2.5.3  | Arbiter                                          | 22 |

| 2.6 | NoC N  | Mapping                                          | 22 |

|     | 2.6.1  | State-of-the-Art Mapping tools                   | 25 |

|     |        | 2.6.1.1 Deterministic Techniques                 | 25 |

|             |        | 2.6.1.2 Stochastic Techniques                                                | 26 |

|-------------|--------|------------------------------------------------------------------------------|----|

| 2.7         | NoC (  | Configuration2                                                               | 28 |

|             | 2.7.1  | State-of-the-art NoC Configuration Tools and Work-flows                      | 28 |

| Chapter 3 O | ptimal | NoC Mapping using HDPSO                                                      | 31 |

| 3.1         | Introd | uction                                                                       | 31 |

| 3.2         | Proble | m Definition                                                                 | 34 |

| 3.3         | HDPS   | O Algorithm                                                                  | 35 |

|             | 3.3.1  | A HDPSO Particle                                                             | 35 |

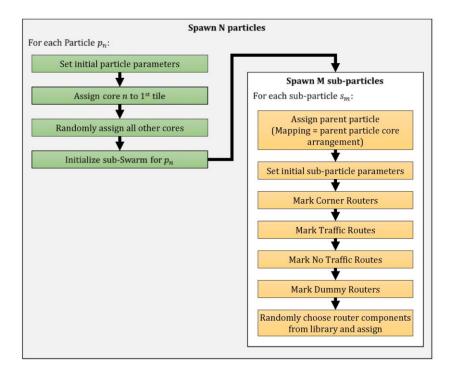

|             | 3.3.2  | Initial Population Generation                                                | 38 |

|             | 3.3.3  | Particle Movement (Applying Swap Moves)                                      | 39 |

|             | 3.3.4  | Tabu-List and Particle Reflection                                            | 41 |

|             | 3.3.5  | Communication Volume based Optimization                                      | 45 |

|             | 3.3.6  | Evolution of Particles                                                       | 46 |

|             |        | 3.3.6.1 Inertia Stage (Stage A)                                              | 47 |

|             |        | 3.3.6.2 Local Convergence Stage (Stage B)                                    | 47 |

|             |        | 3.3.6.3 Swarm Convergence Stage (Stage C)                                    | 48 |

|             |        | 3.3.6.4 Traffic Load Optimization Stage (Stage D)                            | 48 |

|             | 3.3.7  | Stopping Criteria                                                            | 18 |

|             | 3.3.8  | Dynamic Tuning Parameters                                                    | 50 |

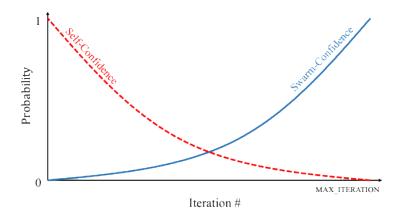

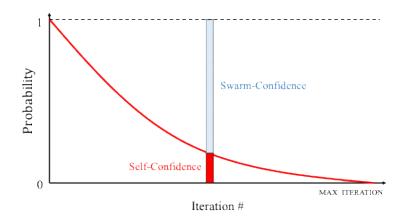

|             |        | 3.3.8.1 Inverse exponential self-confidence and exponential swarm confidence | 51 |

|             |        | 3.3.8.2 Inverse exponential self-confidence and remaining swarm confidence   | 52 |

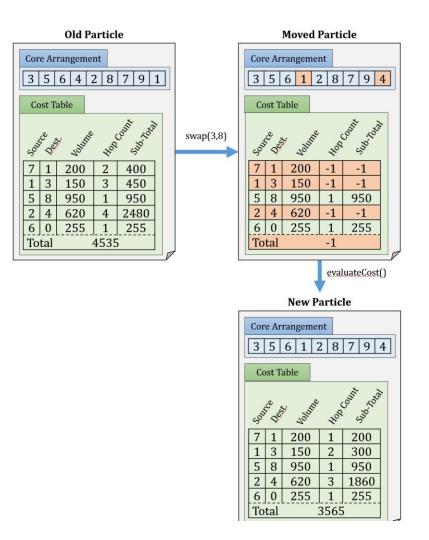

|             | 3.3.9 Particle Cost Pre-calculation              | 52 |

|-------------|--------------------------------------------------|----|

| 3.4         | Experimental Results for NoC Mapping (Particles) | 53 |

| 3.5         | Summary                                          | 63 |

| Chapter 4 ( | Optimal NoC Configuration using Sub-swarm        | 64 |

| 4.1         | Introduction                                     | 64 |

| 4.2         | Problem Definition                               | 69 |

|             | 4.2.1 Constraints                                | 73 |

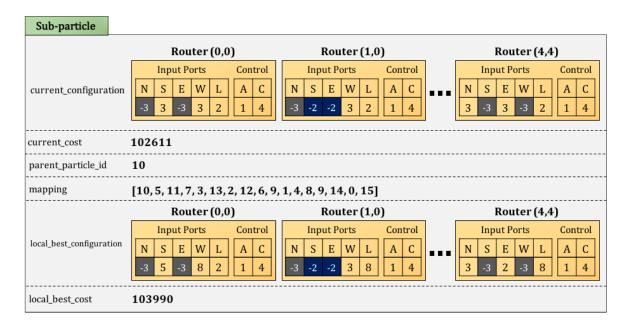

| 4.3         | Configuration Solution Space                     | 73 |

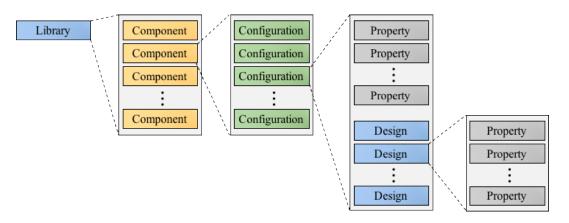

| 4.4         | Router Sub-component Library Representation      | 75 |

|             | 4.4.1 Library                                    | 76 |

|             | 4.4.2 Component                                  | 76 |

|             | 4.4.3 Configuration                              | 77 |

|             | 4.4.4 Design                                     | 77 |

|             | 4.4.5 Property                                   | 78 |

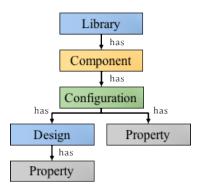

| 4.5         | A Sub-particle (Configuration Solution)          | 78 |

| 4.6         | Configuration for Topology                       | 79 |

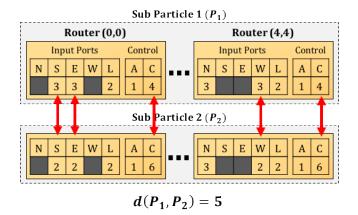

| 4.7         | Initial Configuration Heuristics                 | 81 |

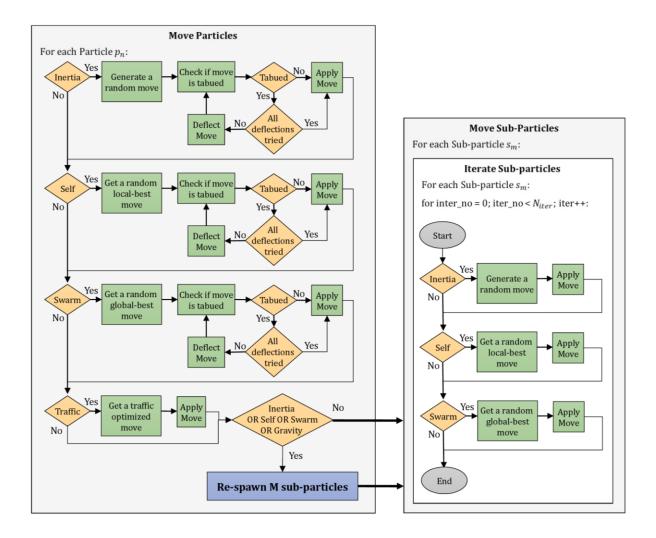

| 4.8         | Sub-Swarm Movement                               | 82 |

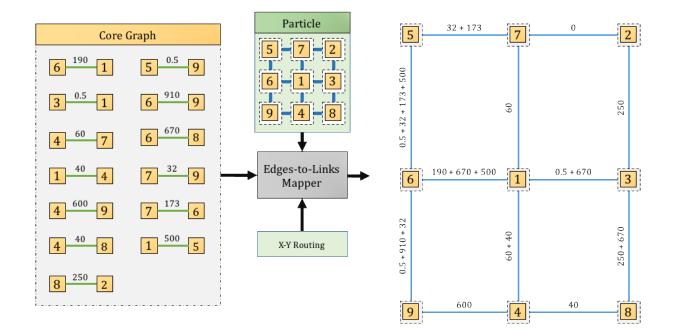

|             | 4.8.1 Mapping Edges to Links                     | 84 |

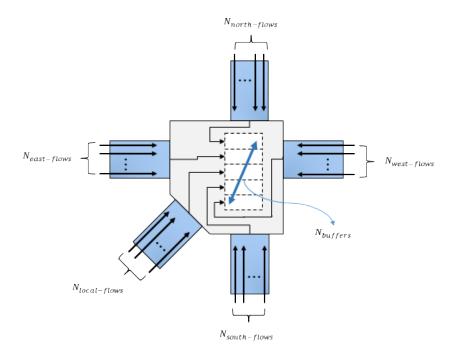

|             | 4.8.2 Buffer Size Optimization                   | 85 |

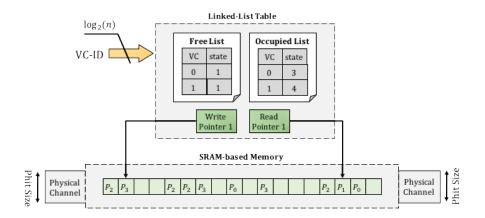

|             | 4.8.2.1        | Conventional Virtual Channel (CVC)        | 85  |

|-------------|----------------|-------------------------------------------|-----|

|             | 4.8.2.2        | Dynamically Allocated Multi-Queues (DAMQ) | 80  |

| 4.9         | Convergence an | nd Stopping Criteria                      |     |

| 4.10        | NoC Configura  | tion Results                              |     |

|             | 4.10.1 Input I | Library                                   |     |

|             | 4.10.1.1       | Crossbar Library                          | 88  |

|             | 4.10.1.2       | Arbiter Library                           |     |

|             | 4.10.1.3       | Input Port Library                        |     |

| 4.11        | Summary        |                                           | 98  |

| hapter 5 C  | onclusion      |                                           |     |

| eferences . |                |                                           | 101 |

| lossary     |                |                                           | 106 |

| -           |                |                                           |     |

## **List of Tables**

| Table 2.1 Flow control protocols at a glance    13                                                     |

|--------------------------------------------------------------------------------------------------------|

| Table 3.1 Application core-graphs used as benchmark    54                                              |

| Table 3.2 Execution Time Comparison of Benchmark CoreGraphs    57                                      |

| Table 3.3 Traditional DPSO vs HDPSO results for 32, 64, and 128 core synthetic application core-graphs |

| Table 4.1 Negative Universal IDs (uIds) and their meanings                                             |

| Table 4.2 Crossbar input library properties    88                                                      |

| Table 4.3 Arbiter input library properties    88                                                       |

| Table 4.4 LLD input port library properties                                                            |

| Table 4.5 ViChaR input port library properties    90                                                   |

| Table 4.6 EDVC-FRW input port library properties    91                                                 |

| Table 4.7 EDVC-FW input port library properties    92                                                  |

| Table 4.8 Area/Power for PIP and MPEG4 in optimal, generous, and minimal configurations                |

## List of Figures

| Figure 1.1 (a) Bus-based interconnection architecture (b) network-based on-chip interconnection                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1 (a) Ring (b) Butterfly (c) Hypercube (d) Mesh (e) Torus (f) Binary Tree (g) Custom Mesh-Type (h) Star (i) Fully-Connected Topology |

| Figure 2.2 (a) A 3 x 3 2D mesh NoC (b) A 3 x 3 torus NoC                                                                                      |

| Figure 2.3 Packet, flit, and phit relationship                                                                                                |

| Figure 2.4 Stall-Go flow control                                                                                                              |

| Figure 2.5 T-Error flow control                                                                                                               |

| Figure 2.6 Ack/Nack flow control                                                                                                              |

| Figure 2.7 Clockwise and Anti-clockwise dead-lock situations                                                                                  |

| Figure 2.8 X-Y routing mechanism for 3 different source and destination packets                                                               |

| Figure 2.9 Routing in 4-ary 2-fly butterfly NoC topology                                                                                      |

| Figure 2.10 Oblivious routing mechanism                                                                                                       |

| Figure 2.11 NoC router micro-architecture                                                                                                     |

| Figure 2.12 NoC design workflow and this work's targeted workflow                                                                             |

| Figure 2.13 Mapping possibilities for a 2 by 2 mesh NoC with 4 cores                                                                          |

| Figure 2.14 Black box analogy of NoC mapping tool                                                                                             |

| Figure 2.15 Æthereal NoC configuration and mapping workflow                                                                                   |

| Figure 3.1 DPSO Search spaces – particles reach sub-optimal solutions                                                                         |

| Figure 3.2 HDPSO Algorithm                                                                                                                    |

| Figure 3.3 Application with multiple modes of operation (AM).                                   |    |

|-------------------------------------------------------------------------------------------------|----|

| Figure 3.4 A HDPSO particle structure for MPEG-4 decoder                                        |    |

| Figure 3.5 Determining distance between particles (particle A & B)                              |    |

| Figure 3.6 Identifying the chosen swap move.                                                    |    |

| Figure 3.7 Complex swap moves                                                                   | 41 |

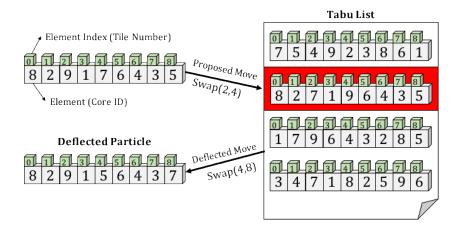

| Figure 3.8 Reflection of particles from the explored search space.                              |    |

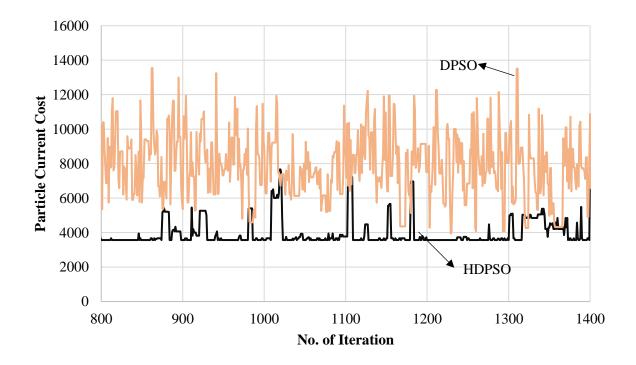

| Figure 3.9 HDPSO vs DPSO particle cost variations for mapping of MPEG4 decoder                  |    |

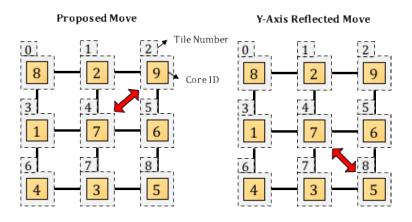

| Figure 3.10 Reflection of a Tabu-ed swap (2,4) move.                                            |    |

| Figure 3.11 Reflection of a swap (2, 4) with respect to y-axis.                                 |    |

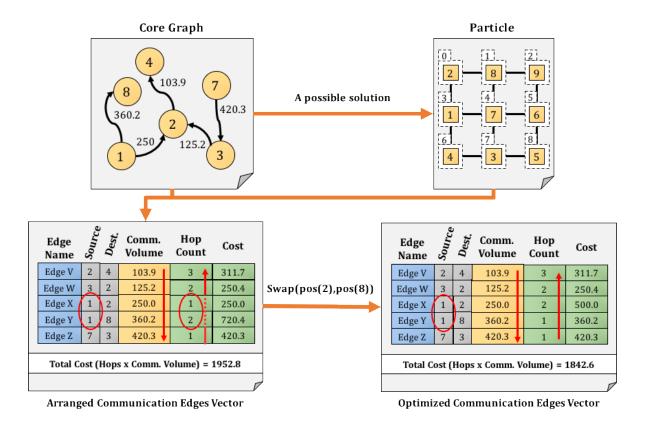

| Figure 3.12 Communication Volume based core swapping.                                           | 46 |

| Figure 3.13 Local Convergence Stage (Stage B) path decider.                                     |    |

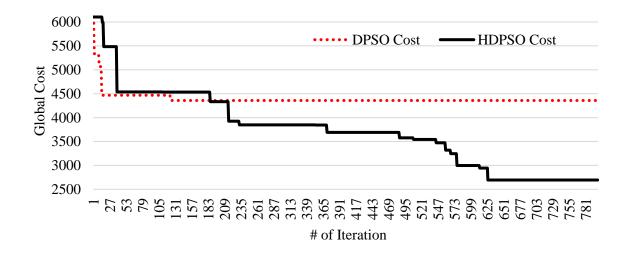

| Figure 3.14 Global cost for same confidence - DPSO vs. HDPSO                                    |    |

| Figure 3.15 Inverse exponential self-confidence and exponential swarm-confidence.               |    |

| Figure 3.16 Inverse exponential self-confidence and remaining swarm-confidence                  |    |

| Figure 3.17 Particle cost pre-calculation                                                       | 53 |

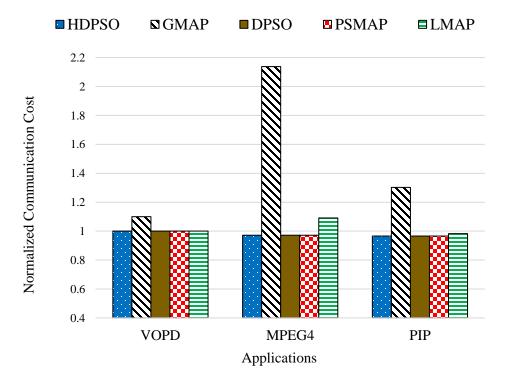

| Figure 3.18 Communication cost normalized to NMAP cost.                                         |    |

| Figure 3.19 Cost improvement DPSO vs. HDPSO.                                                    | 56 |

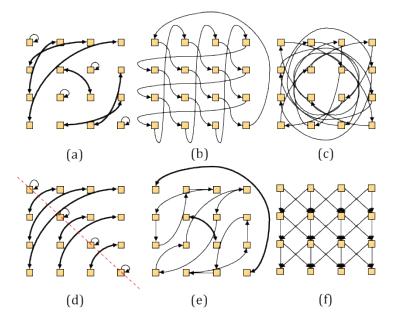

| Figure 3.20 Traffic patterns used to evaluate the HDPSO based NoC mapping (a) Bit-reversal, (b) | •  |

| (c) Tornado (d) Transpose (e) Shuffle (f) Stencil.                                              |    |

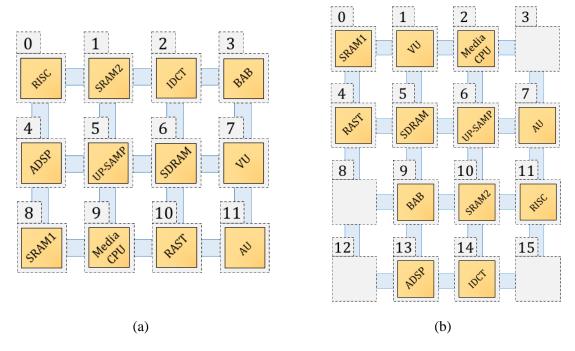

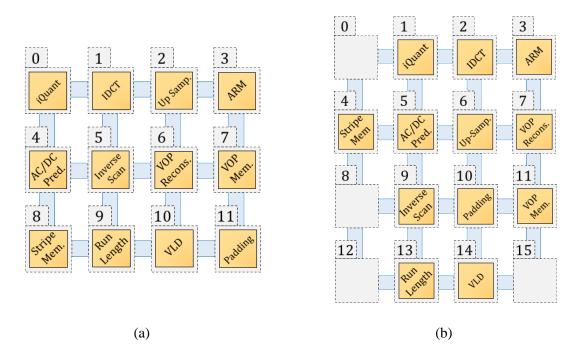

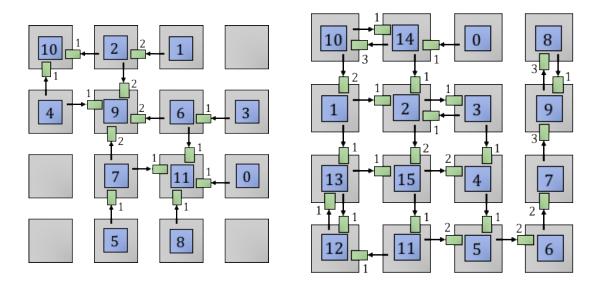

| Figure 3.21 HDPSO generated optimal (a) 3×4 (b) 4×4 NoC mapping of MPEG4 decoder                |    |

| Figure 3.22 HDPSO generated optimal (a) 3×4 (b) 4×4 NoC mapping of VOP decoder.                 |    |

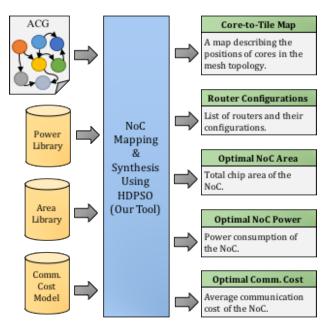

| Figure 4.1 CAD system architecture for NoC synthesis                             |                              |

|----------------------------------------------------------------------------------|------------------------------|

| Figure 4.2 Typical NoC synthesis workflow.                                       |                              |

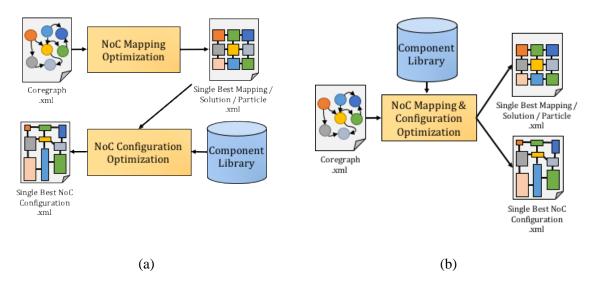

| Figure 4.3 (a) Segregated search space optimization workflow (b) combined se     | earch space optimization. 67 |

| Figure 4.4 The proposed hybrid workflow for NoC mapping and configuration        | ι68                          |

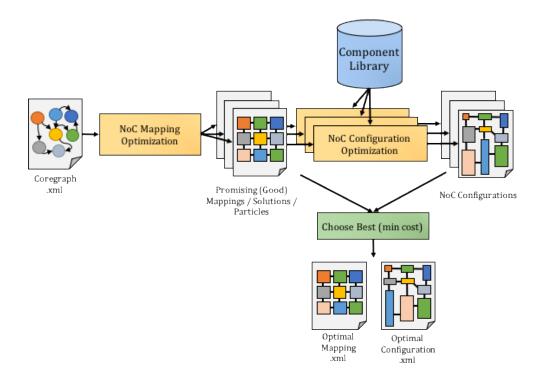

| Figure 4.5 Inner workings of the mapping and configuration HDPSO algorithm       | n69                          |

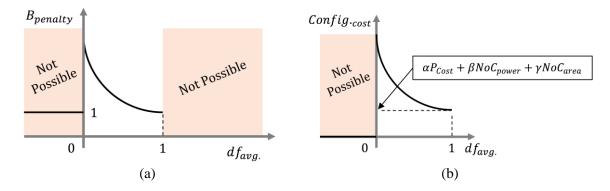

| Figure 4.6 (a) Average duty factor and buffer penalty relationship (b) Average d |                              |

| Figure 4.7 NoC Configuration solution space.                                     | 74                           |

| Figure 4.8 NoC Configuration library XML element hierarchy.                      |                              |

| Figure 4.9 Library element hierarchy and relationship                            |                              |

| Figure 4.10 A library element defined in XML format.                             |                              |

| Figure 4.11 A component element defined in XML format.                           | 77                           |

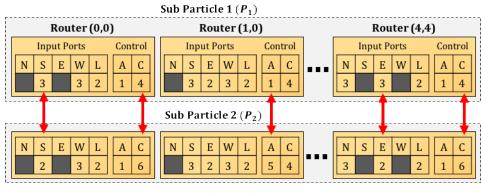

| Figure 4.12 Internal structure of a sub-particle                                 |                              |

| Figure 4.13 Identification of un-used input ports                                |                              |

| Figure 4.14 Determining distance between sub-particles (configuration solutio    | ns)81                        |

| Figure 4.15 Initial Configuration heuristics.                                    |                              |

| Figure 4.16 HDPSO sub-particle movement algorithm                                |                              |

| Figure 4.17 Link traffic volume calculation.                                     |                              |

| Figure 4.18 Link stress estimation.                                              |                              |

| Figure 4.19 CVC input port architecture.                                         |                              |

| Figure 4.20 Determining minimum number of buffers required                       |                              |

| Figure 4.21 DAMQ VC input port architecture                                                     | 87  |

|-------------------------------------------------------------------------------------------------|-----|

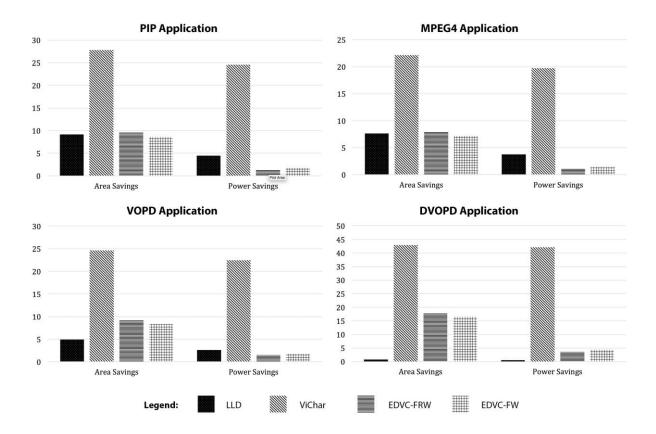

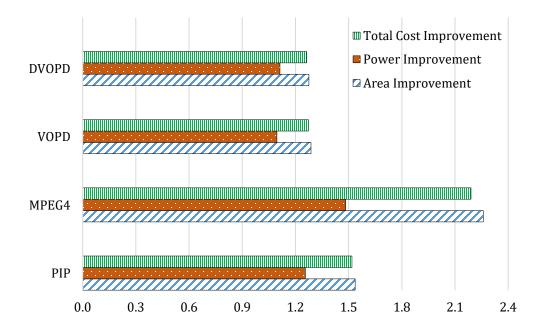

| Figure 4.22 Power and area % savings observed when comparing HDPSO optimized configuration to u | ın- |

| optimized generous configuration                                                                | 94  |

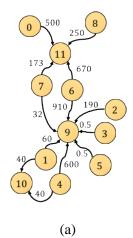

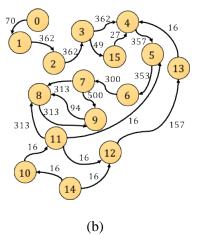

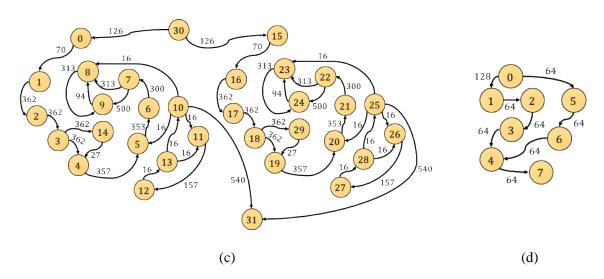

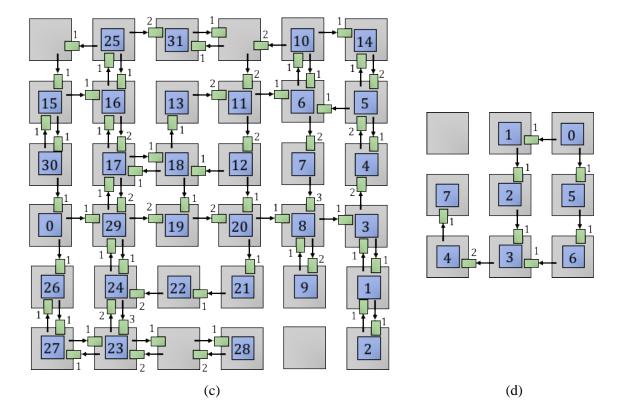

| Figure 4.23 NoC coregraphs (a) MPEG4 (b) 16-core VOPD (c) DVOPD (d) PIP.                        | 95  |

| Figure 4.24 NoC configuration and mapping solutions (a) MPEG4 (b) VOPD (c) DVOPD (d) PIP        | 96  |

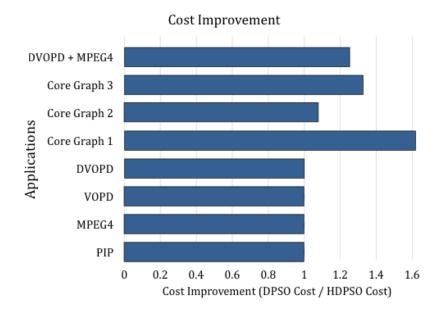

| Figure 4.25 Cost improvements due to configuration optimization                                 | 98  |

# Chapter 1

### Introduction

To meet complex functions support, minimum area, and small power consumption demands of embedded devices, System-on-a-Chip (SoC) designers are squeezing multiple and more complex Silicon Intellectual Properties (SIPs) onto a single chip. However, major design challenges while integrating multiple SIPs include reducing chip area and power consumption while maintaining high performance specifications. To deal with interconnection complexity, abstraction and regularity of interconnection architecture is required. Network-on-Chips (NoCs) have emerged recently as viable interconnection alternative instead of buses. NoCs provide high data bandwidth, high network throughput, multiple transactions per cycle, and scalability.

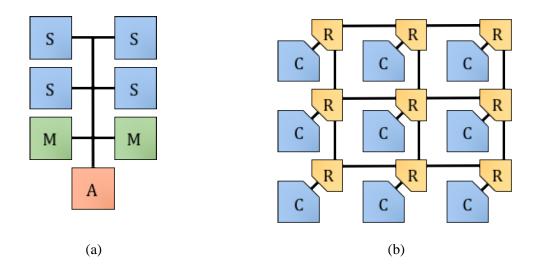

Traditionally, SIPs or cores were mapped using static bus architectures eg. AMBA, AXI, STBus etc. A conventional non-hierarchical bus architecture is shown in Figure 1.1(a). Slaves (S) are SIPs which respond to requests or commands of Masters (M) SIPs on the bus. Since there are multiple masters, bus access is controlled through a component called arbiter (A). Usually, bus masters are Central Processing Units (CPUs) and Direct Memory Accessors (DMAs) while slaves are peripherals, I/Os, and memories.

Bus architecture has many drawbacks when increasing the number of SIP blocks on the SoC. Since bus is a collection of wires, only one core can use those wires to communicate to another core. The core which initiates the signals and generates control signals is called a bus master. At a time, only one master and one slave can communicate with each other. This is to ensure that there are no short-circuits because one core has pulled the signal low while the other core pulls it high. While two cores are communicating with each other, other cores might also be waiting for bus access and precious time is being wasted.

Secondly, every SIP block attached in bus adds a parasitic capacitance degrading the data signal integrity. This is a huge issue in bus architectures that do not use tri-state buffers to disconnect cores which are not communicating. For example, Avalon bus architecture uses multiplexers as switching component rather than tri-state buffers. This increases parasitic capacitance as more SIPs are added onto the bus.

Thirdly, data bandwidth in bus-based systems is limited and is shared among all IPs attached because only one transaction can occur in a single clock cycle. If there is contention for bus-access, lower priority masters are forced to wait until higher priority masters have completed their transaction. This is true even if the master A wants to talk to slave C and master B wants to talk to slave D. This can cause a starvation condition in which masters with low priority never get access to resources. To tackle this issue, SoC designers are forced design and install custom hardware to detect starvation condition.

Lastly, bus arbitration logic delay grows as more number of masters are added onto bus. [1] The decision tree of who should get the bus access grows as more bus nodes are added and so does the arbitration logic, area occupancy, and power consumption. This large arbitration ladder logic increases critical path delay which in turn reduces the maximum operational frequency and degrades the performance.

A typical on-chip network architecture is shown in Figure 1.1(b). Label 'C' signifies SIP Cores and are connected to other SIPs through **R**outers labelled 'R'. NoC allows core's signals to be packetized and transmitted over fabric of switches and routers. Packetization of data also allows each channel's bandwidth to be shared among multiple sources using Virtual Channels (VCs).

NoCs improve throughput, are easily scalable, and allow multiple transactions to occur in a clock cycle. However, NoCs still need to overcome several challenges such as significant static and dynamic power consumption, large chip area occupied by network hardware, traffic congestion, and high data transfer latencies. Network resources also need to be managed efficiently in order to avoid expensive design costs while keeping the networks performance maximum.

There are three NoC optimization metrics we will be addressing in this work, average communication latency, power, and area. We will be using a library of pre-synthesized NoC router components and information about application (CoreGraph) to optimize these metrics. The architecture of these pre-synthesized router components are discussed by Oveis-Gharan and Khan [2, 3, 4, 5, 6, 7]. These pre-synthesized components are imported into our tool and their power and area metrics are presented in Section 4.10.1. Our optimization method is a hybrid of well-known stochastic techniques Discrete Particle Swarm Optimization (DPSO) [8] and Tabu-Search (TS) [9]. However, we have modified the underlying DPSO algorithm significantly to cater to our NoC mapping and configuration solution space. DPSO algorithm will be discussed in detail in chapter 3.

Figure 1.1 (a) Bus-based interconnection architecture (b) network-based on-chip interconnection.

Power consumption is composed of two sub-components, static and dynamic. Static (leakage) power consumption is mainly due to reverse-bias leakage between diffused regions and the substrate of transistors. This power consumption is due to the small current leaking through a transistor even-though depletion region is thick and present. Useful analogy is to imagine a water tap which was left little open and water droplets are still falling. Like in the water tap, a lot of force is required to close the tap completely, high voltage needs to be applied to the gate of the transistor to close it completely. However, this high voltage is not available to the transistor (VSS and VDD) because modern chips and cores operate at around 1.1V or even lower subject to the operating frequency requirement and the technology cell library specification.

Dynamic (switching) power consumption is calculated by adding transient power and capacitiveload power consumption. Dynamic power consumption is due to the current that flows only when the transistors of the devices are switching from one logic state to another. This power is consumed in charging external load capacitance and is dependent on switching frequency. Dynamic power consumption increases when more data transfers or transactions occur among network nodes/routers. One way to reduce dynamic power consumption in NoCs is to place SIPs which communicate with high volume near each other at minimum hop distance. In this work, we use the worst-case dynamic power for each router component. This is calculated by simulating sending of toggling bits through the input ports of the component.

Flit buffers are major contributors to network static power consumption [10]. Flit buffers are essentially Static Random Access Memories (SRAMs) used to store small data units called flow control un**its** (flits) in the router input ports. As technology process nears submicron level, static power consumption gains major share in total power consumption [10]. SRAMs are major shareholders of chip area because 1 D-flip-flop holds 1 bit and we need 8 of those to store just 1 byte. For example, if the flit size is 128-bits and the buffer depth is 4 flits for each input port, a 4x4 mesh NoC will have total  $128 \times 4 \times 5 \times 16 = 40,960$  flops. On top of that, all modern ASICs have Memory Built-In Self-Test (MBIST) components inserted for each D-flip-flop. This further increase the chip area requirement even-though MBIST hardware is redundant in normal functional mode of the chip. Hence, it is becoming crucial to choose right amount of flit buffers in an on-chip network to reduce NoC power and area.

#### **1.1 Motivation**

Three major VLSI hardware trends compel us to do research on NoC optimization tools. The first is increased usage of NoCs on SoCs and microcontrollers for IoT. SoC designers are realizing that there is simply no better way to integrate large number of cores onto a single chip rather than a NoC. Each core's designer can request a throughput from SoC team and be assured that the throughput is going to be available no matter how many cores are being added on the chip level. Because each additional core brings with itself more network throughput, bandwidth is not shared, unless two or more cores are trying to communicate with the same core. Yesterday's researches often predicted that NoC usage will become a reality in future. The future is here and it is looking bright for NoCs. The second is lack of optimization tools that optimize for heterogeneous SoCs which are often required to operate on wide variety of operating modes involving multiple cores on a chip. There is a need for optimization tool which co-optimizes NoC mapping and NoC configuration, takes into consideration multi-modal application, and uses a stochastic optimization technique. The third reason is that most of the NoC optimization tools do not use pre-synthesized router

components to optimize NoC latency, power, and area. NoC area and power can be more accurately measured once the values for real synthesized components is available. Existing tools often try to use parametric equations to predict the area and power of a NoC before synthesis and those can sometimes be far-off from real values. Due to these reasons, we have proposed a C++ based tool which performs optimization of NoC area, power, and latency by using library of pre-synthesized router components.

#### **1.2 Objectives & Contributions**

Our main contributions include combining exploration abilities of particle swarm with exploitation abilities of traffic-load directed swapping (Section 3.3.6.4), development of linear particle deflection mechanism (Section 3.3.4) based on Tabu memory which is well-suited for NoC mapping problem space, combining particles and sub-particles to form con-joined search space for mapping and synthesis problems (Section 4.8), defining workflow for NoC mapping and configuration optimization (Section 4.1), and proposing a stopping criteria based on the average mapping solution distances and swarm divergence factor (Section 3.3.7). All in all, the resulting optimization tool is based on Hybrid Discrete Particle Swarm Optimization (HDPSO) method and is tested for some synthetic and real-life applications yielding promising results (Section 4.10).

#### **1.3 Thesis Structure**

The remaining thesis is organized as follows. Chapter 2 provides an introductory background on on-chip networks. We introduce some basic NoC topologies and how their routing mechanisms work. Secondly, NoC Packet structure and micro-architecture of a typical NoC router is discussed. Thirdly, past works in NoC mapping and configuration domain will be discussed.

In Chapter 3, we define NoC mapping, which is the first half of optimization problem. We also discuss how an application is parsed into CoreGraph suitable for input into our optimization tool. We describe the inner workings and algorithm of particle solution space. We also discuss the tool turning parameters and propose optimization stopping criteria. We conclude the chapter with experiment on synthetic and real applications and present results from the tool while comparing it against traditional DPSO and other methods.

In Chapter 4, we characterize NoC configuration problem and propose a sub-swarm technique to solve it. We also propose design constraints which allows the tool to restrict to interesting router configuration solutions. Additionally, we also list and detail NoC component libraries we used for

optimization. We compare our sub-swarm with un-optimized configuration results and provide the improvement metrics achieved. Chapter 5 concludes the thesis and provides future direction for future work.

# Chapter 2

### **Overview**

#### 2.1 NoC Topologies

NoC allows SIPs or modules to be connected in any topology with aid of on-chip routers. Popular on-chip network topologies are 2D Mesh, Hypercube, Torus, and Butterfly. An *n*-dimensional radix-*k* torus, or *k*-ary *n*-cube, consists of  $N = k^n$  nodes arranged in an *n*-dimensional cube with *k* nodes along each dimension. Each node in the topology is assigned an *n*-digit radix-*k* address  $\{a_{n-1}, ..., a_0\}$  and is connected by a pair of channels (one in each direction) to all nodes with addresses that differ by  $\pm 1 \pmod{k}$  in exactly one of the address digit [11].

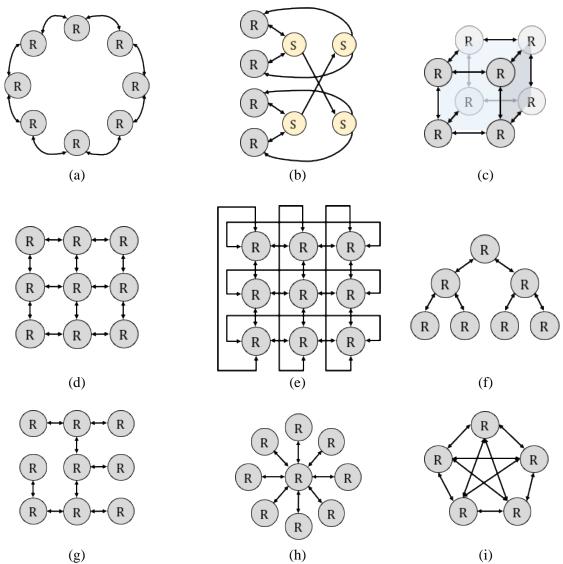

Popular NoC topologies being used by the researchers include ring, butterfly, hypercube, mesh, torus, tree, custom-mesh, star, and fully-connected as shown in Figure 2.1. In figure 2.1, 'R' signifies a Router (node with a local core attached), and 'S' indicates a switch (a node with no core attached to itself). We consider a 2-D mesh topology for this work and modify it according to the application needs such that it ends up becoming a custom-mesh type topology Figure 2.1g after optimization.

A ring topology (Figure 2.1a) has advantages of containing very few links and 2 data paths to a specific router i.e. clock-wise and anti-clock wise. However, each router is connected to only 2 other

routers. Therefore, most of the remaining cores are at greater than 1 hop distance away. A ring topology is rarely used in NoC because of low radix, the fact that wires are cheap (in terms of area and power) on the chip, and high hop-count and latency for routers which are on the other side of the ring.

A butterfly topology (Figure 2.1b) has frequently communicating cores placed near each other while cores that communicate less frequently are placed at more hop distance. The Figure 2.1b shows a folded perspective of butterfly topology. However, butterfly topology can have very congested routers which can increase latency of the network and is difficult to scale because addition of each core onto the network not only requires addition of a router (as with all topologies), it requires addition of more switches.

Hypercube topology (Figure 2.1c) is a very interesting topology for 3D Integrated Circuits (ICs) as it allows components on the top and bottom silicon layers to be incorporated into the mesh network. However, this means that each router will have 2 additional input and output ports compared to a mesh topology which increases the complexity of the network. In case of 2D ICs, this topology increases the interconnection complexity posing difficulty in floor-planning and increases router size (increased power and area consumption) while not presenting significant trade-off advantages in network latency.

2-D Mesh network topology (Figure 2.1d) has regularity of design, increased network throughput with addition of any new node, and alternative routes to destinations providing fault-tolerance A 2D-mesh network has a router connected to each core and each router connected to four other routers..

2D-torus network topology (Figure 2.1e) has the same advantages as a mesh network and some more. A 2D-mesh network is often congested in the center because the radix of the boundary routers is low, radix 2 for corners and radix 3 for routers that are at boundary but not corners. The torus topology removed this problem by making the topology circularly symmetrical which increases the radix of boundary routers and increases possible data paths. Disadvantages include increased chip area and power compared to mesh network due to addition of input and output ports on the boundary routers.

Tree topology (Figure 2.1f) is good for small applications which have groups of cores which communicate among themselves in high volume (Locality). Tree topology can take advantage of locality and place highly communicating cores under the same tree node while less frequently communicating cores in different branches. As the application size grows, tree structure can grow exponentially as addition of 1 core can cause root structure to grow too in order meet the increased throughput demand. However, this topology is widely in use in todays SoCs because it supports hierarchical approach which block designers, core designers, and SoC integration designers take while designing ASICs. The block-level designers can

design a router for their internal sub-components and have one link installed in it for communicating with the upper core level logic. The core-level designers may design a router for their internal blocks and have one link installed in it for communicating with the upper SoC level logic.

For an application specific mesh topology when a specific static routing mechanism (eg. XY-routing) is chosen and fixed, there tends to be some links in the mesh network which never get used. So, the chip designers can remove the links and the associated hardware to reduce area occupied by the NoC and NoC power consumption. What results after this, is a custom mesh-like topology (Figure 2.1g). In this topology all links which never get used are removed and the routers area and power is greatly reduced. This topology is very interesting for applications containing heterogeneous cores. Unless the design contains N number of processing units (multicore CPUs) or N number of compute units (SIMD/GPU workgroups), there are always some links in the mesh network that can be trimmed off. Almost all real-word applications contain heterogeneous cores and there is a need to customize a popular homogenous-friendly mesh topology to become heterogeneous.

Every core in a star topology (Figure 2.1h) is at most 2 hop distances away from any other core. However, it is rarely used in a NoC because of poor scalability. Every additional core requires addition of a local router and expanding the central router. Applications with more than 10 cores require a huge central router increasing the chip area and power requirements. Additionally, central router is very congested as all the traffic must pass through it.

Fully connected mesh network (Figure 2.1i) is a perfect topology in terms of latency as the hop distance from any core to another is just 1. However, it is a nightmare for floor planning and does not scale well with application. Each additional core requires addition of another router and modification of all other routers as well (to accommodate one more input and output port).

Figure 2.1 (a) Ring (b) Butterfly (c) Hypercube (d) Mesh (e) Torus (f) Binary Tree (g) Custom Mesh-Type (h) Star (i) Fully-Connected Topology.

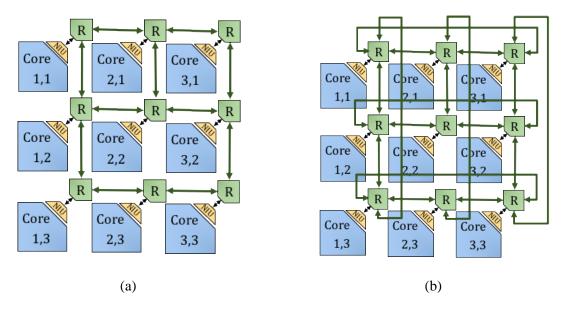

On-chip mesh network and torus network are shown in Figure 2.2. Each core is placed at a tile in the topology. A tile is an empty seat or place in the network at a specific location in which a core can be connected. Each core is then connected to its appropriate Network Interface Unit (NIU) and NIUs are connected to routers marked as R in Figure 2.2.

Figure 2.2 (a) A 3 x 3 2D mesh NoC (b) A 3 x 3 torus NoC.

#### 2.2 NoC Packet Structure

Bus transactions signals from SIPs are converted into packets by Network Interface Unit (NIU) before sending it to NoC fabric. NIU is also responsible for setting the priority of the packet and in case of transaction, it makes sure that no other data reaches the core until the transaction is complete. It also deconstructs the in-coming packets and generates appropriate signals for the core to understand. NIUs can be different for each core according to the interface signals they have. For example, a core with Advanced eXtensible Interface (AXI) bus interface will require a NIU that converts AXI bus signals into network packets. Usually theses are standard NIUs and its Register Transfer Level (RTL) hardware can be generated by a synthesis tool easily. A conventional NIU contains Generic Core Interface (GCI), Packet Maker (PM), Packet Disassembler (PD), and Asynchronous FIFOs for buffering and Clock Domain Crossing (CDC) synchronization [12]. Any core specific wrapper can communicate with the GCI with simple predefined handshaking signals to initiate read and write to and from NoC. PM assembles packets for the network and places them in order in the PM memory from where an asynchronous FIFO can take it out and send to the network. PD takes packets from the asynchronous FIFO and decodes them into signals for the GCI. Since on-chip network might be operating at a different clock/frequency than the core, there is need for asynchronous FIFOs to allow different read and different write speed. Synchronization blocks and buffers are added to the control signals to remove CDC and meta-stability issues.

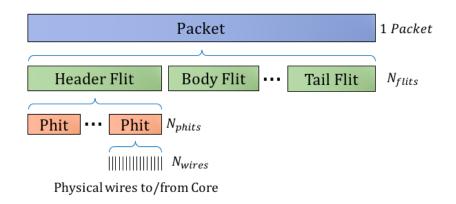

A packet is composed of a header flit, some or no body flits, and a tail flit as shown in Figure 2.3. The header flit contains metadata about the packet. For example, source id, destination id, length of packet, and Virtual Channel (VC) id if VCs are used. Each flit can be broken down into Physical Transfer Units (phits) according to the physical interconnection bus width. Phits consist of bits which are transmitted through the interconnection fabric one clock cycle at a time.

Figure 2.3 Packet, flit, and phit relationship.

#### 2.2.1 Flow Control Unit (flit)

Network packets are broken down into flits so that arbitration and flow control can be done on each flit individually. For example, arbiter generates grant signals for a particular flit, a credit is generated for a particular flit, etc. When a grant signal is received for a flit, all bits in the flit must be transmitted from input port to the output port. Similarly, when an input port's buffer becomes available, a credit is generated for the upstream router so that it can send another flit. Breaking down packets into flits presents several advantages because flit size is fixed as per the capability of routers to store them. A router can easily store flits in their input port buffers, whereas it is difficult to store the whole packet especially if the length is varying. Since memory is a huge consumer of chip area and power, it is better to keep buffer quantity as low as possible. We will be addressing optimization of these input port buffers in this work (Section 4.8.2).

#### 2.2.2 Physical Transfer Unit (phit)

Phit is composed of bits which are transferred from one router's output port to another router's input port in one clock cycle. For those interconnection architectures where a flit size is larger than the phit size, multiple clock cycles are used to transmit one flit and the input port also contains a shift register to move the bits over as soon as next bits arrive. As soon as the shift register is full, the flit is latched into

FIFO and a request might be generated for the arbiter. Making phit size smaller than flit size requires less interconnection wires from the source output port to the destination input port. There is very little advantage in terms of chip area and power savings to reduce number of interconnection wires. Interconnection wires are easy to synthesize, they increase network throughput, and reduce clock cycles required to transmit data. On the other hand, decreasing interconnection wires will provide very little area and power savings. Additionally, if phit size is smaller than flit size, a shift register is required to shift the previous bits over and latch-in the next in-coming bits. Therefore, in this work, we assume flit size is equal to the phit size.

#### 2.3 Flow Control

Flow control in a network basically defines set of rules to move data from the sender to the receiver. It is a protocol using which routers communicate with each other to transfer data. Flow control also involves routers informing other routers of its intentions and status by using meta-data and control links. Table 2.1 shows buffering requirements and features of popular flow control protocols.

| Characteristic  | STALL/GO    | <b>T-Error</b> | ACK/NACK  | <b>CREDIT-BASED</b> |

|-----------------|-------------|----------------|-----------|---------------------|

| Buffer Area     | 2N+2        | 3N+2           | 3N+k      | 2N+2                |

| Logic Area      | Low         | High           | Medium    | Low                 |

| Performance     | Good        | Good           | Depends   | Good                |

| Power (est.)    | Low         | Medium/High    | High      | Low                 |

| Fault Tolerance | Unavailable | Partial        | Supported | Unavailable         |

Table 2.1 Flow control protocols at a glance

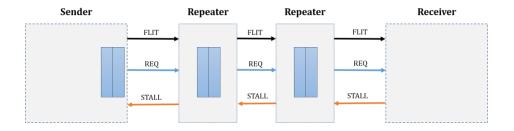

#### 2.3.1 STALL-GO Flow Control

In this type of flow control, the receiver informs the sender whether it is ready to receive more data. This is a type of explicit flow control where the control decision is taken at the receiver's end.

The router is modified to have two more signal wires other than phit length (Figure 2.4). One signal forward indicating presence of new data and another backward informing condition of input buffers either Filled('STALL') or Empty('GO'). If not enough buffer space is available in the next router/repeater, the stall signal is send to the previous router/repeater.

Figure 2.4 Stall-Go flow control.

However, the main disadvantage of STALL/GO flow control is that no fault handling is done should any flit get corrupted. In case of a corrupted flit, the error handling task is delayed over to some higher-level protocol.

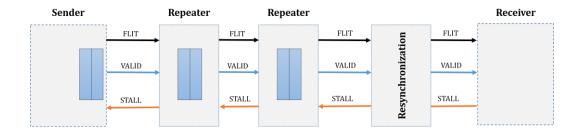

#### 2.3.2 **T-Error Flow Control**

This type of flow control is similar to STALL-GO flow control except that an extra resynchronization stage is added between the end of the link and the receiving switch as shown in Figure 2.5. T-Error flow control often increases the operating frequency of the link. This requires an additional resynchronization stage near the end of the link which is done with the help from combination of clock and delayed clock signals.

Figure 2.5 T-Error flow control.

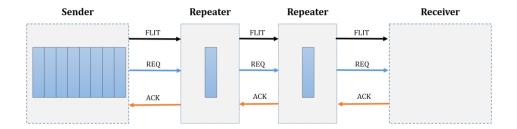

#### 2.3.3 ACK/NACK Flow Control

In this type of flow control, a copy of the flit is kept at the sender's end and the flit is sent. If the receiver acknowledges that it received the packet, the flit is discarded and the next one is sent as before procedure. As shown in Figure 2.6, repeaters on the link can be simple registers while the number of buffer requirements for the sender and receiver side is 2N+k buffers to guarantee maximum throughput. N: Number of repeaters.

Figure 2.6 Ack/Nack flow control.

It can be implemented in two ways, end-to-end and switch-to-switch. In end-to-end, the copies of flits are kept at the sender side and the final receiver acknowledges reception of flit. On the other hand, in switch-to-switch, the copies of flits are kept in any sending switch and the acknowledgement of flit received is sent back from the next switch.

#### 2.3.4 Credit-based Flow Control

In this type of flow control, the sender keeps a count of the number of free flit buffers in each virtual channel in the receiver. Anytime the sender sends the flit to receiver, the count is decremented and it is incremented if the receiver consumes/forwards the packet further. One credit connection is required from the receiver router to the sender router. When the receiver pulls this signal high, this indicates to the sender that a packet just left receiver's buffer and there is an empty space for it to send another packet.

#### 2.4 Routing Mechanisms

Routing mechanisms determine how packets/flits move from source/sender to sink/destination. There are basically two categories of routing algorithms. A good routing algorithm must prevent any potential dead-lock, starvation, and live-lock situations of packets/flits in the network.

#### 2.4.1 Starvation

Starvation is denying a core access to necessary resources. Routing starvation problem occurs when the routing algorithm services an area of routers heavily while neglecting another area. A routing algorithm might prefer to service cores on the right side of the mesh. So, the packets travelling east reach first and have higher priority than packets travelling west. This will cause starvation to the cores present on the left side of the mesh.

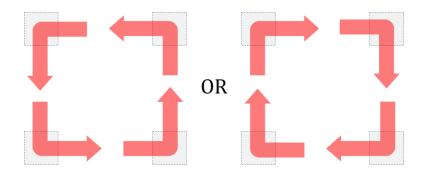

#### 2.4.2 Dead-locks

Deadlock situation may arise in NoC when any circular waiting path is generated from the routing algorithm. Any waiting for acknowledgement or waiting for credit path which cycles back to the original router is a deadlock. For example, router 1 is waiting for acknowledgement/credit from router 2, router 2 from router 3, router 3 from router 4, and router 4 from router 1 again. Two types of dependency cycles can be formed in a mesh network, clockwise and anti-clockwise; those are shown in Figure 2.7. To prevent any deadlock, at least one of the cyclic dependency must be broken. This is done by either creating virtual channels or by restricting the packet movement in a specific dimension/direction.

Figure 2.7 Clockwise and Anti-clockwise dead-lock situations.

#### 2.4.3 Live-locks

In this situation, flits keep travelling through the network in circle without reaching a destination. Because the flits do move instead of being stored in a buffer and not transmitted, as in dead-lock situation, we call it 'live'-lock. Live-locks mainly occur when deterministic routing is not used or flits are allowed to take non-minimal paths to the destination.

#### 2.4.4 Deterministic Routing

The route taken by the packet in reaching from source/sender to sink/destination is pre-determined and known. Each source and sink pair have a unique route which is constant throughout the run time.

2.4.4.1 Dimension ordered routing (X-Y) or (Y-X)

The flit first moves in one dimension and reaches the destination's row or column and then continues to move in other dimension to reach destination. In this type of routing, each router knows where

other routers are and can determine if the flit's destination lies at west, east, south or north of it. An example of X-Y dimension ordered routing is shown in Figure 2.8. Each flit first decides it needs to go east or west to reach the column of destination. Then it travels north or south to reach the row of destination. This way a packet which has travelled north or south, never takes east or west turn. Two turns become illegal to break the dead-lock situation. A packet travelling north/south will never take east turn and a packet travelling north/south will never take a west turn.

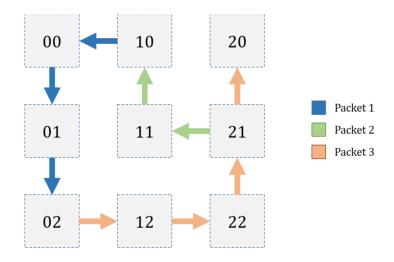

Figure 2.8 X-Y routing mechanism for 3 different source and destination packets.

#### 2.4.4.2 Destination-Tag Routing

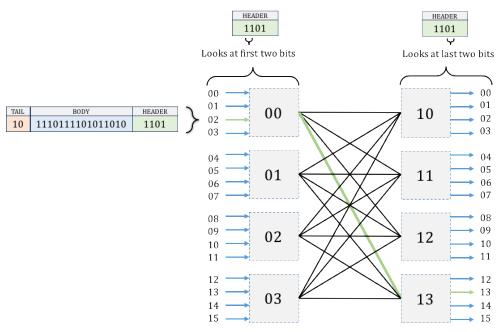

Each packet from the sender/source to the receiver/sink is tagged with a destination address in the header. Based on this tag, the intermediate nodes/routers determine the path packet has to take using the routing table. An example of this type of routing is a 4-ary 2-fly butterfly network shown in Figure 2.9.

Figure 2.9 Routing in 4-ary 2-fly butterfly NoC topology.

#### 2.4.5 Oblivious Routing

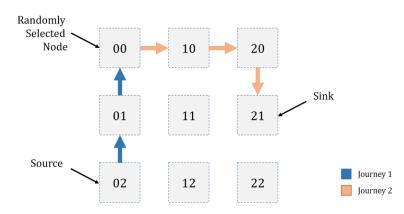

Oblivious literally means being "unaware of". In this type of routing, a packet is routed without regard for the current state of the network. If a packet is to be send from A to B, another node is chosen at random by the sender A and the packet is sent first to this randomly chosen node. Then this node forwards the packet to node B. The Figure 2.10 shows the process of oblivious routing.

Figure 2.10 Oblivious routing mechanism.

This type of routing causes the load on all channels to distribute and spread out toward the network rather than sticking to one side of the network. The advantage of oblivious routing is that the channel loads and traffic patterns are linearly related. Hence it makes it easy to compute ideal throughput and traffic pattern from given channel load. [13]

However, because the source router can select any intermediate router to send the message first to, the traffic is widespread over the whole network. To preserve locality of the network, the intermediate router is chosen from a defined region around the sender with minimal path. This known as minimal oblivious routing.

#### 2.4.6 Adaptive Routing

Adaptive routing algorithms use information about the network in real-time to adapt and change how different packets are routed on the network. The major challenge in adaptive routing is the fact that the route for each packet is decided in real-time just before a packet is sent from one node to another which can cause live-locks. When a router receives a packet, it calculates the path to destination according to the algorithm hardware.

#### 2.4.6.1 Load Balanced Adaptive Routing

The algorithm tries to equalize the traffic load on all the links equally. An example of load balanced adaptive routing is given in [14] where the authors try to balance the load by using Ant Colony Optimization (ACO). ACO is a biologically inspired from ant colonies and how they locate optimal paths by use of pheromones, attractants, and accumulation of paths. They propose a NoC version of ACO which was used extensively in Wide Area Networks and call it Regional ACO-based Cascaded Adaptive Routing (RACO-CAR). This technique eliminates tables which contain redundant information, shares routing tables with neighboring routers and merge information, and cascades routing to distribute the load in the network.

#### 2.4.6.2 Fully Adaptive Routing

This type of routing algorithm adapts to the congestion and blocking in the network and re-routes the packets away from congested or blocked areas. Liu *et al.* propose a fully adaptive routing algorithm called FreeRider [15]. A non-local adaptive congestion aware algorithm where the congestion information of whole network (non-local) is used to make routing decisions. Rather than using the Congestion Propagation Network (CPN) to propagate congestion information, but instead they propose to use free bits in header flit to carry congestion information. This improves the throughput, shortens the latency, and reduces the power consumption.

#### 2.4.6.3 Minimal Adaptive Routing

Minimal route searching algorithms look for the shortest/minimal path to the destination before sending each packet. Since it is a type of adaptive routing, this algorithm looks for congestion and prefers another route if it is of same hop distance. However, NIUs have to take care of out-of-order arrival of flits.

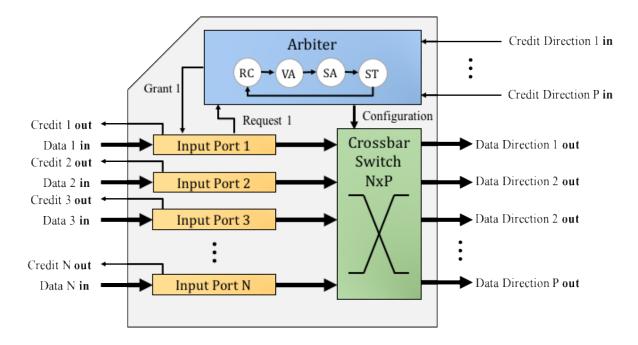

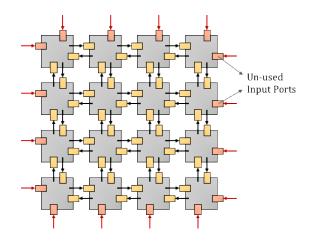

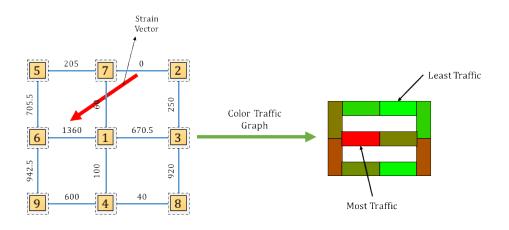

#### 2.5 NoC router micro-architecture

A typical NoC router is composed of input ports, output ports, an arbiter, and a switch [16] shown in Figure 2.11. Minimum delay of the data path determines a maximum data frequency of the router. An arbiter delay dominates among the other critical path delays and determines the maximum frequency of the router ( $F_{max}$ ) [2]. When designing a router, minimization of latency while meeting bandwidth requirements is of utmost importance. Extensive amount of work has already been done in developing power and area efficient designs of arbiters, crossbars, and input ports [7, 4, 3, 2, 17, 5, 6, 16]. NoC router buffers are expensive in terms of power and area and constitute as fundamental variable in NoC optimization [18]. Oveis-Gharan and Khan have extensively compared existing router architectures with special focus on their EDVC organization [2]. We propose an algorithm to determine the optimal router components which results in an optimal performance NoC with lower area and power costs.

Figure 2.11 NoC router micro-architecture.

#### 2.5.1 Crossbar

Crossbar switch is an asynchronous combinatorial logic sub-component of the router which has multiple input buses and output buses. It allows any input bus to be connected to at most one output bus. This enables data to traverse through the crossbar to any output bus. To control which input bus is connected to which output bus, an input configuration bus is used. Crossbar is made up of many de-multiplexers (demux), where each demux is connected at the input to one of the input port of the crossbar, at the output to all router outputs, and the mux selection port is connected to configuration port from arbiter. If multicast crossbars are used, data from 1 input port can stream to multiple output ports. However, tri-state buffers need to be added to solve fan-out problem. In this work, we will only consider crossbars and NoCs without multi-cast feature.

#### 2.5.2 Input port

This is the major component in the router since it consumes majority of the power and takes up majority of the chip area. Input port is essentially composed of a FIFO (no Virtual Channel) or multiple FIFOs and multiplexers (in case of >1 Virtual Channels). A D-Flip flop (primary 1-bit storage element) is made up multiple NAND and OR gates. While designing large storage elements, several flip-flops are

arranged in an array and some fabrication fail components are added. Some of these components include flip-flop scanners to identify faulty flip-flops, and some design fuses to disconnect failed components permanently. Since 32 flip-flop are required to store 1 32-bit word, SRAM has large power consumption and takes up large chip area.

Since FIFOs is a type of buffer and are essentially made up of D-flip flops, it is crucial to manage their size and organization to save chip area and power. Number of flits a FIFO can store is known as its depth. The router can have one pool of memory for all input ports, or each input port can have one pool of memory for each virtual channel. In each case, the depth/share of each input port or virtual channel can be static or dynamic.

#### 2.5.3 Arbiter

Arbiter stores and decides the configuration to set for the crossbar. It manages flit requests coming from the input ports and grants them as per the arbitration scheme. Arbiter contains the main brains and logic for entire router. Arbitration scheme can be static (decided during design) or dynamic (decided as per congestion/traffic during run-time). It makes the output port status 'free' as soon as the tail flit traverses and makes its status 'occupied' before the header flit traverses through the crossbar. In this work, we will consider several fixed priority arbiters and use their synthesis libraries.

# 2.6 NoC Mapping

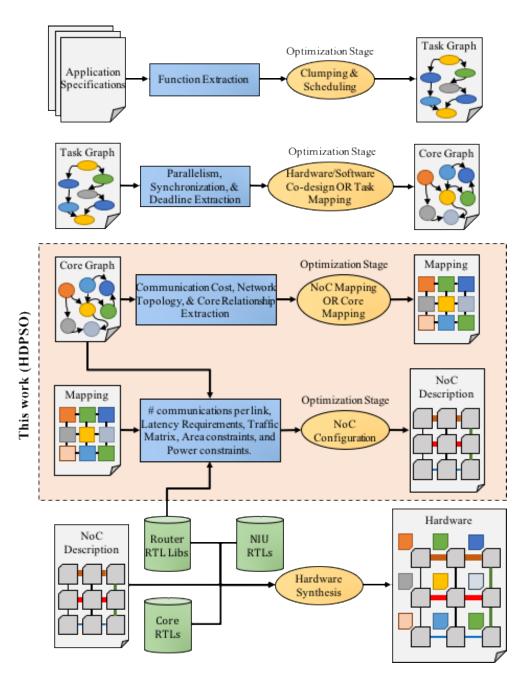

While designing any embedded system with top-down approach, the application is first broken down into tasks and their data dependencies. This is represented in the form of Task Graph (TG). Task graph is a Directed Acyclic Graph (DAG) in which nodes represent tasks and edges represent the data dependency and execution sequence. Tasks are grouped and assigned to hardware execution blocks such as CPU, DMA, GPU, co-processor, Accelerator etc. This is called Task assignment or task mapping shown as second optimization stage in Figure 2.12. This problem falls under Hardware-Software Co-design domain where the designer is still deciding on which task to execute on hardware and which task to execute using software (ie. CPU/co-processor). In this work, we are not addressing task mapping problem. We will be addressing core mapping and configuration problem shown as 3<sup>rd</sup> and 4<sup>th</sup> optimization stage in Figure 2.12 NoC design workflow and this work's targeted workflow.

Figure 2.12 NoC design workflow and this work's targeted workflow.

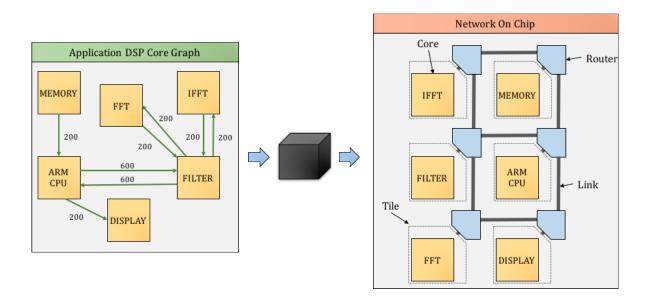

After tasks are mapped onto hardware execution blocks/SIPs, the result is an Application Core Graph (ACG). An ACG is a DAG which contains hardware execution blocks/SIPs/Cores as nodes and their communication information in the form of edges connecting from one node to another. Assigning SIPs to locations (tiles) in a network topology is known as core mapping. Henceforth, we will be referring to core mapping problem as mapping problem. We define the NoC mapping as conversion of Application Core-

Graph (ACG) to a 2D-mesh NoC m(x, y). The NoC mapping CAD tool determines a mapping m(x, y) such that the overall NoC communication cost and energy are minimal. A mapping tool is efficient if it produces a minimum communication cost and energy NoC mapping solution with minimum number of iterations consuming least amount of compute time.

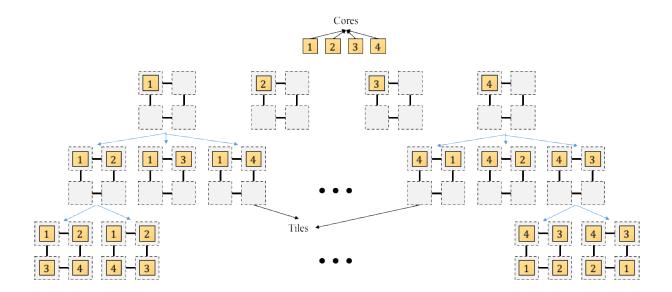

NoC mapping solutions are combinations/arrangements of cores in an order which corresponds to the tiles of a topology. Mapping IP blocks or cores onto a NoC topology becomes complex (Figure 2.13), as the size of NoC (search space) grows factorially with increase in the number of cores and topology tiles. This is shown for a small application which contains 4 cores to map which results in  $4! = 4 \times 3 \times 2 \times 1 = 24$  possible mapping solutions out of which only one is optimal. The formula for size of the search space is given below:

Size of Search Space =

$$n!$$

(1)

where n is total number of cores in an application

Figure 2.13 Mapping possibilities for a 2 by 2 mesh NoC with 4 cores.

Application mapping for 2D-mesh NoC is often considered as a constrained quadratic assignment problem of NP-hard complexity [19, 20, 21]. This means that the problem is not solvable in real time but it is verifiable in polynomial time. In other words, given a solution, we can check wether it is a good one or not but we cannot come up with a optimal solution within polynomial time. For example, we cannot directly

come up with a best core mapping for a large application in short time. However, if someone provides a core mapping to check, we can easily check its cost. These kind of problems are best solved using stochastic algorithms which try and check many promising solutions before reaching a final solution.

Mapping is one of the major steps in NoC design where the cores are positioned onto topology nodes. It is crucial to choose an optimal mapping that results in minimal latency and energy consumption while maximizing the NoC bandwidth. A black box analogy of NoC mapping tool is shown in Figure 2.14.

Figure 2.14 Black box analogy of NoC mapping tool.

#### 2.6.1 State-of-the-Art Mapping tools

#### 2.6.1.1 Deterministic Techniques

Jiang *et al.* have proposed to use a tree based branch-and-bound search technique to find all the combinations of possible solutions for a hybrid switched network [22]. During the execution of algorithm, each link in the hybrid network is permutated either to be circuit or packet switched. Finally, the best switching technique for each link is found. For deterministic algorithms, time to reach an optimal solution increases factorially with the solution space. Their methodology also consumes more time as compared to NMAP [23], NormalBB [21], and DPSO [24] techniques. Another popular deterministic technique is Mixed Integer Linear Program (MILP), which depends on iterations of linear equations of integers to solve the

optimization problem. Bender has proposed an MILP model which determines optimal mapping based on execution time, processor cost, and communication cost [25].

#### 2.6.1.2 Stochastic Techniques

Among the multi-dimensional or large search space evolutionary algorithms, the Genetic Algorithm (GA) is an interesting alternative to produce near-optimal solutions. Morgan *et al.* have used GA to optimize NoC mapping with a complex cost function involving power, chip-area, latency, and reliability [20]. GA based optimization techniques are compared extensively with other popular optimization techniques by Sahu and Chattopadhyay [26] and found that GA algorithm is not suitable for NoC mapping solution space since it converges using a single point rather than two or three reference points as in particle swarm (ie. local-best and global-best).

Yang *et al.* have presented an accelerated simulated annealing (SA) technique, which initially executes a few iterations in branch-and-bound method to reach a temperature called  $t_k$  and then iterates through the temperatures using traditional SA algorithm [27]. As opposed to other mapping algorithms, their  $t_k$ -SA technique focuses on generating better initial heuristics. However, their algorithm has been applied only to homogeneous NoC cores.

In Tabu Search (TS) techniques, a short-term memory is used to remember the previously visited solution space and put a "Tabu" on them, meaning the algorithm is forbidden to visit that space again. Tino and Khan have employed Tabu search to map application cores to an application specific NoC topology [28]. They intend to optimize power, and performance where the NoC performance is evaluated based on the dynamic factors such as contention. Each time a new solution is generated, it is analyzed by invoking the floor-planner that minimizes the wire length and area along with providing the power consumption. The newly proposed solution is accepted and memorized if it is present in the neighborhood or in the Aspiration list but not in the Tabu list. The algorithm stops as soon as it finds a solution that satisfies the stopping criteria. However, there may be other solutions, which result in lower power and area consumption.

Nedjah *et al.* have proposed a structured representation of the task graph and IP library [29, 30].We use similar XML representations as input to our tool. Task assignment problem, in which tasks are mapped onto IPs, precedes mapping problem. Previous mapping tools first come up with an optimum assignment and then find optimal mapping for it. On the other hand, their technique uses several assignment solutions instead of one to generate several mappings, which allows them to trade-off the design objectives of interest. The cost function is composed of hardware area, execution time (deadline criteria), and power consumption.

In assignment and mapping optimization, they use well-known GA algorithm type NSGA-II, CAFES, and micro-GA to compare the results. microGA worked better in saving the chip area and power up to 80% but at the cost of higher application (tasks) execution time of up to 600%. However, it can explore more search space in less amount of time as compared to NSGA-II.

Particle swarm optimization is a population-based technique inspired by social behavior of a group of animals that was developed in 1995 by Eberhart and Kennedy [8]. Each particle is a candidate solution and new solutions are generated based on the particle's own best-found optimal solution (local best) and swarm's best optimal solution (global best) [24]. Transformation from an old solution to a new solution is known as particle movement. It has more exploitation capabilities and more stable as compared to Genetic Algorithm (GA). This is because in GA, new offspring (current solution) depends just on its parent(s) (previous solution), but in DPSO a new solution depends on its local best and global best. In the beginning of DPSO algorithm, particles spawn in different promising search space regions. As the algorithm iterates or progresses through time, the particle moves in the search space looking for optimal solution. It also remembers its previous best fit positions, while learning from the past experiences of other particles. The quality of a particle is evaluated based on its fitness such as cost. We are proposing an extended formulation for our HDPSO based NoC mapping methodology.

As with all the stochastic optimization techniques, the DPSO might not find the optimal solution as it does not search the entire search space. Probability of catching an optimal solution mainly depends on the initial heuristics that place the search agents (or particles) in the search space. A good heuristic algorithm might place particles in some promising regions of the search space and find an optimal solution early. In most of the applications, DPSO particles spend a large amount of time exploring the regions of space already explored by themselves or by the other particles. This causes the algorithm to waste time and iterations in determining the cost of the same solution again and again.

In the past, there have been many modifications done to the baseline DPSO algorithm to improve or cater to a specific application. On such attempt was done by Li *et al.* [31] where they have proposed an improved particle swarm optimization algorithm which embeds a repulsion operator and local searching operator for each particle to induce swarm diversity and local refinement. This repulsion operator is enhanced and used in our tabu-ed reflection mechanism described in Section 3.3.4. They have used an XY routing mechanism and optimize the NoC for either communication power consumption or communication delay due to link load. However, their algorithm does not perform multi-objective optimization resulting in a solution with optimal communication power and delay. We have adopted a similar formulation for our HDPSO based NoC mapping methodology.

## 2.7 NoC Configuration

In addition to NoC mapping, next major steps in designing NoC include finding paths for the traffic flows while reserving resources across the NoC and determining NoC architectural parameters, such as the data width of the links, buffer sizes used in the router, and frequency of operation [32]. After cores are mapped to their respective nodes in topology, each communication edge in the core graph has to be assigned a physical path (links) with a bandwidth high-enough to support it. Then the resources along these paths are reserved to support edges communicating through them. Resources should be allocated generously to be able to support the collective bandwidth required by the edges communicating along the path, but at the same time to have minimum chip area and power consumption. These conflicting requirements give rise to the configuration optimization of NoC. Since there are many different possibilities (combinations) of architectural parameters that can satisfy a given application bandwidth on a given topology, there is a need to find an optimal solution. On the same lines of NoC mapping, NoC configuration solution space also grows factorially with an increase in the number of cores and library component options available. Therefore, there is a need to employ a stochastic technique to consider promising solutions rather than developing a deterministic methodology.

#### 2.7.1 State-of-the-art NoC Configuration Tools and Work-flows

NoC mapping and configuration are two separate but linked optimization problems, which have an input-output relationship. NoC mapping optimization produces input for the NoC configuration optimization. NoC mapping optimization problem has been exhaustively researched and various optimization techniques have been employed [19, 33, 20, 21, 24, 32].

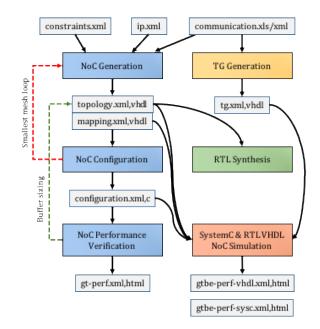

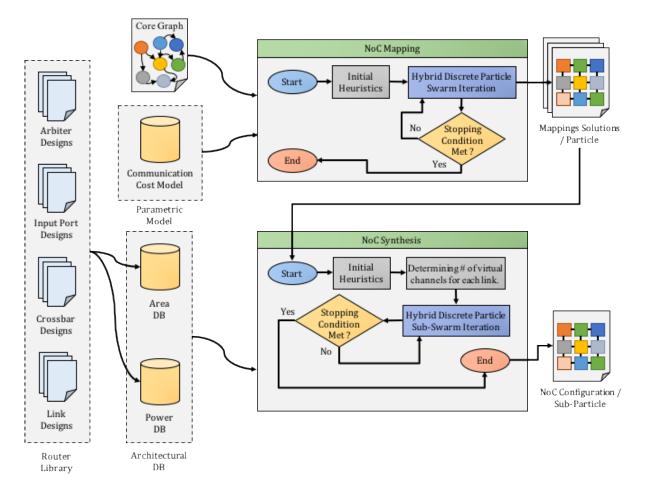

Æthereal design flow for NoC synthesis was proposed by Philips/NXP research along with Goossens et al. [34]. It offers operational design flow to dimension and generate application specific NoC instances and configurations [35]. Æthereal design flow, as shown in Figure 2.15, incorporates two optimization loops, one for NoC mapping and another for NoC configuration. In this design flow, only buffer sizes are optimized. Stergiou *et al.* have proposed another NoC synthesis oriented design library called Xpipes Lite which aids in automatic generation of heterogeneous NoCs [36].

Figure 2.15 Æthereal NoC configuration and mapping workflow.

NoCTweak [37] is a highly parameterized NoC simulator which can simulate some embedded or synthetic traffics including (uniform random, tornado, shuffle, hotspot, etc.) for large network sizes. It combines usage of cycle-accurate SystemC models of routers along with router RTL coded in VHDL and synthesized using 65nm CMOS standard cell library. The simulator reports packet delay, network throughput, average power of router and each of its components, global clock tree and PLL, and energy consumption per packet. However, it does not allow NoC designers to expand the RTL library and provide their own custom router sub-components. The tool can only simulate for 65 nm technology as it was coded using models of 65 nm components.

Another major drawback is that while it does provide energy and power information of the NoC, it does not allocate or configure the routers so that the network occupies minimum chip area and consumes minimum power. Buffer sizes in the tool are modifiable manually when starting the simulator but it modifies the buffer depth for all routers in the network. This homogenous increase in buffer depth help just uniform random traffic but critical power and area savings opportunities are missed if the application does not have a traffic pattern of uniform random. NoCTweak allows custom applications to be imported and simulated, however it only performs mapping of the application using NMAP [23] optimization technique. NMAP is a good stochastic technique but further researches have outperformed it on many fronts [26].

Intelligent buffer merging technique is presented by Tsai *et al.* [38] where each routers input port load is calculated by using a traffic matrix and mapping the coregraph edges onto physical links. This edge-to-link mapping gives rise to a bandwidth constraint which should be satisfied by the input port configuration algorithm. Since they consider adaptive routing mechanism, data from a single source core can arrive from two input ports (two routes) and put into the same buffer. The edge-to-link mapping algorithm is improved and used in our configuration HDPSO algorithm described in section 4.8.1.

# **Chapter 3**

# **Optimal NoC Mapping using HDPSO**

## 3.1 Introduction

PSO [8] is an optimization method that optimizes a problem by first coming up with random solutions and then iteratively improving them by using basic equation of motions (ie. distance, velocity, and acceleration of particles). A candidate solution is called a particle and the all-time best candidate solution is known as global-best particle. Collection of particles which are linked together by common global best-particle is called a swarm.

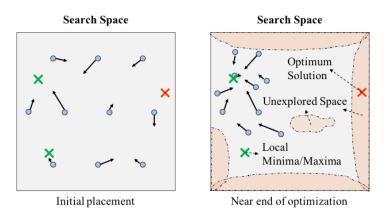

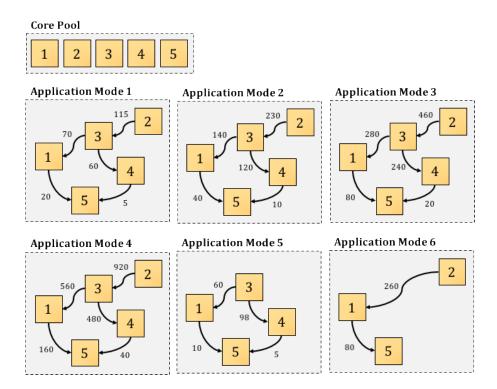

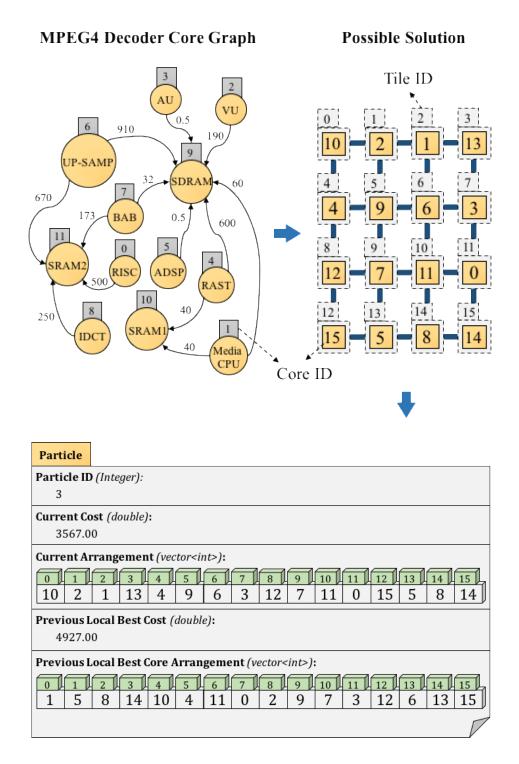

DPSO is used for optimization of a discrete search space. A discrete search space implies that the solution is a combination, a permutation or a quantized quantity. For NoC mapping, the search space represents all the combinations of cores mapped to different tiles. Therefore, DPSO can be used to find the optimal mapping of cores to a suitable size 2D-mesh NoC. Traditionally, DPSO for NoC mapping starts with an initial population (particle) generated through some heuristic method to predict promising regions of the search space. Then the iterations cause the particle to evaluate its current cost and swarm the best global cost. The operation of a typical DPSO mechanism is shown in Figure 3.1.

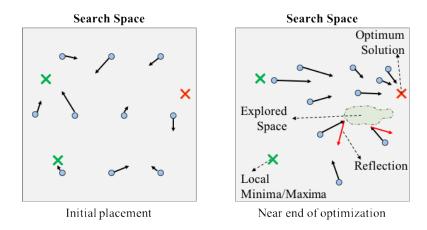

Figure 3.1 DPSO Search spaces - particles reach sub-optimal solutions

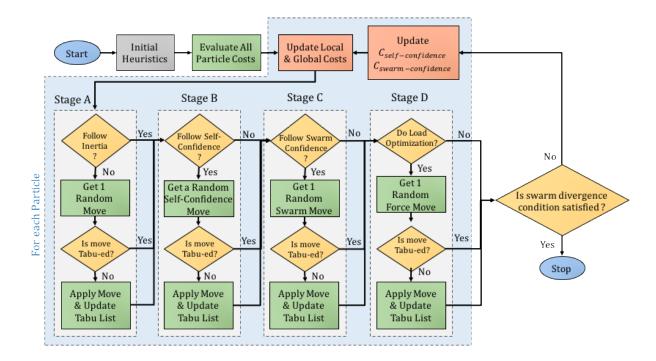

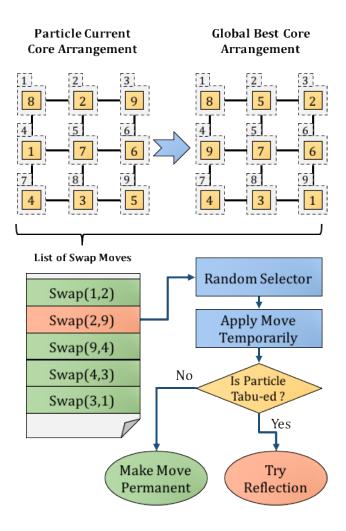

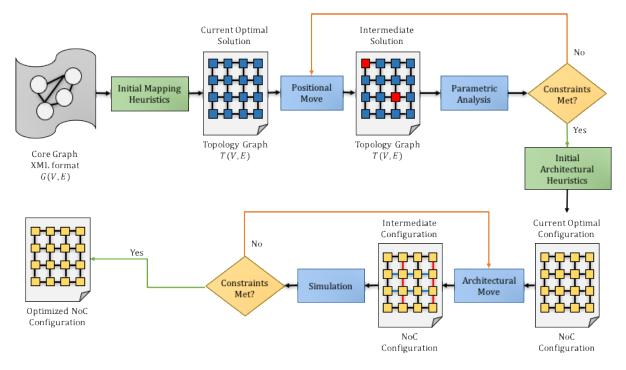

A major issue with the DPSO based methodology is the particles that waste the computing resources and time while staying in the previously explored solution space rather than exploring the unchartered solution space. We propose a hybrid discrete particle swarm optimization methodology that overcomes this shortcoming. In our mechanism, we add the concept of Tabu-search to discourage the particles (or search agents) to pass through the solution space that has been already explored. The overall detail of our methodology having four stages is presented in Figure 3.2.

Figure 3.2 HDPSO Algorithm.

In each iteration, a particle's new position is calculated based on three of particle's own properties and one global swarm property. Consider the position of the particle at iteration k i.e.  $p_k = \langle p_{k1}, p_{k2}, p_{k3}...p_{kn} \rangle$  where  $p_{kn}$  represents a tile and n indicates the tile number. The iterative formulation for the HDPSO particle is given in the following equation:

$$p_{k+1} = \begin{pmatrix} C_{inertia} \times I \\ \oplus \\ C_{self-confidence} \times (p_k \to local_{best}) \\ \oplus \\ C_{swarm-confidence} \times (p_k \to global_{best}) \\ \oplus \\ C_{load-opt} \times (p_k \to load_{optimized}) \end{pmatrix} \times p_k$$

$$(2)$$

where  $p_{k+1}$  and  $p_k$  represent next generation and current particle core arrangements respectively

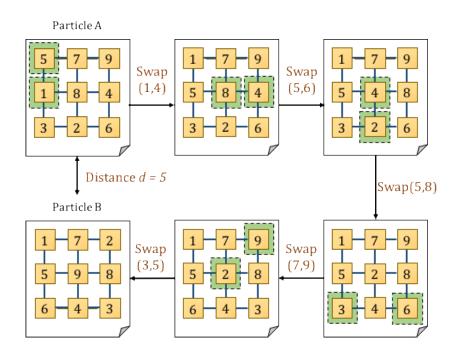

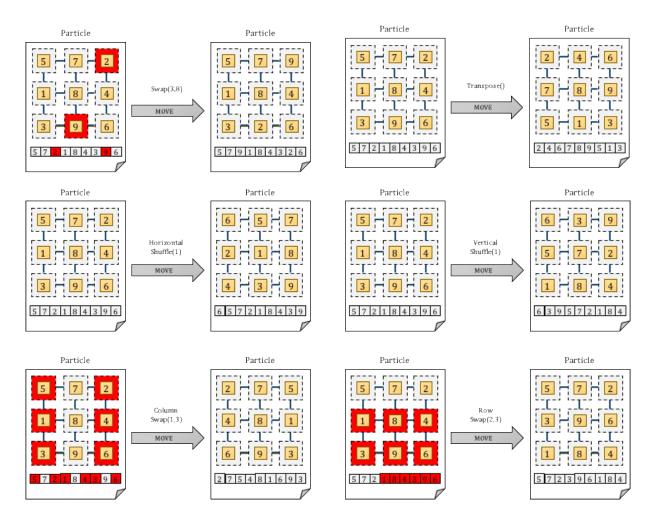

$a \rightarrow b$  is a sequence of swaps applied on components of *a* to transform it to *b* (see Figure 3.5)

$\oplus$  is a fusion operator. For two sequences *a* and *b*. *a*  $\oplus$  *b* is the sequence in which the sequence of swap of *a* is followed by sequence of swaps of *b*

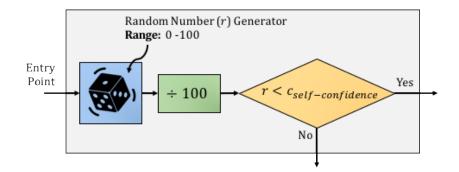

$C_{inertia}$  is inertia constant that determines the particle's willingness to stay at the current solution or move on to another solution