# A SPECIAL HIGH-FREQUENCY SOFT-SWITCHED DC/DC POWER SUPPLY FOR GCT GATE DRIVER

by

Jahangir Afsharian

Bachelor of Engineering, Ryerson University, Canada, 2005

#### A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

**Master of Applied Science**

in the Program of

**Electrical and Computer Engineering**

Toronto, Ontario, Canada, 2009 ©(Jahangir Afsharian ) 2009

PROPERTY OF RYERSON UNIVERSITY LIBRARY

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholar research.

### A Special High-Frequency Soft-Switched DC/DC Power Supply for GCT Gate Driver

#### **Master of Applied Science**

2009

#### Jahangir Afsharian

#### **Electrical and Computer Engineering**

**Ryerson University, Canada**

## ABSTRACT

This thesis is devoted to the development of a novel parallel isolated power supply (PIPS) for the gate driver of integrated Gate Commutated Thyristors (GCT). The proposed PIPS is essentially a special high frequency soft switched DC/DC converter, integrating six parallel isolated power supplies in one module where each power supply generates a regulated dc supply for the GCT gate driver. In commercial GCT power supplies, a high-voltage isolation transformer is indispensable but highly inefficient in terms of cost and size, which can be significantly improved by the optimized transformer. In all, this design strives to achieve a general power supply for powering up the gate drivers of all types of GCT devices in all MV applications with minimal changes in configuration.

In this thesis, the configuration of PIPS is presented and its operating principle is elaborated. The transformer optimization procedure satisfying the voltage isolation requirement for GCT gate drivers is extensively discussed. The performance of PIPS, including the front end DC/DC converter, zero voltage switching phase-shift full bridge (ZVS-PS-FB) converter, and the optimization of the transformer, is verified by simulations and experiments where a 360W laboratory prototype is built for the experimental use.

iv

## ACKNOWLEDGEMENTS

Dedicated to the memory of my father, who gave me life and showed me the key to success.

I would like to express my deep gratitude to my supervisor, Professor Bin Wu, for his foremost support and help during my graduate studies at Ryerson University. His valuable advice and guidance has greatly enhanced my academic knowledge, scientific inspiration and practical skills.

I am grateful to all fellow students, especially Mr. Ahmad Yafaovi, at LEDAR for their useful discussions on my research. My appreciation also goes to Dr. Navid Zargari, Mr. Vijay Khatri and Mr. Angelo Bortolus for their guidance on experiments at Rockwell Automation Canada.

Finally, I wish to share my achievements with my family, and to especially thank my mother and twin sister for their endless love and support.

v

# **TABLE OF CONTENTS**

| CHAPTER 1 INTRODUCTION                                                      | 1  |

|-----------------------------------------------------------------------------|----|

| 1.1 Existing Power Supplies for GCT Gate Drivers                            | 4  |

| 1.1.1 Commercial Power Supply for GCT Gate Drivers                          | 4  |

| 1.1.2 Self-Powered Supply (SPS) for GCT Gate Drivers in MV-CSR Applications | 5  |

| 1.2 DC/DC Converter for The Proposed Power Supply                           | 7  |

| 1.2.1 Circuit Topologies                                                    | 8  |

| 1.2.2 DC/DC Efficiency Improvement                                          | 9  |

| 1.2.3 Higher Switching Frequency                                            | 9  |

| 1.2.4 Soft Switching Techniques                                             | 10 |

| 1.3 Motivation and Objectives                                               | 12 |

| 1.3.1 Contributions                                                         | 13 |

| 1.3.2 Objectives                                                            | 13 |

| 1.4 Thesis Organization                                                     | 15 |

|                                                                             |    |

| CHAPTER 2 PRINCIPLE OF PARALLEL ISOLATED POWER SUPPLY FOR GCT GATE DRIVER   | 17 |

| 2.1 Introduction                                                            | 17 |

| 2.2 Technical Requirements and Configuration of the Proposed PIPS           | 18 |

| 2.2.1 Technical Requirements                                                | 18 |

| 2.2.2 PIPS Configuration                                                    | 19 |

| 2.2.3 Converter 1 for The Supply of Power with High Voltage Isolation       | 22 |

| 2.2.4 Cost and Size of High Voltage Isolation Level Transformer             | 28 |

| 2.2.5 Optimization Procedure for the Transformer Design                     | 29 |

| 2.2.6 Converter 2 for Regulated DC Output Voltage                           | 35 |

| 2.3 Summary and Discussion                                                  | 37 |

|                                                                             |    |

| CHAPTER 3 COMPONENTS SELECTION AND EFFICIENCY OPTIMIZATION FOR PIPS         | 39 |

| 3.1 PIPS PSPICE Mode                                                        | 39 |

| 3.1.1 Modeling of Current Sense Transformer                                 | 41 |

| 3.1.2 Verifying Circuit Design Parameters for MOSFET Gate Driver            | 42 |

| 3.2 Simulation for Key Component Selection                                  | 45 |

| 3.2.1 Simulation Waveforms for Phase-Shift Operation Using UCC3895          | 45 |

| 3.2.2 The Maximum Input Voltage of Converter 2 at No-Load                   | 47 |

| 3.2.3 Simulation for Output Diode and Power MOSFET Selection                | 48 |

| 3.3 Simulation for Maximum Efficiency Fulfillment with Optimized Transformers |    |

|-------------------------------------------------------------------------------|----|

| 3.3.1 Loss Analysis of Converter1 Operating at 3 Different Frequencies        | 51 |

| 3.3.2 State of ZVS for Switching Loss Reduction                               | 53 |

| 3.4 Summary                                                                   | 56 |

|                                                                               |    |

| CHAPTER 4 HARDWARE IMPLEMENTATION AND VERIFICATION                            |    |

| 4.1 PIPS Prototype                                                            |    |

| 4.2 Experiments on PIPS                                                       |    |

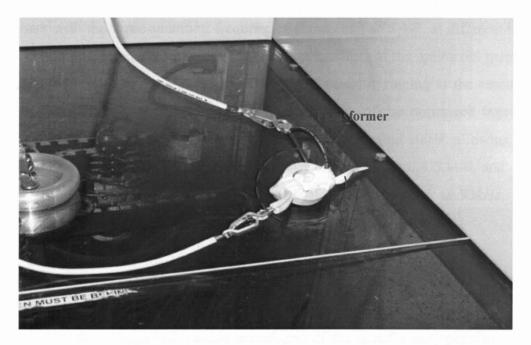

| 4.2.1 Experimental Verification of Transformer Optimization                   | 61 |

| 4.2.2 High Pot and Corona Testing on Optimized Transformers                   |    |

| 4.2.3 Overall Performance of Optimized Transformers on Converter 1            |    |

| 4.2.4 Output Voltage Regulation with Different Load Conditions                |    |

| 4.3 Overall Efficiency of PIPS                                                |    |

| 4.3.1 ZVS Design                                                              |    |

| 4.4 Summary and Discussion                                                    |    |

|                                                                               |    |

| CHAPTER 5 CONCLUSION                                                          |    |

| 5.1 Summary                                                                   |    |

| 5.2 Contributions                                                             |    |

| 5.3 Future Work                                                               |    |

|                                                                               |    |

| APPENDIX                                                                      |    |

| A. Experimental Results on Toroidal Transformer                               |    |

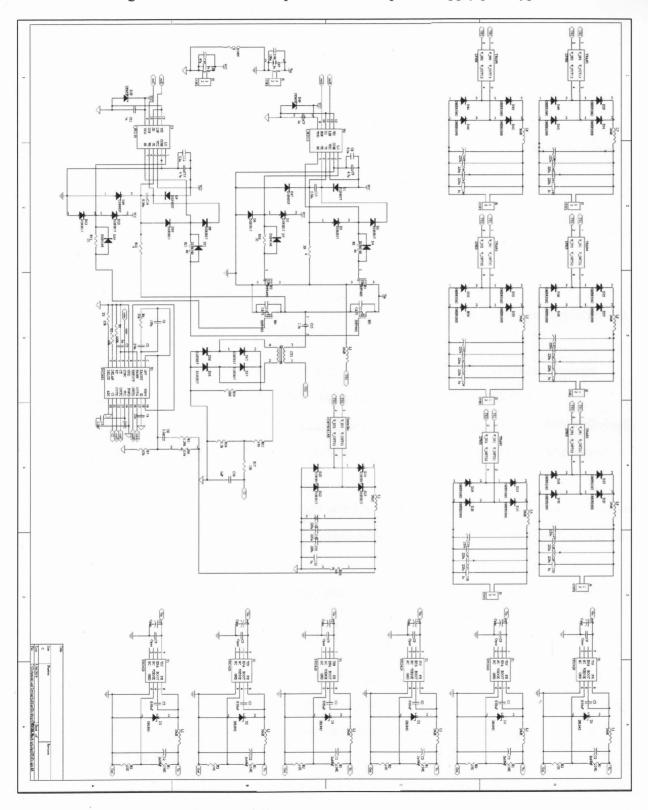

| B. Schematic of the PIPS Prototype                                            |    |

| •                                                                             |    |

|                                                                               |    |

| FERENCES |

|----------|

|----------|

## **LIST OF TABLES**

| Table 2-1 | Core material characteristics                                       | 30 |

|-----------|---------------------------------------------------------------------|----|

| Table 2-2 | Specifications of three different toroidal cores                    | 32 |

| Table 2-3 | High voltage isolation wire                                         | 35 |

|           |                                                                     |    |

| Table 3-1 | Specifications of bootstrap components for IR2110                   | 44 |

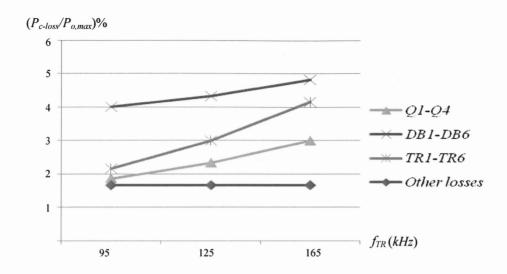

| Table 3-2 | The total power losses breakdown at different operating frequencies | 51 |

|           |                                                                     |    |

| Table 4-1 | Parameters of Converter 1.                                          | 60 |

| Table 4-2 | Parameters of Converter 2.                                          | 61 |

| Table 4-3 | Experimental results for transformer optimization                   | 62 |

|           |                                                                     |    |

# **LIST OF FIGURES**

| Fig. 1-1  | GCT block diagram.                                                            | 2  |

|-----------|-------------------------------------------------------------------------------|----|

| Fig. 1-2  | A typical 4160-V CSI drive with a PWM rectifier and inverter.                 | 2  |

| Fig. 1-3  | PWM current source rectifier (CSR)                                            | 3  |

| Fig. 1-4  | Block diagram of the commercial gate driver power supply for GCT devices.     | 5  |

| Fig. 1-5  | Circuit diagram of the self-powered supply for GCT gate drivers               | 6  |

| Fig. 1-6  | Simplified block diagram of the proposed power supply for 6 GCT gate drivers. | 8  |

|           |                                                                               |    |

| Fig. 2-1  | Block diagram of the parallel isolated power supply for GCT gate drivers      |    |

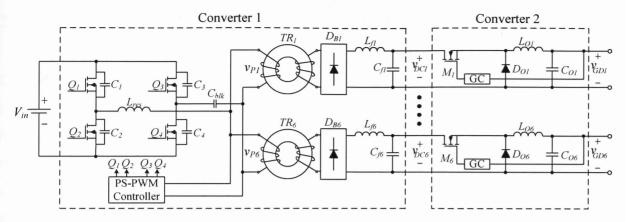

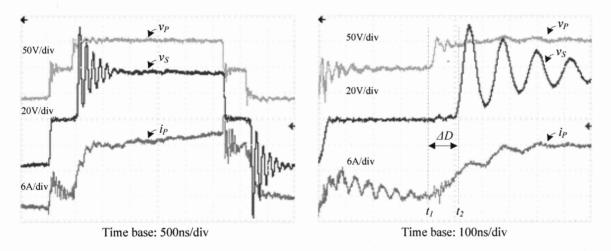

| Fig. 2-2  | Circuit diagram of the parallel isolated power supply for GCT gate drivers    | 21 |

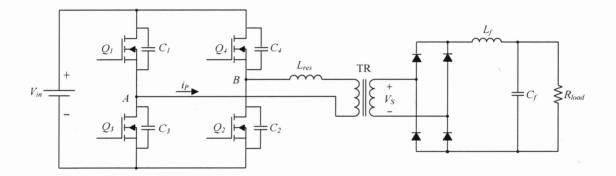

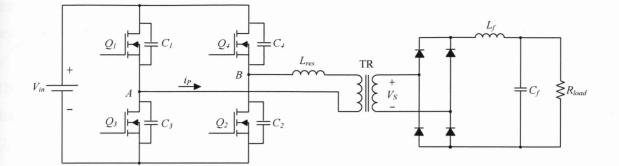

| Fig. 2-3  | Phase shifted FB-PWM converter.                                               | 23 |

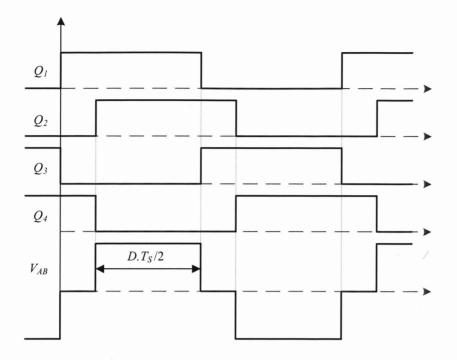

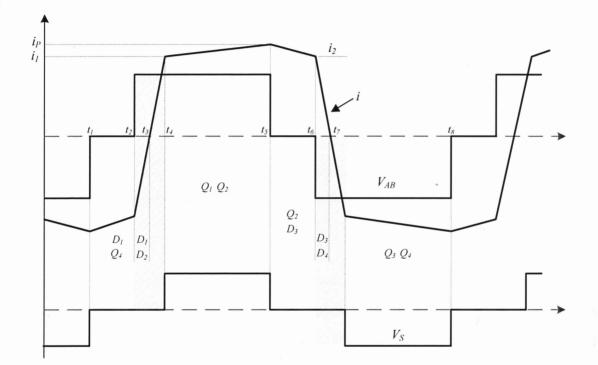

| Fig. 2-4  | Principle of operation of phase shifted FB-PWM converter.                     | 25 |

| Fig. 2-5  | Dimension of the toroidal core                                                | 31 |

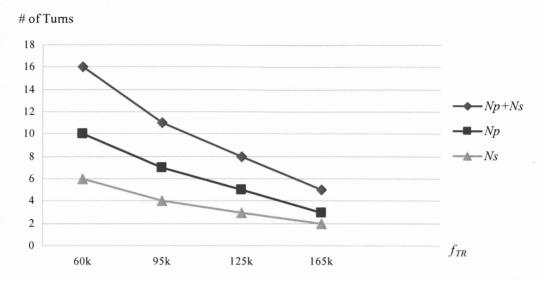

| Fig. 2-6  | Number of primary and secondary turns vs. operating frequency                 | 34 |

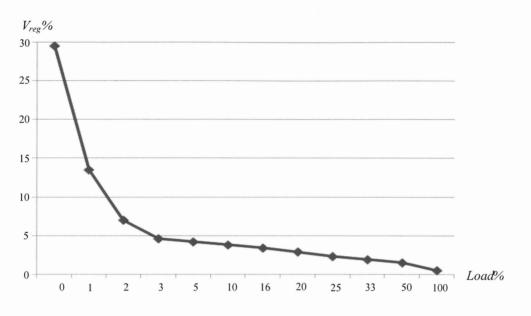

| Fig. 2-7  | Voltage regulation of Converter 1 without Converter 2.                        |    |

| Fig. 2-8  | Simplified schematic of DC/DC step-down converter.                            |    |

|           |                                                                               |    |

| Fig. 3-1  | Simulation model for six parallel isolated power supplies (PIPS).             | 40 |

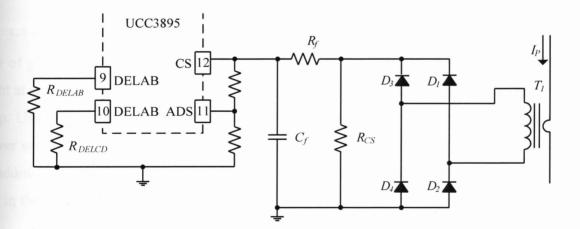

| Fig. 3-2  | Modeling of current sensing transformer with delay circuit.                   | 41 |

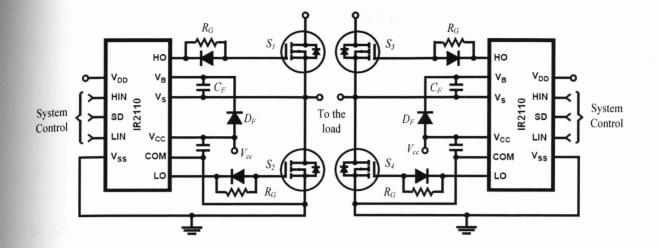

| Fig. 3-3  | The modeling of MOSFET gate driver circuit.                                   | 43 |

| Fig. 3-4  | Voltage simulation waveforms of MOSFET gate driver using IR2110               | 44 |

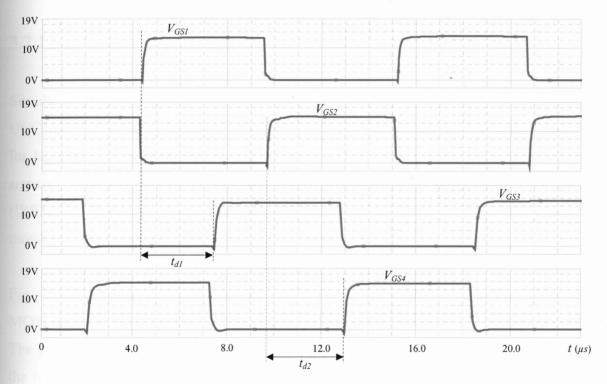

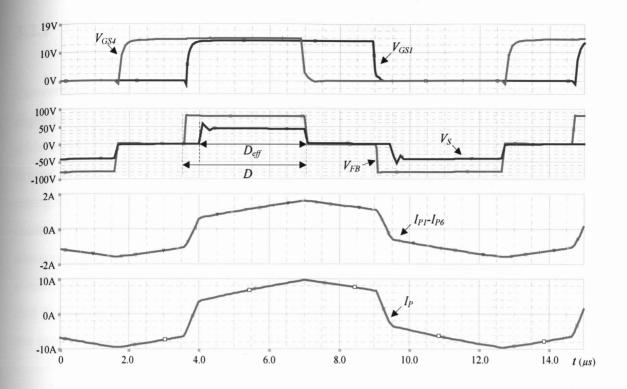

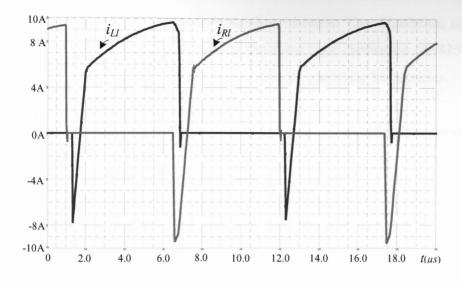

| Fig. 3-5  | Simulation waveforms for phase-shifting operation.                            | 46 |

| Fig. 3-6  | Simulation waveforms for maximum input voltage of DC/DC converter             | 47 |

| Fig. 3-7  | Simulation waveforms for maximum voltage rating of output diodes              | 49 |

| Fig. 3-8  | Simulation waveforms for maximum current rating of power MOSFETs.             | 50 |

| Fig. 3-9  | Ratio of component loss to maximum output power vs. operating frequency.      | 52 |

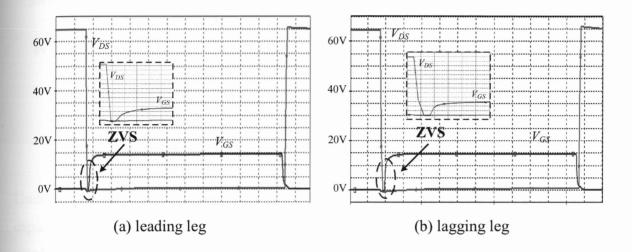

| Fig. 3-10 | 2VS operation at full-load for (a) leading leg (b) lagging leg                | 54 |

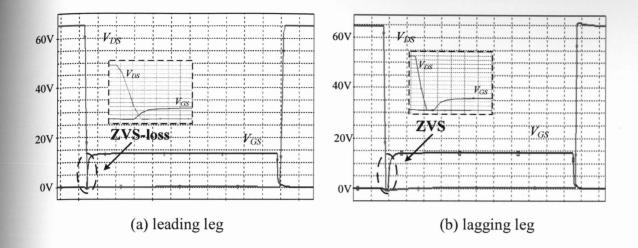

| Fig. 3-11 | ZVS operation at 25% of full-load for (a) leading leg (b) lagging leg         | 55 |

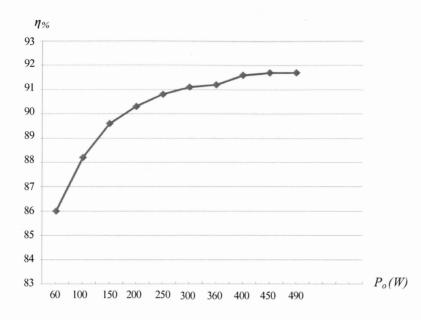

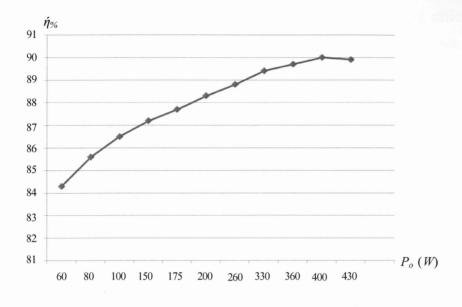

| Fig. 3-12 | 2 Efficiency curve of Converter 1                                             | 56 |

|           |                                                                               |    |

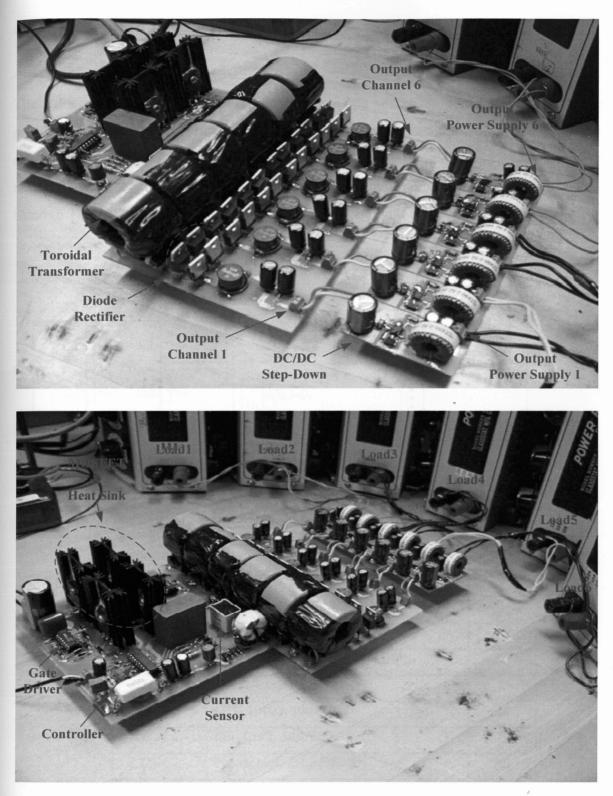

| Fig. 4-1  | Prototype of Parallel Isolated Power Supply (PIPS).                           | 59 |

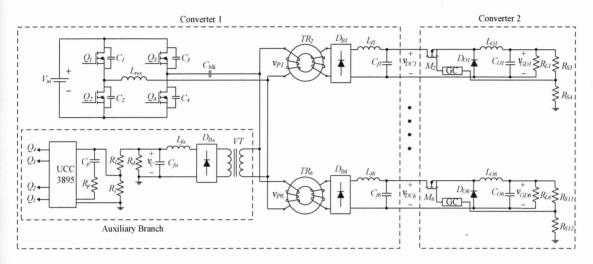

| Fig. 4-2  | Simplified PIPS circuit diagram                                               | 60 |

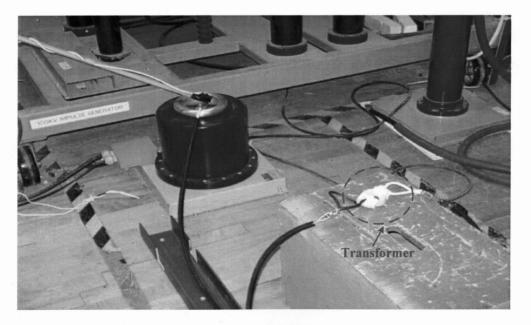

| Fig. 4-3  | Hi Pot testing on optimized transformers at 37kV/60Hz.                        | 62 |

| Fig. 4-4  | Corona testing on optimized transformers at $12kV/60Hz$                         | 3 |

|-----------|---------------------------------------------------------------------------------|---|

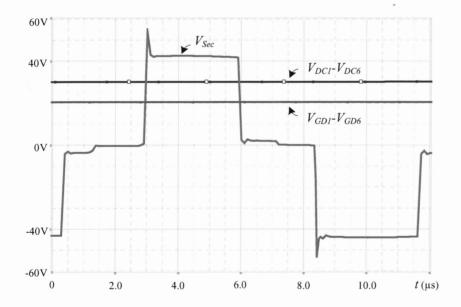

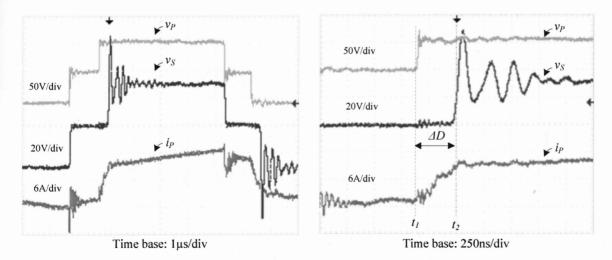

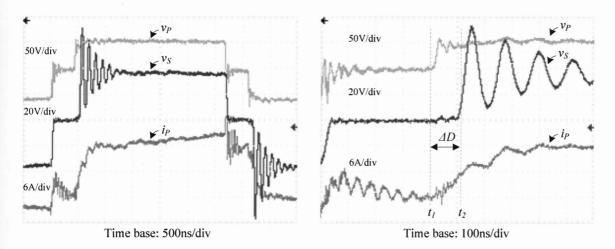

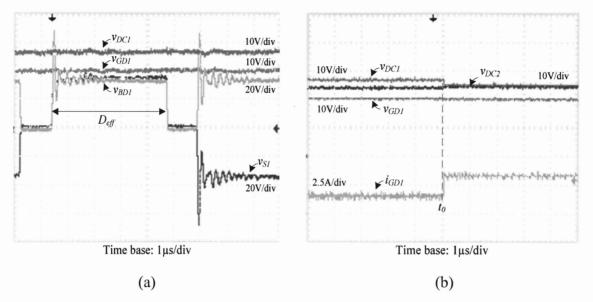

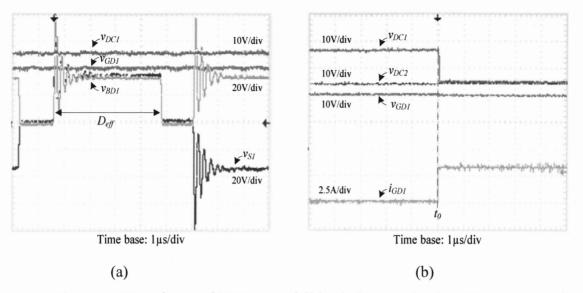

| Fig. 4-5  | Voltage and current waveforms of optimized transformer operating at 95kHz       | 4 |

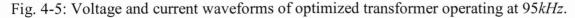

| Fig. 4-6  | Voltage and current waveforms of optimized transformer operating at 125KHz      | 5 |

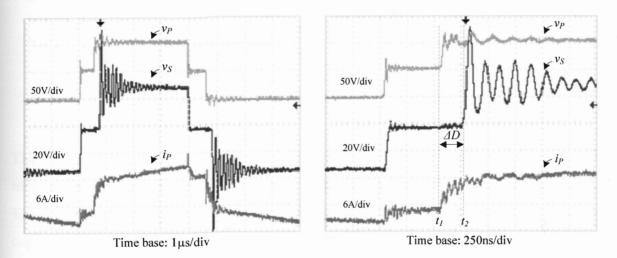

| Fig. 4-7  | Voltage and current waveforms of optimized transformer operating at 165kHz      | 6 |

|           | Circuit diagram of PIPS for GCT gate drivers                                    |   |

|           | Waveforms of PIPS (a) at no load; (b) at no load to 50% of full-load            |   |

|           | ) Waveforms of PIPS (a) at 50% of full-load; (b) at no load to 50% of full-load |   |

| Fig. 4-11 | Waveforms of PIPS (a) at full load; (b) at no load to full-load                 | 0 |

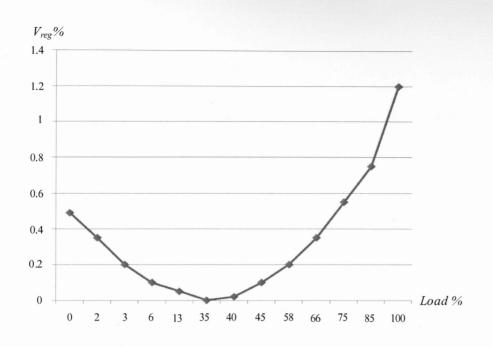

| Fig. 4-12 | 2 Experimental voltage regulation of one of the six power supplies              | 1 |

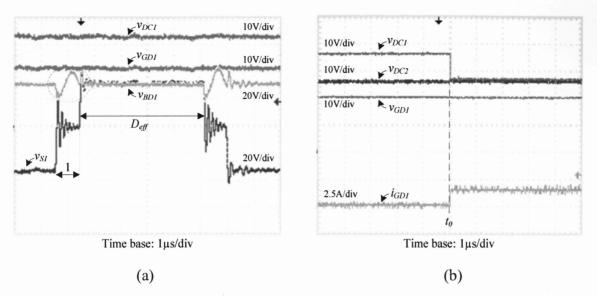

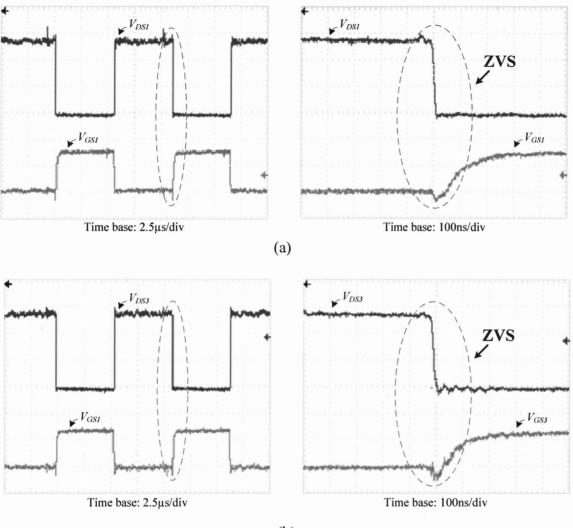

| Fig. 4-13 | 3 Experimental waveforms of ZVS (a) leading-leg; (b) lagging-leg                | 6 |

| Fig. 4-14 | Efficiency curve of Converter 1                                                 | 7 |

х

я

## **CHAPTER 1: INTRODUCTION**

High power converters with power rating from 0.4MW to 40MW at the medium voltage level of 2.3KV to 13.8KV are widely adopted in industry. Applications of these converters can be found in medium voltage (MV) drives, static reactive compensators (STATCOM), and dynamic voltage restorers (DVR) [1-2]. In high power converters, high power Insulated Gate Bipolar Transistors (IGBTs) and integrated Gate Commutated Thyristors (GCTs) have been broadly used since late 1990s. These new generation switching devices become very popular in the main areas of high-power electronics due to their superior switching characteristics, reduced power losses, and ease of gate control. Currently, the voltage and current rating of IGBT devices can reach 6.6kV/0.6KA or 1.7KV/3.6KA, while the ratings of GCTs can be up to 6KV/6KA, indicating that GCTs are more suitable for higher power applications.

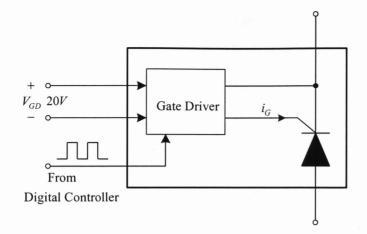

The GCT device is essentially a high power GTO (Gate Turn Off) integrated with a specially designed gate driver [3]. The gate driver has an extremely low gate inductance, which leads to great improvement on the GCT turn-off capability over conventional GTOs. There are two types of GCTs, namely, symmetrical GCT and asymmetrical GCT. The symmetrical GCT is mainly used for current source converters. Fig. 1-1 shows the block diagram of a GCT device. The gate driver, which is normally powered by a 20V dc supply, converts the gate signals generated by the digital controller into required GCT gating currents. Asymmetrical GCT gate drivers are generally employed in voltage source converters where the reverse voltage-blocking capability is not required [4-6]. The power supply input for the asymmetrical GCT will be different, since the voltage operation of gate drivers for these two types of GCTs differs. In order to simplify the control interface and reduce the system cost, a rectifier and voltage regulator are further integrated in the gate driver board. It allows the direct connection to an isolation transformer with an ac square-wave output voltage ranging from 28V to 40V (15kHz to 100kHz) [6]. It is also possible to supply the gate unit with dc voltage.

1

Fig. 1-1: GCT block diagram.

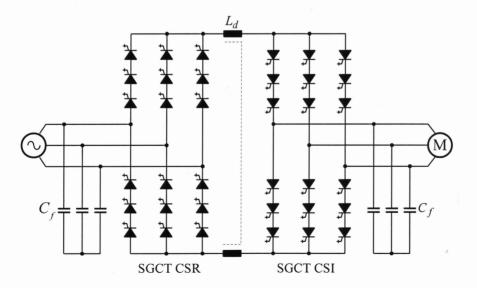

Fig. 1-2 illustrates a CSI drive using a single-bridge PWM current source rectifier (CSR) as a front end, where 36 GCT devices are employed. The rectifier and inverter have an identical topology using symmetrical GCTs. With the GCT voltage rating of 6000V and two GCTs connected in series in each of the converter branches, the drive is capable of operating at the utility voltage of 4160V (line-to-line). For higher operating voltages, the number of series connected devices can be increased while the converter topology remains unchanged. For example, three GCTs can be in series for the 6600V drives [1]. Typically, the number of GCT devices employed in MV applications is 6, 12, 24, or 36.

Fig. 1-2: A typical 4160-V CSI drive with a PWM rectifier and inverter.

2

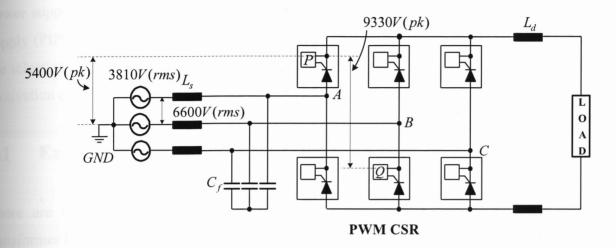

Fig. 1-3 displays the topology of GCT-based Current Source Rectifiers (CSR) commonly used in medium voltage drives as a front-end converter [7]. The line inductance  $L_s$  and filter capacitor  $C_f$  form a low pass filter to attenuate harmonics generated by the CSR. The dc choke  $L_d$  is used to smooth the dc current.

Fig. 1-3: PWM current source rectifier (CSR).

Since the gate driver is connected to the cathode and the gate of the GCT device, the gate driver and its power supply are at the same potential of the GCT. For example, in a 6600V system, the voltage of gate driver P with respect to ground GND is 5400V(peak), and the voltage between gate driver P and gate driver Q is 9330V(peak). As a result, high voltage isolation for the power supply is required.

To fulfill the isolation requirement, separate power supplies insulated by isolation transformers are adopted for GCT gate drivers. These isolation transformers are quite expensive and bulky, which causes an increase in the manufacturing cost and physical volume of the power converters.

In order to decrease the system cost and power supply size for the GCT gate driver, self-powered supply (SPS) techniques are proposed in the literature. SPS seems to be the ideal solution where the energy from the power converter or snubber circuits of the switching devices is used to power the GCT gate drivers such that the isolation transformers can be eliminated for system cost reduction. However, SPS bears a major drawback which is the limited application in

medium voltage MV-CSR converters. It motivates us to seek for a general solution for the power supply in GCT gate driver applications.

In what follows, a review on the existing power supply technologies is provided, including the pros and cons of each technology in GCT gate driver applications. The absence of a general power supply for GCT gate drives indicates the need for the proposed parallel isolated power supply (PIPS), which overcomes the drawbacks of the existing power supplies. Discussions on the selection of DC/DC converter for the proposed PIPS are the focus of Section 1.2. Finally, the motivation and objectives, and the organization of this thesis are presented.

## **1.1 Existing Power Supplies for GCT Gate Drivers**

There are two types of power supplies for GCT gate drivers, the commercial isolation transformer based power supplies and the self-powered supplies. In this section, these two types of power supplies are introduced, discussed, and compared.

### 1.1.1 Commercial Power Supply for GCT Gate Drivers

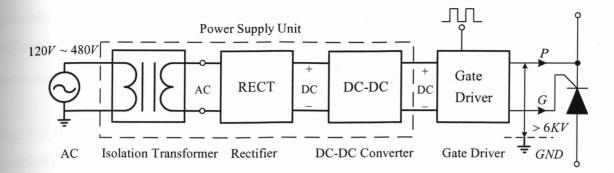

A commercial power supply for a switching device gate driver is normally composed of an isolation transformer, a rectifier, and a dc-dc converter. Fig. 1-4 depicts the typical block diagram of this type of power. Depending on GCT's current capability, the power rating of the GCT gate driver is normally in the range of 10W to 60W. The isolation transformer converts a utility ac to a lower ac voltage, which is then converted into a dc voltage by the rectifier. This dc voltage may vary with the utility voltage and/or the load conditions, and thus it is further stabilized to power the gate driver by a dc-dc converter.

4

Fig. 1-4: Block diagram of the commercial gate driver power supply for GCT devices.

Another important function of the isolation transformer is to provide isolation between utility power supply and the gate driver. Since the voltage between the switching device and the ground of the utility power supply can be a few thousands volts in MV applications, the isolation transformer must be specially designed and manufactured. Hence the cost of such a transformer is high and its physical size is large.

#### 1.1.2 Self-Powered Supply (SPS) for GCT Gate Drivers

To reduce the cost and volume of gate driver supplies, several self-powered supply (SPS) techniques were proposed in the literature for SCR, GTO and GCT [8-13]. The purpose of these techniques is to utilize the energy from power circuits or snubber circuits to power the gate drivers, instead of using energy transferred from the utility power supply via isolation transformers. As a result, the isolation transformers are avoided and the associated cost and physical occupancy are saved. The discussions in this section are restricted to the SPS technique for GCT devices since the scope of this thesis is the design of power supply for GCT gate drivers.

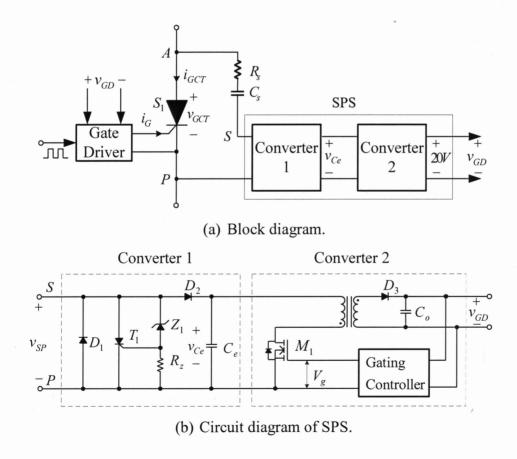

The block diagram of the proposed self-powered supply for GCT gate driver in medium voltage current source rectifier (MV-CSR) is shown in Fig. 1-5 (a). The supply consists of two converters: Converter 1 and Converter 2. The main functions of Converter 1 are to transfer the energy from the snubber capacitor  $C_s$  to the energy-storage capacitor  $C_e$  and to minimize

possible interference to the snubber circuit operation. Converter 2 converts the unregulated dc voltage  $v_{Ce}$  to a regulated dc voltage  $v_{GD}$  for the GCT gate driver, and also provides insulation between the snubber circuit and the gate driver.

Fig. 1-5 (b) illustrates a circuit diagram of the proposed SPS [13]. When a positive voltage is established between the terminals S and P, a current flows through diode  $D_2$  to charge the energy storage capacitor  $C_e$ . Once  $v_{Ce}$  reaches its maximum value  $V_{max}$ , set by the zener diode  $Z_1$ , the diode  $Z_1$  will breakdown and conduct, causing thyristor  $T_1$  to conduct. The current from S to P is thus diverted from  $C_e$  to  $T_1$ . In this case, diode  $D_2$  is reverse-biased, preventing  $C_e$  from discharging through  $T_1$ . When the voltage between S and P becomes negative, the diode  $D_1$  will conduct, providing a current path for the snubber circuit. Moreover, in order to minimize the impact of the SPS on the snubber operation,  $C_e$  should be much greater than  $C_s$ .

Converter 2 is essentially a flyback converter, which converts the unregulated dc voltage on  $C_e$  to a regulated dc voltage  $v_{GD}$  for the gate driver. This converter consists of a power MOSFET, a high-frequency transformer and a controller. The transformer produces a step-down voltage and provides the required isolation (hundreds of volts) between the RC snubber circuit and the GCT gate driver. Based on the output feedback, the duty cycle of the MOSFET is controlled, so that the dc output voltage of the converter  $v_{GD}$  is regulated at 20V.

This scheme features a regulated dc supply for the GCT gate drivers in MV-CSR applications. However, there are several drawbacks associated with the SPS design. One drawback is that the SPS for GCT gate driver can only be used for CSR in MV applications. Another limitation is that the SPS has small impact on the operation of the snubber since SPS is in series with snubber. In addition, the mounting of SPS for GCT gate drivers in CSR is difficult. It is therefore concluded that SPS is not an ideal candidate for GCT gate driver power supply.

The above drawbacks of the existing power supplies for GCT gate drivers motivate us to develop a general power supply to power all types of GCT devices (symmetrical and asymmetrical) in all MV applications such as CSI, CSR, VSI, etc. The proposed power supply supports six GCT devices in one module as depicted in Fig. 1-3. To accomplish this design, an appropriate isolated DC/DC converter should be chosen to reduce the cost and size for system preservation, and meet the voltage isolation requirement for GCT devices. In Section 1.2, the key aspects of DC/DC converter are investigated and the most desirable isolated DC/DC converter for the proposed power supply is discussed.

## **1.2 DC/DC Converter for The Proposed Power Supply**

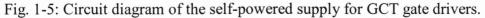

DC/DC Converter design tends to be a process of making tradeoffs between converter size, cost, and performance. This procedure motivates and guides the designer towards choosing a suitable type of converter. Since six power supplies are placed in one unit in the proposed design, an effective and efficient DC/DC converter design is indispensable. A simplified block diagram of the proposed power supply is drawn in Fig. 1-6. It is important to keep the front end DC/DC

converter operating at high switching frequency and high efficiency, so that the transformer with high voltage isolation requirement for GCT devices can be optimized and all six power supplies can be place in one module.

Fig. 1-6: Simplified block diagram of the proposed power supply for 6 GCT gate drivers.

At higher switching frequency, the size of the required magnetic components may be decreased, leading to the reduction in raw material costs along with the converter bearing less physical volume. These factors render the proposed power supply a highly economical solution particularly from the viewpoint of the whole-system conservation.

### 1.2.1 Circuit Topologies

It is of paramount importance to minimize the cost of components, by choosing a reasonable isolated DC/DC converter topology for proposed power supply. There are many high frequency topologies for isolated DC/DC converters such as push pull, forward, flyback, half-bridge, full-bridge [14], [15]. After comparing all these topologies, full-bridge is selected as the most appropriate topology for the parallel isolated power supply. For one thing, full-bridge is capable of handling higher power, and the supply isolation between the input and output of the GCT gate drivers is superior with respect to other topologies for this application. The main transformers of full-bridge can operate under full symmetry of volt-seconds, which eliminates the saturation of

the transformer and greatly reduces the size of the transformers [15]. For another, full-bridge topology can easily achieve zero voltage switching (ZVS) controlled by a phase-shift controller, resulting in an increase in the efficiency and reliability. Therefore, the full-bridge topology is chosen as the optimal isolated DC/DC converter for the proposed power supply. The transformer optimization for high voltage isolation for GCT gate drivers is rendered easier by the converter operating in full-bridge topology.

#### **1.2.2 DC/DC Efficiency Improvement**

Improving the efficiency, reliability and flexibility of the DC/DC power converter while maintaining or decreasing cost, may provide a solution to the general conservation goal. There exist many design principles that may be adapted for use in achieving this goal. Operating a converter using a constant switching frequency allows the magnetic components and the filter design to be optimized, resulting in increased the overall efficiency and decreased size of these components [14-16]. Efficiency in a power system may also be improved by ensuring that the switching duty cycle operates the closest possible to 50%, which reduces the stress on components within the system. In [17], a duty cycle significantly less then 50% was linked to decreased efficiency and poor transient response performance in comparison to operating at 50% duty cycle. A small duty cycle also limits switching frequency in a power conditioning system since malfunction can happen due to the extremely short conduction times [18]. One concept that can be beneficial for enhancing efficiency in power system design is operating at a higher switching frequency. This diminishes the cost and size of the power converter while improving the reliability and efficiency of the system, although these benefits can be voided if effects of increased frequency-dependent losses, switching losses, output capacitance losses and gate losses are not counteracted.

#### **1.2.3 Higher Switching Frequency**

It is well documented that converters designed with higher switching frequencies can reduce the size and weight of transformers and filter components together with improving transient response

[15]. At a higher switching frequency, smaller size of the magnetic components may give rise to lower raw material costs and less volumed converter. These factors can potentially improve the economics of power electronics applications in terms of system conservation.

Although higher switching frequency leads to benefits such as cost and reliability, these benefits can quickly be voided by the decrease in efficiency due to increased switching. Obviously, high switching frequencies result in increased switching losses responsible for nullifying the aforementioned advantages of the higher switching frequency. To realize the benefits of a high switching frequency, switching losses must be eliminated and a common and effective approach for achieving this involves the implementation of Zero Voltage Switching (ZVS) [16], [17], [18]. ZVS is a technique that removes switching losses by ensuring that the switch voltage is roughly zero during the switch transition. The employment of ZVS technique produces higher efficiency through the removal of switching losses, allowing all the benefits of higher switching frequency to be realized. In the next section, a brief survey is presented to explain the choice of ZVS as the soft switching technique for the proposed power supply.

### 1.2.4 Soft Switching Techniques

The main trend in achieving higher power density for switched mode power supplies is the increase in switching frequency. Hard-switched converters cannot operate above an upper frequency due to switching losses. This upper frequency is about 70-80*kHz* for MOSFETs and about 20-30*kHz* for IGBTs if power ratings of several kilowatts are considered [19]. The switching losses in DC/DC converters can be reduced by using snubbers, quasi-resonant or fully resonant circuits, or soft-switching circuits [20]. Soft switching is preferred because of the following advantages: 1) simpler control circuits, 2) simpler power circuit, 3) simpler analysis, 4) better exploitation of the power transistors and rectifier diodes, 5) high efficiency, and 6) low EMI. At power levels high enough to justify the use of four controlled switches, probably the best choice is the full bridge soft-switching forward converter [21-25], which is controlled by phase-shifted (four state) PWM. The soft switching PWM converter is defined as the combination of converter topologies and switching strategies that result in zero-voltage and/or zero-current switching in. This type of soft switching converter has been referred to by different

names in the literature, such as pseudo-resonant, quasi-resonant, resonant transition, clamped voltage topologies and so forth. In these converters, the resonant transition is employed merely for a short switching interval. The output voltage is usually controlled by PWM with constant switching frequency.

Soft switching PWM converters can be classified as follows: 1) ZCS (Zero Current Switching) PWM converters, 2) ZVS ZCS PWM converters, and 3) ZVS (Zero Voltage Switching) PWM converters. The ZCS PWM converters can be derived from the ZVS PWM converters by applying the duality principle. These converters are attractive for applications with high output voltage, e.g., power factor correction circuits, where the rectifiers suffer from severe reverse recovery problems when conventional PWM, ZVS-QRC, or ZVS-PWM converter techniques are used. The efficiency of the converter drops significantly at low line and heavy load since the switches begin to lose zero current switching. The zero-voltage zero-current switching (ZVZCS) PWM converters are derived from the full-bridge phase shifted zero-voltage (FB-PS-ZVS) PWM converters. The PS-ZVS PWM converter is often used in many applications in that this topology permits all switching devices to operate under zero-voltage switching by using circuit parasitic such a transformer leakage inductance and devices junction capacitance. However, due to phaseshifted PWM control, the converter has a disadvantage that circulating current flows through a transformer and switching devices during freewheeling intervals. The ZVZCS DC/DC PWM converter can operate very well at nominal load, but is not capable of operating over wide load range (from no-load conditions to short circuit) with zero-voltage or zero-current switching for all power switches. Auxiliary circuits are needed in order to achieve soft switching at no-load conditions and at short circuit. The ZVS PWM converter is controlled by the phase-shifted PWM technique. To solve the problems of conventional pulse width modulated (PWM) dc-dc converters, several high-frequency (HF) isolated soft-switching (including resonant) converters have been developed in the past [22, 24], [26-29]. These converters have reduced size, weight, and cost. Variable-frequency control used in resonant converters suffers from several disadvantages.

To overcome these problems, fixed-frequency resonant and soft-switching PWM converters emerged as an active area of research [22, 24], [26-29]. Among these converters, the most

popular configuration is the ZVS phase-shifted bridge converter. The ZVS PWM converter exhibits low primary-side switching loss and generated EMI. Furthermore, the ZVS technique can be used to increase the converter efficiency. For instance, at high-power levels, the full-bridge (FB) ZVS phase shift DC/DC converter has been an attractive choice, since it provides high-power density with high efficiency and low electromagnetic interference [20, 21, 23, 24]. Besides the constant frequency operation with linear output characteristics, it integrates the stray elements (junction capacitances and leakage inductance). In addition, this converter incorporates the advantages of low-conduction losses present in hard switching technology, as well as small-switching losses provided by soft-switching technology [20, 21]. As mentioned above, compared to other topologies such as ZCS-PWM and ZVS ZCS-PWM, ZVS-PWM is the most appealing and desirable soft switching technique. With ZVS, the converter can achieve a switching frequency of up to several kilo-Hertz, which is an attractive feature and ideal property for the design and implementation of the proposed power supply.

### **1.3** Motivation and Objectives

Based on the previous discussions, the motivation and objectives of this thesis are addressed in this section. Recall from Fig. 1-3 that the minimum number of GCT devices in medium voltage current source inverter (CSI) or medium voltage current source rectifier (CSR) is six. Each GCT device normally requires a specially designed power supply for its gate driver. Moreover, the commercial GCT power supplies are quite expensive and bulky since they have to provide an electrical isolation of a few thousand volts through a high-voltage isolation transformer. To reduce the cost and size of the power supplies for GCT gate drivers, self-powered supply (SPS) without isolation transformers are proposed in the literature. However, the SPS design for GCT gate drivers is restricted to Current Source Rectifier (CSR) in MV applications and cannot be adopted for GCTs in other converter topologies. Furthermore, the SPS-produced small impact on the operation of the snubber circuit of medium voltage converter is undesirable.

## **1.3.1** Contributions

This thesis is dedicated to the development of a general power supply with low cost, compact size, and high efficiency, for all MV applications where the GCT gate driver is indispensable. Based on the extensive literature survey on the existing power supply for all high power semiconductor switches (SCR, GTO, IGBT, ETO, and GCT) [8-13], the proposed PIPS is demonstrated to be a unique design where six parallel isolated power supplies with optimized transformers are implemented in one unit to supply six GCT devices with high voltage isolation level requirement. To be elaborative, the proposed power supply is designed to feature a high frequency soft switched DC/DC converter, which can deliver the maximum power at high efficiency giving rise to high power density and compact size. As a result, the cost of the major components such as high voltage isolation transformers, filters, and heat sink can be avoided. In addition, operating at high switching frequency and high efficiency results in less complex optimization for the transformer and lower cost attributed to the employment of ferrite transformers. Simulations and experiments will be leveraged to indicate the practicality and effectiveness of the proposed PIPS for the GCT gate driver. Detailed potential contributions to addressing the challenges in the PIPS design are discussed in the following section.

#### 1.3.2 Objectives

This thesis aims to present a simple, general, and cost-effective power supply for six GCT devices (symmetrical and asymmetrical) employed in MV applications. The potential contributions or main objectives of this thesis thus lie in the design and implementation of PIPS, which are achieved by providing solutions to the following challenges and difficulties:

1. Need for general power supply in GCT gate driver applications—It may not be difficult to come up with a design specifically coping with the issues present in a particular application scenario, where the issues will have limited impact, as in the case of self-powered supply techniques applied in (certain type of) GCT gate drivers. On the other hand, it would be much more challenging, if not impossible, to invent a generally-applicable technique which must deal with all possible issues in a wider range of applications and the potentially broader impact of these issues. As the main goal and mission of this thesis, the

proposed parallel isolated power supply strives to address the challenge of designing such a general technique for all MV applications where the GCT gate driver is indispensable.

- 2. High power required for GCT power supply—Depending on the GCT current rating, the power required for GCT power gating is usually around 60*W*. There are 6 GCT devices in the CSI or CSR for MV applications and the power supply module with 6 parallel isolated power supplies requires 360*W* output power.

- 3. Transformer optimization for high voltage isolation level between input and output of the power supply—The most important issue in designing the proposed power supply is the transformer design optimization. Since the power supply will be adopted in applications where high voltage isolation level is required, the transformer need be capable of producing an isolation level of up to several kilovolts, while bearing low cost and small size.

- 4. Regulated output voltage—Most of the GCT devices require a stable output voltage of 20V with a maximum error of  $\pm 0.5V$ . Therefore, the output voltage of each isolated power supply in the proposed PIPS should be controlled with desirable voltage regulation.

- **5. Reduced cost and size**—The cost and size of a commercial product are the key elements in attracting wide industrial adoptions, which directly determine the success and usefulness of such product. The proposed power supply is by no means an exception. In the proposed PIPS, it is important to minimize the cost of the components such as transformers, output filters, and heat sinks, by choosing a high frequency and high efficiency isolated DC/DC converter topology for high voltage isolation transformers, the difficulty of which is exaggerated when six parallel isolated power supplies are placed in one unit.

- 6. High efficiency and high frequency operation—As mentioned in Section 1.2.2, high switching frequency introduces many desirable features to the converter but also results in increased switching losses as the byproduct. To fully realize the benefits of high switching frequency, one of which being the increased efficiency of the converter, switching losses must be eliminated or suppressed to an acceptable level. A common and effective approach

for achieving this involves the implementation of Zero Voltage Switching (ZVS), the employment of which can potentially produce the required efficiency for the converter through the removal of the byproduct.

7. Simulation and experiments—To facilitate the analysis and design of the proposed PIPS, a suitable and comprehensive simulation model for the proposed PIPS should be developed. In addition to the simulations, experiments must be extensively conducted to verify the simulation results and the performance of the proposed power supply for GCT gate drivers, through building and testing the prototype of the power supply.

## 1.4 Thesis Organization

This thesis consists of five chapters. The background information pertinent to comprehending the proposed parallel isolated power supply is presented in this chapter, including the introduction of the GCT device, the review on the existing power supply techniques for GCT gate drivers, and the brief survey on the topologies and techniques for the DC/DC converter. According to the review and survey, clear choices on the power supply technique, the converter topology, and the switching technique are stated. The main objectives of the thesis are defined, with associated challenges and difficulties identified and discussed.

In Chapter 2, the proposed novel parallel isolated power supply (PIPS) for GCT gate drivers is introduced. The operating principle of the PIPS circuit is elaborated. Theoretical analysis and design guide for PIPS is also provided. Furthermore, the detailed optimization procedure for the design of the high voltage isolation transformer is presented.

Chapter 3 focuses on the modeling and analysis of the proposed power supply. The performance of PIPS is then investigated through simulations, which verify the key component selection and the maximum achievable efficiency with the optimized transformers, and assist in the calculation of total power losses.

Chapter 4 provides experimental evaluation of the proposed PIPS. A laboratory prototype is designed and built to test the performance of the proposed power supply. Extensive experiments on the optimized transformers with different core sizes are then conducted. Detailed discussions on the experimental results, comprising observations and their indications, are also included in this chapter.

Finally, Chapter 5 concludes this thesis. A summary of the results are presented, along with a review of the contributions and possible suggestions for future work.

## CHAPTER 2: PRINCIPLE OF PARALLEL ISOLATED POWER SUPPLY (PIPS) FOR GCT GATE DRIVER

This chapter starts with an introduction to the novel isolated power supply for GCT gate drivers, followed by detailed discussions on its operating principle. The design requirements for the proposed supply are also elaborated. In addition, the optimization procedure for high voltage isolation level transformers required for GCT gate drivers is presented.

## **2.1 Introduction**

Due to the limitations of the aforementioned approaches introduced in Chapter 1 and the special gating requirements for GCT devices, none of the existing solutions in the literature can be readily employed for GCT gate unit supply under all different MV converter topologies (not only CSR) [8-13]. In order to reduce the cost of main components (such as high voltage isolation transformers), compact size, and simple circuit implementation, a novel parallel isolated power supply (PIPS) for GCT gate drivers, is therefore proposed and described in this chapter. The design features a general power supply for GCT devices used in different converter topologies where high voltage insulation level is required, e.g., Medium Voltage Neutral Point Clamped or PWM CSI converters. The proposed power supply is a high frequency soft switched DC/DC converter with 6 parallel high voltage isolation level transformers that operate at 165kHz switching frequency. The proposed PIPS obtains power from a (50V-80V) dc input voltage. Each channel of PIPS regulates a 20Vdc supply to drive the GCT gating circuits at very high voltage isolation level and very high efficiency. Consequently, the expensive and bulky isolation transformers used in commercial power supplies for GCT gate drivers can be eliminated.

## 2.2 Technical Requirements and Configuration of the Proposed PIPS

Parallel Isolated Power Supply (PIPS) was initiated as an effort to reduce the cost on the existing power supply for GCT gate drivers. It is of paramount importance to minimize the cost of components for the proposed power supply, by choosing a reasonable isolated DC/DC converter topology for high voltage isolation transformer. At higher switching frequency, the size of the magnetic components required may be decreased leading to a reduction in raw material costs, along with the converter bearing less physical volume. These factors render the proposed power supply, a highly economical solution particularly from the viewpoint of the whole-system conservation.

### **2.2.1 Technical Requirements**

Each GCT device normally requires a specially designed power supply for its gate driver. Accordingly, the proposed PIPS should meet following requirements.

#### 1. The power required for the GCT gate driver

The GCT power gating is usually around 60W. A major portion of the required energy is transferred to the gate driver during the GCT turn-off. Another portion of the energy is dissipated for turning on the GCT device, including the generation of turn-on pulse and back-porch current. The third portion, around 5W, is the gate driver component dissipation. Obviously, the supply should be designed to fulfill a total power of 360W for 6 GCT gate drivers.

#### 2. Regulated output voltage

Since the load conditions in different switching periods of the gate driver are distinct, and the voltage requirement  $(20\pm0.5V)$  of the power supply for GCT gate drivers is critical, the output voltage of the designed PIPS must be regulated in order to achieve reliable GCT switching.

#### 3. Transformer optimization with high voltage isolation level required for GCT gate driver

The optimization for the high voltage isolation transformer is imperative because the transformer must provide an isolation level of up to several kilovolts for GCT gate drivers, at low cost and small size. Such optimization is achievable by using ferrite core, which is chosen due to its low-cost and low-loss characteristics when used for transformers in the frequency range of 20kHz to 1MHz.

#### 4. High efficiency and high frequency operation

The proposed power supply must operate at high frequency and high efficiency to optimize the transformer. As mentioned in Section 1.2.2, high switching frequency introduces many desirable features to the converter but also results in increased switching losses as the byproduct. To fully realize the benefits of high switching frequency, one of which being the increased efficiency of the converter, switching losses must be eliminated or suppressed to an acceptable level. A common and effective approach for achieving this involves the implementation of Zero Voltage Switching (ZVS), the employment of which can potentially produce the required efficiency for the converter through the removal of the byproduct.

The novel parallel isolated power supply is designed based on the above requirements. The circuit configuration and analysis are given in following sections.

### **2.2.2 PIPS Configuration**

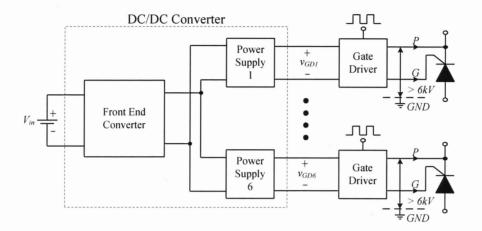

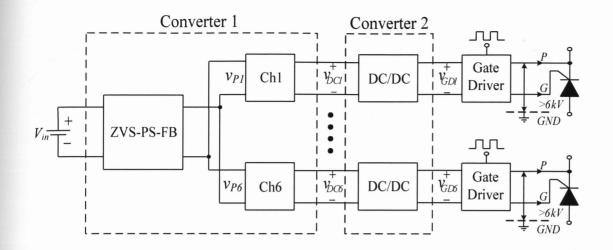

#### 1. PIPS block diagram

The block diagram of the proposed power supply is shown in Fig. 2-1. The supply consists of two converters. Converter 1 consists of main block ZVS-PS-FB (high frequency zero voltage switching phase-shift full-bridge) and six parallel isolated channels (Ch1 to Ch6).

Fig. 2-1: Block diagram of the parallel isolated power supply for GCT gate drivers.

The main function of Converter 1 is to supply rated power for all GCT gate drivers at very high voltage isolation level (a few thousands volts) through a high voltage isolation transformer. In addition, Converter 1 is used to maintain the output dc voltage ( $v_{DC1}$  to  $v_{DC6}$ ) of each channel under wide input dc voltage range  $V_{in}$  not subject to load variation. Since there is no output voltage feedback with respect to the load changes for each channel in Converter 1, Converter 2 is added for output voltage regulation. Converter 2 consists of 6 DC/DC converters. As a result, the output dc voltage of each channel in Converter 1 is regulated to dc voltage ( $v_{GD1}$  to  $v_{GD6}$ ) for the GCT gate driver by the DC/DC functionality of Converter 2.

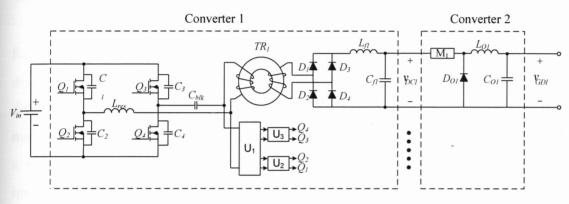

#### 2. PIPS circuit diagram

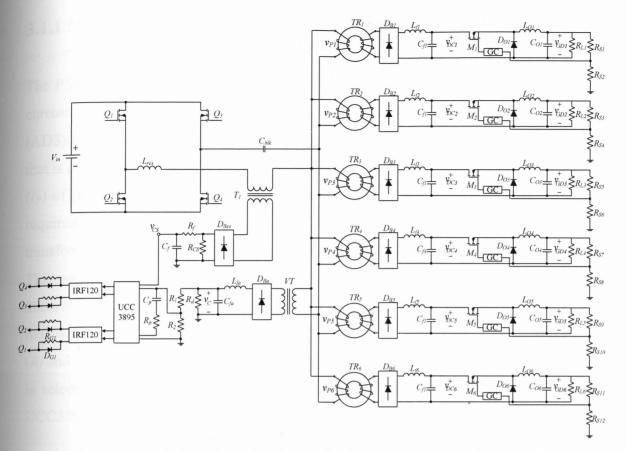

The circuit diagram of the proposed PIPS is drawn in Fig. 2-2. One of the main challenges in the design of PIPS lies in Converter 1, which is essentially a high-frequency zero voltage switching phase-shift full-bridge DC/DC converter.

Fig. 2-2: Circuit diagram of the parallel isolated power supply for GCT gate drivers.

Phase-shift full-bridge generates high frequency quasi-square wave voltage for all its 6 parallel ferrite transformer ( $TR_1$  to  $TR_6$ ) connections, since ferrite transformer operating at high frequency. The circuit of Converter 1 can be further described in detail as follows:

- The gating for the 4 power MOSFETs ( $Q_1$  to  $Q_4$ ) of the ZVS-PS-FB converter is generated by phase-shift PWM (PS-PWM) controller which operates under voltage mode control feedback.

- The resonant inductance  $L_{res}$  (in most case the leakage inductance of transformer) requires operation in Zero Voltage Switching (ZVS) in conjunction with output parasitic capacitances of MOSFET switches ( $C_1$  to  $C_4$ ).

DAEDOUT INITENSIA LIABURI

- A DC blocking capacitor  $C_{blk}$  is used for blocking any DC components of the primary current.

- Six parallel isolated channels (Ch1 to Ch6) each has high frequency ferrite toroidal transformer  $T_{RI}$ , diode bridge  $DB_I$ , filter  $L_{fI}$  and  $C_{fI}$ . The output voltage of each channel ( $v_{DCI}$  to  $v_{DC6}$ ) is regulated with respect to input dc voltage change  $V_{in}$ .

Converter 2 consists of 6 DC/DC step-down buck converters, each of which steps down the putput voltage of one channel of Converter 1 ( $v_{DC1}$  to  $v_{DC6}$ ) to a regulated dc voltage ( $v_{GD1}$  to  $v_{GD6}$ ) for the GCT gate driver. Each DC/DC in converters 2 is integrated with FET and gating controller and has output filters ( $L_{O1}$ ,  $C_{O1}$  to  $L_{O6}$ ,  $C_{O6}$ ). Based on the output feedback for each DC/DC in Converter 2, the duty cycle of the MOSFET is controlled, such that the dc output roltage of each DC/DC converter ( $v_{GD1}$  to  $v_{GD6}$ ) is regulated at 20*V*.

### 2.2.3 Converter 1 for The Supply of Power with High Voltage Isolation

Converter 1 is a high frequency soft switched DC/DC converter which is utilized to supply rated power with an electrical isolation of a few thousand volts for six GCT gate drivers. As mentioned in Chapter 1, there are many advantages of employing ZVS-PS-FB as the isolated converter topology for proposed power supply. The ZVS-PS-FB converter achieves zero switching loss under heavy load conditions at higher switching frequency with a low component count, leading to the high efficiency of the converter.

In addition, operating Converter 1 at high switching frequency and high efficiency facilitates the optimization of the transformer for high voltage isolation, and hence enables the adoption of low-cost and small-sized ferrite transformers and the placement of six isolated power supplies in one module.

Furthermore, ZVS-PS-FB is capable of handling the power rating of more than 1kW. In other words, ZVS-PS-FB can easily supply the required power if it is later on needed to add another group of 6 parallel high voltage isolation level transformers to the proposed PIPS, in one unit, i.e., supplying power for 12 GCT gate drivers. This is the key advantage and functionality of ZVS-PS-FB in reducing the cost of the power supply with minimum number of components.

Besides the aforementioned merits, this section also outlines the operation principle, converter analysis and transformer design for zero voltage switching phase-shift full-bridge (ZVS-PS-FB) converter, followed by detailed optimization procedure for the high voltage isolation level transformer.

#### 1. Principle of operation

In order to reduce the size and the weight of magnetic components, it is desirable to increase the switching frequency for DC-DC converters. When conventional PWM converters operate at high frequencies, the circuit parasitics have negative effects on the converter performance [30]. Switching losses increase in high power applications and snubbers and/or other means of

protection are required, which introduces significant losses and decreases the efficiency. In the case of the conventional full bridge converter, the diagonally opposite switches  $(Q_1 \text{ and } Q_2, \text{ or } Q_3 \text{ and } Q_4)$  are turned on and off simultaneously. In the FB-PWM converter, when all four switches are turned off, the load current freewheels through the rectifier diodes [15]. In this case the energy stored in the leakage inductance of the power transformer causes severe ringing with MOSFET junction capacitances. This creates the need for using snubbers that increase the overall losses bringing down the efficiency. If snubbers are not used, the selection of the devices becomes more difficult as the voltage rating for these switches has to be much higher. As the voltage rating goes up, so do the conduction losses, the overall losses increase and the cost increases as well.

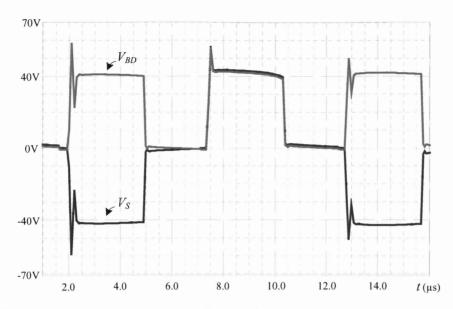

In order to minimize the parasitic ringing, the gate signals of  $Q_2$  and  $Q_4$  are delayed (phase-shifted) with respect to those of  $Q_1$  and  $Q_3$  [17], as shown in Figure 2-3, so that the primary of the transformer is either connected to the input voltage or shorted.

Fig. 2-3: Phase shifted FB-PWM converter.

The leakage inductance current is never interrupted, thus solving the problem of parasitic ringing associated with the conventional full-bridge PWM converter. The energy stored in the leakage inductance can be used to discharge the energy stored in the MOSFET junction capacitances to achieve zero voltage switching (ZVS) conditions for all four switches in the primary side. In this case, the converter requires no additional resonant components.

#### 2. Converter analysis

The zero voltage switching phase-shift full-bridge (ZVS-PS-FB) converter provides ZVS for all four switches in the bridge. However, the mechanism by which ZVS is achieved is different for the two legs of the bridge. For transistors  $Q_2$  and  $Q_4$ , the ZVS is provided by the resonance between the leakage inductance,  $L_{LK}$ , and the output capacitance of the switch.

Fig. 2-4: Principle of operation of phase shifted FB-PWM converter.

The needed energy for achieving ZVS is given by

$$E = \frac{1}{2}L_{LK}I_2^2 \ge \frac{4}{3}C_{mos}V_{in}^2 + \frac{1}{2}C_{TR}V_{in}^2 \quad , \tag{2-1}$$

where  $I_2$  is the current through the primary when  $Q_2$  turns off as shown in Fig. 2-4,  $V_{in}$  is the input voltage, and  $C_{TR}$  is the transformer winding capacitance. The factor 4/3 represents twice the

energy stored in the nonlinear drain to the source capacitor, whose capacitance is inversely proportional to the square root of the voltage [17].

The resonance between  $L_{LK}$ ,  $C_{mos}$ , and  $C_{TR}$  provides a sinusoidal voltage across the capacitances that reaches the maximum at one fourth of the resonant frequency period. The dead time between  $Q_2$  and  $Q_4$  must be set to  $\delta t_{max}$  to ensure that there is sufficient time to charge and discharge the capacitances. The dead time required to ensure ZVS with the maximum possible load range can be determined by the following equation:

$$\delta t_{\max} = \frac{T}{4} = \frac{\pi}{2} \sqrt{L_{LK} C},$$

(2-2)

Where  $C = C_{mos} + C_{TR}$ .

Whether ZVS can be achieved for  $Q_2$  and  $Q_4$  is dependent on the load level of the converter. For light loads, the current though  $L_{LK}$  when  $Q_2$  and  $Q_4$  are turned off may not be enough to turn on the anti-parallel diode.

For switches  $Q_1$  and  $Q_3$ , ZVS is provided by a different mechanism. Before  $Q_1$  is turned off the current in the primary is reaching its peak value. The primary current is the filter inductor current reflected to the primary. When  $Q_1$  is turned off, the energy available for charging the output capacitance of  $Q_1$  and discharging the output capacitance of  $Q_3$  is the energy stored in  $L_{LK}$  and that in the output filter inductor. This energy in the output filter inductor is available because the filter inductor current does not freewheel through the rectifier until the voltage across the secondary has fallen to zero.

Since the energy in the filter inductor is large compared to the energy stored in the switch capacitances in the primary, the charging of the switches can be approximated by a linear charging with a constant current. Consequently, the dead time  $dt_1$  required between the turn-off of  $Q_1$  and turn-on of  $Q_3$  can be determined by:

$$dt_1 I_p = 4C_{mos} V_{in} \quad , \tag{2-3}$$

where  $4C_{mos}V_{in}$  corresponds to twice the charge stored in the nonlinear output capacitance of the MOSFET and  $I_P$  is the peak current in the output filter inductor reflected to the primary. The dead time can be calculated for the minimum  $I_P$  chosen to achieve ZVS. If load current is further reduced, the ZVS property cannot be maintained.

Critical current for ZVS—The ZVS for  $Q_1$  and  $Q_3$  can be achieved even at light loads because  $D_1$ and  $D_3$  can always be turned on by the energy stored in the output filter inductance. However, ZVS for  $Q_2$  and  $Q_4$  can only be achieved for a load current above the critical values, which is shown as:

$$I_{CRIT} = \sqrt{\frac{2}{L_{LK}} \left(\frac{4}{3}C_{mos}V_{in}^{2} + \frac{1}{2}C_{TR}V_{in}^{2}\right)}$$

(2-4)

The available current through  $L_{LK}$  at  $t_2$  can be calculated by:

$$I_{2} = \frac{N_{s}}{N_{p}} \left( I_{load} + \frac{\Delta I}{2} - \frac{V_{out}}{L_{LK} + L_{f}} (1 - D) \frac{T}{2} \right)$$

(2-5)

Finally, ZVS is achieved for a load current so that  $I_2 > I_{CRIT}$ . The load current can be expressed as:

$$I_{load} \ge \frac{N_{P}}{N_{S}} I_{CRIT} - \frac{\Delta I}{2} + \frac{V_{out}}{L_{LK} + L_{f}} (1 - D) \frac{T}{2}$$

(2-6)

#### 3. Transformer Design

The most important step in designing PIPS is the transformer design for ZVS-PS-FB DC/DC converter (Converter 1) displayed in Fig. 2-3. Since this ZVS-PS-FB DC/DC converter will be adopted in applications where high voltage isolation level is required as shown in Fig. 2-2, the transformer need be capable of providing an isolation level of up to several kilovolts. Unfortunately, off-the-shelf transformers cannot directly suit the proposed power supply,

necessitating the need for designing an efficient transformer for the proper functioning of the converter. In particular, the transformer should operate at high switching frequency in order to reduce size and cost of magnetic components.

Due to the key role of this transformer, especially its cost and size efficiency, in the high voltage isolation level power supply design for GCT gate drivers, the next two sections are dedicated to extensive discussions on the importance of this transformer. Specifically, Section 2.2.4 provides analysis on the high cost and large size of the power supply for GCT gate drivers due to the high voltage isolation transformer, thereby emphasizing the necessity of transformer optimization in terms of cost and size. Section 2.2.5 accordingly presents the detailed optimization procedure yielding a high voltage isolation transformer with reduced cost and size, satisfying one of the major design goals of PIPS.

## 2.2.4 Cost and Size of High Voltage Isolation Level Transformer

The most important function of the isolation transformer is to provide isolation between the utility power supply and the gate driver. Since the voltage between the GCT device and the ground of the utility power supply can be a few thousands volts in MV applications, the isolation transformer must be specially designed and manufactured. In general, the cost of such transformers is high and the physical size is large. These inferiorities of the existing commercial power supplies motivate us to reduce the cost and size of high voltage isolation transformers for GCT gate driver power supplies.

Six parallel high frequency ferrite transformers are placed in one PCB unit to supply the minimum six GCT devices employed in MV applications. In addition, each of these transformers should meet the voltage isolation requirement for the GCT gate driver. In the next section, the optimization procedure for the high voltage isolation transformer is presented in great detail.

## 2.2.5 Optimization Procedure for the Transformer Design

The choice of magnetic for power transformers will be influenced by several factors including [30-32]: 1) circuit topology, usually chosen to yield the best combination of minimum power transistor off voltage and peak current stresses. Cost and component count must also be taken into account, 2) operating frequency of the circuit, 3) power requirements, 4) regulation, 5) cost, 6) efficiency, and 7) input/output voltage. These factors will determine the transformer core material, configuration, and size, as well as the winding parameters for the transformer.

The optimization of the high voltage isolation level transformer should be incorporated to reduce the number of primary and secondary winding turns and provide large distance gap between primary and secondary winding which would assist in enhancing the possibility of meeting the corona requirements (i.e., voltage isolation more than 9KV). Consequently, potting the core for the transformer is unnecessary and hence the associated cost can substantially be reduced.

The optimization procedure for the high voltage isolation level transformer is described in what follows.

#### 1. Transformer core material

Ferrite core is chosen as the material of the high frequency transformer due to its low-cost and low-loss characteristics for transformers in the frequency range of 20kHz to 1MHz. Three low-loss materials, Magnetics R, P, and F, are engineered for optimum frequency and temperature performance in power applications. These materials provide superior saturation, high temperature performance, and low loss. Based on the results given by the manufacturer in Table 2-1, at the frequency of 100kHz, flux density of 100mT, and different temperature rises, R material outperforms all the other materials including P and F. As a result, R material was chosen to be the main core material which causes the lowest core loss and temperature rise.

| Temperature Rise              | Power loss $P_L [mW/cm^3]$       |       |     |  |  |  |  |

|-------------------------------|----------------------------------|-------|-----|--|--|--|--|

|                               | @ $f_{TR}=100[kHz], B_m=100[mT]$ |       |     |  |  |  |  |

| $\Delta T_{Rise} [^{\circ}C]$ | R                                | R P F |     |  |  |  |  |

| 25                            | 140                              | 125   | 100 |  |  |  |  |

| 60                            | 100                              | 90    | 180 |  |  |  |  |

| 100                           | 70                               | 125   | 225 |  |  |  |  |

| 120                           | 90                               | 165   |     |  |  |  |  |

Table 2-1: Core material characteristics.

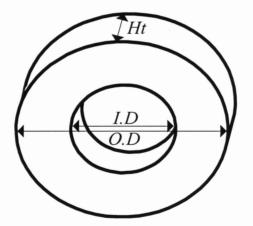

#### 2. Transformer core shape and size

In order to meet the design criteria for high voltage isolation level transformer, the core must be selected carefully. The toroidal core is opted for to satisfy the transformer design requirements, because toroidal core provides the most desirable voltage isolation level compared to other core shapes [31]. Ferrite toroids also offer high magnetic efficiency as: 1) there is no air gap, and 2) the cross-sectional area is uniform and does not need a bobbin [32]. Besides, the cost of toroid is lower than other shapes such as E, EP, and PQ. Another key design consideration is the core size. It should be selected to provide large distance gap between primary and secondary winding, in which case the corona between primary and secondary windings can be eliminated.

The power handling capability of a core is related to its area product,  $A_p$ , by the following equation, which can be written as:

$$A_{p} = \frac{P_{i}(10^{4})}{K_{f}K_{u}B_{m}Jf} , \qquad (2-7)$$

where  $P_t$  is the sum of the output power and the input power is assumed to be 200*W*. The winding factor is  $K_u = 0.3$  depending on the core shape and  $K_f = 4$  for square wave. Typically, a good working level of current density ( $J = 400 A/cm^2$ ) is assumed.

The initial estimation for the operating frequency of the transformer  $(f_{TR})$  is 100 kHz, which was derived as a reasonable and practical tradeoff between minimized core losses and reduced transformer volume. The operating flux density  $(B_m)$  is determined by the transformer operating frequency, allowable core loss  $(P_{fe})$ , and the core set volume  $(V_e)$ . The initial value for  $B_m$  is set low in order to minimize core losses. Then, from Eq. (2-7), the area product  $A_p$  can be calculated.

Using the core selection table by the area product distribution  $W_aA_c$ , three cores, 43610, 43615, and 43825TC, from Magnetics Inc. were selected as shown in Table 2.2. The dimension of the toroidal core is shown in Fig. 2-5. These cores yield bigger area product than the original area product initially calculated in Eq. (2-7). The reason for selecting a bigger toroidal core is to increase the distance gap between primary and secondary windings, which in turn leads to the increased voltage isolation level of the transformer.

There are several types of available coating for toroids: Parylene Y, Nylon V, and Epoxy Z. The Z coating is chosen for toroid since it outperforms Y and V, in terms of a minimum voltage breakdown of 2000V (wire to wire) it offers and temperature that is rated to 200  $^{\circ}C$  continuous operation.

Fig. 2-5: Dimension of the toroidal core.

| Part    | O.D  | I.D  | H <sub>t</sub> | le                 | Ac                 | Ve                 | W <sub>a</sub> A <sub>c</sub> | Coating |

|---------|------|------|----------------|--------------------|--------------------|--------------------|-------------------------------|---------|

|         | (mm) | (mm) | (mm)           | (mm <sup>2</sup> ) | (mm <sup>2</sup> ) | (mm <sup>3</sup> ) | (cm <sup>4</sup> )            |         |

| 43610TC | 36   | 23   | 10             | 89.7               | 62.6               | 5,616              | 2.61                          | Z       |

| 43615TC | 36   | 23   | 15             | 89.6               | 95.9               | 8,366              | 3.93                          | Ζ       |

| 43825TC | 38.1 | 19   | 18             | 82.8               | 231                | 19,304             | 6.58                          | Z       |

Table 2-2: Specifications of three different toroidal cores.

#### 3. Number of turns

In order to meet other design criteria for the high voltage isolation level transformer, the number of turns on primary and secondary windings must be reduced. This can be fulfilled by operating at high frequency and choosing a core with a big cross-sectional area (43825TC).

In voltage transformer design, input/output voltages are known and thus the transformer ratio  $N = \frac{V_P}{V_s}$  is given. The primary turns can be expressed using Faraday's Law:

$$N_{P} = \frac{V_{in(\min)} D_{\max}(10^{4})}{A_{C} B_{m} f K_{f}} , \qquad (2-8)$$

where  $A_c$  is a core cross-sectional area which can be found in Table 2-2. In this particular design:  $V_{in(min)} = 50V$ ,  $D_{max} = 0.9$ . Therefore, the primary number of turns can be calculated from Eq. (2-8) as  $N_P = 7$  turns.

The number of turns for each secondary winding is calculated based on the available volt-second product on the primary winding and the desired output voltage. The exact transformer primary to secondary turns ratio (N) is derived from the following relationships used for any buck-derived converter :

$$V_{out} = \frac{D_{\max}}{\frac{N_P}{N_S}} V_{in(\min)} \quad , \tag{2-9}$$

where  $D_{max}$  is the maximum obtainable duty cycle of the converter, which occurs at the minimum input voltage,  $V_{in(min)}$ .  $V_{out}$  is the peak value of the output voltage, which is 24Vdc. Consider the duty cycle loss of 10% at the secondary winding of the transformer caused by the leakage inductance.

Substituting the turns ratio  $N = \frac{N_P}{N_S}$  into Eq. (2-9), the following is obtained:

$$N = \frac{D_{\text{max}}}{V_{out}} V_{in(\text{min})}$$

(2-10)

= 1.75.

Therefore, the secondary number of turns is:

$$N_s = \frac{N_P}{N} = 4$$

turns

Optimizing the number of turns at different operating frequencies with core 43825TC—Fig. 2-6 illustrates the relationship between the optimization of the number of primary and secondary turns, and different operating frequencies, at fixed input voltage and the operating flux density between 80mT and 100mT.

Fig. 2-6: Number of primary and secondary turns vs. operating frequency.

It is observed that as the operating frequency of the transformer increases, the number of turns on primary and secondary is reduced. The lowest number of primary and secondary turns is 3/2, which can be attained at the transformer operating frequency of 165kHz indicating that the phase-shift full-bridge DC/DC converter must operate at 330kHz clock frequency.

#### 4. Wire size

The size of the wire is calculated based on the primary and secondary currents at current density  $J = 400A/cm^2$  [31], [32]. The required number of primary and secondary strands is  $S_{np} = 4 x$  AWG#23 and  $S_{ns} = 8 x AWG#23$ , respectively. Generally, for high frequency transformer above 100*kHz*, the stranded wire (litz wire) for transformer winding should be considered in order to reduce the skin effect losses. However, it is difficult to find litz wire with high voltage isolation coating. As a result, the wire with high isolation coating in the range of 20kV to 40kV is chosen to provide high voltage isolation level for the transformer as shown in table 2-3.

Table 2-3: High voltage isolation wire.

| Wire # | Voltage rating | AWG | Temp | Miscellaneous        |

|--------|----------------|-----|------|----------------------|

| 1      | 20 <i>kV</i>   | 16  | 150  | Thermal Wire & Cable |

| 2      | 40 <i>kV</i>   | 18  | 150  | Thermal Wire & Cable |

| 3      | 30 <i>kV</i>   | 18  | 150  | Thermal Wire & Cable |

| 4      | 30 <i>kV</i>   | 20  | 80   | Thermal Wire & Cable |

#### 5. Discussion

The main issue in designing high voltage isolation level transformer is to reduce or eliminate the corona between primary and secondary windings to meet the BIL (basics insulation level) rating on the transformer. It serves as an assurance to routinely withstand power surges up to the given rating emanating from any number of common sources [34], [35]. The corona can be reduced by eliminating any air entrapped between primary and secondary windings of the transformer. It is realized by first evacuating the air between windings and then potting the core to meet the high voltage isolation requirement of several kilovolts. However, this process is fairly expensive and thus the transformer optimization goal, as mentioned above, is to reduce the cost incurred in this process. With the above optimization procedure, low number of winding turns, wide gap between primary and secondary windings, and high voltage isolation wire for winding, it is possible to satisfy the voltage isolation requirement for the GCT gate driver. The voltage isolation level of the transformer can be further improved by spraying a low-priced special insulating coating to eliminate the air entrapped between primary and secondary windings of the transformer.

#### 2.2.6 Converter 2 for Regulated DC Output Voltage

Converter 1 alone without any output voltage feedback cannot regulate a stable output voltage of  $20\pm0.5V$  (required for GCT gate drivers) at light load conditions. As shown in Fig. 2-7, the voltage regulation performs reasonably at full load, while poorly at very light load or open circuit, the reason being that there is no output voltage feedback with respect to the load changes.

Fig. 2-7: Voltage regulation of Converter 1 without Converter 2.

As a result, the output voltage of the first converter tends to increase to the peak of the secondary overshoot voltage of the transformer at light load. Therefore, an additional DC/DC is cascaded to the output of each isolated power supply in Converter 1 at very low cost, small size, and high efficiency to tackle the problem, resulting in the voltage regulation effective from full load to open load under wide input voltage range for GCT gate drivers.

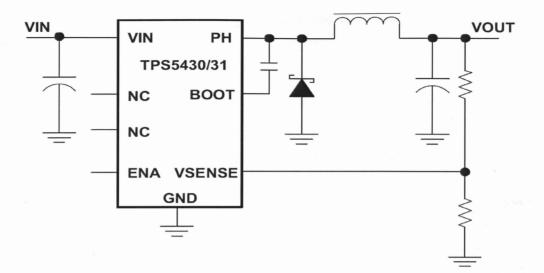

Converter 2 is a DC/DC step-down converter with integrated FET (TPS5430) from Texas Instruments as shown in Fig. 2-8. The main function of this DC/DC converter is to satisfy the GCT gate driver voltage regulation of 20V dc and the maximum power of 60W required for the GCT gate driver.

Fig. 2-8: Simplified schematic of DC/DC step-down converter.

The main features of this DC/DC converter are given as follows: 1) It operates under wide input voltage range of 23.6V to 36V to regulate 20V output voltage and 3A continuous (4A Peak) output current; 2) It yields high efficiency for up to 97% enabled by  $110m\Omega$  integrated MOSFET switch; 3) It has fixed 500kHz switching frequency for small filter size. Note that to reduce the design complexity and external component count, the TPS5430 feedback loop is internally compensated; and 4) the system is secured through overcurrent limiting, overvoltage protection, and thermal shutdown.

## 2.3 Summary and Discussion

In this chapter, a novel parallel isolated power supply (PIPS) for GCT gate drivers is proposed. The proposed design includes six parallel isolated power supplies (PIPS), each supplying a GCT gate driver at regulated 20Vdc. The supply is composed of two power converters, Converter 1 and Converter 2. The former is used to provide electrical isolation between each channel of PIPS and its gate driver, whereas the later is utilized to regulate the output voltage of the supply. This design features a general power supply for powering the gate drivers of switches used in different converter topologies where high voltage insulation level is required, such as Medium Voltage Neutral Point Clamped to PWM CSI converters.

Through the elaboration on the design requirements and the operating principle, the proposed power supply is shown to be able to power up the GCT gate driver. The optimization procedure for the high voltage isolation level transformer is discussed which eliminates the necessity of potting the torodial transformer, and substantially saves the costs on both potting and expensive/bulky commercial power supply.

## **CHAPTER 3: Component Selection and Efficiency Optimization for PIPS Using Pspice Simulation Model**

This chapter starts with the development of a simplified simulation model for PIPS, using commercial software Pspice. In order to obtain accurate design and control, PIPS must first be properly modeled and simulated. With a suitable model in place, the performance of PIPS with optimized transformers (i.e., with minimized cost and size) and its maximum efficiency can be investigated. More importantly, the results of the simulations enable us to predict the performance of the converter and its controller before the actual building and deployment of the hardware, and to assure that all the selected components meet the requirements.

## **3.1 PIPS PSPICE Model**