# DEVELOPMENT OF AN ELECTROTHERMAL

# SIMULATION TOOL FOR INTEGRATED CIRCUITS

by

# Sara Sharifian Attar

BASc. Ferdowsi University of Mashhad, Iran

March 2002

A thesis

presented to Ryerson University in partial fulfillment of the requirement for the degree of Master of Applied Science in the program of Electrical and Computer Engineering.

Toronto, Ontario, Canada 2006

© Sara Sharifian Attar 2006

PROPERTY OF RYERSON UNIVERSITY LIBRARY

#### UMI Number: EC53477

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC53477 Copyright 2009 by ProQuest LLC All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Signature

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for he purpose of scholarly research.

Signature

-

# **Instructions on Borrowers**

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

## Abstract

#### Sara Sharifian Attar

# Development of an Electrothermal Simulation Tool for Integrated Circuits Master of Applied Science, Electrical and Computer Engineering Ryerson University, Toronto, 2006

The goal of this research was to develop a capability for the electrothermal modeling of electronic circuits. The objective of the thermal modeling process was to create a model that represents the thermal behavior of the physical system. The project focuses on electrothermal analysis at devices and chip level. A novel method to perform electrothermal analysis of integrated circuits based on the relaxation approach is proposed in this research. An interface program couples a circuit simulator and a thermal simulator. The developed simulator is capable of performing both steady state and transient analysis at devices and chip level.

The proposed method was applied to perform electrothermal analysis of Silicon Bipolar Junction Transistor (BJT) to predict the temperature distribution and the device performance in a circuit. Thermal nonlinearity due to temperature-dependent material parameters in the context of thermal modeling of the device and circuit has also been considered. The DC characteristics of the device were investigated. The obtained results indicate that the operating point of the device varies while the device reaches its junction temperature.

The accuracy of the electrothermal simulator has been evaluated for steady state analysis. The experimental results of a BJT amplifier were compared to the simulator results of the similar circuit. The electrothermal simulation results of BJT amplifier circuit indicate a good agreement with the available experimental results in terms of power dissipation, collector current and base-emitter voltage.

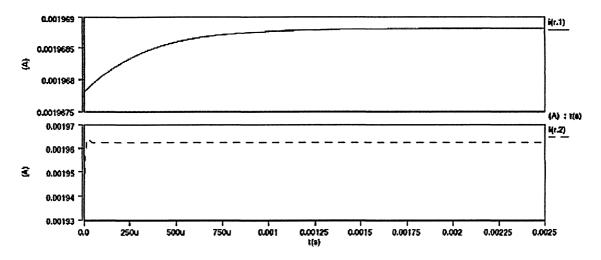

The performance of the electrothermal simulator has been evaluated for transient analysis. A current mirror circuit using Si NPN BJTs was simulated. According to the electrical simulator, the output current follows the reference current immediately. Nonetheless, the electrothermal simulator results depict that the load current has delay to reach a constant value which is not the same as the reference current, due to the influence of thermal coupling and self heating. The obtained results are in agreement with the available results in literature.

# Acknowledgements

First, I would like to thank my supervisor Dr. Farah Mohammadi for accepting me as her MASc. student in Ryerson University and giving me the great opportunity to research in the amazing area of VLSI circuits and systems. Without her excellent guidance, engagement, encouragement and wisdom, it would have been so much harder to conduct this work.

I would like to thank my committee members Dr. Vadim Geurkov, Dr. Eddie Law and Dr. Kaamran Raahemifar for their great advices and supports.

I would like to thank my friends Rushin Shojaii, Sina Zarei, Huma Mehmud, Sumandeep Virk and Sudeshna Pal for all the wonderful time that we shared and their help and advices during my research.

I would like to thank the supports provided by National Science and Engineering Council of Canada (NSERC) and Ryerson University.

I would like to thank my father, my mother and my two brothers, Ehsan and Hassan, whom I love with all my heart, for all their supports.

In closing, I thank God. For only through God's grace and blessings has this pursuit been possible.

# Dedication

To my dear husband, Farhad, for his encouragement, support, patience and model of perseverance, without whom this would have never been possible.

# **Table of Contents**

| List of Figures x                     |

|---------------------------------------|

| List of Tables xii                    |

| 1. Introduction 1                     |

| 1.1 Thesis Objectives2                |

| 1.2 Thesis Outline                    |

| 2. Heat Transfer 4                    |

| 2.1 Heat Conduction 4                 |

| 2.1.1 Fourier's Law                   |

| 2.1.2 Thermal Conductivity 5          |

| 2.1.3 Heat Capacity 6                 |

| 2.2 Heat Radiation7                   |

| 2.2.1 Stefan-Boltzmann Law 8          |

| 2.3 Heat Convection                   |

| 2.3.1 Newton's Law of Viscosity9      |

| 2.3.2 Newton's Law of Cooling10       |

| 2.4 Boundary and Initial Conditions11 |

| 2.5 Summary 12                        |

| 3. Thermal Analysis 13                |

| 3.1 Fourier Series                    |

| 3.2 Finite Element Method15           |

| 3.3 Finite Difference Method                                         | 18 |

|----------------------------------------------------------------------|----|

| 3.4 Boundary Element Method                                          | 21 |

| 3.5 Analytical Solution                                              | 21 |

| 3.6 Thermal Network                                                  | 22 |

| 3.7 Summary                                                          | 25 |

| 4. Electrical Analysis                                               |    |

| 4.1 BJT SPICE Model                                                  |    |

| 4.3 Power Dissipation and Temperature Effects on Integrated Circuits |    |

| 4.4 Summary                                                          |    |

| 5. Electrothermal Analysis                                           | 40 |

| 5.1 Direct Method                                                    | 40 |

| 5.1.1 Literature Review on Direct Method                             |    |

| 5.2 Relaxation Method                                                | 49 |

| 5.2.1 Literature Review on Relaxation Method                         |    |

| 5.3 Summary                                                          |    |

| 6. Implemented Methodology                                           |    |

|                                                                      |    |

| 6.1 Methodology of Simulators Coupling                               |    |

| 6.1.1 Implemented Algorithm                                          |    |

| 6.1.2 Coupling COMSOL and MATLAB                                     |    |

| 6.1.3 Coupling PSpice and MATLAB                                     |    |

| 6.2 Summary                                                          | 61 |

| 7. Electrothermal Investigation of Si BJT Circuits                   |    |

| 7.1 Active BJT                                                       |    |

| 7.1.1 Electrical Model                                               | 63 |

| 7.1.2 Thermal Model                                                  | 65 |

| 7.1.3 Simulation Results                                             | 67 |

-

| 7.2 BJT Amplifier                            |     |

|----------------------------------------------|-----|

| 7.2.1 Electrical Model                       | 71  |

| 7.2.2 Thermal Model                          |     |

| 7.2.3 Simulation Results                     | 74  |

| 7.3 BJT Current Mirror                       |     |

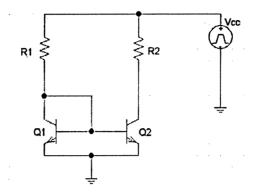

| 7.3.1 Electrical Model                       |     |

| 7.3.2 Thermal Model                          | 80  |

| 7.3.3 Transient Simulation Specifications    |     |

| 7.3.4 Simulation Results                     |     |

| 7.3.5 Constant Time Step Effect              |     |

| 7.3.6 Validation of Electrothermal Simulator |     |

| 7.4 Summary                                  |     |

| Conclusion and Future Work                   |     |

| References                                   |     |

| Publications                                 | 102 |

# List of Figures

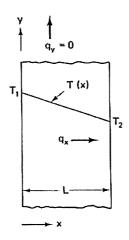

| Figure 2.1: 1D conduction heat transfer in a plate with $T_1 > T_2$ ; $q_y = 0$ and $q_x = 0$ [10] | 5   |

|----------------------------------------------------------------------------------------------------|-----|

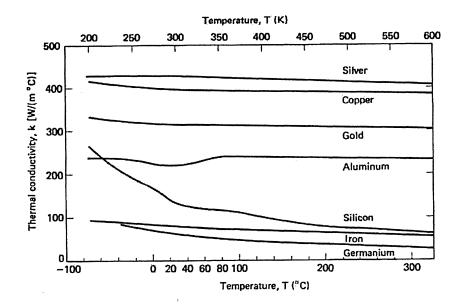

| Figure 2.2: Thermal conductivity of different materials versus temperature [10]                    | 6   |

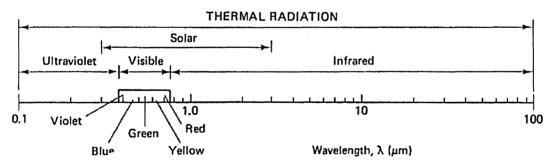

| Figure 2.3: Electromagnetic spectrum for thermal radiation wavelength band [10]                    | 7   |

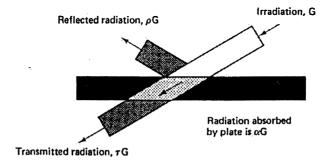

| Figure 2.4: Absorption, reflection and transmission of thermal radiation incident on a surfa       | ice |

| [10]                                                                                               | 8   |

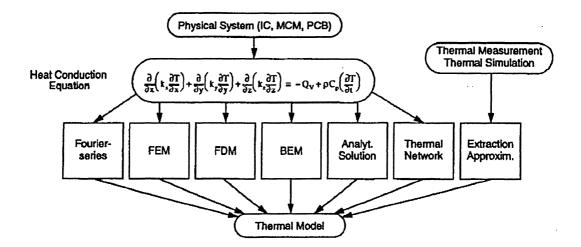

| Figure 3.1: Thermal modeling approach [8]                                                          |     |

| Figure 3.2: Thermal model of an IC and its packaging [13]                                          |     |

| Figure 3.3: Some typical generic elements for 1D, 2D and 3D mesh geometries [15]                   | 16  |

| Figure 3.4: Network of subvolumes and nodes of a rectangular solid. Shading indicates              |     |

| representative interior and exterior nodes [10].                                                   | 19  |

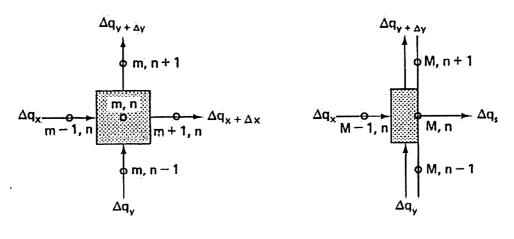

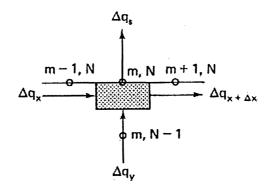

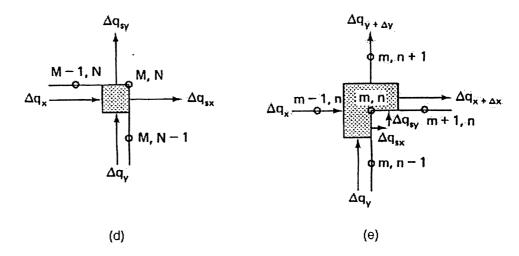

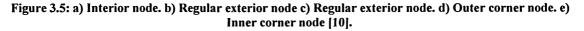

| Figure 3.5: a) Interior node. b) Regular exterior node c) Regular exterior node. d) Outer          |     |

| corner node. e) Inner corner node [10].                                                            | 20  |

| Figure 3.6: Interior finite-difference subvolume [10]                                              |     |

| Figure 3.7: Equivalent thermal network for interior subvolume [10]                                 | 24  |

| Figure 3.8: a) Exterior finite-difference subvolume. b) Equivalent thermal network for             |     |

| exterior subvolume [10]                                                                            | 24  |

| Figure 4.1: BJT SPICE model [19]                                                                   | 27  |

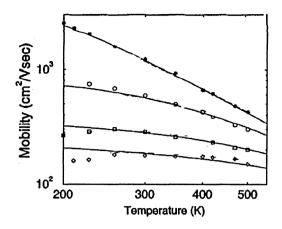

| Figure 4.2: Electron mobility variations vs. temperature [22]                                      | 31  |

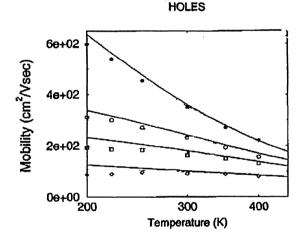

| Figure 4.3: Hole mobility variations vs. temperature [22]                                          | 31  |

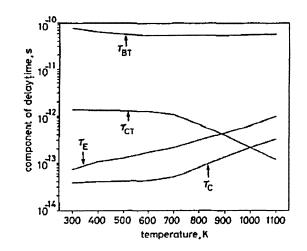

| Figure 4.4: Collector, Emitter and Base transient and charging time variations with                |     |

| temperature [23]                                                                                   | 32  |

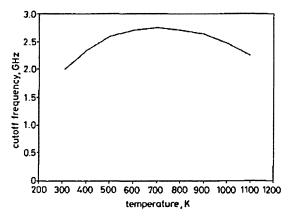

| Figure 4.5: BJT cut-off frequency variations with temperature [23]                                 | 32  |

| Figure 4.6: Collector saturation current variations with temperature [24]                          |     |

| Figure 4.7: Base-Emitter voltage variations versus temperature [23].                               | 33  |

| Figure 4.8: Current gain variations with temperature [23].                                         | 34  |

| Figure 4.9: I-V characteristics of common emitter Si BJT. Data was taken at 4µs (solid line        | e), |

| 40µs (semi-dashed line), 100µs (dashed line) and 200µs (dotted line) [25]                          | 35  |

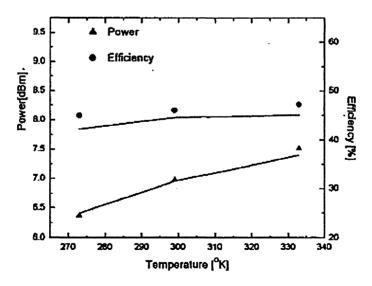

| Figure 4.10: BJT power and efficiency variations with temperature [26]                             | 35  |

| Figure 4.11: Power density trends [27]                                                             |     |

| Figure 4.12: Equivalent Schematic of VBIC model. [28]                                              | 38  |

| Figure 4.13: DC transfer curve of Op-Amp 741[29].                                                  |     |

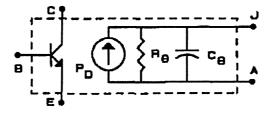

| Figure 5.1: The BJT CAD model showing the electrical analog circuit between nodes J and            | ΙA  |

| which models thermal effects [32]                                                                  |     |

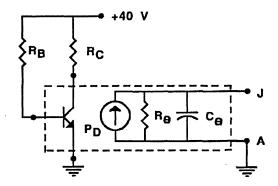

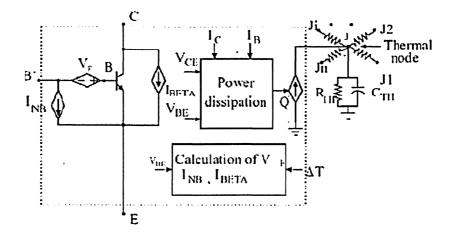

| Figure 5.2: The BJT circuit and its electrical analog thermal circuit [32]                         | 43  |

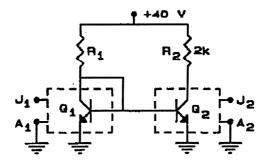

| Figure 5.3: The current mirror circuit and the thermal nodes of the BJTs [8]                       |     |

~

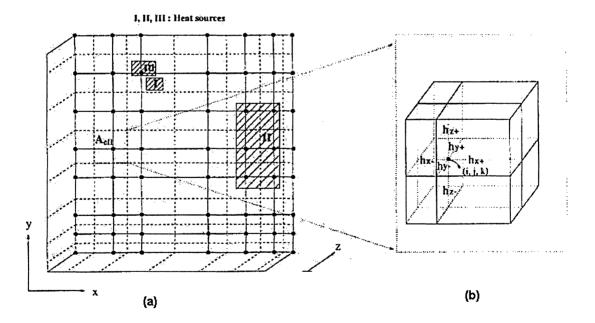

| Figure 5.4: (a) Top view of the solid containing heat sources, and (b) 3-D view of grid point    |      |

|--------------------------------------------------------------------------------------------------|------|

| (i, j, k) [35]                                                                                   |      |

| Figure 5.5: Thermal model of Shelar et. al [21].                                                 |      |

| Figure 5.6: BJT thermal model of Shelar et. Al simulator [21]                                    |      |

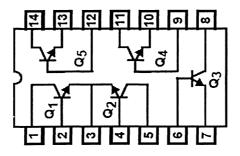

| Figure 5.7: Pin diagram of HFA3046B [21]                                                         | . 47 |

| Figure 5.8: Circuit diagram of the current mirror using HFA3046B [21]                            | . 48 |

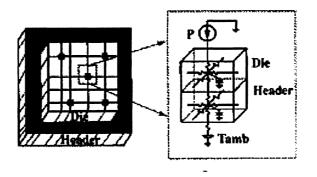

| Figure 5.9: Lumped RC thermal model for the die/header structure [36].                           | . 50 |

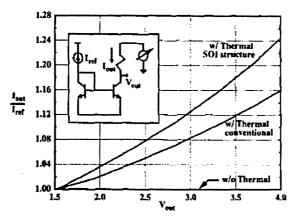

| Figure 5.10: DC gain versus output voltage of a current mirror using SOI and trench isolat       | ed   |

| BJT devices, with and without thermal effects [36].                                              |      |

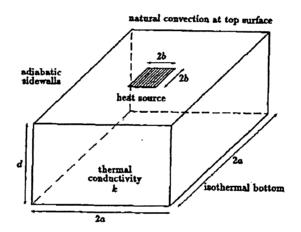

| Figure 5.11: One layer model for a typical heat conduction problem [37]                          | . 52 |

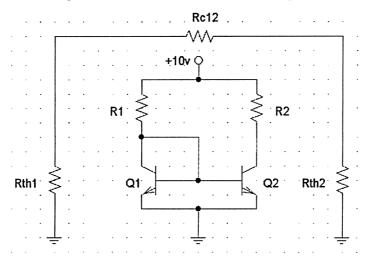

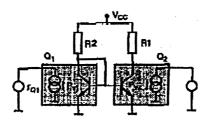

| Figure 5.12: Current mirror circuit implemented in SABER [38]                                    |      |

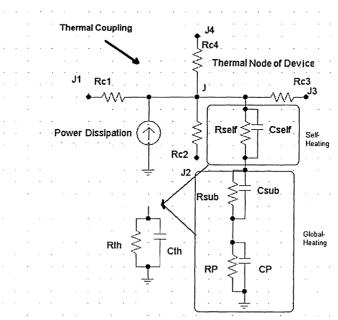

| Figure 5.13: Thermal model of the device [38].                                                   |      |

| Figure 5.14: Simulation results of Wunsche et. al simulator [38].                                |      |

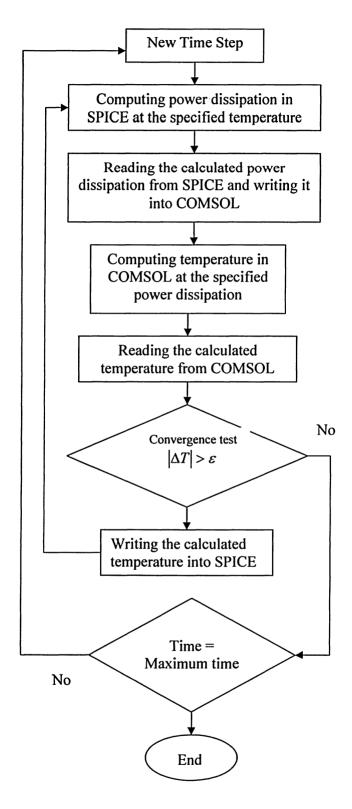

| Figure 6.1: Flow chart of the electrothermal simulator.                                          |      |

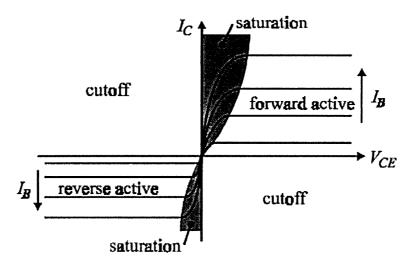

| Figure 7.1: BJT regions of operation [3].                                                        |      |

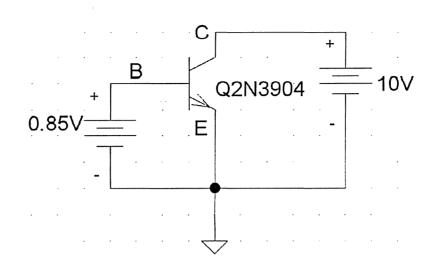

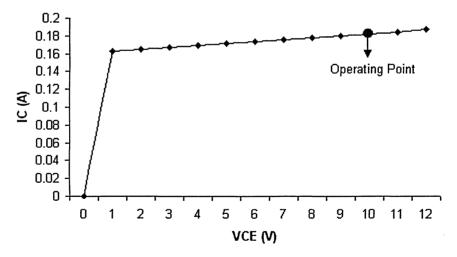

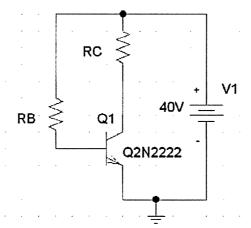

| Figure 7.2: Circuit of the active BJT.                                                           |      |

| Figure 7.3: BJT DC characteristics.                                                              |      |

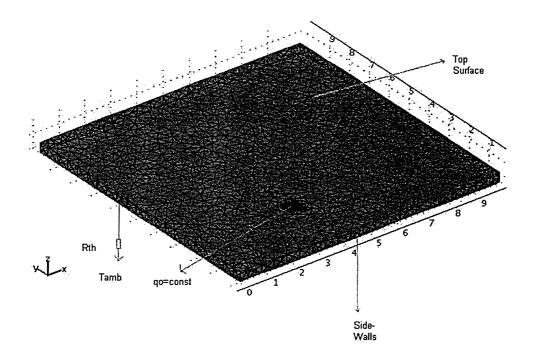

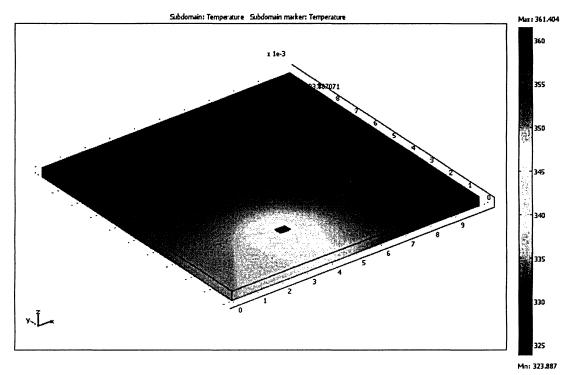

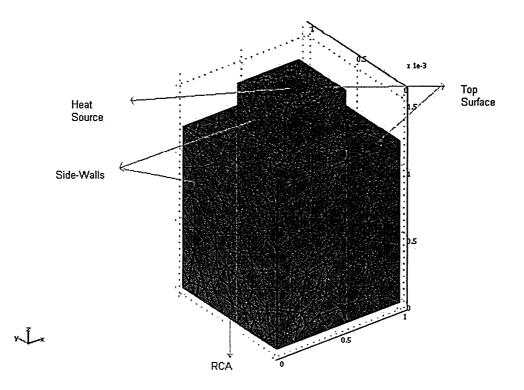

| Figure 7.4: Finite element model and boundary condiction.                                        |      |

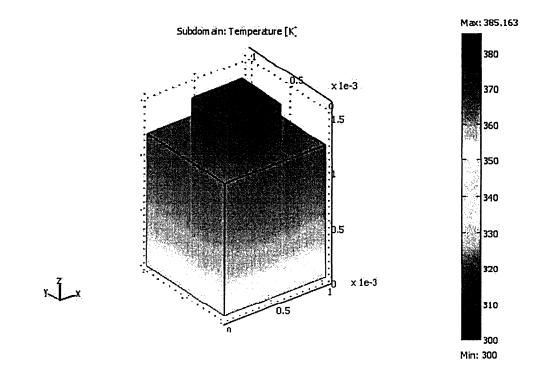

| Figure 7.5: 3D temperature distribution at a power dissipation of 1.83W.                         | . 67 |

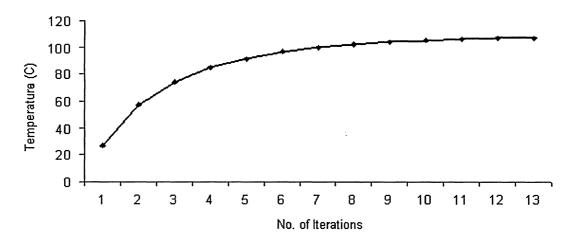

| Figure 7.6: Device temperature variations versus numbers of iterations                           | . 68 |

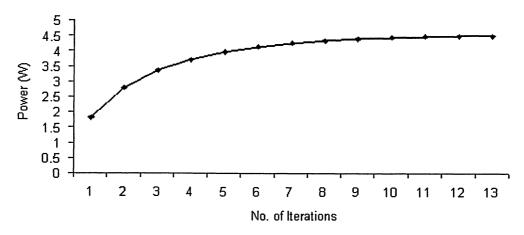

| Figure 7.7: Device power variations versus numbers of iterations                                 |      |

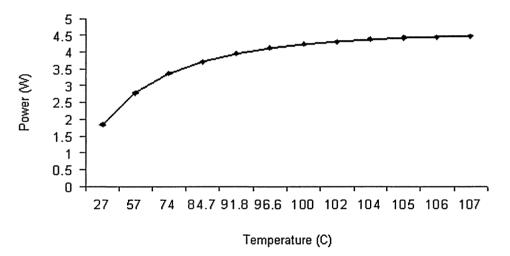

| Figure 7.8: Device power variations versus its temperature                                       |      |

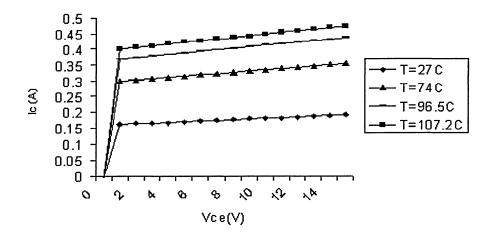

| Figure 7.9: $I_C$ versus $V_{CE}$ while device reaches its junction temperature                  |      |

| Figure 7.10: BJT amplifier circuit.                                                              |      |

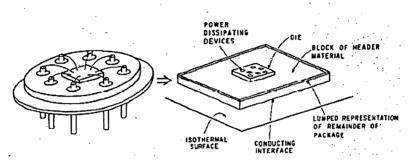

| Figure 7.11: Die and header of an IC and its simplified physical model [29]                      |      |

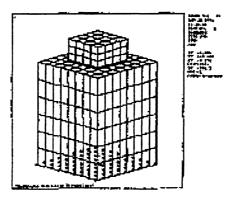

| Figure 7.12: Finite element model of BJT amplifier.                                              |      |

| Figure 7.13: 3D temperature distribution across the amplifier thermal model                      |      |

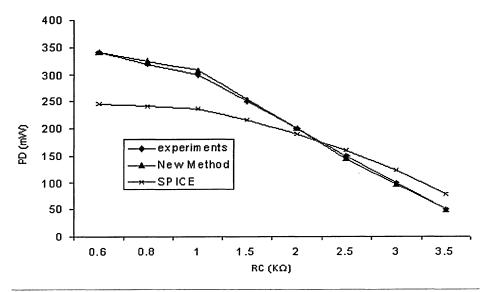

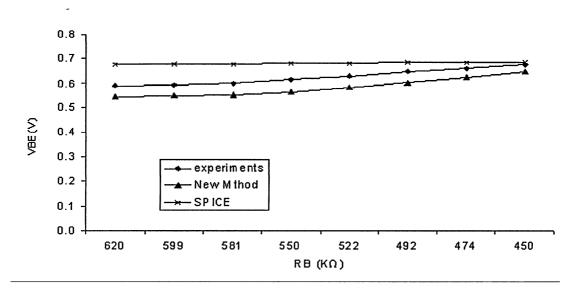

| Figure 7.14: Power dissipation variations of the compared methods versus variations of $R_c$     |      |

| rigure 7.14. I ower dissipation variations of the compared methods versus variations of te       |      |

| Figure 7.15: Current gain variations of the compared methods versus variations of R <sub>c</sub> |      |

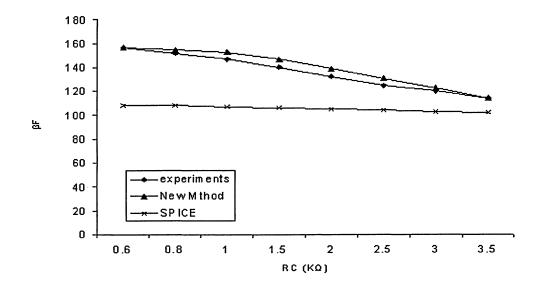

| Figure 7.16: Base-Emitter voltage variations of the compared methods versus variations of        |      |

| R <sub>C</sub>                                                                                   |      |

| Figure 7.17: Implemented current mirror.                                                         |      |

| Figure 7.18: Finite element model of the current mirror.                                         |      |

| Figure 7.19: 3D temperature distribution across the current mirror thermal model                 |      |

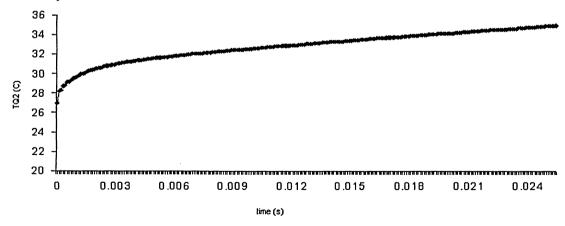

| Figure 7.20: Temperature variations of the active devices over time                              |      |

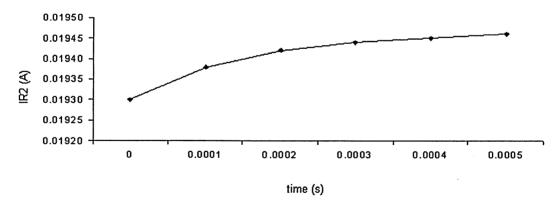

| Figure 7.21: Variations of the reference current over time                                       |      |

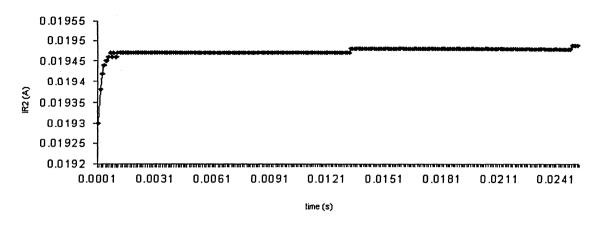

| Figure 7.22: Variations of the output current over time.                                         |      |

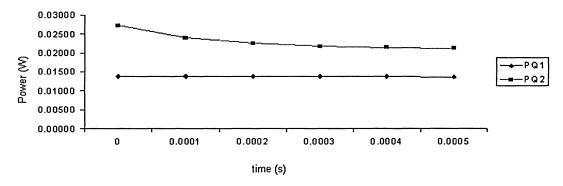

| Figure 7.23: Variations of the power dissipations of the active devices by time                  |      |

| Figure 7.24: Variations of $TQ_2$ versus time while time steps were equal                        | . 88 |

| Figure 7.25: Variations of $I_{R2}$ versus time while time steps were equal                      |      |

| Figure 7.26: Variations of the output current over variations of time versus No. Of time ste     |      |

|                                                                                                  | -    |

| Figure 7.27: Variations of the $T_{Q2}$ over variations of time versus No. of time step.         |      |

| Figure 7.28: Wunsche et al's a)Temperature, b)Output current and c) Reference current            |      |

| simulation results [38]                                                                          | . 91 |

|                                                                                                  |      |

# List of Tables

| Table 3.1: Electrical Analogy.                                                               | . 22 |

|----------------------------------------------------------------------------------------------|------|

| Table 4.1: Some BJT parameters variations with temperature.                                  | . 28 |

| Table 4.2: Parameters definitions.                                                           | . 29 |

| Table 4.3: Improvement trends for ICs enabled by feature scaling [27]                        | . 37 |

| Table 7.1: Silicon thermal charactristics                                                    | . 66 |

| Table 7.2: Material properties and dimensions of layers of the thermal model                 | . 73 |

| Table 7.3: Comparison results of the power dissipation                                       |      |

| Table 7.4: Comparison results of the collector current                                       | . 76 |

| Table 7.5: Comparison results of the Base-Emitter voltage.                                   |      |

| Table 7.6: Comparison results of the current gain                                            |      |

| Table 7.7: Material properties and dimensions of layers of the thermal model.                |      |

| Table 7.8: Results of the transient simulation of the current mirror                         |      |

| Table 7.9: Experimental results, and Munro et. al and Shelar et. al's results of the current |      |

| mirror.                                                                                      | . 90 |

·,

## **Chapter 1**

# 1. Introduction

Shrinking device sizes and higher integration densities are giving rise to numbers of new challenges in designing the next generation of integrated electronic circuits. Many roadmaps now recognize advanced electrothermal analysis as one of the major challenges in electronic product innovation. The reasons are due to ongoing push of technology towards higher speed and device density and/or higher power and increased complexity. The compounding effects of size reduction and increased power lead invariably to higher heat generation per unit area. Without accurate prediction of the temperature profile, it is impossible to determine properly the electrical characteristics of devices and therefore these devices may be at risk of overheating thus causing early device failure. When a device operates at high power dissipation, self heating and thermal coupling are the main issues in its performance and reliability [1]. Device temperature enhancement affects its electrical properties such as carrier mobility, electron saturation velocity, ionization rate, thermal conductivity, operating frequency, and power dissipation [2].

BJTs are commonly utilized in high power applications due to their high voltage/current characteristics. High power applications evidently cause increase in temperature. Temperature enhancement causes thermal runaway in bipolar transistors in contrary to field effect transistors. BJTs have positive temperature coefficient on collector current. Increase of temperature causes increase of current gain, which determines the value of the collector current. The more the current flows into the device, the higher its temperature rises. Increase of temperature results in increase of current gain and consequently an increase in current.

The positive loop continues until the device fails due to thermal runaway [3]. Therefore, it is critical to perform electrothermal analysis on BJTs.

Electrothermal simulation of VLSI circuits prior to the manufacturing enhances the estimation accuracy of the circuit performance at the operating temperature. With increasing concerns for on-chip power dissipation due to high packing density and high-frequency operation, electrothermal analysis has become critically important for accurate assessment of thermally activated device and ciorcuit failures, and for timing analysis.

There are mainly two methods for electrothermal analysis: *Direct method and Relaxation method*. In direct or simultaneous iteration method [4] the thermal system is represented by an electrical model network, which has common nodes with the electrical only network, the so-called thermal nodes. In relaxation method an interface program couples two powerful electrical and thermal simulators. One simulator uses the updated results of the other simulator in the iterative process.

#### **1.1 Thesis Objectives**

The goal of this research was to develop a capability for the electrothermal modeling of electronic circuits. The objective of the thermal modeling process was to create a model that represents the thermal behavior of the physical system. This research project aimed to create simulation method to enable rapid assessment of thermal parameters affecting performance in electronic equipment. The project was focus on electrothermal analysis at devices and chip level.

Using relaxation method, an algorithm was developed in MATLAB [5] to create an interface between PSpice [6], as the electrical simulator, and COMSOL [7] as the thermal simulator. Applying this algorithm, an electrothermal simulator to analyze different electronic circuits and devices was obtained. The implementation of the electrothermal simulator requires: a) Communication between two simulators to receive and to send calculated parameters to another simulator. b) Time step to reach steady state values of parameters in that particular time step in a transient simulation. c) Convergence test. The developed algorithm in MATLAB controls these requirements. The developed simulator is capable of performing both steady state and transient analysis at devices and chip level.

The electrothermal simulator was employed to investigate the thermal effects in an active BJT, operational amplifier circuit and current mirror circuit. The results obtained from simulation were compared to the available experimental results to validate the accuracy of the electrothermal models. In addition, the performance of the electrothermal simulator has been evaluated through steady state and transient analysis of operational amplifier circuit and current mirror circuit.

## **1.2 Thesis Outline**

In this research we have attempted to provide coverage of important subjects required for electrotheraml analysis of device and circuits.

The first four chapters are designed to present the fundamental building blocks in an electrothermal simulation. Chapter 2 discusses an general introduction to heat transfer. The available methodologies to solve the heat transfer governing equations are elaborated in chapter 3. In chapter 4, SPICE electrical simulator is briefly introduced and BJT SPICE modeling and its temperature dependency is discussed. The deficiency of SPICE simulator in considering device temperature is also investigated. Chapter 5 focuses on the framework of an electrothermal simulator. The results of chapter 3 and 4 are combined to study several techniques of electrothermal analyses. Literature review on these techniques is also included in this chapter.

Chapter 6 concentrates on the proposed method and developed algorithm for electrothermal simulation. The developed algorithm is first presented. An incremental simulation strategy used in simulation efforts is illustrated in this chapter.

Chapter 7 addresses three important applications of the electrothermal analysis, based on the building blocks discussed in previous chapters. The impact of the thermal effect on the circuit performance is examined. Finally, the conclusions and suggested future works are summarized in chapter 8.

# **Chapter 2**

To be able to perform thermal analysis on a circuit we need to know the basics of heat transfer. This chapter is an introduction to the fundamentals of heat transfer and thermal equations. Heat transfer mechanisms are examined and the governing heat transfer equation is introduced. The boundary conditions and initial condition that can be applied to a thermal model are explained for different environments.

# 2. Heat Transfer

In general, Heat Transfer or *Heat* is defined as "the energy in transit due to a temperature difference" [9].

There are two major mechanisms of heat transfer, *Conduction* and *Radiation*, which occur in solids and fluids. However if heat transfers from a solid surface to a moving fluid by conduction, it is known as *Convection* [10].

## 2.1 Heat Conduction

When heat is transferred within a material due to the molecular agitation, it is called *Conduction*. For instance, heat is transferred into a metal rod from one end to the other due to the temperature difference.

#### 2.1.1 Fourier's Law

According to *Fourier's law*, the amount of heat being transferred by conduction in a onedimensional plane per unit time can be expressed as equation (2.1), where k (W/mK) is the thermal conductivity and T is temperature in K [10].

$$q_x = -k\frac{dT}{dx} = -k\nabla T \tag{2.1}$$

The negative sign indicates that heat is transferred in the direction of decreasing temperature.

Figure 2.1 shows that plate surface temperatures are  $T_1$  and  $T_2$ ; assuming  $T_1$  is greater than  $T_2$ . In this example heat is transferred only by conduction in x direction. Temperature differences in y and z directions are assumed to be zero.

Figure 2.1: 1D conduction heat transfer in a plate with  $T_1 > T_2$ ;  $q_y=0$  and  $q_x=0$  [10].

#### 2.1.2 Thermal Conductivity

Thermal conductivity, k, is a thermo-physical property of materials. It represents the rate of conduction heat transfer per unit area for a temperature gradient of 1°C/m. It has SI units of W/m°C [10].

Most materials have a thermal conductivity that varies with temperature. Figure (2.2) shows thermal conductivity of different materials versus temperature variations.

Figure 2.2: Thermal conductivity of different materials versus temperature [10].

A constant thermal conductivity can be assumed for a substance if its temperature variations are small.

In case of semiconductors, a nonlinear thermal conductivity variable with temperature is considered, equation (2.2).

$$k(T) = k(T_o) \left[ \frac{T}{T_o} \right]^n$$

(2.2)

Where n = -1.25 for Silicon [11].

#### 2.1.3 Heat Capacity

*Heat Capacity, c*, is the quantity that represents the amount of heat required to change one unit of mass of a substance by one degree. The SI units of heat capacity are J/kg°K [10].

$$Q = mc\nabla T \tag{2.3}$$

where Q is the heat energy received or given out by the substance, m is the mass of the substance, and  $\Delta T$  is the change in temperature.

Heat capacity is often expressed in a constant volume,  $C_v$ , or a constant pressure,  $C_p$ .

A heat source can be either internal or external in a heat transfer system. Transistors, resistors and semiconductor chips are good examples of internal heat sources. Examples of external heat sources are different types of cooling systems such as fans and fins in power devices.

Considering heat is transferred only by conduction, heat sources are all internal and thermal conductivity is temperature dependent, by applying Fourier's law, time dependent heat transfer equation is defined as follows:

$$\rho C_p \frac{\partial T}{\partial t} + \nabla (-k\nabla T) = Q \qquad (2.4)$$

Where T (°K) is temperature, t (s) is time,  $\rho$  (kg/m<sup>3</sup>) is density, and  $C_p$  (J/kg°K) is specific heat capacity. Q (W/m<sup>3</sup>) is the heat source or heat sink density; depending on the heating or cooling behavior, it is positive or negative respectively.

#### 2.2 Heat Radiation

*Heat Radiation* is an exchange of temperature between two surfaces with different temperature via electromagnetic waves [10]. Figure (2.3) illustrates electromagnetic spectrum for thermal radiation wavelength band.

Figure 2.3: Electromagnetic spectrum for thermal radiation wavelength band [10].

The medium through which thermal radiation passes can be a vacuum or a transparent gas, liquid or solid. Objects within the path of heat radiation *absorb*, *reflect* and in case of transparent materials, *transmit* these electromagnetic waves. Absorptivity  $\alpha$ , reflectivity  $\rho$ ,

and transmissivity  $\tau$ , of a body represent how much a body absorb, reflect and transmit in the presence of thermal radiation. These parameters ( $\alpha$ ,  $\rho$ , and  $\tau$ ) depend on the material of the body and the temperature of the emitting source [10].

$$\alpha + \rho + \tau = 1 \tag{2.5}$$

#### 2.2.1 Stefan-Boltzmann Law

According to Stefan-Boltzmann law, the total emissive power,  $E_b$ , for a blackbody is the total rate of thermal radiation emitted by a perfect radiator per unit surface area [10].

$$E_b = \sigma T_s^4 \tag{2.6}$$

A blackbody is an object that absorbs all the radiant energy reaching its surface,  $\alpha = 1$ . Where  $\sigma$  is Stefan-Boltzmann constant and  $T_s$  is the absolute surface temperature.

For non-blackbody surfaces the total emissive power is generally given in the following form:

$$E = \varepsilon E_b = \varepsilon \sigma T_s^4 \tag{2.7}$$

Where the emissivity ( $\varepsilon$ ) can have a value between zero and one.

The total radiative heat flux that arrives at a body is called *irradiation*, *G*. The thermal irradiation received by a surface is distributed as follows (see Figure 2.4):

Thermal radiation flux absorbed =  $\alpha G$

Thermal radiation flux reflected =  $\rho G$

Thermal radiation flux transmitted =  $\tau G$

Considering an opaque surface, the total radiative heat flux that leaves the body is called *radiosity*, J [9].

$$J = \rho G + \varepsilon \sigma T^{4} \tag{2.8}$$

Therefore the net radiative heat flux into the body is obtained according to equation (2.9).

$$q = G - J \to q = (1 - \rho)G - \varepsilon\sigma T^{4}$$

(2.9)

If the surface is diffusive-gray (gray body is a surface whose emissivity is independent of the electromagnetic wavelength) and opaque then the net radiative heat flux into a boundary is:

$$\rho = \varepsilon \to q = \varepsilon (G - \sigma T^{4}) \tag{2.10}$$

Consequently, heat transfer equation is defined as in equation (2.11), when heat is transferred by conduction and radiation.

$$\rho C_{p} \frac{\partial T}{\partial t} + \nabla (-k\nabla T) = Q + \varepsilon (G - \sigma T^{*}) \quad (2.11)$$

### **2.3 Heat Convection**

When a fluid flows over a solid, with different temperature than the solid, the process of heat transfer is called *Convection*. Heat convection is generally the conduction mechanism of heat transfer when the heat source is external; therefore, heat conduction has primary roll in heat convection.

#### 2.3.1 Newton's Law of Viscosity

Newton's Law of Viscosity describes the velocity of a flowing liquid. Newton viewed laminar flow as the behavior of a liquid separating two solid parallel plates [9] as

$$\mu = \frac{Fy}{Au} \tag{2.12}$$

where  $\mu$  is the viscosity (kg/ms), F is the shear force (kg.m/s<sup>2</sup>), y is the distance between the plates (m), A is the area of each plate (m<sup>2</sup>), and u is the fluid velocity, (m/s).

Therefore, the shear stress is defined as:

$$\tau = \frac{dF}{dA} = \mu \frac{\partial u}{\partial y}$$

(2.13)

#### 2.3.2 Newton's Law of Cooling

Newton's law of cooling states that the rate of cooling of an object is proportional to the temperature difference between the object and its surroundings [9].

$$\frac{dT}{dt} = -k(T - T_a) \tag{2.14}$$

In equation (2.14),  $T_a$  is the ambient temperature, T is the temperature of the solid and k is a positive constant.

Applying Newton's law, the local convection heat flux of a fluid passing over a surface is expressed as:

$$q'' = h(T_s - T)$$

(2.15)

Where  $T_s$  is the surface temperature and h is the local convection coefficient.

Since the heat convection coefficient and local heat flux vary by the flow conditions, the total heat flux rate is defined as follows:

$$q = \int_{A_s} q'' dA_s \tag{2.16}$$

This leads to another way of expressing total heat flux, equation (2.17).

$$q = h(T_s - T) \tag{2.17}$$

Where  $\overline{h}$  is the *mean coefficient of heat transfer*. It has SI units of (W/(m<sup>2°</sup>K)). It depends on flow regimes, fluids and thermodynamic conditions.

Therefore, heat transfer equation is defined as follow (considering heat is transferred by all types of the above mechanisms) [12]:

$$\rho C_{p} \frac{\partial T}{\partial t} + \nabla (-k\nabla T) = Q + \varepsilon (G - \sigma T') + \overline{h} (T_{s} - T)$$

(2.18)

where  $\rho C_p \frac{\partial T}{\partial t}$  represents the rate of energy increase in the solids,  $-k\nabla T$  is the heat conduction term, and the right side of the equation represents the heat generation amount in the system.

For most electronic component, heat conduction is the most important heat transfer phenomenon; therefore most researchers consider a component that has thermal conduction as its only mode of internal heat transfer. Therefore equation (2.18) can be expressed as:

$$\rho C_{p} \frac{\partial T}{\partial t} + \nabla (-k\nabla T) = Q \qquad (2.19)$$

## 2.4 Boundary and Initial Conditions

A boundary condition is a mathematical concept relevant to the dependent variable, which in this case is temperature, T. Defining boundary conditions are necessary to solve any differential equation. Number of required boundary conditions for an ordinary differential equation is equal to the highest-order derivative of the equation.

If the heat transfer is unsteady, there must be an initial condition or initial spatial distribution known for temperature at t = 0.

The heat conduction equation given in (2.19) is subjected to the general boundary condition:

$$k\frac{\partial T}{\partial n} + hT = F \tag{2.20}$$

and the initial temperature condition:

$$T(t=0) = G \tag{2.21}$$

F and G are the arbitrary functions, and n is the outward direction normal to the surface.

The following three types of thermal boundary conditions are the most common boundaries which can be applied to the electronics' object boundaries, depending on the packaging materials and the surrounding environment.

Isothermal (Dirichlet):

$$T = F(x, y, z, t)$$

(2.22)

Insulated (Neumann):

$$\frac{\partial T}{\partial n} = 0$$

(2.23)

Convective (Robin):

$$k \frac{\partial T}{\partial n} = h(T - T_{ambient})$$

(2.24)

Where T<sub>ambient</sub> is the ambient temperature.

To solve the boundary value problem of heat conduction, many existing analytical or numerical approaches are available. This will be addressed in the next chapter.

# 2.5 Summary

Heat transfer mechanisms (Conduction, Convection, and Radiation) and governing equations are introduced. For most electronic component, heat conduction is the most important heat transfer phenomenon; therefore most researchers consider a component that has thermal conduction as its only mode of internal heat transfer.

The thermal boundary conditions and the initial temperature condition are given. The three thermal boundary conditions are: Isothermal, Insulated and Convective.

# Chapter 3

This chapter is an introduction to different types of analysis for the heat transfer equation obtained in chapter 2. Numerical and analytical approaches are briefly introduced in this part.

# 3. Thermal Analysis

In this research we performed the thermal analysis on integrated circuits without forced heat convection for the cooling system and heat was mainly transferred by conduction; hence, for the thermal analysis, the other two mechanisms of heat transfer are neglected. Consequently, the main focus is on the procedures that are developed to analyze conduction-heat-transfer systems.

There are different methods to solve heat conduction equations such as, Fourier series, Finite element method (FEM), Finite difference method (FDM), Boundary element method (BEM), Analytical approaches, Thermal network and Extraction approximation approaches. Figure (3.1) shows different approaches for thermal analysis.

Figure 3.1: Thermal modeling approach [8].

# **3.1 Fourier Series**

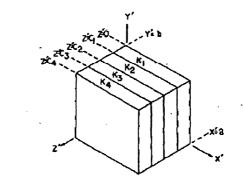

One of the primary methods to solve heat transfer equation is Fourier series. Considering Figure (3.2) as the thermal structure of an IC and its packaging, it has four layers of different types of materials with different thermal conductivities.

Figure 3.2: Thermal model of an IC and its packaging [13].

The only heat source is located at the z = 0 coordinate. It can be expanded for more than one heat source employing superposition. Considering the steady state heat transfer equation with uniform thermal conductivity (k):

$$\nabla^2 T = -\left(\frac{1}{k}\right)Q\tag{3.1}$$

The boundary conditions are defined according to boundaries of layers. Both temperature at field point r' and the source heat dissipation per unit volume parameters are expanded in a double Fourier cosine series to obtain:

$$Q(r') = \sum_{\alpha} \sum_{\beta} \varepsilon_{\alpha} \varepsilon_{\beta} \phi_{\alpha\beta}(z') \cos \alpha x' \cos \beta y'$$

(3.2)

$$T(r') = \sum_{\alpha} \sum_{\beta} \varepsilon_{\alpha} \varepsilon_{\beta} \psi_{\alpha\beta}(z') \cos \alpha x' \cos \beta y'$$

(3.3)

where

$$\alpha = \frac{l\pi}{a}, \beta = \frac{m\pi}{b}, m, l = 0, 1, 2, 3, \dots$$

and  $\varepsilon_{\alpha} = \begin{cases} \frac{l}{2}, \alpha = 0\\ l, \alpha \neq 0 \end{cases}, \varepsilon_{\beta} = \begin{cases} \frac{l}{2}, \beta = 0\\ l, \beta \neq 0 \end{cases}$

where a and b are the package dimensions at the x and y directions of a three dimensional coordinate system respectively. The Fourier coefficients  $\phi_{\alpha\beta}$  are given by:

$$\phi_{\alpha\beta}(z') = \left(\frac{4}{ab}\right) \int_{x'=0}^{a} \int_{y'=0}^{b} Q(r') \cos \alpha x' \cos \beta y' dx' dy'$$

(3.4)

The surface source Q(r') at z = 0 is:

$$Q(z') = q(x'y')\delta(z')$$

(3.5)

q(x'y') is source heat dissipation per unit area and  $\delta(z')$  is the Dirac delta function.

In all the above equations, the Fourier coefficients  $\psi_{\alpha\beta}$  are unknown and are not simply computed. They are calculated by means of Green's function which has been elaborated in [13].

This method is computationally very complex when temperature variations with time and thermal conductivity variations with temperature are considered. It becomes more complex when additional layers and heat sources are added to the thermal structure.

#### **3.2 Finite Element Method**

Finite element method (FEM) was first developed for problems in stress analysis of solids and structural systems. However, its power and wide applicably can be fully recognized when it is applied on nonstructural problems: heat transfer and fluid flow [14]. FEM is a *discretization* method. It is a subdivision of a mathematical model into nonoverlapping components of simple geometry. The response of each element is characterized by the finite number of degrees of freedoms (DOFs) [14].

Considering a system that has finite number of DOFs. DOFs are collected in a column vector u, also called state vector. For a set of DOFs there is a set of conjugate quantities called *forces* which are the factors of change. They are also collected in a column vector f. The relation between u and f is assumed linear and homogenous. If u vanishes so does f. Equation (3.6) shows the relation between f and u.

$$K \times u = f \tag{3.6}$$

K is called the *stiffness matrix*. The physical meaning of u and f varies according to the modeled application. In case of heat transfer modeling, u represents temperature and f represents heat flux.

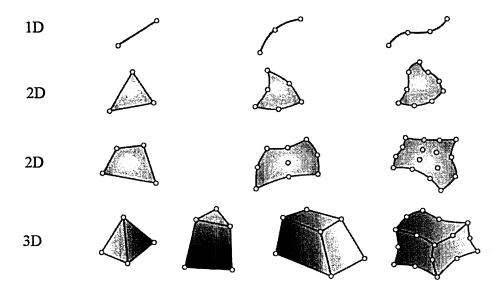

In direct stiffness method elements are disconnected from their neighbors by disconnecting the nodes; then, each element is modeled by a generic element. Figure (3.3) illustrates some typical generic elements for 1D, 2D and 3D geometries.

Figure 3.3: Some typical generic elements for 1D, 2D and 3D mesh geometries [15].

To analyze a discrete system the following steps are required [14]:

1. System Idealization, in which the actual system is idealized as an assemblage of elements.

2. Element Equilibrium, in which the equilibrium requirements of each element are recognized by state variables.

3. Element Assemblage, in which the element interconnection requirements are applied to recognize the set of simultaneous equations for the unknown state variables.

4. Solution of Response, in which the simultaneous equations are solved for the state variables and using the element requirements the response of each element can be calculated.

To develop a finite element solution scheme on heat transfer equation, we consider the heat conduction equation in electronic components (see section 2.3, equation (2.19)), given by

$$\rho C_{p} \frac{\partial T}{\partial t} + \nabla (-k\nabla T) = Q(T)$$

(3.7)

A discretization based on variation Galerkin procedures gives, after integration by parts of the  $(-k\nabla T)$  term, the problem

$$\delta \Pi = \int_{\Omega} \delta T \rho C_p \frac{\partial T}{\partial t} d\Omega + \int_{\Omega} (\nabla \delta T) (-k \nabla T) d\Omega - \int_{\Omega} \delta T Q(T) d\Omega - \int_{\Gamma} \delta T (-k \nabla T)_n d\Gamma = 0 \quad (3.8)$$

Where  $\delta$  denotes "variation in".

This variation (weak) formulation is still valid even if the term  $(-k\nabla T)$  and/or Q (indeed the boundary conditions) are dependent on T or its derivatives. Introducing the interpolations

$T = N\overline{T}$  and  $\delta T = N\delta\overline{T}$ , a discretized form of (3.8) is given as:  $f(\overline{T}) - C(\overline{T}) - P(\overline{T}) = 0$  (3.9)

Where

$$f = \int_{\Omega} N^{T} Q(T) d\Omega - \int_{\Gamma} N^{T} (-k\nabla T)_{n} d\Gamma$$

$$C = \int_{\Omega} N^{T} \rho C_{p} N d\Omega$$

$$P = \int_{\Omega} N^{T} (-k\nabla T) d\Omega$$

For steady state heat analysis the equation (3.9) can be written as:  $P(\overline{T}) = f(\overline{T})$ .

Equation (3.9) states the equilibrium of heat flow at all time. To discritize this equation, we consider the first step of Newton-Raphson iteration for the heat flow equilibrium in which:

$${}^{\prime+\Delta t}T^{(i)} = {}^{\prime+\Delta t}T^{(i-1)} + \Delta T^{(i)}$$

(3.10)

where i is the number of iteration.

Therefore, at time  $t+\Delta t$  and for element m:

$$^{I+\Delta I}T^{(m)} = H^{m\,I+\Delta I}T$$

(3.11)

$$^{\iota+\Delta\iota}T^{\prime(m)} = B^{m\,\iota+\Delta\iota}T \tag{3.12}$$

Hence,  ${}^{t+\Delta t}T$  a vector of all nodal point temperatures at time  $t + \Delta t$  is defined as:

$$^{t+\Delta t}T^{T} = \begin{bmatrix} t+\Delta t T_{1} & t+\Delta t T_{2} & \dots & t+\Delta t T_{n} \end{bmatrix}$$

(3.13)

$H^m$  is the element temperature matrix and  $B^m$  is the temperature gradient interpolation matrix [14].

#### **3.3 Finite Difference Method**

The basic concept of the finite difference approach is to approximate the partial derivative of a given point by a derivative taken over a finite interval across that point. Let f(x) be a function which is finite, continuous and single valued. The derivative of f(x) at point  $x_i$  can be approximated by the following difference equation:

$$\left. \frac{df(x)}{dx} \right|_{x_i} = \frac{f(x_i + \Delta x) - f(x_i - \Delta x)}{2\Delta x}$$

(3.14)

Where  $(x_i + \Delta x)$  and  $(x_i - \Delta x)$  are the two neighboring points. The central finite difference approximation of the second derivative of f(x) can be written as:

$$\frac{\left. \frac{d^2 f(x)}{dx^2} \right|_{x_i} = \frac{f(x_i + \Delta x) + f(x_i - \Delta x) - 2f(x_i)}{\Delta x^2}$$

(3.15)

The finite difference expression of (3.14) and (3.15) can be applied to equation (2.19) with respect to the time domain and the space domain. The object under simulation is first discretized into many space grid point  $x_i$  and the algebraic difference equations are obtained for each  $x_i$ . The resulting set of equations that represent all grid points can be solved for the successive time points provided that temperature distribution at t = 0 is known.

Here, we explained this method for 2D system. It can be expanded for 3D analysis.

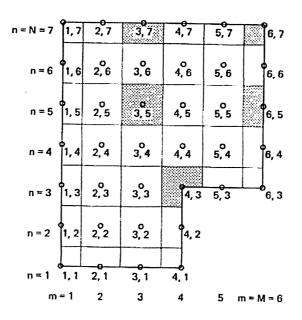

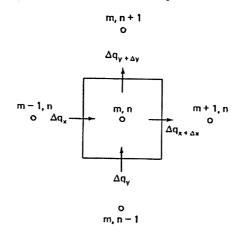

For 2D analysis the dimensions of each subvolume is  $\Delta x \Delta y \delta$  where  $\delta$  is the thickness of the plate, as shown in Figure (3.4). To provide such a network the horizontal and vertical

construction lines are primarily sketched which are  $\Delta x$  and  $\Delta y$  apart. In general,  $\Delta x$  and  $\Delta y$  are equal. To create the subvolumes, horizontal and vertical lines are drawn in the middle of each two construction lines.

Figure 3.4: Network of subvolumes and nodes of a rectangular solid. Shading indicates representative interior and exterior nodes [10].

The resulting network is represented by nodes. The nodes are located at the intersections of construction lines. Each subvolume is treated as a lumped subsystem. The mass of each subvolume is considered to be located at the node and the temperature of the node represents the mean temperature of the subvolume. The distance between two adjacent nodes is  $\Delta x$  and  $\Delta y$ . The coordinates x, y of each node are equal to  $(m-1).\Delta x$  and  $(n-1).\Delta y$ , respectively, where *m* is an integer value in the rage of [1, M] and *n* is an integer value in the range of [1, N]. M and N are the total number of nodes in x and y directions, correspondingly.

Figures (3.5a-e) illustrates different types of locations of nodes.

To solve the heat conduction differential equation, first law of thermodynamics needs to be applied on each node. For instance, for Figure (3.5a) it is written as:

$$\Delta q_{x} + \Delta q_{y} + q' \Delta V = \Delta q_{x+\nabla x} + \Delta q_{y+\nabla y} + \frac{\Delta E_{s}}{\Delta t}$$

(3.16)

where q' is the internal energy of the subvolume. In case of steady conduction heat transfer,  $\frac{\Delta E_s}{\Delta t} = 0$ .

Applying simple difference approximations for the Fourier's law, the equation can be simplified into an algebraic equation:

$$\frac{\left(T_{m-l,n} + T_{m+l,n} - 2T_{m,n}\right)}{\Delta x^2} + \frac{\left(T_{m,n-l} + T_{m,n+l} - 2T_{m,n}\right)}{\Delta y^2} + \frac{q'}{k} = 0 \quad (3.17)$$

where  $T_{m,n}$  is the temperature of the node located at x, y.

## **3.4 Boundary Element Method**

Boundary element method is a numerical technique which solves boundary integral equations. This method is very similar to FEM. It is a *discretization* method, which enforces boundary elements along the material interfaces and obtains a set of boundary integral equations [16]. By disritizing the boundaries into boundary elements a set of linear equations are obtained. Variables at any point of space may be attained by performing integration associated with the equivalent sources at the boundaries.

#### **3.5 Analytical Solution**

In analytical solution or differential formulation the heat conduction equation is solved directly. There are three steps to solve the equation.

Considering  $T_i$  as the initial temperature and q' as the internal energy generated per unit volume, according to the *first law of thermodynamics* we obtain:

$$dq_{x} + dq_{y} + dq_{z} + q'dV = dq_{x+dx} + dq_{y+dy} + dq_{z+dz} + \frac{\partial(\rho dVC_{v}T)}{\partial t}$$

(3.18)

*First law of thermodynamics* (conservation of energy) expresses that the change in internal energy of a system is equal to the heat added to the system minus the work done by the system [10].

Utilizing the definition of partial derivative the following replacement is applied:

$$dq_{x+dx} = dq_x + \frac{\partial(dq_x)}{\partial x}dx \qquad (3.19)$$

Similarly, equations for  $dq_{y+dy}$ ,  $dq_{z+dz}$  are obtained.

Therefore, equation (3.18) changes to:

$$q'dV = \frac{\partial(dq_x)}{\partial x}dx + \frac{\partial(dq_y)}{\partial y}dy + \frac{\partial(dq_z)}{\partial z}dz + \frac{\partial(\rho dVC_v T)}{\partial t} \quad (3.20)$$

Implementing Fourier's law of conduction and dividing through by differential volumes, it revised to:

$$\frac{\partial}{\partial x} \left( \frac{k \partial T}{\partial x} \right) + \frac{\partial}{\partial y} \left( \frac{k \partial T}{\partial y} \right) + \frac{\partial}{\partial z} \left( \frac{k \partial T}{\partial z} \right) + q' dV = \frac{\partial (\rho C_{\nu} T)}{\partial t}$$

(3.21)

Equation (3.21) can be further simplified if  $k, \rho, C_{\nu}$  are considered constant values.

## **3.6 Thermal Network**

Since there are analogies between heat transfer and flow of electric current, FDM concept is put into the form of a RC network. Table 3.1 explains this analogy [10].

| Electrical                       | Thermal                        |

|----------------------------------|--------------------------------|

| E <sub>e</sub> : Voltage (V)     | T: Temperature (°C)            |

| I <sub>e</sub> : Current (A)     | q: Rate of Heat Transfer (W)   |

| $R_e$ : Resistance ( $\Omega$ )  | R: Thermal Resistance (°C/W)   |

| C <sub>e</sub> : Capacitance (F) | C: Thermal Capacitance (J/ °C) |

Table 3.1: Electrical Analogy.

In addition, comparing Fourier equation to the differential equation for voltage distribution in an electrically conducting multidimensional system shows that an electrical

field set up within an electrical conductor corresponds to the thermal field in the modeled heat transfer problem.

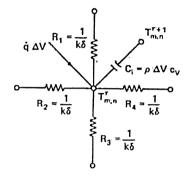

Considering Figure (3.6), which is a subvolume of a 2D finite difference model with interior node, an energy balance on this node is developed as follows:

Figure 3.6: Interior finite-difference subvolume [10].

$$q'\Delta V + \Delta q_x + \Delta q_y - \Delta q_{x+\nabla x} - \Delta q_{y+\nabla y} = \frac{\Delta E_s}{\Delta t}$$

(3.22)

Applying Fourier's law of conduction we obtain:

$$\Delta q_{x} = -k\delta\Delta y \frac{T_{m,n}^{\tau} - T_{m-l,n}^{\tau}}{\Delta x} = \frac{T_{m-l,n}^{\tau} - T_{m,n}^{\tau}}{1/(\delta k)}$$

(3.23)

$$\Delta q_{x+\Delta x} = \frac{T_{m,n}^{\tau} - T_{m+1,n}^{\tau}}{1/(\delta k)}$$

(3.24)

$$\Delta q_{y} = \frac{T_{m,n-l}^{\tau} - T_{m,n}^{\tau}}{1/(\delta k)}$$

(3.25)

$$\Delta q_{y+\Delta y} = \frac{T_{m,n}^{\tau} - T_{m,n+1}^{\tau}}{1/(\delta k)}$$

(3.26)

Considering  $R = 1/(\delta k)$  and  $C = \rho C_v \nabla V$  equation (3.22) is revised to:

$$q'\Delta V + \sum \frac{T_i^{\tau} - T_{m,n}^{\tau}}{R_i} = C_i \frac{T_{m,n}^{\tau+1} - T_{m,n}^{\tau}}{\Delta t}$$

(3.27)

The above equation shows that the summation of the currents flowing into the node (m, n) from the surroundings is equal to the flow of current into the capacitor. In a steady state

situation no current flows into the capacitor and the summation of the currents is zero, since  $T_{m,n}^{r+1} = T_{m,n}^{r}$ .

Note that equation (3.27) must assure stability requirements that restrict  $\Delta t$ . In case of severe restrictions, equation (3.27) can be written as:

$$q'\Delta V + \sum \frac{T_{i}^{\tau} - T_{m,n}^{\tau}}{R_{i}} = C_{i} \frac{T_{m,n}^{\tau} - T_{m,n}^{\tau-1}}{\Delta t}$$

(3.28)

Figure (3.7), illustrates the equivalent thermal network of Figure (3.6).

Figure 3.7: Equivalent thermal network for interior subvolume [10].

Applying similar calculations, RC network can be developed for subvolumes with exterior nodes, which is shown in Figure (3.8b).

Figure 3.8: a) Exterior finite-difference subvolume. b) Equivalent thermal network for exterior subvolume [10].

## 3.7 Summary

So far different thermal analysis methods have been reviewed. In general, the numerical method is more powerful and can be more easily applied to various kinds of heat conduction problems (e.g. linear, non-linear, homogeneous, non-homogeneous). The analytical method, on the other hand, is more restrictive in solving complex problems. For instance, if the thermal conductivity (k) is temperature dependent, some variable transformation technique may need to be used to simplify the original problem.

Finite element method (FEM) is chosen in this research as the numerical thermal simulation method. This is one of the most popular numerical methods used by design engineers in today's product design process in industry. The great advantage of FEM programs is their generality since they can simulate structures with arbitrarily complex geometries. In case of thermal analysis on VLSI circuits, FEM simulators are more accurate especially when the packaging of the IC is also considered. FEM is computationally less complex compare to methods such as Fourier series, FDM and thermal network.

# **Chapter 4**

In this chapter SPICE electrical simulator is briefly explained. SPICE is the implemented electrical simulator in our research work to perform electrical analysis. SPICE model of a bipolar junction transistor is also expanded, since our major focus is on BJT circuits.

To illustrate the temperature dependency of BJT parameters, their variations with temperature, which are obtained by experiments, are presented. The deficiency of SPICE simulators to consider temperature in simulations is also discussed.

The importance of power dissipation of VLSI circuits is also presented and the effects of power dissipation on circuit performance and junction temperature are briefly investigated.

# 4. Electrical Analysis

To perform an electrical analysis on an integrated circuit an electrical circuit simulator is needed. Every circuit simulator has a library which includes model definitions for each element type. In these models a set of equations are defined to specify the characteristics of the element.

One of the primary circuit simulators is called SPICE (Simulation Program with Integrated Circuits Emphasis) which was originally developed at the electronic research laboratory of the University of California, Berkeley in 1975. There are different versions of SPICE such as PSpice which is a PC version of SPICE and HSpice which runs on UNIX workstations and large computers. HSpice is the fast version of SPICE and is normally used. In this research we used PSpice as the electrical simulator [6].

## **4.1 BJT SPICE Model**

Bipolar Junction Transistor was the first solid state amplifier, which revolutionized the solid state electronics. BJT has many advantages over other types of transistors in terms of speed, current drive, transcunductance and noise figure. These advantages make BJT suitable in applications for ultra high speed discrete logic circuits such as emitter coupled logic (ECL), power switching applications and in microwave power amplifiers. They are also used in electrical circuits where current needs to be controlled. Some of the areas are: switching elements to control DC power to a load, amplifiers for analog signals, and 3-phase AC motors [17].

All the above applications of a BJT are directly dependent on its operating point and therefore its power dissipation. Since BJT is very sensitive to temperature variations, any changes in the device junction temperature or the temperature of the surrounding environment can cause changes in the device operating point and power dissipation. Temperature variations may also cause device failure; hence, failure of the entire circuit.

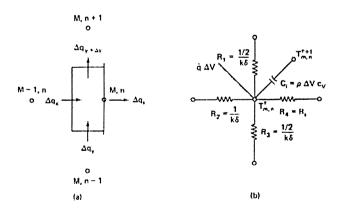

There are two main models for a BJT: Eber-Molls model and Gummel-Poon model. In today's SPICE simulators the latter is employed, since it considers the second order effect, therefore, it is more accurate in high and low current levels [18]. Figure (4.1) shows PSpice model of a BJT.

Figure 4.1: BJT SPICE model [19].

For DC current, the bipolar equation system is defined as follows:

$$I_{b} = \frac{I_{bel}}{\beta_{F}} + I_{be2} + \frac{I_{bcl}}{\beta_{R}} + I_{bc2}$$

(4.1)

$$I_{c} = \frac{I_{bel}}{K_{qb}} - \frac{I_{bcl}}{K_{qb}} - \frac{I_{bcl}}{\beta_{R}} - I_{bc2}$$

(4.2)

$$I_{bel} = I_{S}.(e^{V_{be}/(N_{F}.V_{t})} - 1)$$

(4.3)

$$I_{be2} = I_{SE} \cdot (e^{V_{be} \cdot (N_E \cdot V_I)} - 1)$$

(4.4)

$$I_{bcl} = I_{S} \cdot (e^{V_{bc} \cdot (N_{C} \cdot V_{l})} - 1)$$

(4.5)

$$I_{bc2} = I_{SC} \cdot (e^{V_{bc} \cdot (N_C \cdot V_t)} - 1)$$

(4.6)

$$K_{qb} = K_{qI} \cdot (1 + (1 + 4K_{q2})^{N_K})/2 \quad (4.7)$$

$$K_{qI} = \frac{I}{1 - V_{bc} / V_{AF} - V_{be} / V_{AR}}$$

(4.8)

$$K_{q2} = \frac{I_{bel}}{I_{KF}} - \frac{I_{bcl}}{I_{KR}}$$

(4.9)

$$V_{t} = \frac{K.T}{q} \tag{4.10}$$

All the parameters are defined in Table 4.2.

Similar to other transistors, BJTs are utilized for applications such as current sources, amplifiers and switches. Reliable BJT current sources, amplifiers and switches need to have stable collector current, stable forward current gain and stable base-emitter voltage, respectively. Nonetheless, all these parameters are temperature variables and strongly depend on device temperature. Table (4.1) indicates an example of these variations [20].

|                      | -      | -         |       |  |

|----------------------|--------|-----------|-------|--|

| T (°C)               | -65    | 25        | 175   |  |

| I <sub>SC</sub> (nA) | 1.9e-3 | 1.0 33000 |       |  |

| β <sub>F</sub>       | 25     | 55        | 100   |  |

| V <sub>BE</sub> (V)  | 0.78   | 0.60      | 0.225 |  |

Table 4.1: Some BJT parameters variations with temperature.

The following represents temperature dependent equations for some parameters that significantly affect the behavior of a BJT in DC applications.

$$I_{S}(T) = I_{S}.e^{(T_{Tnom}^{-1}).(E_{N,V_{t}}^{E})}.(\frac{T}{Tnom})^{XTI_{N}}$$

(4.11)

$$I_{SE}(T) = (I_{SE} / (\frac{T}{Tnom})^{XTB}) \cdot e^{(T_{Tnom}^{-I}) \cdot (\frac{Eg}{N_E \cdot V_I})} \cdot (\frac{T}{Tnom})^{XTI_{NE}}$$

(4.12)

$$I_{SC}(T) = (I_{SC} / (\frac{T}{Tnom})^{XTB}) e^{(T_{Tnom}^{-1}) (E_{N_{C},V_{I}}^{E})} (\frac{T}{Tnom})^{XTI_{N_{C}}}$$

(4.13)

$$I_{SS}(T) = (I_{SS} / (\frac{T}{Tnom})^{XTB}) \cdot e^{(T/_{Tnom} - 1) \cdot (Eg/_{N_S, V_t})} \cdot (\frac{T}{Tnom})^{XTI/_{N_S}}$$

(4.14)

$$\beta_F(T) = \beta_F \cdot \left(\frac{T}{Tnom}\right)^{XTB} \tag{4.15}$$

$$\beta_R(T) = \beta_R \cdot \left(\frac{T}{Tnom}\right)^{XTB} \tag{4.16}$$

#### Table 4.2: Parameters definitions.

| $\beta_F$         | Ideal Maximum Forward Beta                    |

|-------------------|-----------------------------------------------|

| $\beta_R$         | Ideal Maximum Reverse Beta                    |

| Eg                | Energy Bandgap                                |

| I <sub>KF</sub>   | Corner for Forward-Beta High-Current Roll-Off |

| I <sub>KR</sub>   | Corner for Reverse-Beta High-Current Roll-Off |

| I <sub>b</sub>    | Base Current                                  |

| Ic                | Collector Current                             |

| Ibel              | Forward Diffusion Current                     |

| I <sub>be2</sub>  | Non-ideal Base-Emitter Current                |

| I <sub>bc</sub> 1 | Reverse Diffusion Current                     |

| I <sub>bc2</sub>  | Non-ideal Base-Collector Current              |

| Is                | Transport Saturation Current                  |

| ISC               | Base-Collector Leakage Saturation Current     |

| I <sub>SE</sub>   | Base-Emitter Leakage Saturation Current       |

| I <sub>SS</sub>   | Substrate p-n Saturation Current              |

| I                 |                                               |

| k               | Boltzman's Constant                              |

|-----------------|--------------------------------------------------|

| q               | Electron Charge                                  |

| $K_{qb}$        | Base Charge Factor                               |

| $N_F$           | Forward Current Emission Coefficient             |

| N <sub>E</sub>  | Base-Emitter Leakage Current Coefficient         |

| N <sub>C</sub>  | Base-Collector Leakage Current Coefficient       |

| N <sub>R</sub>  | Reverse Current Emission Coefficient             |

| N <sub>K</sub>  | High-Current Roll-Off Coefficient                |

| Ns              | Substrate p-n Emission Coefficient               |

| V <sub>be</sub> | Built-in Base-Emitter Voltage                    |

| V <sub>bc</sub> | Built-in Base-Collector Voltage                  |

| V <sub>AF</sub> | Forward Early Voltage                            |

| V <sub>AR</sub> | Reverse Early Voltage                            |

| Tnom            | Reference Temperature                            |

| XTI             | Temperature Effect Exponent                      |

| XTB             | Forward and Reverse Beta Temperature Coefficient |

|                 | l                                                |

The equations show that temperature variations can significantly affect the operation of a bipolar transistor, especially the scaling of transistor geometries that increase current density and thermal spreading impedances [21].

## 4.2 Temperature Effects on BJT Parameters

In this part we will review some experimental results regarding BJT parameter variations with temperature.

Fundamentals of a BJT operation are based on carrier mobility which is a temperature dependent factor. Figure (4.2) and Figure (4.3) indicate temperature reliance of electron and hole mobility for different doping concentration obtained by experiments [22].

Figure 4.2: Electron mobility variations vs. temperature [22].

Figure 4.3: Hole mobility variations vs. temperature [22].

These curves show that electron and hole mobility decreases with increase in temperature. In case of an NPN BJT, it results in reduction of base and collector transient time.

Variations of Base transient time,  $\tau_{BT}$ , Collector transient time and charging time,  $\tau_{CT}$  and  $\tau_{C}$ , and Emitter charging time,  $\tau_{E}$ , are obtained according to Figure (4.4) for an NPN BJT [23].

Figure 4.4: Collector, Emitter and Base transient and charging time variations with temperature [23].

Decrease in the base and collector transient time while increase in emitter and collector charging time reduces the device switching speed and cut-off frequency.

Figure (4.5) indicates the variations of cut-off frequency,  $f_T$ , versus temperature attained by observation [23]. Reduction of  $f_T$  influences the current gain and device efficiency.

Figure 4.5: BJT cut-off frequency variations with temperature [23].

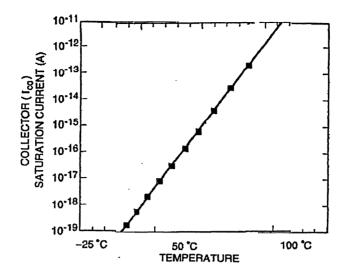

Figure (4.6) shows variations of collector saturation current versus temperature, when the device works at high temperatures. It shows that as temperature increases the saturation current increases accordingly. Variations in  $I_{co}$  cause variations of the device collector current. This is very critical mainly if the device is operating as a current source, as it needs a constant collector current [24].

Figure 4.6: Collector saturation current variations with temperature [24].

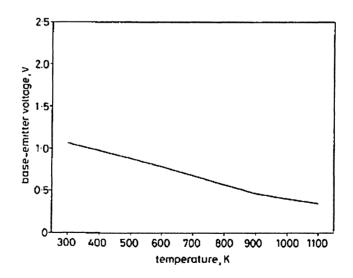

Figure (4.7) illustrates the Base-Emitter voltage,  $V_{BE}$ , variations with temperature. It shows that  $V_{BE}$  decreases with temperature increase.  $V_{BE}$  is a very important parameter in a BJT performance. It indicates the region of the device operation. For instance, variations in  $V_{BE}$  may change BJT operating as a current source into a resistor [23].

Figure 4.7: Base-Emitter voltage variations versus temperature [23].

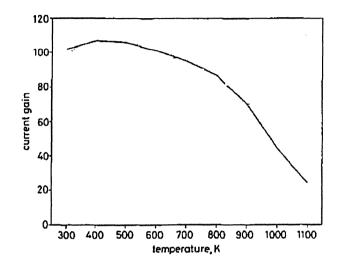

Figure (4.8) shows variations of BJT current gain versus temperature. Since BJTs are recognized by their high currant gain, it is very critical to be able to determine the current gain accurately [23].

Figure 4.8: Current gain variations with temperature [23].

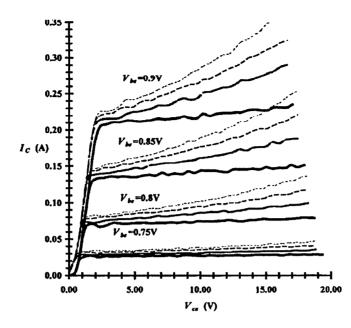

The above graphs confirm that device temperature variations result in changes of the device operating point. Figure (4.9) shows the DC characteristics of an NPN Si BJT for different  $V_{BE}$  as operating time increases. It shows that at a constant  $V_{BE}$  and  $V_{CE}$ ,  $I_c$  increases by time since device junction temperature increases. This data obtained by experiment for a common emitter circuit [25]. The value of  $I_c$  converges to a constant value when device reaches its steady state junction temperature.

Figure 4.9: I-V characteristics of common emitter Si BJT. Data was taken at 4µs (solid line), 40µs (semidashed line), 100µs (dashed line) and 200µs (dotted line) [25].

Figure (4.10) shows power dissipation and efficiency of a Si BJT. It shows that the power dissipation increases by increase of device temperature; therefore, the efficiency decreases [26]. This defect is more significant in high power applications which produce high temperature.

Figure 4.10: BJT power and efficiency variations with temperature [26].

# 4.3 Power Dissipation and Temperature Effects on Integrated Circuits

In 1965 Gordon Moore observed that the total number of devices on a chip doubled every 1.5 year. Today's low cost, high speed electronic devices consisted of multimillion gate ICs prove the validation of Moore's Law [27].

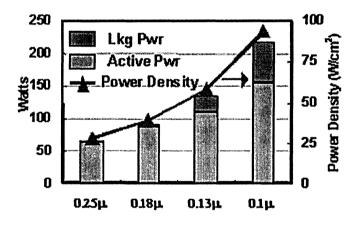

Technology shrinkage culminates in some difficulties; one of them is IC power consumption. Even though many efforts have been performed to reduce IC power supply voltages, the number of devices per chip and their operating frequencies enhance faster than their reduction of power consumption. Figure (4.11) shows power dissipation drifts with technology [27]. It indicates that by decreasing device size its power density increases in contrary. In Figure (4.11), LKg Pwr denotes device Leakage power; it is proportional to the current leakage of the device through its substrate. Active Pwr denotes device Active power. It is the device power dissipation when it is working in its active region.

Figure 4.11: Power density trends [27].

ITRS (International Technology Roadmap for Semiconductors) assigned a maximum allowable power for three of the primary types of electronic products; they are shown in Table (4.3). It shows improvements on the power limitations of ICs over 5 years.

| Allowable Max Power (W) | 2002 | 2003 | 2004 | 2005 | 2006 | 2007 |

|-------------------------|------|------|------|------|------|------|

| High-Performance        | 140  | 150  | 160  | 170  | 180  | 190  |

| Cost-Performance        | 75   | 81   | 85   | 92   | 98   | 104  |

| Hand-Held               | 2.6  | 2.8  | 3.2  | 3.2  | 3.5  | 3.5  |

Table 4.3: Improvement trends for ICs enabled by feature scaling [27].

There are two main sources of power dissipation in a chip, dynamic power dissipation and static power dissipation. Dynamic power is due to charge and discharge of node capacitances of gates and interconnects. It increases as the chip operating frequency rises. Static power is due to leakage current that flows at the silicon substrate. It intensifies by downscaling of the technology.

The electrical power dissipated in devices causes the increase of the inside temperature above the ambient one, as a result of non-ideal conditions of the heat abstraction. Therefore, the mutual interactions between the electrical and the thermal phenomena both in devices and between them exist.

Another important heat generator in an IC is device self heating. Current flowing through a device substrate or chip interconnects creates heat due to their electrical resistance.

Temperature distribution along a chip influences the IC performance. Even if the maximum temperature has not reached, the IC may malfunction due to non-uniform distribution of power consumption along the chip.

Because power consumption and power management of ICs are critical, power analysis become indispensable for IC design and is one of the fields which is currently under extensive investigation. IC power analysis becomes more critical and more important as the number of gates increase. A common goal of power analysis is to accurately calculate the power consumption of the system under analysis.

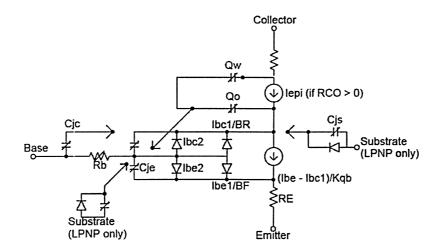

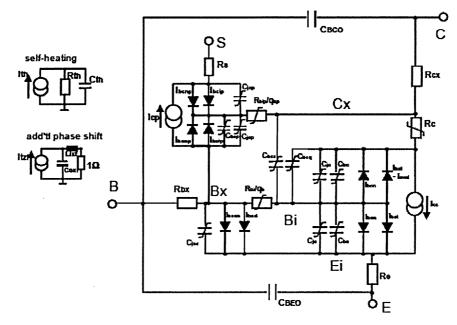

The SPICE-like simulators are usually the analysis engine to perform power analysis. However, SPICE simulators are not able to model all thermal effects (see section 5.1) on a device. In 1995 a new model for bipolar transistors was proposed. It was called VBIC, Vertical Bipolar Intercompany Model. It improved some deficiencies of BJT GP model including self heating effect. Figure (4.12) shows the equivalent schematic of VBIC model. It shows that a simple thermal network has been used for the model. Such a simple thermal circuit is not able to perform accurate thermal analysis and present temperature distribution across the IC. Also, it is not able to consider temperature dependency of thermal conductivity of semiconductors. In case of complex circuits the model is incapable of performing thermal coupling.

Figure 4.12: Equivalent Schematic of VBIC model. [28]

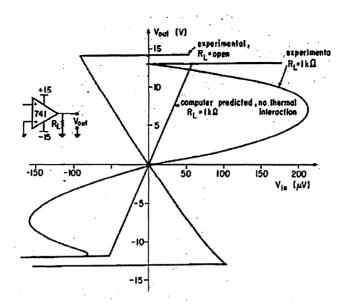

To present an example of limitations of circuit simulators the results of the electrothermal simulation of Op-Amp 741 obtained in [29] is presented. Figure (4.13) shows the DC transfer characteristic of the operational amplifier attained by experiment and computer prediction. It shows a seriously distorted DC transfer curve when the output load resistance,  $R_L$ , is 1 k $\Omega$ . The load results in power dissipation in the output transistors; Hence, increasing their temperature. The heat dissipated at the output transistors propagates inside the chip toward the input transistors; while the input stage of an Op-Amp is very temperature sensitive. This thermal feedback results in a distorted transfer curve [29, 30].

1

Figure 4.13: DC transfer curve of Op-Amp 741[29].

Even though thermal feedback can be reduced by applying special rules to the layout of analog or mixed signal circuits, the need to apply electrothermal analysis on VLSI circuits is still vital.

As discussed above electrical and thermal characteristics of an IC are strongly subjected to each other; therefore, to obtain an accurate estimation of power dissipation and temperature distribution in a chip, electrical and thermal analyses need to be performed simultaneously.

## 4.4 Summary

In this chapter we introduced SPICE electrical simulator, which is the applied electrical simulator in the developed electrothermal simulator. The deficiency of SPICE in regards to device temperature variations was discussed. Since the main focus of this research is on BJTs, BJT SPICE model and its parameters variations with temperature were presented. To confirm the parameters variations with temperature some experimental results were also illustrated.

The effects of increase of power dissipation on VLSI circuits and its consequence on the circuit temperature were discussed.

PROPERTY OF , RYERSON UNIVERSITY LIBRARY

# **Chapter 5**

In this chapter two numerical methods that are implemented to design an electrothermal simulator are introduced. The first one is called the *direct* method. The second method was called the *relaxation* method. For each of these methods the available electrothermal simulators in literatures are described. However, the attention is on the simulators with BJT circuit's application.

# 5. Electrothermal Analysis

As it has been discussed earlier in two previous chapters (chapter 2 and chapter 4), the performance and characteristics of semiconductor components in electronic circuits can be considerably affected by temperature variations. Therefore, accurate circuit simulation requires that the dynamic temperature effects induced by the heat dissipated in the circuit be taken into account. Modeling electrothermal interactions in integrated circuits has been addressed in a variety of ways [31]. Based on the literature and available researches, existing methods can be broadly classified into two major methods: *direct* method and *relaxation* method. In this chapter different techniques that have been designed to perform an electrothermal analysis are examined.

## **5.1 Direct Method**

One way of incorporating thermal effects in a circuit simulator is to make the thermal model look like an electrical circuit. The thermal and electrical problems are then solved simultaneously as if they were one large electrical problem. This strategy is based on transforming the thermal problem into an equivalent electrical problem (see also section 3.6). The iterative solution takes place simultaneously for the electrical and thermal sub-networks. This electrical modeling of thermal characteristics is possible thanks to the similarities that exist between some fundamental electrical and thermal behaviors of solids. Electrical potential difference between two points of a conductor causes electrical charge movements inside it and temperature gradient between two points of a conductor causes heat flows through it. This means different locations within a component and their corresponding temperatures can be modeled by nodes of an electrical network and their corresponding voltages. Amount of heat transferred between two locations and its rate on the other hand can be represented by electric charge and its rate which is electrical current.

Assuming that:

$\Omega_i$ : A physical location inside a component, of node *i* of electrical model.

$T_i$ : Temperature of  $\Omega_i$ .

V<sub>i</sub>: Voltage of node *i*.

$\Delta Q_{ih}$ : Heat flow from one location to another location.

$\Delta Q_e$ : Electrical charge moving from one node to another node.

q: Heat transfer rate from one location to another location.

*I*: Charge transfer rate or electrical current from one node to another node.

The relation between voltage difference and current of an electric conductor is called *Ohm's law*. The relation between temperature gradient and heat transfer rate is called *Fourier's law* (see also section 2.1.1).

*Ohm's law*:  $I = \Delta V/R$ , where R is electrical resistance.

Fourier's law:  $q = \Delta T/R_{th}$ , where  $R_{th}$  is thermal resistance.

Electrical resistance and thermal resistance are dependent to both physical characteristics and physical dimensions of a material.

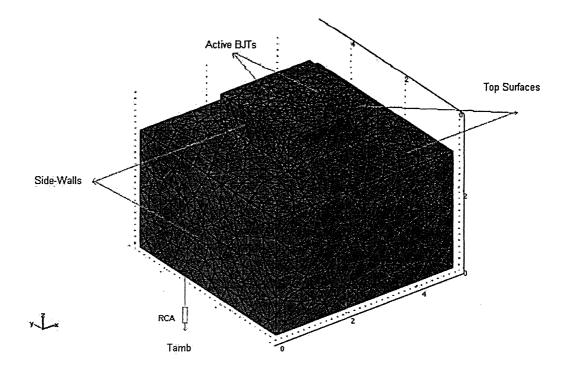

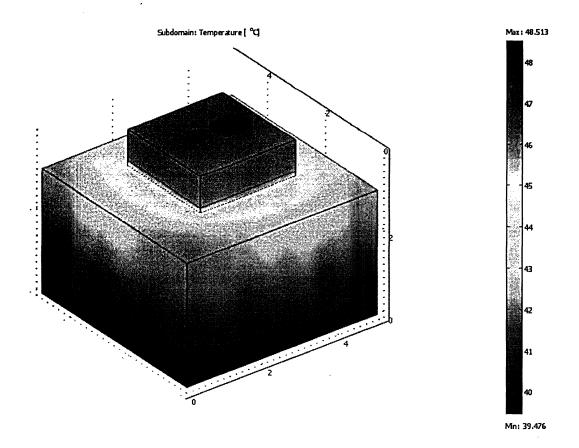

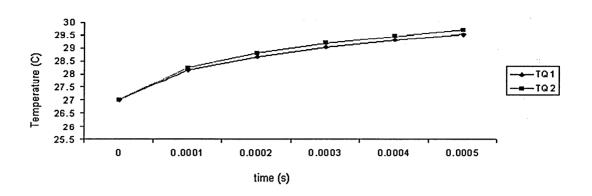

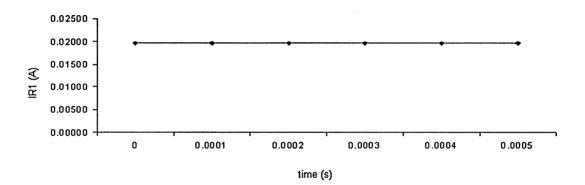

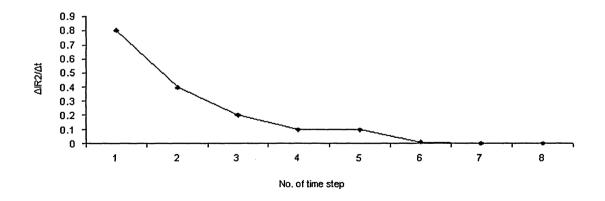

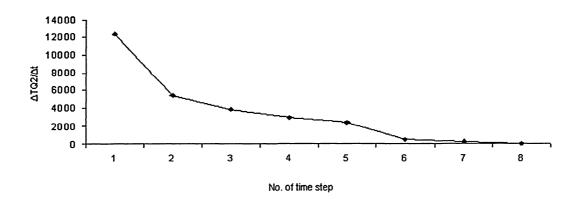

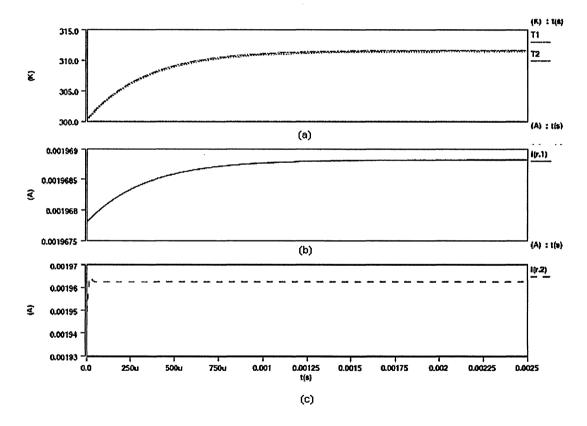

Electrical resistance:  $R = \frac{l}{\sigma} \times \frac{L}{A}$ Thermal resistance:  $R_{lh} = \frac{l}{k} \times \frac{L}{A}$  Where  $\sigma$  represents electrical conductivity of material and k represents thermal conductivity of material. A is the cross section and L is the length of the component.