## DEVELOPMENT AND IMPLEMENTATION OF THE METHOD FOR HIGH RESOLUTION OBJECT TRACKING IN 3D SPACE

by

Spiros Jason Hippolyte

Master of Science in Electrical Engineering, DeVry University, Illinois, U.S.A., 2010. Bachelor of Science in Electronics Engineering Technology. Calgary, Alberta, 2004.

> A project presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Engineering in the Program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2016 © Spiros J. Hippolyte 2016

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A Project

I hereby declare that I am the sole author of this project. This is a true copy of the masters' report, including any required final revisions.

I authorize Ryerson University to lend this masters report to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this masters report by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my masters report may be made electronically available to the public.

## Abstract DEVELOPMENT AND IMPLEMENTATION OF THE METHOD FOR HIGH RESOLUTION OBJECT TRACKING IN 3D SPACE

by

Spiros Jason Hippolyte

Master of Engineering Electrical and Computer Engineering Toronto, Ontario, Canada, 2016 © Spiros J. Hippolyte 2016

The means to track objects in 3D space is paramount to computer vision and robotics. Improving upon prior work of the M.A.R.S. project enabled more accurate object tracking and ranging, required investigation into current techniques of stereo depth estimation, object tracking algorithms and the use of FPGA platforms. The research focused on aviation, ground vehicle and robotic applications of stereo computer vision and image processing methods. The implementation of the project design focused on how to obtain greater disparity resolution from the stereo system while minimizing memory resources. The analysis of the optimal method and then the coding and debugging of the optimal solution was performed to insure inter-operability with the existing system and lay the foundation for further expansion of the system. Comparative analysis of Xilinx FPGA platforms and MATLAB simulation of the concept provided data on hardware resources, improved disparity output and the minimal use of memory.

### Acknowledgements

I wish to thank the support and advise of Victor Dumitriu & Rishabh Kumar, for aiding me in the technical matters relating with this master's report.

### Dedication

To my parents who have supported me in all my endeavours. This paper is a testament and is made manifest thanks to their support and love.

## Table of Contents

| AUTH    | OR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A Project             | ii   |

|---------|---------------------------------------------------------------------|------|

| Abstra  | ct                                                                  | iii  |

| Acknow  | wledgements                                                         | iv   |

| Dedica  | tion                                                                | v    |

| List of | Tables                                                              | viii |

| List of | Figures                                                             | ix   |

| List of | Abbreviations                                                       | X    |

| 1 Int   | troduction                                                          | 1    |

| 1.1     | Motivation                                                          | 1    |

| 1.2     | Objective                                                           | 3    |

| 1.3     | Original Contribution                                               | 4    |

| 1.4     | Organization                                                        | 5    |

| 2 Li    | terature Observations                                               | 6    |

| 2.1     | UAV Tracking                                                        | 6    |

| 2.2     | Landing Quad Rotor UAV's                                            | 9    |

| 2.3     | Stereo computer vision                                              | 12   |

| 2.4     | CAMSHIFT Improved                                                   | 14   |

| 2.5     | AER Object Tracking                                                 | 16   |

| 2.6     | TLD Stereo vision                                                   |      |

| 2.7     | Literature Classification                                           | 21   |

| 3 De    | esign Synthesis                                                     | 22   |

| 3.1     | Research Analysis                                                   | 22   |

| 3.2     | Requirements                                                        | 22   |

| 3.3     | Design Specification                                                | 23   |

| 3.3     | 3.1 High Resolution Stereo System Block (functional specification): | 23   |

| 3.3     | 3.2 High Resolution Stereo System Block (technical specification):  | 24   |

| 3.4     | Design Symbol                                                       | 25   |

| 3.5     | Entity Declaration                                                  |      |

| 3.6     | Design Block Diagram                                                | 27   |

| 3.7     | Process Diagram                                                     |      |

| 3.8     | Model Timing Diagram                                                |      |

| 4 Im    | plementation & Test verification                                    |      |

|     | 4.1      | Module Description                     | 33 |

|-----|----------|----------------------------------------|----|

|     | 4.2      | Functional Overview                    | 33 |

|     | 4.3      | Testing Methods                        | 36 |

|     | 4.4      | Design Implementation & Considerations | 37 |

|     | 4.5      | System Integration & Test              | 38 |

|     | 4.6      | Verification                           | 42 |

| 5   | Com      | parative analysis                      | 49 |

|     | 5.1      | Resource Utilization                   | 51 |

|     | 5.2      | Object Tracking Performance            | 58 |

| 6   | Sum      | mary                                   | 60 |

|     | 6.1      | Conclusion                             | 60 |

|     | 6.2      | Future Work                            | 60 |

| Re  | ference  | es                                     | 61 |

| De  | finition | ns                                     | 64 |

| Inc | lex      |                                        | 65 |

## List of Tables

| Table 1. HiResObjScan Entity Input signals.                              | 26 |

|--------------------------------------------------------------------------|----|

| Table 2. HiResObjScan Entity Output signals.                             |    |

| Table 3. Zyng Resource Utilization.                                      |    |

| Table 4. Virtex-4 (Simulated) Resource Utilization.                      |    |

| Table 5. Zybo Complete System (Base+Project) model resource utilization. | 53 |

# List of Figures

| Figure 1. Previous system PTU camera tracking, dual stereo PTU camera system                  | 7  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2. Theoretical model, Pixel deviation compensation model                               | 8  |

| Figure 3. Algorithm for landing a small UAV                                                   | 10 |

| Figure 4. Stereo vision model presenting the two cameras                                      | 13 |

| Figure 5. Disparity image before & after interpolation [4].                                   | 15 |

| Figure 6. Conventional camera (left), AER from DVS [7]                                        |    |

| Figure 7. Six examples over 20 second tracking sequence of AER depth representation           | 17 |

| Figure 8. Representation of L-N learning. The object is tracked & detected                    | 19 |

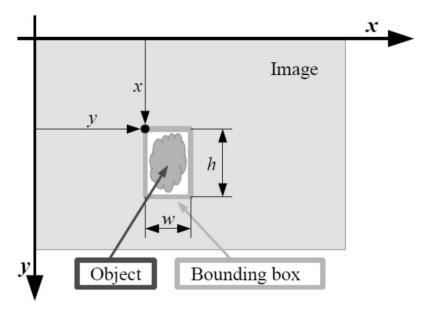

| Figure 9. Bounding box tracking with object parameters (x,y,h,w)                              | 20 |

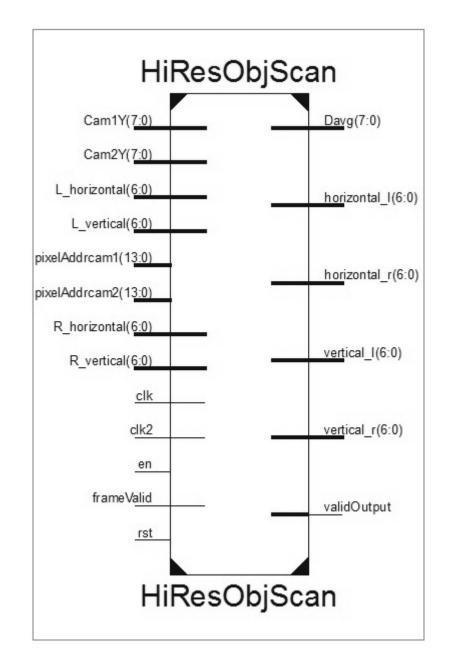

| Figure 10. Top level Design Entity: Hi-Resolution Object Scanner.                             | 25 |

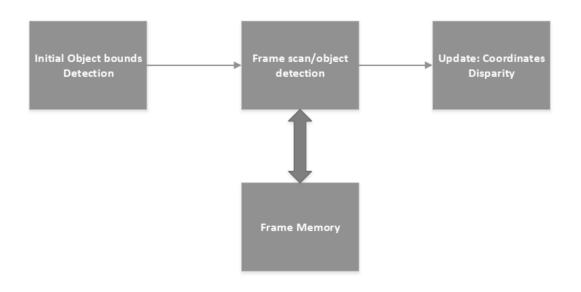

| Figure 11. Design High level Operational Diagram.                                             | 27 |

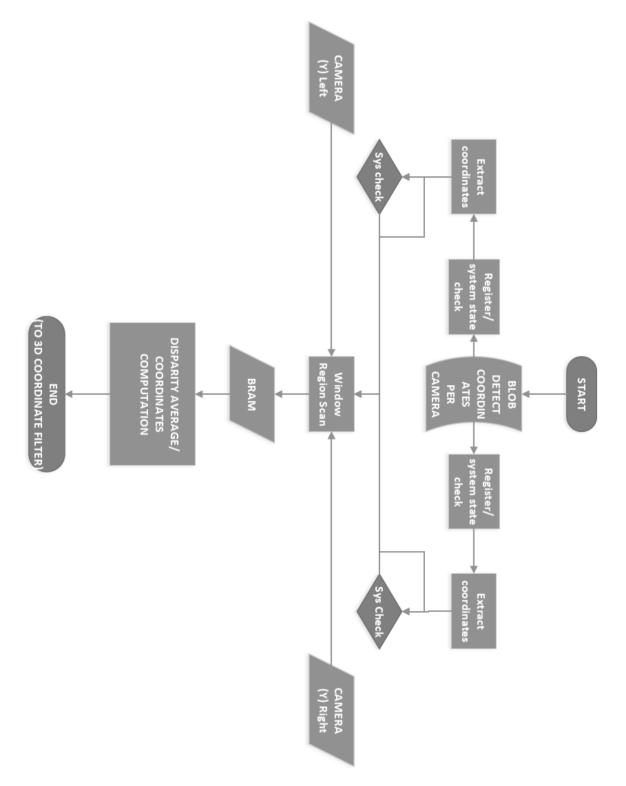

| Figure 12. System General Process Diagram                                                     | 28 |

| Figure 13. Row/Line Operations                                                                |    |

| Figure 14. Frame Disparity & Co-ordinate updates                                              | 30 |

| Figure 15. Frame/Memory Operations                                                            |    |

| Figure 16. Timing Model of system                                                             |    |

| Figure 17. Stereo System Design Overview, M.A.R.S. platform [10]                              | 34 |

| Figure 18. Region of Interest Window modelled by VHDL process                                 |    |

| Figure 19. System Integration of Project Module: Hi-Resolution Object Scanner                 | 39 |

| Figure 20. Top Level Test System.                                                             |    |

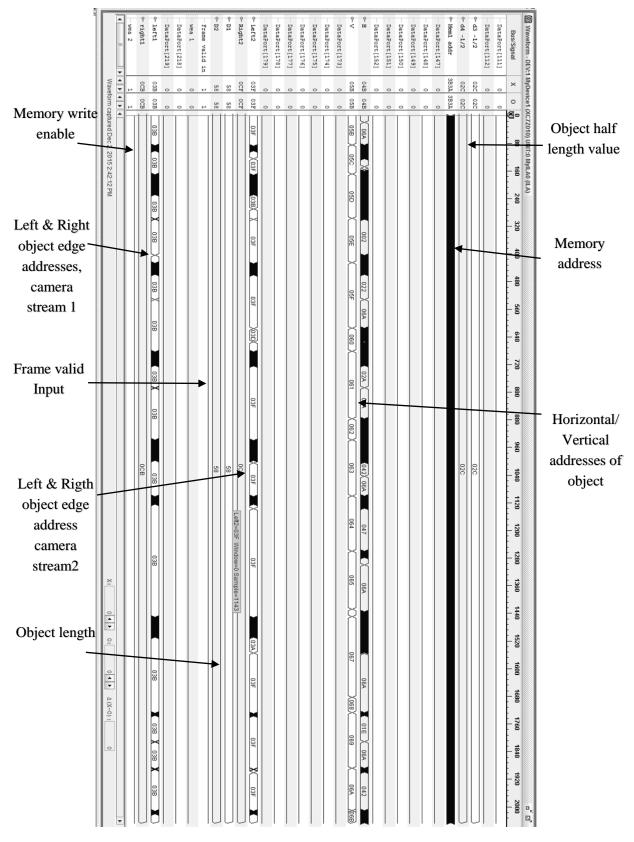

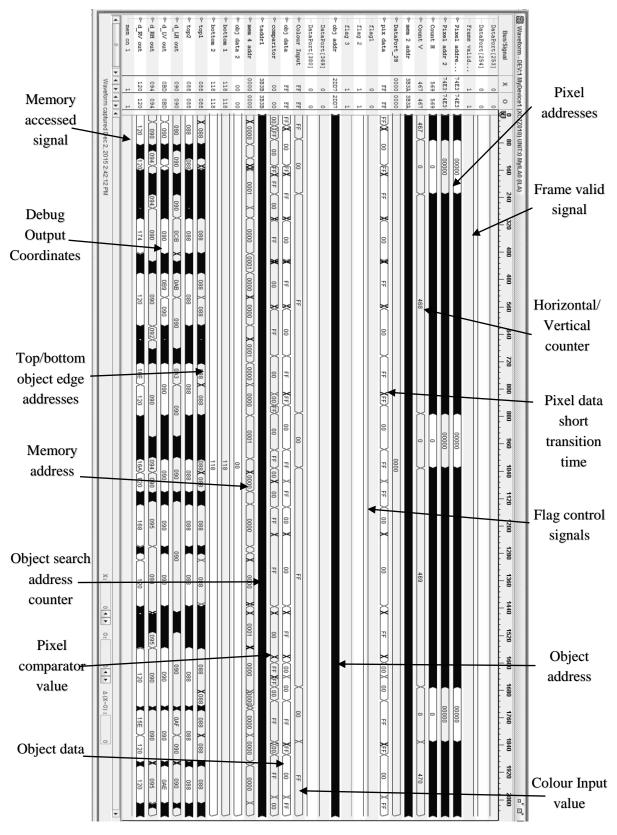

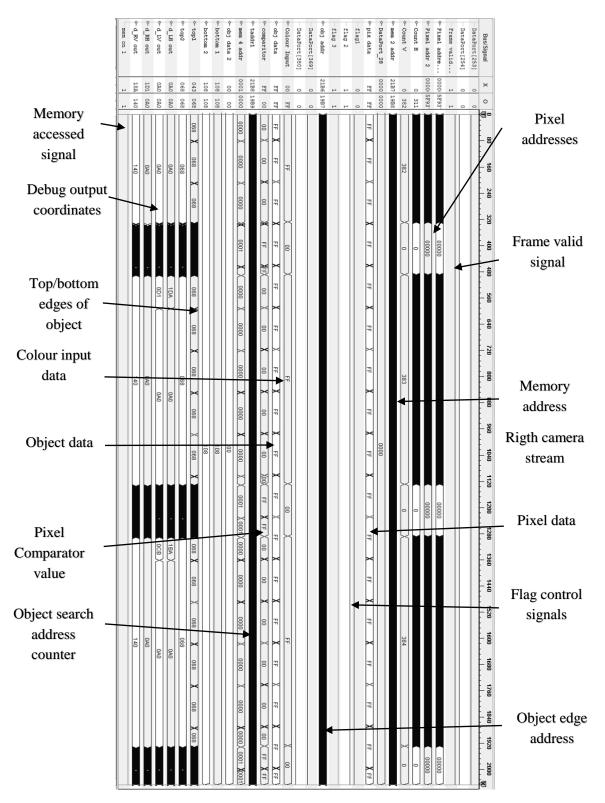

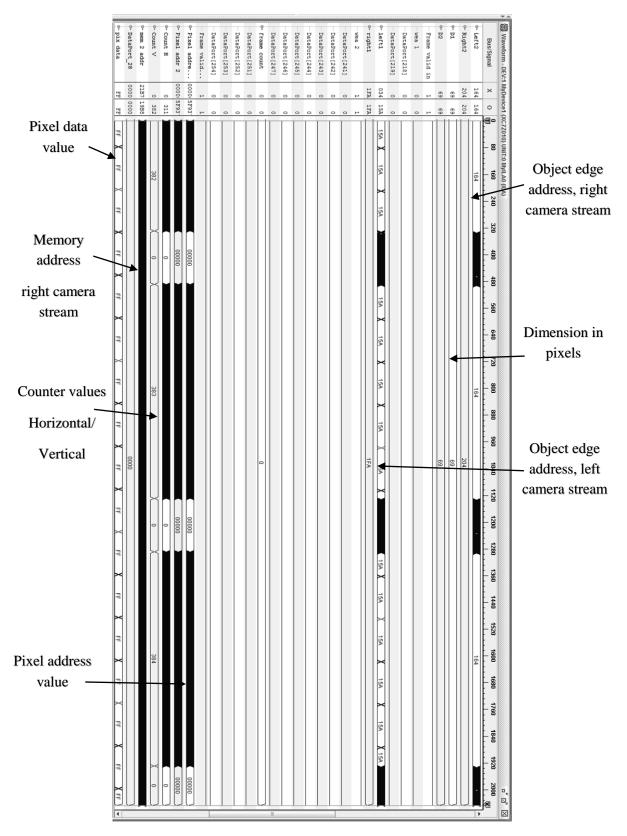

| Figure 21. Chipscope Data Capture/Operations.                                                 |    |

| Figure 22. Additional Cycles, enable signals shown (top section)                              |    |

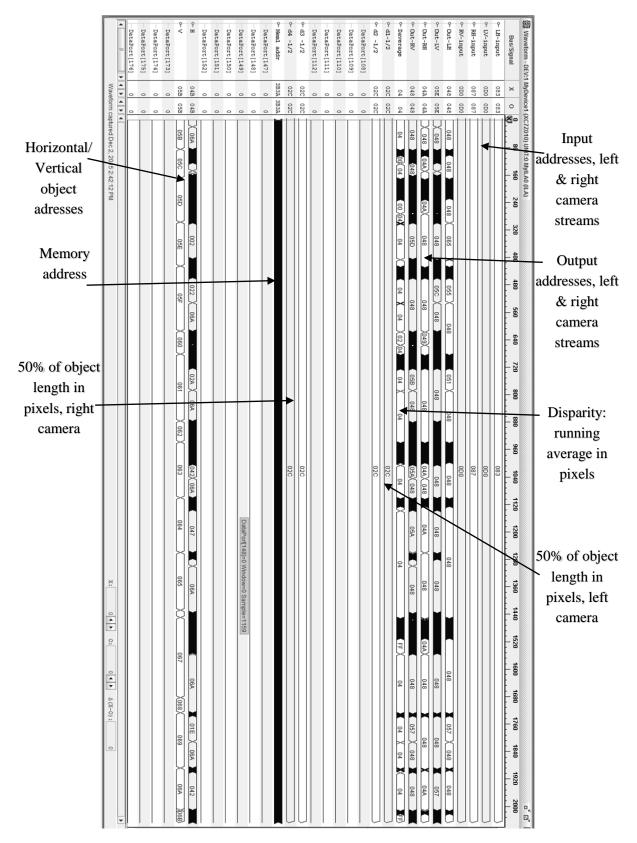

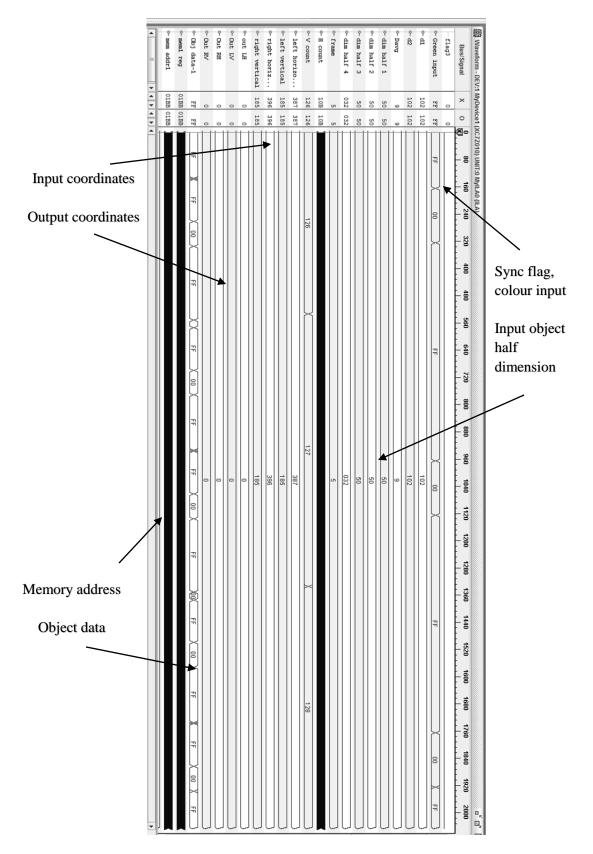

| Figure 23. Coordinate updates, with data input (green colour signal) from pattern generator   |    |

| Figure 24. Pixel address and the horizontal/vertical counter transitions                      | 46 |

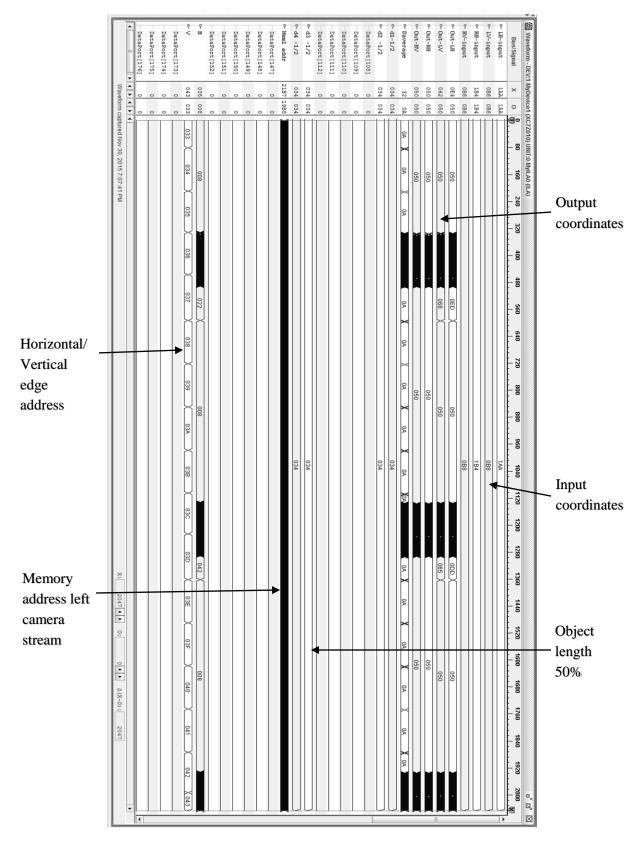

| Figure 25. From the top (timing data) to bottom, shows the left & right object edge addresses |    |

| Figure 26. In & output coordinate appear from the top where timing information is shown       |    |

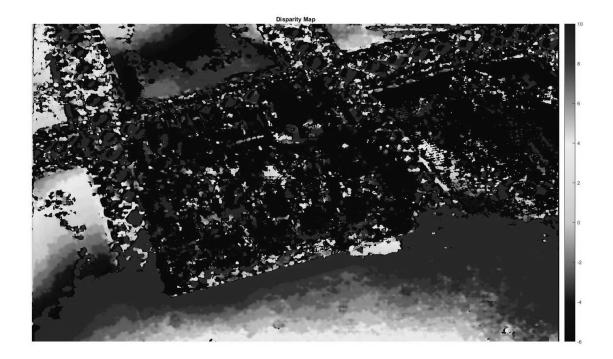

| Figure 27. Rectified Stereo Composite Image with anaglyph.                                    | 50 |

| Figure 28. Disparity Map of rectified image, with map scale                                   | 50 |

| Figure 29. Stereo vision Configuration                                                        |    |

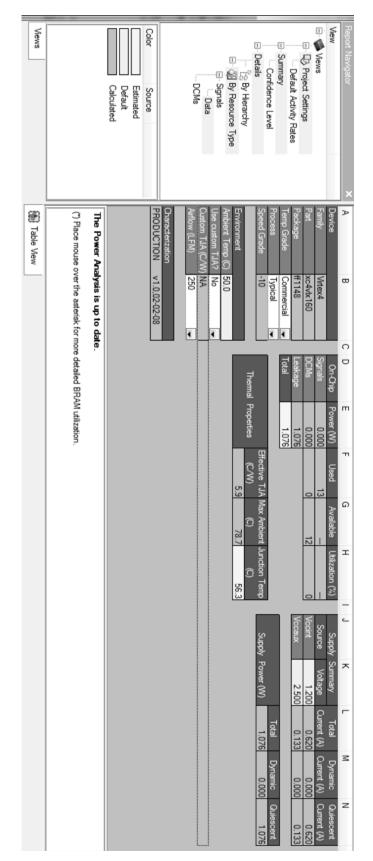

| Figure 30. Emulated Full FPGA Report Summary Zynq platform                                    |    |

| Figure 31. Virtex-4 Simulated Power Resources                                                 |    |

| Figure 32. Zynq Power Metering of Resources.                                                  |    |

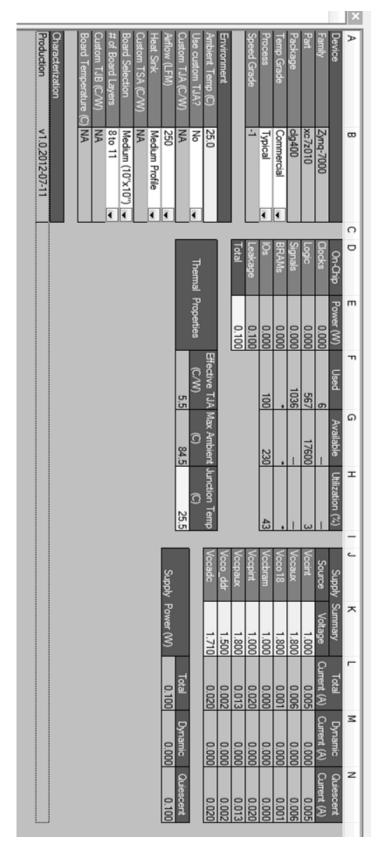

| Figure 33. Power simulation of unified system (base + project)                                |    |

| Figure 34. Input/output Coordinate, disparity tracking (Davg)                                 | 59 |

## List of Abbreviations

| ANN      | Artificial Neural Network                      |

|----------|------------------------------------------------|

| BRAM     | Block RAM                                      |

| CAMShift | Continuously Adaptive MeanShift                |

| CC       | Clock Cycle                                    |

| DSP      | Digital Signal Processing                      |

| FOV      | Field of View                                  |

| FPGA     | Field Programmable Gate Array                  |

| HDL      | Hardware Description Language                  |

| IOB      | Input Output Block                             |

| IP       | Intellectual Property                          |

| Kb       | Kilo bit                                       |

| KTL      | Karhunen-Loeve transform                       |

| LUT      | Look Up Table                                  |

| PC       | Personal Computer                              |

| RAM      | Random Access Memory                           |

| VGA      | Video Graphics Array                           |

| VHDL     | VHSIC (Very High Speed Integrated Circuit) HDL |

### 1 Introduction

#### 1.1 Motivation

The full implementation of computer controlled systems for use in the physical world and beyond can be accomplished by developing autonomous systems, allowing its embedded computing system to perform all required processing tasks with additional human guidance of the system. Such a system can be utilized in robotic, satellite and vehicle operations. Many of these functions are linked to image processing for operations in physical environments. This is because to fully operate in a three dimensional environment requires the ability to determine the distance to objects within the operational area. Many autonomous robotic and human operated systems would benefit from a stereo vision system as robotic systems (ex. planetary probes, autonomous vehicles, manufacturing) would have a direct method to know the range to objects within the environment. This is also true of human interfaced systems where the operator needs this information as well in order to manipulate objects in the environment. Accurate range and object dimensional data would allow robotic systems to more readily operate in environments with similar perception to humans and the means to manipulate objects in the environment to perform useful tasks. An example of such tasks are operations in environments hostile to humans (space exploration, nuclear reactor maintenance/fuel handling, mining etc.) where regular commands from a human operator may not be possible so the robotic system must perform a set of decisions and actions to compete its task, which are based on its perception of its operating environment (ex. Moving toward an object of interest, tracking it if moving and holding manipulating it). Given depth perception data, an object's dimensions can be determined by knowing the differences in range from the observer. This is more pronounced for tracking a moving object that possess a velocity and direction of motion from the point of view of the observer. The system of stereo vision described here is modelled from biological systems, mammal (predator) & human vision. This method of image processing would allow the robotic or computer controlled system to navigate environments, track and manipulate objects, by only using a pair of cameras to see and detect the world in a similar way to humans. (Digital cameras focus the light on to photo sensitive transistor array-CMOS; the image formed per unit of time is called a frame). Unlike similar systems that use one camera, LIDAR or RADAR (these detection systems are effective at large distance, from metres to kilometres, but are not effective in detecting object distances of units less one metre to centimeters), a visible or near infra-red 3D camera system is less affected by weather [1] and provides a direct means of depth perception using less complex hardware (LIDAR for 3D measurement uses a rotating scan head with an array of lasers to map out objects and detectors to measure the returned laser light, while RADAR wave-lengths are used for detecting vehicles and precipitation via

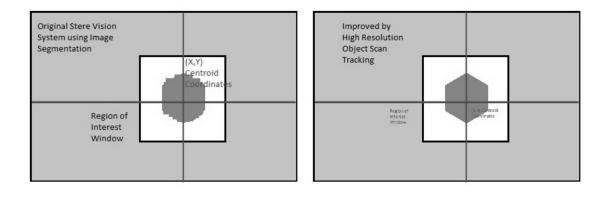

1

the Doppler effect) [2]. In comparison a pair of cameras is far less equipment and uses less power than a LIDAR system or an antenna/dish/emitter and klystron equipment used for RADAR [2]. The range to an object is determined from the stereo vision method by using a pair of cameras and by the focal length of each camera. The distance between the stereo pair (base line), the camera focal length and the relative distance of the object to each camera is used to triangulate the distance to the object of interest. The stereo vision computer vision process requires the rectification of the separate images into one (the images are aligned to match similar points along the horizontal axis) and compute the disparity between them (the displacement along the horizontal axis of similar points representing the same object). This information is used via triangulation to find the distance to the object. The position of the object that is determined in the stereo vision process by the relative position within the camera frame, these coordinates within the frame are at the centre of the object, called a <u>centroid</u>. This project was presented originally to augment and improve upon an existing system the Multi-mode, Adaptive, Reconfigurable System or M.A.R.S., which employ a stereo set of cameras to perceive the robotic probe model environment and object tracking capabilities. The original system utilized frame image averaging to reduce memory costs and provide object tracking. By tracking an object from the averaged frames, the tracking and dimensioning of object data is less accurate and so is the ranging data because of this. Also the applications of the stereo vision system extend to human interface systems (augmented reality) where computing the distance from the operator's field of view to the projected virtual image is critical for successful human machine interfacing [1-31].

#### 1.2 Objective

The objective of the project report is to optimize the M.A.R.S., 3D stereo vision system through higher image resolution; therefore, improving object tracking and ranging of the system with further implications for robotic vehicle operations. This will allow robotic systems to more fully operate in a real environment as it must be able to efficiently detect, analyse and estimate the distances to objects within the operating area. This method of image processing would allow the robotic or computer controlled system to navigate environments, track and manipulate objects, by only using a pair of cameras to see and detect the world similarly to humans.

The key objective as defined by the project specification are outlined as follows:

- 1. Improving distance measurement from computed disparity.

- 2. Optimize and minimize memory/logic recourses on the FPGA (Field Programmable Gate Array).

Branching from the key objective are the sub objective tasks:

- 1. To improve the object tracking behaviour of the system by providing higher image detail within the window region of interest.

- 2. Compute the object centroid and dimensions.

- 3. Analysis the accuracy of object tracking by comparison of initial to updated object coordinates.

- 4. Optimize the object tracking algorithm to provide updates on the objects position and distance.

- 5. Optimize the use of FPGA resources to minimize chip area, time delay of the system.

- 6. Integrate the new high resolution object tracking stereo vision system into the existing M.A.R.S. and compare its performance.

- 7. Insure minimal object image artifacts caused by moving complex objects (ex. people) and focus tracking of the object centroid.

#### 1.3 Original Contribution

The original contributions in the project is the concept of enhancing an existing stereo vision system, that is outlined as follows. The review of related and relevant research into computer vision, to focus on the best methods to accurately and efficiently measure depth from a digital camera system. From the research to synthase the best architecture for a system to address operating requirements, defining the engineering specifications. The testing and implementation of the system architecture to confirm its correct operation as compared to the project requirements. And finally to analyze the results from the system to measure its performance in comparison to the original system. This project contributes the higher resolution, object tracking VHDL module to accomplish the goal. From a stereo video source (which must provide current object coordinates and dimension relative to each camera data stream) it can directly track the object of interest and produce its coordinates and distance relative to the stereo cameras. The project objective is accomplished by the implementation of a region of interest window, where image data is read at the frame resolution (in this case 640x480 pixels). Also the disparity is computed based on the object edge found within the region of interest window. Achieving the objectives of the project requires implementing a means to directly inject higher resolution camera image data into the system. This is enabled by integrating and utilizing higher camera resolution data to detect the object, update system data, track the object motion and extract the object distance and dimensional data in an efficient way. By using a higher resolution camera scan to augmented a lower resolution system, the data loss and resultant reduction in accuracy due to compression techniques like averaging can be avoided to provide improved object tracking performance [3-20].

#### 1.4 Organization

The project report is organized in to the following six chapters after the first, the introduction. Chapter 2, the literature review provides a synopsis and analysis of research related to the project objective of stereo vision methods and its applications to object detection, tracking and navigation. The example applications include an automotive self driving vehicle, navigating autonomous aerial vehicles and object tracking methods using neural networks as a feedback control system. The concept of stereo vision explained in full via the mathematical model.

Chapter 3, design synthesis explains why the proposed solution was chosen. This fully explorers what was outlined in the contribution section of the introduction and conceptualized in the motivation section. The possible project solutions and its limitations are discussed and where the project solution is fully described as the only logical course of action given the objectives and specifications of the project. Chapter 4, implementation & test provides details into the logic structures used to build the project solution and how testing methods were established and performed. The VHDL code structure is explained based on its required functions to achieve the project objectives. The methods of testing and tools used are also explained in full (from the design interface software, FPGA hardware platform to the signal waveform display).

Chapter 5, comparative analysis presents and analyzes the results of FPGA resource utilization and object tracking performance. This chapter will direct FPGA logic utilization data from the ISE and explain how the report objectives were satisfied.

The sixth and final chapter is the summary of the report, that provides a summary of the project report and concluding remarks on its findings from the previous chapters. Furthermore, future work proposals will be included.

The references, definitions and index of key word follow afterward.

### 2 Literature Observations

The following synopses of near current research into 3D stereo image processing and its applications is presented to provide background knowledge, observations and analysis in comparison to the report objectives. The process of 3D stereo vision involves the main stages of rectifying the two camera images (image matching is improved by aligning the cameras in the horizontal plane), then the disparity map is created from the images, matching the same object from both left and right camera images. From the disparity map the relative displacement of the object on each of the image are used compute the distance to the object based on the trigonometry of the cameras and the object. These aspects are further reviewed in the multiple synopsis of the research papers and its analysis [3-31].

#### 2.1 UAV Tracking

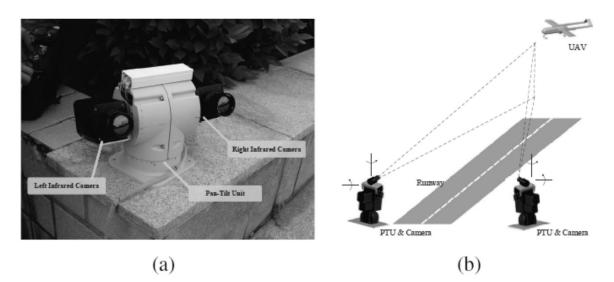

The first paper [3] uses a pair of stereo cameras to track an unmanned aerial vehicle (UAV), triangulate its location to compute landing information for the UAV. This major area in robotics research into UAV has many military and civilian applications. An open problem remains flight operations in GNSS (global navigation satellite system) denied environments. The task of landing a UAV requires high precision motion control and reliability of its sensor system. "So the main idea in this research is enlarge the navigation range during the landing progress and detect the fixed-wing UAC as early as possible" [3]. A novel ground based system was developed (figure 1). On either side of the runway, independent stereo vision units are installed to separately scan the airspace above the runway. When an aircraft is detected, the units can cooperate to estimate the relative position between the UAV and the runway via triangulation. Unlike on-board sensor solutions, the ground-to-air visual system has no payload restriction and allows high computation power. The paper [3] contributes the ground based platform with a large field of view (FOV), eliminating the need for GNSS, utilizing the image processing algorithm Ad-aBoost for target detection and tracking under varying light condition and the system used a middle sized fixed wing aircraft [3].

Figure 1. (a) Previous system single PTU camera tracking, (b) developed dual stereo PTU camera system [3].

UAV landings have employed GNSS and IMU (inertial measurement unit) to complete this task. Yet in urban environments or low altitude operations the GNSS receiver antenna can lose line of sight of the GPS satellites, therefore the UAV loses its position data. Military grade UAV systems also used millimeter wave track radar, laser pointers and cooled infrared cameras to provide further position data in non-GNSS environments. Previous methods for rotary wing UAVs used monocular vision or dual camera feedback. Fixed wing aircraft landing proves more challenging since tiny errors in guidance could yield system damage. The flight system in the paper [3] is composed of its aircraft platform and ground based visual system and communications. The fixed wing aircraft is a Pioneer by VIGA Tech Company. It is gasoline powered radio-controlled, approximately 2.3 metres in length with a 5kg payload capacity. The model aircraft uses the iFLY-F1A module for autopilot, "a ground control station, a redundant power management module and an engine RPM monitoring module" [3]. The G2 module possess a GNSS and IMU instruments. The ground based visual system components consist of two DFK 23G445 visible light cameras, with an image resolution of 1280x960 pixels at 30fps. It has the GigE interface. A PTU (pan tilt unit) is used to extend the field of view. "Its pan/tilt speeds up to 50 degree/sec with the position resolution of 0.00625 degree" [3]. The PTU-D300E is programmable via Ethernet and RS-232 interfaces. The ground station uses the EOS-1200 embedded vision system for transmitting control command to the UAV and records GNSS data. The communication system utilizes a radio modem, operating at 900 MHz with a range of 22km and data rates from 10 to 23000 bps. Each vision unit independently operates and transfers image processing data & PTU status to the navigation computer. Then the estimated relative position of the UAV is calculated [3].

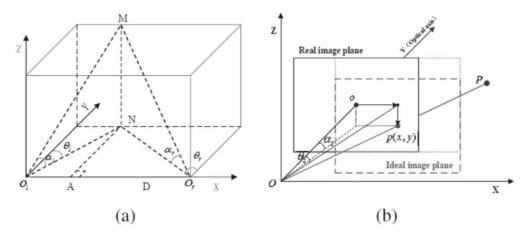

Figure 2. (a) Theoretical model, (b) Pixel deviation compensation model [1].

The model of the optical system (figure 2) is based on both cameras at the same baseline, the X axis, with its optical direction shown be the Y axis. The coordinate system origin starts at the left camera. A tracked aircraft converges the cameras at point M. The tilt and pan of the cameras are shown by  $\alpha$  and  $\theta$  respectively. Pixel deviation is compensated for since point M may not coincide with the centre of the image plane. Measurement error and its analysis is taken into account, since intersection of the camera at point M is not perfect. "The method estimates intersecting point by means of optical axis combined vertical line of two different planes in space" [3]. The optimal point of point M is the vertical line segment centre, the least square method is used to better meet this condition [3]. Error analysis is based on examining the partial derivatives of the equations with respect to the pan & tilt angle and its influence from the gradient. For the landing trajectory, the UAV must keep an angle of attack between 5 to 7 degrees with the runway. Error within 100 m to the landing area produces an error of altitude of 0.02 m, while errors at greater distances are more notable [3]. The experiments conducted tested the MATLAB ground control software for aircraft detection via training samples, also under varying light conditions, approximately two hours about sunset [3]. The aircraft would takeoff (navigation via DGPS), proceed to set waypoints around the flight area, then in position for approach the ground system takes control to guide the aircraft to the runway from distances over 600 m [3]. This paper [3] presents a dual stereo camera system with PTU at the landing zone (runway) to control and guide the aircraft to the ground. This increases the computational tasks compared to a single stereo camera system with fixed FOV, as this report focuses on, in its implementation. With the computer control system on the ground and not on the aircraft, it removes hardware mass/power limitations. This report will focus on FPGA implementation to allow for an aircraft based control system. Having a ground based landing system allows for safer flight operations in controlled airspace [3].

#### 2.2 Landing Quad Rotor UAV's

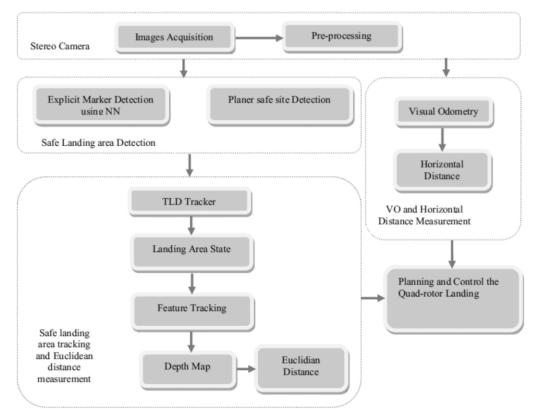

The second paper [4] proposes an autonomous means of controlled landings of UAV and quad rotors utilizing stereo camera and the FPGA to operate the real time neural network architecture. This system can overcome human factors of piloting UAVs given "limited situation awareness and lack of realism" [4] for the most critical phase of flight, landing [4]. "Most of the [v]ision based landing systems detect known visual markers" [4] which is used to compute the vehicles relative position, such as a heli-pad 'H' or high contrast patterns (ex. Checkerboard). The alternative approach is to land with any marker or target, where the flight system determines the safe landing area, attitude and distance of the UAV to the landing zone [4].

The idea is to track the landing area identified by the safe landing area module, measure the displacement & relative position between the landing target and the UAV. This is implemented using C/C++ and MATLAB based on OpenCV, while landing area tracking is performed by an FPGA. Extensive validation of the practical scenarios was performed in RTL simulations, power and area constraints of the system were also evaluated. Algorithmic development and evaluation was first done using MATLAB then in Verilog HDL [4]. The Xilinx XC2V1000 is used to synthesize the system architecture on FPGA. This low end model was selected to match the limited area requirements with a low power platform for the proposed design approach. The algorithm for the proposed method (figure 3) operates as follows: the stereo cameras obtain the images; the left camera image is taken as a reference. Next the visual odometry module estimates the relative position/rotation (Euclidean distance) of the UAV and tracks the landing target. This is enabled by the safe land detection module and the safe landing area tracking/Euclidean distance measurement module. The visual odometry module processes image gain correction, calibration and rectification in the calibration and pre-processing step. Next key points are taken from the left camera image using the FAST algorithm for real time 30fps operation. The object feature/key points detected in the left image are mapped to the right image. The features (part of or property of interest, for example: tip or colour) are searched within a disparity limit (ex. 16 x16 pixel square). "Normalized correlation is computed between feature[s] in [the] left image and all potential features in that box using zero normalized correlation (ZNCC) [4].

Figure 3. Algorithm for landing a small UAV [4].

The Kanade Lucas Tomasi (KLT) tracker is used to track key-point locations between frames. KLT applies the affine distortion (non-rectangular camera pixel matrix transformation representing the distance between images) model to better detect large changes. The disparity is calculated to compute the horizontal displacement between stereo frames, corresponding to a real world point. From the disparity map 3D points are calculated for the triangulation step. Outliers are rejected using RANSAC, rotation and translation is estimated using the 3-point algorithm. The horizontal displacement between landing target and UAV is calculated by the visual odometry pose estimation, via the height data [4]. The objective for the safe landing area detection module is as follows: the landing area is a flat level plane without obstacles, its large enough for the UAV and has sufficient features to be tracked. The safe landing area is tracked frame to frame by the TLD (tracking-modeling, detection) tracker. The TLD output is a bounding box representing a safe landing area called "Landing Area State" [4]. The bounding box is initially set to maximum, if it exceeds its threshold it then creates another box within the first which is less than the threshold, this relates to the UAV altitude. When the landing zone distance decreases the bounding box will increase; therefore, the centre is targeted (second smaller bounding box) and tracked. The IMU provides direct measurement of the UAV angle to calculate the Euclidean distance [4].

The algorithmic level of the automatic identifier & classifier is composed of the following: image acquisition & pre-processing (the UAV front facing camera is used for obstacle avoidance and object recognition), detection and segmentation (extraction of features from the background via neural network), classification (matching of target feature using an ANN, so centroid calculation is not required). The target templates are based on complete or partial target information, saved in a knowledge base. Template based matching are sensitive to affine moments; extracted features are matched based on reliable features; the KNN based classifier produces minimal distances for similar objects, rejecting similarities amongst different classes [4]. "The neural network performs a series of matching by minimizing the distance between the learnt model features and measurement points" [4]. The KNN function classifier provides power and storage advantages over traditional linear search methods. KNN performance remains linear over the range of recognition. FPGA based KNN classifier offers parallelism and flexibility in numeric precision. Neural network weights can be easily updated via writes to block RAM elements. The ANNs have its input/output data interface, where each computes the Euclidean norm for the distance. The hardware uses square root approximation (exponentially reduces computation compared to cordic, newton Raphson method square root cores from Xilinx). To optimize the implementation, fixed point C was used to implement quantization noise and the optimum word length was defined to minimize the effect on system performance, while reducing hardware area. The control block is responsible for data flow control in real time, acquiring data and updating neural weights. Implemented on the FPGA, a group of 8 neurons each with 128 Byte feature vector (weights). The critical path length approaches 85ns in the FPGA, operating at 11MHz, yet still meets performance requirements given the parallel architecture with wider data paths. The control block manages the data during the learning process, the output is used to define a match with the given data set. The results yielded an efficiency of 71% of feature extraction. From 5000 patterns 8% were matched with F.A.R. [4]. The approach for a complete system to detect and land a UAV in unknown locations is the logical future step for this report's future development. Having the image processing and neural network for feature matching (via an onboard expert system) on a low power FPGA presents the versatility of design of hardware and software. Though the paper's [4] results were preliminary, improvements in the learning data of the expert system can produce improved results [4]. The use of the neural network provides flexibility in processing features compared to subdividing an image into blocks to isolate a specified feature. It would also make high resolution image rescan redundant since it can be done at the beginning. The system in the paper [4] was developed for recognizing relatively static targets at a distance. For moving targets at close range the neural network would require a training data specific to extracting features from fast moving targets.

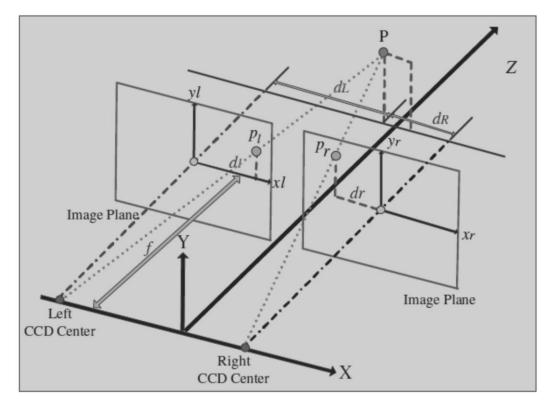

#### 2.3 Stereo computer vision

The third paper [5] studies and implements a 3D stereo computer vision system. This form mimics human vision by using two cameras. Its applications cover autonomous vehicle, virtual reality, video surveillance systems and 3D television for example. The advantage of stereo vision is acquiring depth perception in contrast to plane vision from a signal camera. Previous video tracking methods have been developed including the following: optical flow, kernel-based tracking, contour tracking, <u>blob</u> tracking, mean shift tracking, Kalman filtering and 3D tracking, etc. [5].

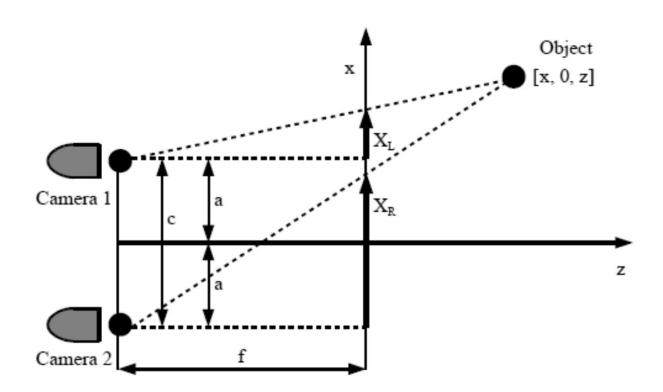

The aim is the study of 3D feature (part of or property of interest, for example: tip or colour) tracking and localization using stereo vision. When the feature to track is defined, the system automatically tracks and localize the given feature in motion, estimating its depth information. The system is designed using two identical cameras, having the same settings. The cameras are installed so its optical axes are parallel to each other and the floor, they're both the same height off the floor. The main system processing includes the following: feature definition, tracking (best matched feature point via minimizing the mean squared error between two blocks in both frames), localization (estimated matching motion vector) and depth computation (computed from the relationship of the camera focal length, position in space, object distance view angle to the camera and light point on the camera lens) (figure 4). The user must indicate a 3D feature point of interest to track using the first frame in the sequences of future frames. Next the system will automatically track the 3D feature in the left video sequence and localize the corresponding 3D feature in motion using the right video sequence. Given the two feature locations, tracking and localization the depth information is computed via triangulation from the object to the cameras [5]. This is based on the pin-hold camera model (extended for stereo vision). The focal length (distance from CCD centre to the image plane), projected pixels on the left & right image plane and its horizontal distances to the respective image plane centre, the horizontal distance from the target point respective to the camera centres, the distance between the two cameras and depth, a measurement from the object feature point to the centre of the two cameras [5].

Figure 4. Stereo vision model presenting the two cameras, with alignment to the object down range [5].

The system was evaluated for its performance in key parameters are as follows: depth (150 to 250 cm), tracking in plane or stereo vision (with respect to depth computation). Feature tracking was evaluated independently for each camera. Therefore, two motion vectors are evaluated independently. The use of kernel functions effects (computed via M.S.E) and integer vs sub-pixel accuracy. "For the integer-pixel accuracy, the original image resolution (i.e., 640x480 pixels in this study)" [5]. Sub-pixel accuracy magnifies the image by k (e.g., k=2) in two dimensions before tracking and localization; therefore, depth data is evaluated by 1/k of the pixel. The error rate of depth perception is computed given the difference in actual and measured depth. The experiments show that depth measurements at the mid-range (200 cm) were most accurate with the sub-pixel function for stereo vision as compared to plane vision with integer pixel accuracy [5]. These findings and methods directly apply to the project report's implementation as it uses a similar physical set up to emulate human vision. The application of sub-pixel accuracy may require further study for implementation. Indicating an image feature to track in real time would also be an interesting addition; in comparison the project will track any one object via blob detection [5].

#### 2.4 CAMSHIFT Improved

In the fourth paper [6] an improved version of the CAMSHIFT algorithm is utilized for stereo vision object tracking is implemented. This involves tracking over successive frame, creating large amounts of video data to be transmitted and processed in real time. Increases in computation power, algorithm design also for implementation single processor systems. While advances in FPGA density, speed and programmability make it a viable alternative [6]. Stereo analysis involves measuring the range to the target object. "The fundamental problem is stereo analysis is finding corresponding elements between the images" [6]. Image illumination, perspective and differences directly effect image correlation. "In visual control systems, real time performance of object recognition with pose has been regarded as one of the most important issues for several decades" [6]. Computational burden is the prime factor for designing vision systems [4]. Related works in 3D vision have focused on improving segmentation of object from the image background, the use of invariant descriptors of local features and colour based trackers. For non-rigid object tracking it is advisable to represent it with probability distributions. The paper [6] presents a modified CAMSHIFT algorithm. In the original "the current frame is searched for a region, a fixed-shape variable-size window, whose colo[u]r content best matches a reference colo[u]r model" [6]. The search is deterministic and may encounter problems when parts of the background present similar colour or the object is blocked from view [6]. The paper [6] operates on both stereo images and its disparity image. The tracking of stable colour features can overcome distortion of shape and partial occlusion [6].

The proposed approach of the modified CAMSHIFT algorithm is as follows: 1<sup>st</sup> the region of interest of the probability distribution is the entire image, 2<sup>nd</sup> an initial location of the Mean Shift search window is selected, this is the target distribution for tracking, 3<sup>rd</sup> find a colour probability distribution of the region of the Mean Shift search window centre, calculate a disparity probability distribution of the Mean Shift search window, obtain the final probability image combining colour and disparity probability distributions, 4<sup>th</sup> next iterate a Mean Shift algorithm to find the centroid of the probability image (storing the 0<sup>th</sup> distribution area & centroid location). And (5) for the next frame, center the search window at the mean location found previously, setting the window size to a function of the 0<sup>th</sup> distribution area and repeat from the 3<sup>rd</sup> step [6]. To produce the probability distribution image, the method of histogram back-projection can be used. The first step of CAMSHIFT is computed to generate the initial histogram from the ROI of the filtered image. The hue channel in HSV colour space is used to isolate pure colour. Saturations & intensity values are selected within threshold values. The output pixel characterizes the probability distribution image where objects are presented in shades of grey. In the modified CAMSHIFT algorithm, the final probability distribution depends on the colour and disparity probability

14

distribution (its proportional the difference of the disparities of the image and mean disparity of the tracked object and is defined per pixel) [6]. The correspondence problem is present when deriving the disparity image. Given the missing data it must be created using "an epipolar line for which we have disparity information" [6] by the formula disp(i) = (1 - y)disp(L) + y(disp(R)). The modified algorithm then follows the next two steps of the original CAMSHIFT algorithm, centroid probability image and marking of the tracked object [6].

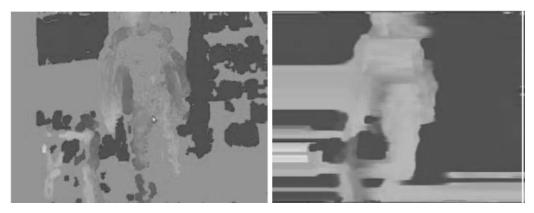

Figure 5. Disparity image before & after interpolation [4].

The algorithm is performed as a node in a Robot Operating System framework. The ROS is based on graph architecture where processing nodes receive, post and multiplex sensor, control and other messages. The nodes developed get image and disparity messages, processes them and post messages with object position data. The initial object position is defined in two ways, a rectangular area with the incoming video stream or the node receives a message with the initial position (from node or human input). The node developed detect people's faces in images and posts messages on their position. The cameras use its FPGA to calculate the disparity image [6]. This reduces the computational load, allowing higher resolution and refresh rates [6]. The experiments in the paper [6] focused on people moving around the camera while the camera is not fixed. The modified algorithm used a dual processor PC. In contrast the lab set up for this report will have the camera at fixed location with objects in its field of view; furthermore, all processing of the image data will be computed by a FPGA board. It would be an advantage to use cameras that can process the disparity map. In the paper [6] 2000 frames were processed, 30Hz a resolution of 640x480 pixels. The report will make note of frame processing with its findings presented in the analysis section. The report will focus on blob region detection with additional high resolution refinement. The CAMSHIFT algorithms, computational time in comparison to hardware platform (PC vs FPGA system) used is an interesting avenue of research. The report's 3D stereo system will work in controlled lit conditions, object tracking given partial occlusions is an interesting point of

comparison with this paper [6]. The improved CAMSHIFT algorithm works with colour data as part of its pixel/object detection process, while this report will work with gray scale pixels only [6].

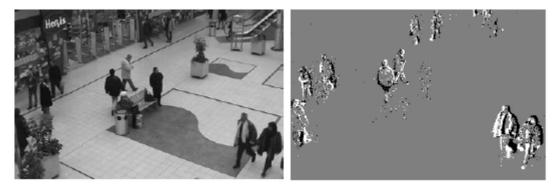

### 2.5 AER Object Tracking

The fifth paper [7] explores the object tracking method of using address-event representation (AER) space to exploit on-chip pre-processing by a dynamic vision sensor (DVS) [7]. The improved efficiency is summarized in three aspects: the reduction of data rate of scene dynamics by on-chip pre-processing of visual data (focal plane processing), the second aspect uses high temporal resolution for edge detection, the third aspect is the high dynamic range. "Edge detection using DVS is robust to varying intra-scene illumination due to the pixel sensitivity to local temporal contrast, rather than temporal intensity change" [7]. The object tracking algorithm is applied on a 3D AER that was generated by a stereo vision system. Address-even representation by DVS presents pixels of light intensity changes (on-event increase, offevent decrease) that show activity events (figure 6), while non-moving objects produce no data [7]. Previous work on monocular DVS using AER to detect moving object by an event-based approach greatly reduced the correspondence problem as compared to frame based tracking. "Because there is no temporal quantization of the information by the vision sensor, it generates events for every pixel along the objects path of motion". The object path is held in a pixel address vector, organized by time. Moving object detection is performed by the sensor, reacting only to changes in the scene reflectance. Also no event buffer is needed and a DSP runs the tracking algorithm. Other methods may support fast object tracking but need more signal processing circuitry [7].

Figure 6. Conventional camera (left), AER from DVS [7].

The 3D dynamic vision system hardware is an embedded stereo system made up of the following functional groups: two sensor elements and a buffer unit (multiplexer, FIFO memory, DSP). The DVS is an array of 128x128 pixels (0.35µm CMOS). The sensors generate address events (AE) that is sent to the

multiplexer, then through the memory buffer to the DSP. The AEs are time stamped at 1ms and used for processing. The address event stereo algorithm produces real time depth estimation that are performed in three steps: camera calibration & rectification, stereo correspondence calculation and reconstruction; an adapted area based method is used. The major differences to conventional stereo vision systems created by use of AE are as follows: AEs are accumulated to find significant visual correlations between both cameras, correlation calculations are only performed on relevant images areas. The stereo algorithm has two functional blocks, AE stream partitioning and Integration [7] are necessary to get AEs in an appropriate form. The stereo correspondence calculation algorithm is modified to utilize AE-based processing. With the AE continuous data stream, the "AE stream partitioning" block partitions the timeslots of duration DT that determine the temporal resolution of the 3D sensor system. A typical value of DT on the system is from 5 to 50ms for the depth map [7]. The tracking algorithm works by continuously finding bounding boxes for each object and using the movement sensitivity characteristic of the DVS [7].

Figure 7. Six examples over 20 second tracking sequence of AER depth representation of a person moving [7].

"Any moving object will generate a number of AEs and appears as a cloud of AEs in space-time" [7]. There is no need to extract objects from the background image, making the bounding box easy to generate. The algorithm functions as follows: first at a starting point a bounding box is made around an object by stepwise expanding of the boxes boundaries in pixel coordinates till no AEs lay on the boundary itself. For the 2<sup>nd</sup> step the first bounding box of the detected object in the sensor is made persistent. A comparison step is performed to match new bounding boxes to previously ones. After a match is found the bounding box is updated in its size and position using new information from the new bounding box using a mean shift algorithm. In the 3<sup>rd</sup> step object trajectory can be reconstructed by updating the position of the persistent box, reporting its current location within the field of view [7]. This dynamic vision system was tested by tracking people (detected from their head) moving through a room (figure 7). The vision system was mounted on the ceiling, 2.5m high tilted at 45 degrees. This would be a slightly different set up in terms of orientation as this report's camera system is based on a platform above the floor with the cameras parallel to it. Also the camera system detects any objects.

This is accomplished by image averaging, rectification and blob detection over the sequence of frames, whereas the DVS methods relies on AER to detect those pixels that have changed light level due to movement. It is a fascinating alternate method of 3D stereo real time object detection that utilizes less computational resources. A full comparison would require placing the DVS on an FGPA SoC, to examine further efficiencies [7].

#### 2.6 TLD Stereo vision

The sixth paper [8] reviewed is about the application of a tracking-learning-detection (TLD) algorithm in stereo vision applied to the Nao robot [8]. TLD detects & tracks an object by a continuous series of video frames. The object position is defined as coordinates of its bounding box. To gain data on an objects distance, a second camera is used to create stereo vision. The 3D information (dimension & position) on the object is sent to a forward arm controller to enable the robot's interaction with a tracked object [8]. The TLD tracking method is meant to work in unconstrained environments, the system is composed of three independent components: the tracker (short term, based on Lucas-Kanade method and used to train the detector), the detector "enables incremental update of its decision boundary and real-time sequential evaluation during run-time" [8] and the learning algorithm (P-N learning), it uses the tracker to generate positive (P) and negative (N) examples used to improve the detector model [8]. Before tracking operations begin the bounding box of the object is manually selected by the supervisor. Then the object is tracked, during tracking the object model is created for the detector. The model is based on the first frame and tracker data. When the detector training successfully completes, re-detection of the object is enabled. Any error by the detector or tracker is mutually canceled out to maintain system stability [8]. The tracker used by TLD is Median-shift. It is based on the Lucas-Kanade tracker "which is robust to partial occlusions and also estimates translation and scale" [8]. It tracks points between consecutive frames, estimating a rectangle displacement and scale change using the median of tracked points that are selected at 50% of the most reliable tracked points within the rectangle boundary. Within each frame a new set of feature points are tracked. This is done using the "forward-backward error [that] is defined as a difference between two feature point trajectories, where the first one is defined by forward motion of tracked point and the second one by its backward motion" [8]. This recursive tracking is possible so long as the object is visible. Failure would result from occlusion or other dynamic changes in object appearance. In this case the TLD relies on the detector [8]. The detector in the TLD system uses methods based on the scanning window and randomized fern forest classifier [8]. In the scanning window approach the input image is scanned across all possible positions and scales. Each sub-window has a binary classifier which decides about the presence of the object [8]. The model of the object is defined as a set of image patches representing possible appearances of the object, each is described by a number of

18

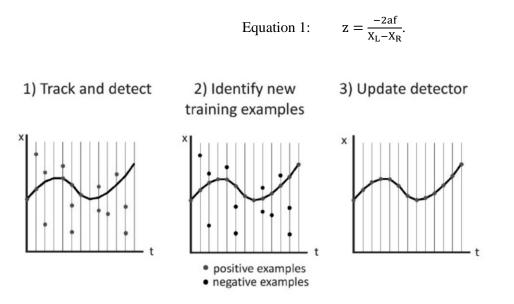

local 2 bit binary patterns. The position, scale and aspect ratio are randomly generated, these features are randomly partitioned into groups of the same size. Each group is a different view of the patch appearance [8]. The main idea of the P-N learning algorithm is to utilize inevitable errors of both the tracker and detector functions. When P-N learning is initialized in the first frame by the initial detector, the Lucas-Kanade tracker initial position is set to the selected path. For each consecutive frame the detector and tracker find location(s) of the object. The distance (close or far) of the detected patch to the tracker trajectory (figure 8) produces the positive & negative learning examples respectively [8]. The stereo vision system advantage provides more depth information unlike single camera systems. With depth data the spatial coordinates of a tracked object can be computed, for the arm controller to move the robot hand towards the object in this paper [8]. Depth is calculated from known values of the focal length of the cameras, the respective horizontal position of the object for each camera and the distance from each other by triangulation via the following equation (1) [8].

*Figure 8. Representation of L-N learning. The object is tracked & detected. Patches close to the trajectory update the detector* [8].

Integration of TLD into the stereo vision tracking system requires two TLD system per camera to track the same object. The user selects the object for tracking from one camera. The initial object model for the first TLD is made and copied to the second TLD, both TLD system synchronize to avoid divergence in object detection. The output of each TLD provides the object bounding box and its object centroid coordinates (figure 9). This method overcomes the correspondence problem of matching point from each image [8]. For the robotic controller the object data is transformed into Cartesian coordinates. The controller performs the moving of its robot hand by using object data from the tracking system that is processed by a feed-forward neural network of three inputs and outputs. To train the neural network a sufficient set of training data is required; it is generated by exploiting the inverse model of the system. The inputs of the artificial neural network are polar coordinates of the object position with respect to the robot body & head position. The outputs are joint position values of the robotic arm corresponding to the current object 3D position. The neural network has two hidden layers, each having four neurons. The training of the neural network is based on defining the transformation matrix from the polar spatial coordinates of the object to the robot arm joint positions. T:  $(d,\alpha,\beta) \rightarrow (s1,s2,s3)$ . One method is to use feedback control, the other is to set the robot hand at the object to get the robot joint positions; therefore, using the inverse transformation, T':  $(s1,s2,s3) \rightarrow (d,\alpha,\beta)$ . This set of input and outputs can be used to train the neural network via the error feedback propagation algorithm. A trained neural network will need to normalize the input/output data between 0 and 1. For example limiting the domain to values of the robotic arm length and the minimum distance range of the stereo vision system [8].

Figure 9. Bounding box tracking with object parameters (x,y,h,w) forming the region of interest window [8].

The TLD system takes an accurate approach to matching feature pixels to create a bounding box patch and using the learning algorithm to adjust and refine the process. In this report's system the goal is add further accuracy by rescanning and updating from known object coordinates, which will be explored in later sections. TLD provides a direct method of high resolution edge detection via the TLD learning algorithm. The application to robotics and use of artificial neural networks provides an example of applications of stereo vision and its advantages. Means of feedback control will warrant future investigation. As will its application on an FPGA to investigate improvements in performance of the system over the original PC platform [8].

#### 2.7 Literature Classification

The papers reviewed for this report and specifically the six prime papers selected can be classified by the camera type, image processing method and its application and use of the vision data. Most of the papers presented in the literature review use digital cameras in the visible light spectrum, while the paper [7] used the dynamic visual sensor (DVS) is a modified class of this as its design to sense light intensity. More specialized algorithms were used for paper [5,6,7] such as object feature tracking, modified CAMSHIFT, address-event representation respectively. All the selected papers directly used stereo vision cameras, while a significant amount reviewed, presented mono camera or LIDAR/RADAR object detection and distance measurement systems [9]. For two of the papers [3, 6] there are limitations that are directly and indirectly linked to the reports motivation and objectives. The first paper requires a ground based general computer system using MATLAB for processing. This negates mobile computing applications and power requirements for such (higher cost and can not be embedded into a system platform [3]. The fourth paper utilizes colour vision for object detection, this has the limitation of poor night vision [6]. This was not an original consideration given the project requirements, yet for broader applications and future work that would be a server limitation for vehicle, real world environment operations. For the set of papers selected [3,4] were used for aviation applications for aircraft landing operations. While the rest of papers [5,6,7,8] were applied to general object tracking. Papers [6,7] in particular focused on tracking human in controlled enclosed or dynamic open environments. Stereo vision image processing forms the first stage of a computer vision system. The next stage is in using the visual information to perform tasks. In paper [4, 8] artificial neural networks were employed as a feedback system to refine the task of identifying visual targets (objects or visual features, like symbols). In these cases, identifying the range to a Heli-pad symbol or adjusting the movement of a robotic arm to reach and grab an object [4,8]. In general, all the papers initially reviewed given the research focus and platform requirements spanned signal/stereo camera detection methods. The included object tracking and navigation methods for vehicles and mobile robots. The examination embedded system and its direct application were also reviewed [12-31].

### 3 Design Synthesis

The project's design, its approach and architecture is based on meeting the specified requirement as a result of the limitations of the existing base system performance and research findings presented in the previous chapter of this report. The presented research among others shows the present state of the art means of implementing computer vision systems and image processing techniques to address the problem of utilizing stereo vision to provide depth information. The original stereo camera system is designed to track objects and measure distances within a laboratory environment 3-6 metres, from cameras at a fixed horizontal level and at a vertical height a metre off the ground. Also to detect objects within the cameras field of view.

#### 3.1 Research Analysis

The papers analyzed in the literature observations represent research that aligns the best with this report's objective. Dozens of papers were reviewed covering computer vision, artificial intelligence and image processing methods & applications. Single camera methods of object detection (edge detection, textures, colour detection, image segmentation) & tracking and its applications for creating a representative navigation map in two dimensions and identifying obstacles in the environment, was prominent in the research. Without additional sensors such as LIDAR to provide range information, getting accurate depth information will be difficult and entail extensive calibration. LIDAR has its limitations given its scan resolution (number of laser points) and the electromechanical device needed to scan the surrounding area to reflect the laser beam via the rotated mirror, providing a 2D representation around the scanner recording depth information. This presents mechanical reliability and precision issues under real world conditions of poor lighting, visibility due to weather and obstacles in the environment smaller than the LIDAR resolution [2]. These methods even when combined into a system of multiple LIDAR's (multiple sources of laser return to reduce wait time) [2] and cameras still present additional operational limitations due to hardware, computational and power requirements. Therefore, a passive system of detection and ranging is necessary, which is stereo vision.

#### 3.2 Requirements

The project's requirements are based on its interoperability with the existing system (Embedded System Reconfigurable Laboratory: MARS platform), its stereo camera field of view, the lab testing environment of a well lit room and the distances involved of within 3 metres to track objects of various sizes.

The project design is based on emulating a natural vision system of nature, stereo vision. It is a direct method that provides image & object details, including distance information on the object of focus. The stereo vision model is based around the original platform, the 3 metre range tracking and the required base line (horizontal distance between the pair of parallel cameras) and base height of one metre. The stereo vision model is depicted graphically in figure 4, where details on the camera specifications (focal length, field of view, pixels per camera image) and additional factors that effect the range of objects that can be targeted. Equation (1) provides the computational model. If a low cost and quality camera is used, then there is the possibility of error in the distances measure, so averaging may be need to provide a Euclidean distance of all points measured, as shown in equation (2), where n is the total number of disparities and z is the z-axis position [4].

Equation 2:

$$d = \frac{\sum_{i=1}^{n} Z_i}{n}$$

Given the current state of the art technology, FPGA's can be used for its lower power consumption, efficient use of chip area, logic programmability and as needed hardware reconfiguration, which provides improved computational efficiency. Furthermore, the use of two cameras provide stereo vision with depth perception at reduced hardware cost compared to a LIDAR 2D system [9]. Also given the current limitations of the existing system mainly its reduction of resolution due to image filtering (mean average of image segments) and FPGA memory the project solution is to employ a stereo vision camera system utilizing a FPGA to provide full resolution and depth information for tracking an object in the field of view.

#### 3.3 Design Specification

The stereo vision high resolution system is described by its functional & technical specifications, providing its behaviours and parameters of operation, as presented in the following list.

#### 3.3.1 High Resolution Stereo System Block (functional specification):

- 1. To accept two sets of co-ordinate inputs for both camera streams (left & right) from the system.

- 2. Accept direct camera data input streams for high resolution detail.

- 3. Produce both sets of co-ordinates of the tracked object as output.

- 4. Produce the disparity distance between the left & right cameras, used to compute object distance.

- 5. Accept data when the valid frame signal input is asserted.

- 6. Assert a valid frame signal output when processing is complete.

- 7. Object dimension data can be accepted to determine region of interest.

- 8. Determine the region of interest that is the probable object location.

- 9. Operate over a minimal set of image frames.

3.3.2 High Resolution Stereo System Block (technical specification):

- 1. The primary clock#1 must operate at 25.175MHz for VGA 640x480 operation.

- 2. A reset signal effects the state of the valid frame signal controlling the process state.

- 3. Process one frame at least every 33 milliseconds, for >30 frames a second.

- 4. Utilize YUV luminescence for camera data for system compatibility.

The following figures (10-16) presents the entity declaration/symbol, the overall design, process & model timing diagrams for the system.

### 3.4 Design Symbol

Figure 10. Top level Design Entity: Hi-Resolution Object Scanner. The input/output flow is depicted from left to right. Note: in testing, additional debug signals and modified camera/pixel bus address sizes were used.

## 3.5 Entity Declaration

| entity HiResObjScan is |                                      |                                      |

|------------------------|--------------------------------------|--------------------------------------|

| port ( pixelAddrcam1   | : in STD_LOGI                        | C_VECTOR (19 downto 0);              |

| pixelAddrcam2          | : in STD_LOGIC_VECTOR (19 downto 0); |                                      |

|                        | clk                                  | : in STD_LOGIC;                      |

|                        | clk2                                 | : in std_logic;                      |

|                        | en                                   | : in STD_LOGIC;                      |

|                        | rst                                  | : in STD_LOGIC;                      |

|                        | frameValid                           | : in STD_LOGIC;                      |

|                        | L_horizontal                         | : in STD_LOGIC_VECTOR (9 downto 0);  |

|                        | L_vertical                           | : in STD_LOGIC_VECTOR (9 downto 0);  |

|                        | R_horizontal                         | : in STD_LOGIC_VECTOR (9 downto 0);  |

|                        | R_vertical                           | : in STD_LOGIC_VECTOR (9 downto 0);  |

|                        | Davg                                 | :out std_logic_vector (7 downto 0);  |

|                        | horizontal_1                         | : out STD_LOGIC_VECTOR (9 downto 0); |

|                        | vertical_l                           | : out STD_LOGIC_VECTOR (9 downto 0); |

|                        | horizontal_r                         | : out STD_LOGIC_VECTOR (9 downto 0); |

|                        | vertical_r                           | : out STD_LOGIC_VECTOR (9 downto 0); |

|                        | validOutput                          | : out STD_LOGIC;                     |

|                        | d1                                   | : in std_logic_vector (7 downto 0);  |

|                        | d2                                   | : in std_logic_vector (7 downto 0);  |

|                        |                                      | _logic_vector (7 downto 0);          |

|                        | Cam2Y : in std                       | _logic_vector (7 downto 0));         |

end HiResObjScan;

| Signal Name                                                                                                        | Description of Inputs                            | Size (bits) |  |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------|--|

| PixelAddrcam1                                                                                                      | Left Camera pixel address                        | 20          |  |

| PixelAddrcam2                                                                                                      | Right Camera pixel address                       | 20          |  |

| Clk                                                                                                                | Main clock signal (internal)                     | 1           |  |

| Clk2 Auxiliary clock signal (external to camera)                                                                   |                                                  | 1           |  |

| EN                                                                                                                 | Enable operation                                 | 1           |  |

| RST                                                                                                                | Reset                                            | 1           |  |

| FrameValid                                                                                                         | Frame ready                                      | 1           |  |

| L_horizontalLeft camera known horizontal object coordinatesL_verticalLeft camera known vertical object coordinates |                                                  | 10          |  |

|                                                                                                                    |                                                  | 10          |  |

| R_horizontal                                                                                                       | Right camera known horizontal object coordinates | 10          |  |

| R(_vertical                                                                                                        | Right camera known vertical object coordinates   | 10          |  |

| D1                                                                                                                 | Object dimension (left camera)                   | 8           |  |

| D2                                                                                                                 | Object dimension (Right camera)                  | 8           |  |

| Cam1Y                                                                                                              | Left camera data                                 | 8           |  |

| Cam2Y                                                                                                              | Right camera data                                | 8           |  |

Table 1. HiResObjScan Entity Input signals.

| Signal Name  | Description of Outputs                             | Size (bits) |

|--------------|----------------------------------------------------|-------------|

| Davg         | Disparity amount (operational average)             | 8           |

| Horizontal_1 | Left camera horizontal updated object coordinates  | 10          |

| Vertical_1   | Left camera vertical updated object coordinates    | 10          |

| Horizontal_r | Right camera horizontal updated object coordinates | 10          |

| Vertical_r   | Right camera vertical updated object coordinates   | 10          |

| ValidOutput  | Frame ready, with updated data                     | 1           |

Table 2. HiResObjScan Entity Output signals.

# 3.6 Design Block Diagram

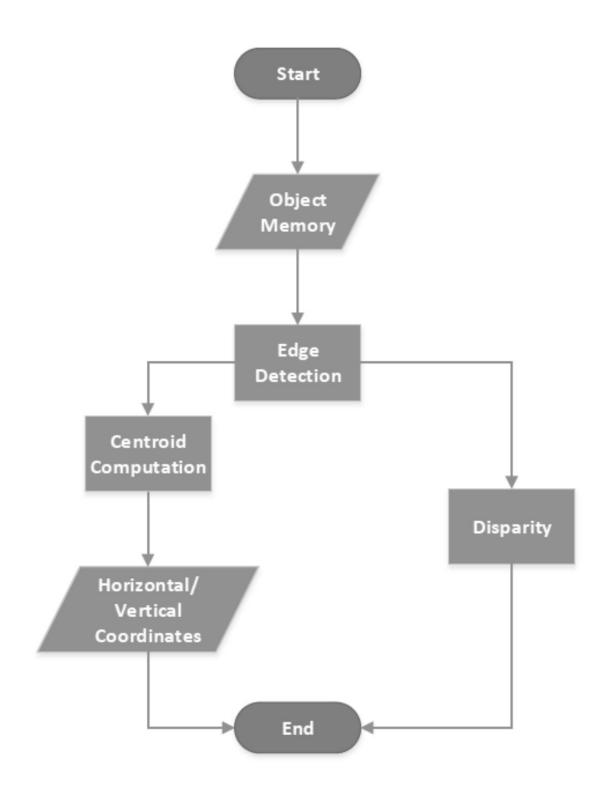

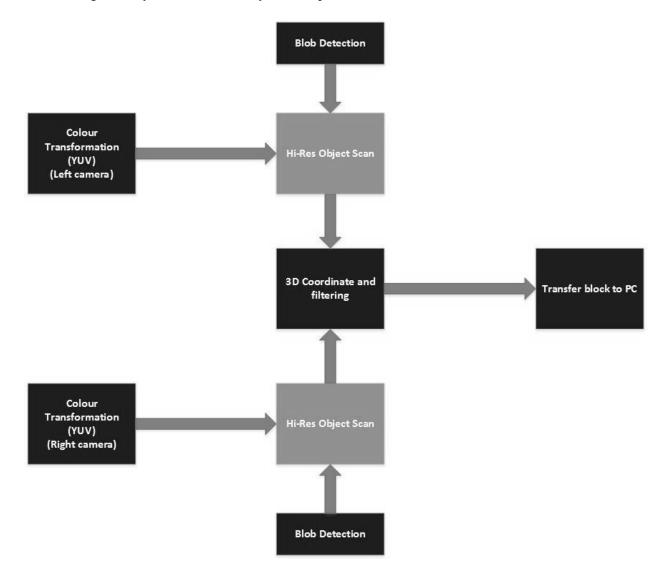

Figure 11. Design High level Operational Diagram.

# 3.7 Process Diagram

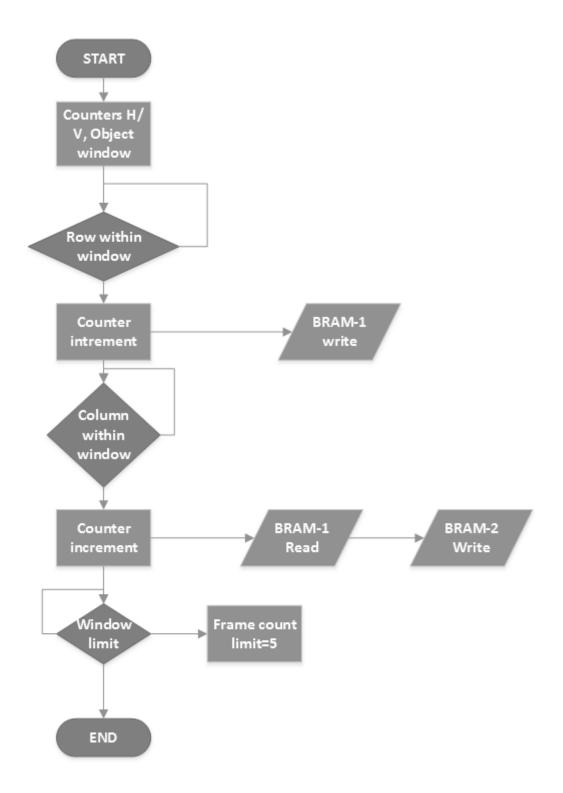

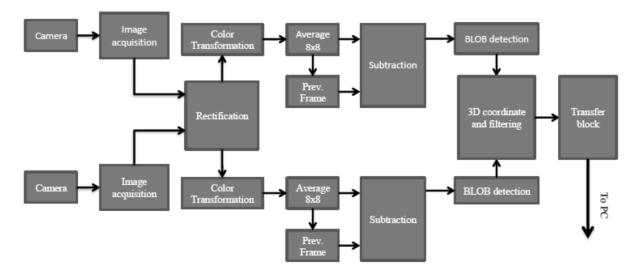

Figure 12. System General Process Diagram. The functional program is depicted, with both left & right data streams. Input coordinates of are corrected for prior compression, then the object scan is perfomed within the region of interest window. When the possible object is found then edge detection and disparity computation is performed.

Figure 13. Row/Line Operations. Each row pixel is check if its within the region of interest. When a frame is read in to memory it is subsequently copied for future comparison to determine frame disparity.

Figure 14. Frame Disparity & Co-ordinate updates. Suspected Object memory is search via a divide and conquer method to find the pixel address of the edges of the object. These are used to compute the object centre coordinates & disparity.

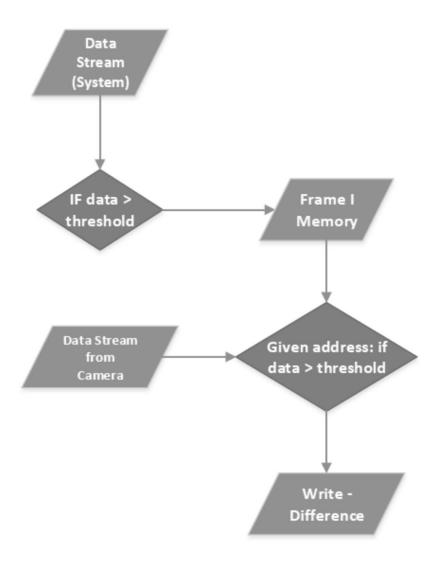

Figure 15. Frame/Memory Operations. The detected pixel data stored from one frame is compared to the next frame, pixel changes indicate the edges of the suspected object.

# 3.8 Model Timing Diagram

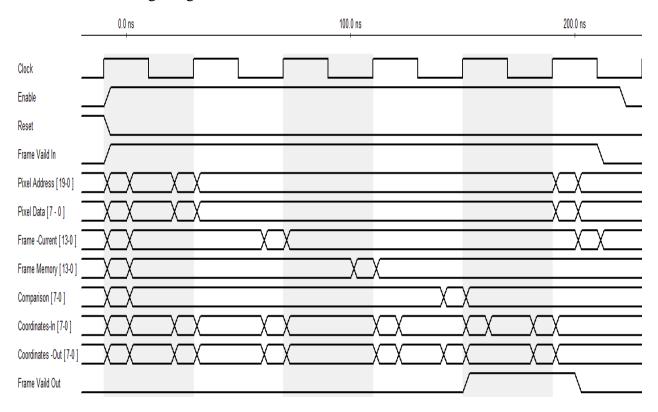

Figure 16. Timing Model of system. This general presentation of system timing shows the critical transitions that are needed for operation, from enabling the system, synchronization of inputs to frame/pixel comparison and coordinate outputs.

# 4 Implementation & Test verification

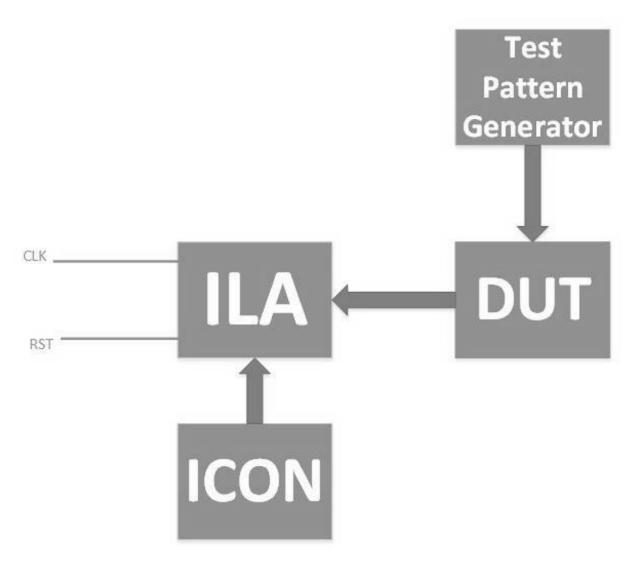

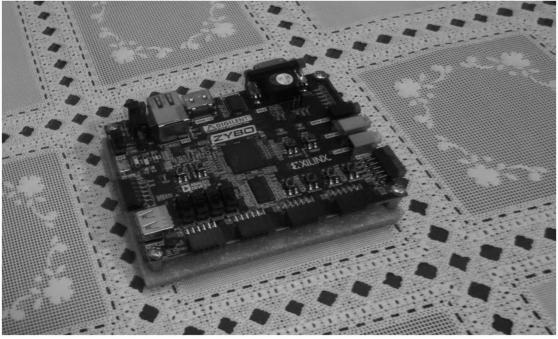

This section of the report presents how the design developed from the project specification, the VHDL coding effort, hardware integration and testing methods used to produce the project design and its results. The main FPGA hardware platform used was the Digilent Zybo: with Xilinx, Zynq FPGA was used to implement the designed solution for the high resolution stereo system (first used was the Xilinx Spartan3E for initial test development, but the system was migrated to the Zybo Zynq-7010 for greater memory and future project development needs). The overall goal for implementation is to integrate the project module into the M.A.R.S. platform. A key indicator of its performance is the functioning of the module on its own, supplied by generated stimuli and the monitoring of critical signals from it to conform functionality. Since the generated signals emulate actual operating conditions then it serves as a key milestone in confirming operational performance.

#### 4.1 Module Description

The module for the high resolution object tracking stereo system was programmed in VHDL (using Xilinx ISE version 14.7), consisting of an entity containing the input for both cameras, clocks, frame valid signal, object blob detection module signals (including object dimension) and the output signals providing the updated object coordinates (two sets of horizontal & vertical), frame valid and average pixel displacement value. The behavioural architecture describes the internal processing of the module. BRAM (block logic reconfigurable RAM) components are instantiated within the architecture to access its memory functions (ex. pixel data storage and retrieval). The code is organized into internal signal registers and process statements. (This design was chosen to make code organization and readability more efficient). The processes operate concurrently to read in old object blob coordinate data, then to gather new camera data from the known coordinates of the object within the frame area and finally to compute the average pixel displacement of the object from both left & right frames and to provide new object coordinates.

#### 4.2 Functional Overview

The module can fit into an existing stereo vision system [10] where luminescence data from both cameras are filtered by the averaging block (reduce memory requirement by 64 times), the difference of current and subsequent frames is computed. Then the object blob detection block determines the pixels which are part of the object. Now the high resolution object tracking module will use the object blob detection module data with updated camera data to provide refined coordinate and depth information. The 3D

33

coordinate & filter block takes the object coordinate data and provides object centroid and depth data that is transferred to a pic-microcontroller/PC interface [10]. It now can accept the more accurate coordinate data of the high resolution object tracking module with improved depth data (figure 17).

Figure 17. Stereo System Design Overview, M.A.R.S. platform [10].