# TIME-INTERLEAVED PULSE-SHRINKING AND ALL-DIGITAL $\Delta\Sigma$ TIME-TO-DIGITAL CONVERTERS

by

Young Jun Park

Master of Science, University of Southern California, USA, 2012 Bachelor of Engineering, Korea Aerospace University, South Korea, 2004

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2017 ©Young Jun Park 2017

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

#### ABSTRACT

#### Young Jun Park

Time-Interleaved Pulse-Shrinking and All-Digital  $\Delta\Sigma$  Time-To-Digital Coverters Doctor of Philosophy, Electrical and Computer Engineering, Ryerson University, 2017

This dissertation deals with the design of sub-per-stage-delay time-to-digital converters (TDCs). Two classes of TDCs namely pulse-shrinking TDCs and  $\Delta\Sigma$  TDCs are investigated.

In pulse-shrinking TDCs, a two-step pulse-shrinking TDC consisting of a set of coarse and fine pulse-shrinking TDCs is proposed to increase a dynamic range without employing a large number of pulse-shrinking stages. A residual time extraction scheme capable of extracting the residual time of the coarse TDC is developed. The simulation / measurement results of the TDC implemented in an IBM 130 nm 1.2 V CMOS technology show that the TDC offers 1.4 ns conversion time, 1 LSB DNL and INL, and consumes 0.163 pJ/step. To further improve the conversion time, a time-interleaved scheme is developed to extract the residual time of the coarse TDC and utilized in design of a two-step pulse-shrinking TDC. Residual time extraction is carried out in parallel with digitization to minimize latency. The simulation and measurement results of the TDC show that it offers 0.85 ns conversion time, 0.285 LSB DNL, and 0.78 LSB.

In  $\Delta\Sigma$  TDCs, a 1-1 multi-stage noise shaping (MASH)  $\Delta\Sigma$  TDC with a new differential cascode time integrator is proposed to suppress even-order harmonic tones and current mismatch-induced timing errors. Simulation results show that the proposed TDC offers 1.9 ps time resolution over 48-415 kHz signal band while consuming 502  $\mu$ W. Finally, an alldigital first-order  $\Delta\Sigma$  TDC utilizing a bi-directional gated delay line integrator is developed. Time integration is obtained via the accumulation of charge of the load capacitor of gated delay stages and the logic state of gated delay stages. The elimination of analog components allows the TDC to benefit fully from technology scaling. Simulation results show that the TDC offers first-order noise-shaping, 10.8 ps time resolution while consuming 46  $\mu$ W.

#### ACKNOWLEDGMENTS

I would first like to thank to my PhD supervisor, Professor Fei Yuan, for supporting me during the past four years. He has provided insightful discussions and suggestions about the research. I could not have completed this work without the support. I also should thank the members of my PhD committee, Professors Vadim Geurkov, Gul Khan, Guangjun Liu and Wai Tung Ng from University of Toronto. Their comments and feedback have been invaluable. I wish to thank my colleagues, Yushi Zhou, Durand Jarrett-Amor, Jean-Claude Clarke, Yue Li, and Matthew Dolan, in the Integrated Circuits and Systems Research group at Ryerson University who provided wonderful ideas and friendship. I would especially like to thank and dedicate this dissertation to my amazing family, my parents, parents-in-law, my sister, brother-in-law and his wife, for the love, support, and constant encouragement over the years. Finally, but most importantly, I wish to thank my wife, Jung Eun Koo, and children, Kyan Park and Lian Park for their patience, assistance, support and faith in me. I could not have completed my doctoral studies without the support of all these wonderful people!

# Table of Contents

| Ta            | Table of Contents     vi |                                            |     |  |  |

|---------------|--------------------------|--------------------------------------------|-----|--|--|

| $\mathbf{Li}$ | List of Tables x         |                                            |     |  |  |

| Li            | st of                    | Figures                                    | xi  |  |  |

| $\mathbf{Li}$ | st of                    | Symbols and Abbreviations                  | xvi |  |  |

| 1             | Intr                     | oduction of Time-Mode Signal Processing    | 1   |  |  |

|               | 1.1                      | Why Time-Mode?                             | 2   |  |  |

|               | 1.2                      | Challenges in Time-Mode Signal Processing  | 3   |  |  |

|               | 1.3                      | An Overview of TDCs                        | 3   |  |  |

|               |                          | 1.3.1 Delay-line TDCs                      | 4   |  |  |

|               |                          | 1.3.2 Vernier delay-line TDCs              | 5   |  |  |

|               |                          | 1.3.3 Hierarchical vernier delay-line TDCs | 6   |  |  |

|               |                          | 1.3.4 Pulse-shrinking TDCs                 | 7   |  |  |

|               |                          | 1.3.5 Gated ring oscillator TDCs           | 9   |  |  |

|               |                          | 1.3.6 $\Delta\Sigma$ TDCs                  | 10  |  |  |

|               | 1.4                      | Motivation                                 | 12  |  |  |

|               | 1.5                      | Contributions                              | 14  |  |  |

|               | 1.6                      | Dissertation Organization                  | 15  |  |  |

|               | 1.7                      | Chapter Summary                            | 16  |  |  |

| <b>2</b>            | 2 Time-Interleaved Pulse-Shrinking TDC |            |                                                                            | 17 |

|---------------------|----------------------------------------|------------|----------------------------------------------------------------------------|----|

|                     | 2.1                                    | Two-S      | Step Pulse-Shrinking TDC                                                   | 17 |

|                     | 2.2                                    | Chara      | cteristics of Two-Step Pulse-Shrinking TDC                                 | 20 |

|                     |                                        | 2.2.1      | Mismatch-induced timing errors                                             | 20 |

|                     |                                        | 2.2.2      | Thermal noise-induced timing errors                                        | 25 |

|                     |                                        | 2.2.3      | Switching noise-induced timing error                                       | 26 |

|                     |                                        | 2.2.4      | Timing error of delay stages                                               | 29 |

|                     |                                        | 2.2.5      | Conversion time                                                            | 29 |

|                     |                                        | 2.2.6      | Power consumption                                                          | 30 |

|                     |                                        | 2.2.7      | Silicon area consumption                                                   | 32 |

|                     |                                        | 2.2.8      | Gain mismatch                                                              | 33 |

|                     | 2.3                                    | Time-      | Interleaved Pulse-Shrinking TDC                                            | 34 |

|                     | 2.4                                    | Chara      | cteristics of Time-Interleaved Pulse-Shrinking TDC                         | 36 |

|                     |                                        | 2.4.1      | Silicon area consumption                                                   | 37 |

|                     |                                        | 2.4.2      | Power consumption                                                          | 38 |

|                     |                                        | 2.4.3      | Mismatch-induced timing error                                              | 39 |

|                     |                                        | 2.4.4      | Conversion time                                                            | 41 |

|                     |                                        | 2.4.5      | Timing analysis                                                            | 43 |

|                     |                                        | 2.4.6      | Jitter                                                                     | 44 |

|                     | 2.5                                    | Simula     | ation and Measurement Results                                              | 46 |

|                     |                                        | 2.5.1      | Simulation results of two-step pulse-shrinking TDC                         | 47 |

|                     |                                        | 2.5.2      | Measurement results of two-step pulse-shrinking TDC                        | 49 |

|                     |                                        | 2.5.3      | Simulation results of time-interleaved pulse-shrinking TDC $\ . \ . \ .$ . | 52 |

|                     |                                        | 2.5.4      | Measurement results of time-interleaved pulse-shrinking TDC $\ . \ . \ .$  | 52 |

| 2.6 Chapter Summary |                                        | er Summary | 57                                                                         |    |

### 3 1-1 MASH $\Delta\Sigma$ TDC

|   | 3.1            | Time   | Integrator                                           | 60 |

|---|----------------|--------|------------------------------------------------------|----|

|   |                | 3.1.1  | Time adder                                           | 60 |

|   |                | 3.1.2  | Time register                                        | 62 |

|   |                | 3.1.3  | Single-ended time integrator                         | 64 |

|   |                | 3.1.4  | Differential time integrator                         | 66 |

|   | 3.2            | Time-  | Mode 1-1 MASH $\Delta\Sigma$ Modulator               | 67 |

|   | 3.3            | Timin  | g Error                                              | 68 |

|   |                | 3.3.1  | Random timing error                                  | 68 |

|   |                | 3.3.2  | Deterministic timing error                           | 72 |

|   |                | 3.3.3  | Total timing error                                   | 75 |

|   |                | 3.3.4  | Model of time integrator                             | 76 |

|   | 3.4            | Discus | ssion                                                | 77 |

|   |                | 3.4.1  | Timing signal                                        | 77 |

|   |                | 3.4.2  | Sampling frequency                                   | 77 |

|   |                | 3.4.3  | Offset time $T_{os}$                                 | 78 |

|   |                | 3.4.4  | Gain of time integrator                              | 78 |

|   | 3.5            | Simula | ation Results                                        | 79 |

|   | 3.6            | Conclu | usions                                               | 83 |

|   |                | TD C   |                                                      |    |

| 4 | $\Delta\Sigma$ | TDC    | with Bi-Directional Gated Delay Line Time Integrator | 85 |

|   | 4.1            | Bi-Dir | rectional Gated Delay Cell                           | 85 |

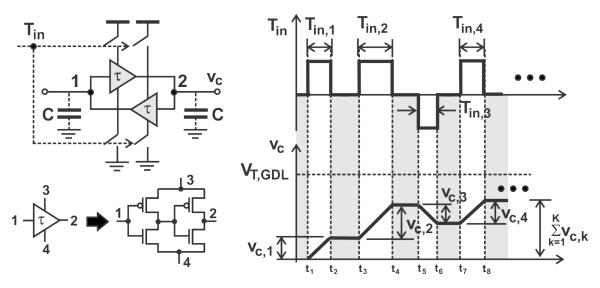

|   | 4.2            | Bi-Dir | rectional Gated Delay Line                           | 87 |

|   | 4.3            | All-Di | gital First-Order Single-Bit $\Delta\Sigma$ TDC      | 89 |

|   | 4.4            | Desigr | n Considerations                                     | 91 |

|   |                |        |                                                      |    |

60

|    | 4.5          | Simulation Results | 92 |

|----|--------------|--------------------|----|

|    | 4.6          | Chapter Summary    | 93 |

| 5  | Con          | clusions           | 95 |

|    | 5.1          | Conclusions        | 95 |

|    | 5.2          | Future Work        | 96 |

| Bi | Bibliography |                    |    |

# List of Tables

| 2.1 | Performance comparison of pulse-shrinking TDCs | 59 |

|-----|------------------------------------------------|----|

| 3.1 | Performance comparison of $\Delta\Sigma$ TDCs  | 83 |

| 4.1 | Performance comparison of $\Delta\Sigma$ TDCs  | 93 |

# List of Figures

| 1.1 | Delay-line TDCs $[1], [2], [3], \ldots, \ldots, \ldots, \ldots, \ldots, \ldots$                                                                                                                                                            | 5  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Vernier delay-line TDCs [4]                                                                                                                                                                                                                | 6  |

| 1.3 | Hierarchical vernier delay-line TDC [5]                                                                                                                                                                                                    | 7  |

| 1.4 | Pulse-shrinking TDCs [6, 7]                                                                                                                                                                                                                | 8  |

| 1.5 | Cyclic pulse-shrinking TDCs.                                                                                                                                                                                                               | 9  |

| 1.6 | GRO TDCs [8]. (A) Block diagram. (B) Waveform                                                                                                                                                                                              | 11 |

| 1.7 | (A) Time adder [9]. (B) Gated delay cell [9]. (C) $\Delta\Sigma$ TDC [10]. (D) Waveform of time adder.                                                                                                                                     | 12 |

| 1.8 | $\Delta\Sigma$ TDCs [6, 7]                                                                                                                                                                                                                 | 14 |

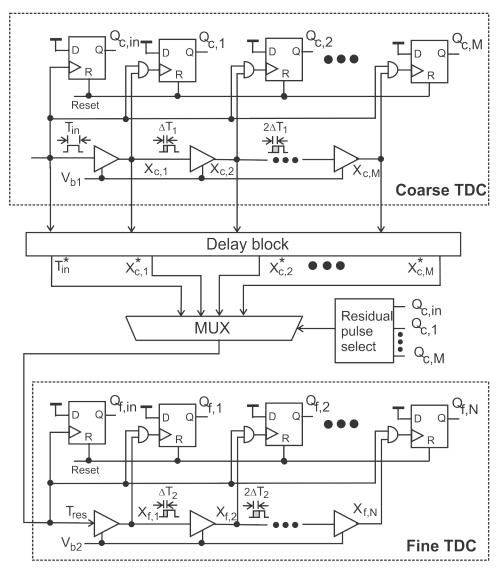

| 2.1 | Simplified schematic of two-step pulse-shrinking delay-line TDC. All D flipflops (DFFs) are positive edge triggered.                                                                                                                       | 19 |

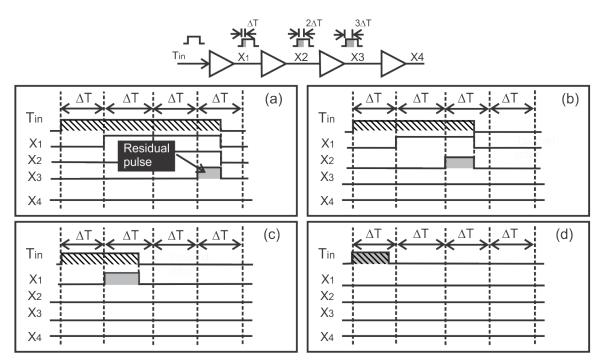

| 2.2 | Extraction of the residual pulse of coarse TDC. (a) $3\Delta T < T_{in} < 4\Delta T$ . (b) $2\Delta T < T_{in} < 3\Delta T$ . (c) $\Delta T < T_{in} < 2\Delta T$ . (d) $0 < T_{in} < \Delta T$                                            | 20 |

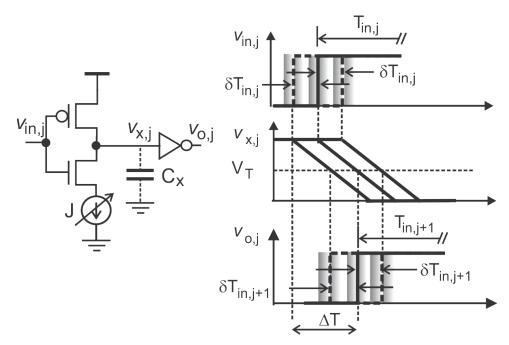

| 2.3 | Simplified schematic of residual pulse selection and waveform. (a) Simplified schematic. (b) $0 < T_{in} < \Delta T$ . (c) $\Delta T < T_{in} < 2\Delta T$ . (d) $2\Delta T < T_{in} < 3\Delta T$ . (e) $3\Delta T < T_{in} < 4\Delta T$ . | 21 |

| 2.4 | Mismatch-induced timing error in pulse-shrinking stage. The timing error at the output of a pulse-shrinking stage contains the timing error present at the input and that induced by the mismatch of the pulse-shrinking stage             | 23 |

| 2.5 | Jitter of pulse-shrinking stages.                                                                                                                                                                                                          | 27 |

| 2.6 | The effect of the delay error of delay stages on the TDC                                                                                                                                                                                   | 30 |

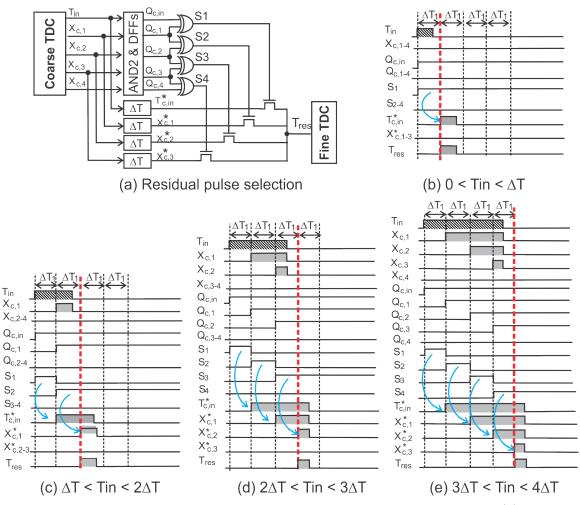

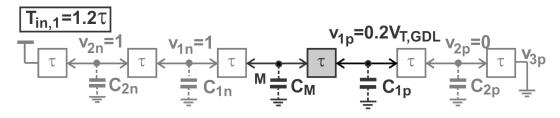

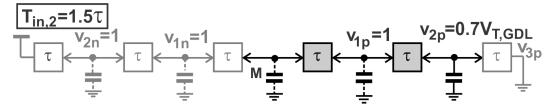

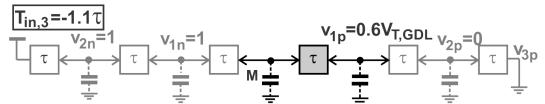

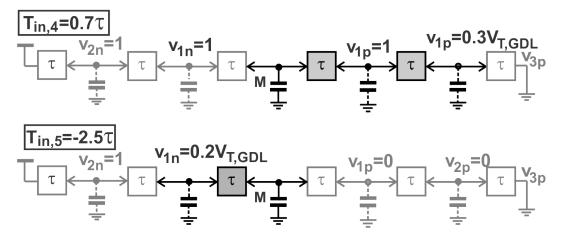

| 2.7  | Residual pulse of coarse TDC. The location and width of the residual pulse $T_{res}$ of the coarse TDC are determined by $T_{in}$ and the residual pulse is only available at the falling edge of $T_{in}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

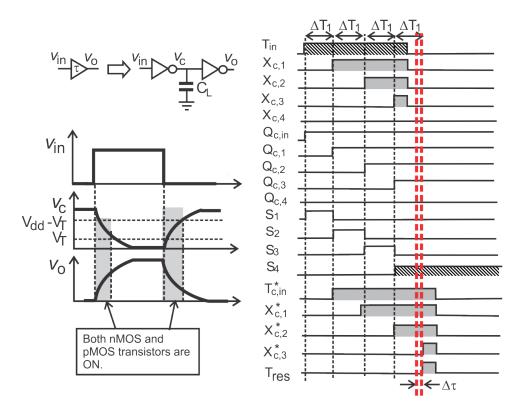

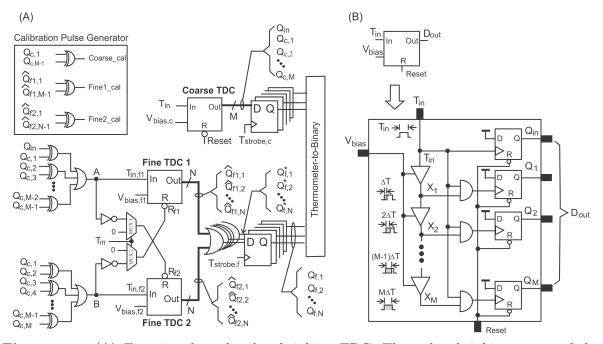

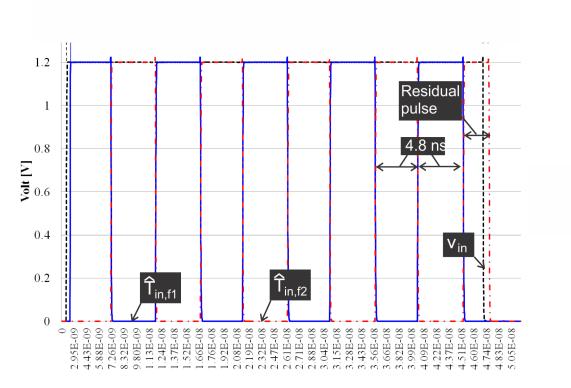

| 2.8  | (A) Time-interleaved pulse-shrinking TDC. The pulse-shrinking stages of the coarse and fine TDCs have the same transistor dimensions but distinct capacitor loads. The load capacitance of the pulse-shrinking stages of the fine TDCs are from devices while that of the coarse TDC is an external 402 fF MiM capacitor. (B) Configuration of pulse-shrinking TDCs. The outputs of the coarse TDC are $Q_{c,1}, Q_{c,2},, Q_{c,M}$ with the first subscript identifying the coarse TDC and the second subscript identifying the delay stage of the TDC. $Q_{in}$ is the input of the coarse TDC. The outputs of the fine TDC are $Q_{f,1}, Q_{f,2},, Q_{f,N}$ with the first subscript identifying the fine TDC and the second subscript identifying the fine TDC. | 36 |

| 2.9  | Non-overlapping waveforms of $T_{in,f1}$ and $T_{in,f2}$ for $T_{in}=45$ ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37 |

| 2.10 | Mismatch-induced time error in pulse-shrinking TDCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42 |

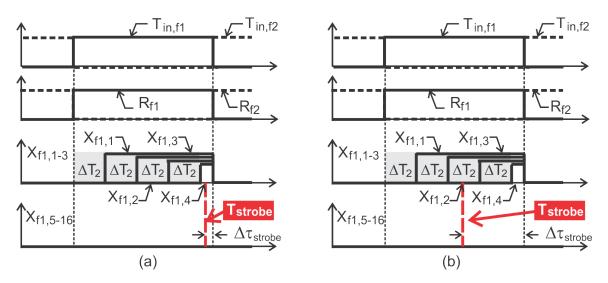

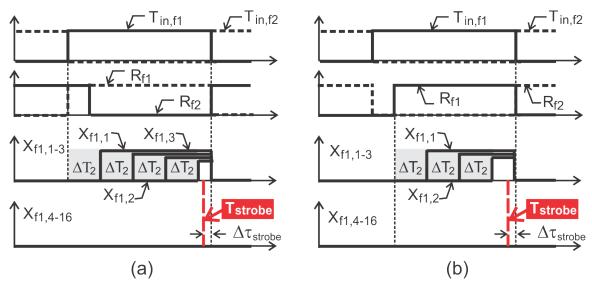

| 2.11 | Strobing the output of fine TDC1. (a) Proper strobing. (b) Early strobing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

| 2.12 | Strobing the output of fine TDC1 with $T_{in}$ mismatch. (a) $T_{in,f1}$ has a mismatch-<br>induced delay. (b) $T_{in,f2}$ has a mismatch-induced lead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44 |

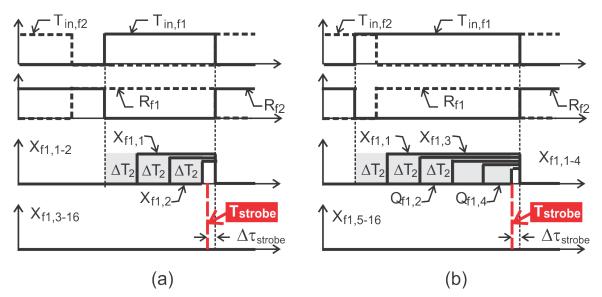

| 2.13 | Strobing the output of fine TDC1 with reset mismatch. (a) $R_{f1}$ has a mismatch-induced delay. (b) $R_{f2}$ has a mismatch-induced delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45 |

| 2.14 | Jitter of pulse-shrinking stages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

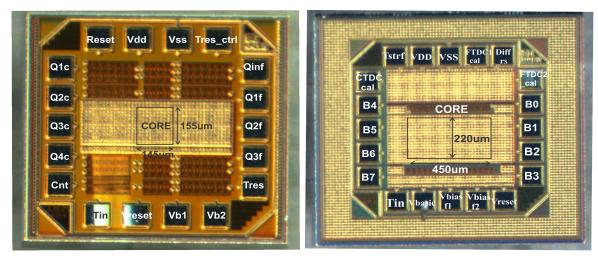

| 2.15 | Die micrograph of the 4 bit two-step pulse-shrinking TDC (left) and that of the 8 bit time-interleaved pulse-shrinking TDC including a thermometer-to-<br>binary encoder (Right). The core area of the two-step TDC : 145 $\mu$ m x 155 $\mu$ m. The core area of the time-interleaved TDC : 450 $\mu$ m x 220 $\mu$ m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47 |

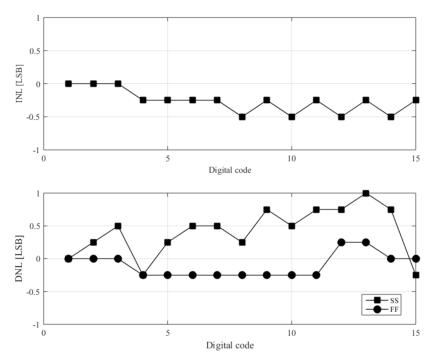

| 2.16 | Simulated DNL of the TDC (post-layout). Top - Normal process condition.<br>Bottom - SS and FF process corners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48 |

| 2.17 | Simulated INL of the TDC (post-layout). Top - Normal process condition.<br>Bottom - SS and FF process corners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

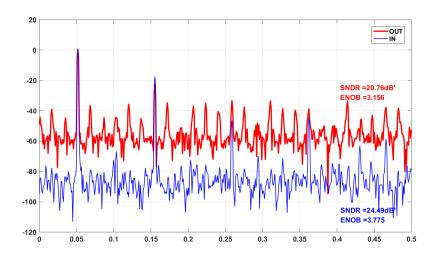

| 2.18 | Simulated spectrum the TDC (post-layout). Input : Sinusoid of 5.176 MHz $@f_s = 100$ MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 |

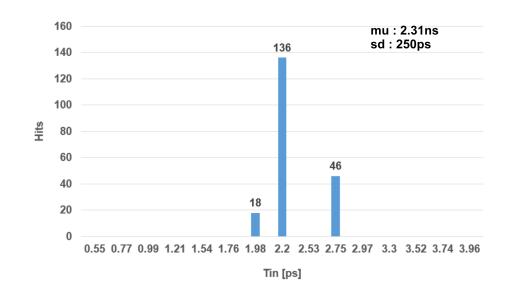

| 2.19 | Monte Carlo simulation results when $T_{in} = 2.2$ ns (200 samples)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50 |

| 2.20 | Test setup of the two-step pulse-shrinking TDC (PCB with SMA connectors for connecting to test equipment not shown)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51 |

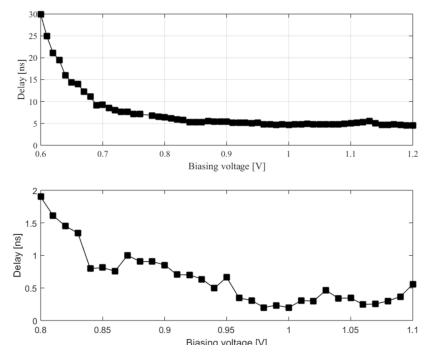

| 2.21 | Measured dependence of the pulse shrinkage of the coarse pulse-shrinking<br>stage on bias voltage. Top - Without offset calibration. Bottom - With 5ns<br>offset calibration                                                                                                                                                                                                                                                                                                           | 52 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

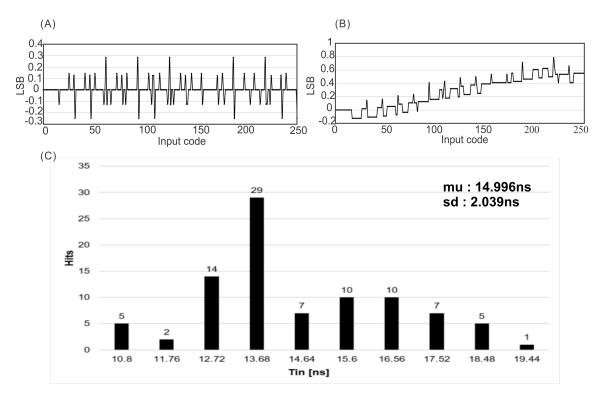

| 2.22 | (A) Simulated DNL (post-layout), (B) Simulated INL (post-layout), (C) Monte Carlo simulation results when $T_{in} = 15$ ns (90 samples)                                                                                                                                                                                                                                                                                                                                                | 53 |

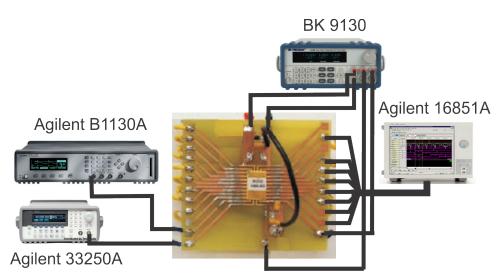

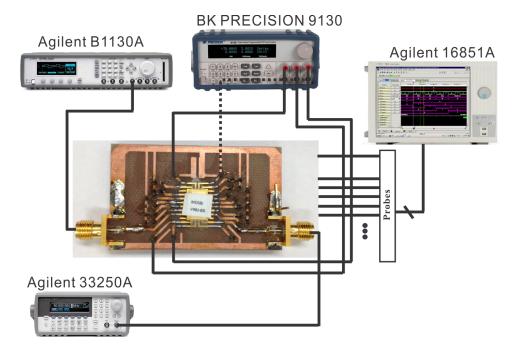

| 2.23 | Test setup of the time-interleaved pulse-shrinking TDC. An Agilent B1130A pattern generator was used to generate $T_{in}$ and an Agilent 16851A logic analyzer was used to capture the digital output of the TDC. Three DC voltages, namely $V_{\text{bias,c}}$ , $V_{\text{bias,f1}}$ , and $V_{\text{bias,f2}}$ for tuning the discharge current of the coarse and fine TDCs so as to obtain the desired per-stage pulse shrinkage are from a BK 9130 multi-channel DC power supply. | 54 |

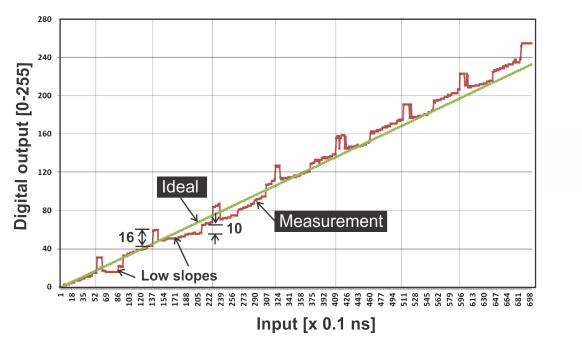

| 2.24 | Measured transfer characteristics of TDC                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55 |

| 2.25 | Screen shot of logic analyzer with $T_{in} = 70$ ns. (A) Single shot, (B) Multiple shots with infinite persistence mode on                                                                                                                                                                                                                                                                                                                                                             | 56 |

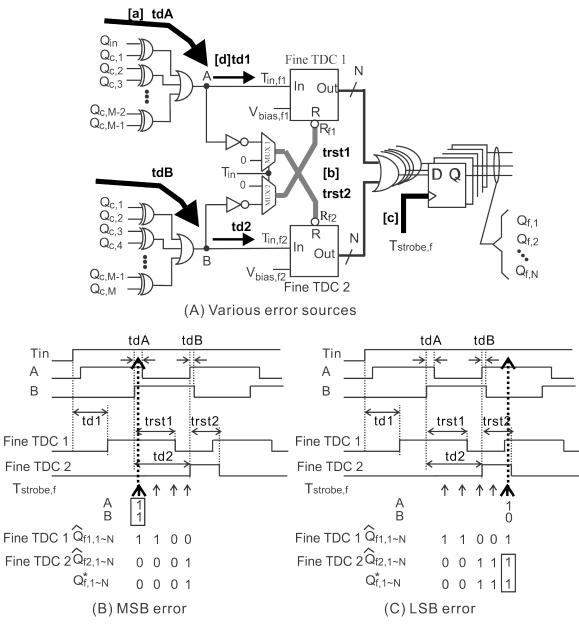

| 2.26 | (A) Major error sources in the test chip. [a] Signal path mismatch. [b] Reset time mismatch. [c] $T_{strobe,f}$ timing error. [d] Propagation delay mismatch between two fine TDCs' input. (B) MSB error. (C) LSB error                                                                                                                                                                                                                                                                | 57 |

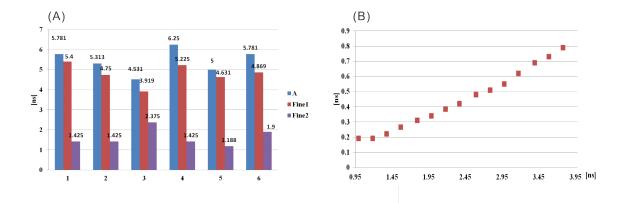

| 2.27 | (A) Pulse width comparison. (B) Coarse TDC pulse shrinkage                                                                                                                                                                                                                                                                                                                                                                                                                             | 58 |

| 2.28 | $V_{ss}$ line resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58 |

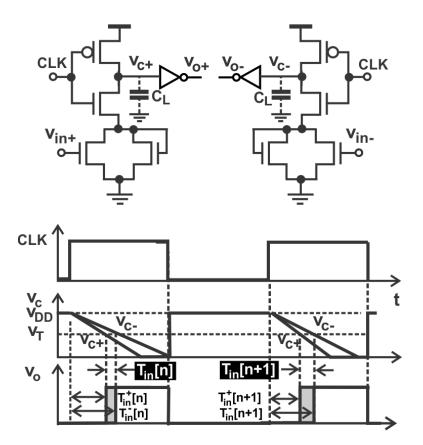

| 3.1  | Time adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61 |

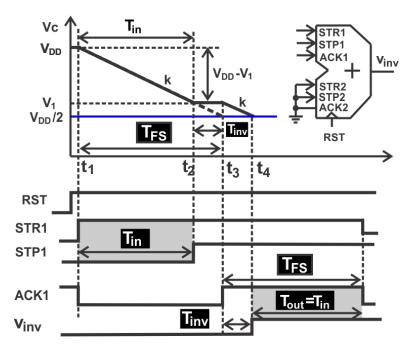

| 3.2  | Timing diagram of time adder                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63 |

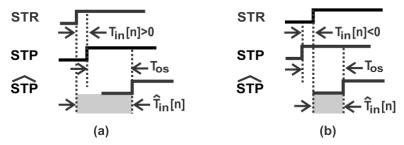

| 3.3  | Polarity of time variables. (a) $T_{in}[n] > 0$ . (b) $T_{in}[n] < 0$ . $\hat{T}_{in}$ is measured from the rising edge of STR to that of $\widehat{\text{STP}}$                                                                                                                                                                                                                                                                                                                       | 63 |

| 3.4  | Time register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64 |

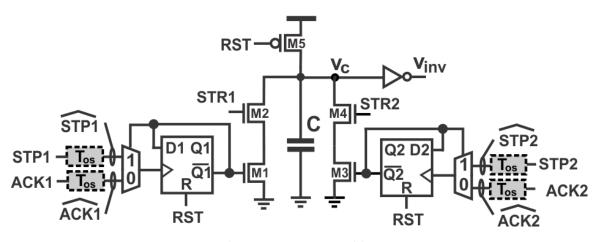

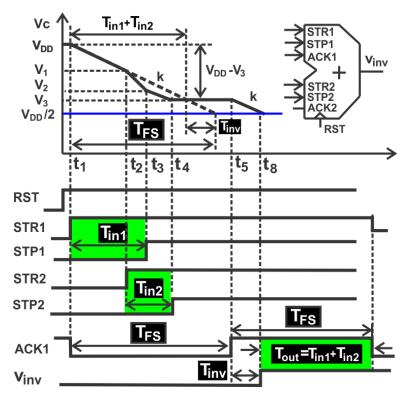

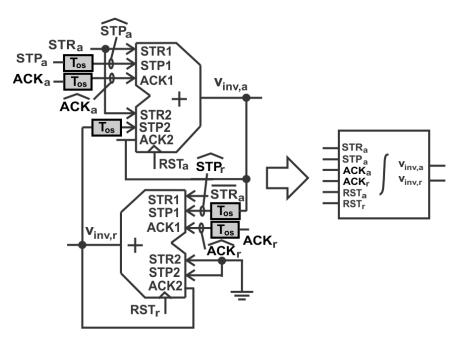

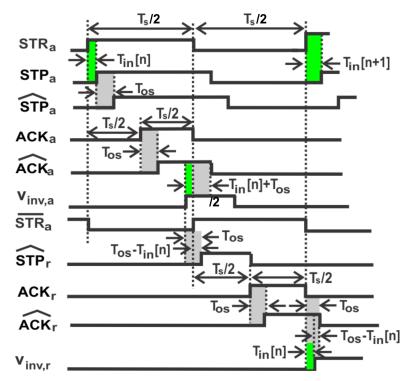

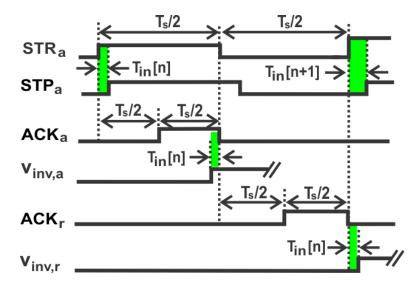

| 3.5  | Schematic of single-ended time integrator. The output of the time integrator<br>is the time interval bordered by the rising edge of $v_{inv,a}$ and that of $\overline{\text{STR}}_a$ .<br>The time offset of ACK <sub>a</sub> changes from $T_{os}$ to $2T_{os}$ after the first cycle of the<br>operation, due to the time duration of the time register                                                                                                                             | 65 |

| 3.6  | Timing diagram of single-ended time integrator. The time offset of $ACK_a$ changes from $T_{os}$ to $2T_{os}$ after the first cycle of the operation, due to the time duration of the time register.                                                                                                                                                                                                                                                                                   | 66 |

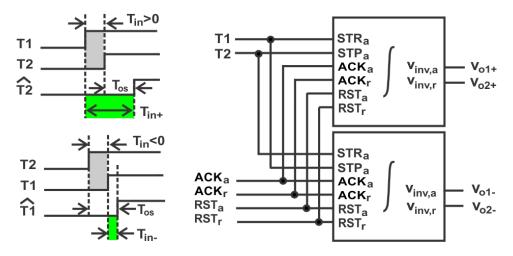

| 3.7  | Differential time integrator.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.8  | Generation of differential sinusoidal time variable                                                                                  | 68       |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

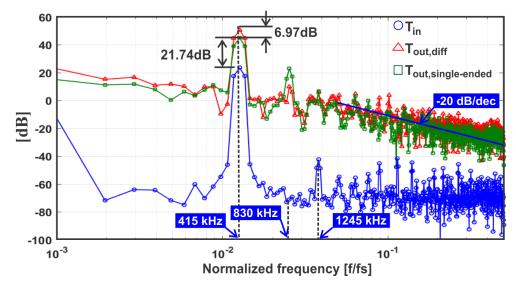

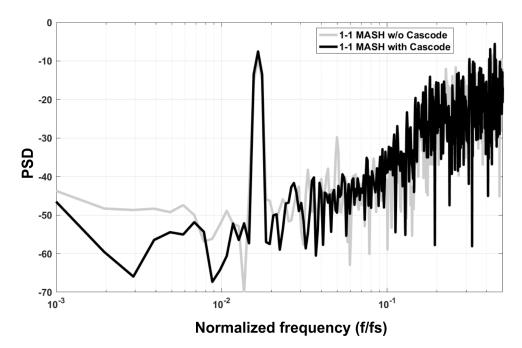

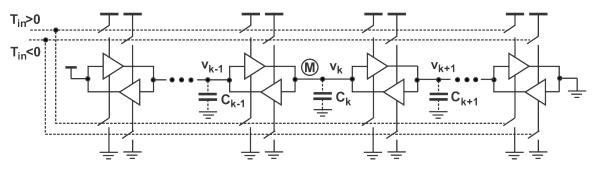

| 3.9  | Spectrum of time integrators. Sampling frequency 25 MHz, input frequency 415 kHz, amplitude 50 ps. 1024 samples with Hanning window. | 69       |

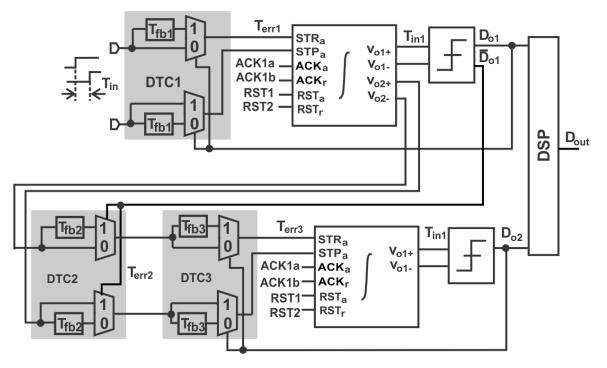

| 3.10 | ) 1-1 MASH time-mode $\Delta\Sigma$ TDC                                                                                              |          |

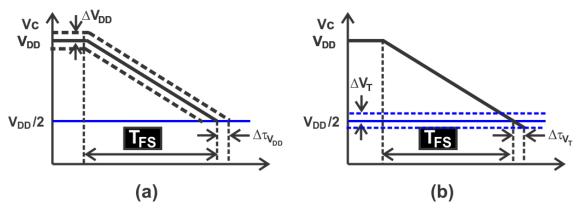

| 3.11 | Timing error due to supply voltage fluctuation (left) and threshold voltage fluctuation of load inverter (right).                    | 72       |

| 3.12 | Current mismatch.                                                                                                                    | 73       |

| 3.13 | Model of time integrator. $E_a$ outside the loop will be shaped out when the integrator is in a $\Delta\Sigma$ modulator.            | 76       |

| 3.14 | Timing of single-ended time integrator                                                                                               | 77       |

| 3.15 | Positive time variable generation.                                                                                                   | 78       |

| 3.16 | Timing diagram of single-ended time integrator with offset time blocks removed.                                                      | 79       |

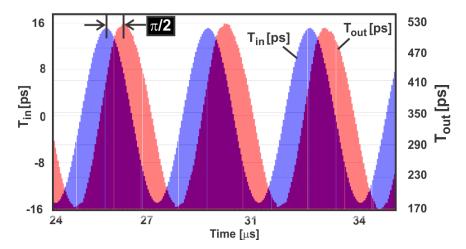

| 3.17 | Waveforms of single-ended time integrator. Input : $T_m = 15$ ps, $f_{in} = 317$ kHz. Sampling frequency $f_s = 25$ MHz              | 80       |

| 3.18 | Behavioral analysis of 1-1 MASH $\Delta\Sigma$ TDC                                                                                   | 81       |

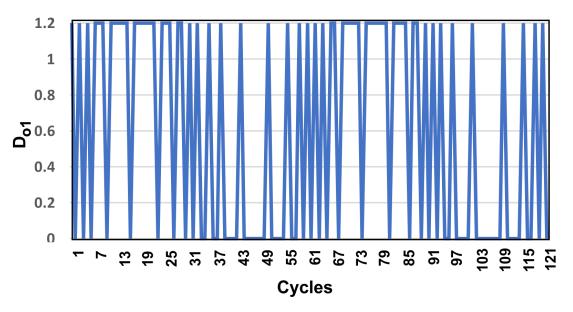

| 3.19 | Waveform of the output of 1-1 MASH $\Delta\Sigma$ TDC from behavioral analysis                                                       | 81       |

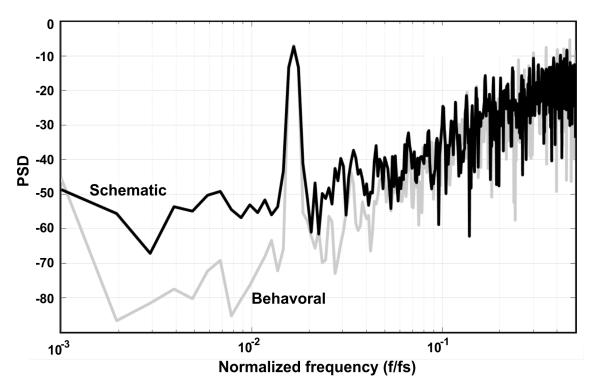

| 3.20 | Spectrum of 1-1 MASH time-mode $\Delta\Sigma$ Modulator from both behavioral analy-                                                  |          |

|      | sis and schematic-level simulation (cascode time integrators with raised thresh-<br>old voltage of load inverter).                   | 82       |

| 3.21 |                                                                                                                                      | 82<br>83 |

|      | old voltage of load inverter)                                                                                                        | 83       |

|      | old voltage of load inverter)                                                                                                        | 83<br>84 |

|      | old voltage of load inverter)                                                                                                        | 83       |

| 3.22 | old voltage of load inverter)                                                                                                        | 83<br>84 |

| 4.4 | (A) Digital-to-time converter [10], (B) Edge alignment block [11]                                                           | 90 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 4.5 | All-digital first-order $\Delta\Sigma$ TDC with a single-bit time quantizer                                                 | 91 |

| 4.6 | Effect of mismatch between forward and reverse gated delay cells                                                            | 92 |

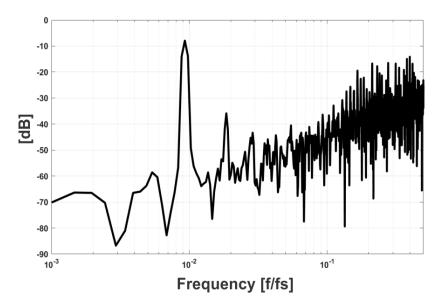

| 4.7 | Spectrum of $\Delta\Sigma$ TDC. $f_{in} = 231.93$ kHz, $f_s = 25$ MHz. ENOB = 6.3 over frequency band $36.62 \sim 232$ kHz. | 93 |

# List of Symbols and Abbreviations

| $\Delta\Sigma$ | Delta-sigma                             |

|----------------|-----------------------------------------|

| ADC            | Analog-to-digital converter             |

| ADPLL          | All-digital phase-locked loop           |

| BSIM           | Berkeley Short-channel IGFET Model      |

| CDR            | Clock and data recovery                 |

| CMOS           | Complementary Metal-Oxide Semiconductor |

| DAA            | Digitally assisted analog               |

| dB             | Decibel                                 |

| DCO            | Digitally controlled oscillator         |

| DFF            | D-type flip-flop                        |

| DNL            | Differential nonlinearity               |

| DR             | Dynamic range                           |

| DTC            | Digital-to-time converter               |

| ENOB           | Effective number of bits                |

| FFT            | Fast Fourier transform                  |

| FoM            | Figure-of-merit                         |

| GDC            | Gated delay cell                        |

| GDL            | Gated delay line                        |

| GRO   | Gated ring oscillator                               |

|-------|-----------------------------------------------------|

| Hz    | Hertz                                               |

| INL   | Integral nonlinearity                               |

| KHz   | KiloHertz                                           |

| LSB   | Least significant bit                               |

| MASH  | Multi-stage noise-shaping                           |

| MHz   | MegaHertz                                           |

| MIM   | Metal-insulator-metal                               |

| MSB   | Most significant bit                                |

| MUX   | Multiplexer                                         |

| NMOS  | n-type metal oxide semiconductor                    |

| NTF   | Noise transfer function                             |

| OPAMP | Operational amplifier                               |

| OSR   | Oversampling ratio                                  |

| OTA   | Operational transconductance amplifier              |

| PFD   | Phase frequency detector                            |

| PLL   | Phase-locked loop                                   |

| PMOS  | p-type metal oxide semiconductor                    |

| PSD   | Power spectral density                              |

| PVT   | process, voltage, and temperature                   |

| SNR   | Signal-to-noise ratio                               |

| SNDR  | Signal-to-noise-plus-distortion ratio               |

| SPICE | Simulation program with integrated circuit emphasis |

| SRO | Switched ring oscillator |

|-----|--------------------------|

| STF | Signal transfer function |

- *TDC* Time-to-digital converter

- *VCDU* Voltage controlled delay unit

- *VTO* Voltage controlled oscillator

- VTC Voltage-to-time converter

# Chapter 1

# Introduction of Time-Mode Signal Processing

The rapid scaling of CMOS technology has resulted in the sharp increase of time resolution and the continuous decrease of voltage headroom. As a result, time-mode circuits where information is represented by the time difference between two rising edges of pulses rather than the nodal voltages or branch currents of electric networks offer a viable and technology friendly means to combat scaling-induced difficulties encountered in design of mixed-mode systems. A time variable possesses a unique duality characteristic. Specifically, it is an analog signal as the continuous amplitude of the analog signal is represented by the difference between two rising edges of the pulses and it is also a digital signal as it only has two largely distinct values. The duality of time variables enables them to conduct analog signal processing in a digital environment. This unique characteristic is not possessed by neither analog nor digital variables. Since information to be processed by time-mode circuits is represented by the time difference of digital signals, these circuits are essentially digital systems and perform mixed-mode signal processing in digital domain without using powergreedy digital signal processing (DSP) blocks. This chapter examines the fundamentals of time-mode circuits. The intrinsic advantages of time-mode signal processing are examined in Section 1.1. The challenges encountered in time-mode signal processing are examined in Section 1.2. Section 1.3 provides an overview of time-to-digital converters (TDCs), the most important building block of time-mode systems. Section 1.4 presents the motivation of this dissertation. Primary contributions of this dissertation is in Section 1.5. Dissertation organization is detailed in Section 1.6. Finally, the chapter is concluded in Section 1.7.

### 1.1 Why Time-Mode?

The performance of analog circuit continues to fall behind the rapid scaling of CMOS technologies mainly optimized for digital circuits. Digitally assisted analog (DAA) circuits have been used to leverage digital circuits to improve the performance of analog circuits by adjusting the parameters of analog circuits so as to meet design specifications. The addition of DAA circuits, however, has a detrimental impact on the performance of analog circuits such as increasing the capacitance of the critical nodes through which high-frequency signals propagate. The intrinsic gate delay of digital circuits, on the other hand, has been the primary beneficiary of technology scaling. The improved switching characteristics of MOS transistors offer an excellent timing accuracy such that the time resolution of digital circuits has well surpassed the voltage resolution of analog circuits implemented in nano-scale CMOS technologies. Since time-mode circuits perform analog signal processing in the digital domain, not only the performance of these circuits scales well with technology, time-mode circuits also offer a number of attractive characteristics including full programmability, the ease of portability, and high-speed operation. As information to be processed by time-mode circuits is represented by the time difference between the occurrence of digital events, timemode circuits are essentially digital circuits. The detrimental effect of technology scaling on the performance of voltage-mode or current-mode analog signal processing vanishes in time-mode circuits. The full programmability of time-mode circuits, attribute to their digital realization, allows them to be deployed in a broad spectrum of applications where tunable characteristics are mandatory. In addition to programmability, portability is of a critical importance in order to minimize design turn-around time. The digital nature of time-mode circuits allows them to be migrated from one generation of technology to another with the minimum design time subsequently the lowest cost. As the intrinsic gate delay of digital circuits benefits the most from technology scaling, time-mode circuits are capable of carrying out rapid signal processing.

# 1.2 Challenges in Time-Mode Signal Processing

Although it is evident from the preceding investigation that time-mode signal processing possesses many desirable characteristics such as excellent scalability with technology, full programmability, the ease of portability, and high-speed operation, a number of challenges are yet to be overcome in order for time-mode circuits to be deployed in a broad range of applications. One of the most challenges in time-mode signal processing is the design of time-mode arithmetic units, especially time integrators. The integration of a variable in the voltage domain can be conveniently realized by representing the variable as a current and integrating the current onto a capacitor. Withholding or storing a time variable, however, is difficult due to the irretrievable nature of time. To implement time integrators, time-mode arithmetic units such as time adders and time registers are critically needed in time-mode signal processing.

### 1.3 An Overview of TDCs

TDCs that map a time variable to a digital code are the most important building block of time-mode systems. Although the applications of TDCs in high-energy physics for time-of-flight measurement in nuclear science dates back to 1970s [12], the deployment of TDCs in analog-to-digital converters (ADCs) [13, 14, 15, 8, 16] and all-digital phase-locked loops (ADPLLs) [17, 18] emerged recently. TDCs can be loosely classified into sampling TDCs and noise-shaping TDCs. A sampling TDC digitizes a time variable using either a high-frequency low-jitter reference clock and counting the number of the cycles of the clock within the duration of the time variable or a delay line to count the number of the stages of the delay line that the front edge of the time variable propagates before the arrival of the rear edge of the time variable directly. Sampling TDCs include delay-line TDCs, vernier delay-line TDCs, and pulse-shrinking TDCs, to name a few. A one-to-one mapping between a time input variable and a corresponding output digital code exists in sampling TDCs. The resolution of these TDCs is bound by quantization noise. Noise-shaping TDCs, on the other hand, suppress the quantization noise of TDCs using system-level techniques such as  $\Delta\Sigma$  operations that are capable of moving most of inband quantization noise to higher frequencies outside the signal band so that the displaced excessive quantization noise can be removed effectively using a decimation low-pass filter in a post-processing step, thereby achieving a large signal-to-noise ratio. As compared with sampling TDCs, noise-shaping TDCs offer the key advantage of a better signal-to-noise ratio (SNR). An example of noise-shaping TDCs is gated ring oscillator (GRO) TDCs that possess first-order noise-shaping obtained by freezing the residual phase of one sampling phase and ported it over to the next phase [13]. Although the in-band noise of noise-shaping TDCs is lower than quantization noise, one-to-one mapping between input time variables and their digital output codes is lost since the average of the output represents the input in  $\Delta\Sigma$ operations.

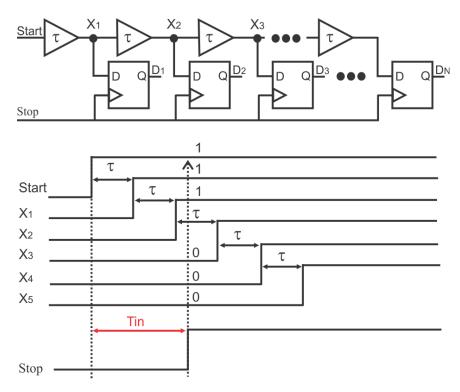

#### 1.3.1 Delay-line TDCs

Delay-line TDCs quantize a time variable using a delay line. The simplified schematic of delay line TDCs is shown in Fig 1.1. The signal, *Start*, is applied to the first delay cell and delayed through the buffer delay chains. Each buffer considered as a reference time difference ladder analogous to the reference resistor ladder in a flash ADC is comprised of two inverters which have the minimum propagation delay in a circuit usually. Each buffer chain is tapped to D input of each D-flip flop (DFF) which is used as a time comparator. The signal, *Stop*, is fed to the clock pins of all DFFs. Finally, the thermometric outputs of the DFFs are fed to a thermometer to binary decoder, not shown in the figure, generating digital codes. The conversion time of a TDC is the amount of the time that the TDC needs to complete the digitization of a time variable. The conversion time of the delay-line TDC is  $T_{in}+\tau_{DFF}$  where  $\tau_{DFF}$  is the clock-to-Q propagation delay of the DFFs. One of the main disadvantages of this architecture is that the time resolution is lower bound by per-stage propagation delay.

Figure 1.1: Delay-line TDCs [1], [2], [3].

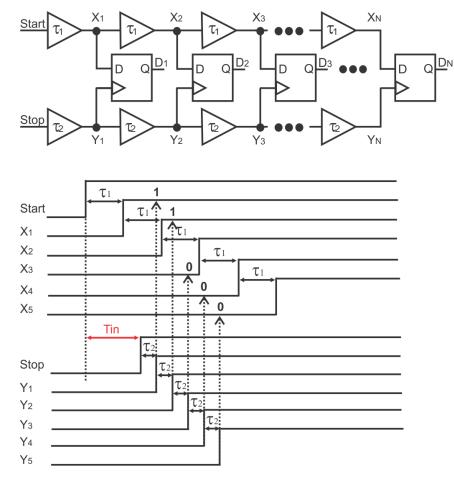

#### 1.3.2 Vernier delay-line TDCs

Vernier delay-line TDCs shown in Fig 1.2 are one of the older techniques that provide time resolution below per-stage delay. A vernier delay-line TDC adds an additional buffer delay chain having a different delay in the *Stop* path. In this case, the effective time resolution is the difference of the two propagation delays,  $\tau_1 - \tau_2$ , where  $\tau_1$  and  $\tau_2$  represent the propagation delay of the buffers in *Start* path and the one of the buffer in *Stop* path, respectively. Since  $\tau_1$  is designed to have larger delay then  $\tau_2$ , *Stop* signal will catch up *Start* signal even though it is launched late. Because the difference between two delay lines is the effective time resolution, vernier delay-line TDC can have a much higher resolution than that of the basic delay-line TDCs shown in Fig 1.1. The time instant at which a catch-up takes place is determined from  $T_{catch} = N\tau_1 = N\tau_2 + T_{in}$ , where N is the number of the stages that *Stop* signal propagates though before the catch-up takes place. For a given  $T_{in}$ , we have  $N = \frac{T_{in}}{(\tau_1 - \tau_2)}$ . Since  $\tau_1 - \tau_2$  is very small,  $T_{in}$  must be small in order to have a manageable value of N. The dynamic range of vernier delay line TDCs is upper-bound by  $N(\tau_1 - \tau_2)$  and lower-bound by  $\tau_1 - \tau_2$  theoretically. Improving time resolution is one of the biggest advantages of this architecture. Long conversion time is one of the disadvantages since the final thermometer output codes will be generated after *Stop* catches up *Start*. To increase a dynamic range, it requires many stages at the cost of increased silicon and power consumption.

Figure 1.2: Vernier delay-line TDCs [4].

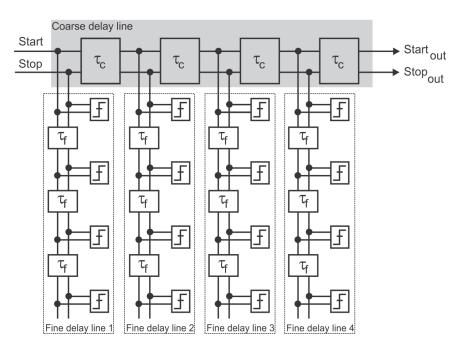

#### 1.3.3 Hierarchical vernier delay-line TDCs

The conversion time of vernier delay-line TDCs can be reduced while preserving the resolution by using the 2-level hierarchical configuration shown in Fig.1.3[5]. Hierarchical

vernier delay-line TDC consists of a coarse vernier delay-line TDC with a total of N stages and N fine vernier delay-line TDCs. If  $\tau_c$  and  $\tau_f$  shown in Fig.1.3 represent the propagation delay of the buffers in coarse delay-line and the one of the buffer in fine delay-line, respectively, the conversion time of the coarse vernier delay-lines is N $\tau_c$ . Since the digitization undertaken by the fine vernier delay-line TDCs is carried out in parallel with that by the coarse vernier delay-line TDC, the total conversion time of the hierarchical vernier delay-line TDC is the same as that of the coarse vernier delay-lines, i.e., N $\tau_c$ . If we assume that  $\tau_c$  can be resolved by the fine vernier delay-line TDCs with a total of M stages,  $\tau_c = M\tau_f$  will hold. It should be noted that the price paid for reducing conversion time is the increased silicon area.

Figure 1.3: Hierarchical vernier delay-line TDC [5].

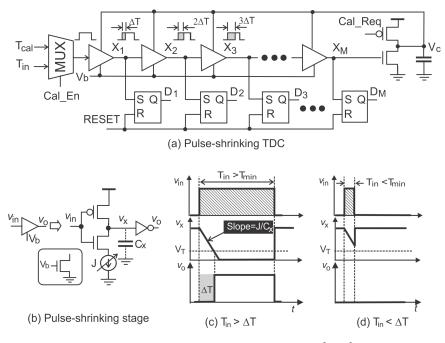

#### 1.3.4 Pulse-shrinking TDCs

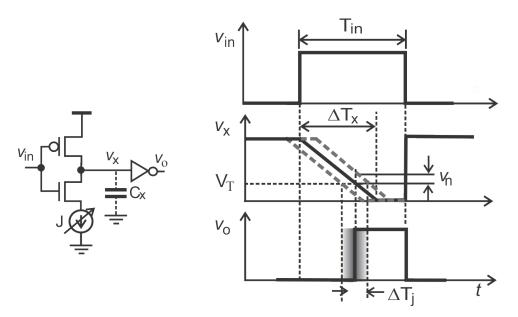

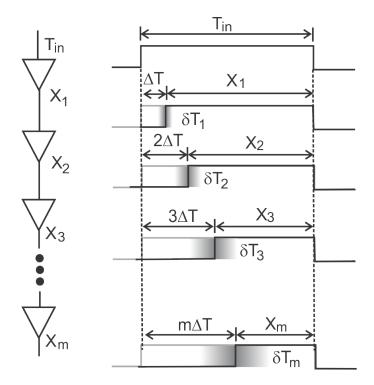

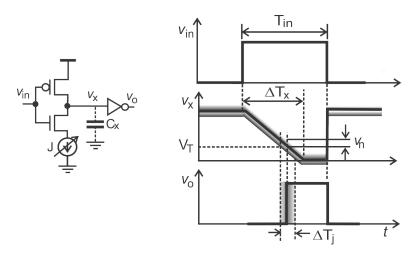

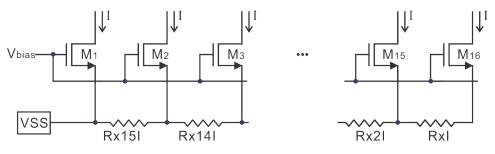

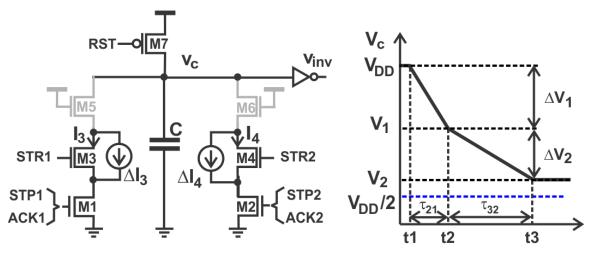

Resolution finer than per-stage delay can also be achieved using pulse-shrinking TDCs shown in Fig.1.4 [6, 7]. To set the resolution,  $V_c$  is set to  $V_{DD}$  and per-stage shrinkage is at the minimum.  $T_{cal}$  is then asserted. The width of  $T_{cal}$  is reduced stage-wise uniformly by  $\Delta T$ .  $\Delta T$  is adjusted by  $V_c$  adjusting the discharge current J of the pulse-shrinking stages until the pulse at the output of the last stage just disappears ( $D_M = 0$ ). Once this occurs, the resolution of the TDC becomes  $\Delta T = T_{cal}/M$ . M is the number of the pulse-shrinking stages. Clearly if M is sufficiently large,  $T_{cal}/M$  can be made arbitrarily small. By adjusting time resolution, calibration is also achieved. Increasing the number of pulse-shrinking stages, though improving resolution, is at the cost of increased silicon and power consumption. The detrimental effect of mismatches between pulse-shrinking stages deteriorates with the increase in the number of pulse-shrinking stages. The conversion range of the pulse-shrinking TDC is given by  $\Delta T \leq T_{in} \leq N\Delta T$  or  $\Delta T \leq T_{in} \leq T_{cal}$ . Although a large N is preferred from a better resolution point of view, the effect of jitter and mismatch intensifies with the increase in the number of pulse-shrinking TDCs in a similar way as that in delay line TDCs.

Figure 1.4: Pulse-shrinking TDCs [6, 7].

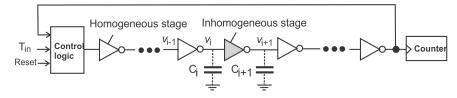

To improve the resolution of pulse-shrinking TDCs without employing a large number of pulse-shrinking stages, cyclic pulse-shrinking TDCs were proposed, as shown in Fig.1.5 [19]. A cyclic pulse-shrinking TDC consists of a delay line with stages 1, 2, ..., i - 1, i + 1, ...having the same dimension (homogeneous stages) and stage *i* having different dimensions (inhomogeneous stage), a control logic block, and a counter. The control logic is designed in such a way that when  $T_{in}$  is applied to the loop, the pulse will continue to circulate the loop until its width reduces to zero. The inhomogeneity of *i*th delay stage gives rise to a reduction in the width of the propagating pulse every time it completes a round trip. A counter is used to record the number of the round trips that the pulse completes before it diminishes. Since the number of the round trips that the pulse completes is directly proportional to  $T_{in}$ . the content of the counter when the pulse vanishes yields the digital representation of  $T_{in}$ . Cyclic pulse-shrinking TDCs exhibit a perfect linearity as the amount of cycle-to-cycle pulse shrinkage remains unchanged. In addition, they do not need to be calibrated periodically as the amount of pulse shrinkage is only set by the physical dimensions of the delay stages. One drawback of cyclic pulse-shrinking delay line TDCs is that an input pulse can be applied only after the previous one has vanished completely, resulting in a long conversion time.

Figure 1.5: Cyclic pulse-shrinking TDCs.

#### 1.3.5 Gated ring oscillator TDCs

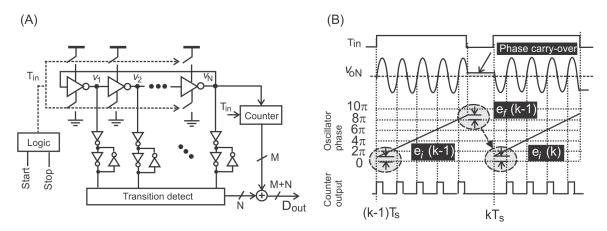

GRO TDCs are one of popular noise-shaping TDCs. The TDC shown in Fig.1.6 (A) digitises time input  $T_{in}$  generated from two input signal, *Start* and *Stop*, by using a gated rign oscillator (GRO) [8]. The operation of GRO is depicted as follows: A GRO is similar to an ring oscillator (RO) except its delay stage has two additional transistors compared to the normal inverter. One is transistor between PMOS transistor and the positive power supply and the other is between NMOS transistor and the negative power supply. They act

like switches. Oscillation is enabled only when  $T_{in} = 1$  and disabled when  $T_{in} = 0$ . The beauty of this structure is that when  $T_{in} = 0$ , the switch transistors are open. Oscillation is suspended and the phase of the oscillator remains unchanged until next  $T_{in}$ . The residue phase is transferred to the next  $T_{in}$ , i.e.  $e_i[k] = e_f[k-1]$ , where  $e_f[k]$  is a residue phase information in  $kT_s$ , and  $e_f[k-1]$  is a residue phase information in  $(k-1)T_s$ . Fig.1.6 (B) shows a waveform based on the basic operation of GRO. The quantization error can be calculated for a given measurement interval between  $kT_s$  and  $(k-1)T_s$ ,  $T_{error}$  is given by

$$T_{error}[k] = e_f[k] - e_f[k-1].$$

(1.1)

The first-order noise shaping of quantization noise is evident in (1.1). In addition to the firstorder noise shaping of quantization noise, the effect of delay element mismatch is also firstorder shaped. The randomness of the initial phase of each sampling period also effectively scrambles quantization error across different sampling periods so that it can be first-order shaped. The resolution of GRO TDCs is lower bound by the oscillation frequency of the ring oscillator of the TDCs, which is inversely proportional to the number of the delay stages of the oscillator. The quantization error of GRO TDCs given by  $\pi/N$  where N is the number of the stages of the oscillator is also inversely proportional to the number of the delay stages of the oscillator. The larger the number of the stages of the oscillator, the lower the quantization noise and the worse the resolution.

GRO TDCs suffer from missing count caused by the early reset of the counter at the end of  $T_{in}$  while the edge-detection and transition detection are still in action [20]. They also exhibit dead-zone behaviour if the period of the gating signal  $T_{in}$  is in the vicinity of an integer multiple of the period of the oscillator [21].

#### 1.3.6 $\Delta \Sigma$ TDCs

It is well understood that  $\Delta\Sigma$  operation offers noise-shaping. However, the realization of  $\Delta\Sigma$  configurations in time-mode is rather difficult because of the lack of time-mode integra-

Figure 1.6: GRO TDCs [8]. (A) Block diagram. (B) Waveform.

tors needed to achieve high-order  $\Delta\Sigma$  modulators. As a result,  $\Delta\Sigma$  TDCs are often realized using a partial time-mode partial voltage-mode approach, more specifically, integrators using OTAs are voltage-mode while quantizers are voltage-controlled oscillator (VCO)-quantizers. Taillefer and Roberts proposed a ring oscillator voltage-to-time integrator consisting of two voltage-controlled delay units [22]. Implementing high-order integrators using this approach is rather difficult.

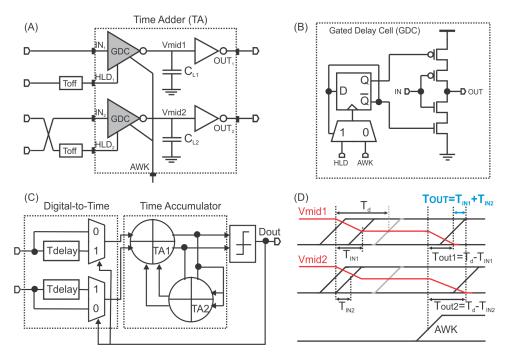

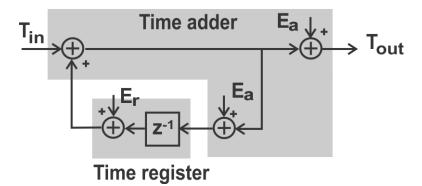

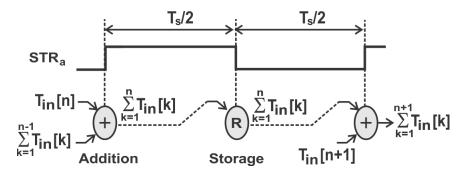

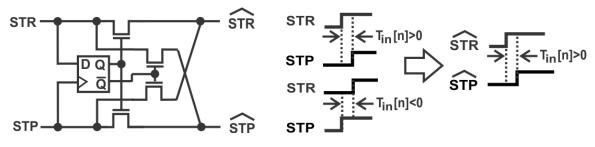

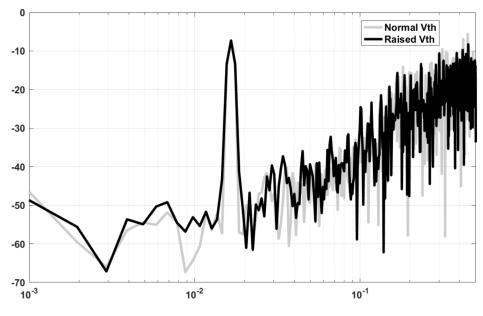

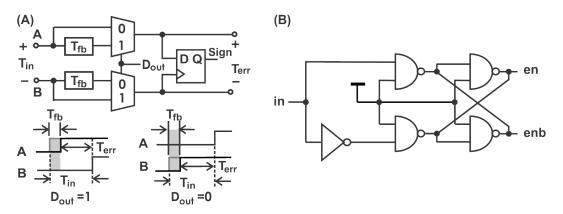

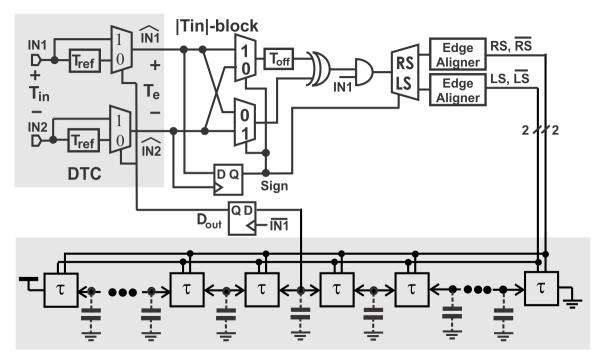

Fig.1.7(C) shows  $\Delta\Sigma$  TDC using the time accumulator in [10]. Time accumulator is evolved from the time adder proposed in [9] shown in Fig.1.7 (A). The core of time accumulator is a time register using gated-delay cell (GDC) shown in Fig.1.7 (B) that holds an input time variable and releases the held time variable on the arrival of a triggering a signal, AWK. Time adder shown in Fig.1.7 (A) consists of two time-registers. The operation of the time register can be briefly depicted as follows: assume  $C_{L1}$  is fully charged initially, when  $IN_1$  arrives,  $V_{mid1}$  starts to drop. When  $HLD_1$  arrives, the gated delay cell enters its hold stage and  $V_{mid1}$  remains unchanged. When AWK is asserted, the gated delay cell is reactivated and  $V_{mid1}$  starts to drop again. If there is another time register whose HLD input and AWK are connected, the output of this time register can be a reference. Therefore, if we compare the time difference between two time registers' outputs, it should be the same as the time input variable. The preceding time register can be utilized to construct a time adder shown in Fig.1.7 (A). It should be noted that the second gated delay cell has a reversing the order of the input data because of  $T_{OUT1} = T_d T_{in1}$  and  $T_{OUT2} = T_d T_{in2}$  leading to

**Figure 1.7:** (A) Time adder [9]. (B) Gated delay cell [9]. (C)  $\Delta\Sigma$  TDC [10]. (D) Waveform of time adder.

$T_{OUT} = T_{OUT1} - T_{OUT2} = T_{in1} - T_{in2}$  instead of  $T_{in1} + T_{in2}$ . To deal with this, the order of the input is reversed as shown in Fig.1.7(A). Fig.1.7(D) shows a timing diagram of the time adder.  $T_d$ is a normal propagation delay of the GDC. The time accumulator consists of two back-toback connected time adders. Fig.1.7(C) shows the schematic of the time accumulator in [10]. In the time accumulator, one of time adders functions like a time register since the inputs of the second time adder are tied together such that  $T_{in2}$  becomes 0. Therefore,  $T_{in1} + 0 =$  $T_{in1}$ , which is identical to  $z^{-1}$  function in discrete-time domain. The operation of the time adder and time register performs  $y[n] = \sum_{k=0}^{n} T_{in}[k]$ .

## 1.4 Motivation

TDCs with a sub-per-stage-delay resolution and a short conversion time are critical to a number of applications. For applications such as  $\Delta\Sigma$  modulators, conversion time directly affects the oversampling ratio subsequently the performance of the modulators. Conversion time is also of a great importance for phase-locked loops (PLLs) with a TDC phase detector. This is because conversion time in this case directly affects the speed of the TDC phase detector subsequently the loop dynamics of the PLLs. Also resolution affects the phase noise of PLLs. Vernier delay-line TDCs and hierarchical vernier delay-line TDCs are not attractive for these applications due to their long conversion time and high power and silicon consumption. Pulse-shrinking that also offer sub-per-stage delay are good candidates for these application. To improve resolution, a large number of pulse-shrinking stages are needed. Reducing the number of pulse-shrinking stages is highly desirable in minimizing nonlinearities arising from stage mismatch. To reduce the number of stages without sacrificing resolution, a two-step architecture is explored in this dissertation. A drawback of the two-step architecture is long conversion time since it needs to extract the residue information then apply to the fine stage. To combat this, a time-interleaved pulse-shrinking TDC is proposed in this dissertation.

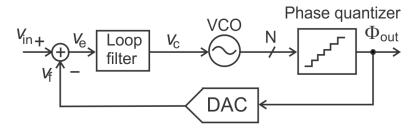

$\Delta\Sigma$  modulation is an effective means to improve time resolution below per-stage delay.  $\Delta\Sigma$  TDCs can be used along with a voltage-to-time converter to perform analog-to-digital conversion. Currently analog-to-digital conversion utilizing time-mode techniques is most realized using a voltage-controlled oscillator (VCO)-based quantizers. VCO-based quantizers offer a number of attractive intrinsic advantages including built-in first-order noise-shaping, inherent multi-bit quantization with a good linearity, fast quantization subsequently a large over-sampling ratio, and full scalability with technology. To have a better signal-to-noiseplus-distortion ratio (SNDR), a high-order OTAs based voltage-mode integrator is required in the forward path in order to have an adequate loop gain to suppress the effect of the nonlinearities and quantization noise as shown in Fig.1.8. These ADCs are therefore not all-digital. As a result, their performance does not scale naturally with technology. As the performance of voltage-mode integrators scales poorly with technology, time integrators with a large in-band gain are critically needed for all-digital  $\Delta\Sigma$  TDC.

Efforts have been made to replace OTA filters with time-mode filters such that entire modulators can be realized digitally. Taillefer and Roberts proposed a ring oscillator voltageto-time integrator consisting of two voltage-controlled delay units (VCDUs) and a static inverter [22]. Implementing high-order integrators using this approach is rather difficult.

Figure 1.8:  $\Delta\Sigma$  TDCs [6, 7].

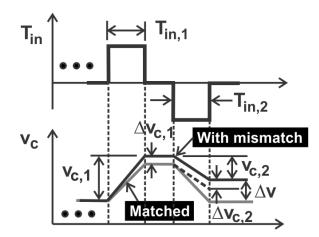

The time accumulator proposed by Hong *et al.* consists of two back-to-back connected time adders realized using four GDCs [10]. The core of the time accumulator is a time register proposed capable of storing a time variable and reading out the stored variable [9]. Kim *et al.* showed that a gated delay line (GDL) functions as a time register with the gating signal consisting of the time variable to be stored and a trigger signal [23, 24]. A time adder is realized using two GDCs, each has a large capacitor. The need for two GDCs, however, increases power and silicon consumption. To minimize power and silicon consumption, a new time integrator is proposed consisting of two new time adders using only one capacitor in each time adder. In this dissertation, two time integrators realized using digital circuits are proposed and are used to implement all-digital  $\Delta\Sigma$  modulators.

### **1.5** Contributions

1) A silicon and power-efficient two-step pulse-shrinking TDC was proposed. The TDC consists of a coarse TDC and a fine TDC with an efficient residual time extraction technique. The proposed TDC in [25] and [26] allows rapid digitization of a time input with the minimum silicon and power consumption without sacrificing time resolution.

2) A time-interleaved pulse-shrinking TDC was proposed to overcome the conversion time inefficiency of the two-step pulse-shrinking TDC also developed in this study. Similar to the preceding two-step pulse-shrinking TDC, the time-interleaved TDC in [27] and [28] is composed of a coarse TDC but a pair of fine TDCs that operate in a time-interleaved manner such that time synchronization logic and associated time latency existing in the preceding two-step pulse-shrinking TDC are removed. 3) A new all-digital time integrator consisting of a cascode time adder with a raised threshold voltage and a time register is proposed. The developed time integrator is utilized in the development of an all-digital 1-1 MASH  $\Delta\Sigma$  modulator to realized an all-digital secondorder  $\Delta\Sigma$  modulator. To the best of the knowledge of the author, this is the first all-digital 1-1 MASH  $\Delta\Sigma$  modulator ever reported in [29], [30] and [31].

4) A novel power efficient time integrator utilizing a bi-directional gated delay line was proposed. The open-loop characteristics of the proposed time integrator enables the rapid integration of time variables without stability constraints and power consumption penalty. The time integrator is utilized in the development of an all-digital first-order  $\Delta\Sigma$  modulator in [32]. The large loop bandwidth of the modulator benefited from the rapid integration capability of the time integrator enables the modulator to digitize large bandwidth signals.

### **1.6** Dissertation Organization

This dissertation comprises of 5 chapters. Chapter 2 presents a time-interleaved pulse-shrinking TDC consisting of a 16-stage coarse pulse-shrinking TDC and a pair of 16-stage fine pulse-shrinking TDCs to overcome the conversion time issue present in two-step pulse-shrinking TDC.

Chapter 3 deals with a 1-1 MASH  $\Delta\Sigma$  TDC by using time integrator. It shows a differential cascode time integrator. The differential cascode time integrator suppresses second-order harmonic tone present in single-ended time integrators. The effect of the nonidealities of the TDC, in particular, the delay uncertainty of the digital-to-time converter functioning as a time summer and jitter due to device current noise and current mismatch between the discharge paths of the time adder, are examined in detail.