# PERFORMANCE AND ENERGY OPTIMIZATION OF HETEROGENEOUS CPU-GPU SYSTEMS FOR EMBEDDED APPLICATIONS

By

Abdullah Siddiqui

Bachelor of Engineering

Ryerson University, 2015

A thesis

presented to Ryerson University

in partial fulfilment of the

requirements for the degree of

Master of Applied Science

in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2018

© Abdullah Siddiqui 2018

## **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

## Performance and Energy Optimization of Heterogeneous CPU-GPU Systems for Embedded applications

Abdullah Siddiqui

Master of Applied Science

Electrical and Computer Engineering Ryerson University

2018

#### Abstract

One of the most critical steps of embedded systems design is Hardware-Software partitioning. It is characterized by distributing the components of an application between hardware and software such that the user defined system constraints are satisfied. Heterogeneous computing platforms consisting of CPUs and GPUs have tremendous potential for enhancing the performance of embedded applications. The challenge of application partitioning for CPU-GPU mapping is much greater on such platforms due to their unique and diverse characteristics. In this thesis, an optimization algorithm is devised and presented for partitioning and mapping computational tasks on CPU-GPU platforms while keeping a check on the power consumption. Our methodology also uses parallelism in applications and their tasks by utilizing the architectural capabilities of the GPU. The optimization algorithm was tested with a MJPEG decoder, several benchmarks and synthetic graphs.

#### Acknowledgment

I would like to first of all thank the Almighty Allah for giving me the inspiration and the perseverance to carry out the work detailed in this thesis document.

I am very grateful to my supervisor, Dr. Gul Khan, for giving me the opportunity to work for him. I was initially fascinated with the subject of embedded systems but thanks to him, that initial fascination has grown into a deep passion for this subject. I always had his encouragement and support throughout the duration of my master's studies and could not have asked for a better supervisor than him to oversee my research efforts. My friend and colleague, Muhammad Obaidullah, generously shared his knowledge of object-oriented programming and design with me. It was invaluable for my research and I shall always be grateful to him for that. I am grateful to Mr. Jason Naughton for providing timely help with the CMC system and uncomplainingly resetting it each time after it crashed. I also want to thank Mr. Jochem Bonarius for giving me feedback for the implementation of the MJPEG decoder. I am also thankful to Ryerson University and the Canadian Microsystems Corporation (CMC) for providing funding and equipment for my research.

Last but not the least, my mother, father and brother Rashed have been a constant source of support and encouragement for me throughout my life. They always pushed me to do my best and were consoling and supportive during my periods of frustration and difficulties. None of my accomplishments would have been possible without the unrelenting dedication and sacrifices of my parents since my childhood up to now. I dedicate this thesis to them.

iv

## Table of Contents

| Aut  | hor's Declarationii                                                                         |

|------|---------------------------------------------------------------------------------------------|

| Abs  | stractiii                                                                                   |

| Ack  | xnowledgementiv                                                                             |

| List | t of Figuresvii                                                                             |

| List | t of Tablesx                                                                                |

| 1 IN | NTRODUCTION1                                                                                |

| 1    | .1 Motivation1                                                                              |

| 1    | .2 Problem Definition                                                                       |

| 1    | .3 Thesis Organization                                                                      |

|      | VERVIEW OF HARDWARE/SOFTWARE CO-DESIGN AND CPU-GPU<br>MPUTING5                              |

|      | Hardware/Software Co-Design                                                                 |

|      | 2.1.1 Emergence of Hardware/Software Co-design as a field of research                       |

|      | 2.1.2 Early work in Hardware/Software Co-design                                             |

|      | 2.1.3 Traditional System-level Design flow                                                  |

|      | 2.1.4 Models of Representation                                                              |

|      | 2.1.5 Limitations of traditional design flow and the need for alternate design strategies10 |

| 2.2  | Design Space Exploration strategies and techniques12                                        |

|      | 2.2.1 Genetic Algorithm                                                                     |

|      | 2.2.2 Simulated Annealing                                                                   |

|      | 2.2.3 Particle Swarm Optimization                                                           |

| 2.3  | Co-simulation and Co-verification16                                                         |

| 2.4  | Heterogeneous Computing-CPU-GPU platforms17                                                 |

|      | 2.4.1 Energy Efficiency and Resource Utilization                                            |

|      | 2.4.2 Profiling Techniques for GPUs                                                         |

|      | 2.4.3 Task-Mapping for CPU-GPU platforms                                                    |

| 2.5  | GPGPU Programming25                                                                         |

|      | 2.5.1 Introduction to the CUDA architecture                                                 |

|      | 2.5.2 CUDA's Programming Model                                                              |

|            | 2.5.3 OpenCL Application Programming Interface            | 27   |  |  |  |

|------------|-----------------------------------------------------------|------|--|--|--|

|            | YSTEM-LEVEL OPTIMIZATION METHODOLOGY FOR HETEROGENEOUS    |      |  |  |  |

| PLA        | ATFORMS                                                   | 31   |  |  |  |

| 3.1        | Introduction                                              | 31   |  |  |  |

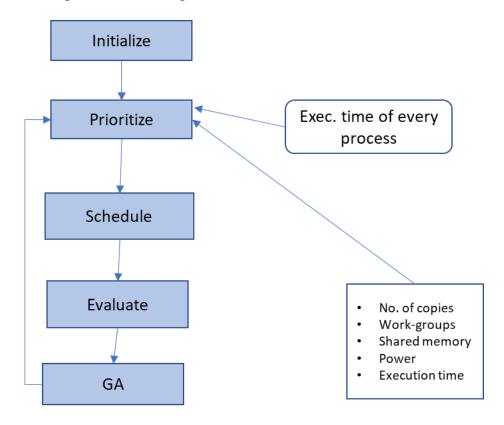

| 3.2        | General Design Flow                                       | 32   |  |  |  |

|            | 3.2.1 Input Specification                                 | 33   |  |  |  |

|            | 3.2.2 Creating a Population                               | 35   |  |  |  |

|            | 3.2.3 Priority Assignment                                 | 38   |  |  |  |

|            | 3.2.4 Scheduling of Processes and Communication Events    | . 39 |  |  |  |

|            | 3.2.5 Evaluation of solutions                             | 44   |  |  |  |

|            | 3.2.6 Producing new solutions using the Genetic Algorithm | 46   |  |  |  |

| 3.3        | HW/SW Partitioning methodology for CPU-GPU platforms      | 54   |  |  |  |

|            | 3.3.1 Task and Data Parallelism                           | 55   |  |  |  |

|            | 3.3.2 Input Specification                                 | 58   |  |  |  |

|            | 3.3.3 System constraints                                  | 60   |  |  |  |

|            | 3.3.4 Characteristics of solutions and population         | 61   |  |  |  |

|            | 3.3.5 Priority Assignment                                 | 62   |  |  |  |

|            | 3.3.6 Scheduling                                          | 62   |  |  |  |

|            | 3.3.7 Solution evaluation                                 | 63   |  |  |  |

|            | 3.3.8 Partitioning GA for CPU-GPU platforms               | 64   |  |  |  |

| 3.4        | Parameter tuning for Performance Improvement              | 66   |  |  |  |

|            | 3.4.1 Introduction                                        | 66   |  |  |  |

|            | 3.4.2 Proposed parameter tuning strategy                  | 66   |  |  |  |

| <b>4 E</b> | XPERIMENT AND RESULTS                                     | 71   |  |  |  |

| 4.1        | Target Architecture-Details                               | 71   |  |  |  |

| 4.2        | Synthetic Graphs                                          | 72   |  |  |  |

|            | 4.2.1 Synthetic graph with 10 nodes                       | 72   |  |  |  |

|            | 4.2.2 Synthetic graph with 30 nodes                       | 78   |  |  |  |

| 4.3        | Benchmarks for Heterogeneous Computing                    | 88   |  |  |  |

|            | 4.3.1 Implementation and Results                          |      |  |  |  |

| 4.4        |                                                           |      |  |  |  |

| 5 C        | ONCLUSION AND FUTURE WORK                                 |      |  |  |  |

| RI         | REFERENCES                                                |      |  |  |  |

## List of Figures

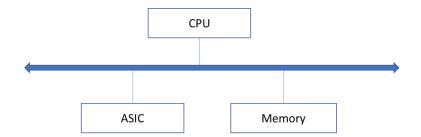

| 2.1 Target architecture for Hardware/Software Partitioning       | 6  |

|------------------------------------------------------------------|----|

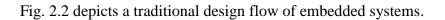

| 2.2 Typical Design Flow                                          | 7  |

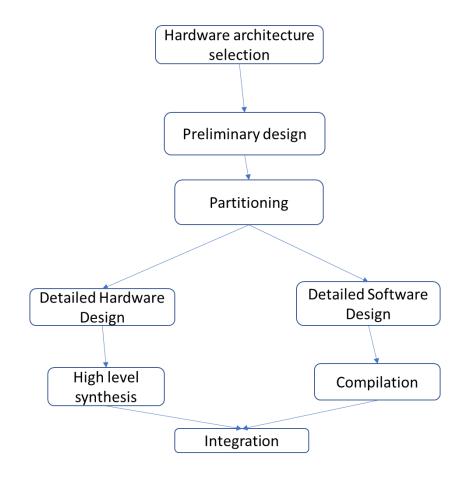

| 2.3 A typical data flow graph.                                   | 9  |

| 2.4 A simple petri-net.                                          | 10 |

| 2.5 A simple FSM                                                 | 10 |

| 2.6 Fused GPU+CPU                                                | 17 |

| 2.7 System overview of the CPU-GPU architecture                  |    |

| 2.8 OpenCL platform and execution model                          |    |

| 2.9 OpenCL memory model                                          |    |

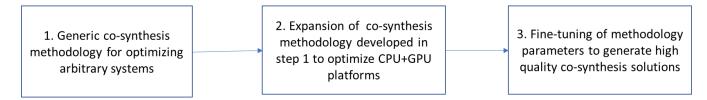

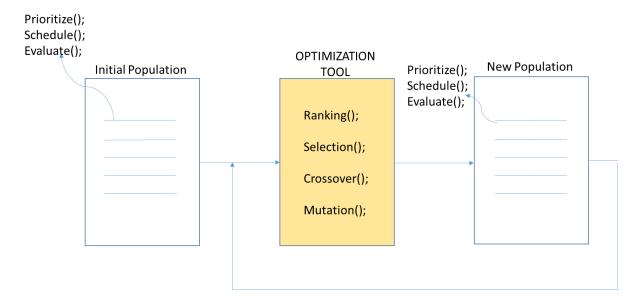

| 3.1 3 stages of the proposed co-synthesis methodology            | 31 |

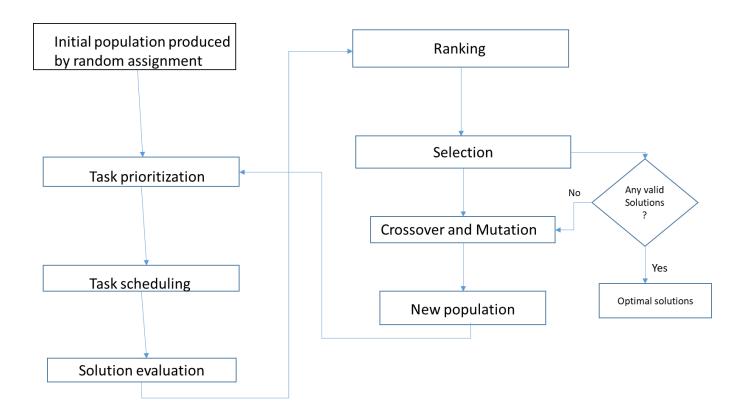

| 3.2 Co-synthesis methodology                                     |    |

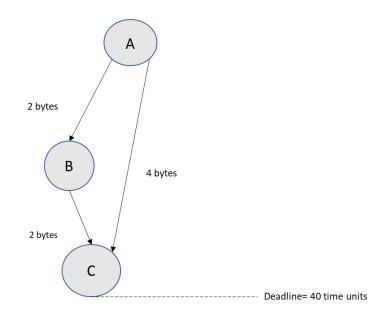

| 3.3 An example of a typical DAG. Node C is the sink node         |    |

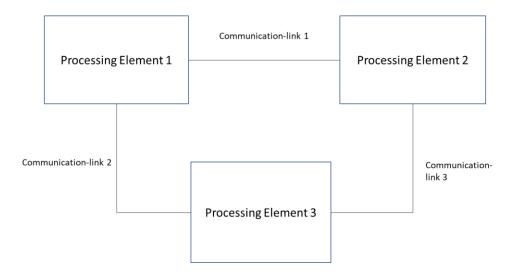

| 3.4 Example of a target architecture                             |    |

| 3.5 Process assignment array                                     |    |

| 3.6 Edge assignment array                                        |    |

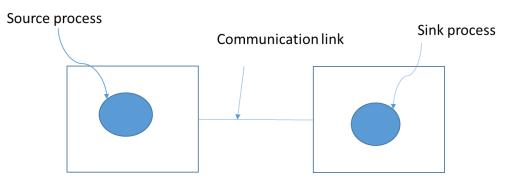

| 3.7 Source and sink processes on different PEs                   |    |

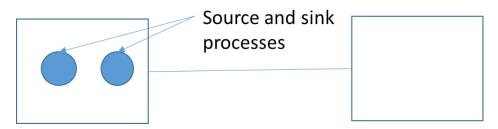

| 3.8 Source and sink processes on the same PE                     |    |

| 3.9 Pseudo-code for Edge assignment array                        |    |

| 3.10 Pseudo-code for recursive deadline and priority assignments |    |

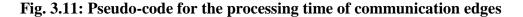

| 3.11 Pseudo-code for the processing time of communication edges  | 40 |

| 3.12 Pseudo-code for scheduling of outgoing edges                | 41 |

| 3.13 Pseudo-code for scheduling a single process                 | 42 |

| 3.14 Pseudo-code for scheduling all the processes                | 43 |

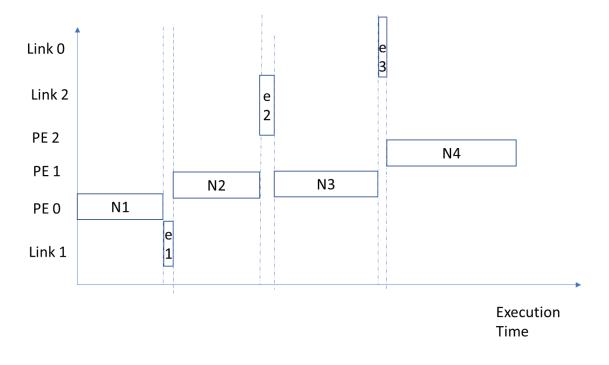

| 3.15 Visual representation of scheduled nodes and edges          | 44 |

| 3.16 Pseudo-code for obtaining deadline violation                | 45 |

| 3.17 Pseudo-code for calculating a solution's final score        | 46 |

| 3.18 Pseudo-code for sorting the solutions in a population       | 47 |

| 3.19 Pseudo-code of selection strategy                           | 49 |

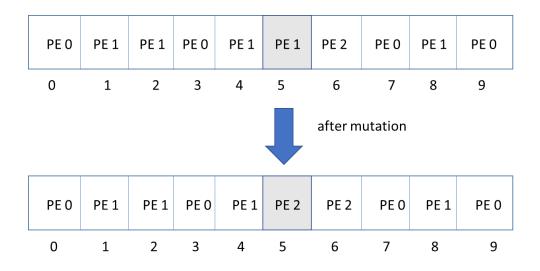

| 3.20 Process 5 is now on PE 2 after mutation                     | 50 |

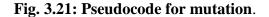

| 3.21 Pseudo-code for mutation                                    | 50 |

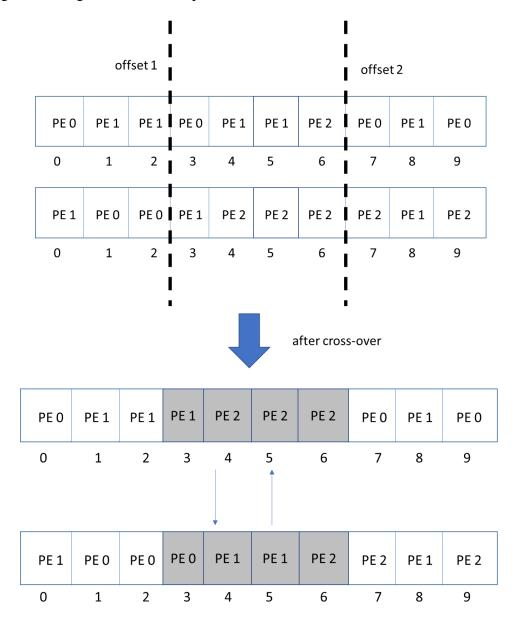

| 3.22 Illustration of crossover for solutions                                                           | 51 |

|--------------------------------------------------------------------------------------------------------|----|

| 3.23 Pseudo-code for crossover                                                                         | 53 |

| 3.24 Newly evolved solutions are prioritized, scheduled and evaluated prior to being pass<br>to the GA |    |

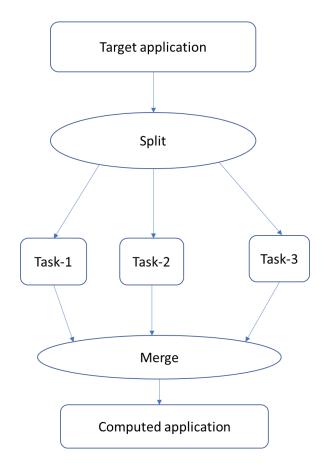

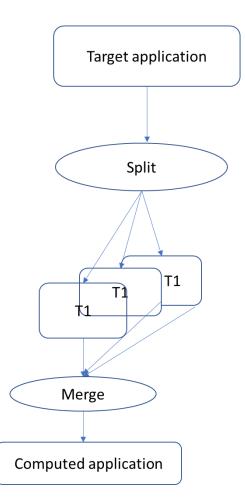

| 3.25 Task parallel computing                                                                           | 56 |

| 3.26 Data-parallel computing                                                                           | 57 |

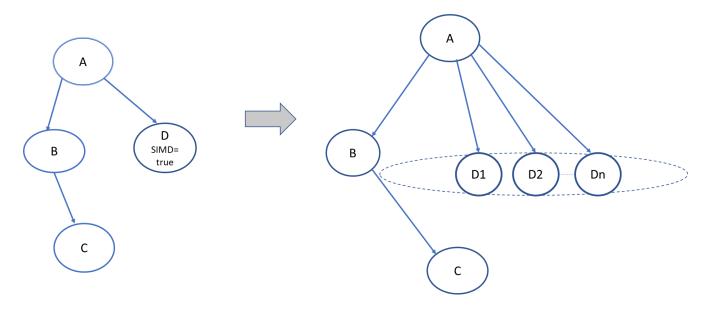

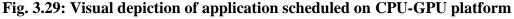

| 3.27 SIMD task is split into a number of concurrent copies for offloading to the GPU                   | 59 |

| 3.28 Pseudo-code for CPU-GPU based process assignment                                                  | 62 |

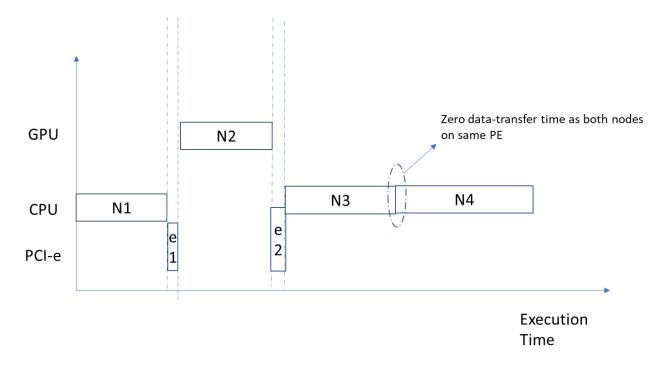

| 3.29 Visual depiction of application scheduled on CPU-GPU platform                                     | 63 |

| 3.30 Pseudo-code for calculating energy consumption                                                    | 63 |

| 3.31 Pseudo-code for rectifying PE assignment                                                          | 65 |

| 3.32 Codesign methodology for CPU-GPU platforms                                                        | 65 |

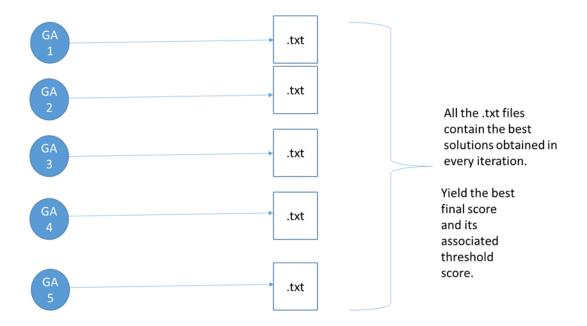

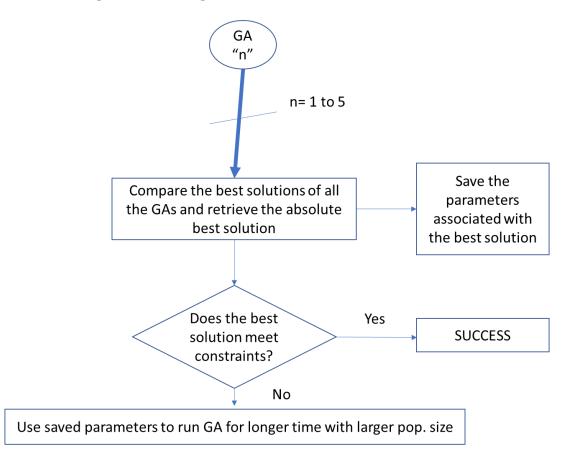

| 3.33 Writing the best scores of each GA to text files                                                  | 69 |

| 3.34 Flowchart of our parameter tuning strategy                                                        | 69 |

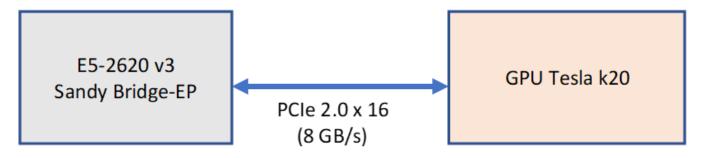

| 4.1 Target architecture                                                                                | 71 |

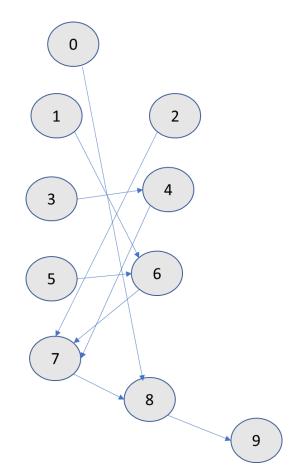

| 4.2 Synthetic graph with 10 nodes. Deadline= 300 units                                                 | 72 |

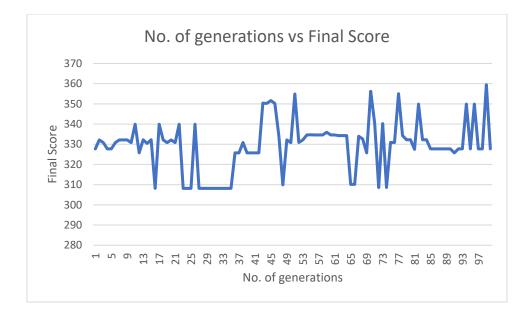

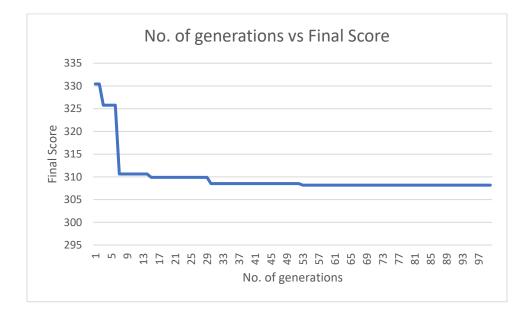

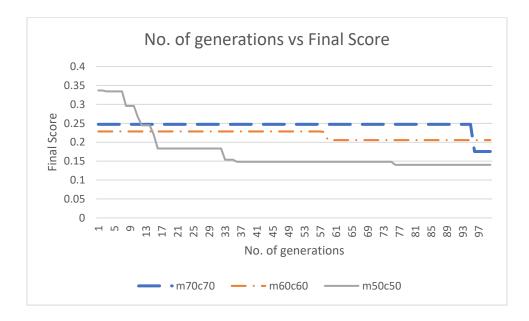

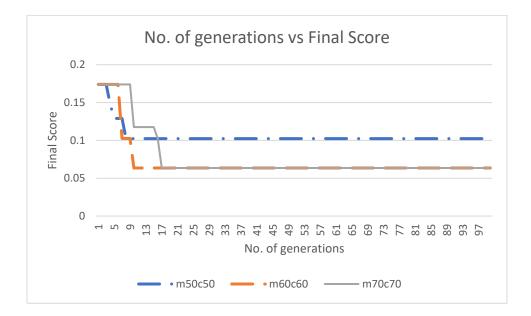

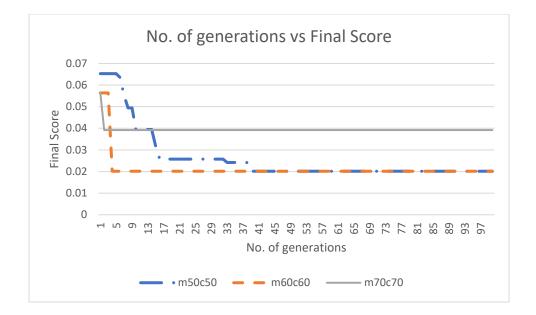

| 4.3 Variations in the quality of the absolute best solutions                                           | 74 |

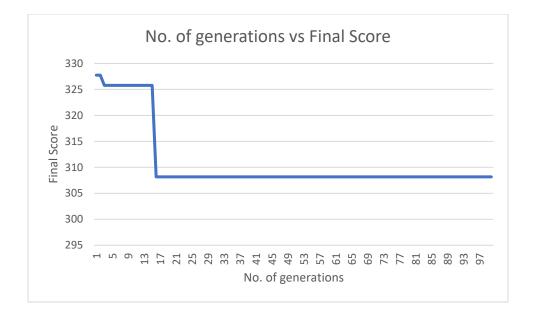

| 4.4 Absolute best solution was retained after every iteration                                          | 75 |

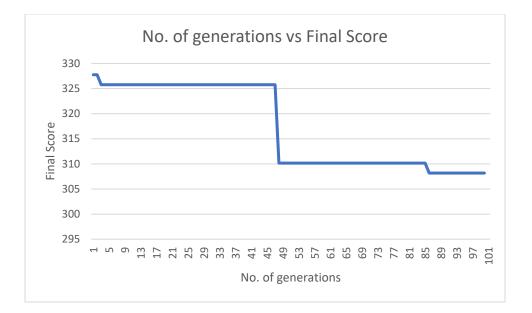

| 4.5 The best solutions when the target score is made stricter                                          | 76 |

| 4.6 Variations in the quality of best solutions for a population size of 10 and a target scor of 450   |    |

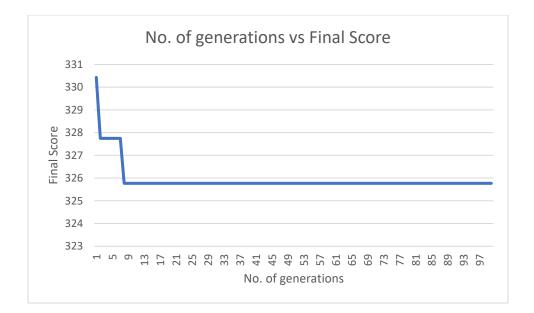

| 4.7 Best solutions in every iteration for a population size of 10 and a target score of 370            | 77 |

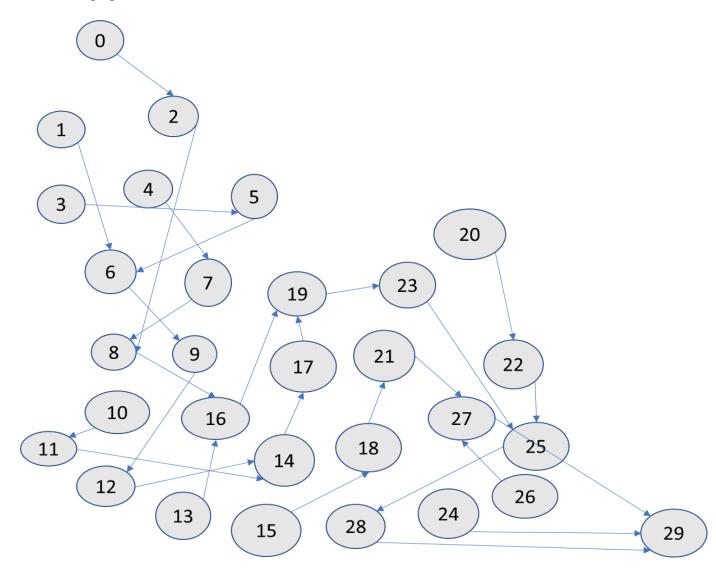

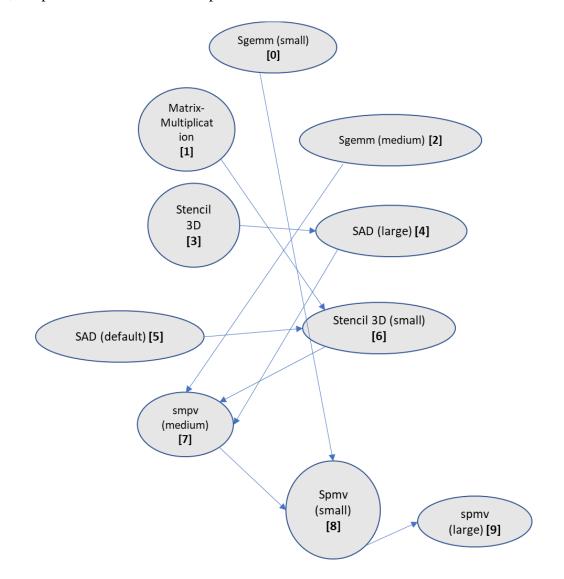

| 4.8 30-node task graph. Deadline= 480 seconds                                                          | 79 |

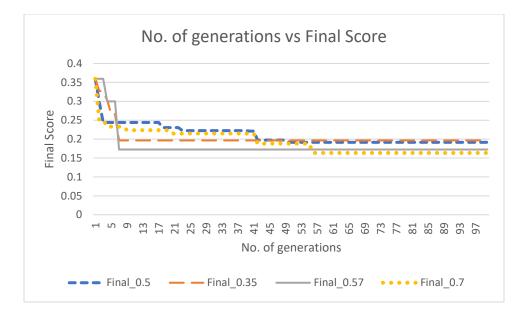

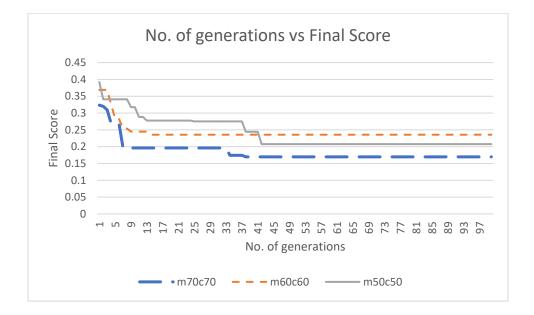

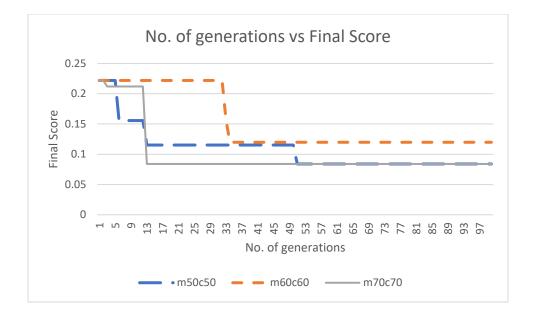

| 4.9 Energy- 33%, Exec. time- 34% and Deadline violation- 33%                                           | 82 |

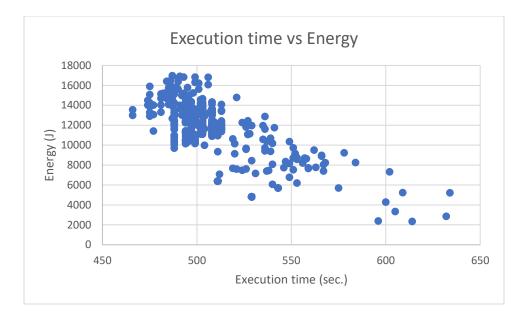

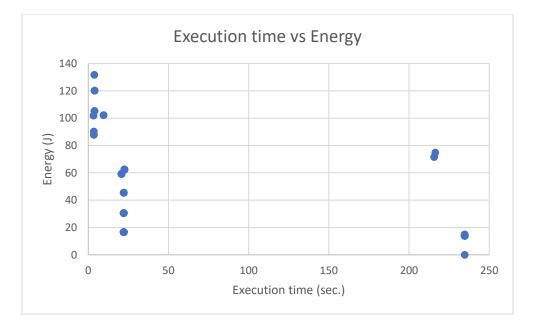

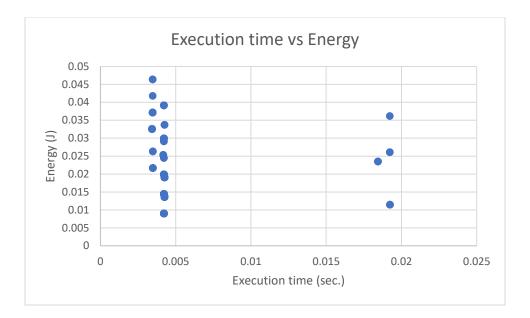

| 4.10 Relationship between Energy and Execution time                                                    | 83 |

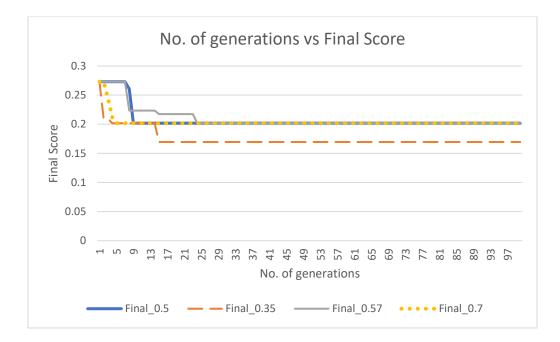

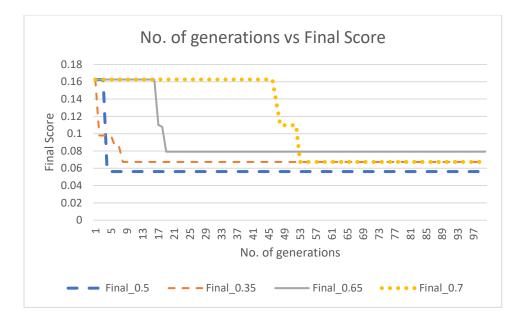

| 4.11 Energy- 33%, Exec. time- 34% and Deadline violation- 33%. Target Score= 0.7                       | 83 |

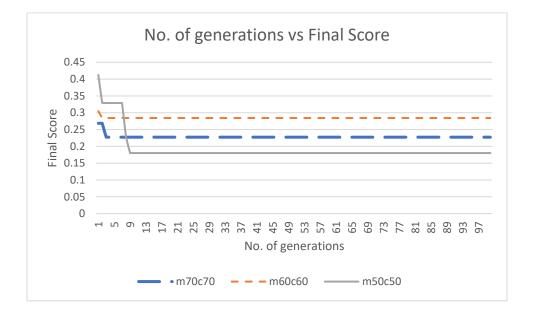

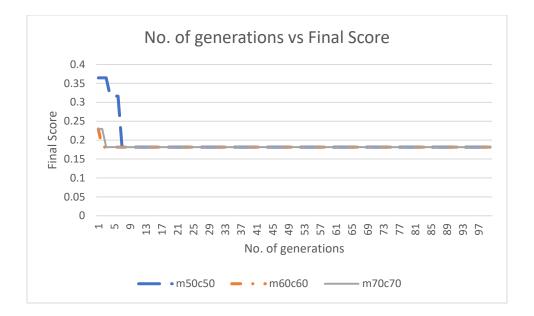

| 4.12 Energy- 80%, Exec. time- 19% and Deadline violation- 1%                                           | 84 |

| 4.13 Energy- 80%, Exec. time- 19% and Deadline violation- 1%. Target Score= 0.7                        | 85 |

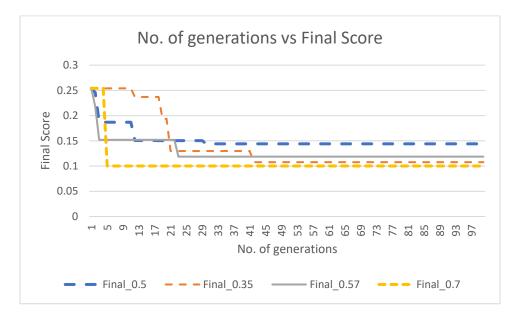

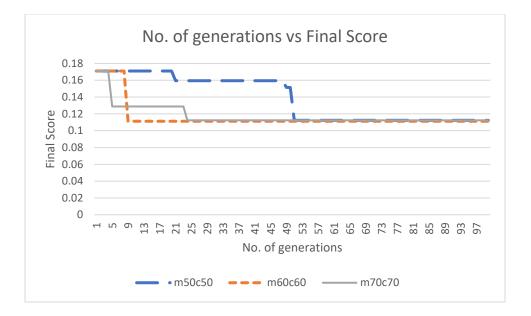

| 4.14 Energy- 19%, Exec. time- 80% and Deadline violation- 1%                                           | 86 |

| 4.15 Energy- 19%, Exec. time- 80% and Deadline violation- 1%. Target Score= 0.5                        | 87 |

| 4.16 Task-graph made from Parboil's benchmarks. Deadline= 8 seconds                                    | 89 |

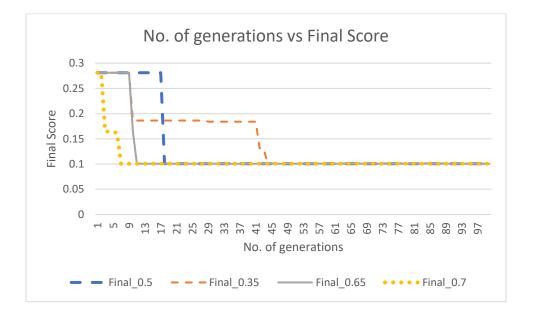

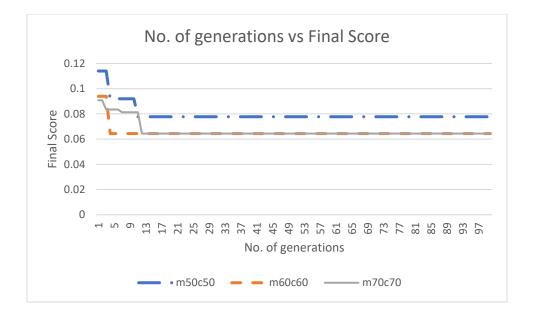

| 4.17 Energy-69 %, Exec. time- 30 % and Deadline violation- 1%.                    | 90  |

|-----------------------------------------------------------------------------------|-----|

| 4.18 Relationship between Energy and Execution time                               | 91  |

| 4.19 Energy-69 %, Exec. time- 30 % and Deadline violation- 1%. Target Score= 0.5  | 92  |

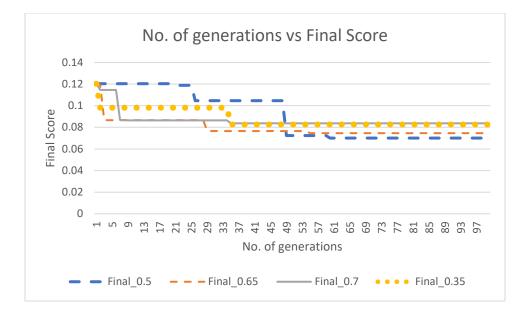

| 4.20 Energy-33 %, Exec. time- 34 % and Deadline violation- 33%.                   | 93  |

| 4.21 Energy-33 %, Exec. time- 34 % and Deadline violation- 33%. Target Score= 0.5 | 94  |

| 4.22 Energy-19 %, Exec. time- 80 % and Deadline violation- 1%.                    | 95  |

| 4.23 Energy-19 %, Exec. time- 80 % and Deadline violation- 1%. Target Score= 0.5  | 96  |

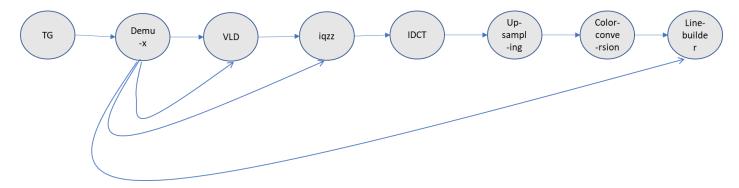

| 4.24 MJPEG decoder- Task graph                                                    | 97  |

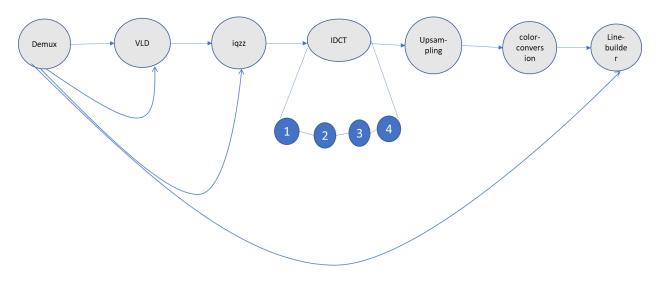

| 4.25 MJPEG decoder- Sequential implementation                                     | 98  |

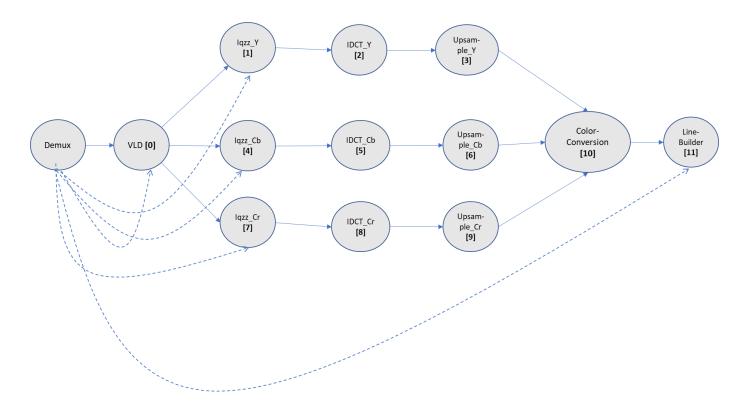

| 4.26 MJPEG decoder-Parallel implementation. Deadline= 0.02 seconds                | 99  |

| 4.27 Relationship between Execution time and Energy                               | 100 |

| 4.28 Energy-33 %, Exec. time- 34 % and Deadline violation- 33%.                   | 101 |

| 4.29 Energy-80 %, Exec. time- 19 % and Deadline violation- 1%.                    | 102 |

| 4.30 Energy-19 %, Exec. time- 80 % and Deadline violation- 1%.                    | 103 |

## List of Tables

| 4.1 CPU and GPU specification details for the graph in Fig. 4.2   | 73  |

|-------------------------------------------------------------------|-----|

| 4.2 Representative solutions for Fig. 4.7 (without normalization) | 78  |

| 4.3 CPU and GPU specification details for the graph in Fig. 4.8   | 80  |

| 4.4 Representative solutions for Fig. 4.9                         | 82  |

| 4.5 Representative solutions for Fig. 4.11                        | 84  |

| 4.6 Representative solutions for Fig. 4.12                        | 85  |

| 4.7 Representative solutions for Fig. 4.13                        | 85  |

| 4.8 Representative solutions for Fig. 4.14                        | 86  |

| 4.9 Representative solutions for Fig. 4.15                        | 87  |

| 4.10 PE library for the task graph in Fig. 4.16                   | 90  |

| 4.11 Representative solutions for Fig. 4.17                       | 91  |

| 4.12 Representative solutions for Fig. 4.19                       | 92  |

| 4.13 Representative solutions for Fig. 4.20                       | 93  |

| 4.14 Representative solutions for Fig. 4.21                       | 94  |

| 4.15 Representative solutions for Fig. 4.22                       | 95  |

| 4.16 Representative solutions for Fig. 4.23                       | 96  |

| 4.17 Resource library for MJPEG decoder (single frame)            |     |

| 4.18 Representative solutions for Fig. 4.28                       | 101 |

| 4.19 Representative solutions for Fig. 4.29                       |     |

| 4.20 Representative solutions for Fig. 4.30                       |     |

## Chapter 1

## Introduction

## 1.1 Motivation

Traditional processors are easy to program and can process any application. However, they are only capable of performing sequential instruction execution and need considerable amount of time to process general applications. Embedded systems especially do not have powerful cores because of power consumption, area, costs, etc. Consequently, their micro-processors are even slower than those in computers at executing sequential code. Dedicated hardware units are faster than software in executing the same functions.

Hardware/Software co-design emerged in the 1990's as a methodology for combining the advantages of fast but expensive dedicated hardware units with slow but inexpensive software-based solutions. It is a process of meeting system-level goals by exploiting the trade-offs involving hardware and software throughout their concurrent design. It mainly targets embedded systems with strict constraints on performance, area and energy expenditure. In current embedded systems, software has become the rigid component while hardware is evolving at a much faster rate. Moreover, increased emphasis on better performance, *green computing* and Moore's law are driving the evolution of computer architectures [1] and [2].

The ambitions of companies such as ARM and Xilinx confirm that the embedded industry is headed towards heterogeneous multicore systems. ITRS Road Map 2007 showed that the paradigm of heterogeneous massively parallel computing should be adopted to meet the demands of next generation's applications. A heterogeneous massively parallel computing platform consists of numerous specialized cores around multiple general-purpose processors which are not independent either from a programming or an implementation perspective. In these systems, homogeneous many core architectures have been compounded with task specific and specialized cores called accelerators. On such systems, control intensive and general-purpose software is

executed sequentially whereas data intensive parts of the application are offloaded to corresponding tailored architectures [2].

A typical modern embedded system has a workload consisting of a mix of tasks which have varied performance and power consumption characteristics depending on the processing element where they will be mapped. This makes them ideal for heterogeneous architectures. Platforms consisting of CPUs, GPUs and FPGAs are becoming increasingly prominent, partly due to the energy, performance and flexibility requirements of modern applications [3].

GPUs, especially, have prompted researchers to explore novel methods of exploiting their immense computational power. General purpose GPUs are now being used in the automation industry, robotics, medicine, etc. The speed-up achieved by the GPUs depends not only on the system hardware but also on how the functionality accesses the resources (shared or global memory, number of registers per thread, etc.). Using GPUs can considerably enhance performance at a fraction of the power needed by conventional CPUs [4].

The process of Hardware/Software Co-design generally consists of the following stages [5]:

- System specification: Co-design starts with a description of the system functionality along with their timing constraints. A specification language is used to keep away from the bias towards hardware or software.

- Functional simulation: The system is then simulated to verify the correctness of the input data sets. Data related to completion times, communication and concurrency is acquired during this step and constitutes the system's dynamic behavior.

- Co-Analysis: System information is extracted in this step through static analysis of the system specification.

- Co-Estimation: This step generates the timing information for every step of the specification for every processor class belonging to a set. Other characteristics such as area consumption are also accounted for in this step.

- Load and bandwidth estimation: The profiling data acquired in the Co-Estimation phase is used to estimate the load for the system functionality execution along with the timing constraints. The bandwidth is estimated after combining the timing and communication data of the application.

- Design Space Exploration: This phase consists of two major tasks: Hardware/Software

Partitioning with the architecture definition and timing co-simulation. The definition of

the architecture along with HW/SW partitioning perform design space exploration to

determine the optimal mapping of system functionality on hardware and software to meet

user-defined constraints. Timing co-simulation is performed to satisfy the timing

constraints of the system architecture and mapping which were already generated. The

purpose of DSE is to minimize the design space exploration time and generate highquality solutions.

- Implementation: Once satisfactory results for the mapping of tasks and the target architecture are obtained, system implementation can be initiated. Software components of the system will be implemented in C while hardware components will be transformed into HDL code which will be synthesizable.

General purpose computing on the GPU (GPGPU) offers the facility of load sharing between the CPU and the GPU in compute-intensive applications such as matrix multiplication, collision detection, ray tracing and so on. Hardware/Software Co-design and GPGPU are analogous to each other at a higher level of abstraction. Hence, the strategies involved in Co-design can also be applied in GPGPU. Design Space Exploration plays a crucial role in Hardware/Software Co-design and consequently also in GPGPU.

Design Space Exploration in GPGPU has its challenges. It is not optimal in all the application scenarios to move everything to the GPU. Moreover, offloading certain functions to the GPU may be of little benefit for the application if those functions do not follow the data-parallel nature of the GPU. In certain applications such as 2-D FFT, it was shown that the application performance can be optimized by appropriately distributing 1-D FFT calculations between the CPU and the GPU. Hence, it is possible to partition both functionality and data and this can be effectively utilized [6].

### 1.2 Problem Definition

Partitioning an application between the hardware and software is a NP-hard problem. This means there is no known algorithm for this problem which runs efficiently for all possible inputs and

always gives the correct answer. Furthermore, after an application is distributed between the hardware and software, deciding the optimal implementation of the application parts on hardware is also difficult to do manually.

We present a co-synthesis tool which tackles these challenges. The hardware of choice in our study is GPU. The application is first specified in a modular fashion prior to being fed to the proposed co-synthesis tool. Our tool partitions the application between the software and the GPU. In addition to that, it leverages the features of both the application and the GPU to arrive at an optimal implementation of the application parts assigned to the GPU in terms of power consumption and execution time.

### 1.3 Thesis Organization

Chapter 2 gives a detailed account of each of the stages of hardware/software co-design discussed this chapter. It contains an extensive review of the work done so far in the different aspects of hardware/software co-design. Additionally, it contains a thorough assessment of the work done in the domain of CPU-GPU systems to optimize and improve various important parameters such as power consumption and execution times of the target applications. The characteristics of important heterogeneous programming frameworks such as OpenCL and CUDA are also discussed in this chapter. A detailed description of the proposed design space exploration methodology is presented in Chapter 3. Chapter 4 depicts the results produced upon applying the proposed methodology to optimize real-world and synthetic applications. The conclusion and suggestions for future work are presented in chapter 5.

## Chapter 2

## Overview of Hardware/Software Co-Design and CPU-GPU computing

## 2.1 Hardware/Software Co-Design

#### 2.1.1 Introduction

A great number of research methods addressed design techniques for software and hardware and not much was known about the joint design of hardware and software. Hardware/software Codesign emerged to address the convergence of problems in integrated system design. Microprocessors were regularly used at that point, but microprocessor-based systems were mainly board-level systems. A class of designers was solely responsible for integrating standard hardware components on the board. It become apparent by the 1990s that microprocessor based system design would become an important discipline for system designers as well. When embedded processors were small and executed only a few hundred lines of code, manual design techniques were sufficient to satisfy functional and performance goals. Modern embedded systems demanded thousands of lines of code and needed to execute at high speeds to meet performance deadlines. Large 32-bit processors were already being used in board-level designs and it was apparent that Moore's law would lead to chips that would include both a CPU and other hardware [7].

Motivated by these developments, researchers began to develop introductory approaches for the design of embedded software running on multiple CPUs and these early efforts formed the basis of the codesign methodology. The predictability of embedded system design was sought to be developed through synthesis methods which indicate if constraints of power, performance, etc.

have been met or not. These methods should also allow the designer to incrementally refine a design over multiple levels of abstraction and create a first working implementation [8].

#### 2.1.2 Early works in Hardware/Software Co-Design

The first major step towards co-design was taken by Prakash and Parker when they formulated the co-synthesis problem as a mixed integer-linear program which could determine a multiprocessor topology while scheduling and allocating tasks on the target architecture [9]. The objective function is composed of functions which can be linearized such as system cost and performance. Constraints can be expressed as timing variables and binary variables. The non-linear constraints are linearized and converted to a MILP formulation [9,10]. This instigated active research on automatically partitioning task graphs into hardware and software [10].

In Hardware-software partitioning, a given functional specification is mapped on a hardware platform which initially consisted of a single CPU and an ASIC where both parts communicate via a bus (Fig. 2.1). As a result, the target platform was already fixed and it was required only for determining which functionalities would be implemented on the ASIC.

Fig 2.1: Target architecture for Hardware/Software Partitioning.

Gupta et al. proposed a partitioning methodology that starts with a hardware-only solution and migrates tasks to software while satisfying performance constraints and reducing system cost [11]. The COSYMA system took the opposite approach and started with a software-only partition and then transferred tasks to hardware to satisfy performance constraints while minimizing the cost of the resulting hardware [12]. Both approaches were based on the assumption that the implementation was single-threaded and the CPU and ASIC worked independently without interacting with one another [11 and 12].

Distributed task allocation algorithms are based on the assumption that processes have been allocated beforehand and the topology of the distributed computing engine is given. Stone presented the first algorithm for allocating processes to processors on distributed systems [13]. Shen and Tsai used a graph matching heuristic for allocating processes [14]. In their work, interprocess communication was minimized and the load was balanced.

#### 2.1.3 Traditional System-level design flow

The design process of embedded systems varies considerably with the complexity of the application. However, the study of a typical design flow shows that hardware and software components have common abstractions. This principle was utilized for efficient hardware/software codesign of systems [1].

Fig.2.2: Typical design flow.

Hardware architecture selection and partitioning are performed later than in a traditional design. This allows the design decisions to be based on more complete and accurate information [15].

Wolf argued that embedded systems design starts with the creation of a specification [7]. A system specification should include functional requirements (operations to be performed by the system) as well as non-functional (speed, power and manufacturing cost) requirements. Embedded system design methodologies should be able to support incomplete specifications or changes to the spec during the design [8]. Axelson outlined the following steps in the co-design of real-time systems [15]:

- System behavioral description: Executable specification of what a system is supposed to do.

- Hardware Architecture Selection: The description of the hardware components to be used and how they should be connected.

- Task scheduler design: The scheduler determines how the different computational resources of the hardware architecture are shared between the tasks of the behavioral description.

- Hardware/Software partitioning: This step determines how the tasks will be distributed among different processing elements.

#### 2.1.4 Models of Representation

Formal representations are important to meet the goals of performance, cost and reliability. An embedded system can generally be represented with two models: the system requirements model and a system architectural model. The requirements model can be a data-flow/control-flow diagram with response time specifications. The architecture model includes an architecture flow diagram (which allocates functional elements of the requirements model to physical units in the architecture) and an interconnection diagram. A model is different from the language used to specify a system. A model of computation can be based on several languages and there are some description languages which manage different models.

A variety of models have been developed and are used to represent heterogeneous systems. A computational model should comprehend concurrency, sequential behavior and communication methods. Some models are meant for data-intensive systems and others are more suitable for

control-oriented systems. There are others which combine data and control to represent systems [16].

#### Data-flow graph

Data-flow graphs are popular in modeling multimedia and similar data-oriented systems. Computationally intensive systems can be denoted by directed graphs where the nodes describe computations and the arcs represent the order in which computations are performed. Fig. 2.3 represents a typical data-flow graph.

Fig. 2.3: A typical data-flow graph

#### Petri-net

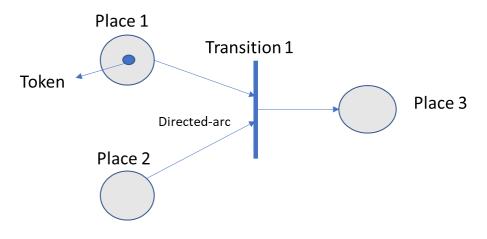

Petri-nets are composed of a set of places, a set of transitions, an input function which maps transitions to places and an output function which maps from transitions to places. Fig. 2.4 represents a simple petri-net.

Fig. 2.4: A simple petri-net

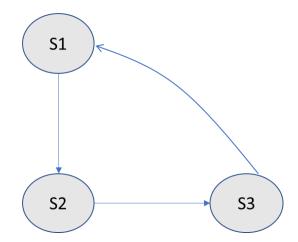

#### Finite State Machine

A finite state machine consists of a set of states, a set of transitions between states and a set of actions associated with these states and transitions [16]. Fig. 2.5 depicts a simple finite state machine. The nodes represent the state of the application and the arrows/arcs represent transitions from one state to another.

Fig. 2.5: A simple FSM

#### 2.1.5 Limitations of traditional design flow and the need for alternate design strategies

The architectural assumptions of earlier works are no longer valid, given the complex SoC architectures that have emerged recently. Most codesign strategies relied on the premise that a single executable description of the system can be compiled into either silicon or CPU code. This created the possibility of uniformly describing the behaviour of a system, which will be implemented in a combination of application-specific hardware and software. The description is partitioned, with the aid of fully/semi-automatic tools, into separate hardware and software parts. The result produced is passed to a high-level synthesis tool (a compiler) for producing the final implementation. The development of such automated tools is however outside the scope of this thesis.

There are many forms of hardware and software and differentiating between them is no longer straight forward. For example, a Field-Programmable Gate Array (FPGA) is a hardware circuit which can be reconfigured to a user-specified netlist of digital gates. The program for an FPGA is a bitstream and is used to configure the netlist topology. A bitstream of an FPGA can even be used to implement a softcore processor that can execute C programs. This has convinced scientists and engineers that the creation of software requires intimate familiarity with the hardware.

The demand for energy efficiency and performance has instigated a preference for hardware (parallel, fixed) implementation over CPU implementation (sequential, flexible). The most popular argument for dedicated hardware has been greater performance gains i.e. more work done in minimal time. Higher performance can be obtained by decreasing the flexibility of the system and specializing the architecture. However, it must be noted that almost every electronic device carries a battery, which in turn imposes energy constraints on the device. To improve energy efficiency, consumer devices are being implemented by using a combination of embedded CPU and dedicated hardware components. Moreover, parallel computer architectures, despite their utility, cannot cover all the applications. As a result, software designers cannot disregard the computer architecture during design and development.

There is considerable evidence to support the claims for the inclusion of on-chip software as well. Simulations need to be performed extensively to test the designs prior to the implementation phase. Since software bugs are easier to address than hardware, there is a

tendency for increasing the amount of software. Compact design schedules require multiple tasks to be performed at the same time. Consequently, hardware and software need to be developed concurrently. Software development begins as soon as the characteristics of the hardware platform are decided and much before a hardware prototype becomes available [15, 17].

Finding the correct balance among all the objectives is a daunting challenge. Adding hardware to a software solution might increase the performance of the overall application but it will also increase the total number of resources. Optimization techniques involving minimization of hardware costs and/or power under performance constraints are too restrictive in their approach and not feasible because each product has different and varied objectives to fulfill. Hence, it is critical for a designer to not only be able to implement the criteria into a CAD environment for codesign, but also to simultaneously account for multiple objectives [10, 17].

The following section surveys the techniques devised to date to address the challenges described here.

### 2.2 Design Space Exploration strategies and techniques

The trade-offs mentioned in the previous section ought to be made in the context of the system design space. For any given application, there are many possible system design solutions. The design space is given by a set of all possible permutations of allocations, mappings and schedules. When system parameters collectively satisfy both functional and non-functional constraints related to cost, performance, temperature, etc., a feasible solution is said to have been found [10]. System-level design space exploration is the task of exploring the set of feasible implementations efficiently and finding not only one but many optimal solutions.

Typical single-objective based techniques, which were proposed in the early days of co-design needed to optimize only a single objective function. Therefore, if a system solution that satisfies multiple objectives has to be found, a weighting function combining all the objectives has to be employed. Moreover, weights to every objective should be properly assigned according to the preferences of the designer. In order to perform a thorough exploration and allowing the designer to determine which trade-offs are achievable, multi-objective exploration techniques are recommended. The number of objectives and evaluation functions need to be chosen by the user.

Any renowned search/optimization technique could be applied to obtain feasible implementation candidates like randomized search techniques, techniques reliant on iterative search improvement or even exact techniques such as ILP [10]. Wolf presented a heuristic algorithm which simultaneously synthesized the hardware and software architectures for systems consisting of several heterogeneous processors and communication links to satisfy the performance goals at a minimal cost. Wolf's algorithm was unique because unlike the previous algorithms, it did not assume that the hardware topology was provided beforehand. It could synthesize the computer system with an arbitrary topology. In this algorithm, processes are first allocated to PEs such that the specifications deadlines are satisfied and then scheduled to determine communication rates. They are then re-allocated to PEs to minimize PE costs. Reallocation occurs again to minimize the communication costs. This is followed by the allocation of communication channels and then devices either to PEs or communication channels. Scheduling occurs during several of these steps to test the feasibility of the designs. The algorithm refines the design from feasible to one with a minimal cost [18].

A graph based approach was presented in 1997 which offered the capability of modeling heterogeneous target architectures and their interconnections. A specification graph consists of a task graph with data dependencies and a target architecture which specifies the available hardware components and their communication facilities. Edges between tasks and resources in this model denote mapping possibilities and contain further details such as power, cost, etc. Communication tasks were used in the place of edges to represent timing delays caused by transferring data (via communication links) between data-dependent tasks. This work specified the problem of allocation (architecture selection) and binding (mapping the application on the selected architecture) as an optimization problem and used an evolutionary algorithm to solve it. Furthermore, it was proved through this work that the problem of allocation and binding is NPcomplete. This technique motivated the development and application of sophisticated algorithms for finding feasible solutions for target architectures [10].

#### 2.2.1 Genetic Algorithm

Genetic Algorithm (GA) is one of the most popular optimization algorithms for process assignment and scheduling. It maintains a set of solutions and these solutions evolve in each generation during the execution of the GA. Solution are improved in every generation by

randomized changes and interchange of information between solutions. "Chromosome", in the context of GA, refers to a candidate solution for a problem. The "Mutation" operation randomly picks a location in the solution array and swaps it with a new value. The other operator, "Crossover", takes two solutions and picks out two locations in these solutions and interchanges parts of solutions between them. After the crossover operation, a new pair of solutions is evolved. This algorithm is capable of handling complex problems which consists of multiple NP-hard problems [19].

Dick and Jha devised a multi-objective optimization strategy, called MOGAC (Multi-Objective Genetic Algorithm for Co-synthesis) which partitions and schedules functional specifications which consist of multiple periodic task graphs. It employs a multi-objective GA based technique to optimize the cost and power and targets real-time heterogeneous architectures and meets hard real-time constraints. MOGAC accepts a library, which specifies the performance and power consumption of each task for every available PE. The edges of task graphs are assigned to communication links for which the criteria of communication time and power consumption are taken into account [20].

Chakraverty et al. proposed a stochastic model called ESCORTS (Evolutionary Scheme for Cosynthesis of Real-Time Systems) for hardware software co-synthesis which treats timing parameters as random variables. A hierarchical GA was used to optimize the task allocations and the resources needed for building the architecture. A stochastic scheduling algorithm was used to generate task schedules. The stand-out feature of this model is that the effective processor pools are evolved, cloned and re-evolved to generate better solutions whereas ineffective processor selections are discarded. Communication buses and edge allocations are similarly optimized and evolved by the cloning process and ultimately low-cost and high-performance architectures are generated [21].

#### 2.2.2 Simulated Annealing

Simulated Annealing (SA) is also a widely used optimization algorithm for process assignment and scheduling problems. In SA, solution changes occur by random "moves" (moving tasks from hardware to software and vice-versa). Eles et al. used SA and Tabu Search for automatic hardware software partitioning of system level specifications. They sought to minimize communication costs between the hardware and software partitions and enhance parallelism in

the eventual performance. They developed a cost function which guided partitioning towards the objective. It was formulated as a graph partitioning problem and implemented SA and Tabu Search on it and found Tabu Search to be superior in performance [22].

Advancements in system design space exploration have also been implemented in MPSoC targets. Xie and Hung proposed a Multiprocessor System-on-Chip (MPSoC) task allocation and scheduling algorithm which relied on temperature. Temperature is a critical factor and affects performance, reliability and cost of the embedded system. Their cosynthesis algorithm takes a task graph and technology library and generates a MPSoC architecture with minimum cost and effectively maps tasks on the generated architecture. It meets the deadline requirements of an application and reduces the average temperatures. Thermal aware heuristics are used and a temperature aware floor planning is employed to reduce the peak temperature and achieve a thermally aware distribution while meeting the real-time constraints. They investigated both power and thermal aware approaches for task allocation and scheduling. It was observed that the thermal aware approach outperformed the power aware schemes in reducing the average and maximal temperatures [10, 23].

#### 2.2.3 Particle Swarm Optimization

Particle Swarm Optimization (PSO) is a population based stochastic optimization technique which was developed by Eberhart and Kennedy. Inspired by the fish schools and bird flocks, PSO is very similar to GA in its approach. But unlike GA, it has no genetic operators such as crossover and mutation. The initial input for PSO is a population of random solutions and optimal solutions are looked for by updating generations. In PSO, potential solutions are referred to as "particles". These particles fly through the solution space by following the current optimum particles [24].

Bhattacharya et al. compared the effectiveness of the PSO algorithm with Integer Linear Programming (ILP), Ant Colony Optimization (ACO) and Genetic Algorithm (GA) by using some standard benchmarks. They found that ILP worked best for graphs with as many as a thousand nodes and produced optimal solutions while PSO produced sub-optimal solutions on an average. In terms of run-time requirements, the performance of PSO was superior than the other tested algorithms [25]. Li et al. sought to devise a solution for the time-consuming nature of PSO to enhance the safety and performance of embedded industrial applications. They proposed a HW/SW co-design architecture for implementing PSO on a FPGA. The Particle Updating Accelerator Module was implemented on the hardware. The other available processors operate in conjunction with the particle updating accelerator module to perform fitness evaluation and speed up the execution performance of PSO. Their design is flexible and various applications can be optimized without redesigning the hardware [26].

Today's exploration tools need to be flexible as any organization using such tools may have to contend with different optimization objectives for different products to be developed. For evaluation, the exploration model could be annotated and used to write user-specific cost functions. Evaluation functions to assess the various user-defined objectives have to be developed [10].

### 2.3 Co-simulation and Co-verification

After a co-synthesis mechanism has produced an architecture as well as mapped and scheduled the system activities, concurrent hardware and software synthesis is performed. These design steps transform the system specification, which has been split between hardware and software, into a physical implementation. System parts which should be mapped on hardware are designed using high-level, logic and layout synthesis tools. System parts that have been mapped on software programmable processors (CPUs, DSPs) are compiled into assembler and machine code, using either standard or specialized compilers and assemblers. Concurrent hardware and software synthesis offers the advantage of co-simulating both system parts, with the aim of finding errors in the design as early as possible to avoid expensive re-designs.

Once the hardware and software components have been implemented, they should be separately tested, integrated and tested again. Both hardware (manufacturing testing) and software testing (system validation) are necessary and both types of elements should be executed together to ensure the system meets its specifications [27].

## 2.4 Heterogeneous Computing: CPU-GPU platforms

There are several challenges involved in the collaborative computing of CPUs and GPUs due to their vastly different architectures. To optimize both performance and energy efficiency, the characteristics of both processors should be taken into account. Conventional optimization techniques which focus solely on either the CPU or the GPU are no longer effective in heterogeneous systems. As a result, novel techniques are required to harness the potential and promise of heterogeneous computing.

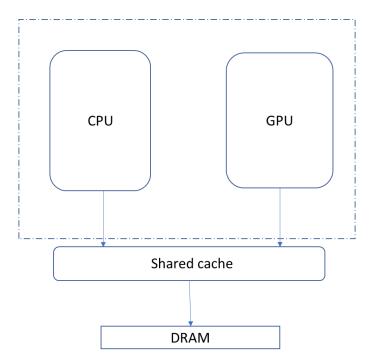

At the architecture level, a chip which has both the CPU and GPU integrated on the same chip is called an Accelerated Processing Unit (APU) or Single-Chip Heterogeneous Processor (SCHP) (Fig. 2.6). This is also known as a fused or integrated system. APUs are characterized by significantly shorter communication paths and a unified address space across the CPU and the GPU. Communication occurs via the shared memory in APUs [28].

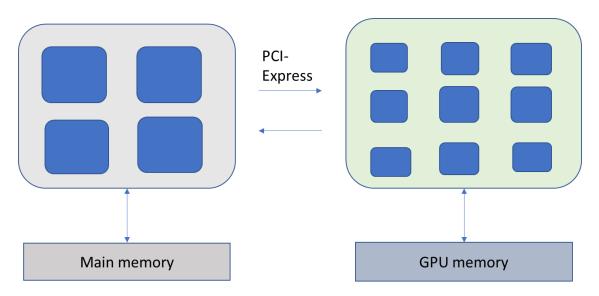

Fig. 2.6: Fused GPU + CPU

A conventional discrete system, on the other hand, has a CPU and GPU on different boards, connected with a Peripheral Component Interconnect Express (PCIe) bus as shown in Figure 2.7 [28]. Communication occurs across the PCI-express connection.

Figure 2.7: System overview of the CPU-GPU architecture.

Both discrete and fused systems have their advantages and disadvantages. Fused systems provide better bandwidth and latency. They bypass the PCI-e bus which is a critical bottleneck for discrete systems. However, fused systems can only serve specific categories of applications such as consumer electronics in the mobile and embedded sector.

Modern multicore CPUs use anywhere from 4 up to 64 cores, which are normally out-of-order, multi-instruction issue cores. These cores also run at a high frequency and utilize large caches to minimize the latency during the execution of a single thread. This makes them suitable for latency-critical applications. GPUs, on the other hand, have a larger number of cores, which are in-order cores that share their control unit. They operate at a lower frequency and have smaller caches. Hence, GPUs are more suitable for applications that have critical throughput requirements. Hence, a system consisting of both a CPU and a GPU can provide high performance for a variety of applications and usage scenarios than single CPU or GPU systems [28].

#### 2.4.1 Energy efficiency and Resource Utilization

Even though GPUs have the potential to speed-up the execution of many applications, they do so at the expense of significant power and energy consumption. Moreover, with the increasing number of installations of GPUs in supercomputers and data centers, their electricity costs bring power and environmental concerns. Dynamic Voltage and Frequency Scaling (DVFS) is a technique used for saving the energy of modern computers. It allows the processors to achieve better energy efficiency with proper voltage and frequency settings. While CPU DVFS techniques are mature, GPU DVS techniques are still in their infancy. Additionally, the CPU techniques cannot be applied to the GPU because the frequency domains of the GPU make it more complex [29].

Wang and Chu proposed a power estimation model based on a support vector regression (SVR) machine which is applicable to real GPU hardware. It can estimate the average runtime power of a GPU kernel by using a set of profiling parameters under different core and memory frequencies. They experimented with 931 samples obtained from 19 GPU kernels running on a real GPU platform with the core and memory frequencies ranging between 400 MHz to 1000 MHz. They further demonstrated that in conjunction with a performance prediction model, the optimal GPU frequency settings could be determined. These frequency settings led to considerable energy savings across 12 kernels [29].

Boyer claims that optimizing applications for systems with a great level of heterogeneity is quite challenging. GPU-enabled systems, despite offering many advantages, deal with applications which are wasteful of performance and energy. This wastefulness stems from a lack of resource utilization. General techniques were proposed to reduce overheads and improve GPU utilization and performance. The underutilization of GPUs was first addressed by reducing CPU-GPU interaction. Their strategies were tested with a leukocyte tracking case study. A dynamic scheduling algorithm was also proposed to balance an arbitrary GPU kernel across multiple devices and to keep each device fully utilized. A DVFS algorithm was also proposed to slow down the under-utilization of unutilized resources to increase effective utilization and energy efficiency [30].

Wang and Song proposed a technique for saving energy in HCSs [31]. This technique models the problem of workload division and voltage scaling as an integer linear programming problem,

with the objective of minimizing energy consumption for a given performance constraint. Voltage scaling and workload division affect each other and also have an effect on the performance and energy consumption of both CPUs and GPUs.

Hamano et al. proposed a task scheduling scheme to optimize the overall energy consumption for heterogeneous clusters consisting of CPUs and accelerators. This scheme has both static and dynamic aspects and is characterized by an acceleration factor. The acceleration factor is used to denote the speed-up a task can achieve upon being implemented on either of the CPU or an accelerator. The scheme uses the acceleration factor as well as other parameters to minimize the EDP (Energy-Delay Product) of each task. EDP enables one to determine the optimum supply voltage and allows flexible power-performance trade-off. This results in the optimization of both the processing time and the energy [32].

Timm et al. proposed a GPGPU-based design space exploration strategy for a biosensor which is used for both in-situ and real-time detection of viruses. Their strategy placed special emphasis on energy reduction. They proved that increasing the number of active cores does not necessarily decrease the application's energy consumption [33]. Komoda et al. presented an efficient power-capping technique by coordinating DVFS and task mapping in a single computing node equipped with GPUs. Power capping is a method used for limiting the power consumption of a system to a predetermined level. To implement the settings of DVFS and task mapping for avoiding power violation and load balance, empirical models for power and performance of a CPU-GPU heterogeneous system were developed. The empirical models predict the execution time and the maximum power consumption in a hybrid power consumption by using both the CPU and the GPU. Performance and power consumption are usually dependent on the CPU and GPU frequencies and the task mapping. The frequencies of the CPU and the GPU and the GPU or the GPU are determined at the start of the application's execution. The outcome of this method is an optimal set of device frequencies and task mapping [34].

Cebrian et al. claim that not all the applications to be ported to GPUs can make use of the available resources due to bandwidth requirements, data dependencies, etc. which in turn reduces the performance per watt. They proposed several strategies involving voltage and frequency scaling and SM (Streaming Multiprocessor) power gating on GPUs. Their work confirmed the

presence of under-utilization and indicated that resource optimization can increase the energy efficiency of GPU-based computation [35].

Lin et al. proposed analytical energy and performance models for auto-tuning GPGPU applications [36]. The objective of their strategy was to find an optimal configuration for a kernel which meets the energy and performance constraints set by the user. Their work consists of an analytical model for estimating the performance and power consumption of kernels and an autotuning framework for automatically obtaining the near-optimal configuration for kernel computation. Their strategy for obtaining the optimal kernel configuration involved Simulated Annealing (SA) or Genetic Algorithm (GA). They performed their experiments with the Intel Core i7-2600 CPU and used five NVIDIA GPUs having either the Kepler or Fermi microarchitectures. They chose some of their applications from popular GPU-based benchmarks and the classic matrix multiplication example from the NVIDIA's SDKs. They experimented with several iteration values, termination conditions, annealing rates and compared their search space results with the brute-force algorithm.

According to Park et al., the following optimization strategies are used for modern GPU architectures:

- Mapping threads to Streaming Multi-processors (SMs) and Streaming Processors (SPs) of GPU

- Coalesced global memory accesses

- Shared memory access devoid of bank conflicts

- Divergence avoidance in conditional statements

- Loop Unrolling or Algorithmic Cascading

- Using Single Precision

- Using Fast math

Park et al. claimed that the most effective optimization strategy is to find the optimal mappings of the application threads to the SMs and the SPs of the GPU. To affirm that claim, they performed design space exploration with a commonly used GPU (NVIDIA GTX 660) to investigate the best kernel grid structure of the GPU for optimal power or energy consumption. They performed their experiments on the dot-product application and sought to identify the thread and block sizes, which lead to the least expenditure of power/energy.

Rethinagiri et al. proposed a two-part methodology consisting of a system-level power/energy estimation strategy and optimization techniques for heterogeneous CPU-GPU platforms. The power estimation technique is devised using functional parameters such as external memory access, bus access rate, cache miss rate, frequency of the processor, etc. Moreover, a system-level simulation prototype was devised to accurately assess the activities of the power model. They leveraged the power estimation methodology to develop novel power optimization techniques involving inter-task DVFS and work-load balancing. The effectiveness of their methodologies was tested using the CARMA kit, consisting of an ARM quad-core processor and a NVIDIA 96 core GPU processor for industrial benchmarks [38].

Timm et al. sought to prove that adding an additional GPU in an embedded system will lead to reduced energy consumption and also speed up applications. They found from their studies that to optimize the benefits of incorporating a GPU in an embedded system, the structure and features of the application (such as parallelism and GPU resource utilization) should be fully exploited. Their methodology consisted of modeling and profiling applications at a coarse-grain level and then performing a profit analysis to confirm the benefits of including a GPU to improve energy efficiency. They used an Intel Atom 270 as their CPU and the NVIDIA 8400 GS as their GPU. They highlighted the necessity of minimizing the idle time, the communication over-head and the incorporation of DVFS techniques to optimize the usage of GPUs [33].

Mapping applications with deadlines onto heterogeneous systems consisting of two or more resources is an NP-hard problem. It calls for designing efficient mapping heuristics which can speed-up the execution of applications to meet their deadlines. Liu et al. sought to devise power-efficient mapping techniques which can meet the timing requirements of applications while reducing power and energy consumption by using the DVFS methodology. Their technique mainly consists of two steps. In the first step, their technique maps the application to either a CPU or GPU to satisfy the timing constraints. The mapping can occur both online and offline. The second step involves using DVFS to both the CPU and the GPU to minimize energy expenditure. They also exploit the fact that average-case execution times are less than the worst-case execution times. Additionally, they leverage the slack from the early completion of tasks by

using DVFS. This leads to considerable energy savings. They used the Intel Xeon 5160 CPU and an AMD Radeon HD 5770 GPU for their experiments [40].

Wang sought to optimize the leakage power of caches in GPUs by dynamically switching L1 and L2 caches in low power modes during periods of inactivity to reduce leakage power. Two DFS techniques were also proposed to improve the performance and the dynamic power of GPUs. One uses a feed-back controlling algorithm to regulate the frequency of parallel processors and memory channels based on the occupancy of memory buffering queues. The other technique is based on maximizing the throughput of all parallel processors under dynamic power constraints. This was formalized as a linear programming problem and solved at run-time [41].

#### 2.4.2 Profiling Techniques for GPUs

Timm et al. measured the overall power consumption at two different points during the execution of the benchmarks [39]. The power consumption of the GPGPU-equipped graphics systems was measured by inserting probes between the supply lines of the PCI Express bus. For measurements, a 0.1  $\Omega$  resistor is embedded into the 12 V and 19 V supply lines and a 0.01  $\Omega$ resistor into the 3.3 V supply line. They measured the voltage drop across these resistors. The power values for the system and the GPU were determined by using the values of the current. The energy consumption for the system alone and the system with the graphics card were found by using the Reimann Sum (approximation method which uses finite sums).

Martin Peres claims that estimating the power consumption can be done in real-time by using two different methods. The first method involves reading the voltage drop across a shunt resistor mounted in series with the chips power-line. The instantaneous power consumption on the chip is equal to the voltage delivered by the voltage controller times the measured current. This method, he notes, also has its flaws. It requires an ADC converter and dedicated circuitry. The setup is expensive and requires dedicated hardware on the PCB of the GPU and a fast communication channel between the ADC and the chip. The other solution requires monitoring the block-level activity inside the chip. Power consumption can be estimated by monitoring the activity of different blocks on the chip, giving them a weight depending on the number of gates they contain, sum all the values, low-pass filter them then integrate over the refresh period of the power estimator. This is done by the hardware itself [42].

Lin et al. do power profiling by considering the fact that power consumed by a kernel is related to the instructions in its assembly code. When a kernel is executed, every instruction consumes several watts. The power consumed by each instruction is measured and the information is used to profile the power consumption of a kernel. The kernel is compiled by NVCC into object code and it dis-assembled into assembly code by a dis-assembler. The power consumption of the given assembly code is analyzed by power-profiling. For their experiments, they used a current clamp to measure the GPU current. The values obtained were used to calculate the power and energy. The electric current was measured from the PCI-e bus to the GPU device. It is then multiplied by the voltage of the PCI-e bus to get the power consumption. The power consumption of the kernel on the GPU [36].

NVIDIA has introduced a tool called Nvidia System Management Interface (nvidia-smi) which provides management and monitoring capabilities for NVIDIA's GPU devices. It allows the user to control the power state of the GPUs and monitor memory usage and power consumption. It is specifically targeted towards NVIDIA's Tesla, Quadro, GRID and GeForce devices [43].

#### 2.4.3 Task Mapping for CPU-GPU platforms

Paone proposed a novel analytic technique for fast pruning of the design space [45]. The methodology exploits the concurrency in an application task graph for efficient mapping on heterogeneous parallel platforms. During the tuning phase, the technique generalizes the previous analysis of interdependent parameters by exploiting a constraint solver to efficiently identify an initial set of task configurations which are compliant with the platform constraints. The second step is a mapping phase where inter-task parallelism is improved while accounting for the overhead of host-to-device and device-to-host memory transfers. The design flow was validated with a stereo-matching application that was implemented in OpenCL.

Vilches et al. presented a novel adaptive partitioning strategy that was geared specifically towards irregular applications running on heterogeneous CPU-GPU chips. This strategy involves exploiting parallel loops in irregular applications running on CPU-GPU chips to dynamically find appropriate chunk sizes for CPU and GPU cores. This strategy was evaluated on the quad-core Intel Core i7-4770 processor which also features the HD-4600 on-chip GPU. They used

applications from the Rodinia and SHOC suites in addition to other regular and irregular applications to test their strategy [45].

Wachter et al. proposed a temperature-aware mapping and partitioning methodology for CPU-GPU MPSoCs. They have done profiling by measuring the temperatures of the CPU and GPU cores while executing different applications at different partitions. The temperature data obtained from evaluated to partition their applications between the CPU and the GPU. They tested their methodology with all the applications in the Polybench benchmark on the Odroid XU-3 platform [46].

## 2.5 GPGPU programming

Many programming options are available to speed up the applications using GPGPU platforms. CUDA, OpenCL and DirectCompute are the most prominent Application Programming Interfaces (APIs) for heterogeneous systems. DirectCompute is a GPGPU API which was developed by Microsoft and it uses the High-Level Shader Language (HLSL). It is easy to use for programmers but does not provide sufficient support and documentation.

Nvidia has developed the CUDA environment. It is a mature framework and has a C like syntax which makes it user-friendly for C programmers. It provides support for GPU optimized libraries and can be used easily with existing solutions. Nevertheless, CUDA is only supported by NVIDIA GPUs and does not fall back to the CPU when the GPU is not detected.

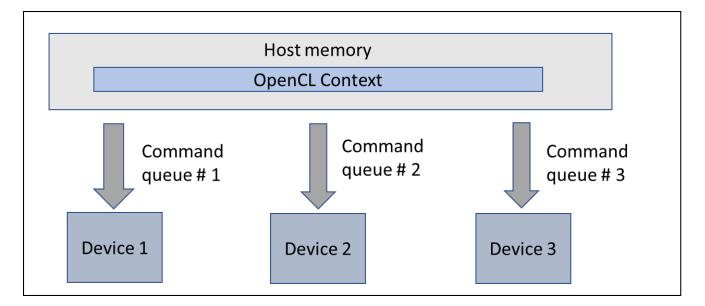

OpenCL (Open Computing Language), on the other hand, is an open environment and has been adopted by several vendors. It facilitates both task parallelism and data parallelism. For each PE, a command queue can be created through which tasks can be submitted. Use of parallel programming can be achieved on each PE individually and on all the PEs collectively. It provides a higher abstraction programming framework and enables the programmer to write portable programs for a wide variety of processing units. This does not necessarily mean that OpenCL can achieve the highest possible performance for heterogeneous systems [47].

#### **2.5.1 Introduction to CUDA architecture**

In GPUs, most of the die area is used for ALUs unlike CPUs, where majority of the area is devoted to the memory cache. GPUs, on the other hand, have relatively small caches. The previous generations partitioned resources into vertex and pixel shaders. The CUDA architecture (Nvidia uses the same name for its GPUs' architecture and their programming environment) includes a unified shader pipeline which allows every arithmetic logic unit (ALU) to be harnessed by the program to perform general purpose computations. NVIDIA intended this new family of processors to be used for general purpose computing. In order to meet this goal, the ALUs were designed to use an instruction set tailored for general computation rather than for graphics. Execution units were allowed arbitrary read and write accesses to memory and to a software managed cache called shared memory. These features enable the CUDA architecture to perform computations and traditional graphics tasks [48].

NVIDIA GPUs consist of several Streaming Multiprocessors (SMs) and they serve as abstractions for the underlying hardware. Every Streaming Multiprocessor has a set of Streaming Processors (SPs), which are commonly called CUDA cores. These cores are solely responsible for executing instructions in a program. The number of SPs in a SM and the number of SMs vary with every GPU device.

The CUDA cores in a SM are called SIMT cores (Single Instruction Multiple Threads) cores. Groups of 32 cores called Warps operate simultaneously to execute the same instructions with multiple data. Every SM has warp schedulers for executing the work performed by the 32 cores.

GPUs have their own memory on board. GPU memory can range from 768 MB to 6 GB of GDDR5 Memory. All CUDA capable cards have a fully coherent L2 cache. A GPU's L2 cache is considerably smaller than a CPU's L2 cache but offers much larger bandwidth. The L1 caches in such CUDA capable cards are not coherent, unlike the L1 caches in CPUs. As a result, if two different SMs are reading from and writing to the same memory location, changes made by one SM will not be visible to the other SM. This complicates the task of debugging errors. Every SM is equipped with its own L1 cache [48, 50].

#### 2.5.2 CUDA's Programming Model

CUDA's parallel programming model has three key abstractions: a hierarchy of thread groups, a hierarchy of shared memories and barrier synchronization. These abstractions provide the facilities of fine-grained data parallelism and thread parallelism, nested within coarse-grained data parallelism and task parallelism. The programmer can partition the problem into coarse sub-problems which can be solved independently in parallel, and then into finer pieces which can be cooperatively solved in parallel. This allows threads to cooperate when solving each sub-problem. At the same time, it enables transparent scalability since each sub-problem can be scheduled to be solved on any number of processor cores and only the run-time system needs to know the processor count. As a result of this model, the CUDA architecture spans a wide range of applications by simply scaling the number of processors and memory partitions [49].

#### 2.5.3 CUDA's Execution Model

A CUDA device is built around a scalable array of multithreaded Streaming Multiprocessors (SMs). A multiprocessor consists of eight Scalar Processor (SP) cores, two special function units for transcendental operations, a multithreaded instruction unit, an on-chip shared memory. The multiprocessor creates, manages and executes threads concurrently in hardware with little scheduling overhead. Fast barrier synchronization together with lightweight thread creation and zero-overhead thread scheduling efficiently support fine-grained parallelism.

To manage hundreds of threads running several different programs, the multiprocessor employs a SIMT (single-instruction, multiple-thread). The multiprocessor maps each thread to one SP, and each scalar thread executes independently with its own instruction address and register state. The multiprocessor SIMT unit creates and manages threads in groups of 32 parallel threads called warps. Individual threads composing a SIMT warp start together at the same program address but are free to branch and execute independently [50].

#### 2.5.4 OpenCL Application Programming Interface

OpenCL is an open-source API developed to allow co-processors to work in tandem with CPUs. It is maintained by the Khronos Group. It is like CUDA and has a C like syntax which can be integrated easily. OpenCL supports multiple devices such as multi-core CPUs, multi-socket CPU, GPUs and cell processors. This allows the programmer to change the hardware

27

architecture without any changes to the code as OpenCL is the standard from which vendors are expected to derive abstractions to support their heterogeneous devices. This provides it the capability to support devices like FPGAs and mobile hardware in the future. Since OpenCL can provide support for a general heterogeneous environment and industry support is available for it, this API is being preferred over others.

Every OpenCL implementation defines platforms which enable the host system to interact with OpenCL-capable devices. The software architecture of all implementations can be described by:

- Platform Model

- Execution Model

- Memory Model

#### **Platform Model**

This model consists of the host connected to one or more OpenCL devices. A device is divided into one or more compute units. Compute units, in turn, are divided into processing elements.

#### **Execution Model**

The Execution Model consists of two parts: kernels which execute on one or more OpenCL devices and a host program which executes on the host. Both the platform and the execution model are visually represented by Fig. 2.8.

Fig. 2.8: OpenCL platform and execution model.

The host program creates the context for the kernels and coordinates their execution. An index space is defined whenever a kernel is submitted to the host for execution. The index space is called ND-Range and is an N-dimensional index space (where N can be 1,2 or 3).

An instance of a kernel executes for each point in the index space. In OpenCL terminology, a kernel instance is called a work-item and is identified by its point in the index-space, which provides a global-id for the work-item. Every work-item executes the same code but the data that every work-item operates upon is different. Work-items are organized into work-groups. Work-groups are assigned a unique work-group ID with the same dimensions as the index space used for the work-items. All work-items in a work-group execute on the same compute unit and are capable of synchronization.

A context is defined for the execution of the kernels. It is created by the host using OpenCL API functions. A context is composed of the following parts:

- Devices: Collection of OpenCL devices used by the host.

- Kernels: OpenCL functions which run on OpenCL devices.

- Program: Source and executable for the implementation of kernels.

- Memory objects: These objects are visible to the host and the OpenCL devices.

Commands are placed in the command queue which are scheduled on the devices within the context. They are of the following types:

- Kernel execution commands which are executed on the processing elements of a device.

- Memory commands are used for transferring data between host and device as well as for mapping and un-mapping objects from the host address space.

- Synchronization commands regulate the order of execution. The command queue regulates the order of execution on a device. Commands can be launched in-order, where they execute in the order they appear in the command queue or out-of-order, where the following commands begin executing before their completion [47, 50].

#### **Memory Model**

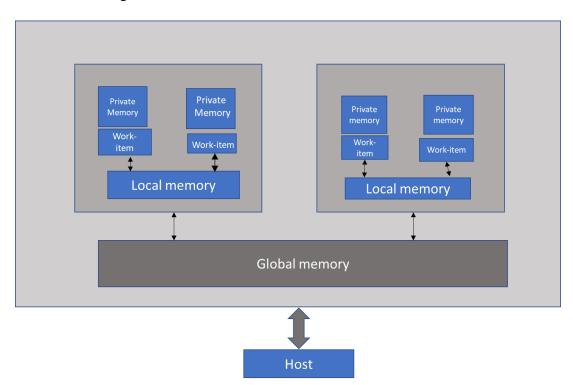

Memory objects can be accessed by all the devices only when they are defined in the same context. Consequently, the work-items which are defined have access to four distinct memory regions as shown in Fig. 2.9:

Fig. 2.9: OpenCL memory model.

1. Global Memory: This region permits read/write access to all the work-items in all workgroups.

2. Constant Memory: It is a region in global memory and remains constant during the execution of a kernel. Memory objects placed into constant memory are allocated and initialized by the hosts.

3. Local Memory: This memory region is only accessible to its corresponding work-group. This memory region can be used to allocate variables that are shared by all the work-items of that work-group. It may be implemented as dedicated regions of memory on the OpenCL device.

4. Private Memory: This memory region corresponds to work-items. The variables in a workitem's private memory are not visible to other work-items.

### Chapter 3

## System-level Optimization for CPU-GPU platforms

#### 3.1 Introduction