## AUTONOMOUS STEREO VISION SYSTEM FOR DEPTH COMPUTATION OF MOVING OBJECT

by

Alejandro Emerio Alfonso Oviedo

Bachelor of Automation Engineering, 2006, Havana University of Technologies

Master of Digital Systems and Computer Electronics, 2011, Havana University of Technologies

A Project

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Engineering

in the Program of

**Electrical and Computer Engineering**

Toronto, Ontario, Canada, 2017

© Alejandro Emerio Alfonso Oviedo 2017

#### AUTHOR'S DECLARATION

I hereby declare that I am the sole author of this project. This is a true copy of the project, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this project to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this project by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my project may be made electronically available to the public.

#### ABSTRACT

# Autonomous Stereo Vision System for Depth Computation of Moving Object

Master of Engineering

2017

#### Alejandro Emerio Alfonso Oviedo

#### Master of Engineering Electrical and Computer Engineering

#### Ryerson University

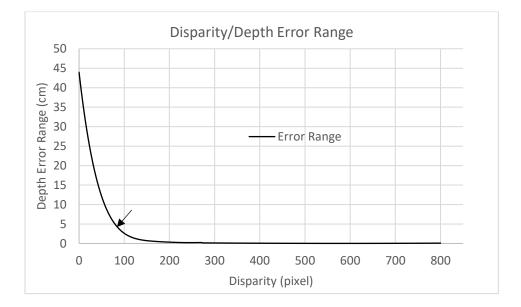

This work targets one real world application of stereo vision technology: the computation of the depth information of a moving object in a scene. It uses a stereo camera set that captures the stereoscopic view of the scene. Background subtraction algorithm is used to detect the moving object, supported by the recursive filter of first order as updating method. Mean filter is the preprocessing stage, combined with frame downscaling to reduce the background storage. After thresholding the background subtraction result, the binary image is sent to the software processing unit to compute the centroid of the moving area, and the measured disparity, estimate the disparity by Kalman algorithm, and finally calculate the depth from the estimated disparity. The implementation successfully achieves the objectives of resolution 720p, at 28.68 fps and maximum permissible depth error of  $\pm 4$  cm (1.066 %) for a depth measuring range from 25 cm to 375 cm.

# Table of Contents

| List of Ta  | Fables                                         | vi  |

|-------------|------------------------------------------------|-----|

| List of Fig | -igures                                        | vii |

| Chapter     | r I Introduction                               | 1   |

| 1.1         | Motivation                                     | 1   |

| 1.2         | Objectives                                     | 2   |

| 1.3         | Stages                                         | 2   |

| 1.4         | Original contribution                          | 3   |

| 1.5         | Organization                                   | 4   |

| Chapter     | r II Background                                | 6   |

| 2.1         | Introduction                                   | 6   |

| 2.2         | Related Work                                   | 6   |

| 2.3         | Theory                                         |     |

| 2.3.        | 3.1 Stereo Vision System                       | 11  |

| 2.3.        | 3.2 Rectification and Calibration              | 13  |

| 2.3.        | 3.3 Correlation-Based Algorithm                | 15  |

| 2.3.4       | 3.4 Feature-Based Algorithm                    | 21  |

| 2.3.        | 3.5 Moving Object Detection and Tracking       | 21  |

| 2.4         | Summary                                        | 28  |

| Chapter     | r III System Architecture Development          | 29  |

| 3.1         | Introduction                                   | 29  |

| 3.2         | General Architecture                           | 29  |

| 3.3         | Algorithm Selection and System Partitioning    |     |

| 3.3.        | 3.1 Hardware                                   |     |

| 3.3.        | 3.2 Software                                   |     |

| 3.4         | Hardware Architecture                          | 34  |

| 3.5         | Software Architecture                          |     |

| 3.5.        | 5.1 Initialization, start and operation block  |     |

| 3.5.        | 5.2 Segmented frame acquisition block          |     |

| 3.5.        | 5.3 Compute depth block                        | 40  |

| 3.6         | Summary                                        | 42  |

| Chapter     | r IV Implementation, Verification and Analysis | 43  |

| 4.1         | Introduction                                   | 43  |

| 4.2                                                                                                                        | Spe  | cifications                                               | 43 |  |

|----------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------|----|--|

| 4.3                                                                                                                        | Plat | tform                                                     | 43 |  |

| 4.3                                                                                                                        | 3.1  | Omnivision (CMOS) OV5642 Camera Module                    | 44 |  |

| 4.3                                                                                                                        | 3.2  | Digilent ZYBO development board                           | 47 |  |

| 4.4                                                                                                                        | Har  | dware Implementation                                      | 47 |  |

| 4.4                                                                                                                        | 4.1  | Capture Frame Block (CFB)                                 | 47 |  |

| 4.4                                                                                                                        | 4.2  | Down-Scale Module (DSM)                                   | 51 |  |

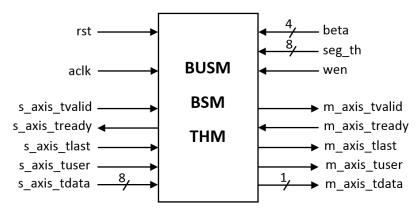

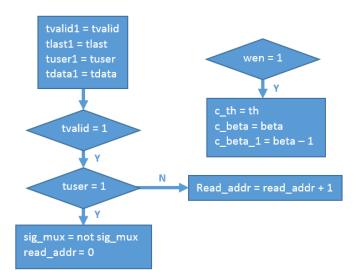

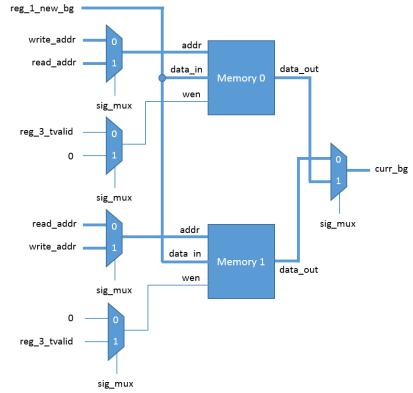

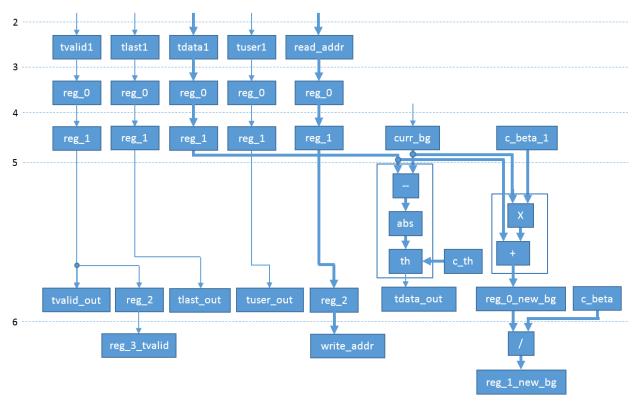

| 4.4.3 Background Update and Synchronization Module (BUSM) plus Background Subtraction (BSM), and Thresholding Module (THM) |      |                                                           |    |  |

| 4.4                                                                                                                        | 1.4  | Serial-In Parallel-Out Shift Register                     | 60 |  |

| 4.4                                                                                                                        | 1.5  | Serial Camera Control Bus (SCCB)                          | 62 |  |

| 4.5                                                                                                                        | Ger  | neral Hardware Characteristics and Performance            | 63 |  |

| 4.6                                                                                                                        | Soft | tware Implementation                                      | 64 |  |

| 4.6                                                                                                                        | 5.1  | Initialization, Start and Operation Block                 | 64 |  |

| 4.6                                                                                                                        | 5.2  | Segmented Frame Acquisition Block (DMA Interrupt Handler) | 66 |  |

| 4.6                                                                                                                        | 5.3  | Computing Depth Block                                     | 70 |  |

| 4.7                                                                                                                        | Sho  | owing Results                                             | 77 |  |

| 4.8                                                                                                                        | Pow  | ver Consumption Control                                   | 78 |  |

| 4.9                                                                                                                        | Sum  | nmary                                                     | 79 |  |

| Chapter V Summary and Future Work                                                                                          |      |                                                           |    |  |

| 5.1                                                                                                                        | Fut  | ure Work                                                  | 83 |  |

| REFERENCES                                                                                                                 |      |                                                           |    |  |

| Glossary of Acronyms and Abbreviations90                                                                                   |      |                                                           |    |  |

### List of Tables

| Table 4.1 CFB resources utilization based on target platform Xilinx Zynq-7010 architecture                 | 51 |

|------------------------------------------------------------------------------------------------------------|----|

| Table 4.2 DSM resources utilization based on target platform Xilinx Zynq-7010 architecture                 | 55 |

| Table 4.3 BUSM-BSM-THM resources utilization based on target platform Xilinx Zynq-7010 architecture        | e  |

|                                                                                                            | 59 |

| Table 4.4 Serial-In Parallel-Out Shift Register resources utilization based on target platform Xilinx Zyng | -  |

| 7010 architecture                                                                                          | 61 |

| Table 4.5 SCCB resources utilization based on target platform Xilinx Zynq-7010 architecture                | 62 |

| Table 4.6 Entire Implementation resources utilization based on target platform Xilinx Zynq-7010            |    |

| architecture                                                                                               | 64 |

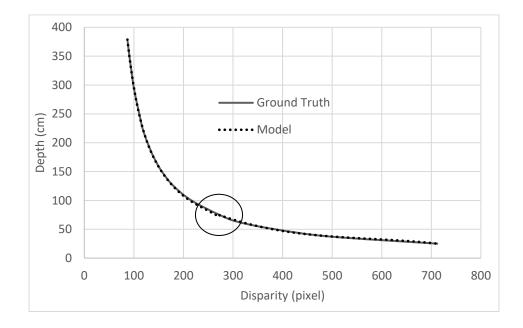

| Table 4.7 Models that fit the ground truth curve in two regions                                            | 75 |

| Table 4.8 Software Implementation building result                                                          | 77 |

| Table 4.9 Implementation DC characteristics                                                                | 79 |

# List of Figures

| Figure 2.1 Stereo camera parallel model                                                               | 12   |

|-------------------------------------------------------------------------------------------------------|------|

| Figure 2.2 Triangulation model                                                                        | 13   |

| Figure 2.3 Support windows on reference and target image                                              | 15   |

| Figure 2.4 a-) Full Cost Computation. b-) 1D incremental optimization technique                       | 16   |

| Figure 2.5 Census transformation                                                                      | 18   |

| Figure 2.6 Hamming Distance                                                                           | 18   |

| Figure 2.7 Eight paths optimization                                                                   | 19   |

| Figure 2.8 Generalized Background Subtraction method                                                  | 22   |

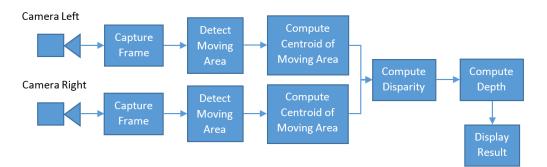

| Figure 3.1 General Architecture of proposed design                                                    | 29   |

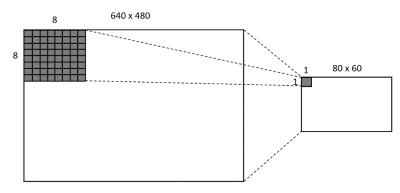

| Figure 3.2 1/8 Down-Scale example by mean of 8x8 pixels blocks                                        | 32   |

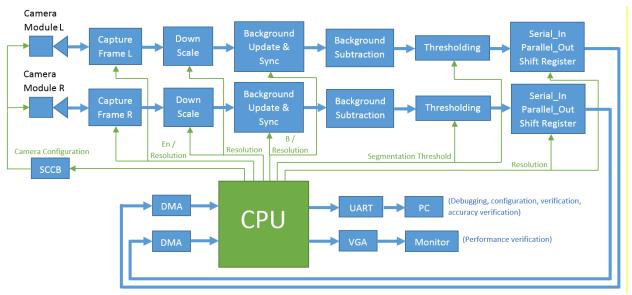

| Figure 3.3 Hardware Architecture of proposed design                                                   | 35   |

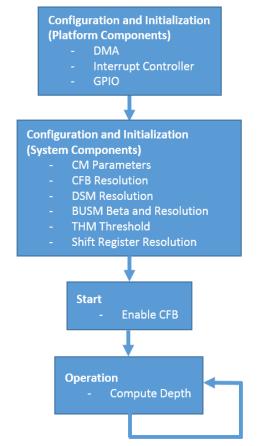

| Figure 3.4 Software Architecture: Initialization, start and operation block                           | 39   |

| Figure 3.5 Software Architecture: Segmented frame acquisition block, Left and Right Channels          |      |

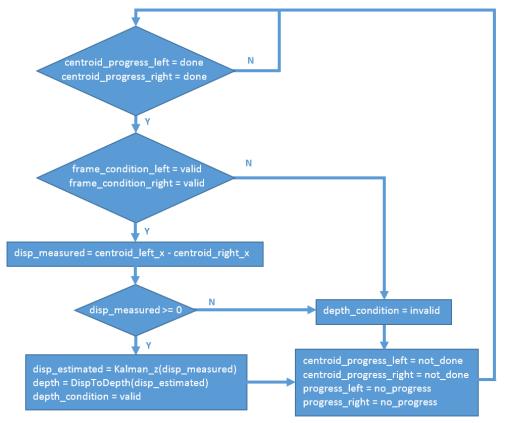

| Figure 3.6 Software Architecture: Compute depth block                                                 | 41   |

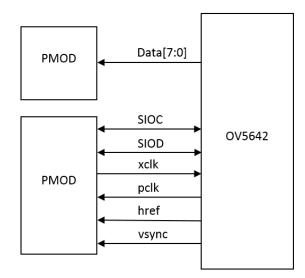

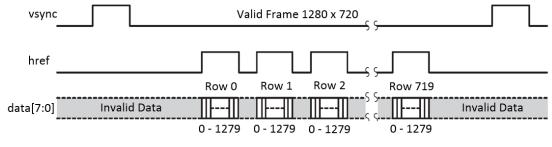

| Figure 4.1 OV5642 8-bits data interface                                                               | 45   |

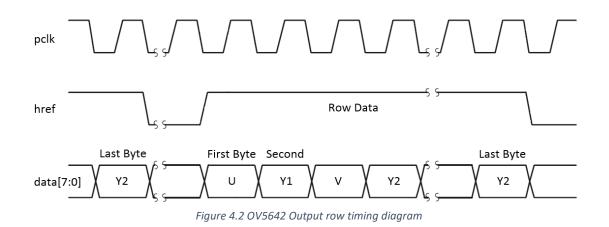

| Figure 4.2 OV5642 Output row timing diagram                                                           | 46   |

| Figure 4.3 OV5642 Frame timing diagram                                                                | 46   |

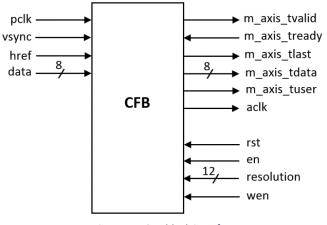

| Figure 4.4 CFB block interface                                                                        | 48   |

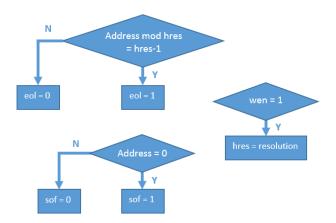

| Figure 4.5 CFB eol, sof and resolution configuration                                                  | 49   |

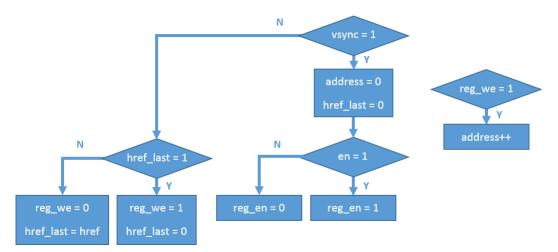

| Figure 4.6 CFB Detecting active portion of frame, enabling capturing and filtering valid portion of c | Jata |

| input                                                                                                 | 50   |

| Figure 4.7 CFB output assignment                                                                      | 51   |

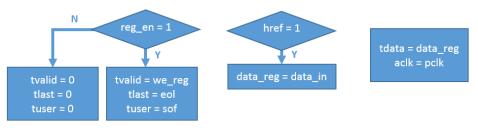

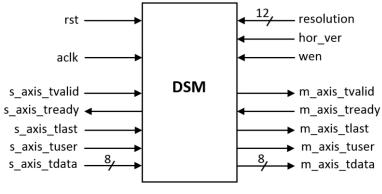

| Figure 4.8 DSM block interface                                                                        | 52   |

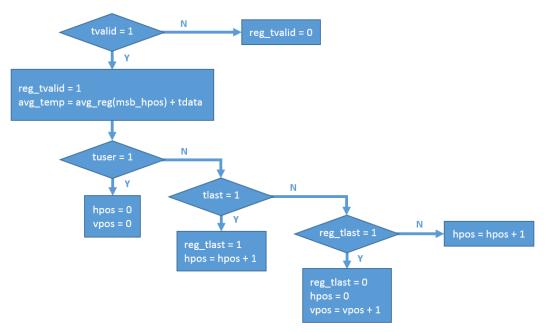

| Figure 4.9 DSM pixel position and data input accumulation functionalities                             | 54   |

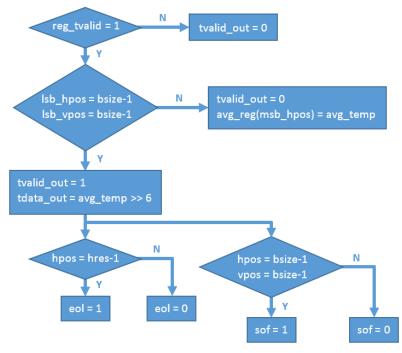

| Figure 4.10 DSM eol, sof, average division and output assignment                                      | 55   |

| Figure 4.11 BUSM-BSM-THM block interface                                                              | 56   |

| Figure 4.12 BUSM-BSM-THM sof initialization and valid input operation                                 | 57   |

| Figure 4.13 BUSM-BSM-THM Current background and new background memory distribution                    | 58   |

| Figure 4.14 BUSM-BSM-THM Computation of background subtraction, thresholding and new                  |      |

| background                                                                                            | 59   |

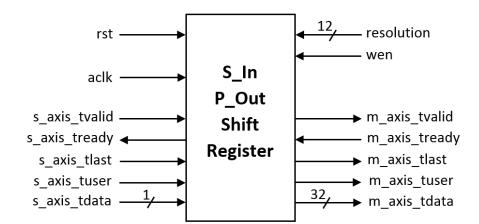

| Figure 4.15 1-bit Serial-In to 32-bit Parallel-Out Shift Register block interface                     | 60   |

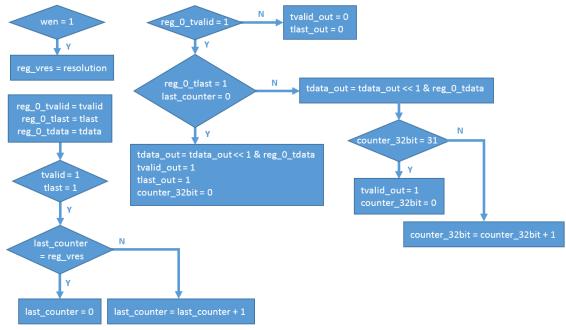

| Figure 4.16 1-bit Serial-In to 32-bit Parallel-Out Shift Register functionalities block diagram       | 61   |

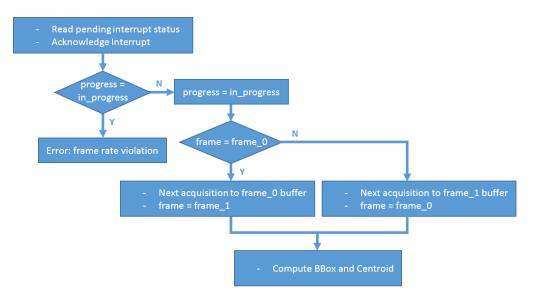

| Figure 4.17 Frame acquisition block diagram (DMA Interrupt handler)                                   | 68   |

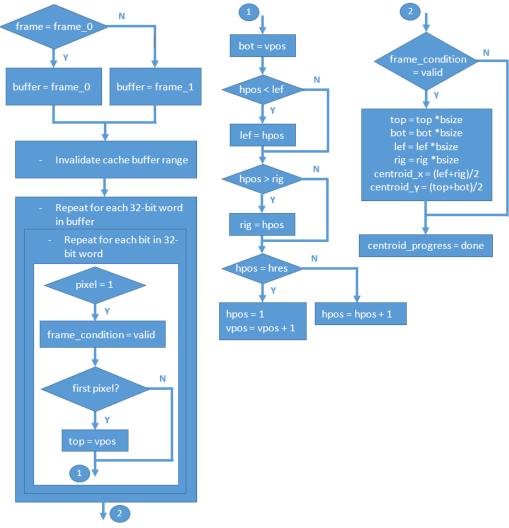

| Figure 4.18 Bounding box and centroid computation                                                     | 69   |

| Figure 4.19 Depth computing block                                                                     |      |

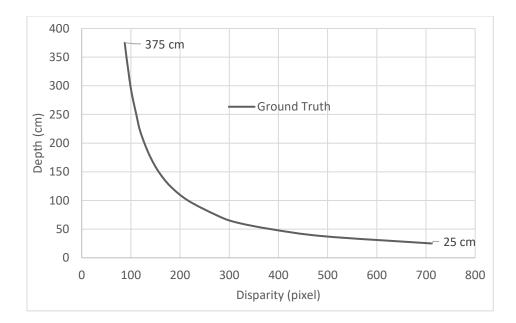

| Figure 4.20 Disparity/Depth ground truth curve built from the extracted reference points              | 74   |

| Figure 4.21 Disparity/Depth model over ground truth                                                   | 75   |

| Figure 4.22 Relation Disparity/Depth Error Range                                                      |      |

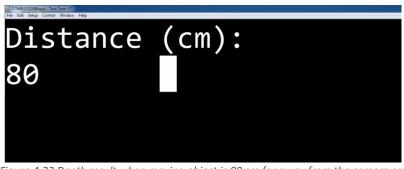

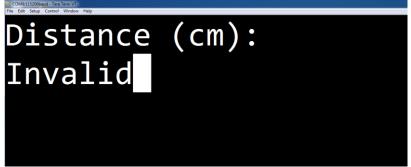

| Figure 4.23 Depth result when moving object is 80 cm far away from the camera set                     | 77   |

| Figure 4.24 Invalid depth result                                                                      | 77   |

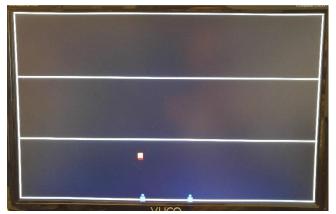

| Figure 4.25 Display for visual performance measurement and debugging                                  | 78   |

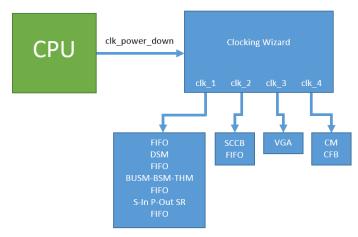

| Figure 4.26 Clock Power Down Control Diagram                                                          | 79   |

### Chapter I Introduction

From the beginning of the creation of digital images, one of the main goals of research has been to extract useful information from images, starting from enhancing the quality of the projection, to object detection, recognition, segmentation, and object tracking which was first done in two dimensions, and soon after in three dimensions as well.

Through decades, there has been a significant interest in depth information to be able to incorporate a third dimension to tracking systems, thus a complete vision of a scene is obtained. Observing the way humans and animals solve this challenge, the main general algorithm of using two different views of a scene in order to be able to extract the depth information was generated. Several methods and algorithms, generally known as computer vision, have been developed based on this concept. Some of these algorithms are more complex than others according to their specifications and objectives. For example, approaches to determine the depth map or depth information of an entire scene are highly complex since they give more information. On the other hand, algorithms based only on features of a specific object being tracked are simpler.

#### 1.1 Motivation

Nowadays, with the increase of autonomy in the automobile industry, robotics, and security detecting, locating, and tracking objects in three dimensional scenes is becoming a common feature of most products. In the automotive industry, for instance, car development is heading towards autonomous emergency breaking systems, as well as the autonomous feature of following the vehicle in front, which, in both cases, involves recognizing shapes and keeping certain distance from them. In robotics, this technology is also used to avoid obstacles, as well as in the guidance of a caravan of several units. In this case, the first unit is the only one that has to

be guided. In security, for example, a stereo camera set can detect the distance of an approaching object, and set off alarms when a specified distance is reached.

The main motivation behind this work is that, given the significance of the application of this technology currently, it is extremely important to design systems for implementation and verification in order to explore and evaluate their variants, issues, drawbacks, and best solutions from all possible approaches depending on the target application, and its specifications and constraints.

#### 1.2 Objectives

The general goal of this work is to implement a system able to perform the application of detecting, locating and tracking a moving object in a three dimensional scene, targeting its depth information. More specifically, the implemented system should be able to locate a moving object in the proximities in front of it. Another objective is to choose the platform and algorithms that allow the system to perform at the resolution 720p at 30 frames per second, and depth error no greater than  $\pm 4$  cm. Finally, the last goal is to include the design of a verification platform as well.

#### 1.3 Stages

Accomplishing the general goal of this work sets a set of specific tasks or stages to be followed. These tasks are related to the specific objectives of this work such as detecting the moving object in the scene, locating the centroid of the object which is the reference point from which the object is tracked, and computing the object depth information. The stages are these:

1. A research on algorithms for detecting movement in a scene has to be done, including the platforms needed for achieving this goal.

2

- 2. Once the moving area is detected, other algorithms are needed to create a reference point or centroid. Therefore, more research on algorithms has to be done for this purpose.

- 3. At this point, the object is located in the two dimensional space, the horizontal and vertical, which brings the challenge of studying the methods and approaches for computing the third dimension, depth or distance, from the system to the centroid.

- 4. After studying the range of possible algorithms and platforms, the next step is to choose the proper ones to achieve the objectives with more detailed specifications and constraints.

- 5. The following step is to design the system from a high synthesis level, partitioning it into hardware and firmware components. This step requires analyzing the design in terms of which portions are either computationally intensive or algorithmically intensive, so the first ones are implemented in hardware and the second ones as firmware.

- 6. Each component needs to be designed according to its functionality, data structure and interface.

- 7. Finally, the last step is to implement and verify the full design on the hardware and software target platforms.

#### 1.4 Original contribution

This work consists of designing, implementing and verifying a solution to target a specific application. Therefore, its original contribution is described as follows:

1. The research of suitable algorithms and target platforms to solve the application problem.

- 2. Several solutions and approaches from the wide range of algorithms and methods in the literature are analyzed in order to determine the most appropriate ones to meet the specified objectives.

- In addition, this work also presents an original design of the methods and algorithms selected, specifically oriented to the selected platform and application to meet its specifications and constraints.

- 4. Finally, this project also designs and implements original verification methods to analyze the results of the proposed solution in terms of performance and accuracy.

#### 1.5 Organization

Chapter 2 provides a brief overview of some of the algorithms and technologies available and currently in research for developing a stereo vision system capable of locating and tracking a moving object in a 3D scene. It presents a review of algorithms for detecting and segmenting the moving object in static and dynamic backgrounds. From the wide range of existing methods for this purpose, the recursive filter of first order and PBAS are described. Furthermore, regarding object tracking, this chapter explains the effective Kalman Filter algorithm. In addition to this, for depth estimation, the approaches based on correlation and feature detection are reviewed. From the correlation methods, the SGM is comprehensively described as well.

Chapter 3 is the first stage of the system design, where the suitable algorithms are selected and the system is partitioned according to the complexity of the selected algorithms. The general architecture is proposed, including the general blocks to capture the frames, detect and track the moving object, and compute the depth. The hardware and software architecture is described after partitioning the system. In general, a detailed plan of the system design is explained in this chapter.

Chapter 4 describes the details of the actual design, including its implementation and verification. This chapter begins with the specifications and the selection of the target platform. According to the specifications, the camera module is also selected, and its interface and features are explained. The hardware blocks are presented in detail one by one through their interface, algorithms and functionalities, data structure and data flow, and resources utilization. The software portion of the design is also described in this chapter, including initialization, configuration, and constraint verification. The results of this work are all presented in this chapter.

Finally, chapter 5 provides a summary and some conclusions of the work, and highlights potential areas for future research.

### Chapter II Background

#### 2.1 Introduction

Several studies have been developed using different approaches to estimate the position of specific objects in a scene, and keep track of their trajectory. Recent studies have included stereo vision platforms and algorithms to estimate the depth of the object as well.

Applications such as visual surveillance, traffic monitoring, vehicle tracking, autonomous navigation, aerospace, and computer vision have the basic requirement of identifying objects and locate them in a scene in real time. For this purpose, there is a wide range of algorithms, from general ones with great accuracy but slow and very expensive in resources utilization, to others with high speed and frame rate, inexpensive and accurate enough for the purpose of this specific application.

This chapter overviews current algorithms and tools to carry out a complete positioning and tracking system for moving objects, such as stereo vision for the depth estimation, camera set calibration, moving object detection algorithms, as well as object tracking algorithms.

#### 2.2 Related Work

*Stereo Disparity*: Disparity computation algorithms are usually classified in two groups. The first group comprises the most general approaches, which are based on the estimation of the disparity map by correlation-based methods. The second group includes algorithms that compute the disparity of the desired pixel only by mean of feature-based methods. The Feature-based method is commonly applied on object detection/tracking algorithms on both paired images, usually looking for pre-determined image characteristics such as object's centroids, contours, edges and corners.

*Correlation-based* algorithms essentially find the correspondence of the pixels from one image on the other image by correlating their similarities. Implementing them requires the application of correlation matching methods like SAD (Sum of Absolute Differences), SSD (Sum of Square Differences) and CC (Cross-Correlation). Using these methods is very expensive computationally since the matching has to be executed several times, depending on the maximum intrinsic disparity in the stereo camera platform, which implies high latency and longer cycle times. However, it can be fully pipelined and parallelized, but the use of resources highly increases.

The correlation-based algorithms may be classified as global and local [1]. Global methods exploit various techniques of global optimization of the whole disparity maps, while local methods provide the disparity maps using local optimization of the disparity map around a pixel only.

Global methods include graph cuts technique and belief propagation technique. These contemporary algorithms provide relatively smooth disparity maps. Unfortunately, these methods are highly complex and expensive in terms of resources. They need significant processing power as well as large memory volume. Consequently, the real-time implementations of these methods are subject to extensive research.

These computational demands produce significant problems in mobile implementations. For example, belief-propagation algorithm [2], used for depth estimation with VGA (640×480) resolution and 32 considered levels of disparities, might require as much as 80MB of space for message passing cache. Another more recent global approach is presented in [3], a sequential tree-reweighted message passing (TRW-S) that can be implemented in hardware and at the same time has reliable convergence achieving 22.8 fps for QVGA.

7

On the other hand, local methods use various types of block matching in order to find the disparity for each pixel independently. Large number of independent block matching allows for massive parallelization of the local disparity estimation algorithms. This enables the usage of even larger blocks (e.g. 35×35 pixels), which mostly provides disparity maps that are better compared to those obtained using small blocks. Unfortunately, large blocks are also very expensive computationally. Hence, the local methods with large blocks are implementable in real-time using the previously mentioned parallelization.

An interesting approach [1] proposes a depth estimation method that would have the advantages of both local and global methods. It uses small-block matching and analyzes estimated disparity values to enhance spatial consistency of the output disparity map. This work achieved very good results, but for resolution 320x240 with only 32 disparity levels. Others like [4,5,6] applied Semi-Global Matching (SGM) methods by Census Transform and Hamming Distance as main matching approaches.

In the work presented in [7], a Guided Image Filter (GIF) is proposed to reduce the complexity of the cost aggregation step, in local Adaptive Support Weight (ADSW) algorithms, for results in the HD video quality 1280x720 at 60 fps implemented on a Kintex-7 FPGA (Field Programmable Gate Array).

On the other hand, more specific approaches to determine the position of a given object in the scene, such as *feature-based algorithms*, can be used as well with very effective results; it all depends on the characteristics of the application. For example, in [8], OpenCV library is used to track up to 8 specific bicolor targets attached to the objects, and then determine their center coordinates per camera. The difference between the two coordinates is the disparity of the particular object. A more sophisticated approach is presented in [9], where Histograms of Oriented Gradients (HOG) is applied to detect vehicles on the road. Again, this is based on the same idea of creating a blob of the detected object, and then computing the centroid on each camera. Another feature-based method was implemented in [10] by using background subtraction to segment a moving object, and then determine its center of mass as centroid.

The relationship between the disparity and the distance of the object in the scene depends on parameters defined by the geometry of the stereo set, which must be known and remain unchanged for the duration of the image pairs acquisition. Assuming that the two camera planes are perfectly parallel simplifies the algorithm of knowing disparity-depth relationship.

However, even when the camera set is precisely built, the two camera planes will not be perfectly parallel. Moreover, the lenses induce distortions to each camera individually. To overcome these issues, a calibration process is required. Some works such as [8,9] perform calibration to adjust the individual camera distortion, as well as the camera planes, as a preprocessing algorithm using OpenCV and Matlab, respectively. This calibration makes the postdisparity processing easier by increasing delay and computation expenses at the pre-processing stage.

Other works such as [10,11] propose taking several reference points to create a curve of disparity over distance. After obtaining the curve that best fits the experimental data, they are able to create a calibration post-processing function that has to be computed only once per frame. This last aspect confers a great advantage to this approach.

Another interesting method is presented in [12], where both pre-calibration as well as post-calibration stages are applied to increase the accuracy of the system.

Moving Object Detection and Tracking: Robust object detection and tracking are important components of many real world image processing and analysis systems. There are

9

countless applications in which these algorithms are needed, among them, autonomous guided vehicles, automated video surveillance systems and video traffic monitoring. For this section of the discussion, there are several related works as well. In [13], background subtraction was applied along with Canny edge detection to detect the boundaries of the object. In this case the background was known and static. A similar approach but using Sobel is presented in [14] and in [15] without applying any edge detection filter.

The challenge in this case is that in many real world applications the background elements may not be static. In such cases, naive approaches like subtracting current frame and background image followed by thresholding are not enough to obtain accurate outcomes. On the other hand, false so-called "ghosts" may occur when an object stops moving. In this case, the object becomes part of the background and when it starts moving again is not detected.

A recent approach, presented in [16], addresses this issue by offering an algorithm for dynamic background for object detection based on recursive filter of first order real-time updating background. To track the object, they applied Kalman filter so the trajectory is smoother.

Others such as [17] implemented a Pixel-Based adaptive Segmenter (PBAS) foreground object detection algorithm, classified as multi-variant. This method combines the advantages of both recursive and non-recursive approaches. PBAS consists of creating a background model of N samples. What makes these algorithms different to any typical buffer method is that the relationship between the samples is not relevant.

The challenge of handling small objects in complicated non-flat scenes is targeted in [18] with a more complex algorithm. In this paper, the authors present a robust method to effectively segment moving objects from a moving platform. They propose two-level registration to

10

estimate and compensate the camera motion. Then, to extract the potential foreground, they apply Gaussian mixture model. They also present the application of Hidden Markov Model (HMM) to classify the pixels. Finally, foreground objects are tracked by a particle filter to improve the detection accuracy.

#### 2.3 Theory

This section reviews the most frequently used approaches for locating and tracking moving objects in a scene, with the particular inclusion of the depth estimation.

#### 2.3.1 Stereo Vision System

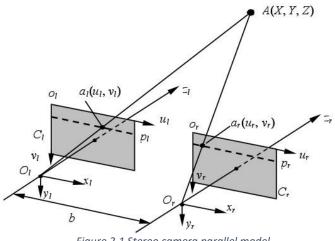

In stereo vision, the distance from the object to the stereo camera set is computed by obtaining the disparity, which is the difference of the projected points on the two stereo images, and then applying trigonometry [6,10,19,20]. Using a general configuration of a camera set, where the cameras can be in any position with respect to each other, the equation system to solve the depth from the disparity is very complex. For this reason, it is preferable to establish some conditions in the design of the set of cameras, so the computation complexity decreases. Setting two identical cameras at the exact same high and with their image planes perfectly parallel allows us to measure the distance of the object by using the parallel equation related to the distance information. In such a case, the geometry parameters of the stereo system can be modeled as presented in Figure 2.1.

Each image plane (u, v) is perpendicular to the *z* axis and parallel to the *x*, *y* coordination system plane. *Ol* and *Or* are the centers of projection of each camera, and *b* is the distance between them. *A* is an object represented by only one point in the world at (X, Y, Z). The plane created by *b*, *Ol*, *Or* and *A* is called epipolar plane, which intersects the image planes

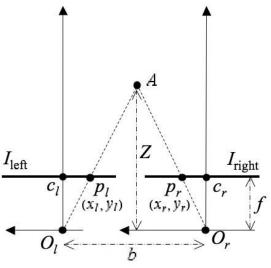

in lines called epipolar lines. In this particular case we are meeting the epipolar constraint as the two epipolar lines are parallel as well as the scan lines in each image plane. Meeting this constraint greatly benefits the algorithm, because it considerably reduces the search area to a single horizontal line. In Figure 2.2, the distance from the object A to the center of projection plane is denoted by Z.

Figure 2.1 Stereo camera parallel model

Via similar triangles, where one triangle is formed by (A, pl, pr) and the other one by (A, 0l, 0r), equation (2.1) below can be obtained, where xl and xr are the distances from the center of the image to the object projection. Let us say (xl - xr) is the disparity d. Then after rearranging and simplifying we can obtain (2.2). The conversion model of xl and xr from the image coordinate system to pixels can be obtained from the parameters of each camera model after calibration.

Figure 2.2 Triangulation model

$$\frac{b}{Z} = \frac{b+xl-xr}{Z-f}$$

(2.1)

$$Z = f\frac{b}{d}$$

(2.2)

#### 2.3.2 Rectification and Calibration

Usually, due to lens distortion or camera misalignment the epipolar lines are not parallel to the baseline, failing to meet the epipolar constraint. Therefore, equation (2.2) cannot be applied to compute the depth from the disparity. There are two general problems related to stereo vision set calibration: the first one emerges from having the individual cameras not calibrated, and the other one from having the stereo set not calibrated to meet the epipolar constraint. If the individual cameras are not calibrated, the problem is that the ground truth disparity for a specific depth may not be constant through the entire image due to the individual distortion on each camera. When the camera set does not meet the epipolar constraint, the depth cannot be calculated by using the equation (2.2); therefore, a more complex method has to be applied to compute the triangulation.

These issues can be solved through a rectification process, which uses the parameters of each camera to undistort each image, and then, the parameters from the stereo camera set to rectify the images planes [5,6,8,12]. These parameters are predetermined by a calibration process, in which a regression method is used to determine the distortion of a predefined pattern, usually a checkerboard. The process of rectification is a series of rotations, translations and scaling.

There are several tools, such as Matlab and OpenCV, to generate and apply the calibration parameters of individual cameras and stereo set. The process of applying this transformation to the incoming video stream is very complex and demands high computational power; hence, it is a factor that truly affects the performance of the system.

For systems based on correlation matching, this pre-processing rectification-calibration stage is critical. First, it simplifies the matching computation. Second, the better the calibration is the more accurate the disparity map will be.

On the other hand, for feature-based systems there are other alternatives because the depth computation is just over a few points on the image. One of the alternatives for overcoming the epipolar constraint is the offline generation of the relationship between disparity and depth proposed by [10,11], for instance. This mechanism generates a curve from several reference points, which relates the disparity to depth. For this approach to be effective, it is required as many reference points as possible across the entire z-axis. This approach allows to generate two possible models: one depending only on disparity (better for systems with at least undistorted images), and another one depending on disparity, x and y (for systems without any kind of

calibration). The second model is more accurate, because it addresses each camera distortion and the epipolar constraint issue, but for the same reason it is also more complex.

Generating these models requires a tool such as Matlab along with a curve fitting tool or algorithm such as least-square. The reference points may be automatically detected from the images using a similar checkerboard pattern and a feature detection algorithm. The application of this type of calibration is performed after the disparity calculation, which infers that there should be enough time to compute the distance until the next feature is detected and the next disparity is ready.

#### 2.3.3 Correlation-Based Algorithm

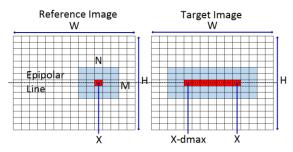

Local approaches compute the matching cost just by aggregating neighbouring pixels for each disparity candidate. These neighbouring pixels are determined by a so-called support window, as shown in Figure 2.3. In the reference image, the support window is located centered on point x, while in the target image, there are dmax support windows centered on points from x - dmax to x respectively [20]. As previously mentioned, cost aggregation functions are several from SAD, SSD, and CC to more hardware optimized versions like Census Transform and Hamming Distance. Then, after computing the aggregated cost of all the possible disparities of each pixel, the best disparity of each pixel is determined by the disparity with the best aggregated cost.

Figure 2.3 Support windows on reference and target image

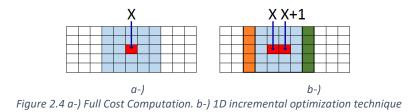

The number of operations in the local method can be dramatically reduced by optimizing the cost aggregation applying incremental techniques. The full cost aggregation for one disparity candidate requires the accumulation of the cost of all the neighbouring pixels, as presented in Figure 2.4.a. However, in Figure 2.4.b, 1D incremental optimization technique [21] is applied, reducing the computation of the cost aggregation of pixel x + 1, just by updating the previous cost aggregation of x by adding the costs in green and subtracting the costs in orange, which means adding the new column of the support window and subtracting the last column that is not part of the supporting window anymore.

Adapting weight algorithms aggregate costs according to weights assigned by examining the image content [21]. The accumulation of costs of the support window depends on weights, that put more relevance in some points than in others. For instance, one common method is inspired by bilateral filtering, where points with similar magnitude to the central point have more influence in the overall cost. Another characteristic is that points closer to the central point have also more significance.

Correlation methods with support window implicitly assume that all pixels within the windows have the same distance from the camera. Abrupt changes in depth discontinuity result in wrong correspondence calculation, thus in random disparity outcomes. Matching wrong content near depth discontinuities brings severe correlation errors, particularly for NCC. Consequently, SSD is used more often. In addition, SSD decreases errors due to matching non-

corresponding pixels. Other non-parametric cost functions such as Rank and Census also reduce this problem. Adapting the size and shape of the window can also diminish this problem. Ultimately, a real solution is only possible by matching pixels individually instead of matching windows.

*Global Matching* approaches use the entire image content to generate the correspondences by applying individual pixel correlation and smoothness constraints that penalizes discontinuities. The general global approach is commonly formulated as in (2.3).

$$E(D) = \sum_{p} \left\{ C(p, D_{p}) + \sum_{q \in N_{p}} PT[|D_{p} - D_{q}| \ge 1] \right\}$$

(2.3)

The first term adds all pixels matching costs over the entire image, while the second term introduces a penalty for all pixels with neighbours that have a different disparity. Consequently, discontinuities are permitted only when the matching is stronger than the penalty. The disparity image D is solved by minimizing (2.1). As this is a nondeterministic polynomial (NP) problem, many approximate solutions have been developed such as Graph Cuts and Belief Propagation, but they still have the drawback of low speed and memory consumption.

*Semi-Global Matching* [5,6,22] effectively combines ideas of global and local algorithms for accurate pixel-wise matching at low runtime. The first SGM implementations used Mutual Information (MI), which is very suitable for unrectified images, because the transformations are irrelevant when only individual pixels are considered. The results of MI degrade with increasing local radiometric differences caused by shadows, for example. Furthermore, it does not scale well with increasing radiometric depth.

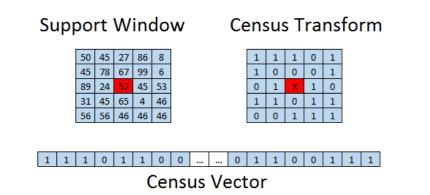

As an alternative, Census is identified as the most robust matching cost function for stereo vision. Census maps a support window surrounding the pixel in calculation, creating a vector that only scores if the compared pixel has a lower value than the center pixel. See Figure 2.5 for an example of a transformation [4,20].

Figure 2.5 Census transformation

Then, the matching cost is computed by the Hamming Distance of the bit vectors of the corresponding pixels from each image. Hamming Distance represents the amount of bit positions that are respectively different from comparing the two vector of the same size. Figure 2.6 presents an example of this calculation, which is done by an *XOR* operation of the two vectors and then counting the amount of ones of the result.

Figure 2.6 Hamming Distance

The principle of Census makes it suitable for global and local radiometric changes. However, it is slightly inferior to MI, if there are only global radiometric changes, and better than MI, for local radiometric changes. The local radiometric changes are present in many realworld applications. *Pathwise Aggregation for SGM* effectively penalizes minor disparity steps as expressed by (2.4) [6].

$$E(D) = \sum_{p} \left\{ C(p, D_p) + \sum_{q \in N_p} P_1 T[|D_p - D_q| = 1] + \sum_{q \in N_p} P_2 T[|D_p - D_q| > 1] \right\}$$

(2.4)

The second term adds a constant penalty P1 for all pixels q in the neighbourhood  $N_p$  of p, for which the disparity slightly changes. It can be just 1 pixel. The third term adds a large penalty P2, for all larger disparity changes, where  $P2 \ge P1$ .

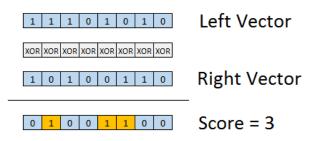

In order to avoid NP computation, which would be minimizing (2.4) in 2D, SGM brings a novel idea of computing along several paths, symmetrically from all directions. Usually 8 optimization paths are used. Figure 2.7 shows the 8 paths approach. The number of paths should be at least 8. Using 16 paths provides a good coverage as well.

Figure 2.7 Eight paths optimization

Equation (2.5), below, shows the cost path function. Lr(p, d) is the cost of the pixel p at disparity d, and C is the pixelwise matching cost that could be either Census Transformation or MI.

$$Lr(p,d) = C(p,d)$$

(2.5)

+ min  $(Lr(p-r,d), Lr(p-r,d-1) + P1, Lr(p-r,d+1)$

+ P1, min  $Lr(p-r,i) + P2) - min_k Lr(p-r,k)$

The second term computes the minimum over four values. The first one is the path cost at the previous pixel, at the same disparity, and without any penalty. The second and third values are the path cost at the previous pixel, with the next lower and higher disparity, and with a small penalty *P*1 added to them. The last value is the minimum cost at the previous pixel over all disparities, with the additional higher penalty *P*2. The last term subtracts the minimum path cost of the previous pixel from the whole value. This is an approach to limit the constant increase of *L*, keeping its value as  $L \leq Cmax + P2$ . The information from all the paths is combined for all the pixels and disparities by (2.6), and the disparity for each pixel corresponds to the minimum cost (2.7).

$$S(p,d) = \sum_{r} Lr(p,d)$$

(2.6)

$$D_L(p) = \underset{d}{\operatorname{argim}} S(p, d) \tag{2.7}$$

The pathwise cost solution does not handle occlusions. However, occlusions can be identified by computing the disparities separately in both directions, from left to right and from right to left, and comparing the results as a consistency check. Further post-processing steps are possible for cleaning up the disparity image. All the inconsistent disparities are set to invalid, also known as holes. Finally, a hole filling stage is required. This step can be performed by a weighted median filter, for example.

#### 2.3.4 Feature-Based Algorithm

Depending on the platform where the system will be implemented, it is sometimes too expensive performing either the lens distortion or the stereo system rectification to meet the epipolar constraint. For some other applications in which only a single object will be tracked, or even several objects, but all of them known, the feature-based approach is well known for its simplicity and less resources utilization.

In all computer vision system whose main objective is tracking objects by movement, shape, color, or specific features, there will be always a blob. Therefore, from the blob we can compute either the centroid or center of mass. By executing this method from both cameras, left and right simultaneously, it is possible to establish a correspondence between the relative positions of the object from both points of view, which is the definition of disparity [8,9,10].

#### 2.3.5 Moving Object Detection and Tracking

The proper determination of an object motion is significantly important in future stages of computer vision systems, such as object tracking, recognition, and path planning. The main algorithms can be classified in three groups based on the method that they apply. These three groups are background subtraction, temporal difference of successive frames, and optical flow.

Background subtraction is characterized by a simple pixel-by-pixel subtraction of a fixed reference frame or background, and the current frame, in order to determine the difference between them. The result difference is the area where the moving object is in the current frame. On the other hand, the temporal difference of successive frames has the same principle as the background subtraction algorithm, but in this case the reference is not fixed, it is updated from previous frames. Finally, the optical flow approaches are more complex because they analyze the dynamic scene from a stream in time, and generate a complete motion field of every pixel.

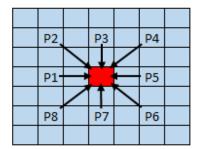

*Background subtraction*: can be generalized as shown in Figure 2.8, below, where the pre-processing stage could be any specific filter to target brightness changes due to camera exposure (poison noise), or just because of light changes in the scene. Well-known filters for this stage are the mean filter or the median filter.

Figure 2.8 Generalized Background Subtraction method

Each new frame after being pre-processed is subtracted from background. Then, in the segmentation stage, the result from the subtraction is compared to a threshold to create a binary image that contains the segmented object extracted from the background. This explanation is mathematically described by (2.8) below, where S(x, y, t) is the result segmented image,  $T_h$  is the predetermine threshold, F(x, y, t) is the current frame, and B(x, y) is the reference or background. In S(x, y), all pixels with value of '1' are considered as moving objects.

$$S(x, y, t) = \begin{cases} 1, & \text{if } |F(x, y, t) - B(x, y)| > T_h \\ 0, & \text{otherwise} \end{cases}$$

(2.8)

A stage of post-processing that targets the noise introduced in the segmented image comes after the segmentation. At that point, the object in the segmented image does not have well defined borders. There are also several small artefacts in the rest of the image S creating false detected objects. This noise is usually attacked with either erosion mode or median filter.

*Dynamic Background*: When scene changes can easily cause false positives results, such as tree branches moving by the wind, there are two effective methods to adequately update the background: the recursive filter of first order, and the PBAS algorithm.

The *recursive filter of first order* is described by (2.9), where  $I_{bk}(x, y)$ ,  $I_{bk-1}(x, y)$  and  $I_k(x, y)$  are the current background, the previous frame and the current frame, respectively, [16]. Term  $\alpha$  is the recursive coefficient, which establishes the background-updating rate and has a value between 0 and 1.

$$I_{bk}(x,y) = (1-\alpha)I_{bk-1}(x,y) + \alpha I_k(x,y)$$

(2.9)

When  $\alpha$  is large, the background adapts to changes rapidly. However, when  $\alpha$  is small, the system is more suitable for detecting slow velocity objects. When  $\alpha = 0$ , the new background will be equal to the previous one, then it will not be updated with the new frame. On the other hand, when  $\alpha = 1$ , the new background will be exactly equal to the new frame, keeping no information from the previous background.

In contrast, *PBAS*, see original articles [17,23], is a more complex algorithm that includes segmentation and background model update. As mentioned before, PBAS is a pixel-based algorithm. In general, the background model is based on a buffer of *N* samples recently observed from the video sequence  $B(x_i)$  as shown in (2.10). The update of this model is performed by random samples with the probability determined by  $T(x_i)$ , which will be defined later.

$$B(x_i) = \{B_1(x_i), \dots, B_k(x_i), \dots, B_N(x_i)\}$$

(2.10)

Pixel  $x_i$  is part of the background, when the distances between the value of the current pixel  $I(x_i)$  and at least Z amount of samples from the background  $B(x_i)$  are smaller than the threshold  $R(x_i)$ . Equation (2.11) describes the mathematical solution of this model. If F is 1, the pixel  $x_i$  is foreground, and background if 0. The distances are defined by the absolute values of the result of subtracting  $I(x_i)$  and each background pixel from  $B(x_i)$ .

$$F(x_i) = \begin{cases} 1, & \text{if } \sum_{k=0}^{N} \{ dist(I(x_i), B_k(x_i)) < R(x_i) \} < Z \\ 0, & \text{otherwise} \end{cases}$$

(2.11)

The *background model update* has to be performed to compensate the dynamic changes in the scene. There are two possible upgrading solutions: one liberal and the other one conservative. In the liberal one, all the pixels are updated, while in the conservative one only the ones marked as background are. The conservative method is more convenient because it avoids inclusion of foreground objects into the background model, which is the main disadvantage of the liberal method. However, the conservative method has its own particular problem, which is that once a pixel is updated as foreground, it will not be updated anymore, and therefore it will be stuck at that status forever. There is a solution that can be applied to prevent from getting this error, which is having a counter for the pixels marked as foreground, and then forcing an update once the counter reaches certain threshold. The update is done by, first, randomly selecting a sample from the background model  $B(x_i)$ , and then replacing it with the value of the pixel  $I(x_i)$ .

Updating the threshold  $R(x_i)$  is done dynamically, so the procedure adapts to the dynamics of the background. Having the measurement of the dynamic of the background is

based on the following procedure. First, whenever an update of the background model is executed, the minimum distance between  $I(x_i)$  and  $B(x_i)$  is saved in another array  $D(x_i) = \{D_1(x_i), ..., D_N(x_i)\}$ . Thus, a history of minimum distances is created for the pixel  $x_i$ . The mean of the values stored in  $D(x_i)$  defines  $\overline{d}_{min}(x_i)$  and the dynamic of the background. Therefore, the decision threshold is dynamically adapted according to (2.12). In [30], the parameters  $R_{\frac{inc}{dec}} = 0.05$  and  $R_{sc} = 5$  are set for a robust algorithm.

$$R(x_i) = \begin{cases} R(x_i)(1 - R_{inc}), & \text{if } R(x_i) > \bar{d}_{min}(x_i)R_{sc} \\ R(x_i) * (1 + R_{inc/dec}), & \text{otherwise} \end{cases}$$

(2.12)

The probability of updating the pixel  $x_i$  in the background model is given by (2.13), where  $T(x_i)$  is the parameter that adjusts this probability for each pixel.

$$p = 1/T(x_i) \tag{2.13}$$

Updating the learning rate  $T(x_i)$  is described by (2.14), where  $T_{inc} = 1$  and  $T_{dec} = 0.05$ .  $T(x_i)$  is also limited between 2 and 200 to avoid erroneous results in highly dynamic and fully static backgrounds.

$$T(x_i) = \begin{cases} T(x_i) + \frac{T_{inc}}{\bar{d}_{min}(x_i)}, & \text{if } F(x_i) = 1\\ T(x_i) - \frac{T_{dec}}{\bar{d}_{min}(x_i)}, & \text{if } F(x_i) = 0 \end{cases}$$

(2.14)

*Kalman Filter* is a very popular and effective mechanism for object tracking [24,25,26,27] that not only smoothens the tracking trajectory of the object, but also corrects

possible errors from the position measuring system or sensor. In addition, it adds the possibility of temporarily track the object in momentarily occlusions and sensor failures.

Its theory derives from the assumption that the state of a system at time t can be predicted from its previous state at time t-1 having the model of the entire system according to the equation (2.15).

$$X_t = F_t X_{t-1} + B_t u_t + w_t (2.15)$$

In the previous equation,  $X_t$  is the state vector,  $u_t$  is the control input vector,  $F_t$  is the state transition matrix that relates the states at time *t*-1, and *t*,  $B_t$  is the control input matrix, which applies the effect of the vector  $u_t$  on the state vector, and  $w_t$  is the process noise for the state vector derived from a multivariate normal distribution with covariance given by the matrix  $Q_t$ . Then, there is an observation or measurement model described by equation (2.16), where,  $Z_t$  is the vector of measurement,  $H_t$  is the transformation matrix that relates the state vector and the measurement, and  $v_t$  is the measurement noise derivative from Gaussian white noise with covariance  $R_t$ .

$$Z_t = H_t X_t + v_t \tag{2.16}$$

In case of one-dimensional tracking problem, the model gets the form of the motion equation (2.17). Here, the definitions are as follows:  $X_t = [X_t, V_t]$ , where  $X_t$  is tracked position and  $V_t$  is the speed of change. t - 1 represents the current state and t the predicted state,  $F_t =$

$\begin{bmatrix} 1 & \Delta t \\ 0 & 1 \end{bmatrix}$ ;  $B_t = \begin{bmatrix} \frac{(\Delta t)^2}{2} \\ \Delta t \end{bmatrix}$ , and  $u_t$  a scalar number that represents the relationship between the forces that move and break the object.

$$X_t = F_t X_{t-1} + B_t u_t \tag{2.17}$$

The algorithm is based on two main procedures: prediction, and measurement update. The prediction equations are (2.17) and (2.18), where  $Q_t$  is the noise covariance related to the noise in the control inputs. For this specific problem  $Q_t$  can be defined as (2.19), where the noise magnitude will just amplify the specified noise model.  $P_{t-1}$  is initially equal to  $Q_t$ .

$$P_t = F_t P_{t-1} F_t^T + Q_t (2.18)$$

$$Q_{t} = \begin{bmatrix} \frac{\Delta t^{4}}{4} & \frac{\Delta t^{3}}{2} \\ \frac{\Delta t^{3}}{2} & \Delta t^{2} \end{bmatrix} * noise\_magnitude$$

(2.19)

The next procedure is the measurement update. This process is given by the equations (2.20) and (2.21), where  $H_t = \begin{bmatrix} 1 & 0 \end{bmatrix}$  and  $K_t$  is the Kalman Gain. The Kalman Gain has to be updated before the measurement update process, which is before equations (2.20) and (2.21). It is represented by equation (2.22) below. In this example,  $R_t$  is a scalar number with the measurement noise amplitude.

$$X_t = X_{t-1} + K_t (Z_t - H_t X_{t-1})$$

(2.20)

$$P_t = P_{t-1} + K_t H_t P_{t-1} \tag{2.21}$$

$$K_t = P_{t-1} H_t^T (H_t P_{t-1} H_t^T + R_t)^{-1}$$

(2.22)

At every measurement we wish to know the best possible estimate of the location of the object, the information for computing the estimation is provided by two sources. First, the estimation is made from the last known position and speed, and second from the real

measurement of the position. Therefore, one cycle of steps to compute Kalman algorithm are prediction applying equations (2.17) and (2.18). Then, there is an intermediate step to update the Kalman Gain using equation (2.22). Finally, the measurement update step is done with equations (2.20) and (2.21).

#### 2.4 Summary

In this chapter, a general overview of algorithms and approaches for stereo vision, object detection, and object tracking applications was presented. In stereo vision applications, obtaining the depth information of the scene can be a highly computationally intensive process, demanding expensive resources. For this reason, choosing the right approach for the application is critical. In order to compute the depth information from a scene, the algorithms based on correlation are very accurate and effective, but at the same time highly computationally expensive. On the other hand, the feature-based algorithms are accurate and effective enough for some applications, with the advantage of being less complex, requiring less computational resources.

Another algorithm also reviewed in this chapter was the Background subtraction, which is a well known approach to detect moving objects. It can be combined with the recursive filter of first order as background update algorithm for targeting dynamic backgrounds with great results. Finally, the trajectory of the tracking object can be smoothened by applying the Kalman filter. Kalman algorithm also allows to decrease measurement errors created by noise.

### Chapter III System Architecture Development

#### 3.1 Introduction

In chapter I, the main objective of this work was defined as the implementation of a system able to perform the application of detecting, locating and tracking a moving object in a three dimensional scene. In order to achieve this general objective, the process was divided into different stages or tasks to be accomplished, such as detecting the moving object, computing its centroid, and then from the centroid calculating the depth. Still, all these steps are very general; therefore, in this chapter, they are described in detail. In addition, the selected algorithms to be used are described as well.

#### 3.2 General Architecture

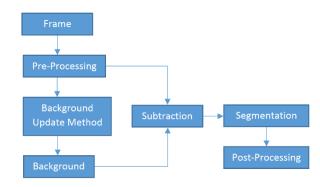

In every computer vision algorithm images are needed. Consequently, a camera is required in order to capture the scene and its changes. Figure 3.1 shows the block diagram of the general architecture to be designed for this project in order to build a system able to perform the required application.

Figure 3.1 General Architecture of proposed design

The first component to include in the system architecture is a Camera Module (CM) with the capability of streaming a video sequence taken from the scene in front of it. The CM outputs frame by frame the scene, allowing next modules to further analyze each frame. The Capture Frame Block (CFB) is a helper that understands the CM interface and converts the streaming frame into a regular interface for next modules.

After capturing a frame, it is required to extract the area that is moving or changing in it. That is the reason why Detect Moving Area Block (DMAB) is placed after the CM. This module is in charge of segmenting each frame. Through this process a segment of the frame is marked as static (no moving object in this segment), and the rest is marked as moving (moving object in this segment). The Compute Centroid of Moving Area (CCMA) computes the reference point of the moving segment. This way, the system is able to track the moving object always according to the same reference. In this work, the center of the moving area is selected as centroid. Following the analysis in chapter II, to extract the depth information from a scene it is required to have two different points of view of the same scene at the same time -this is known as stereo vision. Hence, the portion of the system described so far is reproduced to acquire the second view of the scene. As a consequence, the system is made of two separated channels of CM, CFB, DMAB and CCMA, one for the left view, and one for the right view. These two channels are connected to the Compute Disparity Module. This module calculates the difference between the two points of view of the same object, which is known as disparity. Having this disparity as input, the next module, Compute Depth, is able to determine the distance from the object to the center of the stereo camera set. The last block, Display Result, is for debugging and verification purposes.

# 3.3 Algorithm Selection and System Partitioning

#### 3.3.1 Hardware

# **Detecting moving area**

In order to detect the moving object, this work proposes the algorithm background subtraction. Background subtraction is simple to design and it does not require many resources, as it works locally on each pair of pixels. This method subtracts each pixel of the current background from the corresponding one of the new frame. This characteristic makes it suitable for processing on a streaming data structure. Then, it compares the absolute value of the difference with a threshold to create a binary image that segments both portions of the frame, the static one and the moving one. Background subtraction is also very effective with some pre-processing and post-processing filters.

One of the challenges to overcome when using Background subtraction is to exclude lighting changes in the scene, and poison noise from being segmented as moving area. That is why the mean filter is selected in this case. This work combines mean filter with downscaling of the frame to solve this issue as pre-processing module before Background subtraction. Downscaling the frame allows the system to store the background directly in internal memory, which is faster. As a result, this part of the algorithm can be implemented in hardware. Each frame is captured and then downscaled to 1/x of the resolution by the mean of all the pixels in squared regions determined by x. Figure 3.2 represents an example of downscaling to 1/8 by mean of 8x8 pixels blocks (64 pixels). In this case, each block of 8x8 pixels in the bigger image becomes 1 pixel in the small image. For an initial resolution of 640x480, the 1/8 scaled resolution is 80x60 pixels.

Figure 3.2 1/8 Down-Scale example by mean of 8x8 pixels blocks

Other small changes in the scene, known as Dynamic Background, are another important task to solve. A well-known recursive filter of first order background update is presented in this project to deal with this situation. As mentioned in chapter II, the recursive filter of first order background update is a pixel wise update algorithm. This feature makes it suitable for being implemented in hardware, as the involved operands per cycle are only the corresponding pixels of the new frame, and the current background frame already stored.

## 3.3.2 Software

# Centroid

Up until now, the design has created a binary image segmenting the area where there is movement. Subsequently, the centroid of this area has to be determined in order to track the target object. This project also has the objective of detecting multiple moving objects in future work. For this reason, the detection of centroids is left to be performed in software due to its complexity for multiple object detection. For the specific work presented here, the system only detects a single object. The extraction of the centroid of the object presented in this work consists in determining first the bounding box that delimits the object, and then the center of such box, which is the centroid. The bounding box is determined by four sides: top, bottom, left, and right, where top is the minimum Y pixel position segmented as moving object, bottom is the maximum Y, left is the minimum X and right is the maximum X. The centroid is then computed as expressed by equations (3.1) and (3.2).

$$Centroid_X = (left + right)/2$$

(3.1)

$$Centroid_Y = (top + bottom)/2$$

(3.2)

# Disparity

Once the system has calculated the centroid of the moving area from the two cameras, it calculates the disparity by determining the difference between the two centroids X coordinates. Being more specific about this calculation, a valid disparity is determined by (3.3). It is important to note that a valid disparity is when this difference is positive.

$$Disparity = Centroid_X_Left - Centroid_X_Right$$

(3.3)

This disparity value is known as the measured disparity, because it is calculated by processing the sensors, which are both, left and right, cameras. This measurement is not always perfect because it is subject to noise, either from the environment components or from the algorithm itself. That is the reason why an estimation approach on top of the measurement is considered in this work to compensate the noise and smoothen the tracking trajectory. The estimation approach is based on Kalman algorithm. This algorithm generally involves floating-point computation, update and storage of almost all the variables implicated in the algorithm, and

update of the estimation model. According to these characteristics, Kalman algorithm is more appropriate for being implemented in software.

# Depth

Depth computation is also a floating-point function based on the characteristics of the stereo vision camera set that is suitable for software as well. This function is a model that relates disparity to depth. This work determines the model of the stereo camera set offline. Taking pictures of several reference points where the distance is known, and then extracting the disparity for every reference point make possible to create the needed relationship function between disparity and depth. Afterwards, this information is entered in a math software tool to extract the function model.

# 3.4 Hardware Architecture

In this section, the hardware architecture is explained in more detail. Figure 3.3 represents a block diagram of the hardware architecture including all components proposed by this work to achieve its objectives. There are four main areas in this architecture: the algorithms implemented in hardware, a CPU (Central Processing Unit) platform to execute the software algorithms and configuration, the communication components between hardware and software, and finally verification components.

First, the two stereo channels, left and right, require to be configured. At the start-up of the system, the CM is initialized and configured by the CPU with the desired frame resolution, output format, and several other parameters. At any point of execution, the CPU is able to reset the system and reconfigure the CM with a different set of parameters. The CPU transmits the CM configuration commands to the hardware module SCCB (Serial Camera Control Bus) which is able to properly communicate with the CM using the SCCB standard protocol [28]. The output of the camera is connected to CFB. This module is also initialized and dynamically configured by the CPU with the frame resolution that the camera has been programmed. This block also has an enable signal connected to the CPU to either enable or disable the capturing process. When CFB switches from disable to enable, it waits for a valid start of frame to start capturing, this way the first frame is captured from its beginning. On the other hand, when it switches from enable to disable, it finishes capturing the entire frame it is currently on before stopping, again ensuring the full frame is acquired.

Figure 3.3 Hardware Architecture of proposed design

The CFB is connected to the Down-Scale Module (DSM), which is also configured by the CPU with the frame resolution the system is working with. According to the working resolution, this module is responsible for grabbing the frame coming from CFB and downscaling it 1/x of the resolution. First, the algorithm creates blocks of x by x pixels, and then computes the average of each block. Once it finishes with the full frame, it outputs the downscaled frame to the next module. The downscaled frame is then passed as input to the Background Update and Synchronization Module (BUSM). This particular module is initialized and reconfigured by the CPU with the update rate parameter of the recursive filter of first order background update ( $\alpha$ ). In order to avoid a floating point computation because  $0 < \alpha < 1$ , this work modifies the background update equation (2.9) from chapter II by transforming  $\alpha = \frac{1}{\beta}$ , where  $1 \le \beta \le max$ . Thus, the BUSM parameter is  $\beta$  instead. The modified representation is presented by the expression (3.4). In this case, when  $\beta$  is small, the background adapts to changes rapidly. On the other hand, when it is large, the system is more appropriate for objects moving slowly.

$$I_{bk}(x,y) = \frac{(\beta - 1)I_{bk-1}(x,y) + I_k(x,y)}{\beta}$$

(3.4)

The background storage elements have some intrinsic latency. This feature is the reason why the synchronization part of the module is intended to synchronize the incoming current frame pixel with its corresponding background pixel. This action requires some additional registers depending on the storage element latency.

BUSM is connected to Background Subtraction Module (BSM). A pair of corresponding pixels, background and current frame, are the input to BSM, which subtracts them and computes the absolute value of the result. Then, the Thresholding Module (THM) compares the absolute value with a programmable threshold configured by the CPU. THM segments the image frame into two parts: moving area and static area. Its output is a binary image. Both binary images, from left and right cameras, are pushed to external memory through DMA (Direct Memory Access) for further processing by the CPU.

As the images are binary, every pixel is one bit and DMA is able to transfer words of a predetermined size. Therefore, a serial-in parallel-out shift register is used to decrease the

amount of DMA transactions. The shift register accumulates the binary pixels into words of size equal to the DMA data bus size, decreasing the amount of transactions by that size.

Debugging, verification, performance, and accuracy measurement are very important aspects to implement in every design. As part of the experimental setup, a UART communication channel connected to a PC, as well as VGA capability connected to a monitor are added to the system prototype. The UART channel introduces debugging capabilities by setting checkpoints so all the components are properly configured, dynamic reconfiguration of the segmentation threshold, background update rate, and resolution. In addition, it allows measuring performance by setting extra checkpoints to make sure that the frame rate specification is met. Also, in terms of accuracy, the system is able to display the exact depth value that it computes, this way the result can be compared with the ground truth. VGA capability connected to a monitor is another way of performance verification by visualizing how fast and precise the trajectory of the object is updated.

# 3.5 Software Architecture

The software architecture includes the algorithmically intensive methods of the design, and it is divided into three main parts: initialization frame acquisition, and depth computing. In the initialization and start stages, the system configures for the first time all the components and sets all the variables, starts the system, and then enters in a loop executing compute depth block. Segmented frame acquisition is the block called when the DMA receives a segmented frame. This block initiates the reception of another frame and computes the bounding box and centroid of the received frame. Finally, compute depth block waits for the two frames, left and right, to be ready, which means received and calculated centroid. Then, it computes the measured disparity, the estimated disparity by Kalman algorithm, and depth, and finally shows the results.

#### 3.5.1 Initialization, start and operation block

Initialization is where the software algorithm starts. It starts off by configuring the general platform components as presented in Figure 3.4. The first component to be initialized is the UART communication with the PC to start debugging the system immediately. Right after, the DMA for left channel, and then the DMA for right channel are also configured. Then the system setups the interrupt controller, so the two DMA channels can interrupt when a full segmented frame is received. After the general components are initialized, the application specific components are configured as well. This part of the process begins by configuring the CM. The CPU writes the proper registers of the camera with the correct parameters. This way, it delivers the frames accordingly. The most important parameters that define the behaviour of the rest of the modules are the resolution and the output format. The CFB and DSM are also initialized with that same resolution. Then, the BUSM is also configured with the parameter background update rate according to the scene speed. Lastly, the software initializes the THM passing the segmentation threshold parameter to it.

After initializing and configuring the general platform and the application specific components, the system is ready to switch to operation mode. Starting the operation mode is done by enabling the CFB. Then the CFB starts capturing frames and passing them to the rest of the system. Once started, the application enters in a loop of depth computing and showing results. At this time, the block that computes the depth is called.

Figure 3.4 Software Architecture: Initialization, start and operation block

### 3.5.2 Segmented frame acquisition block

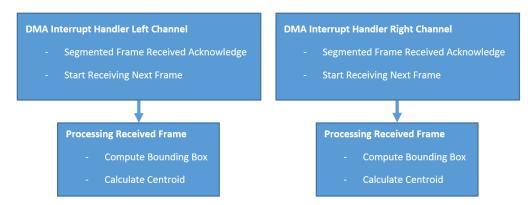

The segmented frame acquisition block has two main parts: the DMA interrupt handler, and, after it, a section to determine the bounding box and centroid. This block is repeated, as there are two acquisition channels, left and right. Figure 3.5 represents the segmented frame acquisition block. The DMA interrupt handler will be called when an entire segmented frame is received. Each channel invokes its own handler. Inside the interrupt handler, the application acknowledges receiving the frame, initializes the DMA channel to receive another frame, and calls the block for computing the bounding box and centroid. Once the bounding box and centroid are ready, it sets a flag for that channel to tell that it is ready for depth computing. The

block that computes depth is always waiting for these two flags to be ready to be able to go ahead and determine the depth from the left and right centroids.

Figure 3.5 Software Architecture: Segmented frame acquisition block, Left and Right Channels

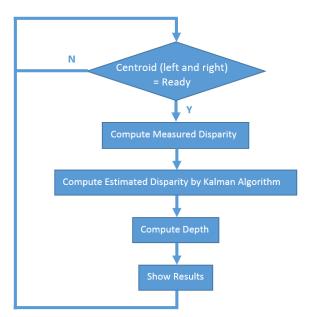

# 3.5.3 Compute depth block

The compute depth block is invoked after enabling CFB. Then, the application enters in a loop where it waits for both receiving channels' flags to be ready. Once they are both ready, the block computes the depth, shows the results, resets the flags, and returns back to waiting again. Figure 3.6 shows the block diagram of this portion of the application.