## **Ryerson University** Digital Commons @ Ryerson

Theses and dissertations

1-1-2008

## Network-On-Chip Topology Generation and Analysis For Transaction-Based Systems-on-Chip

Victor. Dumitriu Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Dumitriu, Victor., "Network-On-Chip Topology Generation and Analysis For Transaction-Based Systems-on-Chip" (2008). Theses and dissertations. Paper 1087.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

## NETWORK-ON-CHIP TOPOLOGY GENERATION AND ANALYSIS FOR TRANSACTION-BASED SYSTEMS-ON-CHIP

by

Victor Dumitriu Bachelor of Engineering Ryerson University, 2006

A thesis

presented to Ryerson University

in partial fulfilment of the

requirements for the degree of

Masters of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada ©Victor Dumitriu 2008

PROPERTY OF RYERSON UNIVERSITY LIBRARY I hereby declare that I am the sole author of this thesis or dissertation.

I authorize Ryerson University to lend this thesis or dissertation to other institutions or individuals for the purpose of scholarly research.

Victor Dumitriu

I further authorize Ryerson University to reproduce this thesis or dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Victor Dumițriu

## Network-on-Chip Topology Generation and Analysis for Transaction-Based Systems-on-Chip

Victor Dumitriu

Masters of Applied Science, 2008

Program of Electrical and Computer Engineering

Ryerson University

#### Abstract

The Network-on-Chip concept is emerging as a promising new method of addressing the communication requirements of complex Systems-on-Chip. However, network design at this level must take into consideration the specific communication protocols of on-chip components. This thesis presents a topology analysis and design method for networks-on-chip based on the transaction-oriented protocols common to on-chip systems. The generated topologies target the latency of critical links in the system, while the analysis method can predict the degree of contention in a system prior to the simulation phase. The proposed topologies are tested using various applications, including an MPEG4 Decoder, and are found to perform the same or better than regular topologies, while using less network resources. The contention prediction method is found to be accurate to within 27% in the worst case scenario.

## Acknowledgment

I would like to thank my supervisor, Dr. G. N. Khan, for his guidance and support throughout my masters studies. I also wish to acknowledge the financial support provided by the National Science and Engineering Research Council of Canada (NSERC), the Canadian Microsystems Corporation (CMC), and Ryerson University.

## Contents

| 1 | The      | esis Inti | roduction                                                   |

|---|----------|-----------|-------------------------------------------------------------|

|   | 1.1      |           | uction                                                      |

|   | 1.2      | Motiva    | tion and Contribution                                       |

|   | 1.3      | Thesis    | Organization                                                |

| 2 | Sys      | tems-o    | n-Chip: Characteristics and Methodologies                   |

|   | 2.1      | The Ri    | ise of the Systems-on-Chip Concept                          |

|   | 2.2      | Plug-a    | nd-Play System Design and Standard Interfaces               |

|   | 2.3      | (96)      | eteristics of On-Chip Communication                         |

|   |          |           | On-Chip Protocols                                           |

|   |          | 2.3.2     | On-Chip Communication Characteristics                       |

|   | 2.4      |           | sion                                                        |

| 3 | Net      | works-    | on-Chip 15                                                  |

| _ | 3.1      |           | rks on Chip: An Introduction                                |

|   |          | 3.1.1     | The XPipes NoC                                              |

|   |          | 3.1.2     | The Aethereal NoC                                           |

|   |          | 3.1.3     | Regular Topology NoCs                                       |

|   |          | 3.1.4     | The Asynchronous NoC: The MANGO Clock-less Network          |

|   |          | 3.1.5     | Commercial NoC Solutions: The Arteris Danube NoC Library 21 |

|   | 3.2      |           | esign Research                                              |

|   | 0.2      | 3.2.1     | XPipes-Related Design Methods                               |

|   |          | 3.2.2     | Tile-Oriented Design Methods                                |

|   |          | 3.2.3     | Irregular Topologies Based on Optimization Methods          |

|   |          | 3.2.4     | Additional Research Projects                                |

|   | 3.3      |           | sion                                                        |

| , | <b>T</b> |           |                                                             |

| 4 |          |           | n-Oriented NoC Design                                       |

|   | 4.1      |           | d Objectives                                                |

|   |          | 4.1.1     | Supported Network Type                                      |

|   | (3/8/22  | 4.1.2     | Method Input and Output                                     |

|   | 4.2      |           | l Program Structure                                         |

|   | 4.3      | Topolo    | gy Generation                                               |

|   |     | 4.3.1 Algorithm 1: Point-to-Point Oriented Topologies                    |

|---|-----|--------------------------------------------------------------------------|

|   |     | 4.3.2 Algorithm 2: Partitioned Crossbar Topologies                       |

|   |     | 4.3.3 Topology Comparison                                                |

|   |     | 4.3.4 Complexity of the Algorithms                                       |

|   |     | 4.3.5 Route Generation                                                   |

|   |     | 4.3.6 Deadlock-Free Characteristic                                       |

|   | 4.4 | Topology Analysis                                                        |

|   |     | 4.4.1 Theory                                                             |

|   |     | 4.4.2 Implementation                                                     |

|   | 4.5 | Method Limitations                                                       |

|   | 4.6 | Conclusion                                                               |

| 5 | No  | C Simulation Environment                                                 |

| J | 5.1 |                                                                          |

|   | 5.2 | Supported NoC System                                                     |

|   | 5.3 | Simulator Models                                                         |

|   | 0.0 | 5.3.1 Traffic Generators and Sinks                                       |

|   |     |                                                                          |

|   |     | 5.3.2 Network Interfaces                                                 |

|   |     | 5.3.4 Switches                                                           |

|   | 5.4 |                                                                          |

|   | 0.4 | Conclusion                                                               |

| 6 | Sim | ulations and Results                                                     |

|   | 6.1 | Test Applications                                                        |

|   | 6.2 | Topology Comparisons                                                     |

|   | 6.3 | Predictor Accuracy                                                       |

|   |     | 6.3.1 Poisson Transaction Patterns                                       |

|   |     | 6.3.2 Specified Transaction Patterns                                     |

|   | 6.4 | Program Execution Time                                                   |

|   | 6.5 | Topology Comparison                                                      |

|   | 6.6 | Message Passing Communication Model in Transaction Based Environments 13 |

|   | 6.7 | Conclusion                                                               |

| 7 | The | esis Conclusion 11                                                       |

117

8 Appendix

# List of Figures

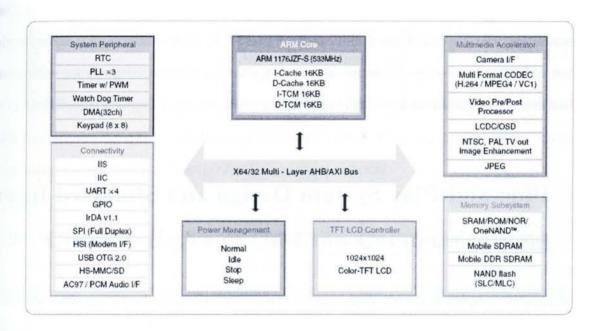

| 2.1  | Example of a Current-Generation SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

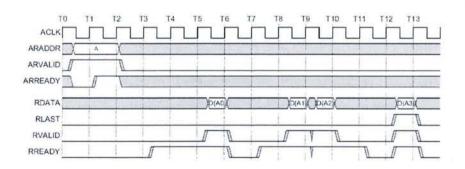

| 2.2  | AXI Read Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1(       |

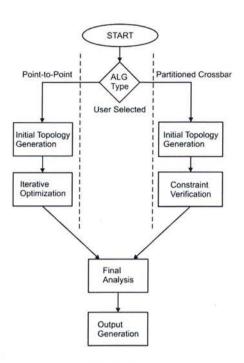

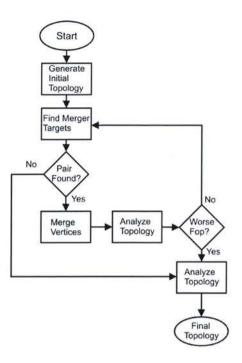

| 4.1  | Main Program Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44       |

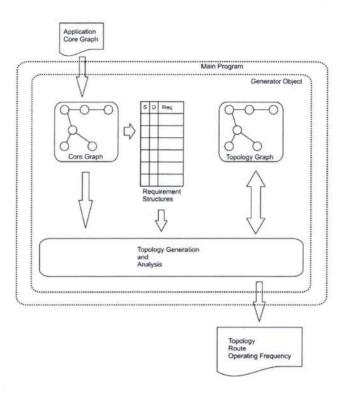

| 4.2  | Main Program Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45       |

| 4.3  | Point-to-Point Oriented Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48       |

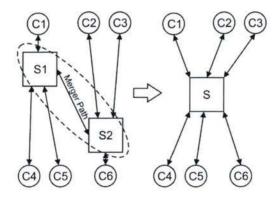

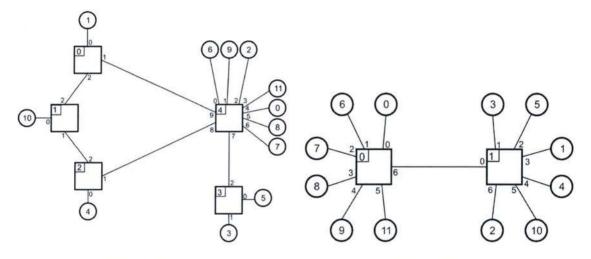

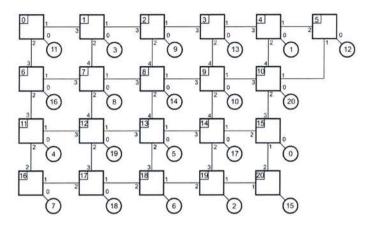

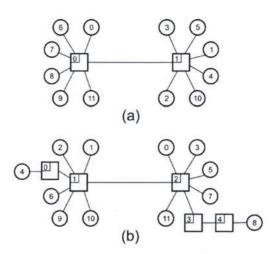

| 4.4  | Example of a Switch Merger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49       |

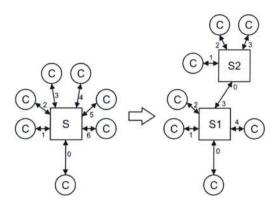

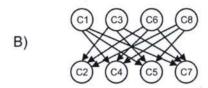

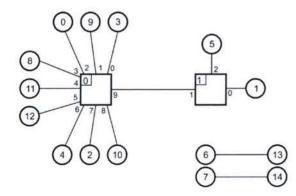

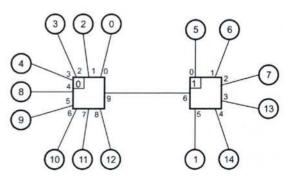

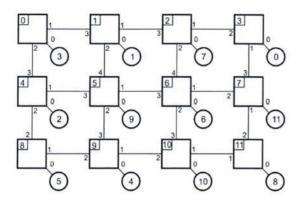

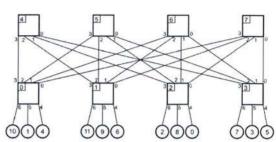

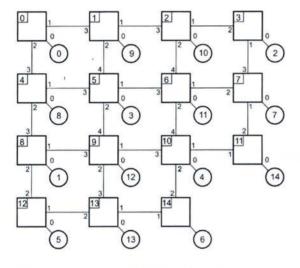

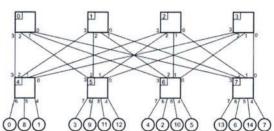

| 4.5  | Example of the Switch Partitioning Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52       |

| 4.6  | Channel Dependence Graph Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57       |

| 4.7  | Partitioning Effect on Channel Dependence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58       |

| 4.8  | Simplified Model Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64       |

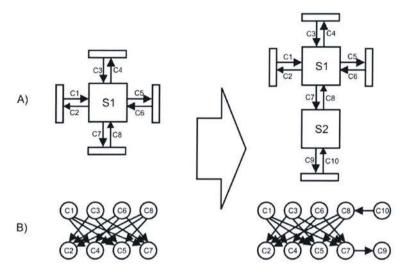

| 4.9  | Output Contention Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

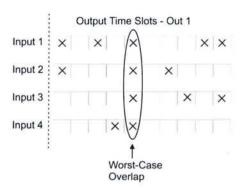

| 5.1  | Structure of Intended Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73       |

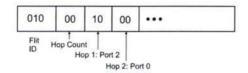

| 5.2  | Example of a 2-Hop Route                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75       |

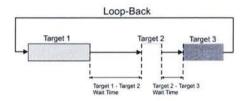

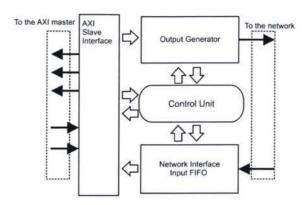

| 5.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78       |

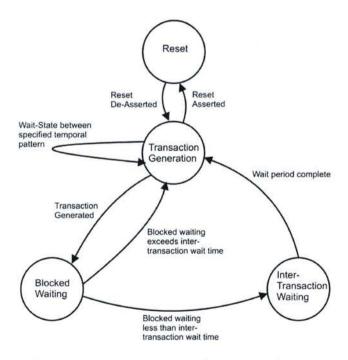

| 5.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80       |

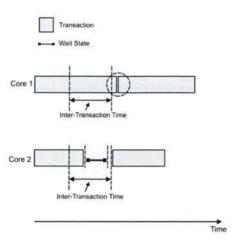

| 5.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83       |

| 5.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85       |

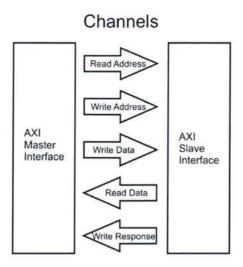

| 5.7  | AXI Channel Arrangement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87       |

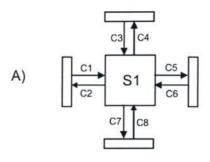

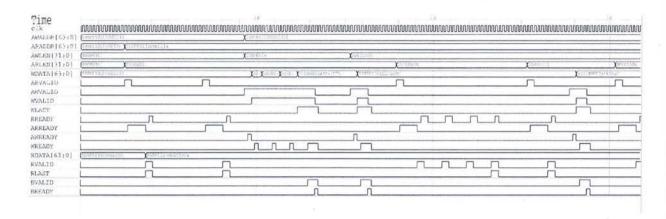

| 5.8  | AXI Implementation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88       |

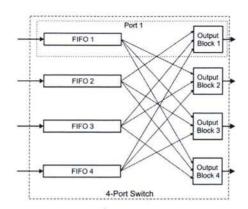

| 5.9  | 4-Port Switch Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89       |

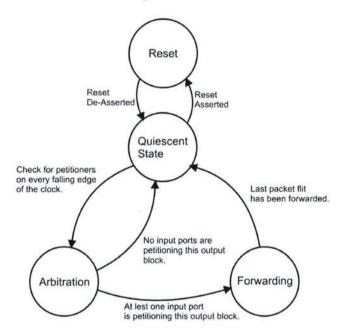

| 5.10 | Output Block State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90       |

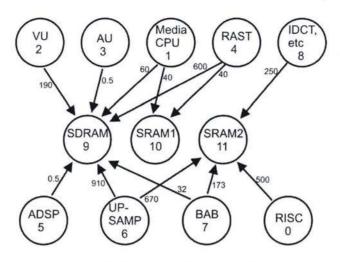

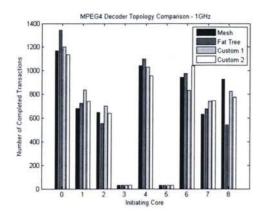

| 6.1  | MECA Deceder Comp (10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00       |

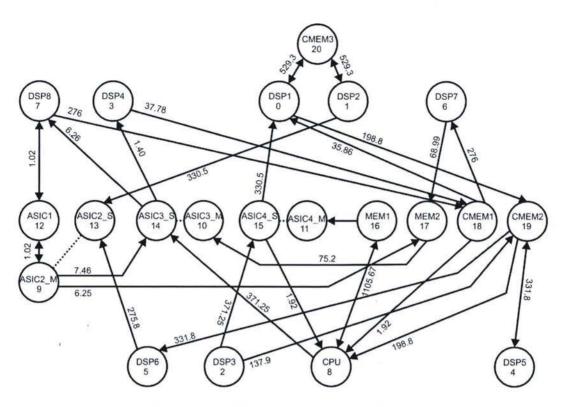

| 6.2  | - 기교장이 있어면 중인생과 "리아스 경기에는 그는 경기에는 대학에서 대학에서 비가에서 다른 이는 것은 것은 사는 것은 것은 것은 것은 것은 것은 것을 다른 것은 것은 것은 것은 것은 것은 것은 것                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93       |

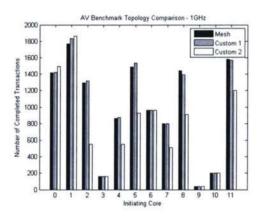

| 6.3  | * 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94       |

| 6.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95<br>96 |

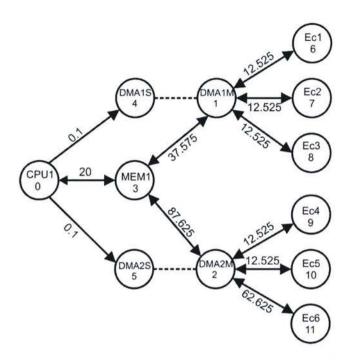

| 6.5  | THE PARTY OF THE PROPERTY OF THE PARTY OF TH | 90<br>97 |

| 6.6  | - "지기에는 지기에서 전혀 보면 가게 하면 하면 가게 되었다면 하는 것이 되었다면 하는 것이 되었다면 보다는 것이 되었는데 보고 있다는데 그리고 있다는데 보고 있다는데 그리고 있다면 되었다면 보다를 하는데 하는데 되었다면 보고 있다면 되었다면 되었다면 되었다면 보고 있다면 되었다면 보다면 보다면 보다면 보다면 보다면 보다면 보다면 보다면 보다면 보                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97<br>97 |

| 6.7  | - 뭐이가는 얼마나면 아니지 그리지 하면 하는 것 같은 아니라 없었다. 그 전화 부스로 아무씨는 그는 이번 경마를 보고 있는 것이다. 그는 것이다는 그는 것이다. 그는 것은 것이다.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97<br>97 |

| 6.8  | 1 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97<br>97 |

| 6.9  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97<br>98 |

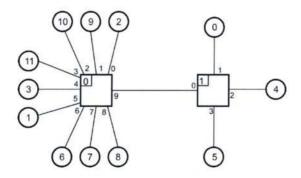

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98<br>98 |

| 0.10 | Av benchmark Custom z Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90       |

| 6.12 | MPEG4 Decoder Fat Tree Topology                                           |   |

|------|---------------------------------------------------------------------------|---|

| 6.13 | MWD Application Mesh Topology                                             |   |

| 6.14 | MWD Application Fat Tree Topology                                         |   |

|      | AV Benchmark Mesh Topology                                                | 1 |

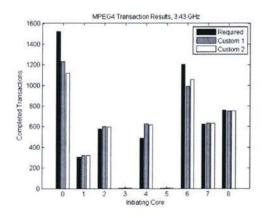

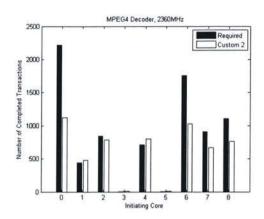

| 6.16 | MPEG4 Decoder Transaction Results                                         | 1 |

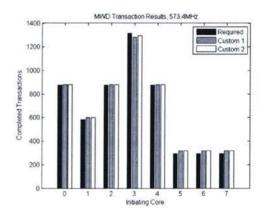

| 6.17 | MWD Application Transaction Results                                       | 1 |

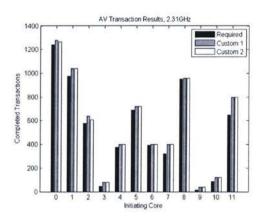

| 6.18 | AV Benchmark Transaction Results                                          | 1 |

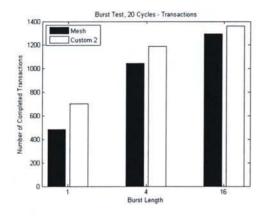

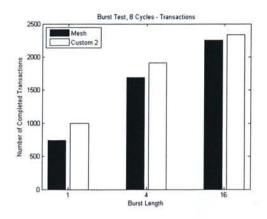

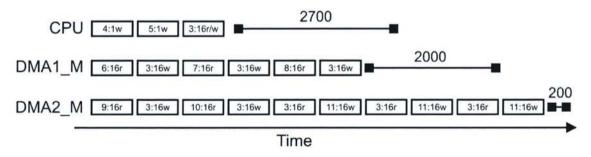

| 6.19 | MPEG4 Decoder Burst Test 1 - Transactions                                 | 1 |

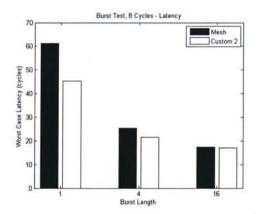

|      | MPEG4 Decoder Burst Test 1 - Latency                                      |   |

| 6.21 | MPEG4 Decoder Burst Test 2 - Transactions                                 | 1 |

| 6.22 | MPEG4 Decoder Burst Test 2 - Latency                                      | 1 |

| 6.23 | MPEG4 Decoder Analysis Accuracy Test                                      | 1 |

| 6.24 | MWD Application Analysis Accuracy Test                                    | 1 |

| 6.25 | AV Benchmark Analysis Accuracy Test                                       | 1 |

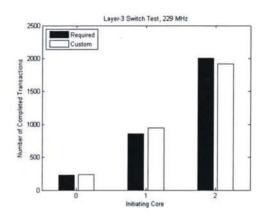

| 6.26 | Layer-3 Switch Custom Topology                                            | 1 |

| 6.27 | Layer-3 Switch Transaction Pattern                                        | 1 |

|      | Layer-3 Switch Accuracy Test                                              | 1 |

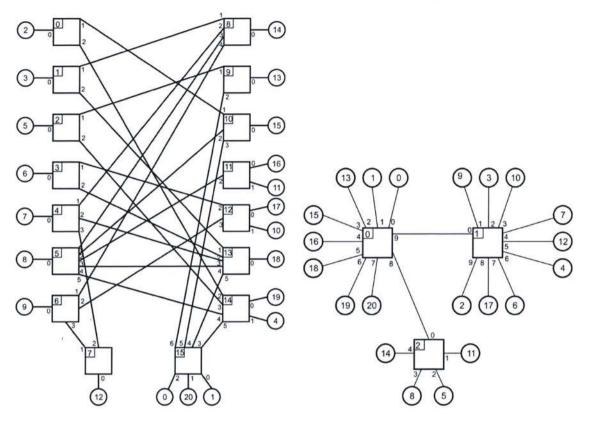

| 6.29 | Topology Comparison: (a) Partitioned Crossbar Topology; (b) Topology Gen- |   |

|      | erated by Srinivasan et al. Method [36]                                   | 1 |