#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2009

## High Level FPGA Implementation Of Adaptive Signal Segmentation And Autoregressive Modeling Techniques

Beibei. Jiao *Ryerson University*

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Jiao, Beibei., "High Level FPGA Implementation Of Adaptive Signal Segmentation And Autoregressive Modeling Techniques" (2009). *Theses and dissertations*. Paper 1136.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

## HIGH LEVEL FPGA IMPLEMENTATION OF ADAPTIVE SIGNAL SEGMENTATION AND AUTOREGRESSIVE MODELING TECHNIQUES

by

## Beibei Jiao

B.Eng., Wuhan University, P.R. China, 2004

#### A thesis

presented to Ryerson University in partial fulfillment of the requirement for the degree of Master of Applied Science in the Program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2009

© Beibei Jiao, 2009

PROPERTY OF RYERSON UNIVERSITY LIBRARY

#### Author's Declaration

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Signature

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Signature

#### Abstract

### HIGH LEVEL FPGA IMPLEMENTATION OF ADAPTIVE SIGNAL SEGMENTATION AND AUTOREGRESSIVE MODELING TECHNIQUES

#### Beibei Jiao

Master of Applied Science Department of Electrical and Computer Engineering Ryerson University, 2009

This thesis contains new FPGA implementations of adaptive signal segmentation and autoregressive modeling techniques. Both designs use Simulink-to-FPGA methodology and have been successfully implemented onto Xilinx Virtex II Pro device. The implementation of adaptive signal segmentation is based on the conventional RLSL algorithm using doubleprecision floating point arithmetic for internal computation and is programmable for users providing data length and order selection functions. The implemented RLSL design provides very good performance of obtaining accurate conversion factor values with a mean correlation of 99.93% and accurate boundary positions for both synthesized and biomedical signals. The implementation of autoregressive (AR) modeling is based on the Burg-lattice algorithm using fixed point arithmetic. The implemented Burg design with order of 3 provides good performance of calculating AR coefficients of input biomedical signals.

## Acknowledgments

I would like to express my deep gratitude to my supervisors Dr. Sridhar Krishnan and Dr. Adnan Kabbani at Ryerson University for their knowledgeable guidance and constant encouragement and support.

I also would like to greatly acknowledge those who have assisted me during my graduate study at Ryerson University. Particularly, I would like to thank all the members in SAR group and my friends for their kindness and encouragement.

Finally, I would like to especially thank my parents for their nonstop and warm support.

# Contents

| 1 | Inti   | roduction                                                                    | 1  |  |

|---|--------|------------------------------------------------------------------------------|----|--|

|   | 1.1    | Motivation                                                                   | 1  |  |

|   | 1.2    | Research objectives                                                          | 3  |  |

|   | 1.3    | Original contributions                                                       | 4  |  |

|   | 1.4    | Thesis organization                                                          | 5  |  |

| 2 | Review |                                                                              |    |  |

|   | 2.1    | Adaptive segmentation                                                        | 6  |  |

|   | 2.2    | Parametric modeling                                                          | 12 |  |

|   |        | 2.2.1 AR modeling                                                            | 13 |  |

|   | 2.3    | Review of hardware implementation of the two applications                    | 15 |  |

| 3 | Ada    | aptive segmentation with RLSL algorithm and hardware implementa-             |    |  |

|   | tion   |                                                                              | 18 |  |

|   | 3.1    | Theory of RLSL algorithm                                                     | 18 |  |

|   | 3.2    | Implementation and verification of adaptive segmentation based on high-level |    |  |

|   |        | language                                                                     | 21 |  |

|   | 3.3    | Design tools and implementation environment                                  | 25 |  |

|   | 3.4    | Implementation of block modules of RLSL using System Generator               | 27 |  |

|   |        | 3.4.1 Designing block modules for RLSL system                                | 27 |  |

|   |        | 3.4.2 Simulation results and Comparison with high-level language             | 40 |  |

|   | 3.5    | Implementation of RLSL on FPGA and result comparison                         | 43 |  |

| 4 | AR  | modeling with Burg algorithm and hardware implementation          | 52 |

|---|-----|-------------------------------------------------------------------|----|

|   | 4.1 | The theory of Burg algorithm                                      | 52 |

|   | 4.2 | Simulink implementation and verification of Burg algorithm        | 59 |

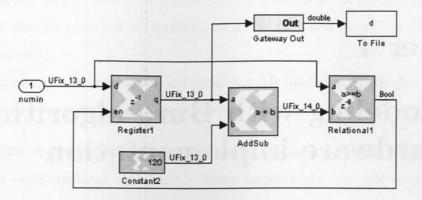

|   |     | 4.2.1 Simulink module design                                      | 59 |

|   |     | 4.2.2 Simulation results and comparison with high-level languages | 67 |

|   | 4.3 | FPGA implementation of Burg algorithm and conclusions             | 69 |

| 5 | Cor | clusion and Future work                                           | 72 |

|   | 5.1 | Conclusions                                                       | 72 |

|   | 5.2 | Future work                                                       | 74 |

# List of Tables

| 3.1 | Corresponding coefficients of $2^{nd}$ round $\gamma_c$ values from C and designed system                              |    |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

|     | for group 1; order from 1 to 16                                                                                        | 41 |

| 3.2 | Corresponding coefficients of $2^{nd}$ round $\gamma_c$ values from C and designed system                              |    |

|     | for group 2; order from 1 to 16                                                                                        | 41 |

| 3.3 | Device utilization summary of RLSL design; target device: xc2vp100-6-ff1704                                            | 43 |

| 3.4 | Comparison of the last $\gamma_c$ value of the $2^{nd}$ round obtained from C and FPGA                                 |    |

|     | implementations                                                                                                        | 46 |

| 3.5 | Group 1: Boundaries obtained from C implementation, simulink block level                                               |    |

|     | and FPGA implementation; $N = 500, M = 5, threshold = 0.9985, min = 120$                                               | 48 |

| 3.6 | Group 2: Boundaries obtained from C implementation, simulink block level                                               |    |

|     | and FPGA implementation; $N = 500, M = 16, threshold = 0.9985, min = 120$                                              | 48 |

| 3.7 | Group 3: Boundaries obtained from C implementation, simulink block level                                               |    |

|     | and FPGA implementation; $N = 600, M = 5, threshold = 0.95, min = 120$ .                                               | 48 |

| 3.8 | Device utilization summary of RLSL design with boundaries subsystem; target                                            |    |

|     | device: xc2vp100-6-ff1704                                                                                              | 48 |

| 4.1 | the relationship between the range of values of the parameters, length of input                                        |    |

|     | data and order for Burg algorithm                                                                                      | 59 |

| 4.2 | Group1: calculating AR coefficients based on three methods; $order = 3$ ,                                              |    |

|     | $N = 120; \ correlation = 100\% - \frac{ Simulinkimplementation-Cimplementation }{ Cimplementation } \times 100\% \ .$ | 69 |

| 4.3 | Group2: calculating AR coefficients based on three methods; $order = 3$ ,                                              |    |

|     | $N = 1000; \ correlation = 100\% - \frac{ Simulinkimplementation-Cimplementation }{ Cimplementation } \times 100\%$    | 69 |

| 3.19 | Block diagram of refcoef f                                                                                                | 38             |

|------|---------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.20 | Block diagram of F update                                                                                                 | 39             |

| 3.21 | Block diagram of gamma update                                                                                             | 39             |

| 3.22 | Block diagram of final gammas subsystem                                                                                   | 39             |

| 3.23 | plots of $\gamma_c$ values from C and designed system for group 1 with order of 16 $$ .                                   | 41             |

| 3.24 | plots of $\gamma_c$ values from C and designed system for group 2 with order of 16 $$ .                                   | 42             |

| 3.25 | plots of $\gamma_c$ values from C and designed system for group 3 with order of 16 $$ .                                   | 42             |

| 3.26 | Comparison of the device slice usage of RLSL algorithm with different orders,                                             |                |

|      | including testbench for each implementation                                                                               | 44             |

| 3.27 | Monitoring signal using Chipscope                                                                                         | 46             |

| 3.28 | Diagram of RLSL with boundaries subsystem                                                                                 | 50             |

| 3.29 | Block diagram of boundaries subsystem                                                                                     | 51             |

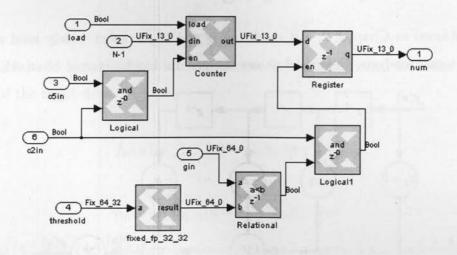

| 3.30 | Block diagram of comparing $2^{nd} \gamma_c$ values with threshold value                                                  | 51             |

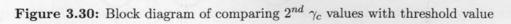

| 4.1  | Signal-flow diagram of AR model                                                                                           | 52             |

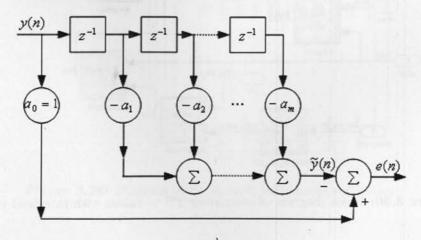

| 4.2  | lattice structure that performs the recursion equations for one stage of Burg                                             |                |

|      | algorithm                                                                                                                 | 54             |

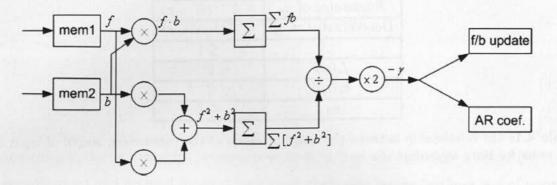

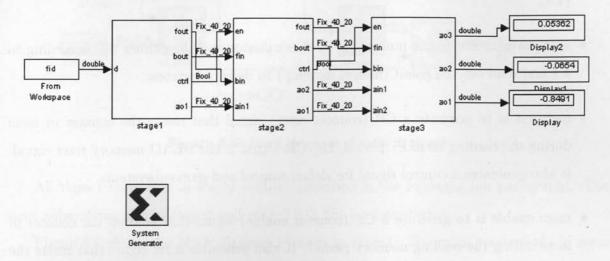

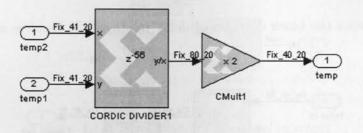

| 4.3  | Diagram of Burg algorithm                                                                                                 | 60             |

| 4.4  | Block diagram of Burg for 3 stages                                                                                        | 61             |

| 4.5  | Block diagram of stage1 for Burg algorithm                                                                                | 61             |

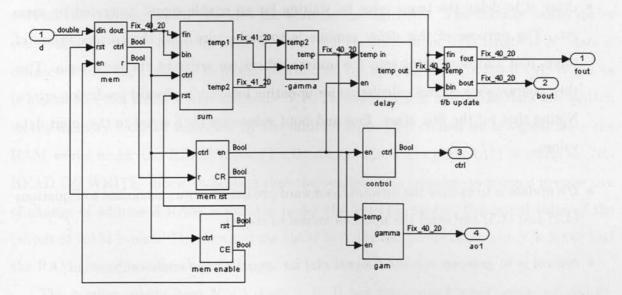

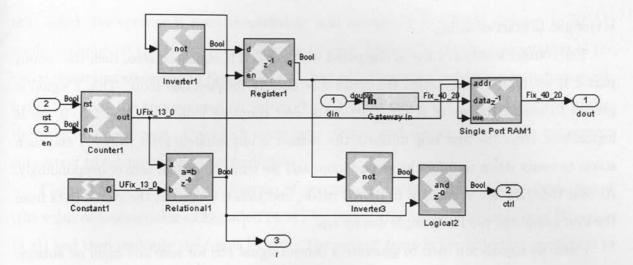

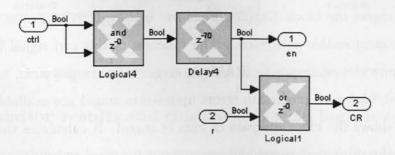

| 4.6  | Block diagram of <i>mem</i> in stage1                                                                                     | 63             |

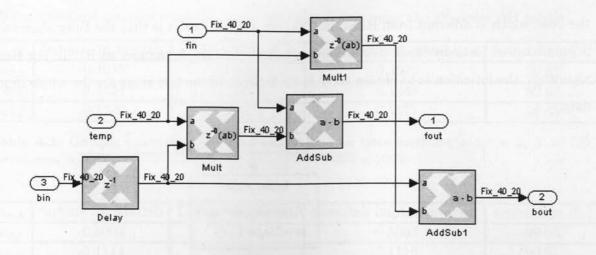

| 4.7  | Block diagram of sum in stage1                                                                                            | 64             |

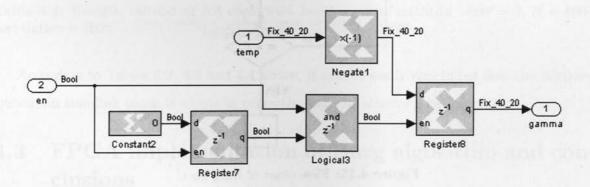

| 4.8  | Block diagram of -gamma of stage1                                                                                         | 65             |

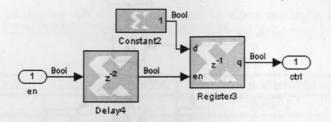

| 4.9  | Block diagram of mem rst of stage1                                                                                        | 65             |

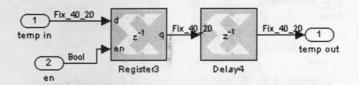

|      | Block diagram of mem enable of stage1                                                                                     | 66             |

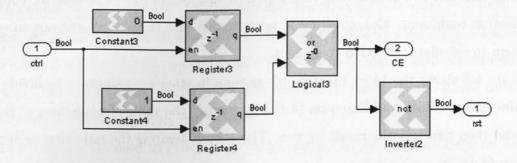

|      | Block diagram of delay of stage1                                                                                          | 66             |

|      |                                                                                                                           | 00             |

| 4.12 | Block diagram of <i>f/b</i> update in stage1                                                                              | 67             |

|      | Block diagram of <i>f/b update</i> in stage1                                                                              | 67<br>67       |

| 4.13 | Block diagram of f/b update in stage1          Block diagram of control in stage1          Block diagram of gam of stage1 | 67<br>67<br>67 |

x

| 4.15 | Flow chart of Burg for C                                                             | 68 |

|------|--------------------------------------------------------------------------------------|----|

| 4.16 | ${\it Output values of AR coefficients obtained from FPGA implementation; } order =$ |    |

|      | 3, N = 8000                                                                          | 71 |

## List of Acronyms

ACF - Autocorrelation function

AR - Autoregressive

ARMA - Autoregressive moving-average

ASIC - Application-specific integrated circuit

DSP - Digital signal processing

ECG - Electrocardiogram

EDA - Electronic design automation

EEG - Electroencephalogram

EGG - Electrogastrogram

EMG - Electromyogram

FFT - Fast Fourier transform

FPGA - Field programmable gate array

GLR - Generalized likelihood ratio

HDL - Hardware description language

**IP** - Intellectual property

LMS - Least-mean-square

LNS - Logarithmic numbers system

MA - Moving-average

MSE - Mean squared error

PCG - Phonocardiogram

QRD-LSL - QR-decomposition-based least-squares lattice

RAM - Random access memory

**RLS** - Recursive least-squares

**RLSL** - Recursive least-squares lattice

SEM - Spectral error measure

STFT - Short-time Fourier transform

TSE - Total squared error

VAG - Vibroarthrogram

VHDL - VHSIC hardware description language

VLSI - Very large scale integration

# Chapter 1 Introduction

### 1.1 Motivation

It is well known that, in the real physical world, there exist abundant kinds of signals. All those signals carry lots of information that are of people's interests. People develop diverse techniques to analyze, interpret, manipulate, and process those signals, trying to obtain the information they are interested in.

Biomedical signals are one type of signals that have strong relationships with human bodies or human organisms, such as ECG (electrocardiogram) related to the heart, EMG (electromyogram) related to the skeletal muscle fibers, EEG (electroencephalogram) related to the brain, EGG (electrogastrogram) related to the stomach, PCG (phonocardiogram) related to the heart and blood, VAG (vibroarthrogram) related to the knee joint, speech signals and so forth [1]. These signals are all generated by human organisms and thus, they certainly carry significant information about these organisms. Having such information can help people understand humans better and then for further purpose, can help improve health care and the quality of life of individuals. Hence, biomedical signal analysis has attracted abundant researchers' attention and has huge clinical significance. For example, ECG is one of the simplest and fastest procedures used to evaluate the condition of heart. The electrical activity of patient's heart is measured, interpreted, and printed out for the physician's information and further interpretation. The results can provide important clues to the cardiologist about the need for further testing to assess for the possibility of either structural or electrical abnormalities.

Biomedical signal processing covers many areas, including filtering; spectral analysis; modeling for feature representation and parameterization; and quantitative or objective analysis of physiological systems and phenomena [1]. It uses signal processing methods and algorithms implemented on computers or in electric hardware to objectively analyze biomedical signals. Although with the help of computers, some subjective errors caused by human observers can be easily avoided, i.e. errors caused by fatigue, there are still many difficulties in biomedical signal acquisition, processing and analysis, such as difficulties in accessibility to the targets, dynamic nature of biological systems, interactions and inter-relationships among physiological systems, physiological artifacts and interference, and energy limitations [1]. However, people can still use specific methods to solve those problems. For instance, the dynamic nature of biological systems is one main difficulty as it causes the signal to have stochastical and nonstationary behavior. To conquer this issue, the parametric modeling method can be used to solve the stochastic problem and segmentation method can be used to solve *nonstationary* problem. Many researches have demonstrated that parametric modeling is a useful method when dealing with random time series [2] [3] [4] and segmentation is an efficient approach to deal with nonstationary signals [1] [5] [6]. All of these researches are achieved by using modern computers, which rely on softwares, such as Matlab.

Since 1970s, VLSI (Very Large Scale Integration) technology has dramatically changed the world and human lives. Nowadays, one can not imagine a life without VLSI-chip dependent devices, like computers, digital cameras, cell phones, MP3 players, digital TV sets and so forth. All those digital products are relying on VLSL chips, including both ASIC (Application-Specific Integrated Circuit) and FPGA (Field Programmable Gate Array). In most recent years, the FPGA technology has been significantly developed and gained people's more and more preference due to its advantages of stronger functions of FPGA itself, shorter time to market, ability to reprogram and lower non-recurring engineering costs. Many applications have been achieved by using FPGA techniques in various areas, i.e. digital signal processing, aerospace, medical imaging, computer vision, speech recognition, ASIC prototyping, bioinformatics. More importantly, with the recent EDA (Electronic design automation) tools, more flexible and efficient high-level design methodology can be applied, such as C-to-FPGA [7], Stateflow diagram to VHDL (SF2VHD) [8], Matlab-to-FPGA (MATCH) [9] [10], Simulink-to-FPGA [11] [12]. In this research, the Simulink-to-FPGA design flow has been chosen to implement two biomedical algorithms for specific applications: adaptive segmentation and AR (autoregressive) modeling. The reason for choosing Simulink-to-FPGA design flow is that with the combination of Xilinx system generator and implementation tools, one can implement designs in a graphical and flexible way.

#### 1.2 Research objectives

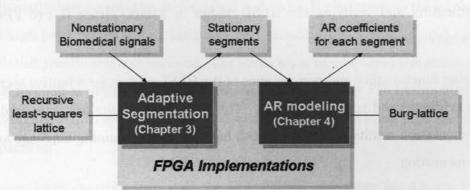

The objective of this research is to develop high level FPGA implementations of popular biomedical signal segmentation and modeling algorithms for further real-time processing purpose. The two algorithms are: RLSL (recursive least-squares lattice) algorithm for adaptive segmentation and Burg-lattice algorithm for AR modeling. The overview of this research is shown in Figure 1.1.

Figure 1.1: Overview of the research work

The RLSL hardware system should be able to calculate the conversion factor gamma values of each input sample for a pre-determined system order, which can be further used to be compared with a threshold value for adaptive segmentation. The Burg-lattice hardware system should be able to calculate the corresponding AR coefficients for the input data based

on a certain system order, which can be used for further AR modeling.

### 1.3 Original contributions

The main contributions of this research are described as follows:

Adaptive Segmentation

- Proposing a new system-level architecture for RLSL algorithm with a specific purpose of adaptive segmentation, which could be used for further real-time processing objective. The proposed design has an adjustable (programmable) order selection function and data length selection function, which are up to 16 stages and 5000 samples, respectively.

- Implementing design of RLSL algorithm using double precision floating point arithmetic for internal computation and data storage. The input data and output data are represented by using fixed point arithmetic type, which are easy to read and analyze.

- Implementing and verifying the RLSL design in Xilinx Virtex II Pro FPGA using Xilinx implementation tools.

- Verifying functionality and performance of the RLSL system for adaptive segmentation using synthetic and real knee signals. The simulation results are compared with the implementation results provided by both high-level programming language and FPGA implementation.

#### Autoregressive Modeling

- Designing the Burg-lattice algorithm on system-level with a specific purpose of calculating model parameters.

- Implementing and verifying the Burg-lattice design in Xilinx Virtex II Pro FPGA and comparing the results with ones obtained by using high-level programming languages.

### 1.4 Thesis organization

This thesis consists of five chapters:

- Chapter 1 introduced the significance of biomedical signal analysis and the reason why biomedical signal processing attracted researchers' interests. It also states the objectives of the project, the contribution of the author and the organization of this thesis.

- Chapter 2 starts with a review of adaptive segmentation methods of biomedical signals and presents the reasons why to choose the target algorithm: RLSL algorithm for hardware implementation. It provides an overview of parametric modeling, particularly AR modeling and the reason for choosing Burg-lattice algorithm for hardware implementation. It also presents a review of hardware implementation of the two applications and algorithms.

- Chapter 3 presents the theory of the RLSL algorithm for adaptive segmentation. The mathematical representation is described in details. It also presents the implementation with high-level programming language and simulink block-models, and provides the simulation results and comparisons. The verification of adaptive segmentation applying RLSL method is stated by using synthesized signals. The FPGA implementation of the designed RLSL system is presented and discussed, providing final test results and comparisons.

- Chapter 4 presents the theory of the Burg-lattice algorithm for AR modeling. The mathematical representation is provided in details as well as the advantages of the algorithm. Implementations with high-level programming language and simulink block models of Burg-lattice algorithm are followed. The simulation results and comparisons are displayed, followed by the FPGA implementation details and testing results.

- Chapter 5 concludes the thesis and presents discussion for future work of this research.

# Chapter 2

## Review

In this chapter, the reason why to choose adaptive segmentation rather than fixed segmentation and a review of adaptive segmentation techniques for biomedical signals will be presented first. Then a brief introduction on parametric modeling, particularly AR (autoregressive) modeling will be followed. At last, a review of VLSI implementations of the two selected algorithms will be stated.

## 2.1 Adaptive segmentation

Biomedical signals are typical nonstationary random signals. They are non-stationary as the statistical properties of such signals vary with time, i.e. the mean value varying with time, or having time-varying frequency spectrum. This causes challenges when one wants to use classical, well-developed spectrum analysis methods (i.e. Fourier transform) to analyze such signals. Take the EEG analysis as an example. The description of EEG in spectral domain can be used for feature extraction [13]. This requires the target signal to be stationary. Unfortunately, during its long time of observation, the EEG signal is non-stationary in nature. However, it can be considered to be locally stationary over short time intervals [13] [14]. Hence, using segmentation technique to partition the signal into stationary components is a straightforward and natural idea.

There are two categories of segmentation. One is fixed segmentation and the other is adaptive segmentation. Fixed segmentation uses fixed-size window for segmentation and it

is usually used in specific applications, such as STFT (short-time Fourier transform) [1]. Although fixed segmentation is simple but its performance is not efficient enough. The main problem for this method is the choice of the window size. Apparently, the window length should be long enough for meaningful analysis and also short enough to make sure that each segment is stationary. On one hand, selecting large fixed-size windows, the signal may still have dynamics during the window duration chosen, which actually requires more segments. On the other hand, selecting small fixed-size windows, the signal may still have stationary status much longer than that window duration, which actually hopes to use larger window size. In short, this method can not guarantee stationarity for each window and can not guarantee that the chosen window size is appropriate. Moreover, short-time analysis could be computationally expensive [1]. For example, the Fourier transform needs to be calculated for each segment of the signal in STFT method. Thus, if the window size is not chosen appropriately, it may have lots of segments in total, which would make the whole computation of using STFT method become very expensive and redundant. Therefore, it is much desirable and reasonable to find a more efficient segmentation method for nonstationary signals.

Adaptive segmentation is an alternative based on a more efficient idea, compared with fixed segmentation. It segments the signal when it is needed according to the dynamic characteristics of the signal itself. This means that the analysis window is kept as long as possible when the signal remains stationary, whereas set up a boundary and used a new window when the signal changes its properties abruptly and dramatically.

There are several approaches that have been used for adaptive segmentation of synthesized and/or real biomedical signals. These approaches are listed and described below.

#### SEM (spectral error measure)

Bodenstein and Praetorius [13] used SEM for adaptive segmentation of EEG signal and for further feature extraction. This method is based on AR modeling, using a fixed-length reference window for calculation of AR parameters in the reference window. And those AR parameters are used to model the samples in a test window and calculate the ACF (autocorrelation function) of the test window, which is finally used to define a spectral error measure (SEM). If the error measure is larger than a specific threshold, then a segment boundary is set up and the procedure starts again. This SEM method was also applied by Tavathia et al. [3] for knee joint vibroarthrography's (VAG) adaptive segmentation.

#### ACF (autocorrelation function)

Michael and Houchin [15] used ACF method for adaptive segmentation, which directly estimated the values of short-time autocorrelation function of the signal to segment the boundaries. This method is the most general in that it does not make use of any explicit model, e.g. AR model. It uses a reference window with fixed-size at the beginning of each segment, and calculates the ACF for the reference window. Then it uses a sliding window (also called as test window) with equal length to the signal and calculates the ACF for the test window. If the difference between the ACF in the sliding test window and the reference window is significant, a segment boundary is set up and then repeats the procedure.

#### GLR (the generalized likelihood ratio)

Appel and Brandt [16] used GLR method for adaptive segmentation. The difference between this method and the previous two is that it uses a continuously growing reference window. The test window is a fixed-size sliding window like the previous two methods. The advantage of using the growing reference window is that it contains the maximum of information available from the beginning of each segment to the current instant, thus leading a minimum variance of the estimation of the reference parameters.

Appel and Briandt also compared these three methods in [17] using both synthesized signals and real EEG signals. They found that the GLR method provided the best performance among the three but had the highest computational complexity.

#### RLS (recursive least-squares)

Moussavi et al [6] used the RLS filter for adaptive segmentation of VAG signals. The advantage of this method, compared with SEM, ACF and GLR, is that it does not require any reference and test windows, but calculates the filter tap-weight vector for each sample of the input signal. It could provide good performance of adaptive segmentation of VAG signals according to Moussavi's tests. However, this RLS method has high computational complexity and does not have the characteristic of modularity in nature for the convenience of hardware implementation.

RLSL (recursive least-squares lattice)

S.Krishnan et al [18] directly used an adaptive filter based on RLSL algorithm for adaptive segmentation of VAG signals. According to their research, this method could provide very good performance for biomedical signal segmentation. They made the input data run into the filter two times, wherein the first running to make the filter converge. For the second running, they compared the selected parameter to a predefined threshold value for each sample. Once the parameter value fell down less than the threshold value, a boundary was set up. S.Krishnan [19] also tested this method using synthesized signal and obtained good results. This method is also a recursive method on a sample-by-sample basis and does not use any short-time windows as the RLS method. More importantly, it is using the lattice structure that makes it more attractive and suitable for hardware implementation.

RLSL algorithm belongs to the fast RLS category. It is based on lattice structure that makes it work faster than the conventional RLS algorithm, since the computational complexity increased linearly with the order M. It involves both time updates and order updates, which makes it distinguishing from many other adaptive algorithms [20].

There are many advantages for RLSL algorithm [20] [21] [22] [23] [24].

- Fast rate of convergence, compared with those algorithms in LMS (least-mean-squares) family.

- Good computational complexity, linear with M, not as square of M like the conventional RLS algorithm or QRD-LSL algorithm.

- High modularity on stage-by-stage, each complete iteration sharing exactly the same structure; parallelism; concurrency.

- Good tracking capability.

• Order recursion, based on lattice structure, leading to computational efficiency and modularity.

RLSL algorithm converges fast as it is derived from the least-squares family. This is the fundamental advantage for consideration when compared with the stochastic gradient approach family, whose most popular algorithm is known as LMS (least-mean-square) algorithm. Fast rate of convergence can make the filter adapt rapidly according to the signals' statistical characteristics. RLSL has good computational complexity: its computational complexity is linear with order M, referred to O(M) as the same as LMS algorithm but better than conventional RLS (recursive least-squares) algorithm. This advantage is due to the order-recursion property of the algorithm: the information gathered from the previous computations for order M-1 is carried over to the next order M. By contrast, the conventional RLS and square-root RLS algorithm (which is derived as to solve the issue of numerical instability in conventional RLS) have a computational complexity linearly increasing with square of M, referred to  $O(M^2)$ , which may become annoying from a hardware implementation point of view, particularly when M is large. RLSL has very high stage-by-stage modularity property. For each iteration, it is sharing exactly the same structure, which is convenient and suitable for FPGA implementation. RLSL also has very good tracking ability that can provide good performance on monitoring the statistical changes in the signal, which has been proved by previous researchers [6], [18]. It has not only time recursion but also order recursion that is based on using a lattice structure. It is evident that the lattice structure itself leads to good modularity and computational efficiency and possess better numerical properties than direct structures [23].

There are also some limitations for this algorithm.

- Possible numerical instability, after hundreds of thousands of literation [20], [22], [23], [25], [26].

- Dynamic range of parameters [21].

Any DSP algorithms implemented or applied in digital systems suffer from the finite word length effects or also called finite-precision effects. In practical, one can not use infinite precision to employ the design digitally. The finite-precision effects influence the performance of a digital implementation of the algorithm and make it deviate from its theoretical value. The two main factors that influence the nature of the deviation are the details of the algorithm itself and the form of numerical computation employed (fixed point or floating point) [20].

For algorithm itself, the RLSL algorithm mentioned before in this chapter is referred as conventional RLSL or indirect updating RLSL algorithm, which has been actually used in many researches [6], [18] and [19] for adaptive segmentation of real biomedical signals. Ling et al [23] proposed a RLSL algorithm with error-feedback, commonly known as the *direct* updating RLSL. They pointed out that the direct version of RLSL has better numerical accuracy and numerical stability based on their computer simulation results. Bunch et al [25] gave the same conclusion but they also mentioned that both the RLSL algorithms had the potential for large relative errors. Nonetheless, no explicit researches have been done using the indirect RLSL algorithm for real signal's adaptive segmentation. Moreover, the direct updating RLSL has more computational complexity than the indirect one.

Paleologu et al in [21] mentioned that the conventional RLSL algorithm had a drawback of large dynamics of parameters. However, they only focused on using a modified cost function to reduce the dynamic range of parameters, nothing related to the hardware implementation and any specific applications.

To sum up, the indirect RLSL algorithm has both advantages and disadvantages as mentioned above. However, it has been already applied for adaptive segmentation of real biomedical signals and achieved satisfactory performance with the use of softwares and programs based on double precision floating point type arithmetic on general PCs. Thereby, double precision floating point arithmetic is chosen to implement the indirect RLSL algorithm and the questions then would become: is this accessible and worthy to implement this algorithm onto specific FPGA and is its performance acceptable? The answers to these two questions and more details will be provided and discussed in Chapter 3.

#### 2.2 Parametric modeling

Parametric modeling is a typical method in dealing with random signals, as long as the signals are stationary. The basic idea for parametric modeling is that the present value of model output is assumed to be the linear combination of several past values of model output plus the linear combination of present and past values of model input, expressed in the following equation [1].

$$y(n) = -\sum_{k=1}^{P} a_k y(n-k) + G \sum_{l=0}^{Q} b_l x(n-l)$$

(2.1)

where  $b_0 = 1$ , x(n) is the model input, y(n) is the model output, and G is the gain factor.

Applying z-transform to the above equation, it is easy to obtain its transfer function as

$$H(z) = \frac{Y(z)}{X(z)} = G \frac{1 + \sum_{l=1}^{Q} b_l z^{-l}}{1 + \sum_{k=1}^{P} a_k z^{-k}}$$

(2.2)

In most cases, the gain factor is not important [1], and thus the system is fully characterized by  $a_k$  and  $b_l$ .  $a_k$  and  $b_l$  determine if the system is an all-pole system or an all-zero system or a pole-zero system.

There are three main modeling methods: AR(Autoregressive) modeling, MA(Movingaverage) modeling and ARMA(Autoregressive moving-average) modeling. AR models correspond to the situation that  $b_l$  in Equation (2.2) is all equal to zero, whereas MA models correspond to the situation that  $a_k$  is all zero, and for ARMA models,  $a_k$  and  $b_l$  are both not all equal to zero. Among these three methods, AR modeling is a very popular one particularly in dealing with biomedical signals for several reasons: 1) some biomedical signals (i.e. speech signal) have an underlying autoregressive structure; 2) generally, any signal (even if it is not necessarily AR in nature) can be modeled as an AR process as long as an appropriate model order is selected; 3) estimation of model parameters is based on finding out the solution of a linear system of equations and many efficient algorithms are available to compute the solution [27] [28]. The following section briefly introduces the AR modeling method.

#### 2.2.1 AR modeling

AR modeling is such a widely used method in biomedical signal processing. For AR modeling, the parameters of AR model are of interests and investigated for use in signal analysis.

It has been demonstrated that in many cases, AR spectrum provides a better resolution than traditional Fourier spectrum [1], which can ease the signal analysis. To obtain the AR spectrum, one has to obtain the AR coefficients of the signal first [29]. Moreover, AR coefficients can be easily used in pattern classification of biomedical signal [30], [31] and data compression application [32].

For an AR model, the output is modeled as the linear combination of P past values of the model output and the present model input (no past values of the model input are used) as [1]

$$y(n) = -\sum_{k=1}^{P} a_k y(n-k) + Gx(n)$$

(2.3)

Again, applying the z-transform to the above equation, then the AR transfer function is

$$H(z) = \frac{G}{1 + \sum_{k=1}^{P} a_k z^{-k}}$$

(2.4)

Factorizing the denominator polynomials in Equation (2.4), the transfer function can be expressed as

$$H(z) = \frac{G}{\prod_{k=1}^{P} (1 - p_k z^{-1})}$$

(2.5)

The parameters  $p_k$ , (k = 1, 2, ..., P), are the poles of H(z) or the system. The AR model only has system poles, no zeros and therefore, it is also called the all-pole model. The purpose here is to obtain those AR parameters (also known as AR coefficients).

In many cases of biomedical signals, e.g. the EEG or the PCG, the input x(n) is totally unknown. Hence, the output y(n) can be only approximately predicted as the linear combination of past values of the output

$$\widetilde{y}(n) = -\sum_{k=1}^{P} a_k y(n-k)$$

(2.6)

Obviously, there exists an error as

$$e(n) = y(n) - \tilde{y}(n) = y(n) + \sum_{k=1}^{P} a_k y(n-k)$$

(2.7)

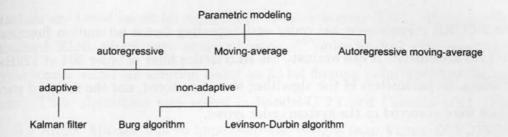

In the method of least-squares, which is derived in the time domain, the parameters  $a_k$  are obtained by minimizing the MSE (mean squared error) or TSE (total squared error) with respect to each of the parameters [1], [33]. There are several techniques that can do the job of computing the model coefficients, directly or iteratively. Generally, iterative methods cost more computation to achieve a desired degree of convergence than the direct methods [33]. There are some commonly used approaches for directly estimating prediction parameters: the autocorrelation method, the covariance method, the square-root or Cholesky decomposition method, and the Burg method. All these methods are trying to solve the normal equations, a set of p equations for the predictor coefficients  $a_k, 1 \le k \le p$ . Autocorrelation or covariance method requires large computational operations and storage locations. Square-root or Cholesky decomposition method has less computations compared with the previous two methods. Further reduction in computation and storage room can be achieved by using Levinson-Durbin algorithm, which provides a recursive method to solve the set of normal equations. This method has big savings in operations and storage locations from the previous methods [33]. The Burg algorithm is another most popular algorithm for non-adaptive AR models such as the Levinson-Durbin algorithm, where non-adaptive means that the model parameters are chosen to give the best fit of a sequence of data samples, not like adaptive models that the values of parameters are updated on the arrival of each new data sample [14]. Figure 2.1 shows the methods of parametric modeling [14].

One main advantage for Burg algorithm compared with Levinson-Durbin algorithm is that in obtaining the solution of AR parameters of order M, one just simply add one more stage without affecting the earlier computations for the lower stages, which is more suitable for VLSI consideration, while for Levinson-Durbin algorithm, one actually computes the

Figure 2.1: Methods for parametric modeling and algorithms for AR modeling

model parameters for all orders up to the desired order M. In addition, Levinson-Durbin algorithm could be numerically relatively unstable [33]. Hence, it is reasonable to conclude that using Burg algorithm to compute AR coefficients is a satisfactory choice and is more attractive for hardware implementation. More details of Burg algorithm will be provided in Chapter 4.

## 2.3 Review of hardware implementation of the two applications

To the best of the author's knowledge, there is no reported literature about hardware implementation of direct adaptive segmentation, but there are few papers discuss the implementation of RLSL algorithms (direct or indirect RLSL) for other applications.

Zdenek Pohl et al. [34] proposed an error-feedback RLSL filter (the direct RLSL) with the estimation of an unknown order and forgetting factor of identified system as a PCORE coprocessor for Xilinx EDK. Their design used the LNS (logarithmic numbers system) arithmetic. The proposed FPGA coprocessor implementation was able to evaluate the direct RLSL filter of order 504 at 12kHz input data sampling rate. The advantage and deficiency of their design are listed below:

• A hardware coprocessor rather than a standalone IP core. The PCORE coprocessor contains a RLS lattice core, which is based on RLSL with error-feedback algorithm (the direct RLSL algorithm as mention before). However, the coprocessor needs the standard C programming and debugging to get accessed, which is still software-based.

- The PCORE corprocessor has order and forgetting factor estimation function using the LNS arithmetic. It can evaluate the RLS lattice filter of order 504 at 12kHz. Nevertheless, no parameters of the algorithm were monitored, nor the range of parameter values were observed as the system order grows.

- The aim of the work was to provide a versatile highly configurable hardware RLSL (direct RLSL) core for DSP applications [34]. Hence, they did not have a specific application purpose of implementing RLSL algorithm, such as biomedical signal adaptive segmentation, which uses the chosen parameter to monitor the significant changes in the target biomedical signal and adaptively segment it.

Antonin Hermanek et al. [35] presented a FPGA implementation of a noise canceler with an adaptive RLS-lattice filter in Xilinx devices. They used LNS for internal computation and demonstrated that the noise canceler could run at the XSV800 prototyping board in realtime with 16 kHz sampling rate for the filter order of 160. They also provided the comparison of the performance of FPGA echo canceler and their implementation on TI TMS320C6711 (IEEE 32-bit floating point device) of 100<sup>th</sup> order. The advantage and deficiency of their design are listed below:

- Used 19-bit LNS arithmetic for computations, decreasing the computational complexity of multiplications, divisions and square-root operations, but increasing the computational complexity of additions and subtractions. The detailed information of accuracy of such LNS arithmetic system was not provided yet.

- Used four pipelined macros running in parallel and each macro used lattice structure in sequential, hence providing up to  $4n^{th}$  order computation. But the information about the usage of device area of their lattice noise cancellation design that could run 160 stages for real-time application was not provided.

F. Albu et al. [36] implemented the conventional RLSL and its normalized version on Virtex XCV2000E-6 operating with 24-bit fixed point input/output signals. Their internal computations are based on 32-bit logarithmic number system (LNS). The normalized and un-normalized RLSL filters were analyzed using  $8^{th}$  order at 36.7 kHz compared to the clock cycle counts with DSP solution based on 32-bit floating point TMS320C3x/4x 50Mhz processors. Their algorithms were coded in Handel-C 2.1 and Celoxica DK1. They used Synplify 5.3 Xilinx Alliance 3.3i to implement the designs onto Virtex XCV2000E-6. The advantage and deficiency of their design are listed below:

- Used 32-bit LNS arithmetic for internal computations, decreasing the computational complexity of multiplications, divisions and square-root operations, but increasing the computational complexity of additions and subtractions.

- Analyzed designs on FPGA under 8<sup>th</sup> order at 36.7 kHz but they did not provided information about their design performance for higher system order.

- Implemented the RLSL algorithm without monitoring any parameters or taking advantage of using those parameters for specific applications, i.e. adaptive segmentation.

For AR modeling, one implementation can be found in [37]. They implemented the Burg algorithm onto the AMD29500 microprogrammable byte slice DSP and NEC $\mu$ PD77230 single-chip DSP. The AMD DSP system can have a sixteenth-order modeling rate at 17kHz while the NEC DSP system can have a sixteen-order model at 8kHz. The advantage and disadvantage of their design are listed below:

- Implemented the Burg algorithm onto a series of DSP microprocessor systems, not implementing on single VLSI chip, either FPGA or ASIC.

- Required DSP board and softwares for real application, e.g. processing medical images.

#### Summary

Adaptive segmentation using conventional RLSL method and AR modeling using Burglattice method are good choices for biomedical signal segmentation and modeling. Moreover, both methods have attractive properties to implement onto hardware. The next two chapters will describe these two methods in more details and their specific FPGA implementations.

## Chapter 3

# Adaptive segmentation with RLSL algorithm and hardware implementation

### 3.1 Theory of RLSL algorithm

The conventional RLSL (recursive least-squares lattice, sometimes regarding as RLSlattice or recursive-LSL) algorithm involves both order and time recursions as mentioned in Chapter 2. It is first a time-recursive algorithm extended from the method of least-squares, and then involves order-recursions using lattice structure to reduce the high computational complexity for RLS algorithm.

The mathematical representations of the RLSL algorithm are expressed as follows [1]. Initialization:

- at n = 0, and for each order m = 1, 2, ..., M, set the cross-correlation  $\Delta_{m-1}(0) = 0$ ; forward/backward prediction error power  $F_{m-1}(0) = B_{m-1}(0) = \delta$ ; the conversion factor  $\gamma_{0,c}(0) = 1$ , where the index *n* represents the number of samples, *M* is the order of the system and  $\delta$  is a small positive constant, e.g.  $\delta = 0.001$ .

- at  $n \ge 1, m = 0$ , set the forward/backward prediction error  $f_0(n) = b_0(n) = u(n)$ ;  $F_0(n) = B_0(n) = \lambda F_0(n-1) + ||u(n)||^2$ ;  $\gamma_{0,c}(n) = 1$ , where u(n) is the input data and  $\lambda$  is the forgetting factor, e.g. $\lambda = 1$ .

• for joint-process estimation, at n = 0, m = 0, 1, ..., M, set the scalar  $\rho_m(0) = 0$ ; at  $n \ge 1, m = 0$ , set a priori estimation error  $e_0(n) = d(n)$ , where d(n) is the desired response.

#### Prediction

For  $n = 1, 2, ..., N_s$ , m = 1, 2, ..., M, the parameters are computed as follows:

$$\Delta_{m-1}(n) = \lambda \Delta_{m-1}(n-1) + \frac{b_{m-1}(n-1)f_{m-1}(n)}{\gamma_{m-1,c}(n-1)}$$

(3.1)

$\Delta_{m-1}(n)$  is the cross-correlation between  $f_{m-1}(n)$  and  $b_{m-1}(n-1)$ .

$$\gamma_{m,f}(n) = -\frac{\Delta_{m-1}(n)}{B_{m-1}(n)}$$

(3.2)

$$\gamma_{m,b}(n) = -\frac{\Delta_{m-1}(n)}{F_{m-1}(n-1)}$$

(3.3)

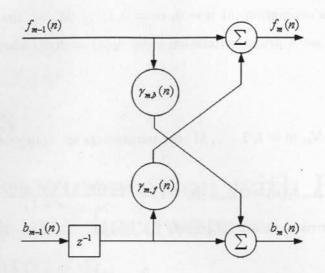

$\gamma_{m,f}(n)$  and  $\gamma_{m,b}(n)$  are the forward and backward reflection coefficients. Generally,  $\gamma_{m,f}(n) \neq \gamma_{m,b}(n)$  as  $B_{m-1}(n)$  and  $F_{m-1}(n-1)$  are unequal. The reason to call this algorithm as indirect RLSL is that it needs to calculate the cross-correlation first, and then to update the forward/backward reflection coefficients, not directly updating the forward/backward reflection coefficients.

$$f_m(n) = f_{m-1}(n) + \gamma_{m,f}(n)b_{m-1}(n-1)$$

(3.4)

$$b_m(n) = b_{m-1}(n-1) + \gamma_{m,b}(n)f_{m-1}(n)$$

(3.5)

$f_m(n)$  and  $b_m(n)$  are forward and backward prediction errors. They are updated based on a lattice structure as Figure 3.1 shows.

$$F_m(n) = F_{m-1}(n) + \gamma_{m,f}(n)\Delta_{m-1}(n)$$

(3.6)

$$B_m(n) = B_{m-1}(n-1) + \gamma_{m,b}(n)\Delta_{m-1}(n)$$

(3.7)

Figure 3.1: Lattice structure for one stage

$F_m(n)$  and  $B_m(n)$  are the forward and backward prediction error powers. The conversion factor  $\gamma_{m,c}(n)$  is updated as:

$$\gamma_{m,c}(n) = \gamma_{m-1,c}(n) - \frac{b_{m-1}^2(n)}{B_{m-1}(n)}$$

(3.8)

Filtering

For  $n = 1, 2, ..., N_s, m = 0, 1, ..., M$ :

$$\rho_m(n) = \lambda \rho_m(n-1) + \frac{b_m(n)}{\gamma_{m,c}(n)} e_{m-1}(n)$$

(3.9)

$$\kappa_m(n) = \frac{\rho_m(n)}{B_m(n)} \tag{3.10}$$

$$e_m(n) = e_{m-1}(n) - \kappa_m(n)b_m(n)$$

(3.11)

where  $\rho_m(n)$  is the scalar,  $\kappa_m(n)$  is the regression coefficient and  $e_m(n)$  is the a posteriori estimation error.

According to [18] [19], the conversion factor  $\gamma_c$  is a good choice for monitoring the statistical changes in the target non-stationary signals. The input data is required to pass

the filter twice. The first pass is to make the filter converge, and the second pass is to obtain the conversion factor  $\gamma_c$  for each sample (the second round  $\gamma_c$ ), which is needed for the further purpose: compare each  $\gamma_c$  with a predefined threshold value to detect the segment boundaries. After a few iterations at the beginning,  $\gamma_c$  gets close to unity. If there is a significant change in the target signal, there will be a dramatical drop of the  $\gamma_c$  value. Whether the drop of the  $\gamma_c$  value can be considered as a dramatical drop is determined by the threshold. If the  $\gamma_c$  value falls down below the threshold, it is believed to have a dramatical drop and should set up a boundary at that instant. Hence, the determination of the threshold value is very important as well. However, this value is user-defined depending on different applications and different kinds of signals. In [19], the threshold value is chosen as 0.9985 to segment VAG signals. In [1], the RLSL algorithm is used to segment PCG signals using a threshold of 0.995. It is reasonable to conclude that to obtain good performance of adaptive segmentation, high precision is certainly required to represent the conversion factor values. For example, if using 0.9985 as the threshold, the RLSL system should be able to distinguish the difference between 0.9985 and 0.9986. Undoubtedly, double precision floating point arithmetic can meet this requirement.

## 3.2 Implementation and verification of adaptive segmentation based on high-level language

To test and verify the selected method of using RLSL algorithm for adaptive segmentation, a C program has been created to implement the RLSL algorithm based on double precision floating point on a general PC. Meanwhile, a synthesized nonstationary signal has been generated for verifying the developed C program.

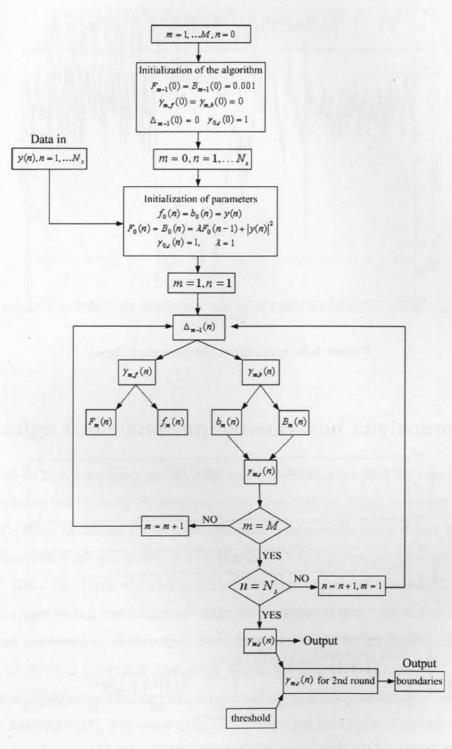

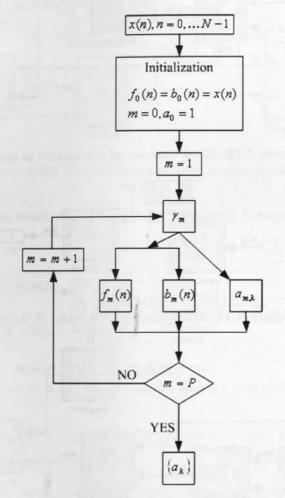

Figure 3.2 shows the flow chart of the RLSL algorithm. According to Figure 3.2, after initialization, the parameters of the first sample, including cross-correlation, forward/backward reflection coefficients, forward/backward prediction errors, forward/backward prediction error powers and conversion factor, will be updated for each stage until reaching the last stage (the system order). After the first sample finishes its update and obtains its conversion factor value of the last stage, the second sample starts to update with the same procedure until the last sample finishes its updates. Furthermore, the  $2^{nd}$  round conversion factor  $\gamma_c$ of each sample is compared with a threshold to detect boundaries.

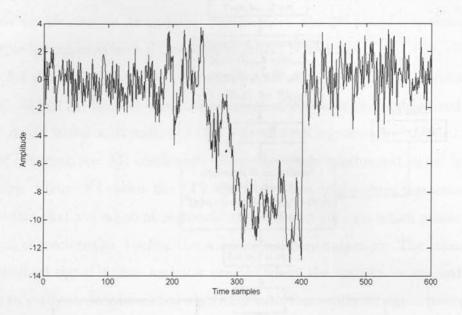

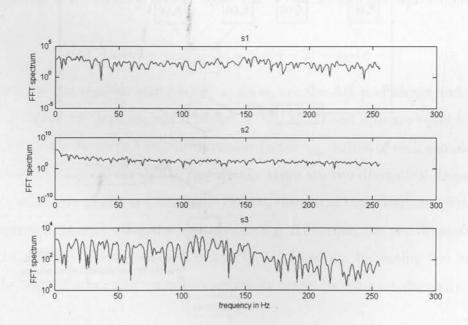

Figure 3.3 shows the plot of a synthesized nonstationary signal. It consists of three segments: s1, s2 and s3. Each of them is a sequence of 200 samples, modeled and generated by a  $3^{rd}$  AR model based on Equation (3.12). The adjacent segments are modeled differently by means of changing one AR coefficient. Thus, the whole synthesized signal is obviously non-stationary. Figure 3.4 shows the FFT-spectrum plots of the three segments in Figure 3.3. It is evident that the adjacent segments have different spectra, which means that they have different characteristics, leading the whole signal non-stationary. The reason of using such a synthesized signal is that we know exactly where the boundaries are and it will be appropriate to verify the segmentation algorithm with this synthetic signal before applying it to real-world biomedical signals. In this case, the boundaries are at 201 and 401 time samples.

Each segment of the whole synthetic signal can be mathematically represented as follow:

$$s(n) = w(n) + a_1 s(n-1) + a_2 s(n-2) + a_3 s(n-3)$$

(3.12)

where w(n) is the random white noise,  $a_1$  to  $a_3$  are the AR coefficients and the initial values of s(n) are equal to zeros, which means s(-2), s(-1) and s(0) are equal to zero.

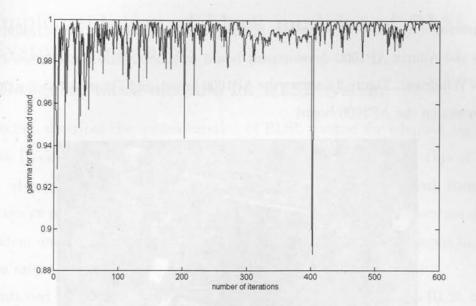

Figure 3.5 shows the second round conversion factor  $\gamma_{m,c}$  values of each sample obtained by using order of 5 (m = 5) for RLSL. Apparently, there are two dramatical drops as shown in the figure, which are at 203 and 402, quite close to the actual time positions (201 and 401). If an appropriate threshold value has been chosen, e.g. 0.95, then, the two dramatical drops, whose values are both below 0.95, will definitely be picked up, indicating two boundaries, and then the segmentation into stationary segments would be done satisfactorily.

Figure 3.2: Flow chart of RLSL algorithm

Figure 3.3: synthesized nonstationary signal

Figure 3.4: Spectra of the three segments consisting of the synthesized non-stationary signal

Figure 3.5: The 2<sup>nd</sup> round conversion factors of the synthesized nonstationary signal

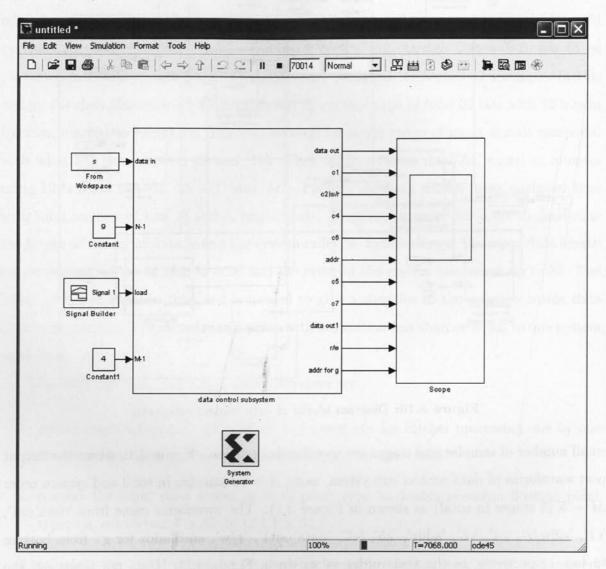

## 3.3 Design tools and implementation environment

After tested on high-level language (C language), the RLSL algorithm for adaptive segmentation is implemented by using System generator provided by Xilinx company in Simulink environment. After installing the system generator successfully, three Xilinx libraries embedded in Simulink were generated: Xilinx Blockset, Xilinx Reference Blockset and Xilinx XtremeDSP Kit. The three libraries provide abundant basic and specified Xilinx blocks, such as adder/subtracter, register, logic units for implementation. All the blocks in these three libraries are based on Xilinx fixed point type and could be implemented onto Xilinx FPGAs. With System Generator and other Xilinx implementation tools, i.e. Xilinx ISE, CoreGenerator, ChipScope Pro, one can implement a full FPGA design flow from Simulink modeling to hardware [11]. For more details about system generator, ISE and other Xilinx implementing tools, one can refer to [38] [39] [40].

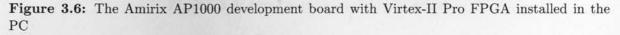

In this research, the target FPGA chip is Xilinx Virtex II Pro xc2vp100-6ff1704. The

platform provided by CMC Microsystems (Canadian Microelectronics Corporation Microsystems) has the Amirix AP1000 development board installed inside a x86-based PC (32-bit editions of Windows). Figure 3.6 shows the AP1000 board, and Figure 3.7 shows the location of components on the AP1000 board.

Figure 3.7: Location of components on the AP1000 board

# 3.4 Implementation of block modules of RLSL using System Generator

### 3.4.1 Designing block modules for RLSL system

This section describes the implementation of RLSL method for adaptive segmentation on simulink block level, using System generator from Xilinx company. One of the most important advantage of using System Generator is that it is combined with Simulink that makes the design procedure more friendly, straightforward and efficient, since one can always run simulation and see the results in various ways, i.e. observing waveforms in scope, or seeing data values in a text file.

As mentioned before, for adaptive segmentation that uses conventional RLSL algorithm, all the input data are necessary to run into the system for two times, hence requiring control subsystem to control the data in and out. Furthermore, all the samples are processed one by one and according to the algorithm (mathematical equations), adjacent samples are interrelated with each other and adjacent stages for one sample are inter-related as well, thereby requiring memory subsystem to store useful values of different parameters. Additionally, it is necessary to have a processing subsystem for calculating the parameters according to Equations (3.1) to (3.8).

To acquire high accuracy as C implementation does, double precision floating point type arithmetic has been used to implement the internal computation of RLSL algorithm. All the data for computing and storing are in 64 bits in total, with 1 sign bit, 11 bits for exponent and 52 bits for fraction. The remaining of this section depicts the models of RLSL system with more details.

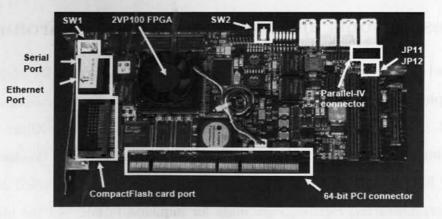

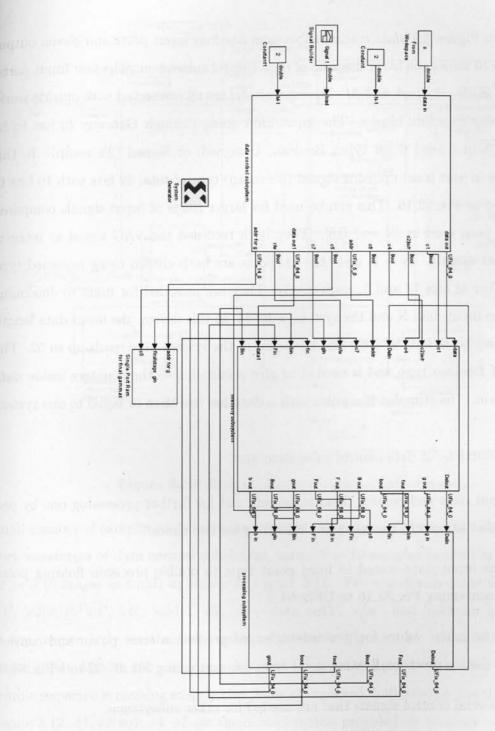

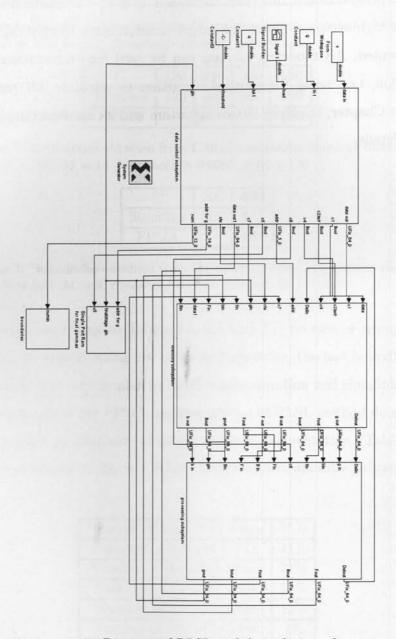

Figure 3.8 shows the conceptual diagram of the whole RLSL system. It consists of four subsystems: data control subsystem, memory subsystem, processing subsystem and final gammas subsystem. The data control subsystem has data communication with all other subsystems. It collects the input data and controls the data flow into other subsystems sample by sample. It also generates several logic control signals for the rest of subsystems

to make the whole system working correctly. memory subsystem has data communication with the processing subsystem as for each sample, the values of parameters for each stage are required to store in memories for further samples or further stages. The final gammas subsystem stores the conversion factor values of the last stage for each sample. This final gammas subsystem could be omitted when used for real-time processing. When used for real-time adaptive segmentation, the threshold is supposed to be known to the user, hence, each new updated final  $\gamma_c$  value can be compared with the threshold immediately without storing.

Figure 3.8: Block diagram of RLSL system

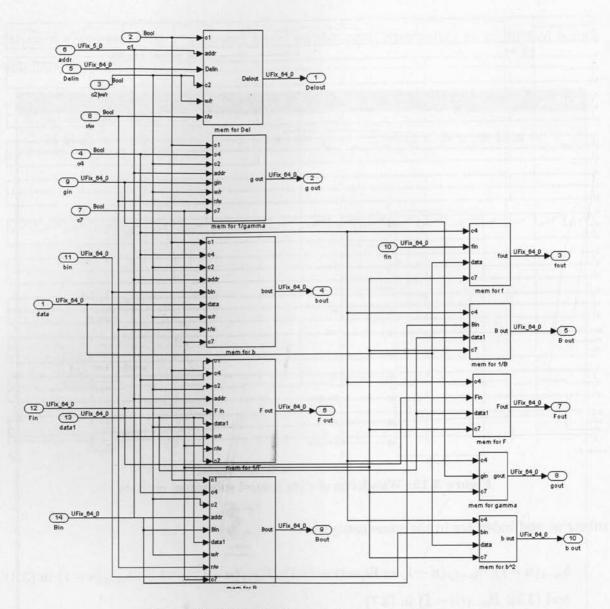

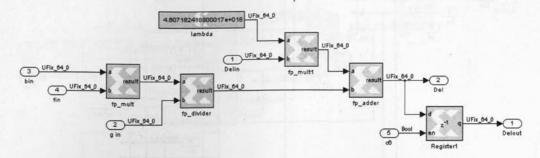

Figure 3.9 shows the real top-level models of RLSL system built in Simulink block level using System generator. Similar to the conceptual diagram of RLSL system, the real RLSL system built in Simulink block level also has four subsystems: *data control, memory, processing and for final gammas.*

Figure 3.9: Top-level model of RLSL system

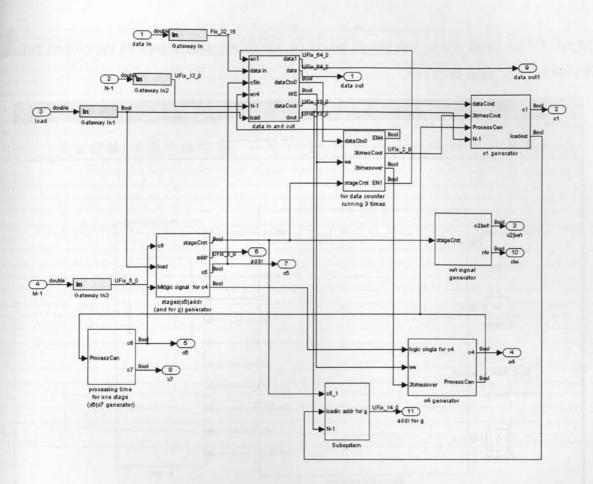

As shown in Figure 3.9, data control subsystem has four input ports and eleven output ports. Figure 3.10 shows the block diagram of data control subsystem. The four input ports, named as data in, N - 1, load, and M - 1, respectively, are all connected with outside world by using Gateway In xilinx blocks. The input data going through Gateway In has to be converted into Xilinx fixed point type: Boolean, Unsigned, or Signed (2's comp). In this design, the data in port is set up using signed (2's comp) type of total 32 bits with 16 bits in fraction, marked as Fix\_32.16. This can be used for larger range of input signals compared with what has been used in [6] and [18]. They both recorded the VAG signal as integers using 12 bits per sample. 'N - 1' and 'M - 1' ports are both chosen using unsigned type with total number of bits 13 and 5, respectively. They are provided for users to determine the length of the input data N and the system order M. In this design, the input data length for processing can be as long as 5000 and the order of the system may reach up to 32. The 'load' port is of Boolean type and is needed to give a stimulus to the counters inside data control subsystem. The stimulus is a pulse with a duration less than or equal to one system clock cycle.

The main functions of data control subsystem are:

- collect input data and control them to be sent out for further processing one by one from the first sample to the last sample looping for two times.

- convert the input data stored in fixed point type to double precision floating point type, i.e. converting Fix\_32\_16 to UFix\_64\_0.

- 3. calculate the initial values for forward/backward prediction error power and convert them into double precision floating point type, i.e. converting Fix\_63\_32 to UFix\_64\_0.

4. generate several control signals that are needed for other subsystems.

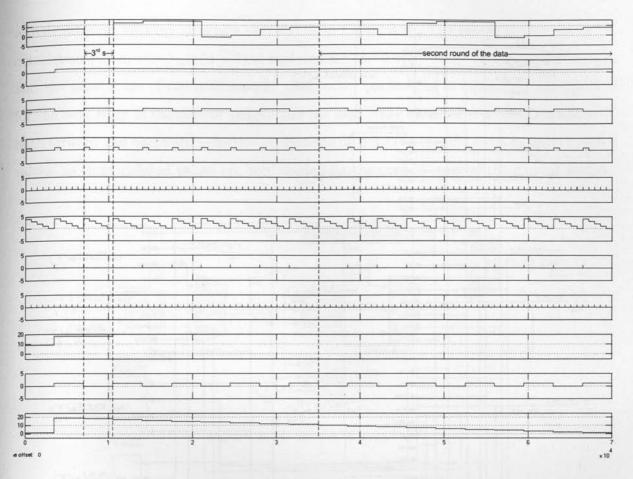

Instead of describing each sub modules within *data control* subsystem one by one, it is more efficient to show the simulation waveforms of the output ports of *data control subsystem* and see their time-sequence relationships. To make it more clear and understandable, only

Figure 3.10: Diagram blocks of data control subsystem

small number of samples and stages are used for this purpose. Figure 3.12 shows the output port waveforms of data control subsystem, using N = 10 samples in total and system order M = 5 (5 stages in total) as shown in Figure 3.11. The waveforms came from 'data out', 'c1', 'c2|w/r', 'c4', 'c6', 'addr', 'c5', 'c7', 'data out1', 'r/w', and 'addr for g', from bottom to top, respectively, as the same order as shown in Figure 3.11. Data out sends out the stored input data to the memory subsystem sample by sample. It is clear that the input sample sequence is running exactly two times as expected, indicated by the third dash line in Figure 3.12. c1, c2|w/r, c4, c7 are the control signals provided for memory subsystem. c6 is generated for the processing subsystem. c2|w/r, r/w, addr generate the read/write control signals and addresses for the RAMs in memory subsystem. data out1 sends out the initial values of  $F_0(n)$  and  $B_0(n)$  calculated based on the input data values as mentioned before, simultaneously with data out.

Figure 3.11: Simulation of data control subsystem

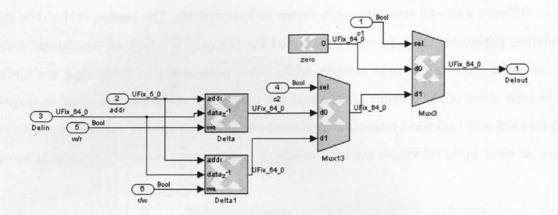

Figure 3.13 shows the block diagram of the memory subsystem. Since RLSL algorithm involves both time and order updates, different parameters need different memory unit structures to store their corresponding values. This could be explained as follows. By observing the right-hand sides of Equation (3.1)-(3.8), it is easy to find out that all the parameters can be divided into three categories as listed below. Those parameters that have the same

Figure 3.12: Waveforms of data control subsystem outputs

subscript and index are in the same category.

- 1.  $b_{m-1}(n-1)$ ,  $\gamma_{m-1,c}(n-1)$  in Equation (3.1);  $F_{m-1}(n-1)$  in (3.3);  $b_{m-1}(n-1)$  in (3.4) and (3.5);  $B_{m-1}(n-1)$  in (3.7)

- 2.  $f_{m-1}(n)$  in (3.1);  $B_{m-1}(n)$  in (3.2);  $f_{m-1}(n)$  in (3.4) and (3.5);  $F_{m-1}(n)$  in (3.6);  $\gamma_{m-1,c}(n), b_{m-1}(n), B_{m-1}(n)$  in (3.8)

- 3.  $\Delta_{m-1}(n-1)$  in (3.1)

Parameters in the same category share the same block structures in *memory* subsystem. Figure 3.14 shows the memory unit for category 1, whereas Figure 3.15 shows the memory

PROPERTY OF RYERGON UNIVERSITY LIBRARY

Figure 3.13: Block diagram of memory subsystem

unit for category 2 and Figure 3.16 shows the memory unit for category 3. It is obvious that the memory unit for category 2 is simpler than that of category 1. This is because for the current sample, those parameters in category 2 just require the values of previous stage of the same sample, not requiring the values of previous stage of the previous sample as what is required in category 1. One should also notice that, although  $\Delta_{m-1}(n-1)$  in Equation (3.1) has the same subscript and index as those parameters in category 1, it has a little different memory structure unit shown in Figure 3.16. The reason is that the crosscorrelation parameter  $\Delta_{m-1}(n-1)$  is updated for the current stage of the current sample and the same stage of the next sample, while other parameters in category 1 are updated for the next stage of the current sample and the next stage of the next sample. In addition, both forward and backward reflection coefficients do not need specific memory units to store values, as their updated values are only needed for the current stage of the current sample.

Figure 3.14: Blocks of mem for F

Figure 3.15: Blocks of mem for f

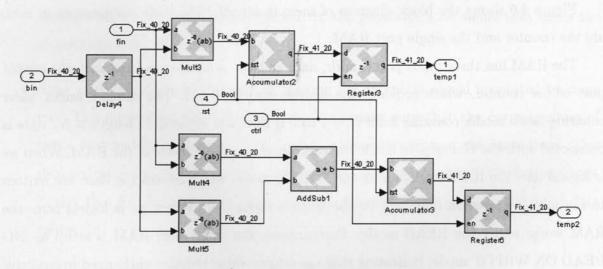

Figure 3.17 shows the block diagram of processing subsystem. It consists of eight subsystems calculating and updating the eight parameters as shown in the figure. The implemented system achieves indirectly RLSL algorithm, since it calculates cross-correlation  $\Delta_{m-1}$  first and then updates reflection coefficients. Hence, the modules of calculating  $\Delta_{m-1}$  and reflec-

Figure 3.16: Blocks of mem for Delta

tion coefficients are in series. However, after calculating forward/backward reflection coefficients, the forward/backward prediction errors, forward/backward prediction error powers and the conversion factor  $\gamma_c$  are all calculated in parallel, all of which send out the updated parameter values to the memory subsystem and store them into corresponding memories for the demand of next stage and/or sample.

Recalling the mathematical equations of RLSL algorithm described earlier in this chapter, to save floating point operation blocks, substitute the sign of minus in Equation (3.2) and (3.3) into Equation (3.4), (3.5), (3.6), and (3.7), and thus obtain the new equations for calculating forward/backward reflection coefficients, and for updating forward/backward prediction errors, forward/backward prediction error powers as follows.

$$\gamma_{m,f}(n) = \frac{\Delta_{m-1}(n)}{B_{m-1}(n)}$$

(3.13)

$$\gamma_{m,b}(n) = \frac{\Delta_{m-1}(n)}{F_{m-1}(n-1)}$$

(3.14)

$$f_m(n) = f_{m-1}(n) - \gamma_{m,f}(n)b_{m-1}(n-1)$$

(3.15)

$$b_m(n) = b_{m-1}(n-1) - \gamma_{m,b}(n)f_{m-1}(n)$$

(3.16)

Figure 3.17: Block diagram of processing subsystem

$$F_m(n) = F_{m-1}(n) - \gamma_{m,f}(n)\Delta_{m-1}(n)$$

(3.17)

$$B_m(n) = B_{m-1}(n-1) - \gamma_{m,b}(n)\Delta_{m-1}(n)$$

(3.18)

Figure 3.18 shows the block diagram of *Delta* for calculating  $\Delta_{m-1}$  values. It has two floating point multipliers, one floating point divider and one floating point adder as the same number processing units in Equation 3.1. Another register is used to store the calculated  $\Delta_{m-1}$  values and wait for the control signal to let it send out the calculated  $\Delta_{m-1}$  value to its corresponding memory.

Figure 3.18: Block diagram of Delta

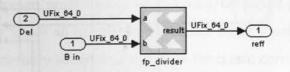

Figure 3.19: Block diagram of refcoef f

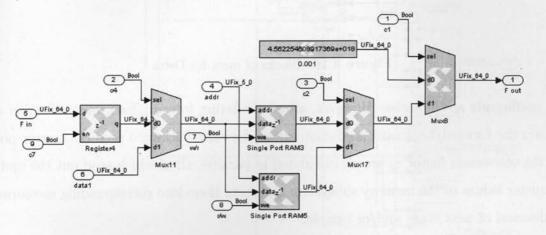

Figure 3.19 shows the block diagram of refcoef f for calculating forward reflection coefficient as in Equation (3.13). It just has one floating point divider since (3.13) has just one division operation. Similarly, the model of calculating backward reflection coefficient is exactly the same as computing forward reflection coefficient: it also has only one floating point divider. The only difference for these two models is their different input port connections. For forward reflection model, the denominator of the divider is connected with B in, while for backward reflection model, it is connected with F in. Apparently, the output ports are different: one is reff and the other is refb, representing forward reflection coefficient and backward reflection coefficient respectively.

Figure 3.20 shows the block diagram F update for updating forward prediction error power. It consists of one floating point multiplier and one floating point subtracter. Similarly, one extra register is used to store the updated values. It holds the same function as Equation (3.17) does. According to Equation (3.15)-(3.18), the modules of updating back-

Figure 3.20: Block diagram of F update

ward prediction error power and updating forward/backward prediction error have exactly the same blocks as F update module shown in Figure 3.20. The only difference for these four models is their different input port connections.

Figure 3.21: Block diagram of gamma update

Figure 3.21 shows the block diagram of gamma update for updating conversion factor  $\gamma_c$  values. It consists of one floating point multiplier, one floating point divider and one floating point subtracter as the same operations in Equation (3.8). Also, another register is used to store the updated  $\gamma_c$  values and wait for being sent out to its corresponding memory.

Figure 3.22: Block diagram of final gammas subsystem

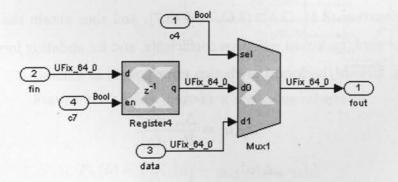

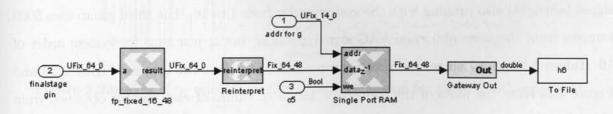

Figure 3.22 shows the block diagram of for final gammas subsystem. In this subsystem,

the floating point data is converted back to fixed point Fix\_16\_48 first and then sent out and stored in a single port RAM for the convenience of further application. The depth of this single port RAM is double-sized as the length of the input samples. However, for real-time purpose application, the threshold is supposed to be known, and then each final  $\gamma_c$  value could be compared with the threshold instantaneously, and there is no need to have a RAM for storing all the  $\gamma_c$  values for all input data.

#### 3.4.2 Simulation results and Comparison with high-level language

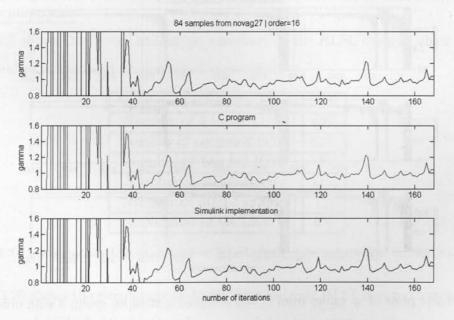

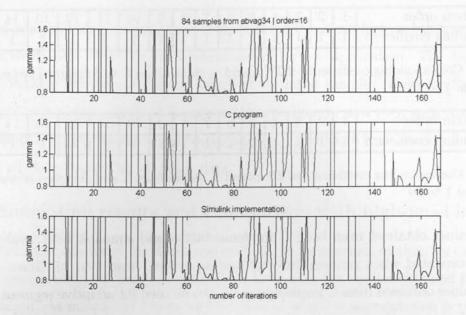

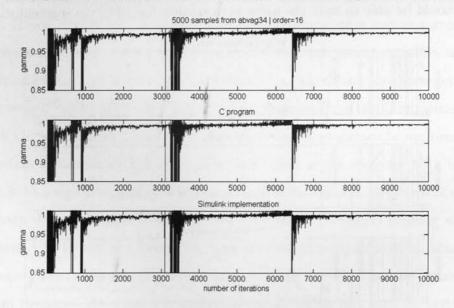

To test the functionality of the RLSL system built in the previous section, we compare the simulation results obtained from simulink block level with the results obtained from the C implementation. As mentioned before, the purpose of adaptive segmentation is to calculate and obtain the second round conversion factor value  $\gamma_c$  of each sample to be compared with a threshold. Hence, the second round  $\gamma_c$  values are more important and extracted compared with C implementation. In addition, the trend of the second round  $\gamma_c$  values of the target signal is more significant than the absolute values of  $\gamma_c$ . Therefore, the corresponding coefficient of the second round conversion factor values obtained from the C implementation and the simulink block implementation have been calculated to evaluate the performance of the designed system at simulink block level. The input data is the same for both implementations, taken from a real VAG signal. The comparison is based on three groups of simulations. The first group uses 84 samples from a normal VAG signal (novag27) running with the system order from 1 to 16 and the second one uses another 84 samples from an abnormal VAG signal (abvag34) also running with the system order from 1 to 16. The third group uses 5000 samples from the same abnormal VAG signal abvag34, but it just runs for system order of 16. Tables 3.1 and 3.2 shows the result comparison of the first two groups. Figure 3.23 and Figure 3.24 show the plots of the conversion factor  $\gamma_c$  values of each sample obtained from C implementation and the simulink block implementation running with system order of 16 in the first two groups. Figure 3.25 shows the  $\gamma_c$  values of each sample in group 3.

In conclusion, according to Table 3.1 and 3.2, the corresponding coefficients for the second

| system order              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| corresponding coefficient | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

**Table 3.1:** Corresponding coefficients of  $2^{nd}$  round  $\gamma_c$  values from C and designed system for group 1; order from 1 to 16

| system order              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| corresponding coefficient | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

**Table 3.2:** Corresponding coefficients of  $2^{nd}$  round  $\gamma_c$  values from C and designed system for group 2; order from 1 to 16

round  $\gamma_c$  values obtained from both C implementation and simulink level implementation are 100% correlated when running different system orders: from 1 to 16. Since the second round  $\gamma_c$  values obtained from C implementation can be used for adaptive segmentation with a good performance, the conversion factors obtained from the designed system at simulink block level should be able to have the same performance for adaptive segmentation as well.

Figure 3.23: plots of  $\gamma_c$  values from C and designed system for group 1 with order of 16

Moreover, according to Figures 3.23, 3.24, and 3.25, the  $2^{nd}$  round  $\gamma_c$  values (from 85 to 168 in x axis of the first two and from 5001 to 10000 in x axis of the third one) obtained from C implementation and the designed system at simulink block level match very well. Thus,

Figure 3.24: plots of  $\gamma_c$  values from C and designed system for group 2 with order of 16

it is concluded that the RLSL system implemented on simulink block level works correctly and satisfactory as C implementation does.

# 3.5 Implementation of RLSL on FPGA and result comparison

After building up the models in Simulink block level, the System generator tool can generate the synthesizable VHDL or verilog code for the design, which can be imported into Xilinx ISE for further design implementation. Xilinx ISE tool can do synthesis, implementation (translate, map, place & route) and device programming for the target design. Behavioral simulation is supported by Mentor Graphics ModelSim. After downloading the design to FPGA successfully, the verification can be achieved by using Xilinx ChipScope Pro tool.

For the design of RLSL, VHDL code is chosen for system generator. The clock frequency is selected as 20MHz. The maximum data length for processing according to the physical design is 5000 samples. The maximum system order for processing according to the physical design is 32. The target FPGA device is xc2vp100-6-ff1704.

#### Area Requirements

Table 3.3 shows the device utilization summary of the RLSL design, which is provided by ISE tool after it has been implemented successfully.

| Number of Slice Flip Flops | 54% |

|----------------------------|-----|

| Number of 4 input LUTs     | 40% |

| Number of occupied Slices  | 61% |

| Number of bonded IOBs      | 11% |

| Number of Block RAMs       | 11% |

| Number of MULT18X18s       | 1%  |

| Number of GCLKs            | 6%  |

Table 3.3: Device utilization summary of RLSL design; target device: xc2vp100-6-ff1704

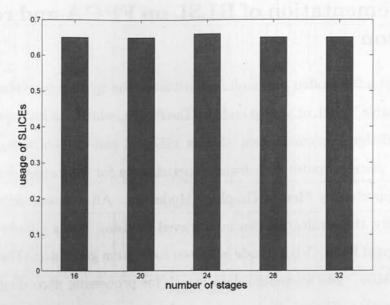

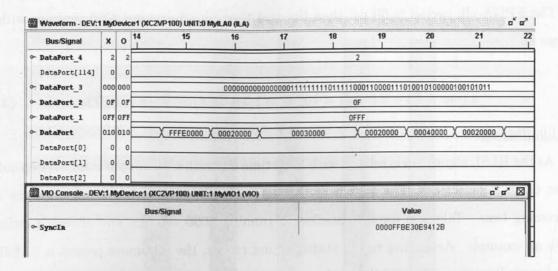

Figure 3.26 shows the percentage of device slice usage of RLSL design running under different system orders, including testbenches for each implementation. The system is running under the order of 16, 20, 24, 28, 32, respectively, with a total of 4096 input data samples.

According to Table 3.3 and Figure 3.26, it is clear that the RLSL FPGA implementation occupies around 61% source of the target device and more importantly, when running different orders (from 16 to 32), the area of the occupied slices does not change much (in

Figure 3.26: Comparison of the device slice usage of RLSL algorithm with different orders, including testbench for each implementation

that the testbench also occupies some source, hence it certainly has some difference, but not much). This is what it is expected, as the whole RLSL design holds the same architecture for each stage of each sample.

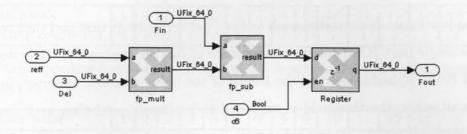

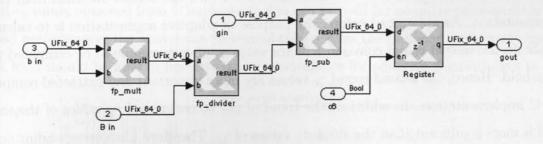

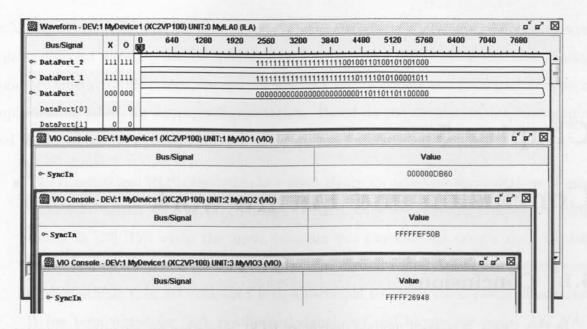

#### Clock and Timing