#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2011

## Five-level parallel current source converter for high power drives with DC current balance control and superior harmonic performance

Navid Binesh *Ryerson University*

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

#### **Recommended** Citation

Binesh, Navid, "Five-level parallel current source converter for high power drives with DC current balance control and superior harmonic performance" (2011). *Theses and dissertations*. Paper 830.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# Five-Level Parallel Current Source Converter for High Power Drives with DC Current Balance control and Superior Harmonic Performance

By

**Navid Binesh** Bachelor of Science, University of Tehran, Tehran, Iran, 2008

> A thesis presented to Ryerson University in partial fulfillment of the requirements for the degree of MASc in the program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2011 © Navid Binesh, 2011

### **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

## Borrower's Page

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

| NAME | ADDRESS | SIGNATURE | DATE |

|------|---------|-----------|------|

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

|      |         |           |      |

### Five-Level Parallel Current Source Converter for High Power Drives with DC Current Balance Control and Superior Harmonic Performance

Navid Binesh Master of Applied Science Electrical and Computer Engineering Ryerson University, Toronto, 2011

### Abstract

In this thesis, space vector modulation is developed for a 5-level parallel current source converter for high power drives. The modulation scheme is designed to bring superior harmonic performance to the currents on the AC sides. This method synthesizes the rotating reference current vector in the converter's space vector plane with three adjacent switching vectors. Unbalanced currents of DC links become a practical challenge when two converters are connected in parallel. To balance the DC currents, the proper switching state for every Small and Medium switching vector is chosen from redundant switching states corresponding to the vector based on circuit circumstances and the designed switching sequence. Simulated results verify the effectiveness of the method. In addition, the switching sequence is designed to lower the switching frequency and minimize the switching loss. Finally, the proposed converter and switching scheme are simulated and steady state and dynamic performance are investigated in detail.

### Acknowledgment

The work presented in this thesis was carried out in the Laboratory of Electric Drive Application and Research LEDAR at Ryerson University.

I would like to thank all people who have helped and inspired me during my study.

First and foremost I would like to express my sincerest gratitude to my supervisor, Professor Bin Wu for his invaluable guidance, generous support, and consistent kindness throughout the course of the work.

I would like to convey special appreciation to all my friends in LEDAR, especially Dr. Jingya Dai, Dr. Jiacheng Wang, Dr. Fangrui Liu, Ning Zhu and Miad Mohaghegh Montazeri for many fruitful discussions and joyful time we shared together. Thanks are gratefully extended to Dr. Navid R. Zargari and other colleagues at Rockwell Automation Canada for their worthy advices.

I thankfully acknowledge financial supports from Ryerson University, professor Bin Wu and Rockwell Automation Canada.

One thing that is beyond doubt is that my studies would not have been completed without understanding and support of my aunt, Nazanin, my uncle, Reza and my cousin, Mahan.

It gives me immense pleasure to thank my girlfriend, Leila for all love and encouragement she gave me.

Last but not the least I should humbly thank my mother, Zhila my father, Rasool and the dearest sisters, Sevgili and Gilda who brought color, warmth and energy to my life. They were always supporting and inspiring me with their best wishes.

Dedicated to my grandmother

## Table of Contents

| Author's Declarationiii                                                   |

|---------------------------------------------------------------------------|

| Borrower's Pagev                                                          |

| Abstract vii                                                              |

| Acknowledgment ix                                                         |

| Table of Contents                                                         |

| List of Figures, Tables and Appendicesxv                                  |

| List of Tables xv                                                         |

| List of Figuresxvi                                                        |

| List of Appendicesxvi                                                     |

| Chapter 1 Introduction                                                    |

| 1.1 Single bridge current source converter                                |

| 1.2 Multi-level current source converter                                  |

| 1.2.1 Multi-level current source rectifier                                |

| 1.2.2 Multi-level current source inverter7                                |

| 1.3 PWM switching schemes                                                 |

| 1.3.1 Trapezoidal pulse-width modulation                                  |

| 1.3.2 Selective harmonic elimination                                      |

| 1.3.3 Space vector modulation 10                                          |

| 1.3.4 Comparison of modulation schemes 11                                 |

| 1.4 Objectives                                                            |

| 1.5 Thesis outline                                                        |

| Chapter 2 Space Vector Modulation for 5-Level Current Source Converter 17 |

| 2.1 Introduction                                                          |

| 2.2 Switching states                                                      |

| 2.3 Space vectors                                                         |

| 2.3.1 Large vectors                                                       |

| 2.3.2 Medium vectors                                                      |

| 2.3.3 Small vectors                                                       |

| 2.3.4 Zero vector                                                         |

| 2.4 Space vector diagram                                                  |

| 2.5      | Vector selection                                                                 | . 28 |

|----------|----------------------------------------------------------------------------------|------|

| 2.6      | Space vector order design to achieve the minimized switching frequency           | . 33 |

| 2.7      | Dwell times                                                                      | . 39 |

| 2.8      | Procedure summary                                                                | . 43 |

| 2.9      | Conclusion                                                                       | . 43 |

| Chapter  | 3 DC Current Balance Control                                                     | . 45 |

| 3.1      | Introduction                                                                     | . 45 |

| 3.2      | Unbalanced DC currents                                                           | . 45 |

| 3.3      | Effect of space vectors on DC currents                                           | . 47 |

| 3.4      | DC current balance control method                                                | . 54 |

| 3.5      | Switching sequence design                                                        | . 56 |

| 3.6      | DC current balance control performance                                           | . 59 |

| 3.7      | Conclusion                                                                       | . 61 |

| Chapter  | 4 Performance Study - Simulation                                                 | . 63 |

| 4.1      | Introduction                                                                     | . 63 |

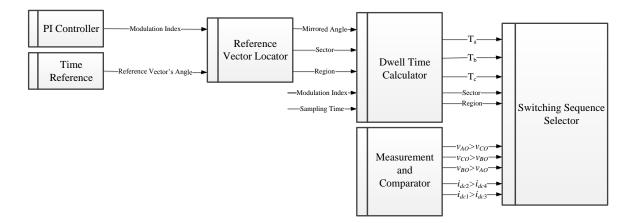

| 4.2      | Modeling the Five-level CSC and SVM in Simulink                                  | . 63 |

| 4.2.     | 1 Five-level current source converter                                            | . 63 |

| 4.2.2    | 2 Space vector modulation                                                        | . 65 |

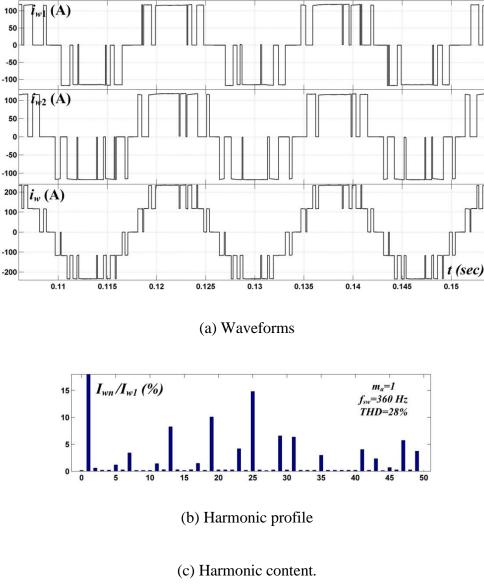

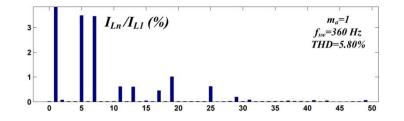

| 4.3      | Steady state analysis - Harmonic performance                                     | . 66 |

| 4.3.     | 1 Rectifier                                                                      | . 67 |

| 4.3.2    | 2 Inverter                                                                       | . 70 |

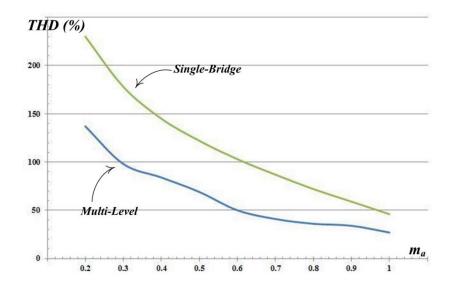

|          | 3 Harmonic performance comparioson between single-bridge and multi-level convert |      |

|          |                                                                                  |      |

|          | 4 Harmonic performance at different switching frequencies                        |      |

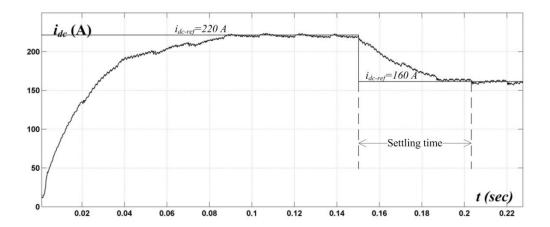

| 4.4      | Dynamic analysis – DC current and load voltage control                           |      |

|          | 1 DC current control                                                             |      |

|          | 2 AC load voltage control                                                        |      |

| 4.5      | Conclusion                                                                       |      |

| Chapter  |                                                                                  |      |

| 5.1      | Contributions and conclusions                                                    |      |

| Appendi  |                                                                                  |      |

| Appendi  |                                                                                  |      |

| Appendi  |                                                                                  |      |

|          | ces                                                                              |      |

| Glossary | of Acronyms and Symbols                                                          | 117  |

## **List of Figures, Tables and Appendices**

### List of Tables

| Table 2-1 Switching states.                                               |  |

|---------------------------------------------------------------------------|--|

| Table 2-2 Large switching states.                                         |  |

| Table 2-3 Medium switching states.                                        |  |

| Table 2-4 Small switching states.                                         |  |

| Table 2-5 Zero switching states.                                          |  |

| Table 2-6 Space vectors specifications.                                   |  |

| Table 2-7 Selected vectors for each triangular area of space vector plane |  |

| Table 2-8 Vector order- sector 1, region 3                                |  |

| Table 2-9 Vector order- sector 1, region 2                                |  |

| Table 2-10 Vector order- sector 1, region 4                               |  |

| Table 2-11 Vector order- sector 1, region 1, Down triangle                |  |

| Table 2-12 Vector order- sector 1, region 1, Up triangle                  |  |

| Table 2-13 Dwell times of space vectors.                                  |  |

|                                                                           |  |

| Table 3-1 Effect of switching states of Medium vector $\vec{I}_7$ on DC currents                     | 50 |

|------------------------------------------------------------------------------------------------------|----|

| Table 3-2 Redundant switching states of Small vector $\vec{I}_{13}$                                  | 51 |

| Table 3-3 Employed switching states of Small vector $\vec{I}_{13}$                                   | 52 |

| Table 3-4 Effect of switching states of Small vector $\vec{I}_{13}$ on DC currents (region 1)        | 52 |

| Table 3-5 Effect of switching states of Small vector $\vec{I}_{13}$ on DC currents (region 6)        | 53 |

| Table 3-6 Selected switching states of $\vec{l}_{7}$ at distinctive circuit circumstances.           | 55 |

| Table 3-7 Selected switching state of $\vec{I}_{13}$ at distinctive circuit circumstances (region 1) | 55 |

| Table 3-8 Selected switching state of $\vec{I}_{13}$ at distinctive circuit circumstances (region 6) | 55 |

| Table 3-9 Switching sequence look-up table- sector 1, region 3                                       | 56 |

| Table 3-10 Switching sequence look-up table- sector 1, region 2                                      | 57 |

| Table 3-11 Switching sequence look-up table- sector 1, region 4                                      | 57 |

| Table 3-12 Switching sequence look-up table- sector 1, region 1, Down triangle                       | 58 |

| Table 3-13 Switching sequence look-up table- sector 1, region 1, Up triangle                         | 58 |

|                                                                                                      |    |

| Table 4-1 THD comparison of $i_w$ at different $m_a$ values                          | 74 |

|--------------------------------------------------------------------------------------|----|

| Table 4-2 Low order harmonics comparison $(m_a=1)$ .                                 | 75 |

| Table 4-3 THD of $i_w$ and $i_L$ at different switching frequencies when $(m_a=1)$ . | 76 |

| Table 4-4 Investigation of dynamic performance of rectifier                          | 80 |

### List of Figures

| Fig. 1-1 Single-bridge current source converters                                            |    |

|---------------------------------------------------------------------------------------------|----|

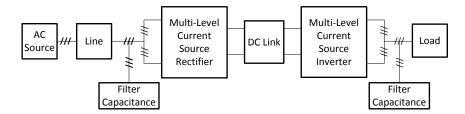

| Fig. 1-2 System block diagram                                                               | 6  |

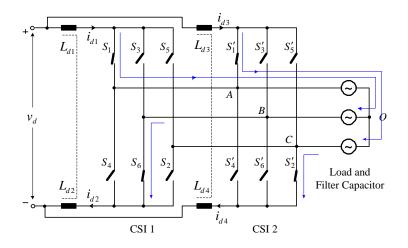

| Fig. 1-3 5-level parallel current source rectifier                                          | 7  |

| Fig. 1-4 5-level current source inverter                                                    | 8  |

|                                                                                             |    |

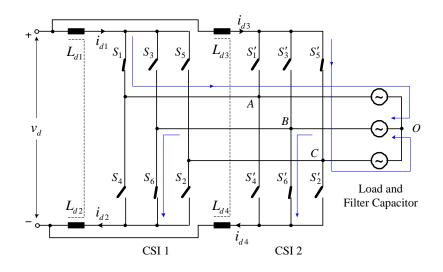

| Fig. 2-1 Current paths in parallel inverters with switching state [16 56]                   | 19 |

| Fig. 2-2 Space vector diagram                                                               |    |

| Fig. 2-3 Space vector diagram- region numbering                                             | 29 |

| Fig. 2-4 Space vector plane (sector one)                                                    |    |

| Fig. 2-5 Space vector plane- sector 1, region 3                                             | 34 |

| Fig. 2-6 Space vector plane- sector 1, region 2                                             | 35 |

| Fig. 2-7 Space vector plane- sector 1, region 4                                             |    |

|                                                                                             |    |

| Fig. 3-1 Current paths in parallel inverters with switching state [12 16]                   | 48 |

| Fig. 3-2 Current paths in parallel inverters with switching state [16 12]                   | 49 |

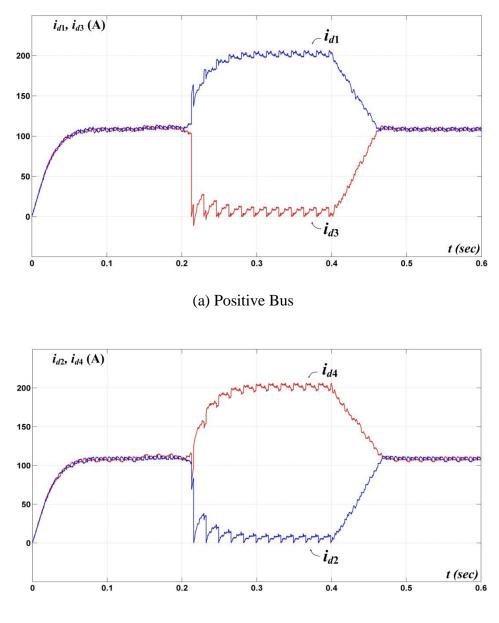

| Fig. 3-3 DC link currents with and without current balance control ( $L_d=1.5 pu$ )         | 60 |

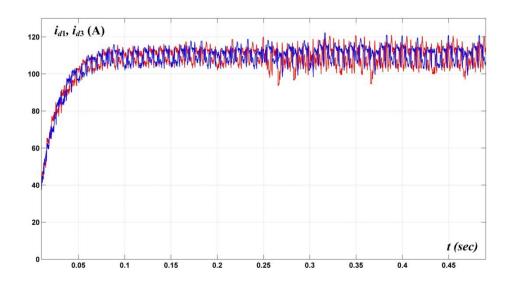

| Fig. 3-4 Positive DC link currents under asymmetrical circuit parameters with current balan |    |

| control ( $L_d=0.75 pu$ )                                                                   |    |

|                                                                                             |    |

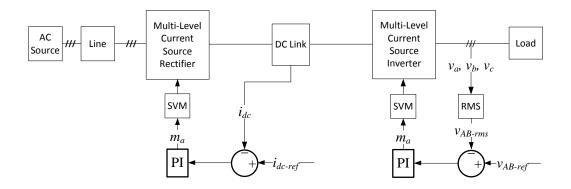

| Fig. 4-1 Converter system configuration                                                     | 64 |

| Fig. 4-2 Model of space vector modulation                                                   | 66 |

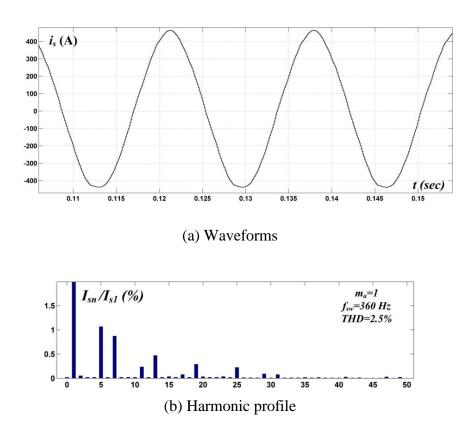

| Fig. 4-3 Input current of rectifier $i_w$ ( $m_a=1$ )                                       | 68 |

| Fig. 4-4 AC line current $i_s$ ( $m_a=1$ )                                                  |    |

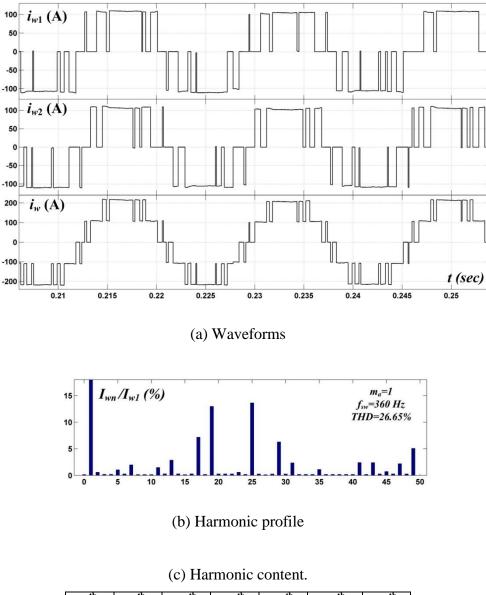

| Fig. 4-5 Output current of inverter $i_w$ ( $m_a=1$ )                                       |    |

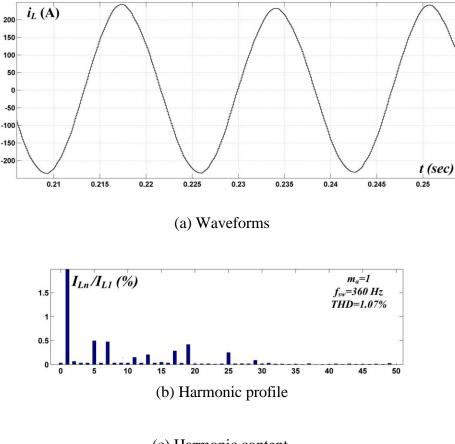

| Fig. 4-6 AC load current $i_L$ ( $m_a=1$ , $C_f=0.3 pu$ )                                   | 72 |

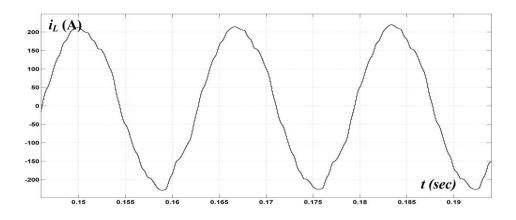

| Fig. 4-7 AC load current $i_L$ ( $m_a=0.95$ , $C_f=0.1$ pu)                                 |    |

| Fig. 4-8 THD comparison of $i_w$ at different $m_a$ values                                  |    |

| Fig. 4-9 PI controller block diagram                                                        |    |

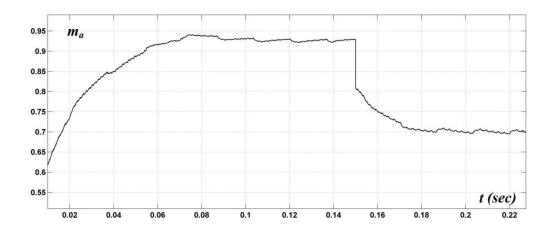

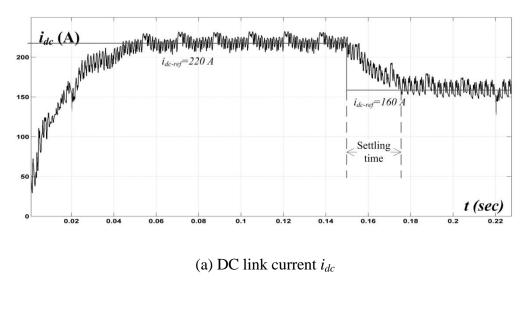

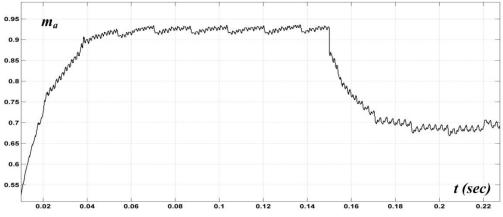

| Fig. 4-10 DC link current control ( $L_d=1.5 pu$ )                                          |    |

| Fig. 4-11 DC link current control ( $L_d=0.3 pu$ )                                          |    |

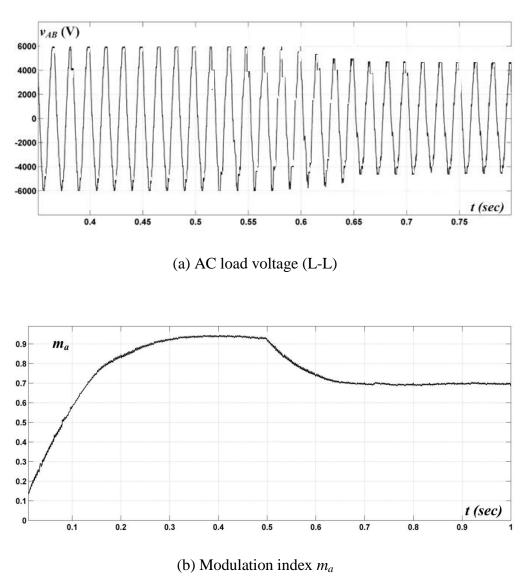

| Fig. 4-12 Load voltage control                                                              |    |

### List of Appendices

| Appendix I   | Effect of Medium vectors on DC currents | 91 |

|--------------|-----------------------------------------|----|

| Appendix II  | Effect of Small vectors on DC currents  | 95 |

| Appendix III | Switching Sequence Look-Up Tables 1     | 03 |

## Chapter 1 Introduction

Recent demand for speed drives in industrial applications at high power and medium voltages has prompted researchers to focus on multi-level converters. Multi-level voltage source inverter (VSI) drives have been applied in many industrial applications. In addition, to provide a higher power range, multi-level VSIs have some other benefits such as reductions in harmonics,  $\frac{dv}{dt}$ , electromagnetic interference and filter size. The most typical topologies include diode clamped inverters, H-bridge inverters and flying capacitor multi-level inverters. Since many voltage levels are needed in very high power usage, some problems limit the drives' functionality. Complex capacitor voltage control in diode clamped, costly and bulky phase-shifting transformer and reduced reliability caused by using so many low power components in H-bridge, and large amount of capacitors and pre-charged circuits in flying capacitor multi-level VSIs reduced the practical usage of these drives [1].

Voltage source converters (VSC) are widely used in industry, while current source converters (CSC) are primarily applied when fast dynamic performance is not needed such as in fans and pumps [2]. The PWM current source inverter (CSI) was proposed in the early 1970s [3] and gained more attention during the 1980s [4]. In comparison to VSCs, CSCs have a simpler topology with a lower switch count, friendly waveforms, inherent four quadrant operation and reliable overcurrent and short-circuit protection [5, 6].

In this thesis, a multi-level CSC is proposed for high and very high power applications. Comprehensive work was carried out to modify and develop space vector modulation (SVM) that not only brings superior harmonic performance, but also provides a DC current balance control. This chapter introduces and analyzes single-bridge CSCs followed by elaboration of a multi-level CSC topology. The organization of the thesis is summarized at the end.

#### **1.1 Single bridge current source converter**

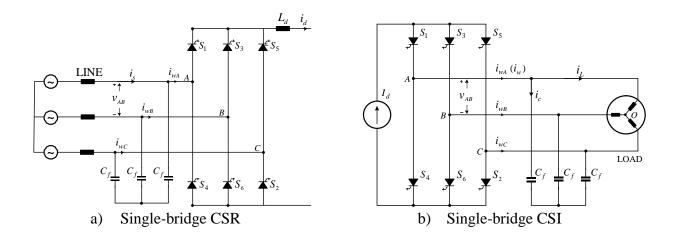

Fig. 1-1 shows a single-bridge current source rectifier (CSR) and a single-bridge current source inverter (CSI).

Fig. 1-1 Single-bridge current source converters.

Six switches, two switches per leg, constitute every single-bridge CSC. Today, symmetrical type GCT devices with a reverse voltage blocking are used in CSCs. This kind of switches does not need anti-parallel free-wheeling diodes. When the rectifier is used as a front end in high power MV drives, two or more GCTs can be connected in series to provide a higher range of voltage.

Three-phase capacitors used in the input terminal of CSR and the output terminal of CSI are necessary in the commutation process. When each switch changes its state from ON to OFF, the current in that switch decreases to zero in a very short time. This current needs a path to continue during the short commutation time or a huge voltage spike will be induced that damages the switching devices. Three-phase capacitor  $C_f$  provides the path for the current of switches during the commutation of devices. In addition, the capacitors act as a high frequency harmonic filter, improving the AC current and the AC voltage waveforms. The capacitor's per-phase value depends on the switching frequency and the THD required for the line current. In addition, the input power factor and LC resonant mode should be counted on the rectifier side. Normally the capacitor per-phase value would be in the range of 0.3 to 0.6 pu for a high power CSC operating with a switching frequency of a few hundred Hz.

A DC choke  $L_d$  is required for each DC link to maintain the DC output current within an acceptable range. Generally, the DC current should contain less than 15% ripple. The size of the DC choke is normally in the range of 0.5 to 0.8 pu.

PWM strategies are applied to generate acceptable input and output waveforms. Different switching strategies yield distinctive performances which may be applied in industry. It is very critical to analyze each of these features in order to match industry demand. Generally speaking, selective harmonic elimination (SHE) switching strategy provides higher harmonic performance, whereas SVM switching pattern brings higher dynamic performance and variable modulation index  $m_a$  to the converter [6-8].

CSC possesses its own features, merits and drawbacks which are detailed as following [6-10].

1) Simple converter topology

CSC employs symmetrical gate commutated thyristor (GCT) devices. The AC voltage can reach up to 6.6 kV by simply connecting devices in series. Therefore, the topology retains its simplicity and low device count even at high voltages. This feature is favorable in applications at high power and medium voltage.

2) AC line and AC load friendly waveforms

Employing PWM causes the input current of CSR and the output current of CSI to exhibit chopped-shaped waveforms. The three-phase capacitor will filter the chopped waveforms resulting in power supply side and load side currents that are close to sinusoidal. In addition, CSC inherently avoids high dv/dt and wave reflection issues.

3) Limited device switching frequency

To minimize power losses and device thermal stress, the device's switching frequency is usually limited to some hundred Hz.

#### 4) Reliable short-circuit and overcurrent protection

VSC generates a large amount of short-circuit current because of the high voltage across the DC link capacitor and the very small inductance between the rectifier and the power supply. In contrast, DC link inductances of CSC limits the current changing rate if a line short-circuit fault occurs.

5) Limited dynamic performance

The main drawback of a CSC is its limited dynamic performance, which is caused by the large DC link inductance. In addition, a switching scheme such as SHE provides less flexibility. Advancements in device characteristics and optimized modulation schemes can improve the dynamic performance of CSC.

6) Possible LC resonances

The three-phase filter capacitor increases the possibility of LC resonances between the harmonic filter and the line inductances. Some active damping and power factor control methods are introduced to mitigate the possible resonances [11].

As mentioned, symmetrical GCT devices are used in CSCs. The input voltage is chosen from common medium range voltages including 2.3 kV, 3.3 kV, 4.16kV and 6.6kV. The output power rating is from 0.1 MW to 7 MW. Power demand in medium voltage applications such as pumps, fans, compressors and conveyors has been increased to more than 15 MW. Therefore, single-bridge CSC is unable to satisfy power demand of some drive applications. The need for drives with higher power ratings encourage researcher to extend work on high power drives. Multi-level CSC is one of the available solutions.

#### 1.2 Multi-level current source converter

Industry demand for a higher power range and superior performance provide a vast opportunity to devise new converters which are a combination of conventional converters. This way, multilevel and multi-module converters came up. Multi-level converters have become an accepted and thus a commercially available alternative [12].

The main advantage of multi-level CSCs is that they provide a higher range of power. Employing specific configurations and applying moderated switching modulations brings higher performance and, consequently, more industry applications. Providing lower harmonic distortion on the AC side is one of the most significant benefits of using multi-level CSC. When using PWM strategies operated at acceptable switching frequencies, multi-level CSC generates AC current and voltage waveforms which satisfy stringent harmonic requirements established by line and load standards.

On the other hand, increased size, additional mass and higher costs are inevitable when combining converters. In addition, control methods must be augmented to eliminate unwanted and adverse phenomena such as circulating current and unbalanced DC currents [13-16].

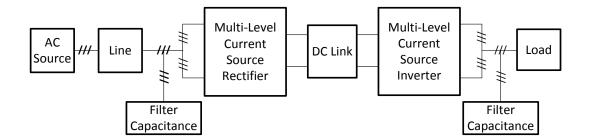

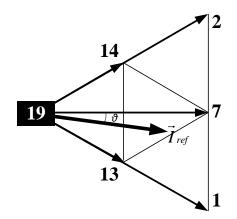

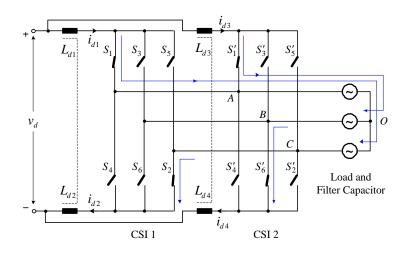

The configuration proposed and employed in this thesis is a back to back CSC, a multi-level CSR connected through a common DC link to a multi-level CSI. Each multi-level converter is built up by two parallel single-bridge CSCs. The AC source is connected to the rectifier side and the load is supplied from the inverter side. Fig. 1-2 illustrates a block diagram of the designed model.

Fig. 1-2 System block diagram

The power source is a three-phase AC voltage in the medium voltage range (i.e. 4.16 kV) connected to a three-phase line which is modeled with a resistance and an inductance in series. The circuit topology is elaborated in detail for two rectifier and inverter sides.

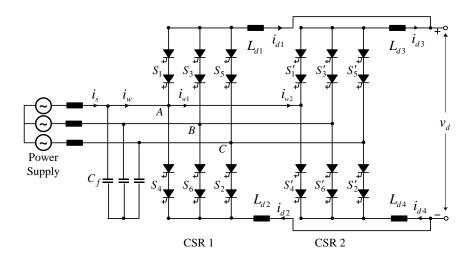

#### 1.2.1 Multi-level current source rectifier

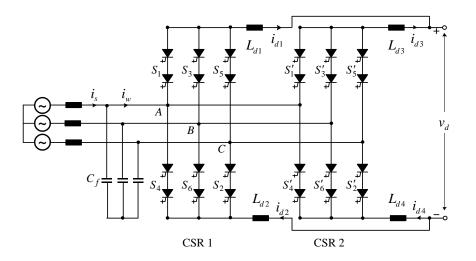

Fig. 1-3 shows a 5-level parallel CSR constituted of two parallel single-bridge rectifiers. Corresponding AC phases are connected together at the input terminals and similar DC link buses are connected at the output terminals of the multi-level rectifier. When the rectifier is used as a front end in high power MV drives, two or more GCTs can be connected in series to provide a higher range of voltage.

The three-phase capacitor  $C_f$  at the input of the CSR assists in commutation of switches and provides a high order harmonic filter. As stated, the value of the capacitor per phase depends on the switching frequency, the input power factor and the LC resonant mode. Since the AC currents and voltages greeted by the multi-level converter contain less harmonic distortion, the size of the filter capacitor can be reduced to a great extent.

To limit the DC output current ripples to an acceptable range, a 0.5-0.8 pu DC choke  $L_d$  is required for each DC link. There are a total of four DC chokes in the designed model.

Fig. 1-3 5-level parallel current source rectifier

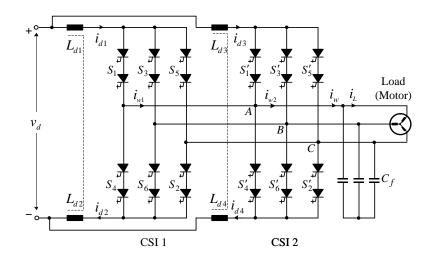

#### 1.2.2 Multi-level current source inverter

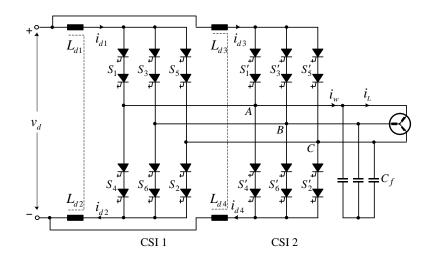

Fig. 1-4 illustrates the 5-level CSI constituted of two parallel single-bridge inverters. The inverter is fed by DC current coming from the rectifier side through four DC inductances  $L_{d1}$ -  $L_{d4}$ . A three-phase capacitor is required at the output terminal of CSI.

#### **1.3 PWM switching schemes**

Any modulation scheme for the CSI must satisfy a basic constraint. At any time instant, two and only two switches in the converter, one connected to the positive DC bus and the other to the negative, must be ON to carry the DC current.

Fig. 1-4 5-level current source inverter

The major modulation schemes for the CSC are trapezoidal pulse-width modulation (TPWM), selective harmonic elimination (SHE) and space vector modulation (SVM). The above mentioned modulation schemes can be applied to both CSR and CSI. The typical switching frequency for practical high power CSC is about 400 Hz to 600 Hz [17].

#### **1.3.1 Trapezoidal pulse-width modulation**

The TPWM method is a carrier based modulation scheme. The carrier and modulation waves for TPWM are specially designed to meet the switching constraints in CSC. The design of TPWM ensures that during a  $\frac{\pi}{3}$  period, three devices out of the six are always off. Among the remaining three, one device is always ON by keeping its carrier wave zero and modulation wave positive; the modulation and carrier waves for the other two devices are arranged to produce complementary gating signals such that only one of them is ON at any time instant. The switching constraints of CSC are thus satisfied.

TPWM is essentially an over-modulation scheme. Although it allows the modulation index to be changed from 0 to 1, the controllable range of output current magnitude is quite limited. In addition, the switching scheme does not provide satisfactory harmonic performance. This is mainly because the trapezoidal modulation waveform itself contains the 5<sup>th</sup> and 7<sup>th</sup> harmonics.

#### **1.3.2 Selective harmonic elimination**

SHE is an offline designed modulation scheme that can eliminate a number of unwanted low order harmonics with limited number of pulses. In order to achieve better harmonic performance and to reduce the complexity in finding switching patterns solutions, the pulses are normally arranged in such a way that the derived waveforms have a quarter-wave symmetrical shape. The total number of harmonics to be eliminated by the SHE, k, is related to the number of pulses in each half fundamental cycle,  $N_p$ ,

$$k = \frac{N_p - 1}{2} \tag{1.1}$$

There is one degree of freedom per each independent firing angle. Mainly, the degree of freedom gives the flexibility to either eliminate harmonics or control the magnitude. For

instance, with two firing angles, you may choose to eliminate two harmonics or eliminate a harmonic and provide an adjustable modulation index. However, a set of offline calculated angles is only valid at a certain modulation index. In practice, SHE is normally utilized with fixed modulation index. If variation of the modulation index is needed, the solutions for all the required modulation indices have to be calculated offline and stored in the system prior to operation. This adds to the complexity of system control and is not practical in real applications. Moreover, the calculation of SHE angle with a large number of pulses per fundamental cycle sometimes involves equations that have no solutions. For example, the SHE scheme is unable to eliminate 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup> and 17<sup>th</sup> simultaneously.

In addition to being able to remove low order harmonics, which is important in power systems, there is a capability to eliminate other harmonics that could cause undesired situations such as LC resonance. For instance, there may be an obligation to eliminate  $5^{th}$  and  $11^{th}$  harmonics instead of  $5^{th}$  and  $7^{th}$ .

#### **1.3.3 Space vector modulation**

Every switching state can be represented as a vector in the converters  $\alpha$ - $\beta$  space vector plane. The three phase currents can be transformed into two phase currents in  $\alpha$ - $\beta$  plane as represented below.

$$\begin{bmatrix} i_{\alpha}(t) \\ i_{\beta}(t) \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_{wA}(t) \\ i_{wB}(t) \\ i_{wC}(t) \end{bmatrix}$$

(1.2)

A resulted space vector can be expressed as equation (1.3).

$$\vec{I}(t) = i_{\alpha}(t) + ji_{\beta}(t) \tag{1.3}$$

The resulted vectors are shown in a diagram which is called space vector diagram. Since, the space vectors do not move, they are called stationary vectors. On the other hand, the desired

three-phase current on the AC side  $i_w$  can be expressed as a reference vector rotating counterclockwise in the vector plane. Each revolution of the reference vector corresponds to an entire fundamental cycle of the AC current. In other words, the reference current vector rotates at the desired AC frequency. The ratio between the magnitudes of the reference vector and the DC current determines the modulation index of the converter.

The reference vector can be synthesized by the adjacent space vectors based on the principle of ampere-second balance. Several switching sequences are available but they are associated with different device switching frequencies and harmonic profiles.

The harmonic profile of the conventional SVM is undesirable for AC filter design in the CSC. The AC capacitor together with the power supply side inductance or machine side inductance will cause LC resonances. The resonance frequency is normally between 3.5pu to 4.5 pu of the fundamental frequency to ensure not only desired current quality but also acceptable cost. The low order harmonic currents, 5<sup>th</sup> and 7<sup>th</sup> orders in specific, will cause harmonic voltages as well as resonance problems.

#### **1.3.4 Comparison of modulation schemes**

SHE provides the best harmonic performance. It is widely used due to its capability of eliminating unwanted low order harmonics with limited switching frequency. However, smooth and flexible modulation index control in real-time is difficult since one set of firing angles is only optimized for a certain modulation index [18-20].

Both TPWM and SVM provide the flexibility of modulation index control. With gating signals generated in real time, both methods have excellent dynamic performances. The practical applications of TPWM and SVM in CSC have been limited to the low fundamental frequency range. This is because of the fact that their currents contain low order harmonics, lying very close to the resonance frequencies of the AC filters and will be amplified if the system damping

is insufficient. However, the TPWM has limited line-side power factor control as well as weak dynamic performance during startup [19-21].

In this thesis, SVM is chosen and will be designed and modified for 5-level parallel CSC. The modulation provides full range modulation index control. In addition, the harmonic profile of the AC currents and voltages will be improved to a great significant by generating multi-level waveforms.

#### **1.4 Objectives**

The main objective of this thesis is to research and develop a novel switching modulation for a 5-level parallel CSC to fulfill industry demands and constraints for high power drive applications. To aim proper objectives to the thesis, first, technical challenges and difficulties must be determined and studied. The industry demand brings distinctive technical challenges. However, some of them are common in most applications.

For instance, the proper operation of multi-level parallel CSC requires the operation of parallel converters with balanced DC link currents. The reasons behind unbalanced DC link currents are discussed later in detail in Chapter 3. However, it can be summarized that the operation of parallel current source converters in practice involves unbalanced DC currents. Operation under unbalanced DC currents is undesirable. Therefore, the need for a practical, effective and fast controller to balance the DC link currents is evident.

Every drive application requires specific harmonic performance. It is thus necessary to develop switching schemes and design controllers to satisfy such harmonic performance. As mentioned in section 1.3.4, the SVM generates AC waveforms with an amount of distortion that is not negligible. In specific, low order harmonics generated by SVM considerably limit the

application of SVM based switching schemes. Hence, the designed switching scheme must be modified and developed to improve the harmonic performance of the converter.

Another technical challenge is the limitation of the switching frequency. Higher switching frequency brings higher total loss and severe thermal stress to the converter system. It is more critical in high power applications, when the converter operates at higher currents and voltages, to limit the switching frequency. It is a great achievement to reach the same performance with lower switching frequency. In this thesis, the switching frequency is minimized without limiting the converter general performance.

Based on technical challenges and difficulties discussed above, several objectives are taken into account, summarized as follows.

#### 1) Balanced DC currents

When connecting two converters in parallel, (either rectifiers or inverters), there will be two positive DC link buses and two negative DC link buses. Different circuit parameters, especially manufacturing tolerance in DC chokes and un-equal ON-state voltages of the switching devices may cause unbalanced DC link currents. Generally speaking, unbalanced DC currents generate current harmonics and higher current distortion. In addition, the imbalance increases total loss of the system and leads to uneven division of power between parallel converters. Therefore, the designed switching modulation must generate balanced DC link currents. An additional controller is necessary to secure balanced DC current (the "DC current balance control").

#### 2) Low harmonic distortion

Multi-level CSC can improve the harmonic distortion content of AC currents and voltages if the switching scheme is designed properly. In this thesis, the switching scheme is designed to decrease the distortion of AC waveforms and improve the harmonic profile of the AC line and AC load currents and voltages. The improved converter does not need a large filter capacitor to satisfy stringent AC side harmonic demands. Therefore, the size of the filter capacitor can be reduced. In addition, decreasing the low order harmonics will eliminate the need for costly and bulky phase-shifting transformers.

#### 3) Minimized switching frequency

Switching the device less frequently reduces the switching loss and places less thermal stress on each device. It is more critical in high power drive application in specific to limit the switching frequency. Usually, the switching frequency is limited to a few hundred Hertz in high power drive applications. In this thesis, the switching sequence is designed to minimize the switching frequency as much as possible.

#### 4) Dynamic performance

As mentioned, the main drawback of a CSC is its limited dynamic performance. Providing active full range modulation index control improves the dynamic performance of converter. SHE switching modulation as dominant switching modulation for CSCs employs off-line tables for different modulation indices and thus cannot provide continuous  $m_a$  control. On the other hand, SVM is capable of providing full range active control. Consequently, the active  $m_a$  control on the CSR maintains the DC current at the desired value while the active  $m_a$  control on the CSI adjusts the AC load voltage at the desired value. In this way, the conducted power is adjusted through the value of the DC link current and adjustable load voltage is achievable.

#### **1.5 Thesis outline**

In this thesis, a novel SVM switching scheme is introduced and elaborated for a 5-level parallel CSC which is applicable on both 5-level parallel CSRs and CSIs. The modulation is augmented

with DC current balance control. The modulation is designed to bring superior harmonic and dynamic performance to the converter system. This thesis consists of six chapters.

Chapter 1 presents the background and introduction of the thesis.

Chapter 2 elaborates the proposed SVM method. Several aspects such as switching states, switching vectors, space vector diagram, reference vector and dwell times are reviewed.

Chapter 3 develops the DC current balance control. Effects of redundant switching states on DC currents are investigated. Small and Medium vectors are employed to balance the DC link currents.

Chapter 4 investigates the steady state and dynamic performance of the proposed modulation. Several aspects such as harmonic profile, DC current control and AC load voltage control.

Chapter 5 summarizes the main contributions and conclusions of the thesis.

## Chapter 2 Space Vector Modulation for 5-Level Current Source Converter

#### **2.1 Introduction**

Several switching modulations are available for multi-level current source converters (CSC). In this thesis, space vector modulation (SVM) is chosen to satisfy the objectives of the design. The basic idea of SVM was presented in the previous chapter. In this chapter, SVM method is specifically modified and developed for 5-level parallel current source converter in specific. The available switching states are introduced. Every switching state can be represented by a vector in the space vector plane. The resulted space vectors constitute the space vector diagram. The switching method of SVM is elaborated thereafter. Three adjacent space vectors are chosen for each area of space vector diagram to synthesize the reference current vector. The order of vectors is designed to minimize the switching frequency. Dwell time calculations are presented at the end of this chapter.

#### 2.2 Switching states

Several switching modulations are available for multi-level CSCs. Generally, whichever one is used as a switching modulation, it should satisfy two requirements: the DC current  $i_d$  should be continuous and the switching chopped current  $i_w$  should be defined [3]. Disregarding to the first

requirement causes very high voltage induced by the DC choke and damages the switches. The second requirement is the main objective of the switching scheme.

Obviously, with no or only one switch ON, the requirement of continuous DC current cannot be satisfied. With more than two switches ON simultaneously, the output current will not follow the switching pattern. In this case, the output current is AC side- line in rectifiers and load in inverters- dependent. So, each switching state should have only two switches ON, one in the top half of the bridge and the other in the bottom half. This rule excludes commutation intervals. Consequently, any designed switching scheme, whether for current source rectifier (CSR) or current source inverter (CSI), must satisfy a constraint that only two switches can be at ON state, one connected to the positive DC bus while the other is connected to the negative DC bus.

Three switches are available at each half of the CSC. One of them must be selected to be at ON state. The others will be remained OFF. Consequently, there are 9 switching states available at each converter. Two converters are connected in parallel to constitute the multi-level converter. Under the mentioned constraint, 81 switching states are feasible in total. Table 2-1 provides the available switching states. Every switching state is represented by 4 digits. The first 2 digits express two switches ON in the first converter and the second 2 digits state two switches ON in the second converter. For example, the expression [16 56] represents the switching state in which switches number 1 and 6 in the first converter and switches number 5 and 6 in the second converter are at ON state. Fig. 2-1 illustrates the current paths when the mentioned switching state is applied in the multi-level parallel CSI.

Fig. 2-1 Current paths in parallel inverters with switching state [16 56].

| [12 12] | [12 32] | [12 52] | [12 16] | [12 36] | [12 56] | [12 14] | [12 34] | [12 54] |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| [32 12] | [32 32] | [32 52] | [32 16] | [32 36] | [32 56] | [32 14] | [32 34] | [32 54] |

| [52 12] | [52 32] | [52 52] | [52 16] | [52 36] | [52 56] | [52 14] | [52 34] | [52 54] |

| [16 12] | [16 32] | [16 52] | [16 16] | [16 36] | [16 56] | [16 14] | [16 34] | [16 54] |

| [36 12] | [36 32] | [36 52] | [36 16] | [36 36] | [36 56] | [36 14] | [36 34] | [36 54] |

| [56 12] | [56 32] | [56 52] | [56 16] | [56 36] | [56 56] | [56 14] | [56 34] | [56 54] |

| [14 12] | [14 32] | [14 52] | [14 16] | [14 36] | [14 56] | [14 14] | [14 34] | [14 54] |

| [34 12] | [34 32] | [34 52] | [34 16] | [34 36] | [34 56] | [34 14] | [34 34] | [34 54] |

| [54 12] | [54 32] | [54 52] | [54 16] | [54 36] | [54 56] | [54 14] | [54 34] | [54 54] |

Table 2-1 Switching states.

### 2.3 Space vectors

Each switching state can be represented by a vector in the converter's space vector plane. To derive the relationship between the switching states and space vectors assume that the converter whether rectifier or inverter is at balanced three phase operation. Therefore,

$$i_{wA}(t) + i_{wB}(t) + i_{wC}(t) = 0$$

(2.1)

where  $i_{wA}$ ,  $i_{wB}$  and  $i_{wC}$  are the instantaneous AC side currents, before the filter capacitor, corresponding to phases A, B and C respectively. The three phase currents can be transformed into two phase currents in  $\alpha$ - $\beta$  plane as represented below.

$$\begin{bmatrix} i_{\alpha}(t) \\ i_{\beta}(t) \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_{wA}(t) \\ i_{wB}(t) \\ i_{wC}(t) \end{bmatrix}$$

(2.2)

A resulted space vector can be expressed as equation (2.3).

$$\vec{I}(t) = i_{\alpha}(t) + ji_{\beta}(t) \tag{2.3}$$

which can be rewritten as equation (2.4).

$$\vec{I}(t) = \frac{2}{3} \left[ i_{wA}(t) e^{j0} + i_{wB}(t) e^{j\frac{2\pi}{3}} + i_{wC}(t) e^{j\frac{4\pi}{3}} \right]$$

(2.4)

in which  $i_{wA}$ ,  $i_{wB}$  and  $i_{wC}$  are determined according to the switching state. For example, for the switching state [16 56] mentioned before, switching currents are presented at (2.5).

$$i_{wA} = \frac{I_d}{2}, \ i_{wB} = -I_d, \ i_{wC} = \frac{I_d}{2}$$

(2.5)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [16 56] can be driven as equation (2.6).

$$\vec{I}_{[16\ 56]} = I_d \ e^{j-60} \tag{2.6}$$

The same calculations can be derived and the corresponding space vector is found for the other switching states. Some of the switching states result in a same vector. Considering that, there are 19 space vectors in total. These vectors are divided to 4 different kinds based on their length; Large, Medium, Small and Zero.

#### 2.3.1 Large vectors

Assume that the converter is operating at the switching state [16 16]. Under the mentioned condition,

$$i_{wA} = I_d, \ i_{wB} = -I_d, \ i_{wC} = 0$$

(2.7)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [16 16] can be driven as equation (2.8).

$$\vec{I}_{[16\ 16]} = \frac{2\sqrt{3}}{3} I_d \ e^{j-30} \tag{2.8}$$

This vector and 5 other vectors have the largest length among space vectors. Table 2-2 presents the switching states result in Large vectors and the corresponding space vectors. Large vectors are labeled  $\vec{I}_1$  to  $\vec{I}_6$ .

| Switching State | Vector                              | Space Vector |

|-----------------|-------------------------------------|--------------|

| [16 16]         | $\frac{2\sqrt{3}}{3}I_d \ e^{j-30}$ | $\vec{I}_1$  |

| [12 12]         | $\frac{2\sqrt{3}}{3}I_d e^{j30}$    | $\vec{I}_2$  |

| [32 32]         | $\frac{2\sqrt{3}}{3}I_d e^{j90}$    | $\vec{I}_3$  |

| [34 34]         | $\frac{2\sqrt{3}}{3}I_d \ e^{j150}$ | $\vec{I}_4$  |

| [54 54]         | $\frac{2\sqrt{3}}{3}I_d e^{j-150}$  | $\vec{I}_5$  |

| [56 56]         | $\frac{2\sqrt{3}}{3}I_d \ e^{j-90}$ | $\vec{I}_6$  |

Table 2-2 Large switching states.

Large vectors employ same switches at both converters. In other words, current paths are symmetrical in both converters. Since, the same AC phases are connected to converters, equal voltages are applied to DC link chokes. Identical changes to DC link currents are expected.

#### 2.3.2 Medium vectors

Assume that the converter is operating at the switching state [12 16]. Under the mentioned condition,

$$i_{wA} = I_d, \ i_{wB} = \frac{-I_d}{2}, \ i_{wC} = \frac{-I_d}{2}$$

(2.9)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [12 16] can be driven as equation (2.10).

$$\vec{I}_{[12\,16]} = I_d \ e^{j0} \tag{2.10}$$

Now, assume that the converter is operating at the switching state [16 12]. Under the mentioned condition,

$$i_{wA} = I_d, \ i_{wB} = \frac{-I_d}{2}, \ i_{wC} = \frac{-I_d}{2}$$

(2.11)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [16 56] can be driven as equation (2.12).

$$\vec{I}_{[16\ 12]} = I_d \ e^{j0} \tag{2.12}$$

In conclusion, switching states [12 16] and [16 12] result in an identical space vector. This vector and 5 other vectors resulted from 12 switching states, have same length among space

vectors. Table 2-3 presents the switching states result in Medium vectors and the corresponding space vectors. Medium vectors are labeled  $\vec{I}_7$  to  $\vec{I}_{12}$ .

| Switchi | Switching State |                 | Space Vector   |

|---------|-----------------|-----------------|----------------|

| [12 16] | [16 12]         | $I_d e^{j0}$    | $\vec{I}_7$    |

| [32 12] | [12 32]         | $I_d e^{j60}$   | $\vec{I}_8$    |

| [32 34] | [34 32]         | $I_d e^{j120}$  | $ec{I}_9$      |

| [34 54] | [54 34]         | $I_d e^{j180}$  | $ec{I}_{10}$   |

| [54 56] | [56 54]         | $I_d e^{j-120}$ | $ec{I}_{11}$   |

| [16 56] | [56 16]         | $I_d e^{j-60}$  | $\vec{I}_{12}$ |

Table 2-3 Medium switching states.

There are two redundant switching states for every Medium vector. In fact, two redundant switching states employ same switches on either top half or bottom half. Different switches are at ON state for the other half. Since, different phases are connected to DC links in converters, asymmetrical changes on DC links are expected.

#### 2.3.3 Small vectors

Assume that the converter is operating at the switching state [14 16]. Under the mentioned condition,

$$i_{wA} = \frac{I_d}{2}, \ i_{wB} = \frac{-I_d}{2}, \ i_{wC} = 0$$

(2.13)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [14 16] can be driven as equation (2.14).

$$\vec{I}_{[14\ 16]} = \frac{\sqrt{3}}{3} I_d \ e^{j-30} \tag{2.14}$$

The switching state [16 14] results in the same vector. Operating at these two switching states, one of the converters bypasses the DC current to the AC side through switches 1 and 4, while DC current is conducted to the AC side through switches 1 and 6. In addition to mentioned switching states, switching states [16 36], [36 16], [16 52] and [52 16] bring the same manner to the converter. The only difference is that the bypass process is conducted through other phases. As expected, calculations show the same space vector resulted from the mentioned switching states.

Now, assume that the converter is operating at the switching states [56 12] or [12 56]. Under the mentioned condition,

$$i_{wA} = \frac{I_d}{2}, \ i_{wB} = \frac{-I_d}{2}, \ i_{wC} = 0$$

(2.15)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [12 56] can be driven as equation (2.16).

$$\vec{I}_{[56\ 12]} = \frac{\sqrt{3}}{3} I_d \ e^{j-30} \tag{2.16}$$

The resulted vector is same as the last mentioned vector. Although none of the converters bypasses the DC current, the bypass process is conducted with cooperation of two converters on phase C. Phase C is not involved in conduction process which is still carried out with switches 1 and 6.

In summary, 8 redundant switching states result in an identical Small medium vector. This vector and 5 other vectors resulted from 48 switching states, have same length among space vectors. Table 2-4 presents the switching states result in Small vectors and the corresponding space vectors. Small vectors are labeled  $\vec{i}_{13}$  to  $\vec{i}_{18}$ . Since, different phases are connected to DC links in two converters, asymmetrical changes are expected.

|         | Switchi | ng State |         | Vector                            | Space Vector   |

|---------|---------|----------|---------|-----------------------------------|----------------|

| [16 14] | [16 36] | [16 52]  | [12 56] | $\frac{\sqrt{3}}{3}I_d e^{j-30}$  | $\vec{I}_{13}$ |

| [14 16] | [36 16] | [52 16]  | [56 12] | $3^{I_d e}$                       | 13             |

| [12 14] | [12 36] | [12 52]  | [16 32] | $\frac{\sqrt{3}}{3}I_d e^{j90}$   | $\vec{I}_{14}$ |

| [14 12] | [36 12] | [52 12]  | [32 16] | $3^{I_d}$                         | * 14           |

| [32 14] | [32 36] | [32 52]  | [34 12] | $\frac{\sqrt{3}}{3}I_d e^{j-150}$ | $\vec{I}_{15}$ |

| [14 32] | [36 32] | [52 32]  | [12 34] | $3^{1_d}$                         | 15             |

| [34 14] | [34 36] | [34 52]  | [32 54] | $\frac{\sqrt{3}}{3}I_d e^{j-30}$  | $\vec{I}_{16}$ |

| [14 34] | [36 34] | [52 34]  | [54 32] | $3^{n_d}$                         | - 16           |

| [54 14] | [54 36] | [54 52]  | [56 14] | $\frac{\sqrt{3}}{3}I_d e^{j90}$   | $\vec{I}_{17}$ |

| [14 54] | [36 54] | [52 54]  | [14 56] | 3                                 | - 17           |

| [56 14] | [56 36] | [56 52]  | [54 16] | $\frac{\sqrt{3}}{3}I_d e^{j-150}$ | $\vec{I}_{18}$ |

| [14 56] | [36 56] | [52 56]  | [16 54] | 3                                 | -18            |

Table 2-4 Small switching states.

#### 2.3.4 Zero vector

Assume that the converter is operating at the switching state [14 14] where both converters bypass the DC link current. Under the mentioned condition,

$$i_{wA} = 0, \ i_{wB} = 0, \ i_{wC} = 0$$

(2.17)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [14 14] can be driven as equation (2.18).

$$\vec{I}_{[14\,14]} = 0 \tag{2.18}$$

The same vector is expected when bypass process is conducted through two other phases. In other words, switching states [36 36] and [52 52] result in Zero vector too. In addition, the

switching states [14 36], [14 52], [36 14], [36 52], [52 14] and [52, 32] bypass the DC currents with cooperation of different phases. These switching states result in Zero vector as well.

Now, assume that the converter is operating at the switching state [12 54] or [54 12] where DC current is bypassed with cooperation of two converters. Under the mentioned condition,

$$i_{wA} = 0, \ i_{wB} = 0, \ i_{wC} = 0$$

(2.19)

Substituting the switching currents into equation (2.4), the resulted vector of switching state [12 54] can be driven as equation (2.20).

$$\vec{I}_{\lceil 12\ 54 \rceil} = 0 \tag{2.20}$$

The same result is expected for operation under switching states [16 34], [34 16], [32 56] and [56 32].

In conclusion, 15 redundant switching states operate as Zero vector. Table 2-5 presents the switching states result in Zero vector and the corresponding space vectors. Zero vector is labeled  $\bar{t}_{19}$ . Some statistical points are summarized in Table 2-6.

Table 2-5 Zero switching states.

| Sw      | itching St | ate     | Vector | Space Vector |

|---------|------------|---------|--------|--------------|

| [14 14] | [36 36]    | [52 52] |        |              |

| [14 36] | [36 52]    | [52 14] |        |              |

| [36 14] | [52 36]    | [14 52] | 0      | $ec{I}_{19}$ |

| [12 54] | [34 16]    | [56 32] |        |              |

| [54 12] | [16 34]    | [32 56] |        |              |

| Space Vector Type          | Large                    | Medium | Small                   | Zero |

|----------------------------|--------------------------|--------|-------------------------|------|

| Length of Vectors          | $\frac{2\sqrt{3}}{3}I_d$ | $I_d$  | $\frac{\sqrt{3}}{3}I_d$ | 0    |

| Number of Vectors          | 6                        | 6      | 6                       | 1    |

| Number of Switching States | 6                        | 12     | 48                      | 15   |

| Number of Redundant States | 1                        | 2      | 8                       | 15   |

Table 2-6 Space vectors specifications.

# 2.4 Space vector diagram

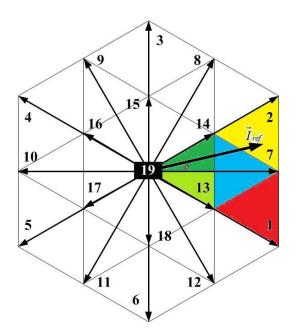

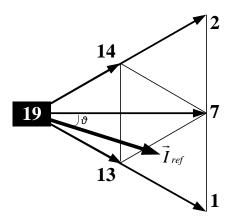

Eighty one switching states result in 19 space vectors. Space vectors form the space vector diagram. Fig. 2-2 illustrates the space vector diagram.

Fig. 2-2 Space vector diagram

In addition to 19 stationary space vectors, one rotating vector is presented on the space vector plane. This vector which is the reference current vector  $\vec{l}_{ref}$ , determines the AC current produced with space vector modulation. In other words, the three-phase AC current is expressed as  $\vec{l}_{ref}$  that rotates with the desired AC frequency (i.e. 60Hz). The length of  $\vec{l}_{ref}$  represents the magnitude of the AC current determined by the modulation index  $m_a$  as described in equation (2.21).

$$m_a = \frac{I_{ref}}{i_d} \tag{2.21}$$

The angle of the reference vector  $\theta$  determiners the phase of the produced AC current. The purpose of the space vector modulation is to estimate the reference vector with the space vectors. A better estimation of the reference vector brings a better performance to the converter system. To improve the estimation of the reference vector space vector plane is divided to smaller areas. Consequently, the reference current vector is synthesized with closest vectors at each smaller area.

As illustrated in Fig. 2-2, Large vectors divide the space vector plane into 6 sectors. For instance, sector 1 is an area between Large vector 1 and Large vector 2. To improve the estimation of the reference current vector, every sector is divided into 4 regions. Consequently, 24 triangular areas constitute the space vector diagram. The space vector modulation chooses three closest vectors at each area to synthesize the reference current vector.

# 2.5 Vector selection

According to the area that the reference current vector is located in, three vectors estimate the reference vector. As the first step in switching sequence design, three vectors should be selected for every area in the space vector plane.

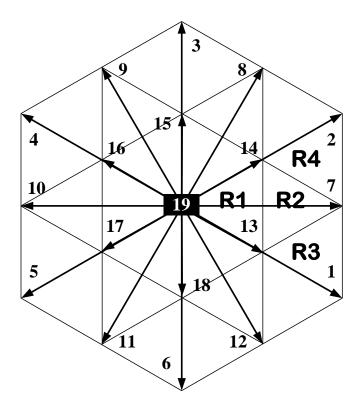

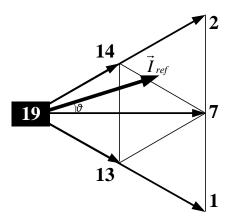

Sector number 1 is divided into four triangular areas and the assigned number is called region number. Fig. 2-3 illustrates the details of the region numbering. Three switching vectors should be selected for each region. The selected vectors must be able to synthesize every reference vector located in the assigned triangle. In addition, being closer to the triangle, brings a better estimation of the reference current. Vector selection process is presented for outer triangles and inner triangles of sector 1 separately. When the modulation index  $m_a$  has lower values, the reference current vector is located in inner triangle R1 (region 1). When the modulation index  $m_a$  has higher values, the reference current vector is located in outer triangles labeled with R2 for region 2, R3 for region 3 or R4 for region 4.

Fig. 2-3 Space vector diagram- region numbering

#### a) Region 1

In design of switching sequence it is necessary to satisfy the constraint that the transient from one vector to another involves at most one device switch-ON and one device switch-OFF at each inverter to produce a lower switching frequency and minimize the switching loss.

The first guess of switching vectors is  $(\vec{l}_{13}, \vec{l}_{19}, \vec{l}_{14})$ . Since, the negative DC bus currents are controlled in sector 1, two switching states [14 16] and [16 14] are available for Small vector  $\vec{l}_{13}$ . Since, the positive DC bus currents are controlled in sector 6, two switching states [36 16] and [16 36] are available for Small vector  $\vec{l}_{13}$ . If Small vector  $\vec{l}_{13}$  is chosen for transient vector between sectors 1 and 6, there might be a transient from switching states [14 16] to [36 16] or [16 14] to [16 36] which include two switches turn-OFF and turn-ON in one of converters. The same analysis can be done for Small vector  $\vec{l}_{14}$  in sectors 1 and 2. Consequently, two Small vectors  $\vec{l}_{13}$  and  $\vec{l}_{14}$  are not proper choices to role as transient vectors.

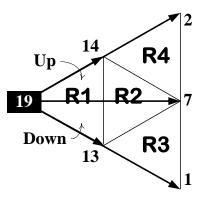

The other guess of switching vectors is  $(\vec{l}_1, \vec{l}_{19}, \vec{l}_2)$ . Employing Large vectors  $\vec{l}_1$  and  $\vec{l}_2$  as transient vectors solves the issue mentioned before. Unfortunately, there is no Medium or Small vector among the vector set which is necessary for the DC current balance control. In addition, employing two Large vectors in region 1 causes a very high dwell time for Zero vector. Subsequently, degrade in harmonic performance is inevitable. To solve the problem, region 1 is divided to two smaller areas which are called Down and Up. Medium vector  $\vec{l}_7$  divides triangle 1 to two smaller right triangles which are called Down and Up.

Fig. 2-4 Space vector plane (sector one)

Fig. 2-4 depicts sector 1 and sub-triangles of the sector. The vector sets of  $(\vec{I}_{19}, \vec{I}_{13}, \vec{I}_7)$  and  $(\vec{I}_7, \vec{I}_{14}, \vec{I}_{19})$  are selected corresponding to Down and Up triangles respectively. Each set includes one Medium, one Small and Zero vector.

### b) Region 2

Two sets of options are available for triangle 2 which are  $(\vec{l}_1, \vec{l}_{19}, \vec{l}_2)$  and  $(\vec{l}_{13}, \vec{l}_7, \vec{l}_{14})$ . The first set employs Zero vector  $\vec{l}_{19}$ . Employing Zero vector increases the distortion content of the AC currents and voltages. Besides, Medium and Small vectors are essential in DC current balance control. There is not any Medium or Small vector among first set of vectors which is necessary for DC current balance control. The second set of vectors includes two Small vectors and one Medium vector. These three vectors are employed to synthesize the reference current vector when located in triangle 2.

#### c) Region 3

The vector set of  $(\vec{I}_1, \vec{I}_7, \vec{I}_{13})$  is selected for triangle 3. The set includes one Large, one Medium and one Small vector.

#### d) Region 4

The vector set of  $(\vec{I}_{14}, \vec{I}_7, \vec{I}_2)$  is selected for triangle 4. The set includes one Large, one Medium and one Small vector.

The same study can be done for the rest of the space vector plane. Each sector can be mirrored on sector 1 and the current vectors are selected same as sector 1. Table 2-7 presents the selected three vectors corresponding to each triangle of the space vector plane.

|          | R  | egion | 1              | Vector         | S              |          | R        | egion | Ţ              | Vector         | S              |                |                |                |

|----------|----|-------|----------------|----------------|----------------|----------|----------|-------|----------------|----------------|----------------|----------------|----------------|----------------|

|          | N  | egion | a              | b              | с              |          | Region   |       | a              | b              | c              |                |                |                |

|          | R1 | Down  | $ec{I}_{19}$   | $\vec{I}_{13}$ | $\vec{I}_7$    |          | R1       | Down  | $ec{I}_{19}$   | $\vec{I}_{16}$ | $\vec{I}_{10}$ |                |                |                |

| S        |    | Up    | $\vec{I}_7$    | $\vec{I}_{14}$ | $\vec{I}_{19}$ | Š        |          | Up    | $\vec{I}_{10}$ | $\vec{I}_{17}$ | $\vec{I}_{19}$ |                |                |                |

| Sector 1 |    | R2    | $\vec{I}_{13}$ | $\vec{I}_7$    | $\vec{I}_{14}$ | Sector 4 |          | R2    | $\vec{I}_{16}$ | $\vec{I}_{10}$ | $\vec{I}_{17}$ |                |                |                |

| H        |    | R3    | $ec{I}_1$      | $\vec{I}_7$    | $\vec{I}_{13}$ | 4        |          | R3    | $\vec{I}_4$    | $\vec{I}_{10}$ | $ec{I}_{16}$   |                |                |                |

|          |    | R4    | $\vec{I}_{14}$ | $\vec{I}_7$    | $\vec{I}_2$    |          |          | R4    | $ec{I}_{17}$   | $\vec{I}_{10}$ | $\vec{I}_5$    |                |                |                |

|          | R1 | Down  | $\vec{I}_{19}$ | $\vec{I}_{14}$ | $\vec{I}_8$    |          | R1       | R1    |                | R1             | Down           | $\vec{I}_{19}$ | $\vec{I}_{17}$ | $\vec{I}_{11}$ |

| S        | M  | Up    | $\vec{I}_8$    | $\vec{I}_{15}$ | $\vec{I}_{19}$ | S        |          |       |                |                | Up             | $ec{I}_{11}$   | $\vec{I}_{18}$ | $\vec{I}_{19}$ |

| Sector 2 |    | R2    | $\vec{I}_{14}$ | $\vec{I}_8$    | $\vec{I}_{15}$ | Sector 5 |          | R2    | $ec{I}_{17}$   | $\vec{I}_{11}$ | $\vec{I}_{18}$ |                |                |                |

| 2        |    | R3    | $\vec{I}_2$    | $\vec{I}_8$    | $\vec{I}_{14}$ | Ű        | R3<br>R4 |       | $\vec{I}_5$    | $\vec{I}_{11}$ | $ec{I}_{17}$   |                |                |                |

|          |    | R4    | $\vec{I}_{15}$ | $\vec{I}_8$    | $\vec{I}_3$    |          |          |       | $\vec{I}_{18}$ | $\vec{I}_{11}$ | $\vec{I}_6$    |                |                |                |

|          | R1 | Down  | $\vec{I}_{19}$ | $\vec{I}_{15}$ | $\vec{I}_9$    |          | R1       | Down  | $ec{I}_{19}$   | $\vec{I}_{18}$ | $\vec{I}_{12}$ |                |                |                |

| S        | M  | Up    | $\vec{I}$ 9    | $ec{I}_{16}$   | $\vec{I}_{19}$ | S        |          | Up    | $\vec{I}_{12}$ | $\vec{I}_{13}$ | $\vec{I}_{19}$ |                |                |                |

| Sector 3 |    | R2    | $\vec{I}_{15}$ | $\vec{I}_9$    | $\vec{I}_{16}$ | Sector 6 |          | R2    | $\vec{I}_{18}$ | $\vec{I}_{12}$ | $\vec{I}_{13}$ |                |                |                |

| <u>ت</u> |    | R3    | $\vec{I}_3$    | $\vec{I}_9$    | $\vec{I}_{15}$ | 6        | R3       |       | $\vec{I}_{6}$  | $\vec{I}_{12}$ | $\vec{I}_{18}$ |                |                |                |

|          |    | R4    | $ec{I}_{16}$   | $\vec{I}_9$    | $\vec{I}_4$    |          |          | R4    | $\vec{I}_{13}$ | $\vec{I}_{12}$ | $ec{I}_1$      |                |                |                |

Table 2-7 Selected vectors for each triangular area of space vector plane.

# 2.6 Space vector order design to achieve the minimized switching frequency

The proper switching sequence should accomplish the following:

a) Produce AC currents and voltages with acceptable harmonic distortion on the AC side. Dividing the space vector diagram into smaller areas and selecting proper switching vectors to estimate the reference current vector provide AC currents and voltages with low distortion content.

b) Bring the identical switching frequency and switching sequence in both inverters. Satisfying this constraint secures an equal fatigue and heat design to parallel converters.

c) Satisfy the constraint that the transient from one vector to another involves at most one device switch-ON and one device switch-OFF at each converter to produce a lower switching frequency and minimize the switching loss. However, to produce a lower device switching frequency the switching sequence is designed to minimize the device switching frequency. In this chapter, the switching vector order is designed to minimize the switching frequency.

The space vector order is analyzed in detail for sector 1. The order of vectors at each region is designed in such a way to transient from one switching state to another involves minimum number of devices. Assume that the modulation index has a high value and the reference current is located in region 3 of sector 1. Fig. 2-5 illustrates the location of the reference current vector.

Fig. 2-5 Space vector plane- sector 1, region 3

As discussed heretofore, the vector set of  $(\vec{l}_1, \vec{l}_7, \vec{l}_{13})$  is chosen to estimate the reference current vector. For Large vector  $\vec{l}_1$  only switching state [16 16] is available. For Medium vector  $\vec{l}_7$  two switching states which are [12 16] and [16 12] are available. DC current balance control chooses the proper switching state based on the circuit circumstances. For Small vector  $\vec{l}_{13}$  eight switching states are available. However, only two of them which are [16 14] and [14 16] are taken into consideration according to the discussions on the DC current balance control.

Large vector  $\vec{l}_1$  is common in region 3 of sector 1 and region 4 of sector 6. By ending the sector 6 switching and starting the switching of sector 1 with vector  $\vec{l}_1$  there will be no device switching in transient from sector 6 to sector 1. Both vectors  $\vec{l}_7$  and  $\vec{l}_{13}$  are common in region 3 and region 2 and all regions 3, 2 and 4 contain Medium vector  $\vec{l}_7$ . Assigning Medium vector  $\vec{l}_7$  as the middle switching vector in regions 3, 2 and 4 of sector 1, symmetry is brought to the switching vectors. Subsequently, Small vector  $\vec{l}_{13}$  is considered as the third vector in region 3. Selecting the same vector as the first vector of region 2, transient from region 3 to region 2 involves an identical vector. Consequently, no or one device switching appears at each parallel

converter. Table 2-9 provides the switching sequence of region 3 of sector 1. It is obvious that transient from one vector to next vector involves at most one switching at each converter.

| Sector 1         | Region 3    |             |                |

|------------------|-------------|-------------|----------------|

| Switching Vector | $\vec{I}_1$ | $\vec{I}_7$ | $\vec{I}_{13}$ |

| Switching State  | [16 16]     | [16 12]     | [14 16]        |

| Surveying State  | [ 10]       | [12 16]     | [16 14]        |

Table 2-8 Vector order- sector 1, region 3.

As time runs, the reference current vector rotates and moves to region 2 of sector 1. Fig. 2-6 illustrates the location of the reference current vector.

Fig. 2-6 Space vector plane- sector 1, region 2

As discussed heretofore, the vector set of  $(\vec{I}_{13}, \vec{I}_7, \vec{I}_{14})$  is chosen to estimate the reference current vector. For Medium vector  $\vec{I}_7$  two switching states which are [12 16] and [16 12] are available. The DC current balance control chooses the proper switching state based on the circuit variables. For each Small vectors  $\vec{I}_{13}$  and  $\vec{I}_{14}$  eight switching states are available. However, only two of them which are [16 14] and [14 16] for  $\vec{I}_{13}$  and [14 12] and [12 14] for  $\vec{I}_{14}$  are taken into consideration according to the discussions on the DC current balance control.

Small vector  $\vec{l}_{13}$  is common in region 3 and region 2 of sector 1. By ending the region 3 switching and starting the switching of region 2 with vector  $\vec{l}_{13}$  there will be no vector change in transient. However, there might be at most one device switching at each parallel converter. As mentioned before, Locating Medium vector  $\vec{l}_7$  as the middle switching vector in regions 3, 2 and 4 of sector 1 symmetry is brought to the switching vectors. Subsequently, Small vector  $\vec{l}_{14}$  is considered as the third vector in region 2. Selecting the same vector as the first vector of region 4, transient from region 2 to region 4 involves an identical vector. Table 2-10 provides the switching sequence of region 2 of sector 1. It is obvious that transient from one vector to next vector involves at most one switching at each converter.

Table 2-9 Vector order- sector 1, region 2.

| Sector 1             | Region 2       |             |                |

|----------------------|----------------|-------------|----------------|

| Switching Vector     | $\vec{I}_{13}$ | $\vec{I}_7$ | $\vec{I}_{14}$ |

| Switching State      | [14 16]        | [16 12]     | [14 12]        |

| S where and a second | [16 14]        | [12 16]     | [12 14]        |

As time runs, the reference current vector rotates and moves to region 4 of sector 1. Fig. 2-7 illustrates the location of the reference current vector.

Fig. 2-7 Space vector plane- sector 1, region 4

As discussed heretofore, the vector set of  $(\vec{I}_{14}, \vec{I}_7, \vec{I}_2)$  is chosen to estimate the reference current vector. For Medium vector  $\vec{I}_7$  two switching states which are [12 16] and [16 12] are available. For Small vector  $\vec{I}_{14}$  eight switching states are available. However, only two of them which are [16 14] and [14 16] are taken into consideration according to the discussions on Chapter 3. For Large vector  $\vec{I}_2$  only the switching state [12 12] is available.

Small vector  $\overline{I}_{14}$  is common in region 2 and region 4 of sector 1. By ending the region 2 switching and starting the switching of region 4 with vector  $\overline{I}_{14}$  there will be no vector change in transient period. However, there might be a change in switches. As mentioned before, assigning Medium vector  $\overline{I}_7$  as the middle switching vector in regions 3, 2 and 4 of sector 1, symmetry is brought to the switching vectors. Subsequently, Large vector  $\overline{I}_2$  is considered as the third vector in region 4. Selecting the same vector as the first vector of region 3 of sector 2, transient from sector 1 to sector 2 involves an identical vector and switching. Table 2-11 provides the switching sequence of region 4 of sector 1. It is obvious that transient from one vector to next vector involves at most one switching at each converter.

| Sector 1         |                | Region 2    |              |

|------------------|----------------|-------------|--------------|

| Switching Vector | $\vec{I}_{14}$ | $\vec{I}_7$ | $\vec{I}_2$  |

| Switching State  | [14 12]        | [16 12]     | [12 12]      |

| Survey State     | [12 14]        | [12 16]     | [ <b>-</b> ] |

Table 2-10 Vector order- sector 1, region 4.

Now, assume that the modulation index  $m_a$  has lower values such that the reference current vector is located in region 1 of sector 1. The vector sets of  $(\vec{l}_{19}, \vec{l}_{13}, \vec{l}_7)$  and  $(\vec{l}_7, \vec{l}_{14}, \vec{l}_{19})$  are selected corresponding to Down and Up triangles respectively. Each set includes one Medium, one Small and Zero vector. The switching states corresponding to Medium and Small vectors are discussed before. Zero vector is employed as the transient vector between different sectors. The proper switching state for Zero vector is the one which minimizes the switching frequency. Medium vector is employed as the transient vector between Down and Up areas. Table 2-12 and Table 2-13 provide the space vector order for Down and Up triangles respectively. The same analysis is done for other five Sectors by mirroring them on Sector 1.

| Sector 1         |                | Region 2       |             |

|------------------|----------------|----------------|-------------|

| Switching Vector | $\vec{I}_{19}$ | $\vec{I}_{13}$ | $\vec{I}_7$ |

| Switching State  | [14 14]        | [16 14]        | [16 12]     |

| Stritening State | [1.1.]         | [14 16]        | [12 16]     |

Table 2-11 Vector order- sector 1, region 1, Down triangle.

Table 2-12 Vector order- sector 1, region 1, Up triangle.

| Sector 1          | Region 2    |                |                |

|-------------------|-------------|----------------|----------------|

| Switching Vector  | $\vec{I}_7$ | $\vec{I}_{14}$ | $\vec{I}_{19}$ |

| Switching State   | [16 12]     | [14 12]        | [54 12]        |

| S writening State | [12 16]     | [12 14]        | [12 54]        |

# **2.7 Dwell times**

Considering the triangle which the reference vector is located in, three nearest vectors are chosen to form the reference current vector. The sampling period  $T_s$  is divided to three parts which are called dwell times, each part for one of the space vectors. In other words, the multi-level converter operates at a switching state corresponding to the selected space vector for the period of dwell time of that vector.

The dwell time of each vector is calculated to satisfy two constraints:

1)

$$\vec{I}_{a}T_{a} + \vec{I}_{b}T_{b} + \vec{I}_{c}T_{c} = \vec{I}_{ref}$$

(2.22)