# VIRTUAL CHANNEL ORGANIZATION AND ARBITRATION FOR NETWORK ON CHIP ROUTER ARCHITECTURE

by

Masoud Oveis Gharan

B.S., Isfahan University of Technology, Iran, 1991

M.A.Sc., Ryerson University, Canada, 2011

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2016

© Masoud Oveis Gharan 2016

# AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the pubic.

# Virtual Channel Organization and Arbitration For Network on Chip Router Architecture Doctor of Philosophy, 2016 Masoud Oveis Gharan Electrical and Computer Engineering Ryerson University

## Abstract

The advent of Multi-Processor Systems-on-Chip (MPSoC) has emphasized the importance of on-chip communication infrastructures. Network on Chip (NoC) has emerged as a state of the art paradigm for efficient on-chip communication. Among the various components employed in NoC routers, Virtual Channel (VC) plays an important role in the performance and hardware requirements of an NoC system. The VC mechanism enables the multiplexing and buffering of several packets to travel over a single physical channel concurrently. VC arbitration (or arbiter) is another critical organization component of a router that has significant impact on the efficiency of an NoC system. Arbiter performs arbitration among the group of VCs that are competing for a single resource (e.g. output-port).

In this dissertation, we propose novel approaches for dynamic VC flow control mechanism and VC arbitration. The first two approaches are based on the adaptivity of VCs in the router input-port that improves the efficiency of NoC system. In both of techniques, the input-port comprises of a centralized buffer whose slots are dynamically allocated to VCs according to a real-time traffic situation. The performance improvement is achieved by utilizing multiple virtual channels with minimal buffer resources. The VC arbitration approach is based on an efficient and fast arbiter that functions upon the index of its input-ports (or VC requests). The architecture of arbiter scales with the  $Log_2$  of the number of inputs where a conventional round robin arbiter scales with the number of inputs. The index based behavior and the architecture of our arbiter leads to lower power consumption and chip area.

This dissertation presents the organizations and micro-architectures of NoC routers. We have employed SystemVerilog at the micro-architectural level design and modeling of NoC components. We employ three CAD platforms namely ModelSim, Quartus (FPGA) and Synopsys (ASIC level) to design, simulate and implement our router based NoCs. The simulation results support the theoretical concepts of our proposed VC organization and arbitration approaches. We have also implemented and conducted simulation and modeling experiments for conventional VC organization and arbitration models. The experimental results verify the efficiency of our proposed models in terms of power, area and performance in different NoC configurations.

### Acknowledgment

Hereby I truly thank all Ryerson University administrators and staffs who helped and support me in financial and registration matters to do the best for my education. I really appreciate the teaching efforts of the professors who taught me during these five academic years. Here I would like to present my especial thanks to Prof. Gul N. Khan for being an exceptional advisor for my entire graduate career. As advisor and friend, he has managed to perfectly balance encouragement and criticism, and I am in his debt for providing me with the facilities to be a successful researcher in an exciting field. I am astounded by his great breadth of knowledge, and ability to focus on the details. His attention to details and network-on-chip opinion is an invaluable asset, and I am really thankful to be his PhD student.

Above all, I am thankful for the love and support of my family. I am positively blessed to have a wife Maryam, a daughter Ghazal, and a baby boy Erfan as wonderful as mine who have given me an amazing life. Their belief in me was a motivator in everything I did, and their advice and understanding could not be more appreciated.

I owe many thanks to all my friends especially those who are in Micro-system Research Laboratory for their unwavering support and friendship. I love spending time with you guys, some of my best memories have been made here.

# **Table of Contents**

| Author's Declaration | ii  |

|----------------------|-----|

| Abstract             | iii |

| Acknowledgment       | V   |

| List of Tables       | X   |

| List of Figures      | xi  |

# Chapter 1

| Introduction1                                                  |

|----------------------------------------------------------------|

| 1.1 Network on Chip a State of the Art Paradigm1               |

| 1.2 Wormhole Routing                                           |

| 1.3 NoC Router Architecture                                    |

| 1.4 VC organization                                            |

| 1.4.1 FIFO Architecture                                        |

| 1.4.2 Queue Buffers7                                           |

| 1.4.3 Traditional Wormhole Routing7                            |

| 1.5 Static and Dynamic VC Organizations                        |

| 1.5.1 Problems in Static VC Organization                       |

| 1.5.2 Head of Line Blocking                                    |

| 1.5.3 DAMQ: Dynamically Allocated Multi Queues11               |

| 1.5.4 Timing Problem of Adaptive Table-based VC Organization14 |

| 1.6 Data Flow Arbitration                                      |

| 1.6.1 Arbiter Pipeline Stages17                                |

| 1.7 Motivation                                                 |

| 1.8 Objectives                                                 |

| 1.9 Thesis Organization                                        |

# Chapter 2

| Previ | ous l | Research Work                           | .22 |

|-------|-------|-----------------------------------------|-----|

| 2.1   | Buf   | fer Organization                        | 22  |

| 2.2   | Ser   | ial and Parallel FIFO Architecture      | 23  |

| 2.3   | DA    | MQ Buffer Organization Research Work    | 26  |

| 2.3.  | .1    | Virtual Channel Regulator (ViChaR)      | 28  |

| 2.3.  | .2    | Self-Compacting Buffers                 | 29  |

| 2.3.  | .3    | Mask-based                              | 31  |

| 2.4   | Lin   | k-List based DAMQ Organization          | 31  |

| 2.4.  | .1    | LLD and Static Read and Write Mechanism | 31  |

| 2.4.  | .2    | LLD Router                              | 32  |

| 2.4.  | .3    | LLD Communication                       | 33  |

| 2.4 | 1.4 | Slot-State Process                   |    |

|-----|-----|--------------------------------------|----|

| 2.4 | 1.5 | Flit Arrival and Departure Process   |    |

| 2.4 | .6  | VC-block Signal                      |    |

| 2.4 | I.7 | VC-Selector Module                   |    |

| 2.4 | .8  | Buffer-full Module or VC-full Module |    |

| 2.5 | Bu  | ffering Organization Approach        |    |

| 2.6 | He  | terogeneous Router Architectures     | 43 |

| 2.7 | Ro  | und Robin Arbiter                    | 46 |

| 2.7 | 7.1 | Conventional Arbiter Design          | 47 |

| 2.7 | 2.2 | Some Well-Known RR Arbiters          | 49 |

# Chapter 3

| Statically Adaptive Multi-FIFO Buffer Organization           |    |

|--------------------------------------------------------------|----|

| 3.1 Static Multi-FIFO (SMF) Buffer Architecture              | 53 |

| 3.2 Communication in CVC and SMF Models                      | 54 |

| 3.3 Similarity of CVC and SMF during Contention              | 56 |

| 3.4 Statically Adaptive Multi FIFO                           | 58 |

| 3.4.1 Dynamic Mode Selector                                  | 60 |

| 3.4.2 Deterministic Mode Selector                            | 61 |

| 3.5 CVC and SMF Router Micro-Architecture                    | 63 |

| 3.5.1 Adaptivity Hardware in SAMF Architecture               | 66 |

| 3.5.2 Synthesis of SAMF Router                               | 67 |

| 3.6 Experimental Results                                     | 69 |

| 3.6.1 Adaptivity of SAMF Mechanism                           | 69 |

| 3.6.2 Experiment Setup                                       | 71 |

| 3.6.3 Experimental Results and Analysis                      | 73 |

| 3.7 Novelty of Approach                                      | 78 |

| 3.8 Summary                                                  | 78 |

| <ul> <li>3.5 CVC and SMF Router Micro-Architecture</li></ul> |    |

# Chapter

4

| Effici | ent | Dynamic Virtual Channel Organization | .80 |

|--------|-----|--------------------------------------|-----|

| 4.1    | Ove | erview                               | 81  |

| 4.1.   | 1   | Simpler Communication in EDVC        | 81  |

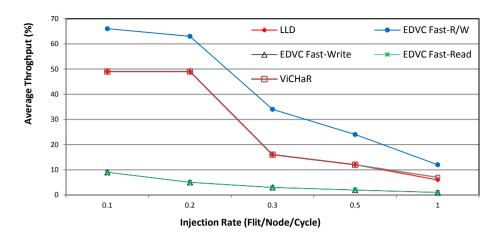

| 4.2    | ED  | VC Router Micro-Architecture         | 83  |

| 4.2.   | 1   | Slot-State Table                     | 84  |

| 4.2.   | 2   | Blocking Circuit                     | 84  |

| 4.2.   | 3   | Enabling Blocked Request and VC-full | 85  |

| 4.2.   | 4   | Operation of Read and Write Pointers | 85  |

| 4.2.   | 5   | EDVC Closing and Requesting Approach | 86  |

| 4.3    | Imp | proving Input-Port Buffer Access     | 87  |

| 4.3.1  | Fast Buffer Write                                   |    |

|--------|-----------------------------------------------------|----|

| 4.3.2  | Fast Buffer Read                                    |    |

| 4.4 No | velty of EDVC Mechanism                             |    |

| 4.4.1  | VCs for Blocked and Unblocked Packets               |    |

| 4.4.2  | Lower Congestion                                    | 90 |

| 4.4.3  | Deadlock Avoidance                                  |    |

| 4.4.4  | Novel EDVC based VC Organization                    | 94 |

| 4.5 Ex | perimental Results                                  | 94 |

| 4.5.1  | Hardware Requirements and Parameters of Input-Ports | 95 |

| 4.5.2  | EDVC Performance Evaluation                         |    |

| 4.6 Co | ncluding Remarks                                    |    |

# Chapter 5

| Rapid an | d Efficient Router Architecture                        | 107 |

|----------|--------------------------------------------------------|-----|

| 5.1 Ra   | pid Dynamic Queue Based Input-Port Structure           | 107 |

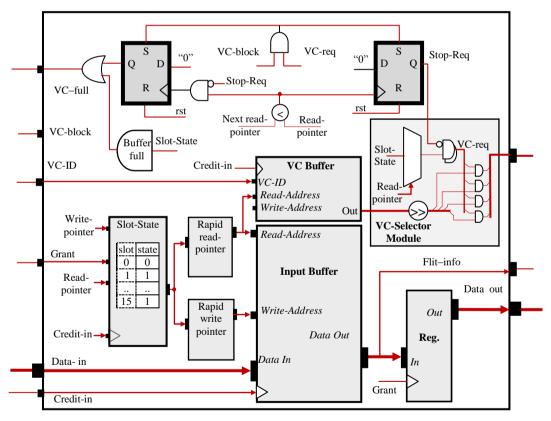

| 5.1.1    | Rapid Read and Write Pointers                          | 108 |

| 5.1.2    | RDQ Closing and Requesting Approach (Blocking Circuit) | 111 |

| 5.1.3    | Back Pressure for Low NoC Traffic                      | 112 |

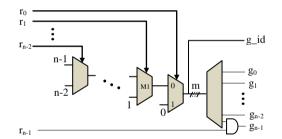

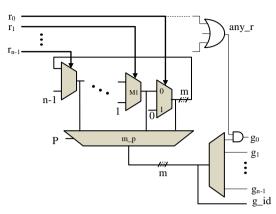

| 5.2 Inc  | lex-based Round Robin Arbiter (IRR)                    | 114 |

| 5.2.1    | Grant Index                                            | 115 |

| 5.2.2    | Fixed and Variable Priority Arbiter                    | 115 |

| 5.2.3    | IRR Arbiter Micro-Architecture                         | 116 |

| 5.2.4    | Functional Behaviour of IRR Arbiter                    | 117 |

| 5.2.5    | IRR Hardware Analysis                                  | 118 |

| 5.3 Sv   | vitch Allocator                                        | 119 |

| 5.3.1    | NoC Switch Allocator Function                          |     |

| 5.3.2    | VC Arbitration                                         | 121 |

| 5.3.3    | Post Switch Allocator Circuits                         |     |

| 5.3.4    | FIFO Arbitration and VC Selector                       |     |

| 5.3.5    | RDQ Router Arbitration                                 |     |

| 5.4 RI   | DQ Based Router Architecture                           |     |

| 5.4.1    | Rapid NoC Circuit Design                               |     |

| 5.4.2    | Fast Router Circuits                                   | 126 |

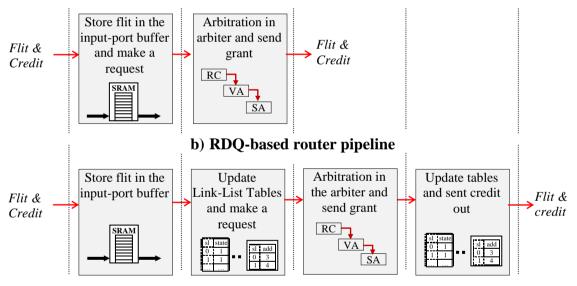

| 5.4.3    | Pipelined RDQ-based Routers                            |     |

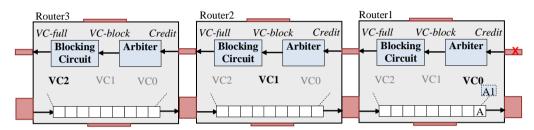

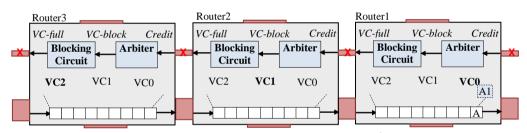

| 5.4.5    | Communication in RDQ-IRR router                        | 131 |

| 5.5 RI   | DQ and IRR based NoC Experimental Results              |     |

| 5.5.1    | IRR Arbiter Evaluation                                 |     |

| 5.5.2    | RDQ based Input-Port Implementation and Results        | 136 |

| 5.5.3    | RDQ based NoC Performance                              | 137 |

| 5.5.4    | NoC Evaluation Result                                  |     |

| 5.5.5 RDQ-IRR ba         | sed NoC Hardware Requirements |  |

|--------------------------|-------------------------------|--|

| 5.5.6 Performance        | Evaluation of RDQ-IRR NoC     |  |

| 5.6 RDQ-IRR Router       | based NoC Features            |  |

| 5.7 Summary and Co       | ncluding Remarks              |  |

| Chapter 6<br>Conclusions |                               |  |

| 6.1 Future Work          |                               |  |

|                          |                               |  |

| G105501 J                |                               |  |

# List of Tables

| Table 3.1. Connection in SAMF mode    60                                            | 0 |

|-------------------------------------------------------------------------------------|---|

| Table 3.2. Synthesis Results for 32nm technology and FPGA    FPGA                   | 8 |

|                                                                                     |   |

| Table 4.1. Closing and Requesting Operations of EDVC Mechanism                      | 6 |

| Table 4.2. Hardware specification of EDVC, LLD & ViCHaR input-ports                 | 6 |

|                                                                                     |   |

| Table 5.1. Closing and Requesting Operations of RDQ Mechanism         11            | 2 |

| Table 5.2. Electrical Parameters Gates from Synopsys Library    11                  | 8 |

| Table 5.3. Characteristics of 4-input Arbiters based on Table 5.2                   | 9 |

| Table 5.4. Hardware Characteristics of Strong Fairness Round Robin Arbiters         | 4 |

| Table 5.5. Hardware Characteristics of Weak Fairness Round Robin Arbiters       13. | 5 |

| Table 5.6. Input-Port Characteristics for DAMQ Approaches    13                     | 7 |

| Table 5.7. Input-port Hardware Characteristics    14                                | 3 |

| Table 5.8. Arbiter Hardware Characteristics    14                                   | 4 |

| Table 5.9. Router Characteristics and Advantage Rate       14                       | 5 |

# List of Figures

| Figure 1.1: a) An SoC with 3×3 Mesh NoC architecture, b) A router architecture         | 2  |

|----------------------------------------------------------------------------------------|----|

| Figure 1.2: A Typical Wormhole Packet Structure in NoC                                 | 3  |

| Figure 1.3: Source, S1 sends a packet consisting of 4 flits (Hf, Bf1, Bf2 and Tf)      | 4  |

| Figure 1.4: A Multiplexer-based Crossbar Switch.                                       | 5  |

| Figure 1.5: Conventional VC Flow Control Communication                                 | 5  |

| Figure 1.6: Register -based Parallel FIFOs                                             | 6  |

| Figure 1.7: SoC (NoC), Router and Queue Architectures.                                 | 8  |

| Figure 1.8: Four Different Scenarios in Conventional Wormhole VC Communication         | 11 |

| Figure 1.9: Input-Ports with Dynamic and Static Queues                                 | 12 |

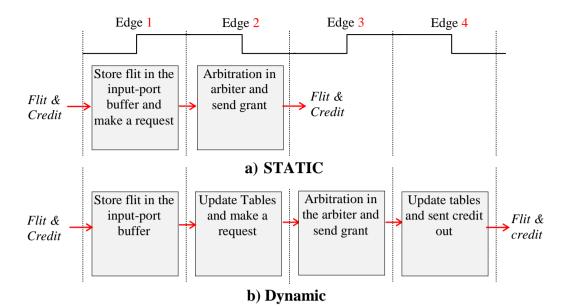

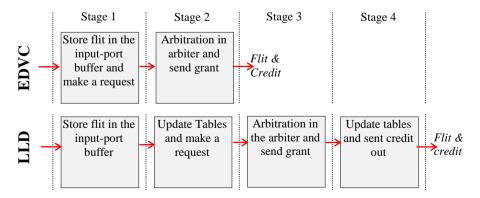

| Figure 1.10: Staic vs. Dynamic Input-Port Pipelines                                    | 15 |

| Figure 1.11: HF Flit in VC1 of Input-port 5 of Router 3 Traveling to Input-port 2      | 16 |

| Figure 1.12: The pipelined stages of a typical VC-based arbiter                        | 17 |

| Figure 1.13: The pipelined stages of a typical virtual channel arbiter                 | 18 |

| Figure 2.1: Conventional Shift Register (serial) FIFO                                  | 23 |

| Figure 2.2: SRAM-Based FIFO Using Parallel Style                                       | 24 |

| Figure 2.3: Buffer Threshold Utilization vs. Buffer Size.                              | 24 |

| Figure 2.4: SRAM-based FIFO                                                            | 25 |

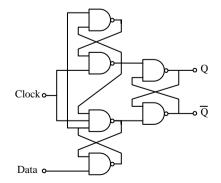

| Figure 2.5: A Positive-Edge-Triggered D-FF                                             | 25 |

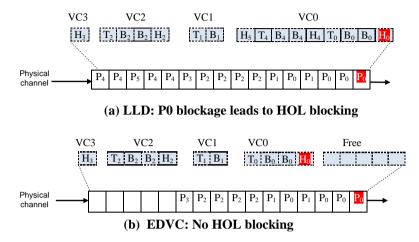

| Figure 2.6: Head of Line Blocking in DAMQ Output Channel                               | 26 |

| Figure 2.7: Reserved Space for Virtual Channels                                        | 28 |

| Figure 2.8: One big table and two trackers used in ViChaR method                       | 29 |

| Figure 2.9: Write and Read Scenario in Self-Compacting Buffer                          | 30 |

| Figure 2.10: Input-Ports with Two Queue Type                                           | 32 |

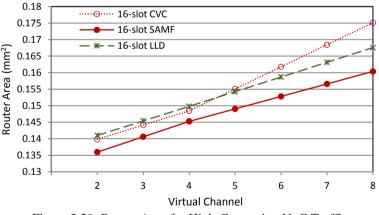

| Figure 2.11: LLD Based Input-Port.                                                     | 32 |

| Figure 2.12: LLD Router (4-VC and 16-slot) – Lookup tables                             | 33 |

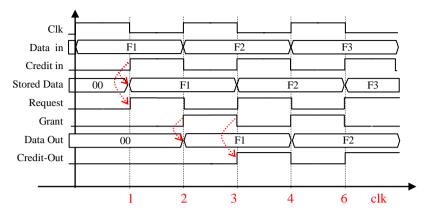

| Figure 2.13: Timing Diagram of a Pipeline Communication inside a LLD Input-Port        | 34 |

| Figure 2.14: Updating of LLD tables                                                    | 35 |

| Figure 2.15: LLD Read and Write Pointers                                               | 35 |

| Figure 2.16: VC-Selector Request Logic                                                 | 37 |

| Figure 2.17: Input-Port Buffer-Full and VC-Full Modules                                | 38 |

| Figure 2.18: Any EB architecture derived for edge-triggered flip-flops                 | 42 |

| Figure 2.19: Organization of the generalized ElastiStore Port.                         | 42 |

| Figure 2.20: Integration of ElastiStore in NoC routers                                 | 43 |

| Figure 2.21: Proposed Hybrid Scheme in A $4 \times 4$ Mesh with two VCs per Input-Port | 44 |

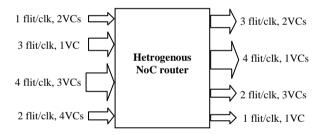

| Figure 2.22: Heterogeneous NoC Router Example.                                         | 45 |

| Figure 2.23: A wormhole v-VC router, the Switch allocator consists of two sets         | 46 |

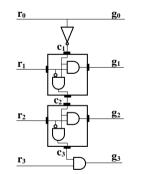

| Figure 2.24: A 4-Input Fixed Priority Arbiter Architecture.                            | 47 |

| Figure 2.25: A 4-Input Variable Arbiter Architecture.                                  | 48 |

| Figure 2.26: A 4-Input RoR Arbiter Architecture.                                   | 48  |

|------------------------------------------------------------------------------------|-----|

| Figure 2.27: A 4-Input Matrix arbiter.                                             | 49  |

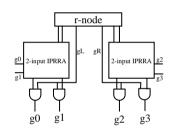

| Figure 2.28: A 4-Input PRRA Architecture.                                          | 50  |

| Figure 2.29: A 4-Input IPRRA Architecture                                          | 50  |

| Figure 2.30: A 4-Input HDRA Architecture.                                          |     |

|                                                                                    |     |

| Figure 3.1: A Typical SRAM-Based FIFO                                              |     |

| Figure 3.2: SMF Input-Port Architecture ( <i>n</i> VC )                            |     |

| Figure 3.3: CVC Input-Port Architecture ( <i>n</i> VC)                             |     |

| Figure 3.4: Conventional VC Flow Control                                           |     |

| Figure 3.5: SMF Flow Control                                                       |     |

| Figure 3.6: 4-VC CVC Buffer (VC3 Write and VC1 Read)                               |     |

| Figure 3.7: 4-VC SMF Buffer (VC3 Write and VC1 Read)                               |     |

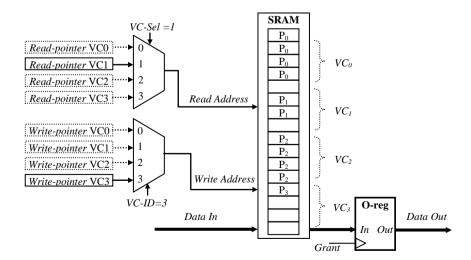

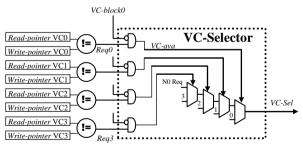

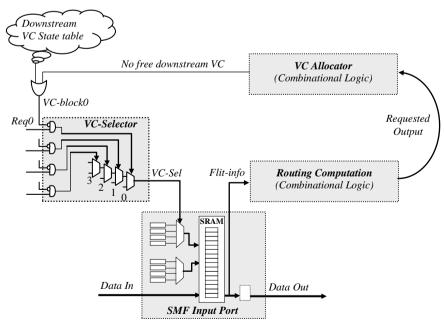

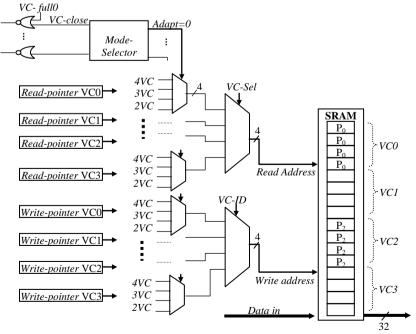

| Figure 3.8: VC-Selector Circuit                                                    |     |

| Figure 3.9: Selection Function of a Free Request                                   |     |

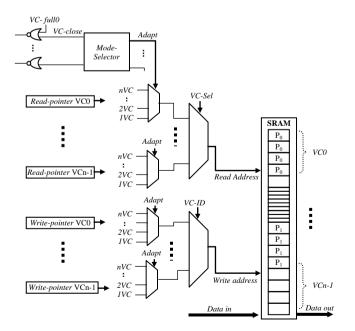

| Figure 3.10: nVC SAMF Architecture                                                 |     |

| Figure 3.11: 4-VC SAMF Architecture with 2 Active VCs.                             | 59  |

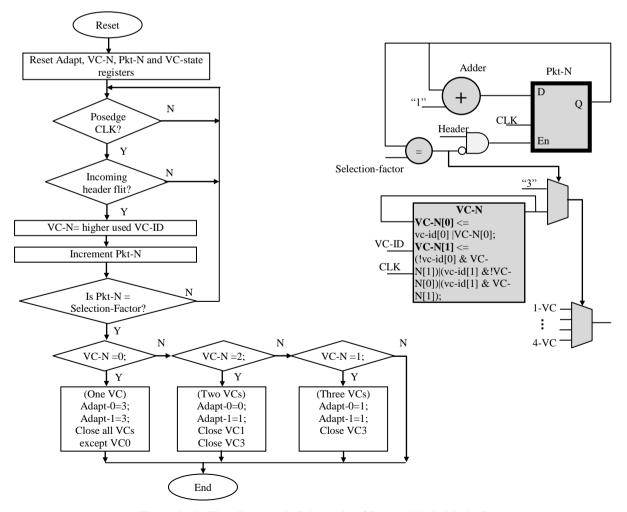

| Figure 3.12: Flowchart Process of the Dynamic Mode-Selector                        | 61  |

| Figure 3.13: Flow Process & Schematic of Deterministic Mode-Selector               | 62  |

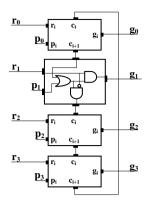

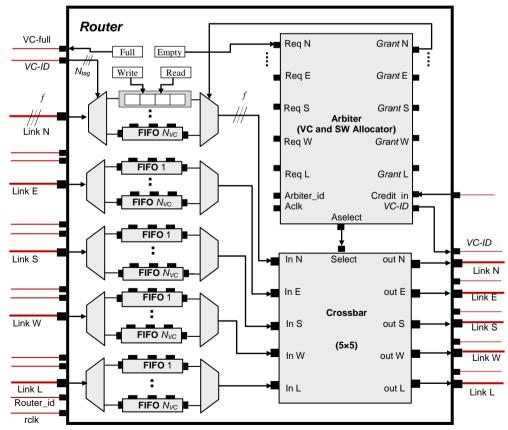

| Figure 3.14: 5×5 CVC Wormhole Router                                               | 63  |

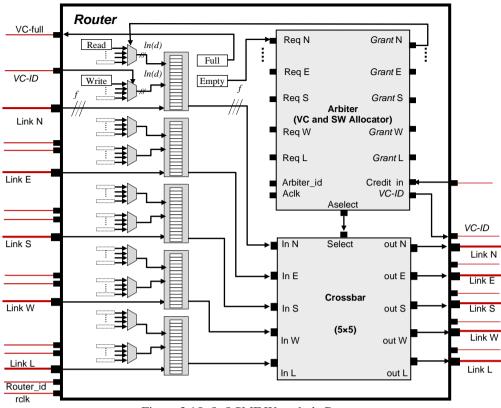

| Figure 3.15: 5×5 SMF Wormhole Router                                               | 64  |

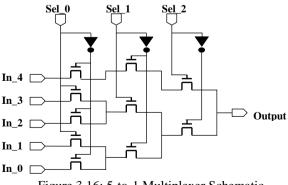

| Figure 3.16: 5-to-1 Multiplexer Schematic                                          | 64  |

| Figure 3.17: A Multiplexer-based Crossbar Switch                                   | 65  |

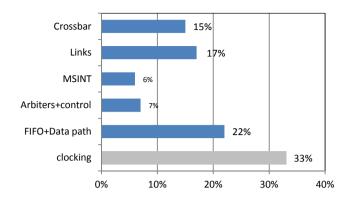

| Figure 3.18: Power Breakdown for a CVC NoC Router                                  | 66  |

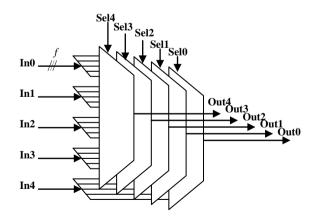

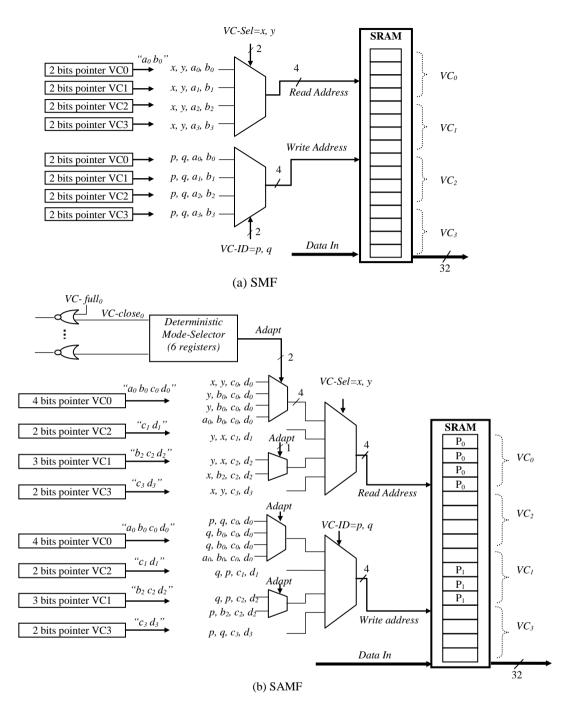

| Figure 3.19: SMF and SAMF Architectures                                            | 67  |

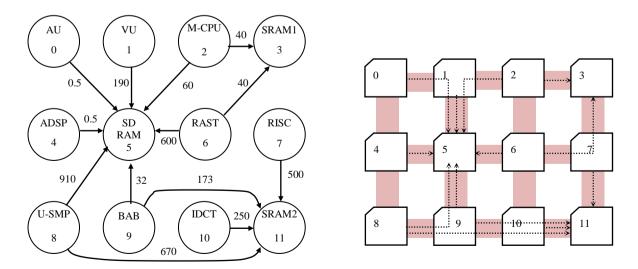

| Figure 3.20: MPEG4 mapping core graph to a Mesh Topology and its XY routing        | 71  |

| Figure 3.21: AV Benchmark mapping core graph to a Mesh Topology and its XY routing | 72  |

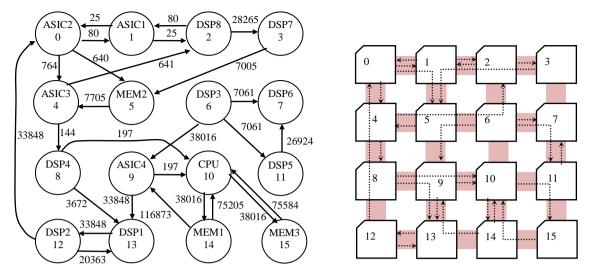

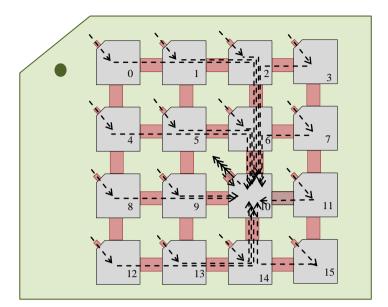

| Figure 3.22: Fixed Communication for a 4×4 Mesh NoC                                | 73  |

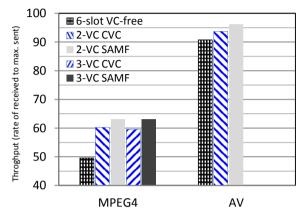

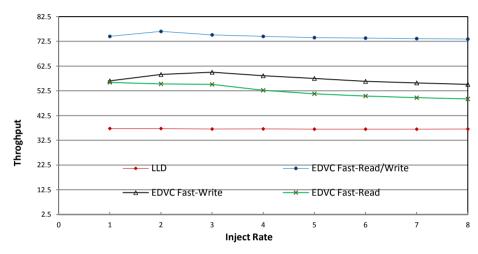

| Figure 3.23: Throughput for Different NoC Applications                             | 74  |

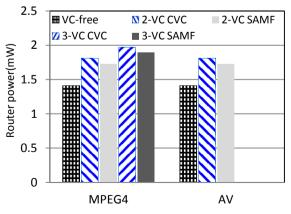

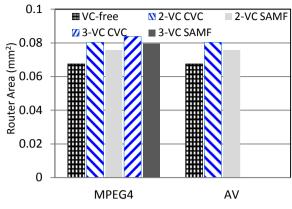

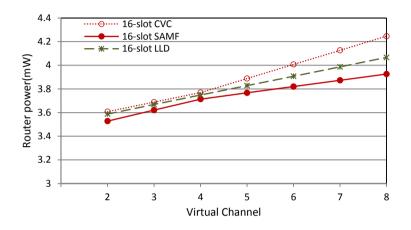

| Figure 3.24: Power of a Router for Different NoC applications                      | 74  |

| Figure 3.25: Area of a Router for Different NoC applications                       |     |

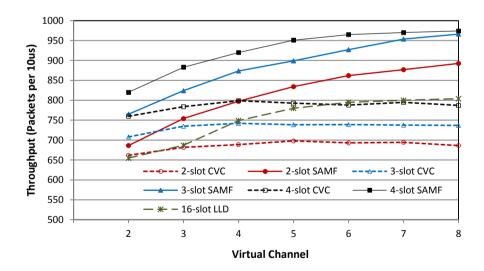

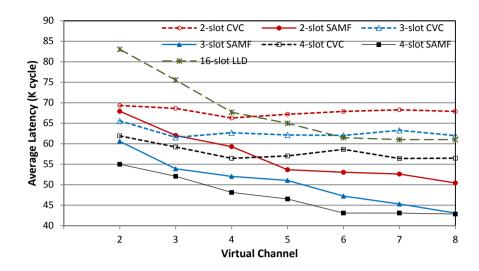

| Figure 3.26: Throughput for High-Contention NoC Traffic                            |     |

| Figure 3.27: Average Latency for High-Contention NoC Traffic                       |     |

| Figure 3.28: Router Power for High-Contention NoC Traffic                          |     |

| Figure 3.29: Router Area for High-Contention NoC Traffic                           |     |

| Electric 4.1. EDVC Is set Dis ele Disconser                                        | 0.1 |

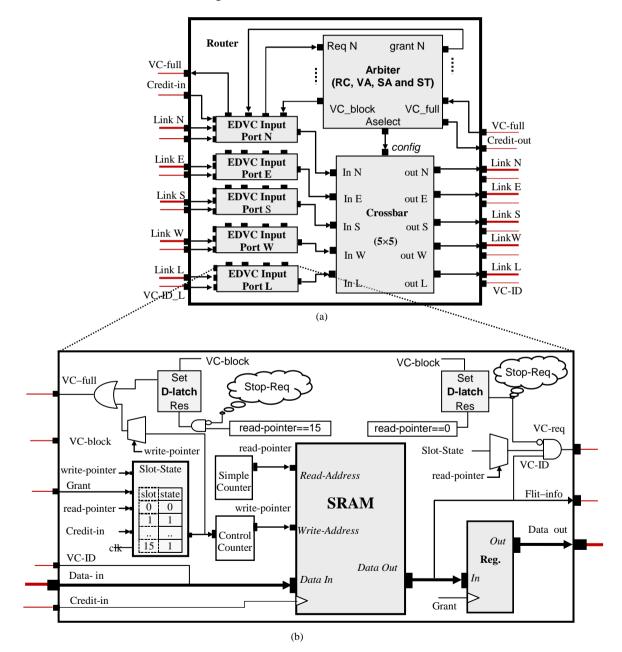

| Figure 4.1: EDVC Input-Port Block Diagram                                          |     |

| Figure 4.2: Three Steps of EDVC VC Flow Control                                    |     |

| Figure 4.3: EDVC vs. LLD Buffer Pipelines                                          |     |

| Figure 4.4: 5×5 EDVC Router and Input-Port Micro-Architecture                      |     |

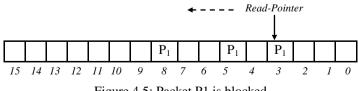

| Figure 4.5: Packet P1 is blocked                                                   | 84  |

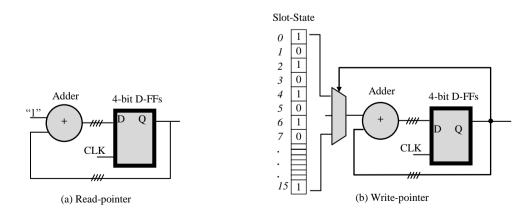

| Figure 4.6: 4-bit Simple Read and Write Pointers                                              | 85  |

|-----------------------------------------------------------------------------------------------|-----|

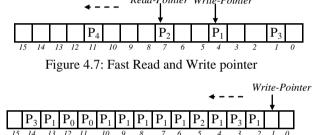

| Figure 4.7: Fast Read and Write pointer                                                       | 87  |

| Figure 4.8: Write at location 15 occurs 14 cycles after a write at location 1                 | 87  |

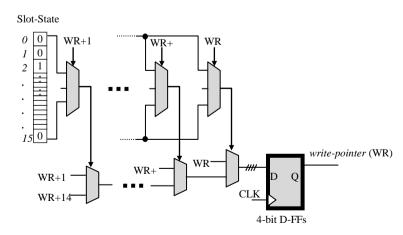

| Figure 4.9: 4-bit EDVC Fast Write-Pointer                                                     | 87  |

| Figure 4.10: 4-bit EDVC Fast <i>Read-Pointer</i>                                              | 88  |

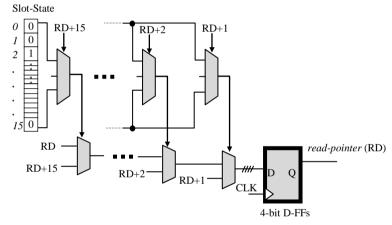

| Figure 4.11: Packet Blocking in LLD and EDVC.                                                 | 90  |

| Figure 4.12: (a) P4, P5 and P6 packets are blocked due to HOL of P0 (b) Free slots            |     |

| Figure 4.13: LLD Packet Flow Situations.                                                      | 91  |

| Figure 4.14: EDVC Packet Flow Situations.                                                     | 92  |

| Figure 4.15: High Contention Situation in a LLD NoC                                           | 93  |

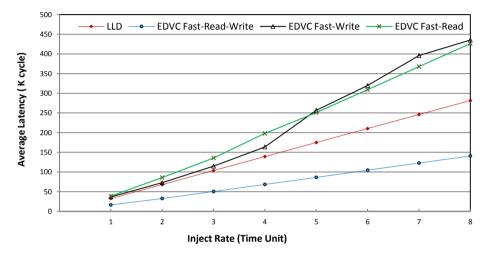

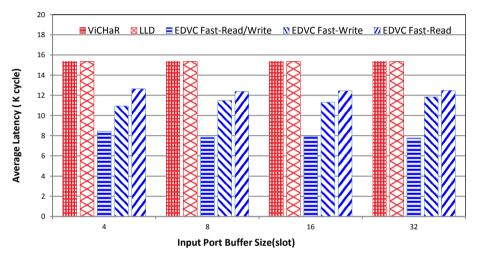

| Figure 4.16: Average Latency for MPEG4 Decoder Traffic                                        | 99  |

| Figure 4.17: Average Latency for AV Benchmark Traffic                                         |     |

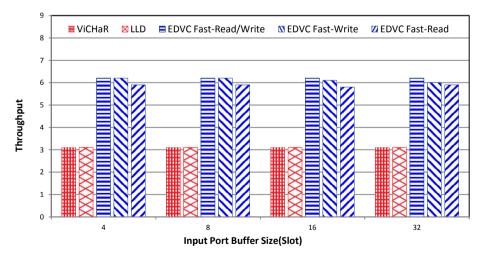

| Figure 4.18: Average Throughput for MPEG4 Decoder Traffic                                     | 100 |

| Figure 4.19: Average Throughput for AV Benchmark Traffic                                      | 100 |

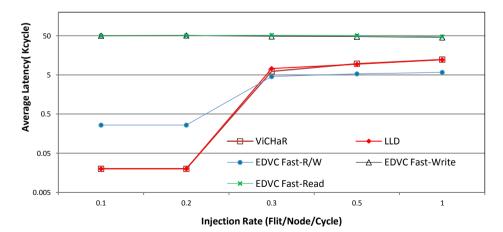

| Figure 4.20: Average Latency for Hotspot Traffic                                              | 101 |

| Figure 4.21: Average Throughput for Hotspot Traffic                                           | 101 |

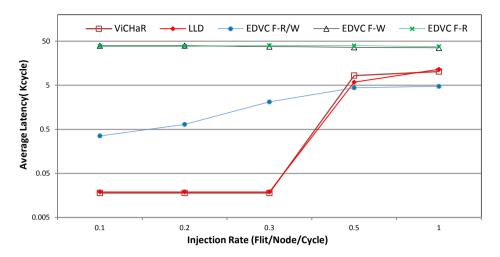

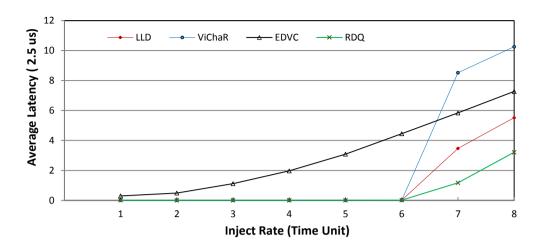

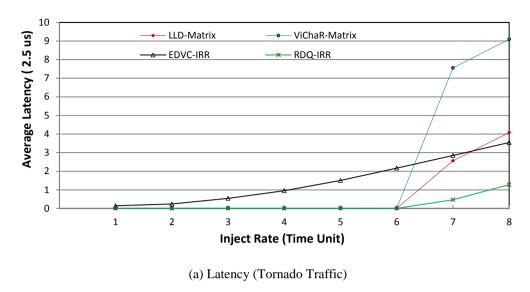

| Figure 4.22: Average Latency for Tornado Traffic.                                             |     |

| Figure 4.23: Average Throughput for Tornado Traffic.                                          |     |

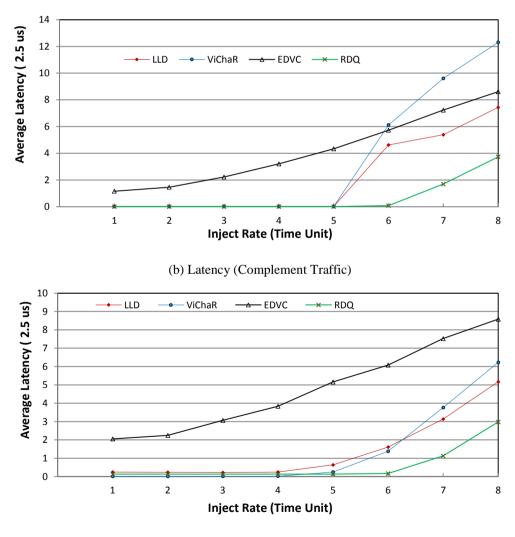

| Figure 4.24: Average Latency for Complement Traffic.                                          | 102 |

| Figure 4.25: Average Throughput for Complement Traffic.                                       | 103 |

| Figure 5.1: RDQ Input-Port Micro-Architecture.                                                | 108 |

| Figure 5.2: Timing diagram of a 2-bit EDVC fast read-pointer for some Slot-State              | 109 |

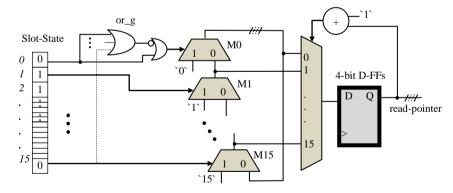

| Figure 5.3: Rapid 4-bit Read-Pointer                                                          | 109 |

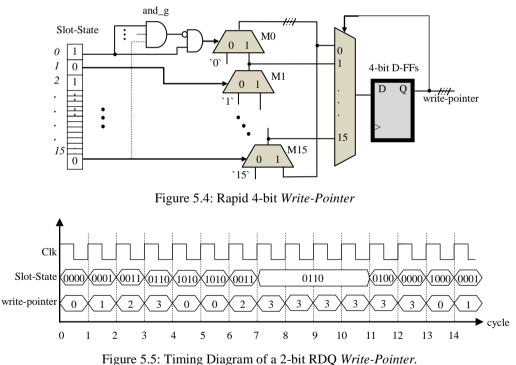

| Figure 5.4: Rapid 4-bit Write-Pointer                                                         | 110 |

| Figure 5.5: Timing Diagram of a 2-bit RDQ Write-Pointer.                                      | 110 |

| Figure 5.6: Low Flit Injection Traffic Scenario in EDVC, LLD and RDQ                          | 113 |

| Figure 5.7: <i>n</i> -input fixed priority arbiter, where $m = \log_2(n)$ .                   | 115 |

| Figure 5.8: <i>n</i> -Input Variable Priority Arbiter                                         |     |

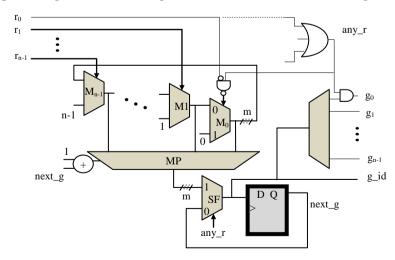

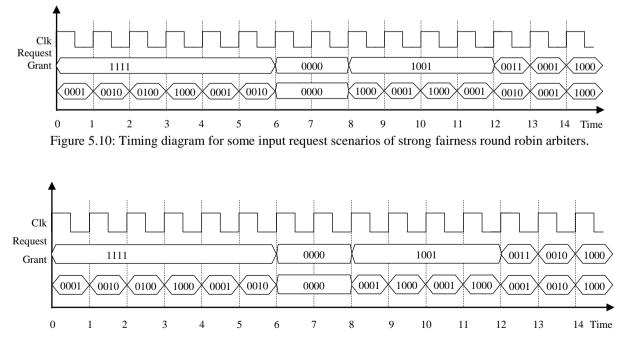

| Figure 5.9: n-Input IRR Arbiter, where $m = log_2(n)$                                         | 116 |

| Figure 5.10: Timing diagram for some input request scenarios                                  |     |

| Figure 5.11: Timing diagram for some input request scenarios                                  | 117 |

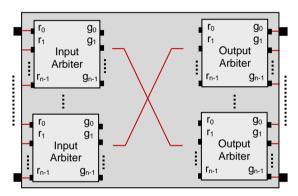

| Figure 5.12: An Input-First Separable Allocator.                                              | 120 |

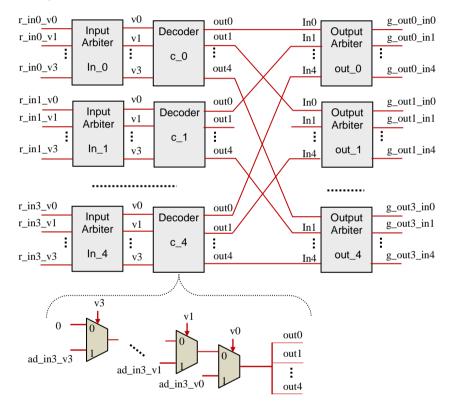

| Figure 5.13: A 5×5 RR-Based Separable SA Micro-Architecture                                   | 121 |

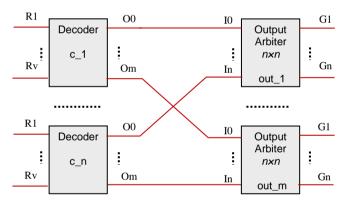

| Figure 5.14: $n \times m$ SA architectures, $n = \#$ of inputs, $m = \#$ of outputs, $v = \#$ |     |

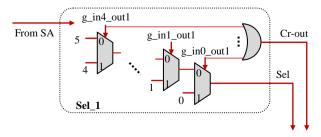

| Figure 5.15: Output-Port 1 of Selection Module                                                |     |

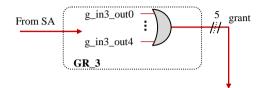

| Figure 5.16: Input 3 of the Grant Module                                                      |     |

| Figure 5.17: RR-based VC-Selector Utilized in LLD and ViChaR                                  | 123 |

| Figure 5.18: RDQ-Based VC-Selector in the Input-port Mechanism.                               |     |

| Figure 5.19: VC0, VC1, VC2 and VC3 Arbitration. RR for LLD and ViChaR                         |     |

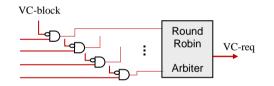

| Figure 5.20: VC-Block Circuit Associated to VC1 of Input-Port 3                               |     |

| Figure 5.21: A LLD-HDRA Router Micro-Architecture                          | 127 |

|----------------------------------------------------------------------------|-----|

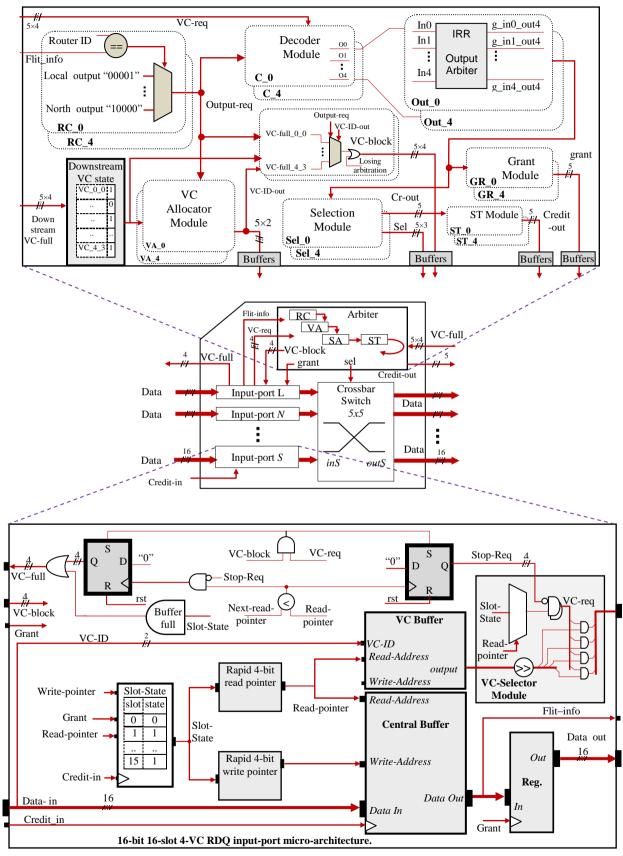

| Figure 5.22: A RDQ-IRR Router Micro-Architecture                           | 128 |

| Figure 5.23: RDL vs. Conventional Dynamic Input-Port (LLD or ViChaR)       | 129 |

| Figure 5.24: RC generates free requested output VC                         | 130 |

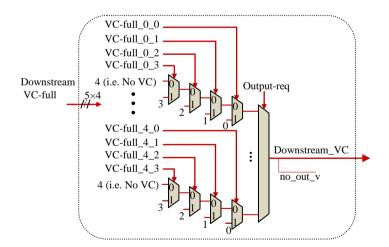

| Figure 5.25: VC Allocator generates free downstream VC                     | 130 |

| Figure 5.26: Three Steps of RDQ-IRR VC Flow Control.                       | 132 |

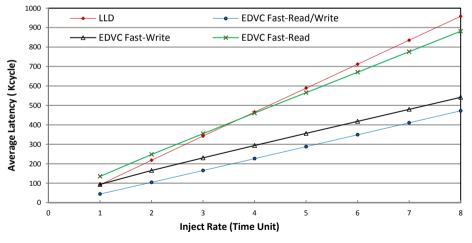

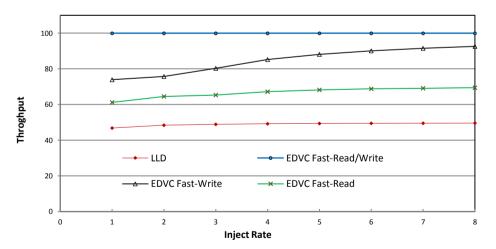

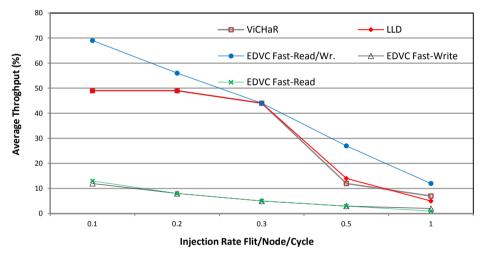

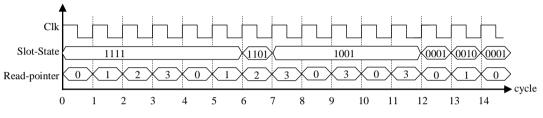

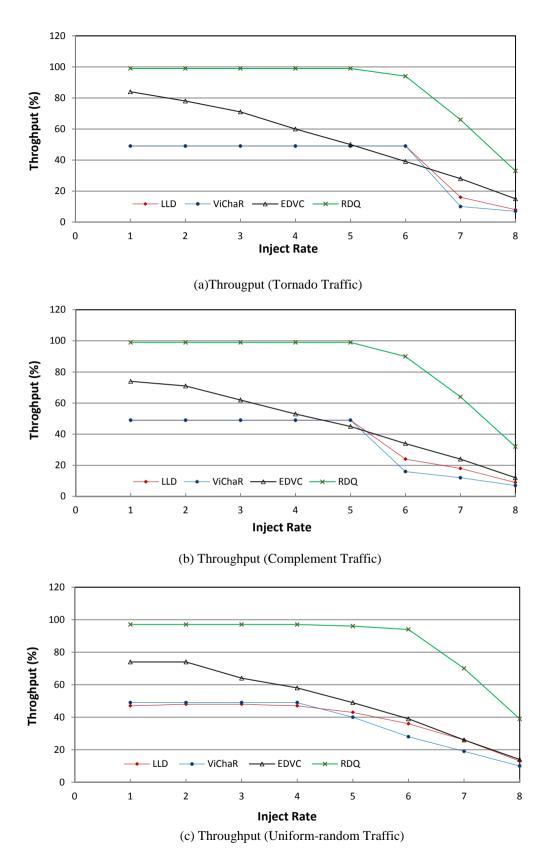

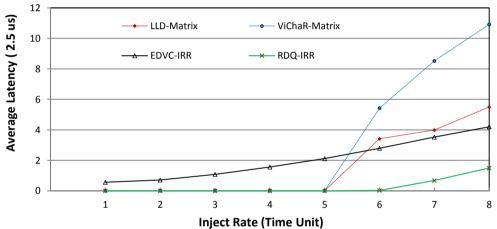

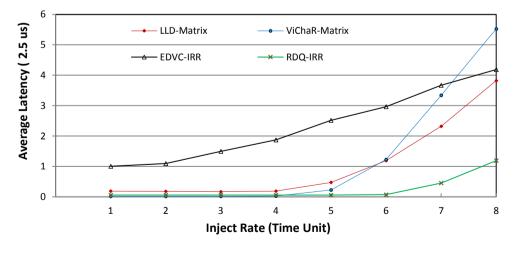

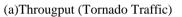

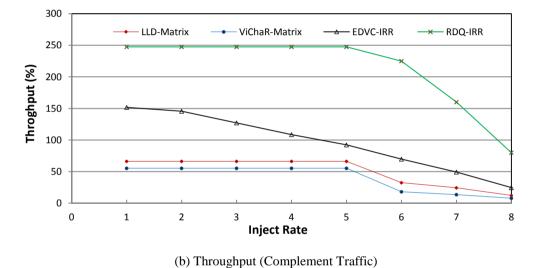

| Figure 5.27: Latency for Tornado, Complement and Uniform Random Traffic    | 139 |

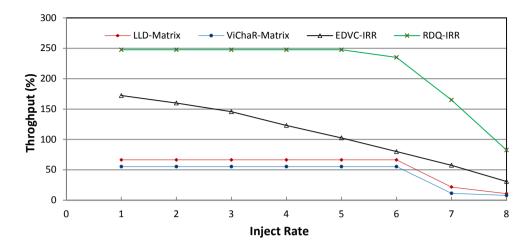

| Figure 5.28: Throughput for Tornado, Complement and Uniform Random Traffic | 140 |

| Figure 5.29: latency for Tornado, Complement and Uniform Random Traffic.   | 147 |

| Figure 5.30: Throughput for Tornado, Complement and Uniform Random Traffic | 148 |

# Chapter 1 Introduction

In this chapter, we introduce the approaches of Virtual Channel (VC) organization and arbitration for novel NoC router design. First of all, we try to present some commonly used terms, mechanisms and micro-architectures used in the design of Network on Chip (NoC) systems. We also introduce the problems related to the conventional NoC designs as well as the objectives that are pursued in this dissertation. Overall, we present three approaches related to NoC design. The first two approaches are related to VC organization and presented in Chapters 3 and 4. The third approach is related to data flow arbitration and key to our rapid NoC router architecture presented in Chapter 5.

## 1.1 Network on Chip a State of the Art Paradigm

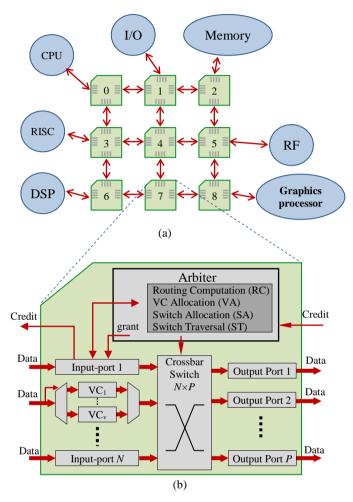

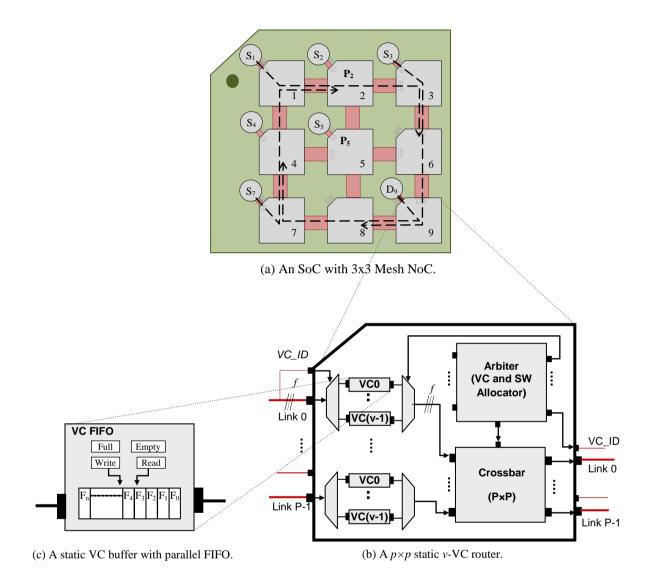

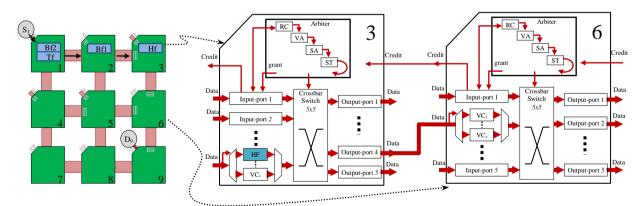

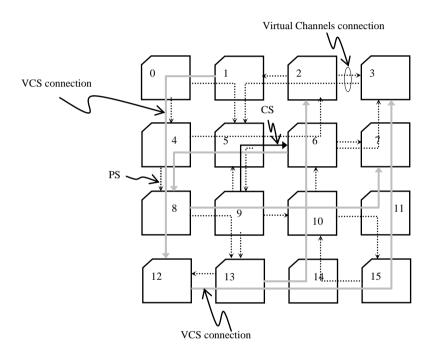

Network on Chip (NoC) architecture provides a communications infrastructure for the cores of a multi-core System-on-Chip (SoC). The NoC enables the SoC-cores to communicate among each other concurrently by sending messages asynchronously. NoC structures improve the scalability and power efficiency of complex SoCs as compared to other conventional communication systems. Figure 1.1a illustrates an SoC including some IP cores that are connected through a  $3\times3$  Mesh NoC architecture. The NoC includes a network of routers (switches) that are interconnected by data links.

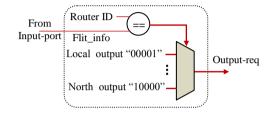

Figure 1.1: a) An SoC with  $3 \times 3$  Mesh NoC architecture, b) A router architecture with N inputs and P outputs.

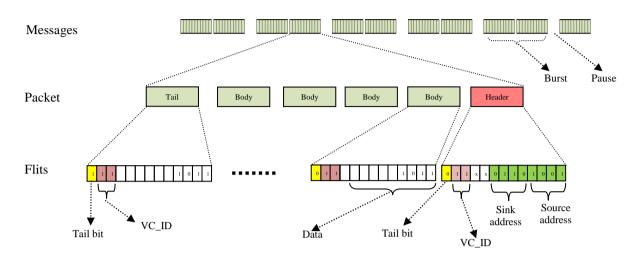

### **1.2 Wormhole Routing**

A most viable communication mechanism employed in NoCs is packet-based wormhole routing [1]. The message in wormhole routing is made of multiple packets where each packet consists of multiple flits. A flit is a basic unit of data that is generally transferred at (the NoC) clock rate. Figure 1.2 illustrates the message structure of a packet-based wormhole flow control. The first flit of a packet is called the header flit and holds the route information of the associated packet. The remainder flits are called body flit where the last flit is known as tail flit. The body and tail flits contain data and may also contain two pieces of information: tail state and VC identification as shown in Figure 1.2. When the header flit of a packet passes through a route

made of routers, the route path is reserved for that packet. The route path remains reserved until all the packet flits pass through it.

Figure 1.2: A Typical Wormhole Packet Structure in NoC.

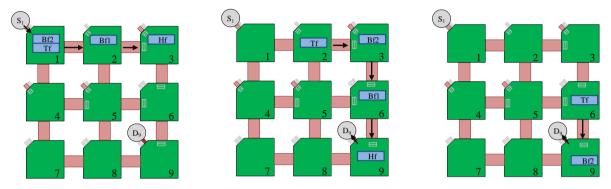

For example, consider a 2D mesh NoC wormhole communication situation depicted in Figure 1.3, where the source, S1 sends a packet consisting of 4 flits (Hf, Bf1, Bf2 and Tf) to the destination D9. Assume that the data (packets) movement follows XY routing methodology where the packets first move in X direction to reach to the Y dimension of their destinations, then they move to Y direction to reach their destination. In a basic NoC communication (no VC), passing the header flit, Hf through each router leads the router's input and output ports to be reserved, where no other packets can pass through those ports. After the passage of tail flit, Tf through each router leads the release of that port. During the packet transfer, the flits are temporarily kept in the input (or output) port buffers of the routers in a First-In First-Out (FIFO) fashion. One important feature of the data flow in the case of Figure 1.3 is that the route-path between S1 and D9 is reserved when the flits move through it. Therefore, the flow of data moves without any blocking. Such kind of data flow does not always provide optimum performance. Other messages of other sources where routes or part of their routes are shared with the reserved route have to wait until the route becomes free. These waiting conditions continue even when there is no communication through the reserved route. Sometimes, the reserved route is sometimes idle and will block other packets to pass through it. This kind of data flow incurs higher latency and lower utilization of shared NoC resources. One way of alleviating this problem and improve NoC throughput is by utilizing Virtual Channel (VC). To facilitate creating multiple VCs per physical channel, the messages are allocated in units of flits. The term "channel" or "physical channel" in this dissertation refers to a data link that connects the output-port and input-port of two interconnecting routers. The critical role of VC mechanism and architecture in the efficiency of NoC has encouraged us to present two novel VC organizations in Chapters 3 and 4. To understand the VC organization, we need to explore the structure and mechanism of a NoC router.

Figure 1.3: Source, S1 sends a packet consisting of 4 flits (Hf, Bf1, Bf2 and Tf) to destination D9.

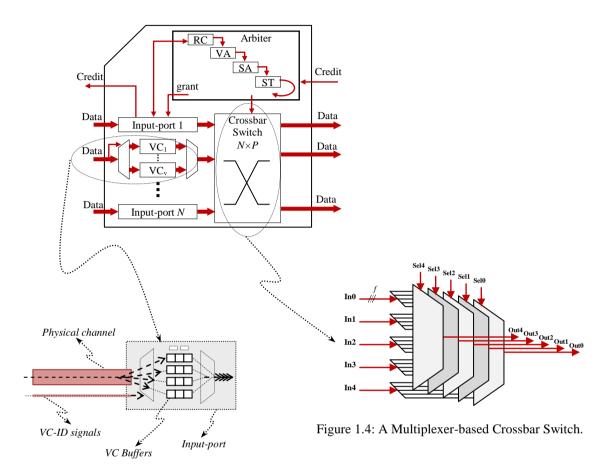

### **1.3 NoC Router Architecture**

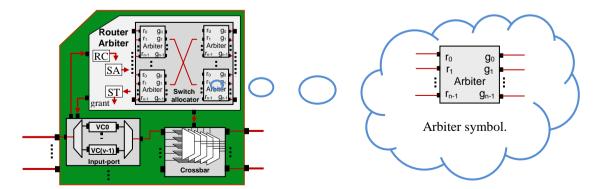

An NoC router accepts packets from the source core (or other router modules) and delivers them to the sink/destination core (or other router modules). The traditional micro-architecture of a router consists of input and output ports, an arbiter, and a crossbar switch as illustrated in Figure 1.1b [1]. The input and output ports can be simple data buses that connect a router to its channels, but at least one of them should consist of a circuit to perform buffering and traversal of the incoming flits. In this dissertation, the input-ports utilize the buffers, and the output-ports are simple data buses. After buffering a flit, the input-port issues a request signal to the arbiter. The arbiter performs arbitration among the potential VC flits that make request to access the crossbar and other shared resources [2]. When a flit wins arbitration and is granted to exit the router, it passes through the crossbar switch. For NoCs utilizing VCs, the structure of router input-port becomes complex. However, it significantly improves the efficiency of NoC. The crossbar switch can be configured to connect any input buffer of the router to any output channel (port), but under the constraints that an input-port is connected to only one output-port. The micro-architecture of crossbar switch is simple as illustrated in the multiplexer-based architecture of Figure 1.4. The structure of a router arbiter can be simple when an NoC does not

utilize VC organization. However, the arbiter becomes complex for a VC based router that can have a direct effect on the efficiency of NoC. The critical impact of arbiter on the efficiency of NoC has encouraged us to design a fast and efficient arbiter in Chapter 5.

Figure 1.5: Conventional VC Flow Control Communication.

### 1.4 VC organization

To improve the data flow efficiency in NoCs, each input or output port can utilize VCs to share a physical communication channel by multiple packets. A VC virtually splits a single physical channel to provide two or more virtual paths for the packets to be routed. Consider the case illustrated in Figure 1.3, two packets can reserve and pass through the same route if there are 2 VCs available for each physical channel. In other words, the flits of one packet will interleave with the flits of the other packet over a physical channel by using a rotating flit-by-flit arbitration. The routing of each flit can be guaranteed because the flits belonging to a packet are attached with the VC identification (*VC-ID*) tag at each router. Then these flits become differentiable at the downstream routers. Figure 1.2 illustrates a 2-bit *VC-ID* tag that exists in all

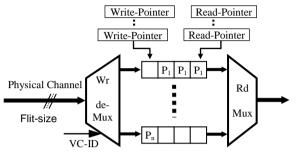

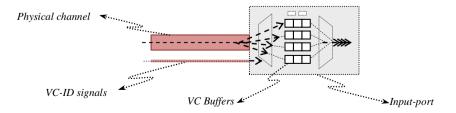

the flits of a packet, and these tags are identical when the flits enter a router. Figure 1.5 illustrates the conventional micro-architecture of a VC decoder based on a simple demultiplexer. The *VC-ID* is connected to the selection port of the de-multiplexer and causes the incoming flit to reside in the associated VC buffer. Basically, the flits of a packet are always stored in the same VC buffer. We assume that a router implements VCs at the input-ports and the input-port storage (buffer) temporarily stores the incoming flits. When a router receives a packet flit, it puts the flit into its input-port buffer, and the flit remains there until the required resources for departure becomes available.

#### **1.4.1 FIFO Architecture**

We introduce the architecture and mechanism of data buffering organization (port architecture) in the NoC routers. As mentioned earlier, the data buffering can be in the form of First-In First-Out (FIFO) to keep the flits of a packet in correct order during communication. Two types of FIFO schemes: serial and parallel have been utilized in digital design [3, 4, 5, 6]. The serial FIFO (e.g. shift register) that works on the fall-through principle (or pipeline) has been the initial FIFO type. However, the architectures of conventional FIFOs are constantly being improved. Currently, most of the FIFOs used are of parallel type, which are faster than serial FIFOs [7].

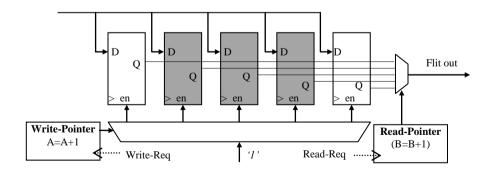

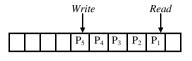

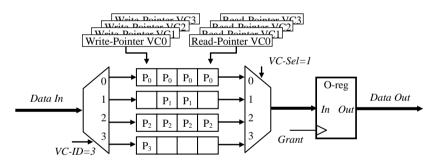

The proposed schematic of Figure 1.6 shows a parallel register-based FIFO. *Write-pointer* and *Read-pointer* are two circular counters that are connected to the selection ports of demultiplexer and multiplexer. When a write is requested, the *Write-pointer* enables the tail register to store the incoming flit. Then it is incremented to enable the next free slot in the FIFO.

Figure 1.6: Register -based Parallel FIFOs

When a read is requested, the *Read-pointer* is incremented to select the output of head slot in the FIFO. Since the pointers increment in a circular manner, the flits enter and exit in a circular manner too. Due to which, the parallel FIFO is also known as a Circular Queue (CQ).

#### 1.4.2 Queue Buffers

In addition to FIFO, another buffering component used in a NoC router is the Queue. A Queue temporarily stores the flit(s) of a packet in a first come first serve (FCFS) manner until the network resources become available. FIFO and Queue terms are sometimes interchangeably referred as an NoC buffer. However, a Queue refers to all types of buffers with the FCFS concept that also contains FIFO buffers. In terms of architecture, FIFO mostly refers to serial or parallel FIFOs as discussed earlier. Serial and parallel FIFO designs are very common in digital design. The concepts discussed in this and previous sections are helpful to clarify the main difference between the VC organizations presented in Chapter 3 and 4. The Chapter 3 approach presents a simple and adaptive multi-FIFO buffer architecture, where the Chapter 4 approach is a small and dynamic multi-queue buffer organization. In the following section, we explain the mechanism and pros and cons of traditional VC organization.

#### 1.4.3 Traditional Wormhole Routing

Wormhole routing is a conventional communication mechanism used in VC based NoC systems. To employ wormhole routing in NoCs, the flit that is part of a packet is buffered at least at the input or output ports of the router [1]. Once the flit of a packet occupies the buffer of a channel, no other packet can access the channel even when the channel buffer is empty. This type of switching flow is prone to contentions and in some cases deadlocks. The contention occurs when the latency of a flit becomes more than the time delay of its location (i.e. router). For example, when a flit is blocked in a router, it should stay in the router until its requested output becomes available. Therefore, the time delay of flit will get higher than the time delay of router that creates a contention situation. Another important issue in the performance of NoCs is the deadlock. Assume wormhole switching and a packet flit is not allowed to pass an element of NoC twice. Then a deadlock will occur when no packet can advance because each packet requires a channel that is already occupied by the other packet. Consider the deadlock situation illustrated in Figure 1.7a. Assume the sources 1, 3, 7 and 9 start sending packet at the same time to the destinations 6, 8, 2 and 4 respectively. The dashed lines in the figure show the route of

each packet. The communication becomes deadlock at routers 1, 3, 7 and 9 as each packet requires a channel that is already occupied by the other packet.

Figure 1.7: SoC (NoC), Router and Queue Architectures.

One of the traditional ways to alleviate contention and remove deadlock is to use the VC mechanism [8]. Consider a configuration where the number of VCs for each channel is equal to the maximum shared packets of that channel. Therefore, as soon as a flit reaches to a router, there will be a free VC facilitating the flit to move to the next router. This means there will be no blocking, and deadlock will not occur in the NoC. Virtual channels are also used to improve message latency and NoC throughput. By allowing messages to share a physical channel, the

messages can make progress rather than remain blocked. Moreover, the overall time that a message is blocked at a router and waits for a free channel is lowered. In this way, the sharing of physical channel leads to faster NoC communication and an overall reduction in message latency. In Conventional Virtual Channel (CVC) method, a physical channel support several virtual channels that are multiplexed across the physical channel as shown in Figure 1.5. As depicted in the router of Figures 1.7b, the implementation of VCs needs extra resources i.e. *FIFO* buffer for each VC, *De-multiplexers* and *Multiplexers* for each input-port as well as *VC allocator* and bigger *switch allocator* for the arbiter [1, 9, 10, 11, 12].

### **1.5 Static and Dynamic VC Organizations**

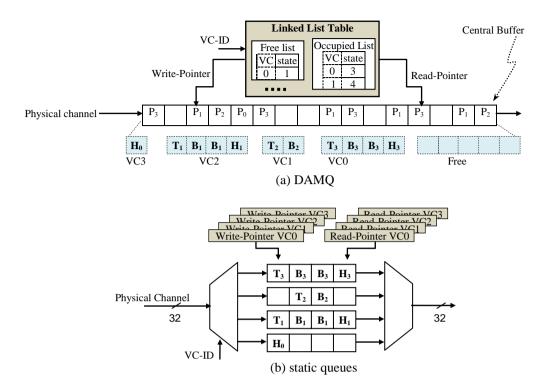

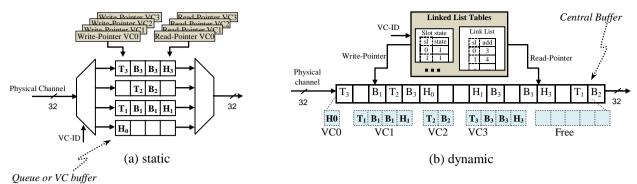

In this report, we have selected to provide buffering organization in the input-ports of channels. The input-ports employ two types of data flow mechanisms commonly known as static and dynamic to organize VCs [4]. In the static mechanism, the buffer slots are statically allocated to the incoming packets, and in the case of dynamic mechanism such as Dynamically Allocated Multi Queues (DAMQ), the buffer slots are dynamically allocated to the incoming packet flits. Most of dynamic VC organizations are table based [13, 14], where a central buffer includes multiple VC queues, and a table keeps the flits of each queue in FCFS order. Basically, the table keeps the address of incoming flits in a FCFS orders.

#### 1.5.1 Problems in Static VC Organization

In the case of static buffering, the numbers of VCs and their buffers remain constant during communication. Various studies have shown that for a large number of static VCs, communication load is difficult to balance across them [1]. Some VCs remain idle while the others are overloaded. Therefore, it is better to allocate more buffer storage to busy VCs and less to the idle VCs. Moreover, static VC buffers are expensive components of routers and they become more expensive for larger flit size or when the VC buffer depth becomes larger. The above drawbacks of static VCs has resulted an adaptive VC organization to achieve VC flow control with maximum buffer utilization.

Now we discuss the conventional VC flow control in a router and a problem associated with buffer utilization. First of all, we define the term, buffer utilization, which is the rate of arrival/departure of flits in a slot buffer per clock cycle. For example, when a slot is empty, or it is full but with the same data per clock cycle, the buffer utilization rate is 0%. Figure 1.7b shows

the architecture of a conventional static VC-based router [13]. The input-port stores data in VC buffers in a FIFO fashion as illustrated in Figure 1.7c. The VC identification (*VC-ID*) of a flit is issued before the flit is transferred to the router. The *VC-ID* selects the VC where the incoming flit should be stored. Therefore, at the input of a router, the flit is stored at the tail of the selected VC buffer ("FIFO" sometimes refers to "FIFO buffer" or "buffer of a VC" in this dissertation). When the flit is reached at the head of the FIFO, a request signal is issued to the arbiter. After the arbitration (VC allocation and switch allocation that will be discussed latter), three signals are issued by the arbiter. First of all, *VC-ID* signal is sent out of the router to let the downstream router know about the VC address of the incoming flit. Secondly, the output address of the flit is issued to the crossbar module. Then, a grant signal is issued to the FIFO that leads the flit to reach the crossbar. The flit passes through the crossbar and exit out of the router.

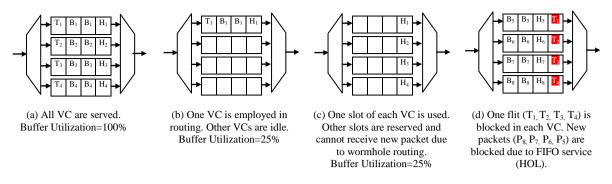

In the VC buffer, the flow of flits follows a wormhole mechanism. Once the flit of a packet occupies the buffer of a VC, no other packet can access it, even when the flit packet is blocked. This type of flow control is problematic in the context of buffer utilization. We illustrate buffer utilization problem through four different scenarios of data flow in a channel in Figure 1.8. In Figure 1.8a, all the VC slots are served and the buffer utilization is maximum i.e. 100%. In Figure 1.8b, one VC is employed in routing and the other VC's slots are idle and cannot participate in the flow result in lower buffer utilization i.e. 25%. In Figure 1.8c, when one slot of a VC is used by a packet, the other slots are reserved and not used by the new packets and will remain empty, which results in a buffer utilization of 25%. In Figure 1.8d, the tail flits (T1, T2, T3 and T<sub>4</sub>) are blocked in each VC. That will block any new packets such as P<sub>8</sub>, P<sub>7</sub>, P<sub>6</sub> and P<sub>5</sub>. This kind of blocking is called head-of-line (HoL) blocking [4]. No arrival/departure of flits results in a buffer utilization of 0%. It also leads to higher contention and lower performance. The effect of lower buffer utilization on power and area usage is obvious. The idle buffers are useless and only increase the hardware usage. In fact, one of objectives of our VC organization approaches presented in Chapter 3 and 4 is the adaptivity of channels. In adaptive channels, the idle buffers are dynamically used to create new VCs or to increase the buffer depths of active VCs. More VCs and higher VC buffer depth improve the performance and latency.

Figure 1.8: Four Different Scenarios in Conventional Wormhole VC Communication.

### 1.5.2 Head of Line Blocking

This section introduces the Head of Line (HoL) blocking. In wormhole routing, when a packet passes through a route, the route is reserved and no other packets can utilize that route. This kind of routing cannot avoid traffic congestion when a packet is blocked. In fact, blocking of a packet leads to the blocking of other packets in the channel causing HoL blocking (Figure 1.8d). The HoL blocking causes higher latency and lower throughput. HoL problem can be alleviated by using Virtual Channels [13]. However, the traditional VC approach does not remove HoL problem completely [13, 14, 15].

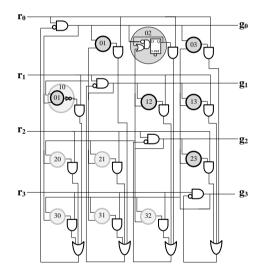

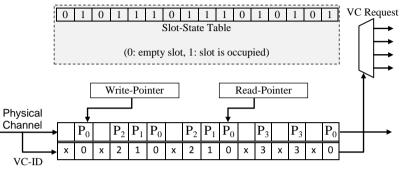

#### 1.5.3 DAMQ: Dynamically Allocated Multi Queues

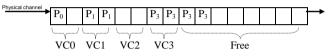

The traditional adaptive VC organization and its limitations are introduced in this section. Dynamically Allocated Multi Queues (DAMQ) is a single storage array that maintains multiple FCFS queues. In DAMQ, packet flits are stored in a central buffer consisting of multiple queues. The DAMQ buffers adapt to network traffic by dynamically allocating queue space amongst the output-ports depending on the traffic [4]. The dynamic queues of DAMQ buffers improves buffer utilization of port by sharing its buffer slots among all the VCs of port and allocating more buffer slots to active VCs. Higher VC buffer depth keeps more flits of a packet and leads to a free route of the packet in wormhole NoC communication. The more free routes lead to lower contention and eventually improve the overall NoC performance. Figure 1.9a illustrates a 4-VC DAMQ buffer where the addresses of flits kept in a linked list table. The linked list table records the flit addresses according to their *VC-ID* and in a FCFS orders.

Figure 1.9: Input-Ports with Dynamic and Static Queues

The micro-architecture of DAMQs can be used for organizing VCs in NoC systems. This technique can also resolve contention, deadlock, or fault tolerance related issues. Despite the performance merits of DAMQ organizations, they have a number of limitations as listed below.

- It has complex hardware due to linked list and dynamic queue management [4, 16].

- Another problem is related to the queue structure that is tailored for deterministic routing. It cannot look after fully adaptive routing since the routing decision for a new packet is made in conjunction with the output queues. With such flow control mechanism, the routing adaptivity cannot be established [4]. Packet flit buffers in NoC routers can be placed at three locations: input-ports, output-ports or both input and output ports [4]. The NoC routers with input-port buffers can easily support adaptive routing as flits resided in an input-port can be processed by following an adaptive methodology. In other words, the incoming flits remain in the input-port buffer until an adaptive routing is implemented (at least one clock cycle) and determines the outputs for the exit of flits. Routers with output-port buffering cannot

implement an adaptive routing mechanism. An incoming flit should be arbitrated as soon as a flit enters the router, and the flits that are buffered in the output-port can only pass through that output (no adaptive routing can implemented). In the initial versions of some DAMQ-based NoCs such as Link-list [14, 17, 18] and ViChaR [13], VC organization techniques had VC buffers at the output-ports. However, some newer versions of Link-list have introduced additional hardware in the form of recruit registers to achieve adaptive routing [4]. Other researchers have also added buffers at the input-ports to support adaptive routing [14].

- Configure limitation is the third problem with some DAMQ mechanisms. For example, three limitations such as limitation in the minimum buffer space of each VC, the number of VC, and the number of flits per packet has been employed in the specifications of some DAMQ schemes [13, 14, 19].

- The Head of Line (HoL) blocking is the forth problem in the communication of some DAMQ schemes. Assuming that a VC (queue) can receive more than a packet, and in case of the packet header blockage, the other packet in the VC has to wait until the blockage removed.

- There are interventions among the VCs of a DAMQ port that can lead to higher traffic congestion as compared to static VCs [20].

- A flit arrival/departure has a large delay due to complex design of DAMQ based VCs.

The initial two problems associated with DAMQ based VCs have also been reported by other researchers and solutions have been proposed [4, 15, 16, 20]. The third and forth problems exist in some DAMQ mechanisms and will be discussed in detail along with our optimal solution in Chapter 4. The last two problems are being introduced in this section. Interventions among VCs exist in all the DAMQ-based mechanisms. As already mentioned, a single storage array maintains multiple VCs of a DAMQ port. Therefore, the communication behavior of a VC directly affects the other VCs. For instance, a blocked VC can occupy the maximum free space of its port buffer, and only a few buffer locations are available to unblocked VCs that lead to higher traffic congestion. We discuss in detail the 5th problem along with our optimal solution in Chapter 4. The longer flit arrival/departure delays mentioned as the last problem exist in table-based DAMQ mechanisms such as Linked list [14, 18] and ViChaR [13] where a central

table, containing the registers, is employed for direct data flow. Registers are updated at a clock edge due to which the table-based DAMQ mechanisms take one additional clock cycle than the static VC-based NoC communication [1]. We further discuss this problem through the pipeline stage analyses of two types of port buffers in the following section.

### 1.5.4 Timing Problem of Adaptive Table-based VC Organization

In this section, we discuss the drawback of table based organizations as compared to static VC organizations. Figure 1.9 shows the architectures of static and dynamic input-ports. The control logic of the static input-port is simpler and each VC can be configured by using a parallel FIFO buffer [20] as illustrated in Figure 1.9b. Each FIFO represents a VC and therefore the number of VCs is equal to the number of FIFOs. The *Read-pointer* and the *Write-pointer* point to the location of FIFO where a flit (data) is read or written respectively. A *pointer* works like a simple counter, which is incremented circularly and continuously for each read and write operation.

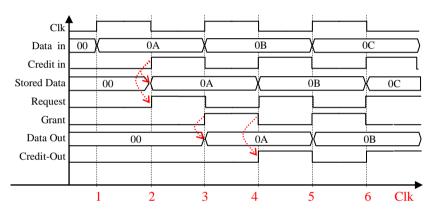

The flit arrival/departure is also simpler in static input-port. If arbitration takes one step, the arrival/departure of flits in a squeezed pipelined scheme consumes two clock edges as illustrated in Figure 1.10a. At the entrance of an input-port, an arriving flit is decoded according to its VC identification (*VC-ID*) and by means of de-multiplexer, then it waits to be latched in the FIFO buffer (VC) before the first clock edge. At the first clock edge, the flit is stored in the VC where a request corresponding to that flit is simultaneously issued to the arbiter. At the 2<sup>nd</sup> clock edge, the arbiter allocates the proper address for the crossbar switch (output) and ID for the downstream router VC then issues a *grant* signal. The *grant* signal causes the flit to exit the router. For proper operation of the decoder at the entrance of the input-port, the *VC-ID* should be issued earlier than the latching of the flit in the buffer. Assuming that the flit and its *VC-ID* are transferred at the same clock transition, each flit arrival/departure takes a two-clock event delay in the static VC router. We have assumed that the FIFOs are dual-port, where the arrival of a flit can coincide with the departure of another flit.

Figure 1.10: Staic vs. Dynamic Input-Port Pipelines

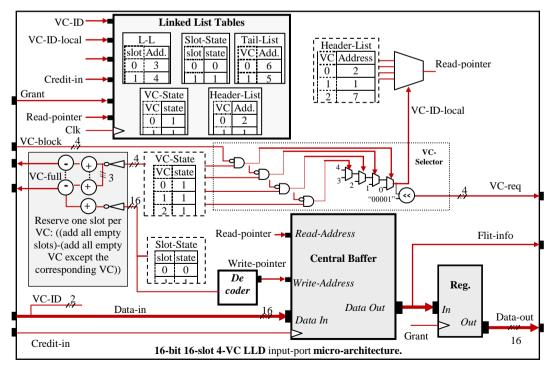

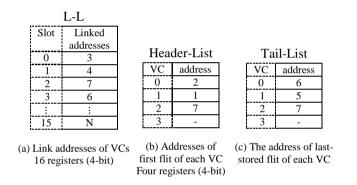

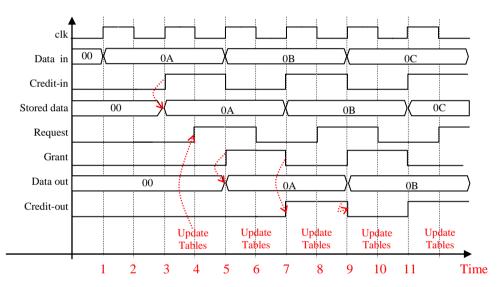

In the case of dynamic VC input-ports, the VC buffers are allocated dynamically based on the traffic resulting in more complex control logic. Linked-List based DAMO has been employed as a conventional DAMQ in many research projects [14, 17, 20, 21]. Using this mechanism, a single buffer (queue) maintains multiple VCs, and the data flow is directed by Linked-List tables as illustrated in Figure 1.9a [14]. The Read-pointer and Write-pointer are updated based on the contents of the linked list tables. In a squeezed pipelined design, when arbitration takes one step, the arrival/departure of flits will take four clock edges as illustrated in Figure 1.10b. A head flit arrives at the input-port and waits to be latched in the VC (buffer). Then the flit is latched into the input-port buffer at the first clock edge. In the 2<sup>nd</sup> clock edge, the Linked-List tables are updated according to the VC-ID, which leads to a request signal being issued to the arbiter. In the 3<sup>rd</sup> clock edge, the arbiter assigns a proper address for the crossbar switch (output) and ID for the VC before issuing a grant signal. The grant signal causes the flit to exit the router, as well as the linked list tables are updated at the 4<sup>rd</sup> clock edge. In a Linked-List DAMQ based VC organization, the read and write pointers cannot be updated at read or write events. Instead, they will be updated one clock event after the read and write (i.e. after updating the tables). However, in the static VC queue, the read and write pointers can be incremented at the read or write events. This causes the pipeline stages in DAMO table-based input-ports to be one clock cycle longer than those of static input-ports. The same communication characteristics are expected for other table-based DAMQ mechanisms e.g. ViChaR [13]. The ViChaR has a central table that contains registers to direct the data flow. Registers are updated at one clock edge that results in the usage of one additional clock cycle. However, the VC organization approach presented in Chapter 4 does not employ tables. Moreover, its flit arrival/departure delay is equal to that of static VCs but with all the advantages of dynamic VCs.

### **1.6 Data Flow Arbitration**

In this section, we introduce the data flow arbitration that is the process after buffering. It also introduces a state of art arbiter in Chapter 5. After buffering a flit in a VC of an input-port, VC issues a request to the arbiter for accessing shared resources. The structure of arbiter becomes more complex when an NoC utilizes VC mechanism in its data path (extra hardware for VC and switch allocators). The arbiter can perform arbitration and allocation in four pipelined stages as follows. First, the route must be computed to determine the output-port (or ports) to which the packet can be forwarded. Then, a downstream router VC (VC in router's input-port) should be allocated. When the flit's buffer space is booked in the downstream router, the flit can begin to compete for access to the crossbar switch. Once a route has been determined and a downstream router VC allocated and the crossbar switch configured, the flit is forwarded over this VC to the downstream router on the route. For explaining, consider the case illustrated in Figure 1.11 where the HF flit (header flit of a packet) is in VC1 of input-port 5 of router 3.

Figure 1.11: HF Flit in VC1 of Input-port 5 of Router 3 Traveling to Input-port 2 of Router 6.

To advance the flit, HF to router 6, a space in a buffer in the input-port 1 of router 6 must be allocated, and HF must win the allocation to traverse the crossbar switch. To begin advancing the HF, the route computation is first performed to determine the output-port to which HF can

be forwarded. Based on XY routing (see Section 1.2) the output-port 4 is assigned. Then, HF requests a VC from the VC allocator (assume VC2 of input-port 1 of router 6). When the buffer space of HF is reserved in router 6 along the output to the downstream router, the flit can compete to access the crossbar switch by means of switch allocator. Once the output-port has been determined, a VC is allocated, and the crossbar switch is configured, the HF flit can travel from output-port 4 to the VC2 of input-port 1 of router 6. We explain the above stages and their timing processes in the following section.

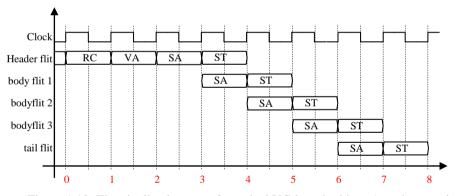

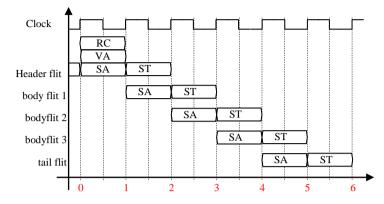

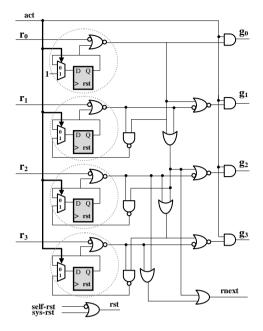

#### **1.6.1** Arbiter Pipeline Stages

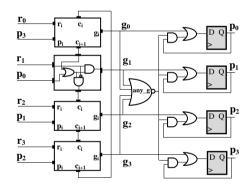

The pipelined stages of a typical VC-based arbiter are illustrated in the timing diagram of Figure 1.12. Each flit of a packet must go through the stages of Routing Computation (RC), Virtual channel Allocation (VA), Switch Allocation (SA), and Switch Traversal (ST) [2]. The RC and VA stages perform computation only for the header flit (once per packet). Body and tail flits pass through these stages without RC and VA computation. In fact, the SA and ST stages operate on every flit of a packet, and only the header flit passes through all the stages.

Figure 1.12: The pipelined stages of a typical VC-based arbiter. A packet consists of 5 flits takes 8 cycles to be arbitrated in case of no stall in the communication.

In our design, the first three stages i.e. RC, VA and SA proceed in parallel and in one clock cycle as illustrated in Figure 1.13. However, in other designs, each stage may take one or more than a cycle. As one can notice in Figures 1.12 and 1.13, ST stage is the last stage and it needs a separated clock cycle. It can work concurrently with the first stage of the following flit [22]. We will discuss the advantage of our pipeline mechanism later. The arbitration process begins when the header flit of a packet leads a request to be issued to the arbiter, assume at cycle event 0 of Figure 1.12. During the following four cycles, the request of flit remains activated that leads all the four stages to proceed. The header flit information is used by the RC stage to select the

requested output-port at the clock event 1. The result of RC stage along with the states of downstream router VCs are used as inputs of VA stage to pick a free downstream router VC for the packet at the clock event 2.

Figure 1.13: The pipelined stages of a typical virtual channel arbiter. A packet consists of 5 flits takes 6 cycles to be arbitrated in case of no stall in the communication.

The information provided by RC stage along with the information of requested downstream router VC are used by SA stage to determine the winner inputs VCs at the clock event 3. At the clock event 3, two tasks such as the issuance of *grant* signal and crossbar address are performed to prepare the route, where the flit passes at the following clock cycle. Therefore, the request of next flit after the header flit can be processed during the fourth cycle. The flit travels to a downstream destination by means of proper handshaking signals during the 4<sup>th</sup> cycle (we assume a credit-based flow control). At the end of RC and VA stages, the information generated by RC and VA stages are saved in a register table and will be used for the following (body and tail) flits of the packet. For example, the result of VA stage is recorded to be issued as a new VC-ID for packet flits. When a body or tail flit makes the request, the recorded RC and VA information are used by the SA stage, and these two stages are bypassed as illustrated in Figure 1.12. From this point until the release of the channel by the tail flit, the recorded RC and VA information remains unchanged. Therefore, the four stages proceed through two distinct frequencies: packet rate and flit rate. RC and VA stages are performed once per packet. On the other hand, SA and ST stages are performed per flit basis.

### **1.7 Motivation**

The motivations for the research conducted and presented in this thesis are listed as follows.

- Network-on-Chip architectures are viewed as a possible solution to meet the wiring challenges of MPSoC systems

- NoC design that consumes minimal power, IC area but with higher performance is a necessity for SoC design especially for low power high performance applications.

- Current NoC router and NoC system designs are not optimal.

- The main problem with the current NoC design is related to lower performance under high contention due to traffic congestion.

- Router is the key component of NoC, and if one improves its design, it will improve the overall NoC performance.

- Both NoC performance and energy budget depend heavily on the routers' buffer resources. One must use the buffer cleverly and intelligently for NoCs e.g. employ Adaptive VCs.

- Adaptive VCs also have maximum buffer utilization of the router.

- Current DAMQ buffer design suffers a number of problems such as complexity, lower buffer utilization, setup limitation, and HoL blocking.

- Arbitration is the other important activity in NoC routers. It can have some problems such as complexity, lower speed, weak fairness, traffic starvation, and pipelined difficulty.

- The above drawbacks and points related to current NoCs have motivated us to investigate the high performance components of NoC router including input-port and arbiter.

### **1.8 Objectives**

NoC architectures have been commonly presented in Globally Asynchronous Locally Asynchronous (GALS) design style [23], and in this thesis we have also followed the GALS style for our NoC router design. In NoC GALS architectures, the routers are locally synchronous, but the NoC architectures are globally asynchronous, i.e. there can be different clock rates for routers. In other words, the routers are independent in terms of clock design, and the faster clock rates of routers leads to faster NoC. The main objectives of the research presented in this dissertation are to design, present and evaluate an efficient NoC wormhole router. The packet-based wormhole routing has been introduced as a viable communication

mechanism being employed in NoCs. The conventional wormhole routing flow is prone to contentions and in some cases deadlocks. One of the traditional ways to alleviate contention and to remove deadlock is to the introduction of VC organization. A traditional form of VC organizations has been of static type. The numbers of VCs stay constant during communication for static VCs. The static VC organization is also expensive in terms of higher number of buffer cells and suffers from lower buffer utilization. To solve the problem related to static VC organization, a commonly used dynamic VC organization namely DAMQ has been introduced. Despite the performance merits of DAMQ organizations, they have a number of limitations such as complexity, lower buffer utilization, lower frequency, longer pipelined stage, configure limitation and HoL problem. The limitations of static and dynamic VC organizations techniques.

The arbitration is another important module requiring new and novel architecture for efficient NoC router design. The arbitration organization is implemented in the arbiter module of router that can have four pipelined stages: Rout Computation (RC), Virtual channel Allocation (VA), Switch Allocation (SA), and Switch Traversal (ST). The arbitration and allocation functions are performed inside the VC and switch allocators of arbiter module. The conventional NoC arbitrations suffer from some drawbacks such as complexity, lower speed, weak fairness, traffic starvation, and pipelining problems. The limitations of conventional arbiter organizations have encouraged us to investigate design and present an efficient and fast arbiter.

Finally, by employing novel VC buffering and arbitration organizations, our main objective is to improve the performance and hardware metrics of routers and NoC systems. The experimental results support the theoretical concepts of our proposed VC organization and arbitration approaches for efficient NoC system.

### **1.9** Thesis Organization

- Chapter 2 reviews some important past research works related to DAMQ based VC organizations and round-robin arbiter architectures.

- Chapter 3 presents and evaluates our adaptive and efficient VC organization based on Statically Adaptive Multi FIFO (SAMF). The SAMF VC buffers are static during a specific time of communication but subsequently adapted to the traffic demand.

- Chapter 4 describes our Efficient Dynamic Virtual Channel (EDVC) organization and its novel features. The EDVC mechanism utilizes the common features of DAMQ inputport to create a dynamic flow control.

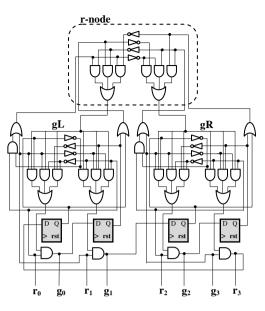

- Chapter 5 provides a detailed presentation and evaluation of our novel and efficient router architecture. The router utilizes two new components including an RDQ input-port and IRR (Index-Based Round Robin) arbiter.

- Chapter 6 will discuss the thesis conclusions and our future works.

## Chapter 2

## **Previous Research Work**

Three types of NoC research is reviewed and investigated in this chapter. First we discuss some approaches related to adaptive buffer organization. Specifically, two major components associated with the conventional buffer organization i.e. FIFO and DAMQ buffers are described in detail in Sections 2.2 and 2.3 in an effort to highlight their problems. Our implementation of a well-known DAMQ architecture i.e. Link-List is presented in detail in Section 2.4. Some researches that focus on the design and organization of NoC routers are investigated in Section 2.6. Then various micro-architectures of a Round Robin arbiter used in the NoC router is presented and discussed in Section 2.7.

### 2.1 Buffer Organization

FIFO or Queue is frequently utilized for buffer organization in NoC routers. They temporarily stores messages in the form of first come first serve (FCFS) order until network resources become available. Commonly used terms, "queue" and "FIFO" sometimes have the same meaning when the concept of first in first out is considered. However, in terms of

architecture, first-in-first-out queue is mostly referred to serial or parallel FIFOs, and the queue is referred to all the buffers with FCFS concept that comprises FIFO buffers too.

In industrial and academic research, many queue architectures have been proposed and the FIFO, Circular Queue (CQ), dynamically allocated multi-queue (DAMQ) and their variants are well-known queue designs [4, 15, 17, 18, 24, 25]. In the following section, the FIFO and CQ organizations are discussed in detail under the name of serial and parallel FIFO [4].

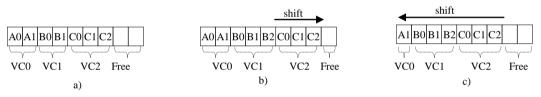

## 2.2 Serial and Parallel FIFO Architecture

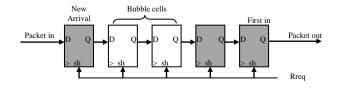

There are two types of FIFO designs and architectures: serial and parallel [4, 7, 13, 26, 27, 28, 29]. The serial FIFO (such as shift register) that works by fall-through principle has been the first FIFO generation as shown in Figure 2.1. However, the architecture of conventional FIFOs is constantly being improved. Currently, most of the FIFOs are parallel, which is an appropriate mechanism to increase the number of stored words along with faster speed [7]. This trend is suitable for network on chip due to two main reasons. The first reason is related to the fallthrough concept where the newly arrived data unit is store at the tail (cell) of the FIFO, and at each shift request it is shifted one step toward the head of the FIFO queue. In this way, the data units are shifted through all the storage location at each request. This concept has three drawbacks of long fall-through delay, bubble cells and high dynamic power consumption. The first drawback is due the fact that when the FIFO's capacity is increased, its fall-through time will increase leading to higher FIFI latency [7]. In fact, the minimum latency of a FIFO depends on the depth of physical FIFO rather than the number of stored items. The second drawback of bubble cells in the FIFO is illustrated in Figure 2.1. The bubble cells can occur when the data input/output rates are different. The third drawback is the dynamic power consumption due to data shifts from tail to the head of FIFO. Serial FIFO is simpler, but it is unsuitable for on-chip implementation [26]. The FIFO architecture should not shift the data items through all the memory locations. In other words, the arrival packet should be stored at the front of empty cell rather than at the tail of a queue.

Figure 2.1: Conventional Shift Register (serial) FIFO.

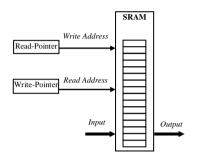

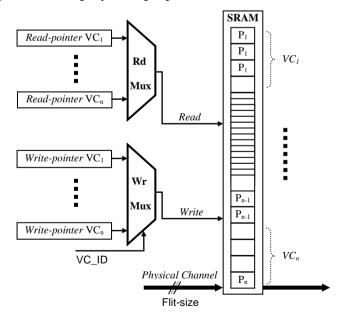

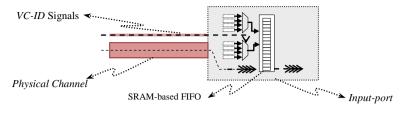

To solve these drawbacks of deep FIFOs, a parallel FIFO mechanism that relies on read and write pointers has been introduced [13]. We have already discussed this mechanism and the architecture of parallel register-based FIFO in Chapter 1, which is illustrated in Figure 1.6. The same style is also used in SRAM-based FIFOs as shown in Figure 2.2. The write and read address ports of the SRAM are the selection ports of de-multiplexer and multiplexer while the *Read-pointer* and *Write-pointer* work as counters.

Figure 2.2: SRAM-Based FIFO Using Parallel Style.

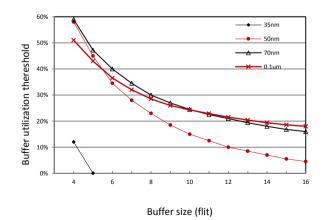

The register-based buffers are usually more expensive in terms of power because they use more transistors than SRAM-based buffers [27]. However, register-based operations (read, write, shift) only involve the occupied cells, while SRAM operations (read, write) involve all the cells due to global bitline and wordline wiring. Therefore, register-based buffer may consume less energy than SRAM based buffers when the buffer utilization is below a certain threshold and higher energy when the buffer utilization is above the threshold [27]. Figure 2.3 shows the threshold utilization of different register-based buffers with different sizes and technologies.

Figure 2.3: Buffer Threshold Utilization vs. Buffer Size.

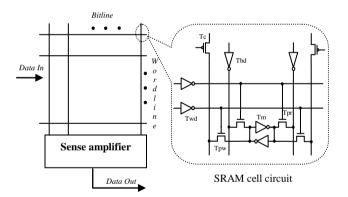

The register-based implementation is still viable at  $0.1\mu$ m technology with relatively smaller buffer size and lower buffer utilization, but it is not a good choice for 35nm technology. This is mainly due to increasing static power for 35nm or lower technologies, where the advantage of fewer activities is completely diminished by the disadvantage of more transistors [27]. As the buffer capacity increases to dozens of flits, the register-based implementation becomes inefficient due to larger chip area occupied by the buffer [26]. The schematics of a dual-port SRAM cell and a D-type flip-flop that are used for large-capacity FIFOs are shown in Figures 2.4 and 2.5 respectively. Assuming that a NOT gate and a NAND gate need two and four transistors in their structures respectively [30]. A SRAM cell occupies only a third of the D-type flip-flop register area. Now-a-days, NoC buffers are mainly implemented by SRAM due to the area and power cost and the availability of the corresponding Intellectual Property (IP) cores [24]. The above facts have encouraged us to use SRAM-based buffer and parallel style mechanism in all the proposed designs presented in this dissertation.

Figure 2.4: SRAM-based FIFO.

Figure 2.5: A Positive-Edge-Triggered D-FF.

## 2.3 DAMQ Buffer Organization Research Work

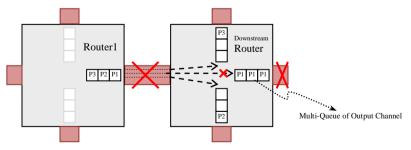

DAMQ that is a unified and dynamically-allocated buffer structure was originally presented by Frazier and Tamir [18]. It is a single storage array that maintains multiple FIFO queues. The DAMQ mechanism dynamically allocates multiple queues on a physical channel. In other words, the DAMO buffers are able to efficiently adapt to network traffic by dynamically allocating queue space among the output-ports according to the network traffic [4]. These dynamic queues of DAMQ buffers lead to maximize buffer utilization. The DAMQ organization can be used in the VC organization of NoC. This technique is able to solve or alleviate the other NoC issues such as contention, deadlock, HoL blocking or fault tolerance. Jamali and Khademzadeh [15] has used DAMQ buffer scheme for fault tolerance in NoC systems. There are some drawbacks related to initial DAMO scheme presented by Frazier and Tamir [18]. We discuss these drawbacks in the following section. The first drawback of scheme is that the packets are stored into the queues of a multi-queue of the output channel for routing. Therefore, in the case of blockage of the output channel, the packets destined to that output-port become blocked. According to Choi and Pinkston, this type of blocking is not HOL [4], but we argue that it is HOL blocking as explained earlier in Section 1.4.5. In fact, packets in an output channel have different destinations, and they travel to different output channels in the downstream router. Therefore, if the head of line of these packets is blocked due to the blocking of its route in the next downstream router, the remaining packets will be blocked even though their routes are open in the next downstream router. Figure 2.6 illustrates a HOL blocking case where eastward output channel of router1 is blocked due to the blocking of P1. The packets P2 and P3 are blocked despite the fact that their routes are open in the downstream router.

Figure 2.6: Head of Line Blocking in DAMQ Output Channel.

The second problem of scheme is again related to the location of queues in output channel. In fact, the queue structure is tailored more for deterministic routing algorithms than for fully

adaptive routing algorithms. In the scheme, a routing decision for a new packet is made in order to assign the packet to one of the output queues. This forces the packet to be routed only through that output. In such a flow control, the routing adaptivity cannot be established [4]. The third problem of initial DAMQ approach is that there is no reserved space dedicated for each output channel [18]. The packets destined to one specific output-port may occupy the whole buffer space. Therefore, the new packets destined to this output-port have no chance to get into the buffer [15]. The fourth problem is related to its hardware complexity caused by the linked-lists and dynamic queue management utilized in the scheme [4]. Despite the performance merits of Link-List mechanism utilized in this scheme, it suffers from a few complications and limitations that we will discuss in detail in Section 2.4. In fact, one of the objectives of our approach presented in Chapter 4 is to implement a DAMQ buffer without Link-List mechanism.

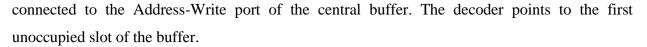

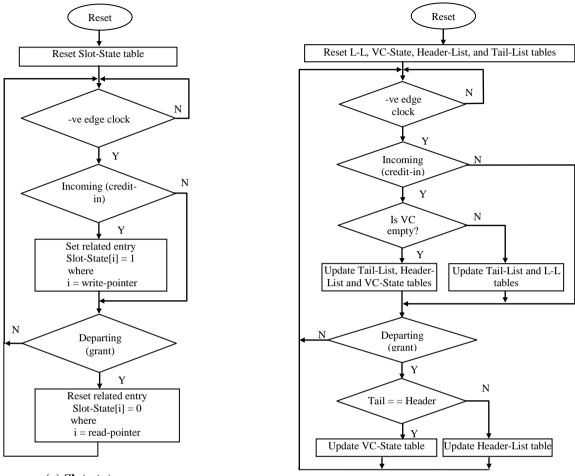

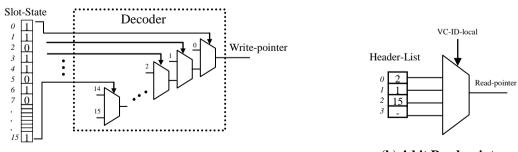

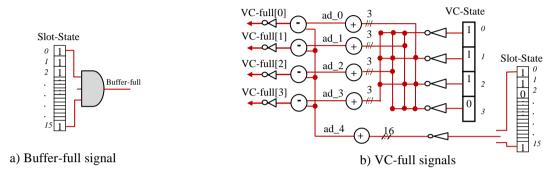

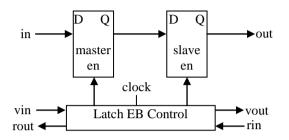

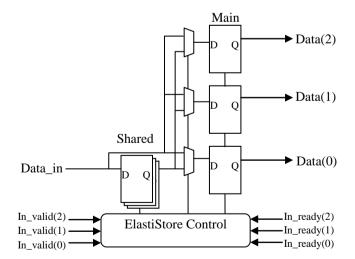

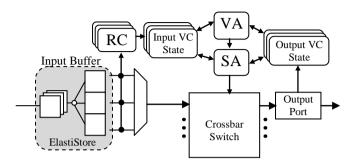

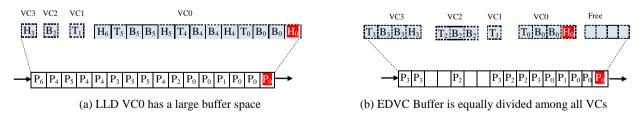

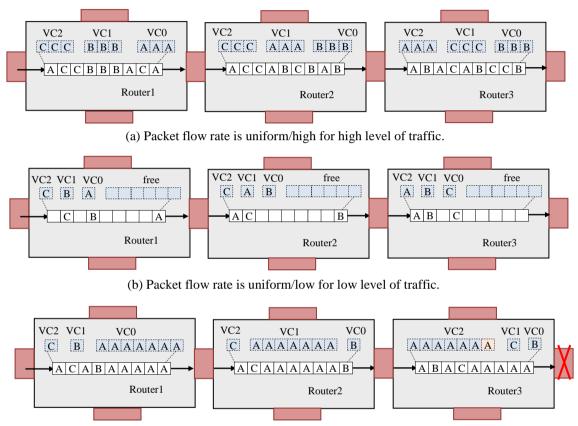

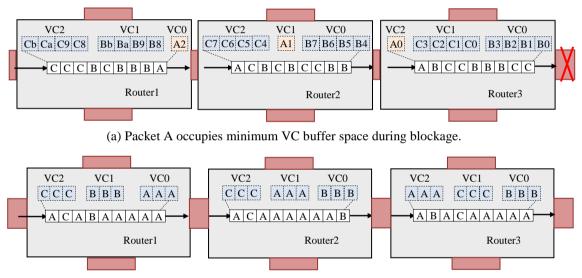

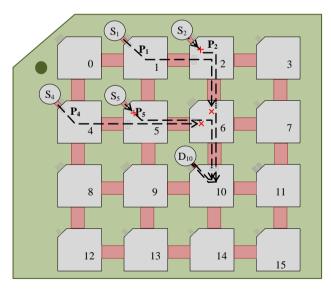

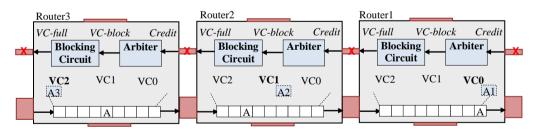

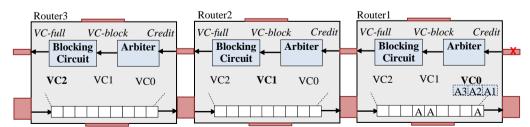

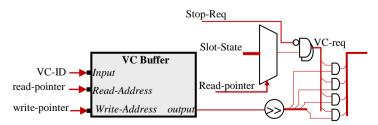

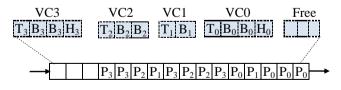

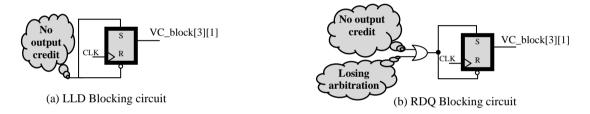

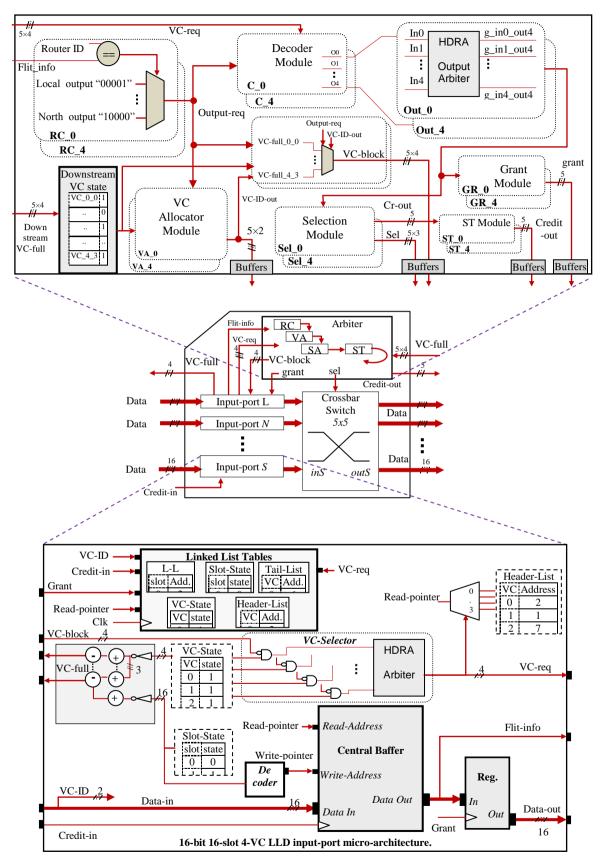

Different buffer architectures are proposed to overcome various limitations of DAMQ used in NoCs. Dynamically allocated multi-queue with recruit registers (DAMQWR) and virtual channel dynamically allocated multi-queue (VCDAMQ) are proposed in an effort to overcome some of the drawbacks of DAMQ [4]. DAMQWR uses DAMQ architecture with some recruit registers to implement adaptive routing for on-chip communication. The main recruit registers assign the packets of blocked sub queues to less congested sub queues. However, in addition to hardware overhead, DAMQWR method has additional delays due to recruit register updates and packet recruit operations. The queue organization that resembles DAMQ in the VCDAMQ method can efficiently adapt to an unbalanced traffic load amongst the VCs by dynamically allocating queue space to virtual channels. In fact, the difference between the VCDAMQ and the traditional DAMQ lies in the fact that the sub queues of VCDAMQ are associated with router VCs while those of the DAMQ are associated with the router output-ports.