# A Delta Diagram Synthesis for Iot Optimization with Grey Wolf Driven Multi-Objective Automation

by

Prathap Siddavaatam

Master of Science, Brock University, 2011

Bachelor of Engineering, Bangalore University, 2001

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2018

©Prathap Siddavaatam, 2018

# AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

## A Delta Diagram Synthesis for IoT Optimization with Grey Wolf Driven Multi-Objective Automation Doctor of Philosophy, 2018 Prathap Siddavaatam Electrical and Computer Engineering Ryerson University

#### Abstract

Today, Internet of Things (IoT) is a major paradigm shift that will mark an epoch in communication technology such that every physical object can be connected to the Internet. With the advent of 5G communications, IoT is in urgent need of optimized architectures that can efficiently support wide ranging heterogeneous multi-objective requirements of communication, hardware and security aspects. The optimization challenges are rooted in the technology and how the information is acquired and manipulated by this technology. My research in this thesis provides a description of compelling challenges faced by IoT and how to mitigate these challenges by designing resource-aware communication protocols, resourceconstrained device hardware with low computing power and low-powered computational security enhancements. This thesis lays the foundation for optimizing these challenging IoT paradigms by introducing a novel Delta-Diagram based synthesizing model. The Delta-Diagram provides a road-map linking the behavioral and structural domains of a given IoT paradigm to generate respective optimizer domain parameters, which can be utilized by any optimizer framework. The fundamental part of the communication synthesizer is a mathematical model, developed to obtain the best possible routing paths and communication parameters among things. The ultimate aim of the entire synthesis process is to devise a design automation tool for IoT, which exploits the interrelations between different layer functionalities. This thesis also proposes a novel cross–layer Grey wolf optimizer for IoT, which outperforms some of the contemporary optimizer algorithms such as Particle Swarm, Genetic Algorithm, Differential Evolution optimizers in solving unimodal, multi–modal and composition benchmark problems. The purpose of this optimizer is to accurately capture both the high heterogeneity of the IoT and the impact of the Internet as part of delta diagram synthesis enabled network architecture. In addition, the Grey wolf optimizer for IoT plays a crucial role in design exploration of system on chip architecture for IoT device hardware. The results generated by the optimizer yielded the most optimum feasible solutions in the design space exploration process of the IoT.

#### Acknowledgements

I would like to express my sincere gratitude to my supervisor Professor Reza Sedaghat for the continuous support of my Ph.D study and related research, for his patience, motivation, and immense knowledge. His guidance helped me throughout the time of research and writing of this dissertation.

My special thanks goes to members of my dissertation examination committee for their valuable feedback.

I owe my deepest gratitude towards my wife Richa for her eternal support and understanding of my goals and aspirations. Her infallible love and support has always been my strength. Her patience and sacrifice will remain my inspiration throughout my life. Without her help, I would not have been able to complete much of what I have done and become who I am. Also, I am thankful to my son Aarav and daughter Reeva for giving me happiness during the course of my studies and being supportive. Without their emotional support in my life, I would have never been able to dedicate the time and effort for pursuing this research and achieving the requisite goals. I would like to thank my mother Meena for her everlasting support and constant encouragement.

Lastly, and most importantly, I wish to thank my late grandmother Jayalakshmamma. She raised me, supported me, taught me about life and loved me. Her words of inspiration and encouragement still lingers in me today. I dedicate this Ph.D dissertation to her.

# Contents

|          | Decl | laration                                  | ii  |

|----------|------|-------------------------------------------|-----|

|          | Abst | ract                                      | iii |

|          | Acki | nowledgements                             | v   |

|          | List | of Tables                                 | xi  |

|          | List | of Figures                                | xii |

| 1        | INT  | RODUCTION                                 | 1   |

|          | 1.1  | ΙοΤ                                       | 2   |

|          | 1.2  | Interconnection Challenge among Devices   | 3   |

|          |      | 1.2.1 Interference: Internal and External | 3   |

|          |      | 1.2.2 Environmental Obstacles             | 3   |

|          |      | 1.2.3 Deployment Environments             | 4   |

|          |      | 1.2.4 Hardware and Software Configuration | 4   |

|          | 1.3  | Motivation                                | 5   |

|          | 1.4  | Research Objectives and Goals             | 7   |

|          | 1.5  | Contributions                             | 9   |

|          | 1.6  | Thesis Organization                       | 10  |

| <b>2</b> | RE   | VIEW: MULTI-OBJECTIVE OPTIMIZATIONS       | 13  |

|          | 2.1  | Strategies for IoT Optimization           | 13  |

|          | 2.2  | Multi–Objective Optimization              | 15  |

|   | 2.3 | Parto-Optimality                                              | 16 |

|---|-----|---------------------------------------------------------------|----|

|   | 2.4 | MOA application for IoT                                       | 18 |

|   |     | 2.4.1 Scalarization Methods                                   | 18 |

|   |     | 2.4.2 Knapsack Problem                                        | 20 |

|   | 2.5 | Genetic Algorithms                                            | 21 |

|   | 2.6 | Swarm Intelligence Algorithms                                 | 21 |

|   |     | 2.6.1 Particle Swarm Optimization                             | 22 |

|   |     | 2.6.2 Grey Wolf Optimizer (GWO)                               | 24 |

|   |     | 2.6.3 Advantages of GWO                                       | 30 |

| 3 | IoT | Network Architecture Cross-layer Optimization                 | 32 |

|   | 3.1 | Problem Statement                                             | 33 |

|   | 3.2 | Contribution                                                  | 36 |

|   | 3.3 | IoT Standards                                                 | 39 |

|   | 3.4 | Network Architecture                                          | 41 |

|   | 3.5 | Cross-layer Optimization                                      | 43 |

|   | 3.6 | Physical Layer Traits                                         | 46 |

|   |     | 3.6.1 Channel model and frequency allocation                  | 46 |

|   |     | 3.6.2 Power, Modulation and BE for Transmission               | 48 |

|   |     | 3.6.3 Probability of Packet Drop-out and Data Buffer Capacity | 49 |

|   | 3.7 | Data Link Layer Synthesis                                     | 49 |

|   |     | 3.7.1 Packet Error Rate and Error Control                     | 50 |

|   |     | 3.7.2 Medium Access Control                                   | 52 |

|   | 3.8 | Network Layer Synthesis                                       | 53 |

|   |     | 3.8.1 Addressing of things and Routing                        | 54 |

|   |     | 3.8.2 Packet Size Impact                                      | 55 |

|   | 3.9 | GWO Cross-layer Optimizer framework                           | 57 |

|   |     | 3.9.1 Background on Grey Wolf Optimizer                       | 57 |

|   |     |                                                               |    |

|   |      | 3.9.2   | Algorithm Set-up                                                  | 57  |

|---|------|---------|-------------------------------------------------------------------|-----|

|   | 3.10 | Real-t  | ime Protocol Testing                                              | 60  |

|   | 3.11 | Conclu  | usion                                                             | 65  |

| 4 | HLS  | 6 for R | Resource Constrained IoT Hardware                                 | 67  |

|   | 4.1  | Backg   | round                                                             | 68  |

|   | 4.2  | Relate  | ed Work                                                           | 70  |

|   | 4.3  | Hypot   | heses and Problem Definition                                      | 70  |

|   |      | 4.3.1   | Execution Time Analysis                                           | 71  |

|   |      | 4.3.2   | Power Consumption Analysis                                        | 76  |

|   |      | 4.3.3   | Area Analysis                                                     | 79  |

|   | 4.4  | Deploy  | yment of GWO-DSE framework for IoT Synthesis                      | 82  |

|   |      | 4.4.1   | Initialization of GWO-DSE                                         | 82  |

|   |      | 4.4.2   | Fitness function Calculation                                      | 82  |

|   | 4.5  | Desigr  | n Flow Analysis                                                   | 84  |

|   |      | 4.5.1   | Resource Libraries and Operational Constraints                    | 86  |

|   |      | 4.5.2   | Architecture Design Space development for Power Consumption       | 88  |

|   |      | 4.5.3   | Architecture Design Space development for Execution Time          | 91  |

|   |      | 4.5.4   | Architecture Design Space development for Area Calculation        | 94  |

|   | 4.6  | Result  | s and analysis                                                    | 98  |

|   |      | 4.6.1   | Preprocessing for Data-path and Control Unit                      | 98  |

|   |      | 4.6.2   | Comparative analysis with Contemporary Heuristic approach and ABF |     |

|   |      |         | method                                                            | 100 |

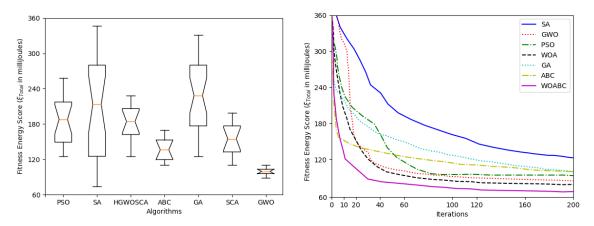

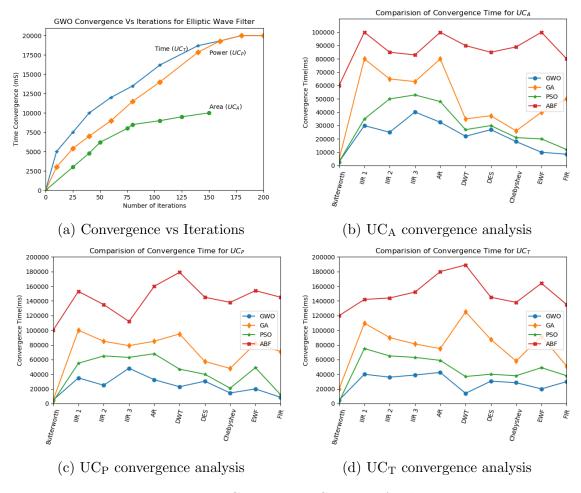

|   |      | 4.6.3   | Convergence Analysis                                              | 104 |

|   | 4.7  | Conclu  | usion                                                             | 109 |

| 5 | Secu | urity E | Enhancement in IoT device                                         | 110 |

|   | 5.1  | Backg   | round                                                             | 111 |

|   | 5.2 | An Ad  | laptive Security Architecture for Lightweight IoT Ciphers 11 | 2 |

|---|-----|--------|--------------------------------------------------------------|---|

|   |     | 5.2.1  | Algebraic Cryptanalysis                                      | 2 |

|   |     | 5.2.2  | Algebraic Attack on IoT based Ciphers                        | 2 |

|   |     | 5.2.3  | Modular Addition                                             | 3 |

|   |     | 5.2.4  | Security Enhancement for Ciphers in IoT                      | 4 |

|   | 5.3 | Modul  | ar Addition Preliminaries                                    | 5 |

|   | 5.4 | The N  | ew Adaptive Lightweight Framework for IoT                    | 7 |

|   | 5.5 | Design | Analysis for New Modular Addition Framework                  | 3 |

|   |     | 5.5.1  | The Characteristics of the New Design Framework              | 3 |

|   |     | 5.5.2  | Carry Absence in Modular Addition                            | 4 |

|   |     | 5.5.3  | Carry Probability                                            | 4 |

|   |     | 5.5.4  | The Complexity Analysis for the New Model                    | 5 |

|   |     | 5.5.5  | Overall Algebraic degree of New Design Framework             | 7 |

|   |     | 5.5.6  | A Corner Case Analysis for the New Design Framework          | 8 |

|   | 5.6 | Case S | Study                                                        | 2 |

|   |     | 5.6.1  | New SNOW 2.0                                                 | 2 |

|   |     | 5.6.2  | Analysis of New SNOW 2.0                                     | 4 |

|   | 5.7 | Conclu | 1sion                                                        | 6 |

| 6 | Con |        | n and Contributions 13                                       | 7 |

| 0 |     |        |                                                              |   |

|   | 6.1 |        | v                                                            |   |

|   | 6.2 |        | butions                                                      | 8 |

|   |     | 6.2.1  | Security enhancement methods for IoT                         | 8 |

|   |     | 6.2.2  | Framework for Rapid DSE of IoT device                        | 9 |

|   |     | 6.2.3  | Grey Wolf Optimizer                                          | 9 |

|   |     | 6.2.4  | Automated Communication Synthesizer                          | 9 |

|   | 6.3 | Future | e Work                                                       | 0 |

Bibliography

## Glossary

159

142

# List of Tables

| 1.1 | Organization Rubric relating Chapters to Research Goals of this Thesis                                                    | 11  |

|-----|---------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | An instance of GWO-DSE framework in action for power analysis. Note.                                                      |     |

|     | Units for Latency is in c.c., $T_{exe}$ is in ms and area in a.u. respectively                                            | 92  |

| 4.2 | An instance of GWO-DSE framework in action for execution time analysis.                                                   |     |

|     | Note. Units for Latency is in c.c., $\mathrm{T}_{\mathrm{exe}}$ is in ms and area in a.u. respectively.                   | 94  |

| 4.3 | An instance of GWO-DSE framework in action for area analysis. Note. Units                                                 |     |

|     | for Latency is in c.c., $T_{exe}$ is in ms and area in a.u. respectively                                                  | 98  |

| 4.4 | Critical Analysis benchmarking ABF vs $\underline{\text{GWO-DSE}}$ framework                                              | 108 |

| 4.5 | Performance highlights of $\underline{\text{GWO-DSE}}$ framework vs $\text{ABF}[1]$ and $\underline{\text{State of the}}$ |     |

|     | $\underline{\operatorname{art}}$ Heuristic method                                                                         | 108 |

| 5.1 | ANF Case Analysis for resultant $\mathfrak{J}_f$ Outputs                                                                  | 130 |

| 5.2 | Comparative Summary of Algebraic Degrees for Summation Component                                                          | 130 |

| 5.3 | Exemplifying differences in Algebraic Degree for Generic and New Design                                                   |     |

|     | Framework of Modular Addition.                                                                                            | 131 |

| 5.4 | Complexity Evaluation using Corner Case Analysis                                                                          | 131 |

| 5.5 | Analysis of Results for the New SNOW 2.0.                                                                                 | 135 |

# List of Figures

| 1.1  | Predicted explosive growth of IoT [2]                                                                      | 2  |

|------|------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Thesis Work Breakdown Structure                                                                            | 12 |

| 2.1  | A typical schema for Optimization Process                                                                  | 14 |

| 2.2  | $\star$ =Solutions of the objective functions in PF, $\bullet$ =Feasible solutions and                     |    |

|      | $\blacksquare = Infeasible solutions where m = 2. \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 17 |

| 2.3  | Social hierarchy of Grey Wolves                                                                            | 25 |

| 2.4  | The design search space positioning for GWO-DSE $[3]$                                                      | 26 |

| 3.1  | Open Systems Interconnection reference model magnifying Network, Data                                      |    |

|      | Link and Physical layers                                                                                   | 33 |

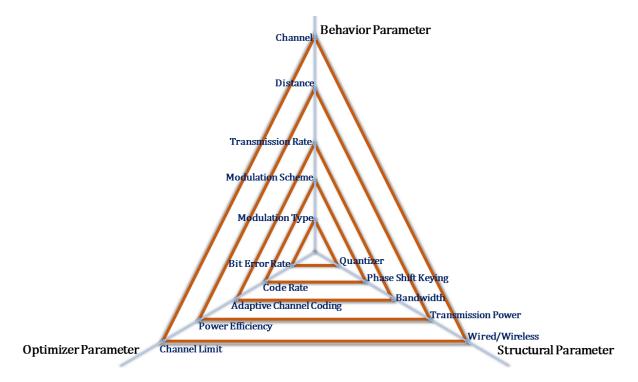

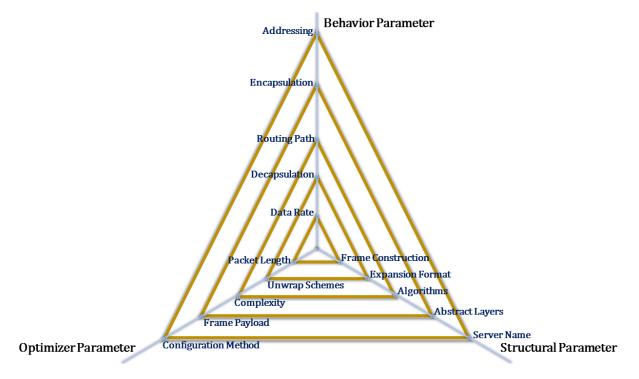

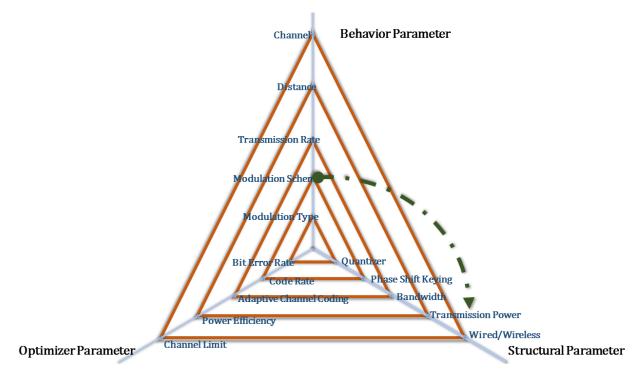

| 3.2  | Delta chart synthesizer for Physical Layer                                                                 | 35 |

| 3.3  | Delta chart synthesizer for Network Layer                                                                  | 35 |

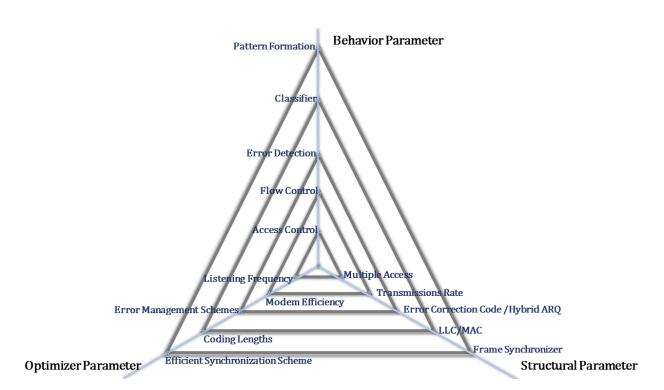

| 3.4  | Delta chart synthesizer for data link Layer                                                                | 38 |

| 3.5  | A example Network Architecture for IoT                                                                     | 42 |

| 3.6  | Parameter synthesizing action for Physical Layer Synthesis                                                 | 47 |

| 3.7  | Parameter synthesizing start action for Data Link Layer Synthesis                                          | 50 |

| 3.8  | Parameter synthesizing sophomore action for Data Link Layer Synthesis                                      | 51 |

| 3.9  | Parameter synthesizing final action for Data Link Layer Synthesis                                          | 52 |

| 3.10 | Parameter synthesizing begin action on Network Layer                                                       | 54 |

| 3.11 | GWO Delta diagram Synthesized Cross-layer solution compared with tradi-                                                                 |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | tional layered solutions                                                                                                                | 63  |

| 3.12 | Network Lifetime and Convergence Scenario Analysis                                                                                      | 65  |

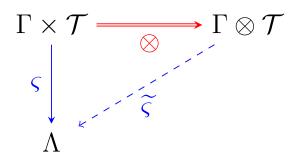

| 4.1  | Universal Property for Tensor Product                                                                                                   | 71  |

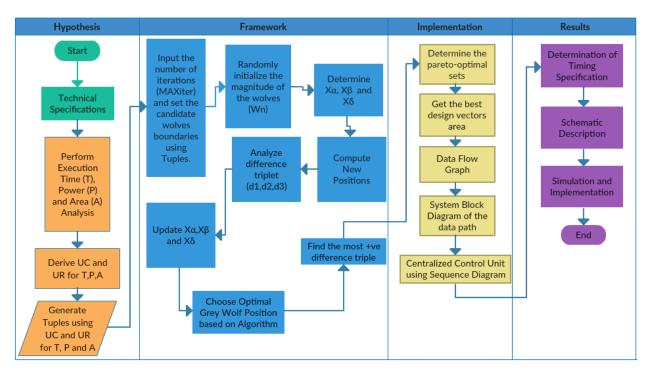

| 4.2  | The proposed framework for high level design flow based on multi-parametric                                                             |     |

|      | optimization.                                                                                                                           | 85  |

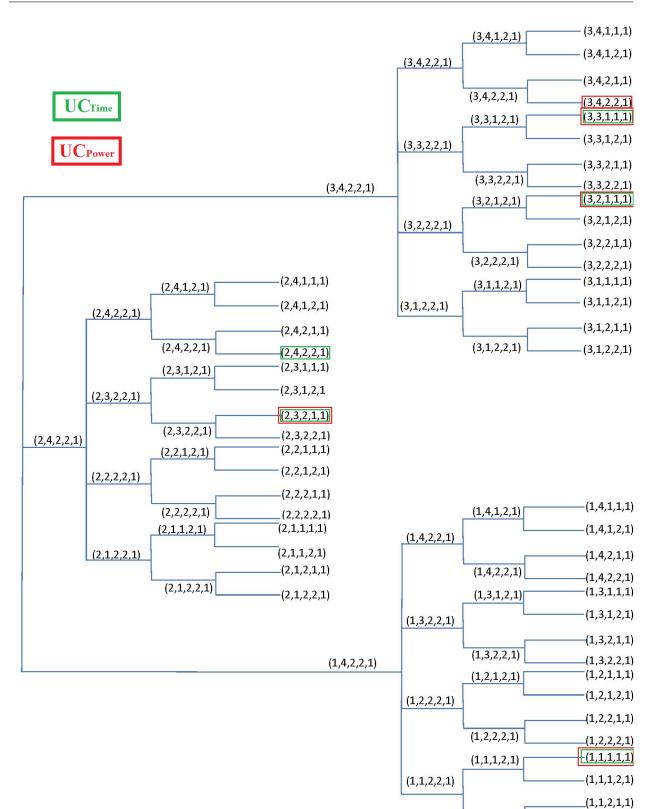

| 4.3  | Phylogenetic tree indicating tuples arising due to $UR_P$ evaluation in Eq. (4.40)                                                      |     |

|      | and Eq. (4.46)                                                                                                                          | 89  |

| 4.4  | Phylogenetic tree indicating tuples arising due to $UR_A$ evaluation in Eq. (4.54)                                                      | 95  |

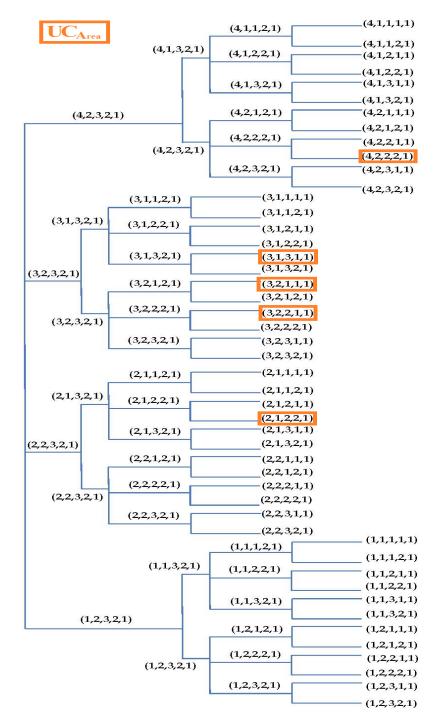

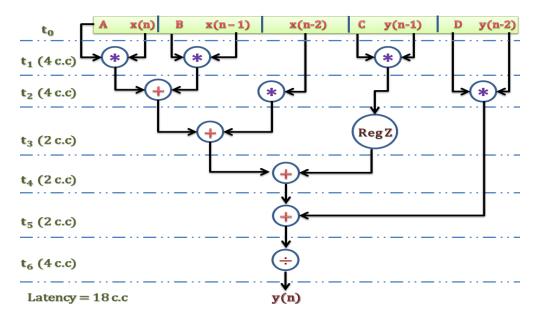

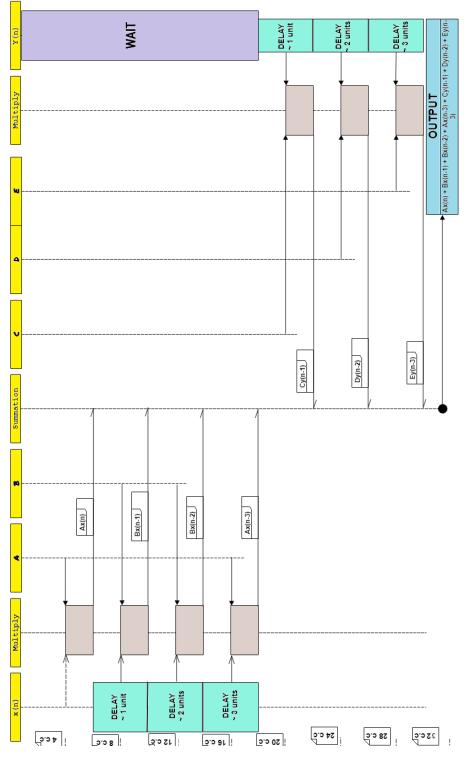

| 4.5  | DFG Sequencing using ASAP algorithm for Elliptic Wave Filter of Eq. $(4.33)$                                                            | 99  |

| 4.6  | Cycle time diagram for finding the optimal tuple in UR based on DFG in                                                                  |     |

|      | Figure. 4.5                                                                                                                             | 102 |

| 4.7  | Convergence Scenario Analysis                                                                                                           | 105 |

| 5.1  | Block Schematic Diagram for New Design Framework of Modular Addition .                                                                  | 114 |

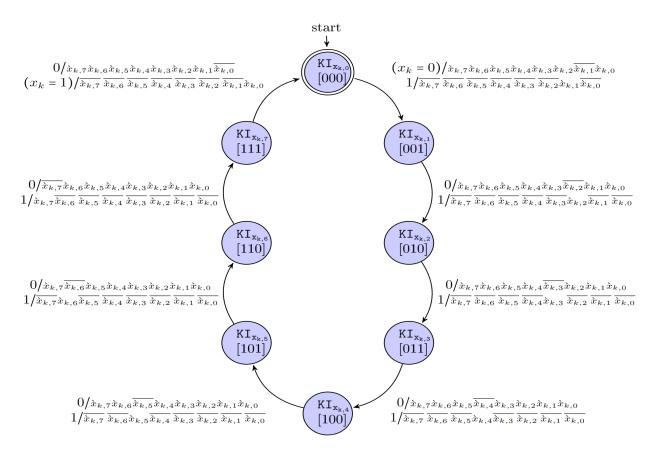

| 5.2  | Inflate function output states $\dot{x}_{k,j}$ depending on control input $KI_{x_{k,j}}$ for $m = 3$                                    | 119 |

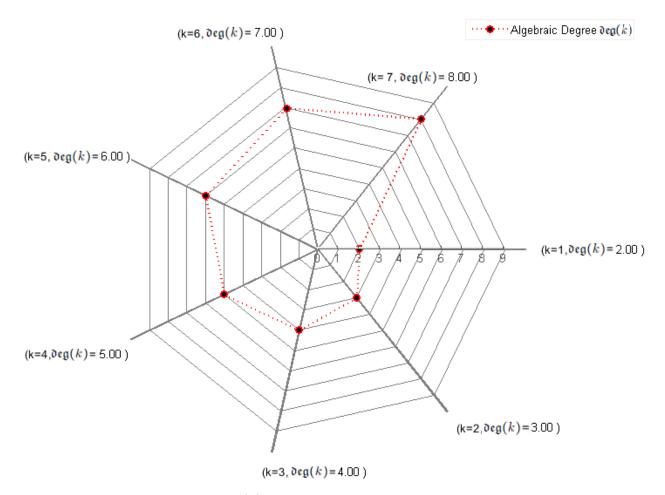

| 5.3  | Algebraic degree $\mathfrak{deg}(k)$ for general Modular Addition corresponding to every                                                |     |

|      | bit k where $1 \le k \le 7$ , $n = 8$ .                                                                                                 | 121 |

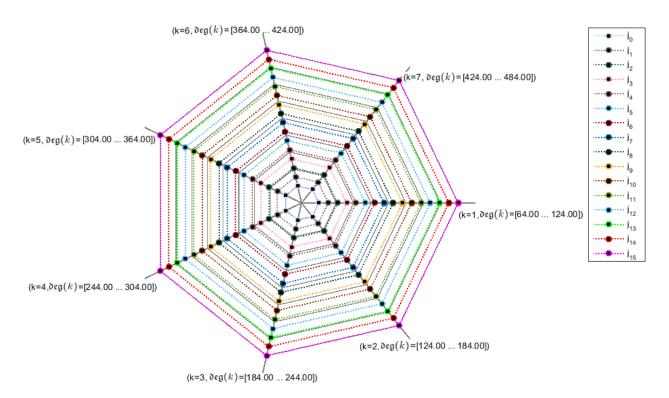

| 5.4  | An outspread of Algebraic degree $\mathfrak{deg}(k)$ for New Design Framework of Mod-                                                   |     |

|      | ular Addition corresponding to every bit k where $1 \leq k \leq 7$ , $n = 8$ and                                                        |     |

|      | $0 < j \le w - 1, w = 15, m = 4$                                                                                                        | 122 |

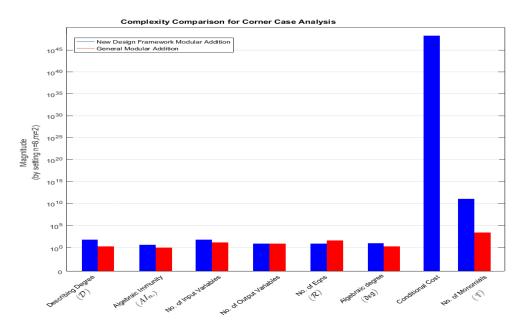

| 5.5  | Differentiating various properties using Corner Case Analysis with $m = 2$ and                                                          |     |

|      | $n = 8. \ldots $ | 128 |

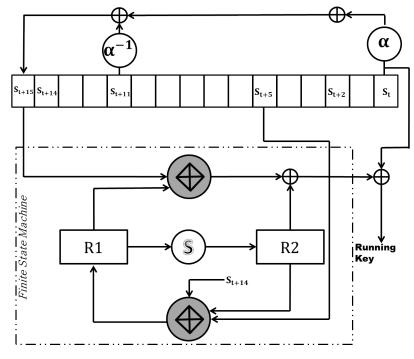

| 5.6  | Schematic for the New SNOW 2.0 Design                                                                                                   | 134 |

## Chapter 1

## INTRODUCTION

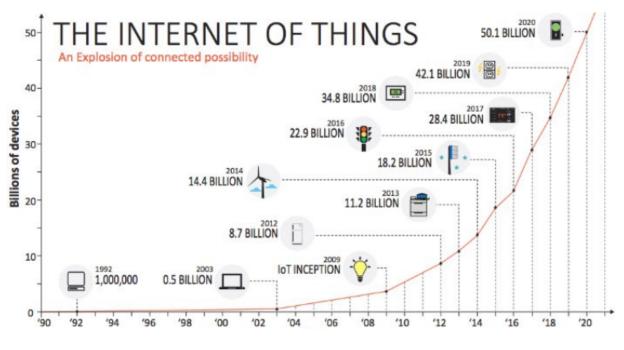

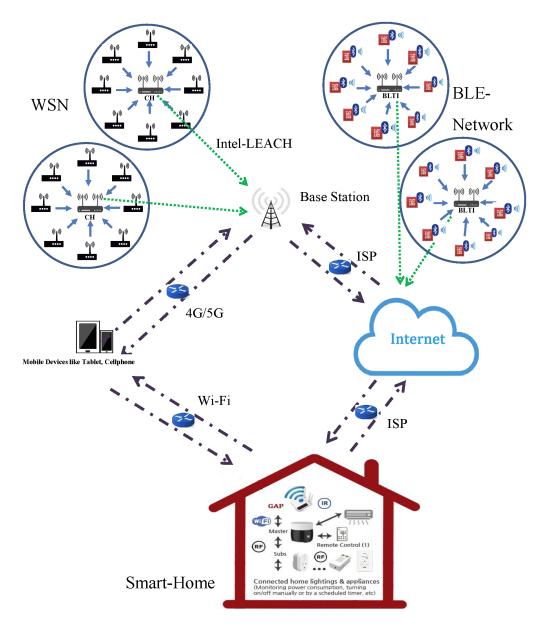

Internet of Things (IoT) is an rapidly emerging concept in the today's world. It encompasses various objects and communication methods for exchanging data. In practice, IoT is a generalized term that describes a vision where everything should be connected to the Internet. IoT is a ground breaking technology for present and future since the concept opens up seamless opportunities for new services and innovations. IoT is revolutionizing many sectors such as logistics and transportation, manufacturing plants and agriculture by increasing their operational efficiency, reducing the energy usage and better management of resources. As IoT expands with unique opportunities, Cisco estimates that there will be around 50 billion IoT devices by 2020[2]. The growth of IoT devices depicted in Fig. 1.1 since its inception in 2009 is phenomenal. As the number of connected devices increases exponentially, achieving higher network capacity and reliability with minimal latency and energy consumption is highly challenging. It is estimated that the IoT will cause a substantial increase in the Internet Protocol (IP) traffic to the tune of 300% by year 2020[4].

Figure 1.1: Predicted explosive growth of IoT [2]

#### 1.1 IoT

Defining the term IoT can be cumbersome since its definitions are usually ambiguous since it is loosely used as a buzzword in scientific research and marketing strategies.

The basic notion of IoT is to link things together which allows them to communicate with each other thereby enabling people to share information [5]. "Things", in the IoT sense, can mean a wide variety of devices depending on the context of term used. However, in general terms legal scholars suggest regarding "things" as an "inextricable mixture of hardware, software, data and service" [6]. In this thesis we follow the definition of IoT proposed by ITU-T's Telecommunication Standardization Sector (a United Nations agency which specializes in Information and Communication Technology): "A global infrastructure for the information society, enabling advanced services by interconnecting (physical and virtual) things based on existing and evolving inter-operable information and communication technologies".

## **1.2** Interconnection Challenge among Devices

The three main tasks of any IoT network are sensing, analyzing and transmitting. Because of the communication capability, thousands of individual nodes form a single entity and provides collective intelligence on the topic of interest. Due to the limited transmission range, IoT devices may have to multi- hop their sensed data possibly over long distances. Therefore, connectivity or communication between individual devices is crucial for the successful operation of the network. Main factors that plague the reliability of the communication are discussed in the following sub-sections.

#### **1.2.1** Interference: Internal and External

An inherent problem associated with the wireless networks is interference. Interference can be internal or external. External interference is caused by other sources such as domestic appliances, Bluetooth devices. Internal interference occurs when the nodes within the same network transmit at the same time.

Wireless Sensor Networks (WSN) operate on an unlicensed ISM bands and therefore the radio spectrum is shared with several other devices[7]. As Wi-Fi uses 2.4GHz frequency, the WSN such as IoT might have to compete to utilize the frequency. Appliances such as microwave oven, plasma lighting system, cordless phones that generate electromagnetic noise are also known to increase the packet loss rate, this, in turn, increases the retransmission rates and latency[7, 8]. Similarly, internal interference due to concurrent transmission also negatively impacts the performance of the network[9]. It is also empirically shown that a cross-channel interference also decreases the packet delivery rate[10].

#### **1.2.2** Environmental Obstacles

Natural obstacles such as office walls, human and vehicular movements, dense vegetation generally deteriorate the signal strength. Humidity and temperature also influences the radio waves[11, 12, 13, 14].

#### **1.2.3** Deployment Environments

When the area to be monitored is large and in a remote location, sensors are usually randomly deployed. The position of the sink node a data aggregation point also plays a crucial role in the performance of the network. Imbalanced traffic load causes some of the nodes in the network to expend more energy, risking the network to become unconnected and thus rendering it useless[15].

If the average number of hops between the source and the sink node is less, the latency and the energy consumption is also relatively lesser compared to the larger number of hops between source and the sink. In addition, if the number of hops between the source and the sink is less, the collision rate is less which in turn results in better packet delivery rate.

#### **1.2.4** Hardware and Software Configuration

Application data rate, the amount of control messages generated by the routing protocol at the network layer, collision avoidance technique employed at the MAC layer greatly influences the performance of the network. Choosing the routing protocol such as Collection Tree Protocol (CTP) that generates the fairly large amount of control packets along with high application data rate increases the contention in the network[16].

Even when the transceivers of the sensor nodes in an IoT network are configured exactly, in the same way, they may distort transmitted or received a signal due to their internal noise[17, 18]. The low power transmits signals are more susceptible to interference and the multi-path distortion. In addition, the remaining battery life is also known to affect the sensitivity of the transceivers[19]. Furthermore, most of the IoT devices have an in-built antenna with irregular radiation pattern. All these factors contribute to the degradation of the communication quality.

## 1.3 Motivation

Multi-objective optimization techniques applied for communication system synthesis have the attractive advantage of explicitly capturing the constraints and preferences of the communicating device that use both small scale as well as large scale networks, and provide unique insight into trade-offs among competing requirements. The next-generation communication systems aim to build an intelligent and efficient transmission by connecting a variety of heterogeneous networks to fulfill information exchange tasks. The motivation (MO) for this thesis is to address various challenging aspects of communication systems such as: (a) the development of new efficient protocols and optimization of existing communicating devices (b) the hardware design improvement of low power embedded devices for network architectures and (c) the security analysis and privacy improvement of low computing powered systems.

MO1: High-reliability Low-latency factor. As discussed in detail from the previous sections, each day the world embraces more devices to connect everything, everywhere, and everyone. Driven by global digitalization and the emerging IoT or IoE paradigms, the number of connected devices are increasing at an exponential rate from the current circa 10 billion to an estimated 20-fold within the next five years (refer Fig. 1.1). The abundant exploitation of wireless sensors, gadgets, multimedia services, autonomous robots or tactile Internet, augmented reality, and other similar applications, will require unparalleled access rates with high reliability and low latency.

MO2: Competing Resources in 5G. The basic idea of this new type of networking and computing paradigm is the pervasive presence of a variety of objects (things), such as WSN, actuators, mobile devices, and RFID tags, which are able to interact with each other and communicate with the Internet infrastructure. Designing such a scalable network that can incorporate dynamic elements such as device-2-device communications, small cell access points, network cloud, and the IoT which is an integral part of 5G cellular network architecture faces many challenges. These challenges are mainly caused by the limited resources available, especially reliable security, limited battery lifetime, computing capacity, and memory space at sensor nodes, and also by dynamic network topology especially in ad hoc sensor networks. On the other hand, special features of WSN such as limited computing power, storage space, battery capacity and limited area for hardware sensory circuits, in particular bring in new requirements on time and space efficiency of the MoAs that can be applied in such an environment.

**MO3:** Scalability of IoT. Many contemporary IoT designs fail to treat the trade-off problems as a MOO issue; instead they choose an objective to optimize, leaving the others as restrictions. This leads to most of them being applied only to networks of limited magnitude, and in very restricted situations. As the scale of commercial systems grows, there is a complete lack of tools to aid in the designing process and the age-old methodology of trial and error is neither effective nor efficient.

**MO4:** Routing in IoT. Routing strategy is another fairly important problem in IoT design [20, 21], which may have a direct impact on multiple aspects of network performance, including data transmission delay, throughput, security and lifetime of individual nodes as well as the entire network. Mobile agents are often used in IoT to visit a sequence of sensors and fuse impotent data. Optimal agent routes also often need to meet multiple objectives such as minimizing total path delay, loss, and energy consumption as well [22]. These MOO trade-off problems are challenging issued that need to be addressed.

**MO5:** IoT Hardware Optimization. To devise a design space exploration (DSE) methodology to perform multi-objective optimization (MOO) subject to constraints with a trade-off requirement from the very earliest stage of designing IoT having low computing power hardware. This will enable the IoT hardware device designers to start the development with an architecture that is already specification aware (high level optimized) from the highest level of abstraction thus rendering more chances that final design (logic/layout) corresponds to the given low computational constraints. A stellar synthesis system can produce several designs from a given hardware specification within reasonable amount of time.

However, the final selection can be challenging with many choices of designs produced (near optimal set). Therefore, an efficient exploration method is currently needed for IoT hardware to tackle the problem from a very high abstraction level. This assures the IoT hardware designer a greater chance of optimization and flexibility to control architecture based on user requirements. More importantly, this allows the developer to explore different trade–offs between cost, speed, power etc. or to take an existing design and produce a functionally equivalent one that is more efficient.

### **1.4** Research Objectives and Goals

The research objective (RO) is to develop an adaptive framework for decomposition of IoT communication system devices and protocols using multi-objective optimization techniques. These techniques are primarily driven by cost-benefit analysis using power-security-execution time and area trade-off circumstances. The results can then be used to assist communicating network interfaces in arriving using optimal solutions that depend on communicating device capabilities. The following research objectives are achieved.

**RO1:** Develop Novel Cross-layer Schemes for the IoT Network. The use of crosslayer communication schemes to provide adaptive solutions for the IoT is motivated by the high heterogeneity in the hardware capabilities and the communication requirements among things. In this thesis, a novel Delta Diagram synthesis for the IoT is proposed to accurately capture both the high heterogeneity of the IoT and the impact of the Internet as part of the network architecture.

**RO2:** Develop a Novel Optimizer Framework based on Grey Wolf Optimizer Algorithm for IoT domain. Design an effective resource management meta-heuristic decision maker using a novel Grey Wolf Optimizer (GWO) framework is proposed to obtain optimal routing paths and the communication parameters among things, by exploiting the interrelations among different layer functionalities in the IoT. Moreover, a cross-layer communication protocol is utilized to implement and test this optimization framework in practical scenarios. The results show that the proposed solution can find near-optimal solutions constructively and outperforms existing layered solutions. The novel Delta-diagram is a preliminary step towards providing efficient and reliable end-to-end communication in the IoT which may be extended to other dimensions of IoT like security and hardware synthesis. **RO3: Develop and demonstrate a Novel design space exploration scheme for IoT hardware architecture synthesis.** To introduce a novel design space exploration (DSE) approach which is based on combination of the Utility Ranking (UR) method and Grey wolf Search based framework that is rapid and accurate in IoT hardware architecture evaluation and selection. The goal for the novel DSE is to apply on a number of standard benchmarks which yielded superior results compared to the current existing DSE approaches [23, 24, 25] for architecture selection. The comparison results of our devised novel approach with the current existing approaches for different benchmarks will be shown and the speed boosts obtained will be presented.

**RO4:** Designing a universal synthesizer for automating communication protocol optimization A novel synthesizer based on Delta diagram approach is developed and can utilized universally for plotting parameters for any layer in the communication protocol stack and subsequently utilized for model optimization strategies for the network. This approach leads to development of more customizable system designs since designers using our framework have the flexibility to choose the most optimized communication channel to meet their trade-off objectives.

**RO5:** Designing a new Modulo Addition for enhancing security of light weight ciphers in IoT We introduce a new Modulo Addition structure that includes components such as Input Expansion, Modulo Addition, and Output Compaction. The security of the new structure is scalable and completely user-defined. It also substantially increases the algebraic degree of the existing cryptographic system and thwarts the probabilistic conditions ideal for hacking attacks. We develop an adaptive and extensible Addition Modulo for IoT based ultra lightweight ciphers which includes both stream and block ciphers, that not only attains optimum security but also its design results in less gate–equivalents (GE's), less memory size, and less power dissipation compared to complete cipher upgrade. This approach is crucial in bringing online certain things with limited security architectures. These things can be older versions of small–scale embedded devices with restricted hardware and cannot be outright replaced but can incorporate certain security upgrades like our proposed model.

## 1.5 Contributions

The fundamental contribution and novelty of this work is to develop innovative optimizer schemes to address three main verticals of IoT domain such as communication system, device hardware and security ciphers and provide a novel seamless solutions to cater these pressing issues in IoT especially with the advent of 5G technologies. The research objectives are realized by employing the following contributions.

Automated Communication Synthesizer. We design and develop a IoT communication framework that utilizes a novel Delta Diagram based model for rapid choosing of network layer parameters to initiate a cross-layer optimization. A fundamental model is developed that caters to the optimization parameters synthesized pertaining to energy, timing, and packet error rates of the network. In addition, the new framework utilizes a Grey wolf optimizer to optimize Quality of Service (QoS) requirements in terms of delay, energy consumption and reliability requirements of an IoT communication network and arrives at near optimal solutions.

Novel DSE methods for synthesizing IoT device hardware. We design and develop a new framework for an accelerated design space exploration of resource constrained IoT hardware. The approach was successful in laying the foundation for exploring the design points from the architecture design space according to the performance objective and intended functionality. This novel method determines the utility coefficients of each resource for designing hardware of IoT. After the architectural design specification were organized in sorted order based on the utility coefficients calculated, the procedure for applying the optimizer algorithm becomes simpler. The research objective is to drastically reduce the number of architectural variants to be analyzed for selection of the system architecture. The proposed mechanism for DSE was able to resolve conflicting objectives in HLS by utilizing a novel Grey Wolf Optimizer. A case study with IoT device based Elliptic Wave filter was presented for further analysis.

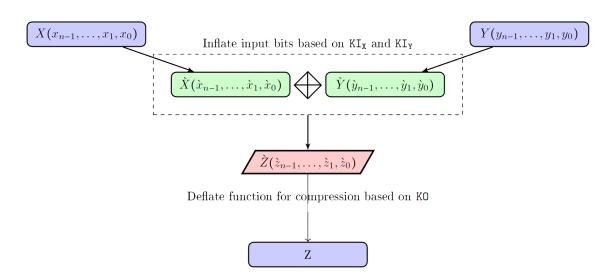

Security Enhancement Techniques for IoT device hardware. We devise a new type of scheme for Modulo Addition to defend against algebraic attacks involving multivariate polynomials for lightweight ciphers. This caters to both Stream an Block type in IoT communication nodes. The developed model features three components: an Expandable Input, Modulo Addition, and a compression module called Deflate function. In addition, the new design framework utilizes an expanding and compacting structure that can fit into various lightweight cryptographic systems based on user–based requirements and depends on the constrained computational power of specific IoT nodes.

### **1.6** Thesis Organization

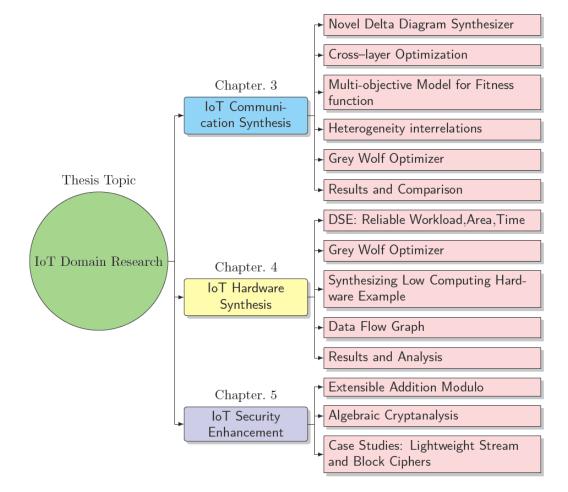

An outline linking our research objectives in IoT domain to the goals realized in following chapters is shown using the Fig. 1.2. This makes the reader gain better understanding of the aims in this thesis. The organization of this thesis linking the chapters to IoT themed research goals is illustrated using organization chart shown in Table. 1.1. The rubric in Table. 1.1 organizes the chapters as follows: Chapter 1 will describe the motivation and objective behind this thesis. Chapter 2 will outline in detail about current research emphasis on MOO techniques and survey the respective methods. Chapter 3 synthesizes the network of resource deprived IoT communication systems using a novel delta diagram based

| Chapters | Research Goals                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------|

| 1.       | Defines IoT and uses, Connects our research goals to current industry trends.                                    |

| 2.       | IoT objectives achieved and potential future work.                                                               |

| 3.       | Surveys contemporary Multi-objective optimizers, choose the best suited for our IoT based research.              |

| 4.       | Utilize a novel approach to choose levelized parameters to initiate cross-<br>layer optimization of IoT network. |

| 5.       | Novel optimization framework for initiating design space exploration on resource constrained IoT Hardware.       |

| 6.       | Novel design for updating IoT based lightweight ciphers sans complete replacement.                               |

Table 1.1: Organization Rubric relating Chapters to Research Goals of this Thesis.

parameter capture method and utilizes a novel Grey Wolf Optimizer to narrow the search space finding near-optimal solutions constructively and compare state-of-the art methods. The research goal described in Chapter 4 formulates High Level Synthesis tools for Design Space Exploration of IoT specific resource constrained devices and also utilizes the novel Grey Wolf Optimizer driven multi-objective optimization algorithm described in Chapter 2 to shortlist near-optimal solutions to get the best hardware IoT configuration. Chapter 5 outlines research based design for security enhancement of IoT based lightweight ciphers on existing devices rather than a complete replacement of the things. In the end, Chapter 6 outlines conclusions drawn from this thesis work and potential future path.

Figure 1.2: Thesis Work Breakdown Structure.

## Chapter 2

# REVIEW: MULTI-OBJECTIVE OPTIMIZATIONS

In this section, we briefly discuss some important Multi–Objective Optimization (MOO) techniques proposed in the literature that are only relevant while tackling constraints associated with resource-aware IoT domain. It is important to note that this chapter is not a comprehensive literature review of general MOO techniques.

### 2.1 Strategies for IoT Optimization

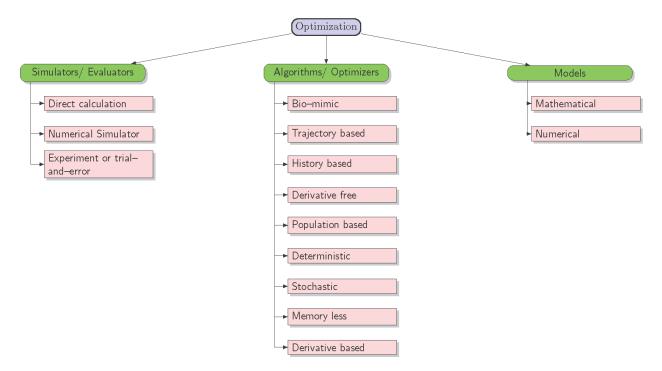

Optimization covers almost all aspects of human life and work. In practice, the resources are limited, hence optimization is significant. Most research activities in IoT engineering involve a certain amount of modeling, data analysis, computer simulations and mathematical optimization. This branch of applied science aims for finding the particular values of associated variables, which results in either the minimum or the maximum values of a single objective function or multiple objective functions [26]. A typical optimization process is composed of three components [27]: the model, the optimizer/algorithm and the evaluator/simulator, as shown in Figure. 2.1. The representation of the physical problem is carried out by using mathematical formulations to establish a mathematical model.

There is no single algorithm that is suitable for all problems arising in IoT domain and an efficient optimizer or algorithm must be designed to ensure that an optimal solution set is obtained. In general, optimization algorithms can be classified as:

- 1. Finitely terminating algorithms, such as the family of simplex algorithms and their extensions, as well as the family of combinatorial algorithms;

- 2. Convergent iterative methods that

- Evaluate Hessians (or approximate Hessians, using finite differences), such as Newtons method and sequential quadratic programming;

- Evaluate gradients or approximate gradients using finite differences (or even subgradients), such as quasi-Newton methods, conjugate gradient methods, interior

Figure 2.1: A typical schema for Optimization Process

point methods, gradient descent (alternatively, "steepest descent" or "steepest ascent") methods, sub-gradient methods, bundle method of descent, ellipsoid method, reduced gradient method, and simultaneous perturbation based stochastic approximation methods; and

- Evaluate only function values, such as interpolation methods and pattern search methods.

- 3. Heuristics/Meta-heuristics that can provide approximate solutions to some optimization problems particularly in resource starved IoT.

Recently, bio-mimetic heuristics/meta-heuristics based strategies have been widely used to solve MoA for designing WSN in the IoT [28], since they are capable of obtaining nearoptimal solutions to optimization problems characterized by non-differential nonlinear objective functions, which are particularly hard to deal with using classical gradient- or Hessianbased algorithms.

## 2.2 Multi-Objective Optimization

Multi-objective optimization (MOO) is a process of simultaneously optimizing multiple conflicting goals or objectives. The difference with single-objective optimization is that MOO results in several/many equally efficient solutions, known as Pareto optimal solutions, instead of one single solution. A MOO problem consists of a set of objective functions that can be either maximized or minimized. A set of constraints limits the set of possible outcomes, known as the solution space. Without loss of generality, a multi-objective minimization problem having n variables and m(m > 1) objectives can be formulated as:

$$\begin{array}{ll} \underset{x}{\operatorname{minimize}} & \mathcal{F}(x) = (f_1(x), f_2(x), \dots, f_m(x)) \\ \text{subject to} & g_j(x) \ge 0, j = 1, 2, \dots, m_{je} \\ & h_k(x) \ge 0, k = 1, 2, \dots, m_{ek} \end{array} \tag{2.1}$$

where we have  $x \in \mathbb{R}^n$  with  $\mathbb{R}^n$  being the decision space,  $(g_j(x), h_k(x))$  are inequality constraint functions and  $\mathcal{F}(x) \in \mathbb{R}^m$  with  $\mathbb{R}^m$  representing the objective space.

### 2.3 Parto-Optimality

The improvement of one of the objectives in Eq. 2.1 may result in the degradation of other objectives, thus it is important to achieve a *Pareto-optimality*, which represents the conditions when none of the objective functions can be reduced without increasing at least one of the other objective functions [29]. For the minimization of m objectives  $\mathcal{F}(x) = (f_1(x), f_2(x), \ldots, f_m(x))$ , we have the following definitions.

- Non-dominated solutions: A solution **a** is said to dominate a solution **b** if and only if [30]:

- 1.  $f_i(\mathbf{a}) \le f_i(\mathbf{b}) \forall i \in \{1, 2, ., m\},\$

- 2.  $f_i(\mathbf{a}) < f_i(\mathbf{b}) \exists i \in \{1, 2, , m\}.$

Solutions that dominate the others but do not dominate themselves are termed nondominated solutions.

• Local optimality in the Pareto sense: A solution a is said to be locally optimal in the Pareto sense, if there exists a real  $\mathcal{E} > 0$  such that there is no other solution **b**

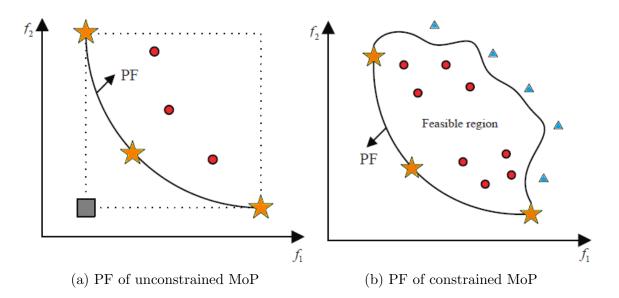

Figure 2.2:  $\star$ =Solutions of the objective functions in PF,  $\bullet$ =Feasible solutions and  $\blacktriangle$ =Infeasible solutions where m = 2.

dominating the solution a with  $\mathbf{b} \in \mathbb{R}^n \cap B(\mathbf{a}, \mathcal{E})$ , where  $B(\mathbf{a}, \mathcal{E})$  shows a bowl having a center a and a radius  $\mathcal{E}$ .

- Global optimality in the Pareto sense: A solution a is globally optimal in the Pareto sense, if there does not exist any vector **b** that dominates the vector **a**. The main difference between global and local optimality lies in the fact that for global optimality we no longer have a restriction imposed on the decision space  $\mathbb{R}^n$ .

- *Pareto-optimality*: A feasible solution is said to be Pareto-optimal, when it is not dominated by any other solutions in the feasible space. Pareto sense, which is also often referred to as the efficient set, is the collection of all Pareto-optimal solutions and their corresponding images in the objective space are termed the PF.

We observe from Figure. 2.2a that the Pareto-optimal solutions of the objective functions in the PF (marked as asterisk) provide better values than any other solution in  $\mathbb{R}^m$ . The ideal solution marked by a square indicates the joint minimum of the objective values  $f_1$ and  $f_2$  and it is often difficult to reach. The remaining solutions marked as solid circles are all dominated by at least one solution of the PF. In contrast to the unconstrained scenario of Figure. 2.2a, in Figure. 2.2b, the curve illustrates the PF of a constrained MoP. The solid circles in the feasible region represent the feasible solutions, while the remaining points outside the feasible region (e.g. the points marked by triangles) are infeasible [31].

### 2.4 MOA application for IoT

A variety of algorithms have been developed for solving MoPs in communication networks and hardware systems related to IoT devices. Multi-objective procedures can be broadly classified into two categories – scalarization and evolutionary methods [32]. Scalarization methods apply in mathematically well defined problems with explicit formulations of objectives and constraints, whereas evolutionary strategies mainly apply in black-box problems, where objectives and/or constraints are evaluated for each value of the optimization variable set. Examples of such evolutionary algorithms are Genetic Algorithms and Swarm Intelligence Algorithms. Some state-of-the art examples of Swarm Intelligence Algorithms include Particle Swarm Optimization (PSO), Grey Wolf Optimizer, Whale Optimizer and Artificial Bee Colony (ABC) algorithms [3, 33, 34, 35].

#### 2.4.1 Scalarization Methods

We briefly describe the most prevalent algorithms in this category: Weighted Sum and  $\mathcal{E}$ -Constraint Methods, and other scalarizing approaches are not relevant to our discussion in this thesis.

#### A. Weighted Sum Method

The weighted sum method assigns a non-negative weight to each objective and normally the weights sum up to one. The mathematical definition is shown in Equation 2.2. The different objectives do not have to be scaled because the weights merely serve to find solutions on the Pareto front. By changing the set of weights, a different point on the Pareto front can be obtained. However, there are three difficulties with the weighted sum method [36]: (i) there is no satisfactory (a priori) selection method to determine the weights that guarantee the final solution to be acceptable, (ii) it cannot find solutions on non-convex regions of the Pareto front, and (iii) varying the weights may not result in an evenly distributed and accurate/complete representation of the Pareto front.

$$\begin{array}{ll} \underset{x}{\text{minimize}} & \mathcal{F}(x) = \sum_{m=1}^{M} w_m f_m(x) \\ \text{subject to} & g_j(x) \ge 0, j = 1, 2, \dots, J \\ & h_k(x) \ge 0, k = 1, 2, \dots, K \end{array}$$

(2.2)

#### B. $\mathcal{E}_{\text{constraint}}$ Method

The  $\mathcal{E}_{\text{constraint}}$  Method optimizes one objective, while the other objectives are used as constraints. It overcomes the limitations of the Weighted Sum Method. Consequently, compared with the weighted sum method (Equation 2.2) there is only one objective function  $(\mathcal{F}_{\mu}(x))$ and additional constraints  $(f_m(x) \leq \mathcal{E}_m)$  that require the other objectives do not exceed the user-defined values. The new equation is shown in Equation 2.3.

$$\begin{array}{ll} \underset{x}{\operatorname{minimize}} & \mathcal{F}_{\mu}(x), \\ \text{subject to} & \mathcal{F}_{m}(x) \leq \mathcal{E}_{\mathtt{m}}, \ m = 1, 2, \dots, M \ and \ m \neq \mu \\ & g_{j}(x) \geq 0, j = 1, 2, \dots, J \\ & h_{k}(x) \geq 0, k = 1, 2, \dots, K \end{array}$$

$$(2.3)$$

Although the  $\mathcal{E}_{constraint}$  method has various advantages over the weighted sum method such as its ability to produce non-extreme efficient solutions, one of the biggest drawback is selecting the value of  $\mathcal{E}$ . Since the best values are not known beforehand, increasing the  $\mathcal{E}$  value with small steps would result in a lot of redundant runs. Increasing with larger steps would result in it missing the pareto optimal solution while optimizing resource-aware IoT systems.

#### 2.4.2 Knapsack Problem

The classical Knapsack Problem (KP) is a variation of the  $\mathcal{E}_{\text{constraint}}$  method where is objective function is a dual viz., we maximize it instead of minimization. We can set  $N := \{1, \ldots, n\}$  of items and a knapsack of limited capacity. To each item we associate a positive profit  $p_j$  and a positive weight  $w_j$ . The problem calls for selecting the set of items with maximum overall profit among those whose total weight does not exceed the knapsack capacity c > 0. KP has the following Integer Linear Programming (ILP) formulation:

$$\underset{x}{\text{maximize}} \qquad \mathcal{F}(x) = \sum_{j \in N} p_j x_j \tag{2.4}$$

subject to

$$\sum_{j \in N} w_j x_j \le c$$

(2.5)

$$x_j \in \{0, 1\}, j \in N \tag{2.6}$$

where each binary variable  $x_j$ ,  $j \in N$ , is equal to 1 if and only if item j is selected. In general, we cannot take all items because the total weight of the chosen items cannot exceed the knapsack capacity c. In the sequel, without loss of generality, we assume that  $\sum_{j \in N} w_j > c$ and  $w_j \leq c$  for every  $j \in N$ . The *k*-item Knapsack Problem (kKP), is a KP in which an upper bound of k is imposed on the number of items that can be selected in a solution. The problem can be formulated as (2.4)-(2.6) with the additional constraint

$$\sum_{j \in N} x_j \le k,\tag{2.7}$$

with  $1 \le k \le n$ . KP has widely been discussed in the literature and we refer to [37] for a comprehensive illustration of the problem. The KP and its multidimensional version (MKP) are basic problems in combinatorial optimization. We utilize this approach in [38] whose objective was to obtain or approximate the set of efficient Pareto solutions for high level synthesis of IoT hardware.

### 2.5 Genetic Algorithms

A genetic algorithm (GA) applied to a MOO begins with an initial set of solutions, represented by chromosomes. In each generation, new solutions are generated using genetic operators such as recombination, crossover and mutation. For each individual in the population (in each generation), a fitness value  $\mathcal{F}(x)$  is calculated representing the goodness of the solution. The algorithm stops when an end condition is satisfied. Crossover takes two individuals and uses random point(s) to cut the chromosome in two segments, a 'head' and 'tail' segment [39, 40, 41]. The tail segments are swapped over to produce two new chromosomes.

GA suffers from innumerable disadvantages such as no guarantee in finding global minima, impractical time taken for convergence, producing incomprehensible engineering solutions, etc. Consequently the GA method is discarded for dealing with critically resource depraved IoT optimization approaches.

## 2.6 Swarm Intelligence Algorithms

The various MoAs discussed so far in the previous sections are subject to many disadvantages. The salient drawbacks include impractical time to reach termination condition, egregious time delay to reach near–optimal solutions, complex aspects such as calculating the fitness function which requires inherent tweaks and adjustments at every iteration, incomprehensible solutions produced leading to multiple re-runs, etc. These drawbacks are in in direct contradiction to optimizing resource-aware and time critical IoT domain. Thus Swarm Intelligence Algorithms seem to be an obvious fit due to their features such as scalability, system robustness, adaptability and flexibility.

Swarm intelligence (SI), an integral part in the field of artificial intelligence, is gradually gaining prominence, as more and more high complexity problems require solutions which may be sub-optimal but yet achievable within a reasonable period of time. Mostly inspired by biological systems, swarm intelligence adopts the collective behavior of an organized group of animals, as they strive to survive. Our primary emphasis is on most popular in literature and state-of-the-art algorithms: PSO and GWO. In essence, we focus on the algorithms inspired by birds and wolves.

#### 2.6.1 Particle Swarm Optimization

PSO is a stochastic optimization algorithm which was derived from the flight patterns of a flock of birds in search for food, overcame majority of the problems that were faced by the algorithms discovered before it.

Two main parameters of the PSO algorithm is finding the most optimal position and the most optimal velocity of the swarm as the birds strive to achieve their personal best position and velocity for themselves as well as the best position and velocity depending upon the group.

The PSO algorithm is similar to GAs because of how randomly ordered the search space is, initially. However, the biggest advantage this algorithm has over GA is that the PSO algorithm has fewer parameters that are needed to be adjusted after every iteration. The change in position and velocity is given by the following equations:

$$x_i(t+1) = x_i + V_i(t+1)$$

(2.8)

Here x denotes the position of the bird in the current time frame, which depends on the position of the bird in the previous time frame and the current velocity of the bird. Note: In the PSO described below (Algorithm. 1), the initialization step updates the position of the primary particles with velocity factor and hence the step of update function is mentioned after velocity adaptation step. Therefore, for this research work we adopt this variation of PSO. The current velocity or the updated velocity of the bird is found using the following equation:

$$V_{i}(t+1) = \omega V_{i}(t) + c_{1}r_{1}\left(x_{i}^{lb} - x_{i}(t)\right) + c_{2}r_{2}\left(x_{i}^{gb} - x_{i}(t)\right)$$

(2.9)

The parameters in the Eq. 2.8 can be summarized as follows:

- $\omega$  is the inertia weight

- $c_1$  and  $c_2$  are the cognitive and the social learning factors respectively.

- $r_1$  and  $r_2$  are random numbers in the range [0,1].

- $x_i^{lb}$  is the position of the local best particle with respect to the minimization problem, and

- $x_i^{gb}$  is the position of the global best particle.

The entire optimization algorithm aims at achieving  $x_i^{gb}$  viz., all the particles try to converge at the best position of one particle, thus reaching a termination point. The pseudo code for PSO described above is outline in Alg. 1. In the process of Systems of Chip (SoC) development, the problem of an exponentially exploding design space can be a major challenge. PSO algorithm can be employed to realize the most optimum resource configuration [42]. In search of the global best solution, the PSO algorithm divides a swarm into multiple subswarms and thus, the objectives could only be handled by one sub-swarm. As a result of this, a bigger swarm size is needed to solve the multi-objective optimization problem. Thus in each iteration, the computation time rises [43].

| ALGORITHM 1: (PSO) Pseudo Code                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Input:</b> Initialize a population of particles with random values positions and velocities                                                                                                                                                |

| from $D$ dimensions in the search space.                                                                                                                                                                                                      |

| 1 while Termination condition not reached do                                                                                                                                                                                                  |

| 2 foreach every particle i do                                                                                                                                                                                                                 |

| <b>3</b> Evaluate the fitness $\mathcal{F}(\vec{X}_i)$                                                                                                                                                                                        |

| $\begin{array}{c c} 4 \\ 5 \end{array}  \begin{array}{c} \mathbf{if} \ \mathcal{F}(\overrightarrow{X}_i) < \mathcal{F}(\overrightarrow{P}_i) \ \mathbf{then} \\ \overrightarrow{P}_i \leftarrow \overrightarrow{X}_i \end{array} \end{array}$ |

| 5 $\vec{P}_i \leftarrow \vec{X}_i$                                                                                                                                                                                                            |

| 6 end                                                                                                                                                                                                                                         |

| 7                                                                                                                                                                                                                                             |

| 8 if $\mathcal{F}(\vec{X}_i) < \mathcal{F}(\vec{P}_g)$ then<br>9 $  \vec{P}_g \leftarrow \vec{X}_i$                                                                                                                                           |

| $9        \overrightarrow{P}_g \leftarrow \overrightarrow{X}_i$                                                                                                                                                                               |

| 10 end                                                                                                                                                                                                                                        |

| 11                                                                                                                                                                                                                                            |

| 12 Adapt velocity of the particle using Equation 2.8                                                                                                                                                                                          |

| 13 Update the position of the particle using Equation 2.9                                                                                                                                                                                     |

| 14 end                                                                                                                                                                                                                                        |

| 15 end                                                                                                                                                                                                                                        |

| 16 return $\overrightarrow{X}_{i}^{gb}$                                                                                                                                                                                                       |

## 2.6.2 Grey Wolf Optimizer (GWO)

Grey wolf optimizer (GWO) [3] is one of recent meta-heuristics swarm intelligence methods. It has proved its efficiency for solving capacitated and non-capacitated optimization problems. It has been widely tailored for a wide variety of optimization problems due to its impressive characteristics over other swarm intelligence methods: it has very few parameters, and no derivation information is required in the initial search. Also it is simple, easy to use, flexible and scalable. It has a special capability to strike the right balance between the exploration and exploitation during the search process which can adapt quickly to different search space terrains and avoid premature convergence. The GWO has recently gained a very big research interest with tremendous audiences from several domains in a very short time [44].

Grey wolfs (*Canis lupus*) are apex predators belonging to the Canidae family [45], which

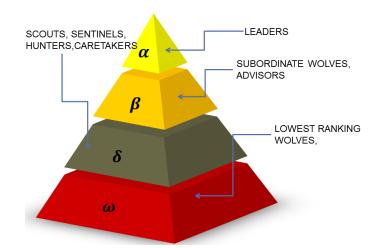

Figure 2.3: Social hierarchy of Grey Wolves.

implies that they are at top of the food chain. The crux of this algorithm is to simulate the Grey wolf behavior which tend to live in a pack. They have a stringent social dominant hierarchy described as follows: The top level comprises the leaders, called alpha. The alpha is the commander of the pack and is responsible for making the decisions. The persistence of the wolf pack is based on alpha's decision. The beta forms the second level which constitute the subordinate wolves. The purpose of a beta is to help the alpha in making important decisions or other activities. The penultimate level consists of subordinate wolves, called delta. The members in this category consist of scouts, sentinels, elders, hunters and caretakers. Scouts are liable for observing the boundaries of region and warn the rest of the pack in case of imminent danger. The sentinels are mandated to protect and guarantee the safety of the pack. Elders are the expertise wolves who used to be alpha or beta. Hunters help the alphas and betas when hunting prey and providing food for the pack and the caretakers are responsible for caring for the weak, ill, or wounded wolves in the pack. The bottom level in the pecking order is omega. The omega wolves have to comply with all the other dominant wolves. In some cases the omega even substitutes as a babysitter in the pack.

The key attribute of Grey wolves is in its ability to memorize the positions of prey and to encircle them. The alpha leads the hunting pack. Consequently, to model the social hierarchy

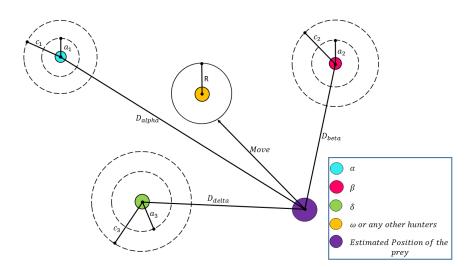

Figure 2.4: The design search space positioning for GWO-DSE [3]

of wolves (shown in Figure. 2.3) mathematically in GWO, the fittest solution is considered to be the alpha ( $\alpha$ ). The beta ( $\beta$ ) and delta ( $\delta$ ) is similar to the second and the third optimal solutions, respectively. The rest of the candidate solutions are assumed to be omega ( $\omega$ ). The alpha, beta and delta guide the entire hunting (optimization) process to form three best solutions which in turn assists the  $\omega$  wolves to update their positions.

#### A. Notations for GWO

Consequently, the prey location will be the optimal solution and the wolves represent the possible solutions in search space. The wolves with least proximity to the prey are the  $\alpha$  wolves and they represent the best solutions among the available solutions. Next to best solutions are the  $\beta$  solutions while  $\delta$  wolves form the third best solutions. Let  $X_{\alpha}$ ,  $X_{\beta}$  and  $X_{\delta}$  denote their locations in the search space respectively. The  $\omega$  wolves update their position in the search space based on their relative positions from  $\alpha$ ,  $\beta$ , and  $\delta$  wolves. Figure. 2.4 shows the positioning of the wolves and prey and the parameters involved in the equations used for updating the positions of the wolves in the search space. The following set of steps must be applied for hunting a prey:

• Initialization

- Prey encircling

- Hunting

- Attack

- Search again

#### **B.** Initialization of GWO

The magnitude of the wolf pack is assumed as  $W_n$ . The locations for  $W_n$  candidate solutions are generated randomly during the phase of initialization as described by Eqs. (2.10) and (2.11) where each candidate wolf is  $\overrightarrow{X_i}$ :

$$\overrightarrow{X}_i = [f_{\text{rand}}(W_n) \cdot (ub - lb) + lb]$$

where  $f_{rand}(x) \sim U([1, x]), (2.10)$

where  $f_{\text{rand}}$  is a uniformly distributed random variable between 0 and x, ub and lb represent upper and lower bounds. If the candidate solutions generated by Eq. (2.10) is beyond the specified range of [lb, ub], the GWO framework must reevaluate the search space using Eq. (2.11), thereby ensuring the initial solution lies within the requisite boundaries.

$$\overrightarrow{X_i} = [\overrightarrow{X_i} \cdot (u+\ell)] + ub \cdot u + lb \cdot \ell$$

where  $u = \overrightarrow{X_i} > ub, \ \ell = \overrightarrow{X_i} < lb$  (2.11)

The GWO framework records fitness values  ${}^{fit}\mathcal{F}$  using a fitness function similar to Eq. 2.1 depending on the context of the problem being solved for each and every candidate solution  $\overrightarrow{X_i}$ . The three most optimal candidate solutions are shortlisted as  $\overrightarrow{X_{\alpha}}$ ,  $\overrightarrow{X_{\beta}}$  and  $\overrightarrow{X_{\delta}}$  respectively.

#### C. Prey Encircling

The pack encircles a prey by repositioning individual agents according to the prey location, as follows: A prey is encircled by the wolf pack by changing the position of individual agents in accordance to the prey location defined by Eq. (2.12).

$$\overrightarrow{X}(t + 1) = \overrightarrow{X}_p(t) + \overrightarrow{A} \cdot \overrightarrow{D}$$

(2.12)

where t is the iteration,  $\overrightarrow{X_p}$  is the prey position,  $\overrightarrow{X}$  is the Grey wolf position and  $\overrightarrow{D}$  is given by,

$$\overrightarrow{D} = |\overrightarrow{C} \cdot \overrightarrow{X_p}(t) - \overrightarrow{X}(t)|$$

(2.13)

where  $\overrightarrow{A}$  and  $\overrightarrow{C}$  are coefficient vectors calculated as follows:

$$\overrightarrow{A} = 2a \cdot \overrightarrow{r_1} - a \tag{2.14}$$

$$\overrightarrow{C} = 2\overrightarrow{r_2} \tag{2.15}$$

where a linearly diminishes over the course of iterations controlling *exploration* and *exploitation*, and  $\overrightarrow{r_1}$  and  $\overrightarrow{r_2}$  are random vectors over the range of [0, 1]. The value of a is the same for all wolves. The Eqs. (2.14) and (2.15) imply that a wolf can update its position in the design search space around the prey at any random location.

#### D. Hunting

The entire wolf pack participates in the activity of hunting based on information relayed by the  $\alpha$ ,  $\beta$  and  $\delta$  wolves, which are expected to record the prey location as specified below,

$$\overrightarrow{X}(t + 1) = \frac{\overrightarrow{X_1} + \overrightarrow{X_2} + \overrightarrow{X_3}}{3}$$

(2.16)

where  $\overrightarrow{X_1}$ ,  $\overrightarrow{X_2}$  and  $\overrightarrow{X_3}$  are defined as follows:

$$\overrightarrow{X_1} = |\overrightarrow{X_{\alpha}} - \overrightarrow{A_1} \cdot \overrightarrow{D_{\alpha}}|$$

$$\overrightarrow{Z_1} = |\overrightarrow{X_{\alpha}} - \overrightarrow{A_1} \cdot \overrightarrow{D_{\alpha}}|$$

(2.17)

$$\overrightarrow{X_2} = | \overrightarrow{X_\beta} - \overrightarrow{A_2} \cdot \overrightarrow{D_\beta} |$$

(2.18)

$$\overrightarrow{X_3} = | \overrightarrow{X_\delta} - \overrightarrow{A_3} \cdot \overrightarrow{D_\delta} |$$

(2.19)

where  $\overrightarrow{X_{\alpha}}$ ,  $\overrightarrow{X_{\beta}}$  and  $\overrightarrow{X_{\delta}}$  are the first three best solutions for the given iteration t,  $\overrightarrow{A_1}$ ,  $\overrightarrow{A_2}$  and  $\overrightarrow{A_3}$  are defined as in Eq. (2.14), and  $\overrightarrow{D_{\alpha}}$ ,  $\overrightarrow{D_{\beta}}$  and  $\overrightarrow{D_{\delta}}$  are assigned using the following:

$$\overrightarrow{D_{\alpha}} = |\overrightarrow{C_1} \cdot \overrightarrow{X_{\alpha}} - \overrightarrow{X}|$$

(2.20)

$$\overrightarrow{D_{\beta}} = |\overrightarrow{C_2} \cdot \overrightarrow{X_{\beta}} - \overrightarrow{X}| \qquad (2.21)$$

$$\overrightarrow{D_{\delta}} = |\overrightarrow{C_3} \cdot \overrightarrow{X_{\delta}} - \overrightarrow{X}| \qquad (2.22)$$

where  $\overrightarrow{C_1}$ ,  $\overrightarrow{C_2}$  and  $\overrightarrow{C_3}$  are specified in Eq. (2.15).

The Eqs. (2.20, 2.21, 2.22) are interpreted by the fact that  $\alpha$ ,  $\beta$ , and  $\delta$  wolves know the best position of the prey and the remaining wolves adapt their positions with respect to position of these wolves.

#### **Attacking Stage**

The agents surround the prey, which is achieved by decrementing the exploration rate a. The parameter a is linearly updated for every iteration to range from 2 to 0 using Eq. (2.23).

$$a = 2 - t \cdot \left(\frac{2}{\text{Iter}_{\text{MAX}}}\right) \tag{2.23}$$

where t specifies the iteration count and  $\text{Iter}_{MAX}$  specifies the maximum number of iterations allowed for the GWO. The exploration and exploitation are guaranteed by the adaptive nature of a value[3], thus allowing GWO to ensure simple transition between exploration and exploitation cycles. Therefore half of the iterations are reserved for exploration while the later half is dedicated to exploitation. The interpretation of this stage is analogous to wolves moving or switching their position to any random position sandwiched between their current position and the position of the prey.

#### E. Search Again

In order to search for the prey, the wolves begin to diverge their paths from each other. This behavior is modeled in GWO by initializing large values for parameter a to allow for exploration of the design search space. The motive is to ensure that the wolves diverge as far as possible from each other to ensure better exploration of the design search space and subsequently converge later to attack, when they spot a better prey. Any wolf can find a better prey (optimal solution). As they get closer to the prey, they will transform into new alphas and the remaining wolves shall be split into beta, delta, and omega depending on the proximity to the prey. The parameter a assigns random weights to prey and specifies the impact of the prey in characterizing the separation of wolves as shown in Eqs. (2.12 and (2.13). This concept helps GWO to exhibit necessary random behavior, which favors exploration and evading local optima. Therefore it can be concluded that the parameter a provides random values throughout the process of exploring design search space which accentuates exploration not only at the beginning of the optimization process but also until its completion.

#### 2.6.3 Advantages of GWO

GWO has several advantages over the existing meta-heuristic algorithms such as PSO, ABC, GA, DE [46]: (1) It is simple to implement, (2) It can maintain the information about the search space and keeps the best solution obtained, (3) It has fewer parameters for fine tuning, and (4) It is a derivative–free algorithm. Due to these comparatively beneficial properties, the performance of GWO far outpaces existing population-based meta-heuristic techniques and it is the hallmark of our optimization procedure for IoT research in this thesis. Consequently we choose GWO algorithm as a optimizer algorithm to build our IoT specific GWO-DSE and GWO-Cross-layer frameworks described in following Chapters. 3 and 4 respectively.

## Chapter 3

# IoT Network Architecture Cross-layer Optimization

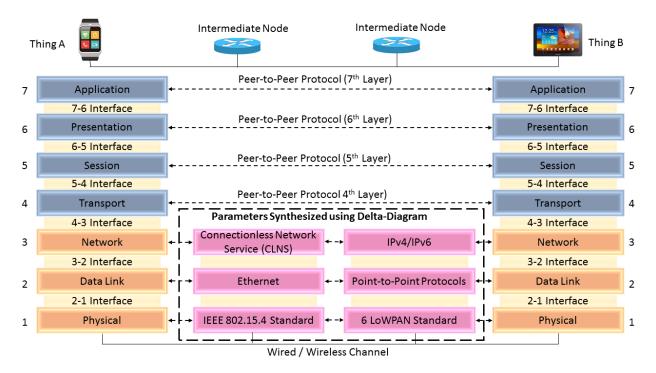

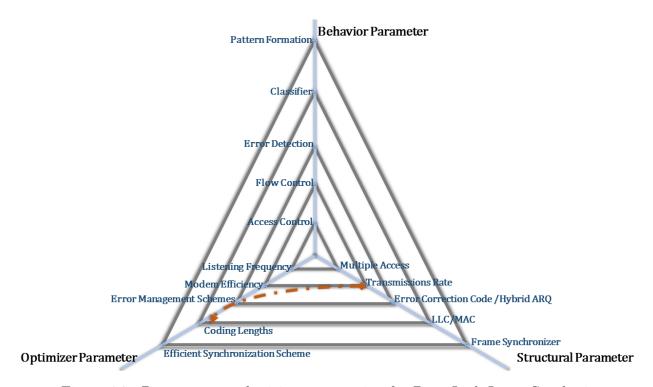

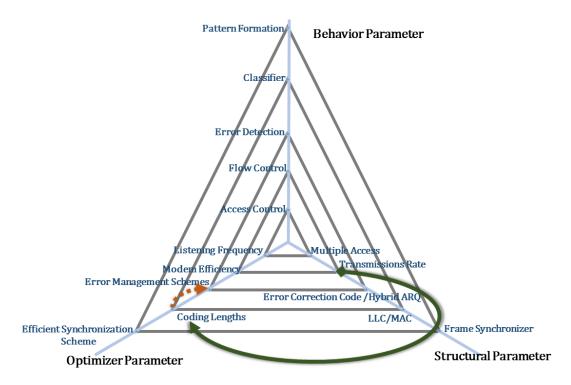

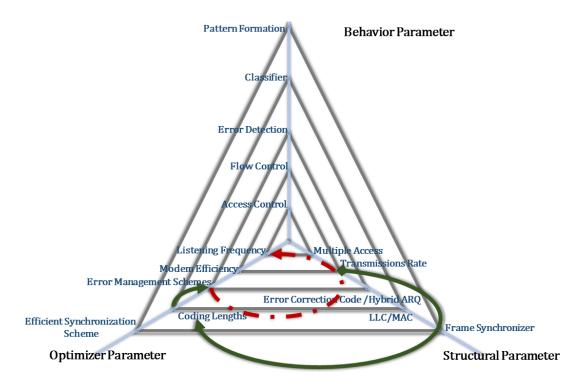

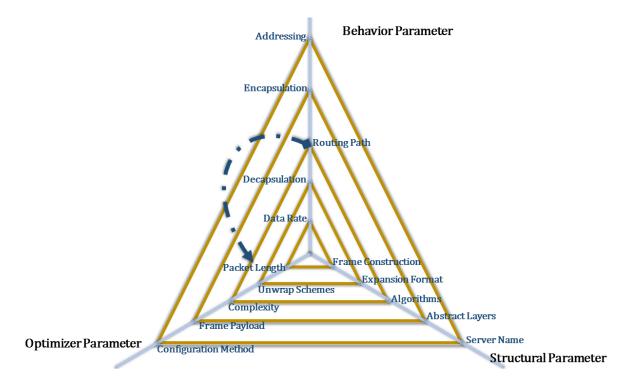

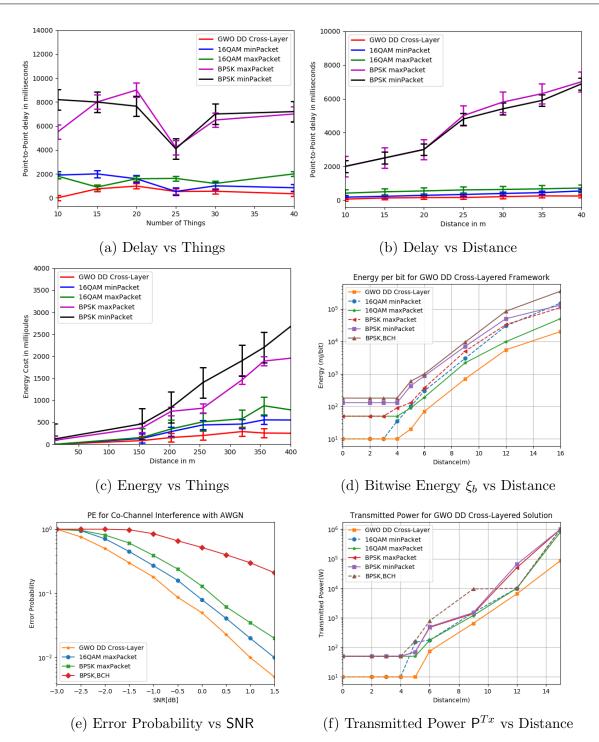

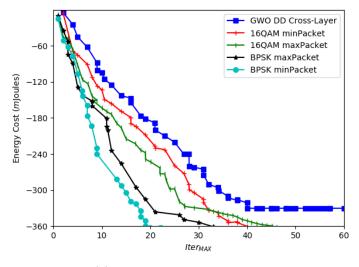

I In this chapter, we propose a novel cross-layer optimization framework and communication module for the IoT using optimizing parameter road map provided by delta diagrams illustrated in [38], 3.3 and 3.4. Our proposed framework captures the high device and service heterogeneities of the IoT. In particular, it exploits the interrelations among the device specifications, physical layer, link layer and network layer, to find the optimal routing paths and their corresponding communication parameters, which jointly optimize the point-to-point delay and energy consumption for given QoS requirements. In addition, the impact of the Internet on the achieved QoS is also taken into account. The results show that the proposed solution outperforms existing layered solutions and the joint-objective cross-layer solution can balance between different design objectives.

Figure 3.1: Open Systems Interconnection reference model magnifying Network, Data Link and Physical layers

## 3.1 Problem Statement