### A DC-SIDE FAULT-TOLERANT BIDIRECTIONAL AC/DC CONVERTER FOR POWER SYSTEM INTEGRATION OF LOW-VOLTAGE DC DISTRIBUTION SYSTEMS

by

Nikoo Kouchakipour

Bachelor of Engineering, KNTU, 2015

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Masters of Applied Science

in the Program of

Electrical and Computer Engineering Ryerson University Toronto, Ontario, Canada

© Nikoo Kouchakipour 2018

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

#### A DC-Side Fault-Tolerant Bidirectional AC-DC Converter for Power System Integration of Low-Voltage DC Distribution Systems

2018

Nikoo Kouchakipour

**Masters of Applied Science**

#### **Electrical and Computer Engineering**

**Ryerson University**

#### Abstract

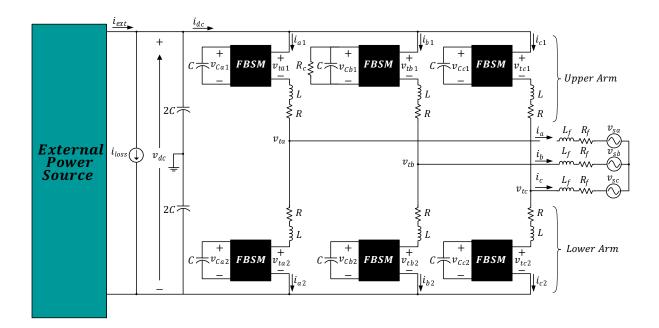

With the rising potential for the employment of low- and medium-voltage direct-current (dc) electric power distribution systems, most notably for a more efficient integration of plug-in electric vehicles and such other distributed energy resources as photovoltaic (PV) panels, there is a need for robust ac/dc electronic power converters that can interface such dc distribution systems with the legacy alternating current (ac) power system. Thus, this thesis proposes a new single-stage low-voltage three-phase ac-dc power converter that is simple structurally, enables a bidirectional power exchanges between the ac and dc distribution systems, and can handle short-circuit faults at its dc as well as ac sides. The proposed converter consists of three legs, corresponding to the three phases of the host ac grid, each of which hosting two full-bridge submodule (FBSM), in an architecture that can be regarded as a special case of the so-called modular multi-level converter (MMC). Thus, at the dc port each FBSM is connected in parallel with a corresponding capacitor, while the ac voltage of each phase is synthesized by the coordinated sinusoidal pulse-width modulation (SPWM) of the two corresponding FBSMs. This architecture allows the generation of low-distortion ac voltage while it also provides the converter with the very important dc fault current blocking capability since, upon the detection of a short circuit across the converter dc port, the switches of the FBSMs are turned off and disallow the flow of any dc current. The thesis also presents a mathematical model for the converter, for analysis and control design purposes. Thus, the control for the regulation of the overall dc-side voltage, as well as those for the regulation of the dc voltages of the FBSMs are devised based on the aforementioned mathematical model and presented with details. It is further shown that the voltage conversion ratio of the proposed converter is the same as that offered by a conventional voltage-sourced converter (VSC), whereas the VSC is vulnerable to dc- side shorts. The proposed converter can be extended to medium-voltage levels by multiplying the number of FBSMs in each leg. The effectiveness of the proposed converter and its controls is demonstrated through time-domain simulation studies conducted on a topological model of the converter in PSCAD/EMTDC software environment.

**Keywords:** Control, dc-side fault, modeling, modular converter, distribution systems, bidirectional, simulation model.

### Acknowledgments

I want to express my deep gratitude for my supervisor, Dr. Yazdani, for his overwhelming support and guidance.

I would also like to thank my family for believing in me and encouraging me throughout my life.

### Contents

| Αι | ithor                                          | 's Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ii                                                       |

|----|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Al | ostrac                                         | :t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                      |

| Ac | knov                                           | vledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | iv                                                       |

| Li | st of ]                                        | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | viii                                                     |

| Li | st of '                                        | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xii                                                      |

| Co | onven                                          | tion for Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xiii                                                     |

| Li | st of A                                        | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xiii                                                     |

| Li | st of S                                        | Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xiii                                                     |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | oduction         Background and Motivation .         Statement of Problem and Overall Thesis Objectives .         Literature Survey Pertinent to the Thesis Objectives .         1.3.1       AC Versus DC Distribution Systems .         1.3.2       Previously Proposed Protection Scheme for LVDC Systems .         1.3.3       Converter Typologies and DC-Side Fault Tolerability in Distribution-Level DC Systems .         Methodology       .         Thesis Contribution and Scope       .         Thesis Outline .       . | 1<br>1<br>3<br>4<br>4<br>7<br>8<br>13<br>14<br>14        |

| 2  | <b>Top</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5  | ology of the Proposed ConverterIntroductionPower-Circuit StructureSwitching SchemePrinciples of Operation2.4.1Operation Under the Normal Conditions2.4.2Operation Under DC-Side Short Circuit FaultsMathematical Modeling of the Proposed AC/DC Converter2.5.1Energy Balance Analysis                                                                                                                                                                                                                                               | 16<br>16<br>16<br>18<br>20<br>20<br>20<br>20<br>21<br>27 |

|    |           |          | Leg Energy Transfer Analysis of the Converter                                         | 28              |

|----|-----------|----------|---------------------------------------------------------------------------------------|-----------------|

|    |           |          | Arm Energy Transfer Analysis of the Converter                                         | 29              |

|    |           | 2.5.2    | Voltage Conversion Ratio                                                              | 31              |

| 3  | Con       |          | the Proposed Converter                                                                | 33              |

|    | 3.1       |          | uction                                                                                | 33              |

|    | 3.2       | Real- a  | and Reactive-Power Controller                                                         | 33              |

|    |           | 3.2.1    | Dynamic Model of Real-/Reactive-Power Controller                                      | 33              |

|    |           | 3.2.2    | Design of the Real-/Reactive-Power Controller                                         | 36              |

|    | 3.3       | DC-Si    | de Voltage Controller                                                                 | 37              |

|    | 3.4       | Energy   | y Balance Controller                                                                  | 41              |

|    |           | 3.4.1    | Leg Energy Balance Controller                                                         | 43              |

|    |           |          | Common-Mode Current Controller Design                                                 | 44              |

|    |           |          | Common-Mode Power Controller Design                                                   | 46              |

|    |           | 3.4.2    | Differential-Mode Active Power Controller                                             | 48              |

|    |           |          | Design of the Differential-Mode Active-Power Controller                               | 50              |

|    | 3.5       | Summ     | ary of the Control                                                                    | 51              |

| 4  | <b>C!</b> | 1.4      | D. 14                                                                                 | 53              |

| 4  |           |          | Results                                                                               | <b>53</b><br>53 |

|    | 4.1       |          | uction                                                                                | 53<br>53        |

|    | 4.2       |          | ystem Configurations                                                                  | 53<br>54        |

|    | 4.3       | •        | Cases and Simulation Results                                                          | 54<br>55        |

|    |           | 4.3.1    | I E                                                                                   |                 |

|    |           |          | Case 1.1: Start Up                                                                    | 55              |

|    |           |          | Case 1.2: DC-Voltage Reference Level Change                                           | 58              |

|    |           |          | Case 1.3: Change of the Value of the External Power                                   | 60              |

|    |           |          | Case 1.4: Change of The Reactive Power Exchanged Between the<br>Converter and AC Grid | 63              |

|    |           | 4.3.2    | Case 2: Non-Ideal Conditions                                                          | 65              |

|    |           | 1.5.2    | Case 2.1: Non-Ideal Converter                                                         | 66              |

|    |           |          | Case 2.2: Non-Ideal Grid                                                              | 69              |

|    |           | 4.3.3    | Case 3: Converter Operation Under DC-Side Short Circuit Faults                        | 72              |

|    |           | т.Э.Э    | Ideal Converter Under DC-Side Fault                                                   | 72              |

|    |           |          | Non-Ideal Converter Under DC-Side Fault                                               | 74              |

|    |           |          | Ideal Converter Connected to a Non-Ideal AC Grid Under DC-Side Fault                  | 76              |

| 5  | Con       | clusion  | and Future Work                                                                       | 79              |

| -  | 5.1       |          | usions                                                                                | 79              |

|    | 5.2       |          | e Works                                                                               | 81              |

| AI | PPEN      | DICES    | 5                                                                                     | 82              |

| ٨  | Cor       | vortor 1 | Paramters                                                                             | 82              |

| A  | COI       |          |                                                                                       |                 |

| B  | Con       | npensat  | ors                                                                                   | 83              |

#### Bibliography

# **List of Figures**

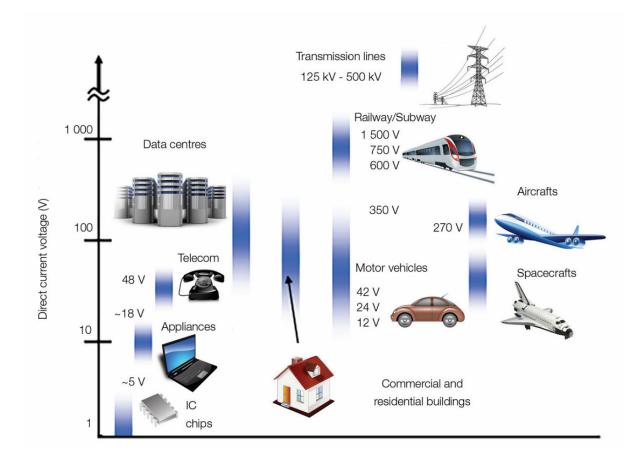

| 1.1 | Voltage range for a number of dc application in today's electricity market[7].                   | 2  |

|-----|--------------------------------------------------------------------------------------------------|----|

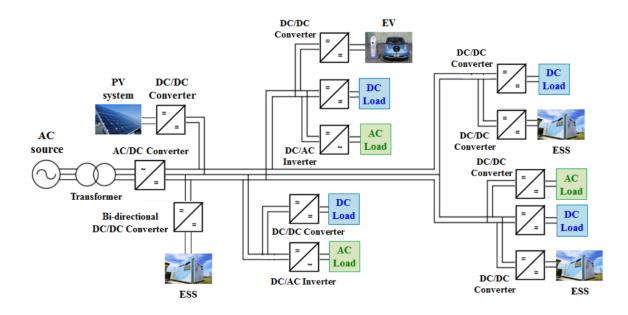

| 1.2 | Concept of an LVDC distribution system [5]                                                       | 3  |

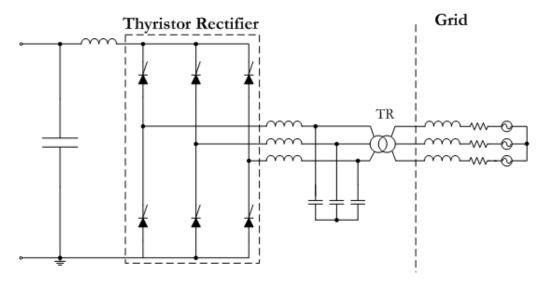

| 1.3 | Schematic diagram of a thyristor rectifier.                                                      | 9  |

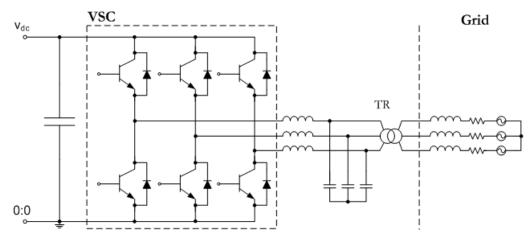

| 1.4 | Schematic diagram of a three-phase, two-level voltage-sourced converter                          | 10 |

| 1.5 | Schematic diagram of a three-level NPC                                                           | 10 |

| 1.6 | Schematic diagram of a 12-pulse thyristor rectifier.                                             | 11 |

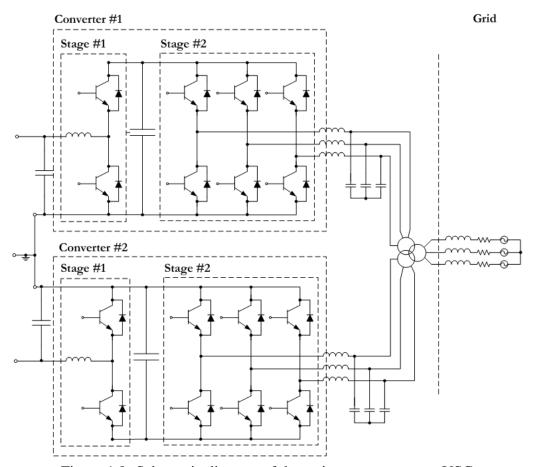

| 1.7 | Schematic diagram of the proposed two-stage VSC in [33]                                          | 12 |

| 1.8 | Schematic diagram of the proposed two-stage NPC VSC                                              | 12 |

| 1.9 | Schematic diagram of the series-type two-stage VSC                                               | 13 |

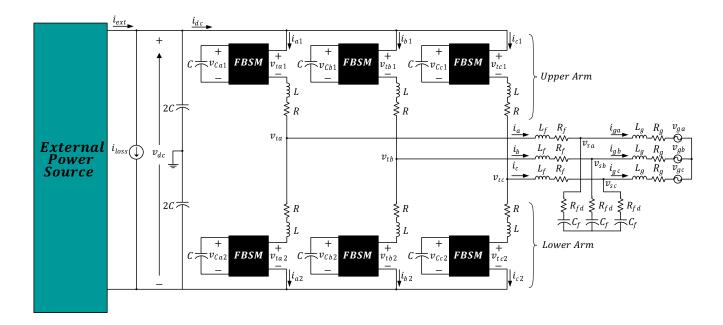

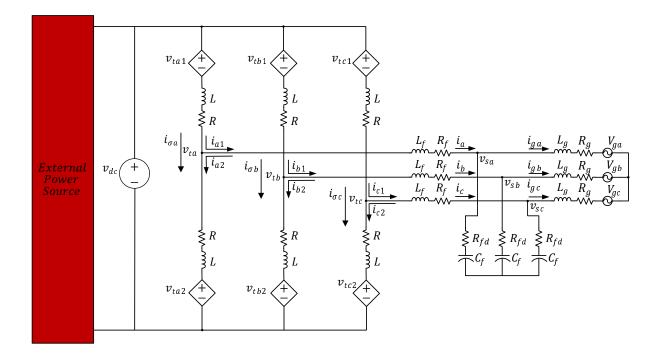

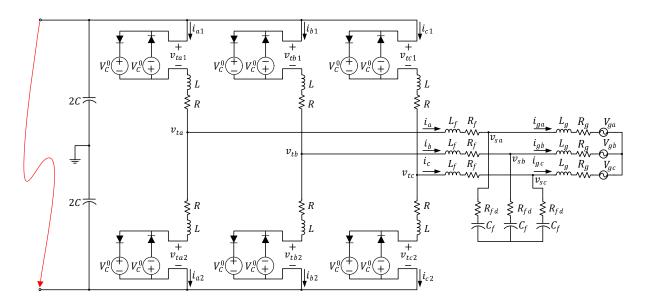

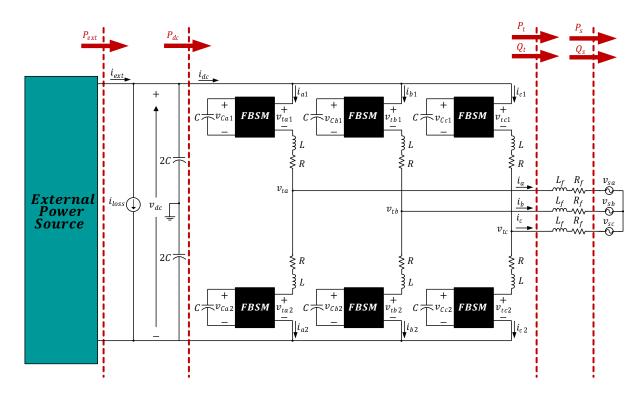

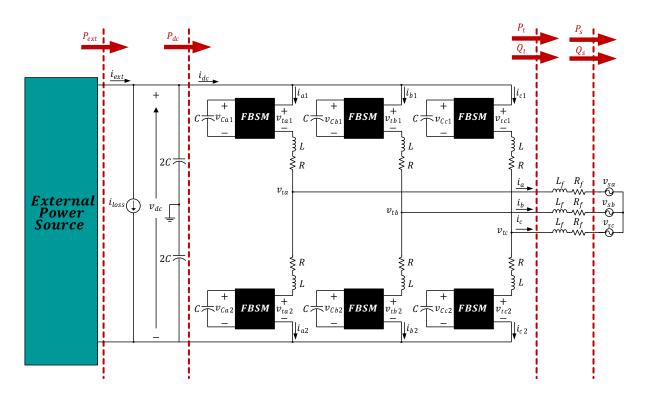

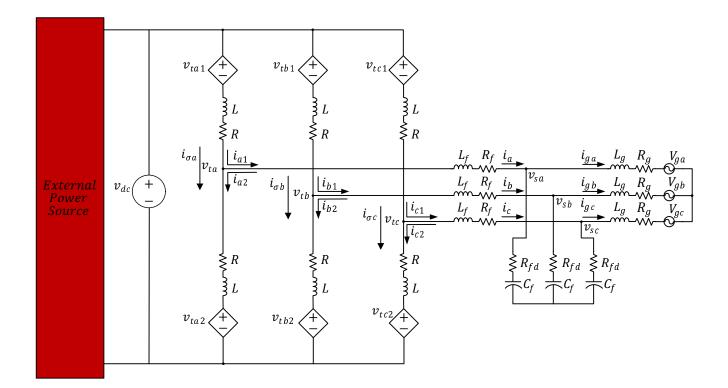

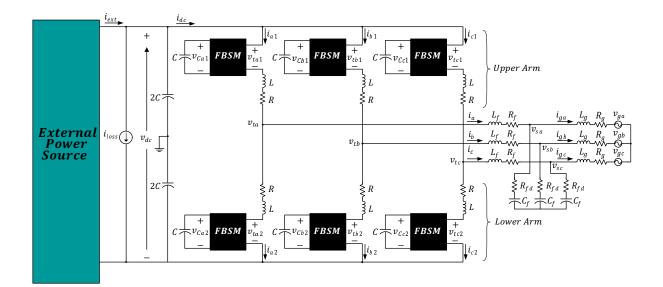

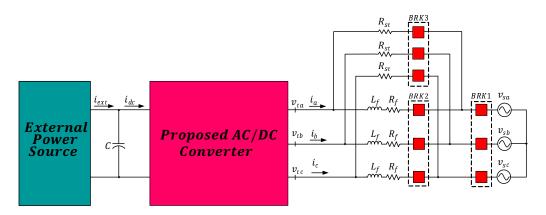

| 2.1 | Schematic diagram of the proposed converter.                                                     | 17 |

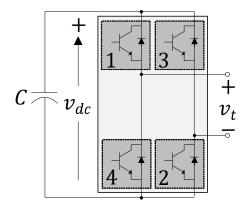

| 2.2 | Schematic diagram of a FBSM                                                                      | 18 |

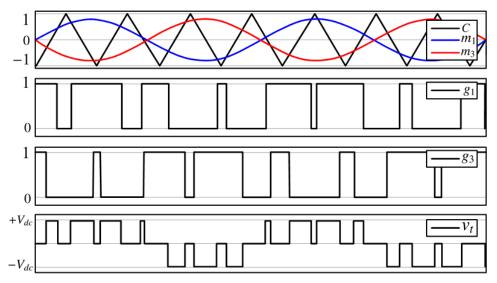

| 2.3 | Waveforms of unipolar PWM.                                                                       | 19 |

| 2.4 | Simplified equivalent Thevenin circuit of the converter from as seen from the                    |    |

|     | ac grid                                                                                          | 20 |

| 2.5 | Schematic diagram of the proposed converter when the converter is operating                      |    |

|     | under normal conditions.                                                                         | 21 |

| 2.6 | Schematic diagram of the proposed converter when the switches are turned off.                    | 21 |

| 2.7 | Schematic diagram of the proposed ac/dc converter illustrating the powers exchanged              | 26 |

| 3.1 | Schematic diagram of the proposed ac/dc converter illustrating the powers                        |    |

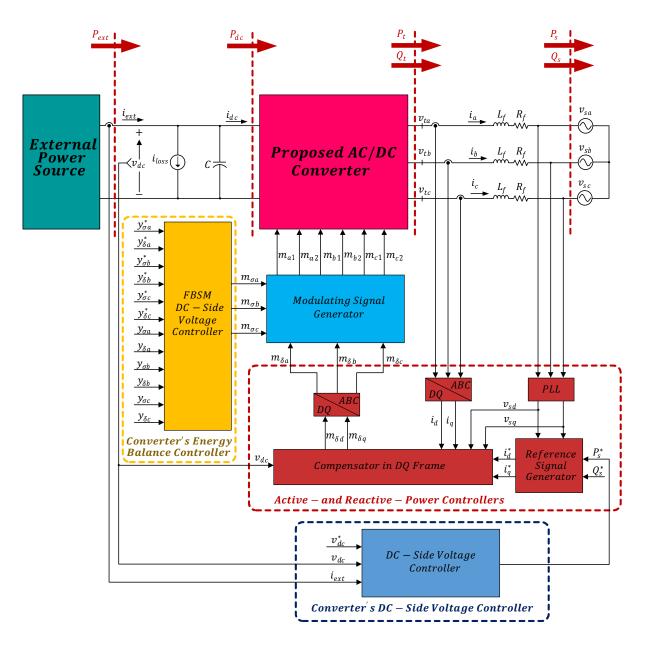

|     | exchanged                                                                                        | 34 |

| 3.2 | Schematic diagram of the proposed converter using current-controlled real-                       |    |

|     | /reactive power controller                                                                       | 35 |

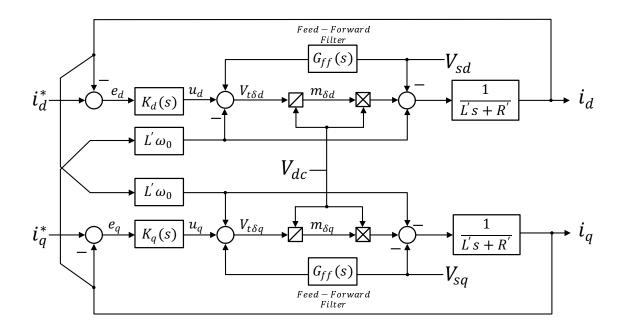

| 3.3 | Control block diagram of the d- and q-axis ac-side current controller for the                    | •  |

|     | proposed converter.                                                                              | 36 |

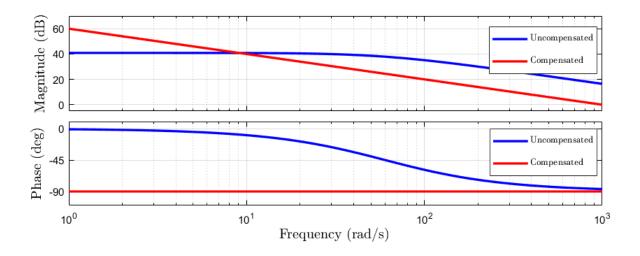

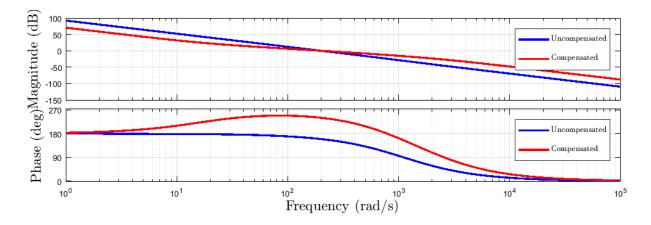

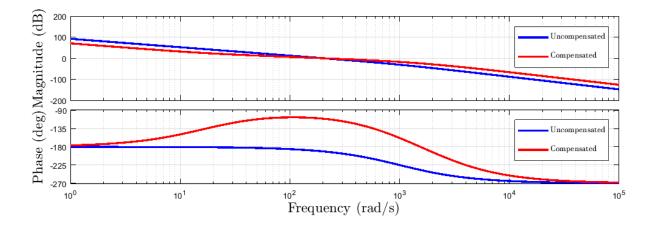

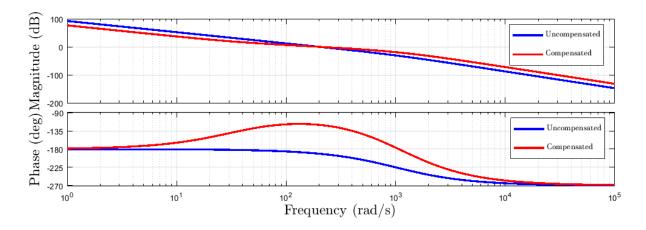

| 3.4 | Bode plot of the uncompensated and compensated open-loop gain of the ac-side current controller. | 37 |

| 3.5 | Schematic diagram of the dc-bus voltage controller with feed-forward com-                        |    |

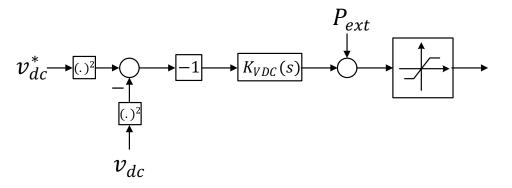

|     | pensation.                                                                                       | 38 |

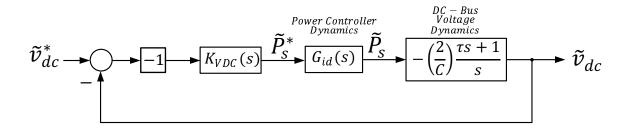

| 3.6 | Control block diagram of dc-bus voltage controller based on linearized model.                    | 39 |

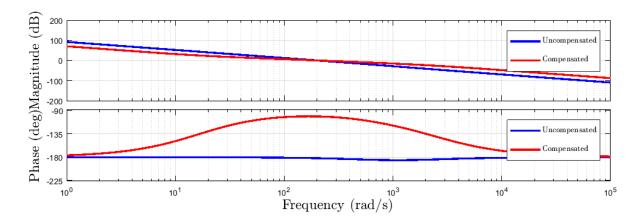

| 3.7 | Bode plot of the uncompensated and compensated open-loop gain of the                             |    |

|     | dc-bus voltage controller for $P_{ext} = -160 \ kW$ .                                            | 41 |

| 3.8 | Bode plot of the uncompensated and compensated open-loop gain of the                             |    |

|     | dc-bus voltage controller for $P_{ext} = 160  kW.$                                               | 42 |

| 3.9   | Bode plot of the uncompensated and compensated open-loop gain of the dc-bus voltage controller for $P_{ext} = 0  kW$ .                                        | 42  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.10  | Control scheme figure for the common-mode dc-side squared voltage controller.                                                                                 | 43  |

|       | Schematic diagram of the proposed converter when the converter is operating                                                                                   |     |

|       | under normal conditions.                                                                                                                                      | 45  |

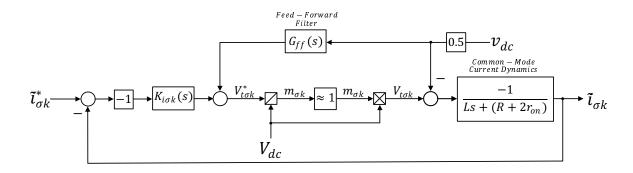

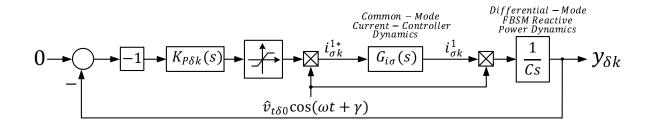

| 3.12  | Control block diagram of the common-mode current controller for the <i>k</i> th leg                                                                           |     |

|       | of the proposed ac/dc converter.                                                                                                                              | 45  |

| 3.13  | Bode plot of the uncompensated and compensated open-loop gain of the                                                                                          |     |

| 0.10  | common-mode current controller.                                                                                                                               | 46  |

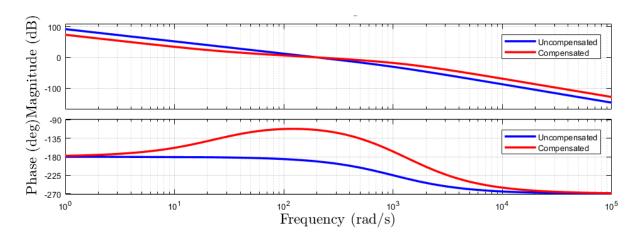

| 3 14  | Bode plot of the uncompensated and compensated open-loop gain of the                                                                                          | 10  |

| 5.11  | instantaneous common-mode FBSM power controller                                                                                                               | 48  |

| 3 1 5 | Control block diagram of the differential-mode dc-side squared voltage                                                                                        | 10  |

| 5.15  | controller for the <i>k</i> th leg of the proposed $ac/dc$ converter                                                                                          | 50  |

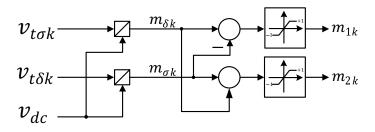

| 2 16  | Schematic diagram of the modulating signal generator of the <i>k</i> th leg of the                                                                            | 50  |

| 5.10  | proposed converter.                                                                                                                                           | 51  |

|       |                                                                                                                                                               | 51  |

| 4.1   | Schematic diagram of the proposed converter when connected to a non-ideal                                                                                     | ~ ^ |

|       | grid                                                                                                                                                          | 54  |

| 4.2   | Schematic diagram of the proposed converter, along with the start-up resistors                                                                                |     |

|       | and breakers                                                                                                                                                  | 56  |

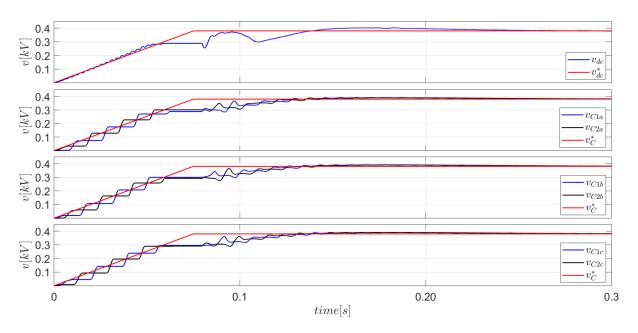

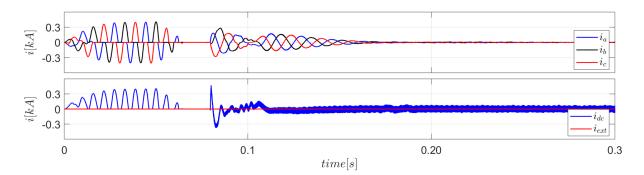

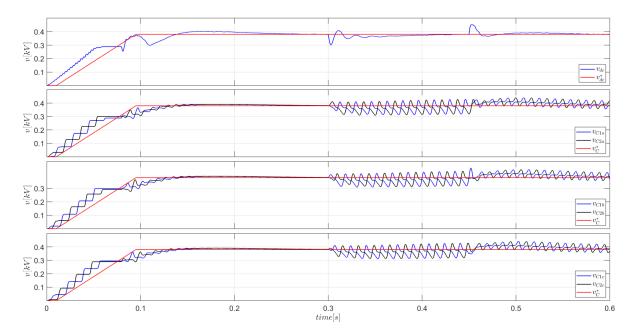

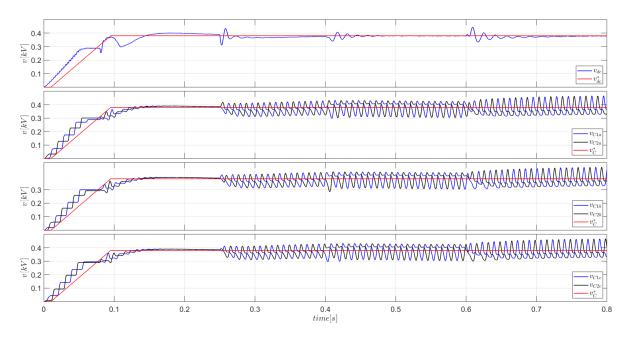

| 4.3   | Dynamic response of the dc-side voltage of the converter and the FBSMs                                                                                        |     |

|       | during the start-up procedure under ideal conditions                                                                                                          | 57  |

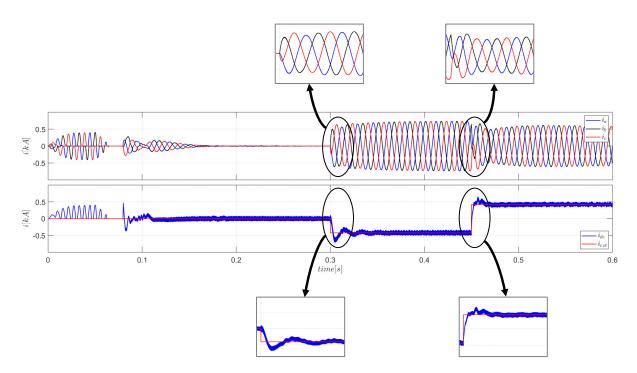

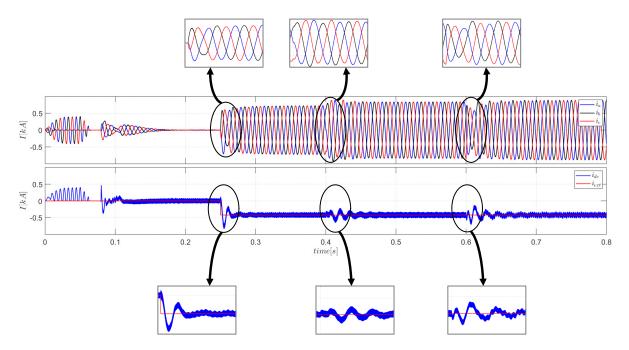

| 4.4   | Dynamic response of the dc- and ac-side currents during the start-up procedure                                                                                |     |

|       | of the proposed converter under ideal conditions                                                                                                              | 57  |

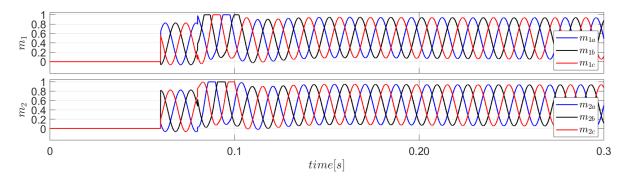

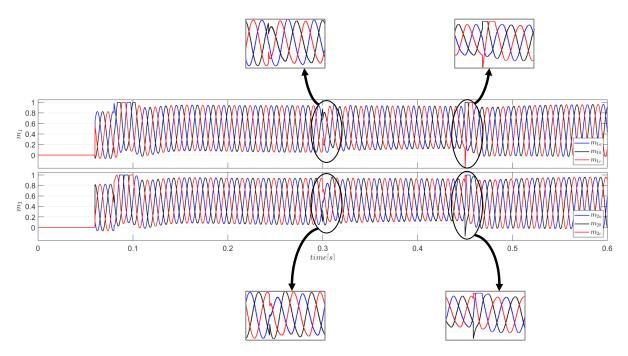

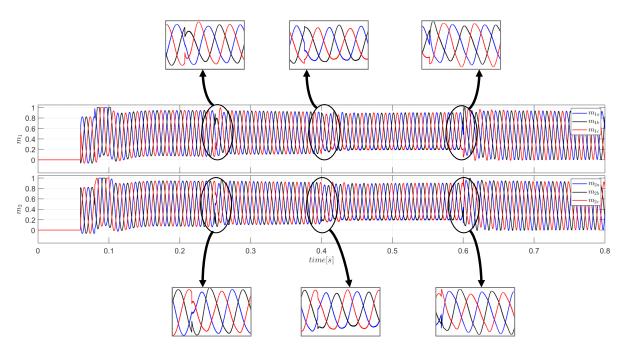

| 4.5   | Modulating signals of the FBSMs of the converter during the start-up procedure                                                                                |     |

|       | of the proposed converter under ideal conditions                                                                                                              | 57  |

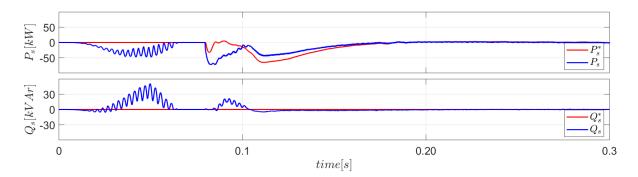

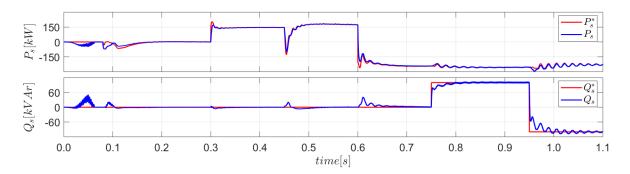

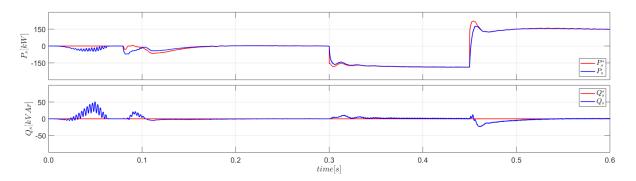

| 4.6   | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ during the start-up procedure                                                       |     |

|       | of the proposed converter under ideal conditions                                                                                                              | 58  |

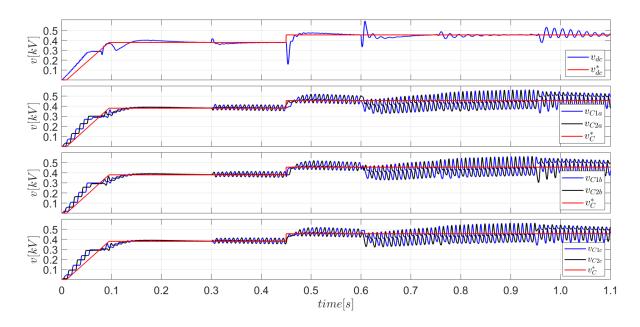

| 4.7   | Dynamic response of the dc-side voltage of the converter and the FBSMs while                                                                                  |     |

|       | facing changes in their reference values under ideal conditions                                                                                               | 59  |

| 4.8   | Dynamic response of the dc- and ac-side current while facing changes in $v_{dc}^*$                                                                            |     |

|       | under ideal conditions                                                                                                                                        | 59  |

| 4.9   | Modulating signals of the FBSMs of the converter while facing changes in $v_{dc}^*$                                                                           |     |

|       | under ideal conditions                                                                                                                                        | 60  |

| 4.10  | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ while facing changes in $v_{dc}^*$                                                  |     |

|       | under ideal conditions $\ldots \ldots \ldots$ | 60  |

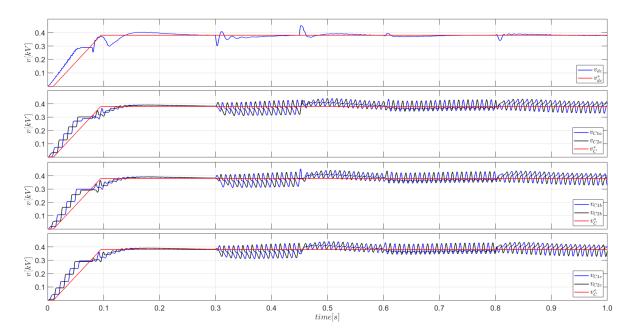

| 4.11  | Dynamic response of the dc-side voltages of the converter and its FBSMs                                                                                       |     |

|       | while facing changes in the external power under ideal conditions                                                                                             | 61  |

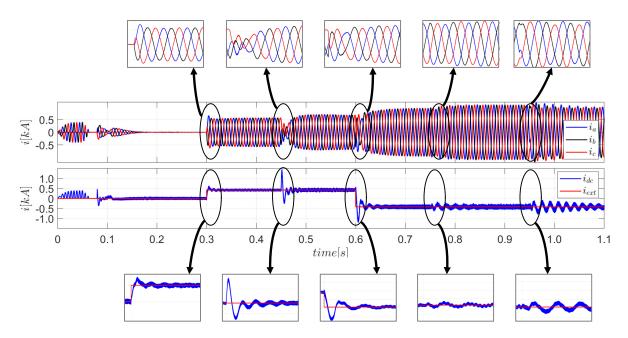

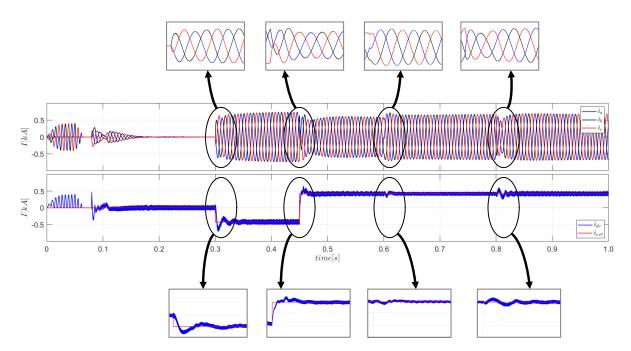

| 4 12  | Dynamic response of the dc- and ac-side current while facing changes in the                                                                                   |     |

| 1.12  | external power under ideal conditions                                                                                                                         | 62  |

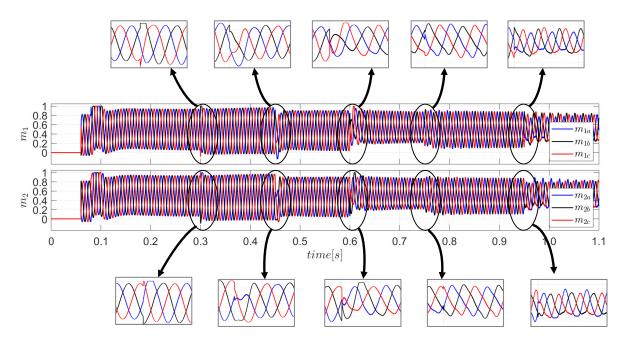

| 4 13  | Modulating signals of the FBSMs of the converter while facing changes in the                                                                                  | 02  |

| т.15  | external power under ideal conditions                                                                                                                         | 62  |

| 1 11  | -                                                                                                                                                             | 02  |

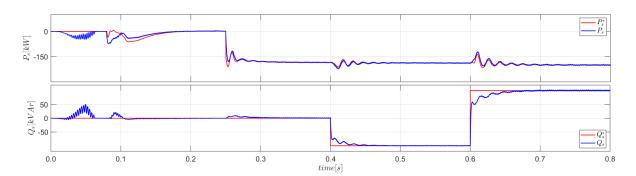

| 4.14  | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ while facing changes in the external power under ideal conditions                   | 63  |

|       | external power under ideal conditions                                                                                                                         | 05  |

| 4.15 | Dynamic response of the dc-side voltages of the converter and the FBSMs while facing changes in the reference value of the reactive power exchanged with the grid under ideal conditions                              | 64       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.16 | Dynamic response of the dc- and ac-side current while facing changes in the reference value of the reactive power exchanged with the grid under ideal conditions                                                      | 64       |

| 4.17 | Modulating signals of the FBSMs of the converter while facing changes in the reference value of the reactive power exchanged with the grid under ideal conditions                                                     | 65       |

| 4.18 | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ while facing changes in the reference value of the reactive power exchanged with the grid under ideal conditions                            | 65       |

| 4.19 | Schematic diagram of the proposed ac/dc converter under asymmetric condition.                                                                                                                                         | 66       |

| 4.20 | Dynamic response of the dc-side voltages of the proposed converter and its FBSMs of the non-ideal converter while facing changes in external power at the dc-side and reference reactive power at PCC.                | 67       |

| 4.21 | Dynamic response of the dc- and ac-side current of the non-ideal converter while facing changes in external power at the dc-side and reference reactive power at PCC.                                                 | 68       |

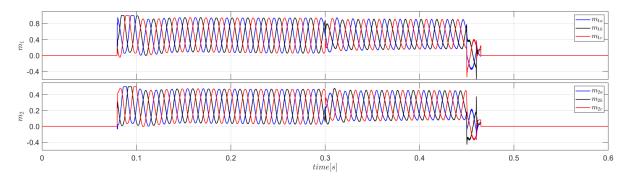

| 4.22 | Modulating signals of the FBSMs of the non-ideal converter while facing changes in external power at the dc-side and reference reactive power at PCC.                                                                 | 68       |

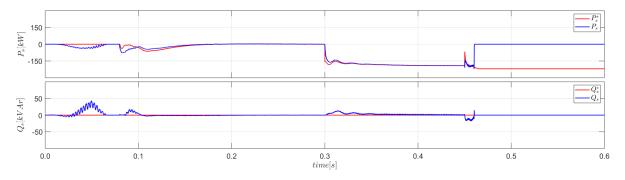

| 4.23 | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ of the non-ideal converter while facing changes in external power at the dc-side and reference reactive                                     | 69       |

| 4.24 | power at PCC                                                                                                                                                                                                          | 69<br>70 |

| 4.25 | Dynamic response of the dc- and ac-side current of the converter, while<br>connected to a non-ideal grid, to the changes in external power at the dc-side<br>and reference reactive power at PCC.                     | 70       |

| 4.26 | Modulating signals of the FBSMs of the converter, while connected to a non-ideal grid, to the changes in external power at the dc-side and reference reactive power at PCC.                                           | 71       |

| 4.27 | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ of the converter, while connected to a non-ideal grid, to the changes in external power at the dc-side and reference reactive power at PCC. | 71       |

| 4.28 | Dynamic response of the dc-side voltages of the converter and the FBSMs of the ideal converter, while subjected to dc-side fault.                                                                                     | 73       |

| 4.29 | Dynamic response of the dc- and ac-side current of the ideal converter, while subjected to dc-side fault.                                                                                                             | 73       |

| 4.30 | Modulating signals of the FBSMs of the ideal converter, while subjected to dc-side fault.                                                                                                                             | 74       |

| 4.31 | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ of the ideal converter, while subjected to dc-side fault.                                                                                   | 74       |

| 4.32 | Dynamic response of the dc-side voltages of the converter and the FBSMs of                              |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | the non-ideal converter, while subjected to dc-side fault                                               | 75 |

| 4.33 | Dynamic response of the dc- and ac-side current of the non-ideal converter,                             |    |

|      | while subjected to dc-side fault.                                                                       | 75 |

| 4.34 | Modulating signals of the FBSMs of the non-ideal converter, while subjected                             |    |

|      | to dc-side fault.                                                                                       | 75 |

| 4.35 | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ of the non-ideal converter,   |    |

|      | while subjected to dc-side fault.                                                                       | 76 |

| 4.36 | Dynamic response of the dc-side voltages of the converter and the FBSMs of                              |    |

|      | the ideal converter, while subjected to dc-side fault                                                   | 77 |

| 4.37 | Dynamic response of the ac-side current of the ideal converter, while subjected                         |    |

|      | to dc-side fault.                                                                                       | 77 |

| 4.38 | Modulating signals of the FBSMs of the ideal converter, while subjected to                              |    |

|      | dc-side fault.                                                                                          | 77 |

| 4.39 | Dynamic response of the $P_{ext}$ , $P_s$ , $P_s^*$ , $Q_s$ , and $Q_s^*$ of the ideal converter, while |    |

|      | subjected to dc-side fault.                                                                             | 78 |

### **List of Tables**

| A.1         | Compensator parameters | • | • | • | • | • | • • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • • | • | • | • | • | • | 82 |

|-------------|------------------------|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|----|

| <b>B</b> .1 | Compensator parameters |   |   |   |   |   |     | • |   |   |   |   |   |   |   | • | • |   |   |   |   | • | •   | • |   |   | • | • | 83 |

# **Convention for Notations**

For clarity and consistency, the following notations are used throughout the presented thesis.

- Circuit parameters are denoted by upper-case letters, for example,  $R_{arm}$ , C, etc.

- Instantaneous voltages, currents and powers are denoted by lower-case letters, for example  $v_{dc}$ ,  $i_{ext}$ ,  $p_g$ , etc.

- Real and reactive powers are denoted by upper-case letters, for example  $P_g$ ,  $Q_g$ , etc.

- dq-transformed variables are denoted by lower-case letters and accompanied by applicable subscript of d or q referring to the d-or q-axis parameter, respectively, for example,  $i_d$ ,  $v_{gq}$ , etc.

- Laplace transformed variables are denoted by upper-case letter and accompanied by (s), for example,  $V_{t\delta q}(s)$

- Subscript  $\delta$  denotes a differential-mode parameter of the converter.

- Subscript  $\sigma$  denotes a common-mode parameter of the converter.

- Subscript *t* denotes a converter phase terminal variable.

- Subscript *g* denotes a converter ac-side variable.

- Subscript *k* denotes phase *a*, *b*, or *c* of the converter.

- Subscript 1 denotes an upper-arm variable.

- Subscript 2 denotes a lower-arm variable.

- Subscript *j* denotes 1, or 2, corresponding to the upper and lower arm of the corresponding leg of the converter.

## **List of Abbreviations**

| DC    | Direct Current                    |

|-------|-----------------------------------|

| AC    | Alternating current               |

| HVDC  | High Voltage DC                   |

| PV    | Photo-voltaic                     |

| LED   | Light Emitting Diode              |

| LVDC  | Low Voltage DC                    |

| kV    | Kilovolt                          |

| MG    | Microgrid                         |

| PCC   | Point of Common Coupling          |

| IGBT  | Insulated Gate Bipolar Transistor |

| CB    | Circuit Breaker                   |

| DG    | Distributed Generation            |

| BESS  | Batter Energy Storage System      |

| EV    | Electric Vehicle                  |

| AES   | All-Electric Ship                 |

| IPS   | Integrated Power System           |

| FACTS | Flexible AC Transmission System   |

| LV    | Low Voltage                       |

| V     | Voltage                           |

| MV    | Medium Voltage                    |

| Hz    | Hertz                             |

| DER   | Distributed Energy Resources      |

| ms    | milliseconds                      |

| EMCB  | Electromechanical Circuit Breaker |

# **List of Abbreviations**

| MCCB           | Molded Case Circuit Breaker                               |

|----------------|-----------------------------------------------------------|

| VSC            | Voltage-sourced converter                                 |

| PWM            | Pulse-width modulation                                    |

| NPC            | Neutral-Point Clamped                                     |

| MMC            | Modular-Multilevel Converters                             |

| PSCAD/EMTDC    | Power Systems Computer Aided Design using Electromagnetic |

|                | Transients including DC                                   |

| FBSM           | Full-Bridge Submodule                                     |

| UPWM           | Unipolar pulse-width modulation                           |

| BPWM           | Bi-polar pulse-width modulation                           |

| PLL            | Phase-Locked Loop                                         |

| EXT            | External                                                  |

| PI Compensator | Proportional-Integrator Compensator                       |

| RHP            | Right-Half Plane                                          |

$v_{dc}$  DC voltage

- $v_{dc}^*$  Reference value of the dc-side voltage

- $v_{gk}$  Grid voltage of the phase k (k=a, b, and c)

- $v_{sk}$  Grid voltage phase k at the point of common connection

- $V_s$  RMS line-to-line ac-side voltage at the POI

- $v_{sd}$  D-axis component of the voltage at PCC

- $v_{sq}$  Q-axis component of the voltage at PCC

- $v_{tk}$  Terminal voltage phase k

- $v_{t1k}$  Terminal voltage of the upper arm FBSM of leg k

- $v_{t2k}$  Terminal voltage of the lower arm FBSM of leg k

- $v_{C1k}$  DC-side voltage of the upper arm FBSM of leg k

- $v_{C2k}$  DC-side voltage of the lower arm FBSM of leg k

- $v_{t\sigma k}^*$  Reference value of the common-mode terminal voltage of the kth leg

- $v_{t\delta k}^*$  Reference value of the differential-mode terminal voltage of the kth leg

- $v_{t\sigma k}$  Common-mode terminal voltage of the *k*th leg

- $v_{t\delta k}$  Differential-mode terminal voltage of the *k*th leg

- $v_{t\delta d}$  D axis component of the differential-mode terminal voltage

- $v_{t\delta q}$  Q axis component of the differential-mode terminal voltage

- *e* equivalent Thevenin voltage seen from the ac side.

- $y_{\sigma k}$  Common-mode dc-side squared voltage of the FBSMs in the *k*th leg of the converter

- $y_{\delta k}$  Differential-mode dc-side squared voltage of the FBSMs in the *k*th leg of the converter

- $\hat{i}$  Ac-side terminal current peak

- $\varphi$  Ac-side terminal current angle

- $i_{dc}$  Dc-side current of the converter

- $i_k$  Ac-side converter current of phase k

- $i_{gk}$  AC grid current of phase k

- $i_{1k}$  Current in the upper arm FBSM of leg k

- $i_{2k}$  Current in the lower arm FBSM of leg k

- $i_d$  Ac-side current d component in dq-frame

- $i_q$  Ac-side current q component in dq-frame

- $i_d^*$  Reference value of the *d* component of the ac-side terminal current in *dq*-frame

- $i_a^*$  Reference value of the *q* component of the ac-side terminal current in *dq*-frame

- $i_{\delta k}$  Differential-mode current of the phase k

- $i_{\sigma k}$  Common-mode current of the phase k

- $i_{\sigma k}^{1*}$  Reference value of the ac component of the common-mode current of phase k

- $i_{\sigma k}^1$  AC component of the common-mode current of phase k

- $I_{\sigma k}^0$  DC component of the common-mode current of phase k

- $i_{DC}$  DC-side current of the proposed converter

- *i*ext External current

- $\tilde{i}_{\sigma k}^*$  Reference small-signal perturbation of the common-mode current of the *k*th leg.

- $\tilde{i}_{\sigma k}$  Small-signal perturbation of the common-mode current of the kth leg

- $\hat{i}^1$  Maximum value of the fundamental-frequency component of the common-mode current

- $m_{\delta d}$  D axis component of the differential-mode modulating signal

- $m_{\delta q}$  Q axis component of the differential-mode modulating signal

- $m_{\delta k}$  Differential-mode modulating signal of the *k*th phase of the converter

- $m_{\sigma k}$  Common-mode modulating signal of the *k*th leg

- $m_{1k}$  Modulating signal of the FBSM in the upper arm of the *k*th leg of the converter

- $m_{2k}$  Modulating signal of the FBSM in the lower arm of the *k*th leg of the converter

- $P_{ext}$  External power

- $P_{dc}$  DC power going through the dc side of the converter

- $P_t$  Ac-side terminal active power

- $P_s^*$  Reference value of the active power exchanged between grid and the converter at PCC

- $P_s$  Active power exchanged between grid and the converter at PCC

- $P_{loss}$  Power loss in the converter

- $P_{1k}$  Rate of change of energy stored in the dc-side capacitor of the FBSM in the upper arm of the *k*th leg of the converter

- $P_{2k}$  Rate of change of energy stored in the dc-side capacitor of the FBSM in the

- $P_{\sigma k}$  Common-mode active power of the FBSMs in the *k*th leg of the converter

- $P_{\delta k}$  Differential-mode active power of the FBSMs in the *k*th leg of the converter lower arm of the *k*th leg of the converter

- $Q_t$  Ac-side terminal reactive power

- $Q_s^*$  Reference value of the reactive power exchanged between grid and the converter at PCC

- $Q_s$  Reactive power exchanged between the grid and the converter at PCC

- $Q_c$  Reactive power delivered by the capacitor of the LCL-filter at the PCC

- $f_g$  Grid frequency

| $f_{sw}$               | Switching frequency of the converter                     |

|------------------------|----------------------------------------------------------|

| ω                      | Grid angular frequency                                   |

| $oldsymbol{eta}_k$     | Initial phase angle of $i_{\sigma k}^1$                  |

| $oldsymbol{\gamma}_k$  | Phase displacement between $i_{\sigma k}^1$ and $v_{sk}$ |

| С                      | DC-side capacitor of the converter and its FBSMs         |

| L                      | Arm inductance                                           |

| R                      | Arm resistance                                           |

| $L_g$                  | Grid inductance                                          |

| $R_g$                  | Grid resistance                                          |

| $L_{f}$                | AC-side filter's series inductance                       |

| $R_f$                  | Ac-side filter's series resistance                       |

| $C_{f}$                | Ac-side filter's shunt capacitance                       |

| $R_{fd}$               | Ac-side filter's damping resistor                        |

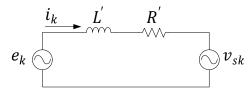

| $L^{'}$                | Equivalent inductance as seen from the PCC               |

| $R^{'}$                | Equivalent resistance as seen from the PCC               |

| <i>r</i> <sub>on</sub> | Online resistance of each switch                         |

| $K_{i\sigma k}(s)$     | Common-mode current controller of the <i>k</i> th leg    |

| $K_{VDC}(s)$           | DC-side voltage controller of the proposed converter     |

| $K_{p\sigma k}(s)$     | Common-mode FBSM power controller                        |

| $K_{P\delta k}(s)$     | Differential-mode FBSM power controller                  |

| $K_d(s)$               | D-axis ac-side current controller                        |

| $K_q(s)$               | Q-axis ac-side current controller                        |

|                        |                                                          |

- BRK1 Breaker 1, connecting the ac-grid to the POI of the proposed converter

- *BRK*2 Breaker 2, connecting the POI of the proposed converter to its terminal through the low-resistive path

- *BRK*3 Breaker 3, connecting the POI of the proposed converter to its terminal through the high-resistive path

# Chapter 1 Introduction

### **1.1 Background and Motivation**

In late 1880s and early 1890s, *Thomas Alva Edison* and *George Westinghouse* publicly debated their proposed power transmission systems, i.e., direct-current (dc) based and alternatingcurrent (ac) based power transmission systems, respectively. The aforementioned debate is known as the *battle of currents* in the literature. The result of the battle of currents was strongly influenced by the invention of a number of breakthrough ac-based devices by Nikola Tesla, and led to the global acceptance of ac-based power system as the main architecture for electricity generation, transmission, and distribution [1]. However, in the past couple of decades, dc-based systems started to return as high-voltage dc transmission systems (HVDC), especially for long distances due to their economical, technical, and environmental advantages[2]. Large-scale integration of renewable energy resources is another major influencer in the return of HVDC systems [3]. It must be mentioned that the invention of transistors had a great impact on the come-back pace of the dc systems. Although, initially, transistors were designed for the applications in computers and communications, as a by-product, they have enabled the transformation of dc voltages, and caused a revolution in power electronics [1].

Over the past two decades a number of trends in the electric power systems, has directed the attention to the use of dc in lower voltage levels. Among the most important trend the growth in photovoltaics (PV)-based power generation, rising interest in the LED lighting, and increasing focus on the sustainable and efficient energy leading to a shift from fossil fuel as the main source of electric power generation can be named [7]. Furthermore, the escalating interest in renewable and distributed generation systems, is another influencer in the growth of low-voltage dc systems [4]. In comparison to the available ac systems, LVDC has a higher power transmission capacity, no need for source synchronization, and doesn't have skin effect associated with it. Furthermore, LVDC networks can reduce the conversion losses by eliminating the redundant conversion stages for distributed renewables which inherently generate dc power [6]. Perhaps one of the earliest applications of low-voltage direct current (LVDC) in recent years, started in 2005 in Finland, with the development of 1-*kV* intermediate LVDC distribution systems [5]. Employing dc systems can also benefit the customers which require dc, by eliminating the conversion stage. Fig. 1.1 presents some of the applications of dc in today's electricity market and the required voltage range for those applications [7].

Figure 1.1: Voltage range for a number of dc application in today's electricity market[7].

Fig. 1.2 presents an example of a basic implementation of the LVDC system which is connected to the ac grid. The aforementioned connection between the dc and ac grid is done through the use of an ac/dc converter, which can be considered as one of the most critical components [11] and [12]. So far, the merits of the LVDC networks were discussed, but it must also be mentioned that LVDC systems have significant technical challenges associated with them in terms of dc-side fault detection and isolation [13]. None the less, ac-distribution systems also have their own merits, like the ability to use transformers, and mature technology of ac circuit breakers [8]. Thus, hybrid ac/dc electrical network through capitalizing the advantages of both ac- and dc-distribution systems is an answer to the needs in today's market [9] and [10]. The aforementioned networks must be interconnected and allow the bidirectional power flow between ac and dc grids. Furthermore, there have been many arguments addressing one of the most important shortcomings of dc grids, i.e., the lack of effective and economical faulthandling capability for dc systems. The proposed solutions can be mainly categorized in two groups: using DC circuit breaker or dc-fault tolerant converters [14]. The focus of this thesis is to propose a new topology and control method for a bidirectional ac/dc converter, with the dc-side fault handling capability.

This chapter, focuses on outlining the merits, problems, and structures of dc distribution and ac/dc power-converter systems. Followed by listing the problems which are addressed in

Figure 1.2: Concept of an LVDC distribution system [5].

the thesis, a literature survey of related prior work done in this area, and the scope of the thesis.

#### **1.2** Statement of Problem and Overall Thesis Objectives

The use of dc networks in distribution systems is an emerging concept and not fully grown. Increasing presence of distributed generation and loads with strict power quality requirements, along with the interest to make the grid more resilient have impacted the characteristics of the traditional distribution systems, and has led to the increase in the popularity of LVDC systems, as they offer several advantages compared to LVAC grids [21]. The mentioned dc systems might even offer the ability to form an isolated power system which is known as microgrid (MG) in the literature [15]. However, even in that case the LVDC microgrid must be connected to its host ac grid through power converters. The connection between the dc and ac system is done through power converters and at the point of common coupling (PCC) [23]. Thus, power converters are responsible for the direction of the power flow. Previously and in the absence of a considerable distributed energy sources such as photovoltaics (PVs), fuel cell and etc. it would've been safe to assume a uni-directional power flow from the ac grid to the dc network. Never the less, with the growing interest in employment of DERs, the power must be able to transfer in both direction which requires a bi-directional converter.

It goes without saying that using LVDC networks, the behavior of the system during the normal operation and in presence of faults, defers from the conventional ac grid. Although, previously the dc section used to have limited extensions and as a result the probability of occurrence of a dc-side fault was considerably low and almost negligible, in recent years the LVDC networks are becoming much more complex and contain more extensions which further signifies the fault related problems on the dc system. The aforementioned issues need to be dealt with by proper and economical protection schemes. In contrary to the protection

technology designed for ac power systems, which is fully grown, achieving appropriate protection for dc power systems is still a challenge [22]. Most commonly suggested protection methods against dc-side faults at PCC are employing dc circuit breaker (CB) or incorporating fault-tolerant converters. At the connection point of ac and dc distribution systems it is desirable to have a bidirectional power flow, and thus bidirectional ac/dc converter using insulated gate bipolar transistor (IGBT) modules are mainly used. Morover, employment of bidirectional ac/dc converters with IGBT modules further complicates the protection system design due to their sensitivity to over-currents and their requirement for fast protection [23]. Although each one of the mentioned methods has a host of merits associated with it, this thesis focuses on the latter approach and presents a bidirectional ac/dc converter with the ability of blocking pole to pole and pole to ground short circuit faults at its dc-side terminal.

### **1.3** Literature Survey Pertinent to the Thesis Objectives

There are a number of literature currently available which investigate the structure and benefits of the low-voltage dc systems in comparison to its equivalent ac system, the problems associated with the mentioned LVDC systems [17] to [19], and topology of the front-end converters as a key equipment in LVDC. This section first presents a brief comparison between the low-voltage ac and dc grid, followed by further analyzing one of the biggest challenges in designing a complex LVDC system, i.e., the ability to handle the faults and the protection methods previously discussed in the literature. This section then moves on to exploring a number of previously proposed ac/dc converters and their effectiveness as a front-end converter in a LVDC system.

#### **1.3.1** AC Versus DC Distribution Systems

Introduction of LVDC systems begins with addressing a number of available areas in the current distribution system infrastructure, in which the main ac-based power system has a number of shortcomings. In this subsection, first these areas are presented along with the merits of both dc- and ac-distribution systems in addressing the aforementioned problems.

- Energy Storage, Distributed Generation, and Micro-grids: In recent years, the trend in the growth of electric power system has increasingly been going towards distributed generations (DGs), since they can lead to efficiency improvement in the system by producing the required energy in distributed manner and close to the demand and thus eliminating the transmission losses [8]. Employing dc system provide the opportunity for a more straightforward integration of distributed energy resources such as PVs, fuel cells, wind, battery energy storage systems (BESSs), etc. [24]. The mentioned dc systems can offer the ability to work independent from the main grid and in islanded mode and form a dc microgrid, which in comparison to the ac microgrid they are less costly while they can benefit from the other advantages of the LVDC systems [20].

- Increasing Application of Electric Vehicles: In recent years, there was a greath growth in the interest in electric vehicles (EVs), including fully electric vehicles and plug-in hybrid electric vehicles, due to the ecological aspects [25] and [26]. Increase in the

number of charging stations, can be named as one of the leading reasons in the growth of the EVs [27]. Furthermore, employing EVs can provide a potential to improve the grid resiliency and assist balance loads. [8] whilst it offers higher efficiency and less noise in comparison to the traditional gasoline vehicles [28].

- Computers, Lighting, and Home Electronics: Electric appliances in homes using power converters such as fridges, freezers, dish washers, washing machines, and modern air conditions, LED lighting, space and water heating with heat pumps or direct heating, etc. could be directly fed by dc power [3]. In the current configuration, each load has its own power supply. However, employing dc distribution systems can eliminate the redundant conversion of power from dc to ac and then back to dc, again [8].

- Shipboard Power Systems: In recent years, increasing the strictness on the government regulation of emissions while customers' fuel-efficiency requirements have risen, has led to the current trend toward the all-electric ship (AES). The most significant feature of the AESs is the concept of the integrated power system (IPS), which minimizes the number of generators in ships and it can be regarded as a large-scale, on-board microgrid [29].

DC-distribution power systems has properties that makes it more suited to address the aforementioned areas than ac-distribution systems. The mentioned properties can be categorized as follows

- **Incorporation of Renewable Energy Resources:** By using dc-distribution system, the incorporation of the renewable energy sources becomes much more simpler. The ease of connecting the renewable energy sources to a dc-distribution system can be justified by the fact that in order to connect an energy source to a dc system only the voltage has to be monitored and controlled. However, connecting renewable energy sources to the ac system requires the voltage magnitude, frequency and phase must match [30].

- Reliability and Un-incorruptible Supplies: Buildings such as hospitals and special offices such as banks and data centers are categorized as critical loads and require a "24-7" access to the electric power. Thus, special measures must be taken to ensure the smooth access to the electricity for critical loads. One measure is to utilize decentralized generation scheme instead of the more traditional centralized generation. By doing this more sources can be integrated to the network at various locations and closer to the critical loads [31]. The aforementioned measure can be done both using ac or dc power systems. However, in comparison to ac solutions, dc measures contain fewer conversion staged and thus increasing efficiency [30]. DC also enables connection of various sources [7] and enables the easy incorporation of more local energy storage and sources, either standby power generation, which are used when a fault occurs on the utility grid or distributed generation which can even work continuously [30].

- Voltage Stability: One of the key components in dc power systems are the power electronic converters. Depending on the type of the converter being used at the point of common coupling of ac and dc grid, it might be possible to control the reactive power

flow independently and according to the requirements of the system in order to achieve the required voltage stability and eliminating the use of other equipment with the sole purpose of controlling the reactive power flow such as capacitor banks and FACTS [8].

- Lighting and Home Electronics: As it was previously mentioned there are a number of equipment in the residential and commercial buildings which inherently uses dc power. Apart from the typical equipment such as freezers, dishwasher and etc. the fluorescent lighting electronic ballasts also require dc power [8]. These devices typically include a rectifier inside them which lets changed their ac input to the required dc. Thus, by building dc buildings all of those unnecessary power conversion stage will be eliminated. As a result, in recent years the possibility of dc homes have been the subject of many researches.

- **Power Quality:** Reactive power consumption and low-frequency current harmonics are two of the issues associated with power quality in traditional ac grids [7]. The power factor correction is one of the performed stages of dc power supplies. This will address the power quality problems associated with the consumption of reactive power. Moreover, by employing accurate design practices and filtering acceptable harmonic quality is also achievable [8].

- Larger Power Transfer: The low-voltage (LV) range for ac and dc systems are 5 1000 V ac and 75 1500 V dc, respectively. Thus, low-voltage dc systems have the ability to transfer larger power in comparison to low-voltage ac system. Moreover, since no reactive power is transferred through the dc grid, the losses are also reduced. The aforementioned property make it possible to even replace the low-power branch of the medium-voltage (MV) ac network by low-voltage dc distribution networks [38].

- **50/60-Hz Concerns:** Employing the dc-power system will lead to elimination of the potential health concerns of being exposed to 50/60-Hz ac-power systems [61].

The ac distribution networks also have its own advantages a number of which are mentioned in this part:

- Voltage Transformation: Historically the main advantage of the ac over dc is the ability to change the voltage levels in an ac systems through transformers [8]. However, even with the current developments in the field of power converters, still these solutions can be much more costly than a transformer.

- Circuit Breaker Protection: One of the most important aspects of any power system is its reliable operation. In case of ac distribution systems, circuit protection is more mature than that of dc systems. Moreover, periodic zero voltage crossings in ac systems greatly benefits the circuit protection of ac circuits. Since, during the zero crossing of the voltage, circuit breakers will have a better likelihood to extinguish a fault current arc [8].

Considering the advantages and shortcomings of both dc and ac distribution systems, and the maturity of current ac distribution system, one can conclude that the best approach is to

form a dc distribution system, in parallel with the current ac distribution system and connect them to one another wherever it's needed. As a result, the advantages of both systems can be used while trying to avoid their demerits.

#### 1.3.2 Previously Proposed Protection Scheme for LVDC Systems

One of the critical issues associated with LVDC networks is designing a reliable protection system. Historically, LVDC systems used to be less complex, and as a result it was less likely to have a fault at the dc network. Furthermore, due to the lack of significant distributed energy resources (DERs) and simplicity of the LVDC networks a bidirectional power flow at the PCC was not a necessity, which enabled the use of grid-connected rectifiers with current limiting capabilities. However, due to the changes in the infrastructure of the distribution systems, the LVDC systems are becoming more complex, which leads to new requirements for the system, one of which is the ability to effectively detect and clear the dc-side faults [23].

Both the problems associated with interrupting faults without having natural zero crossing points, which is the case for the ac, and changes in the nature and transient response of the faults which are a consequence of employing complex LVDC networks, have made it more difficult to handle the dc-side faults. Previously done research in this area ([46] - [47]) show that a dc-side fault at terminals of a converter can result in a high short-circuit transient current with a magnitude of up to 35 times the steady-state fault current, and a duration of less than 4 *ms*. As a result, a significant thermal energy  $(I^2t)$  will flow through the network components. Hence, in the absence of an effective fault-current limiting device, the ratings of the components in the network must be higher, which in turn increases the costs of the plant [47].

There are a number of methods proposed in the literature to eliminate the dc side faults. These methods are briefly explained here.

- Measuring the dc-side voltage and current and operating the ac-side breakers during the faults: This method is an economical way to deal with the dc-side faults an is mostly used in HVDC systems. However, employing this method for dc distribution system leads to disconnecting the entire network from the grid until the available fast acting mechanical switch available on the dc system reconfigure the dc lines. Consequently, using the mentioned method can lead to problems associated with power quality and load stability [47].

- Create zero-crossing points for dc fault currents: This method employs a series reactor with the conventional electromechanical circuit breaker (EMCBs) on the dc side, to limit the magnitude of the dc-side fault current, and by causing it to oscillate create a zero crossing which then leads to fault current interruption by the EMCB during the first zero crossing. However, this method is not as reliable for high impedance faults, which require large reactors. Furthermore, addition of more reactance will increase the fault stress which is a result of releasing larger stored energy during the fault [47].

- Direct elimination of dc-side fault using equipment that do not require zero crossing points: Using fuses and EMCBs such as molded case circuit breakers (MCCBs), the fault current can be eliminated without using the zero-crossing points. However, the aforementioned devices have slower operation for dc in comparison to ac systems. As a

result these methods will not be able to protect the converters and other sensitive devices against the transient period of the discharge of the capacitors, and thus requires higher ratings for the devices. Moreover, the high transient current will also cause the dc-voltage to rapidly drop to zero and converters loosing the control. Furthermore, the undervoltage conditions during the transient period will make it more difficult to maintain the stability of local micro generators and avoid sympathetic tripping against remote dc faults [47].

Hence, there is a lack of fast yet mature and effective protection method for LVDC systems. As a result, recently more attention is payed to designing a converter with the ability to tolerate the faults at its dc side [48], which is the focus of this thesis.

#### 1.3.3 Converter Typologies and DC-Side Fault Tolerability in Distribution-Level DC Systems

So far a number of advantages of the dc and ac distribution systems have been presented, and it was concluded that by building the two systems in parallel to each other the merits of both can be taken advantage of. It must be mentioned that these systems must be able to connect to each other at various locations, which is done through the use of power electronic converters. Thus, one of the key enabling components towards the realization of building a dc-distribution system along side the currently available low and medium voltage ac system, is the power-electronic converter. Moreover, as it was mentioned in the previous section, designing converter topologies with the ability to tolerate dc-side faults, will further solve the issues associated with the currently employed protection system for LVDC networks. There are various topologies suggested in the literature that would satisfy one or both network requirements previously mentioned in this chapter, i.e., bidirectional power flow and the ability to tolerate dc-side fault. This section of the thesis presents a summary of the aforementioned converter topologies which ranges from a thyristor bridge which is one of the most simple and economical solutions, to more complex designs like neutral-point clamped VSCs.

- Three Phase Thyristor Rectifier: One of the most basic and economical ac/dc converters is the thyristor rectifier which converts the ac input to a constant polarity dc. Figure 1.3 illustrates the schematic diagram of a three-phase thyristor rectifier. As it an be seen from Fig.1.3, the thyristor rectifier is a diode rectifier, where the diodes are replaced with thyristors. This converter is able to create a unidirectional power flow from the ac to dc system and can be used in feed and control of the dc motors among other applications. Since the thyristors do not let the current to pass in the reverse direction and there is no anti-parallel diodes in this scheme, the thyristor rectifiers have the ability to tolerate the dc-side faults. However, since thyristor rectifiers cannot enable the reversal of power flow, they can't be used as front-end converters in recent and more complex dc distribution systems with distributed generation. Moreover, they result in relatively high harmonics in the dc-side current and they require a transformer at their ac side in order to be able to change their ac-side voltage to the ac-grid voltage level and connect the converter to the grid, [32].

- Voltage-Sourced Converter: Figure 1.4 presents the schematic diagram of a three-phase voltage-sourced converter. Typically, in power-system applications the VSC is inter-

Figure 1.3: Schematic diagram of a thyristor rectifier.

faced with the ac grid through a transformer using a VSC as a front-end converter the bi-directional power flow from the ac grid to the dc side and vice versa. As it can be seen from Fig. 1.4 the VSCs consist of switches composing of anti-parallel connection of a fully controllable unidirectional switch and a diode [43]. The commutation of the aforementioned switches can be achieved through different modulation schemes, like pulse width modulation (PWM), and thus produces a low harmonic contribution. Moreover, using VSC the reactive power flow can be controlled independently. Hence, it has the ability to control the power factor and thus improving the voltage stability of the system. The applications of VSCs include HVDC light transmission, ac/dc converter in drives, and front-end converter in LVDC microgrids [32]. Hence it can be concluded that by employing a pulse width-modulated (PWM) voltage-sourced converter (VSC) operated as a controlled dc voltage power port the aforementioned shortcomings of the thyristor rectifier can be avoided.

However, upon occurrence of a fault at the dc-side of the VSC the dc-side capacitor will start to discharge which causes a fault current with a high magnitude and low rise time, and small duration. Furthermore, once the dc-link voltage drops to almost zero, which is the case during a short-circuit fault, the converter loses its capability to control the current. Consequently, fault current will start to go through the anti-parallel diodes of the isolated gate bipolar transistors. As a result, VSCs are vulnerable to dc-side faults, which in turn makes them unsuitable for current dc distribution systems [23].

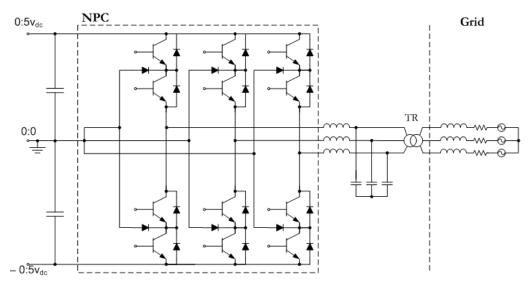

• Neutral-Point Clamped (NPC) VSC: As it can be seen from Fig. 1.5 NPC is a combination of two-level half-bridge converters and two additional diodes. Similar to what has been previously mentioned regarding VSCs, NPCs not only have the ability to allow the bidirectional power flow, but also use various modulation schemes, like PWM, and thus result in low harmonics on the dc-side current. Neutral-point clamped (NPC) converters also require transformer at their ac side in order to connect to the ac grid [43]. Moreover, as it can be interpreted from Fig. 1.5, the NPC topology also results in bipolar dc-side

Figure 1.4: Schematic diagram of a three-phase, two-level voltage-sourced converter.

voltage. However, the same short circuit fault analysis previously described for VSCs can be applied to the NPC converters. Furthermore, the pole-to-ground short-circuit fault can travel through the clamping and anti-parallel diodes [48]. Consequently, similar to what was discussed for the VSCs, the ratings of the power electronic devices available in NPC converters must also be selected higher than what is required for normal applications, in order to be able to tolerate the thermal energy released during the short circuit faults and in absence of an effective protection scheme against the dc-side faults.

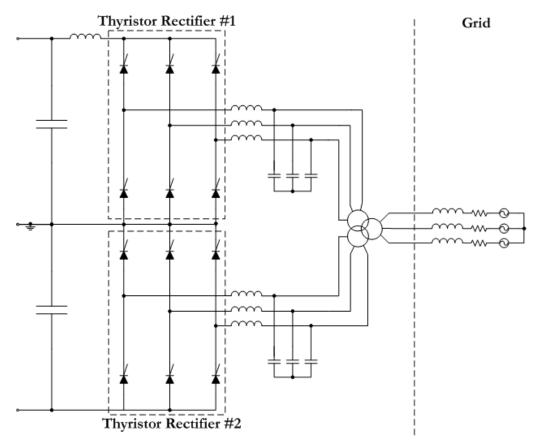

• 12-Pulse Thyristor Rectifier: Figure 1.6 shows the typical configuration of a 12-pulse series-type thyristor rectifier, which consists of two identical six-pulse thyristor rectifiers. Hence, by employing the 12-pulse thyristor rectifiers, the merits of the simple thyristor converter including its ability to tolerate the dc-side fault is achievable. Furthermore, the dc-side current harmonics will be less than the 6-pulse thyristor rectifier, presented in Fig. 1.3, and results in bipolar dc-side voltage. However, in comparison to VSC and NPC, the

Figure 1.5: Schematic diagram of a three-level NPC.

dc-side current of the 12-pulse thyristor rectifier will still be considerably higher. It must also be mentioned that the 12-pulse thyristor rectifier requires a three-winding rectifier in order to be connected to the ac grid.

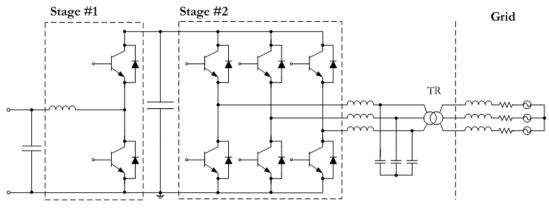

• **Two-stage VSC:** Previously the single-stage two-level VSC topology was analyzed, and it was outlined that one of the major problems associated with these type of the converters is their vulnerability to the dc-side faults. Hence, a new updated topology is presented here, which enables the user to benefit from the advantages of a typical single-stage VSC while providing protection against dc-side faults. The proposed design is a modified version of the discussed design in [33], where the H-bridge converter available in the second stage was replaced with a VSC. This design not only provides a path for bidirectional power flow between the ac and dc systems, and provides low harmonic output, but also is able to limit the short circuit current and behave as an electric dc breaker [33]. Figure 1.7 presents the discussed converter's topology. As it can be seen from the mentioned figure, the proposed two-stage converter consists of a series connection of a buck and VSC as the first and second stage of the converter, respectively. Furthermore, the presented two-stage VSC also leads to a reduction of the size of the dc-link capacitor [33]. However, all of the aforementioned merits are achieved by sacrificing the efficiency of the converter. Although employing a synchronous buck converter instead of a typical buck converter with diodes will lead to an increase in the overall efficiency, but it is still

Figure 1.6: Schematic diagram of a 12-pulse thyristor rectifier.

Figure 1.7: Schematic diagram of the proposed two-stage VSC in [33].

less than a single-stage VSC [49].

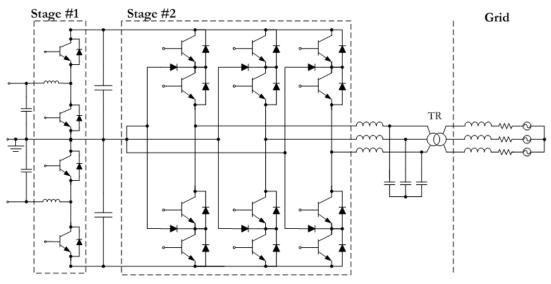

- **Two-stage NPC VSC:** Using the same strategy proposed for a two-stage VSC, a two stage NPC VSC can be designed, which is presented in Fig. 1.8. As it can be seen from Fig. 1.8 the two-stage NPC converter consist of cascading a step-down converter with the NPC converter shown in Fig. 1.5. Although, the aforementioned topology has the ability to tolerate dc-side faults, as well as offering the rest of the merits of the NPC, which were mentioned earlier, it consists of two stages, which in turn leads to decrease in the efficiency of the converter.

- Series-type two-stage VSC: As it can be seen from Fig. 1.9, series-type two-stage VSC analyzed here consists of the series connection of the sample two-stage VSC presented in Fig. 1.7. By employing the aforesaid settings, as well as benefiting from all the previously discussed advantages of the two-level VSCs, the bipolar dc side voltage can be achievable. However, a three-winding transformer is required in order to connect the

Figure 1.8: Schematic diagram of the proposed two-stage NPC VSC.

aforementioned converter to the ac-grid.

As it can be realized from the above explanations, majority of the most common ac/dc converters, used in LVDC systems, either are not able to tolerate the dc-side faults or have been upgraded to multiple-stage converters in order to achieve tolerance for such fault. Consequently, they have lower efficiencies. Furthermore, some of the topologies can not be used as a front-end converter in complex dc systems, as they do not offer bidirectional power flow between the ac and dc systems. As a result, this thesis proposes a unique single-stage bidirectional ac/dc converter, with the ability to tolerate faults at its dc side. The initial idea for this converter came from the design of the modular-multilevel converters (MMCs), which are wildly used in HVDC systems, [50] - [52].

### 1.4 Methodology

In order to achieve the objectives of this thesis, first a bidirectional ac/dc converter topology is proposed, whose structure makes it tolerant against dc-side short circuit faults. After mathematical modeling and achieving the effective controller design, the proposed converter was modeled in detail in the power systems computer aided design using electromagnetic transients

Figure 1.9: Schematic diagram of the series-type two-stage VSC.

including dc (PSCAD/EMTDC). The model is then used in order to evaluate the performance of the ac/dc converter and the effectiveness of the proposed control schemes through a number of case studies, using PSCAD/EMTDC software environment.

### **1.5** Thesis Contribution and Scope

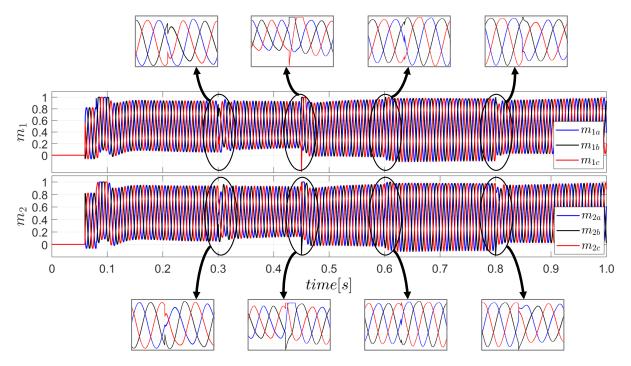

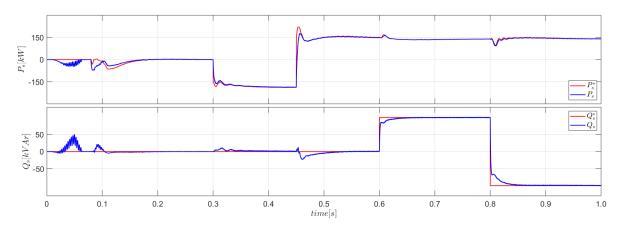

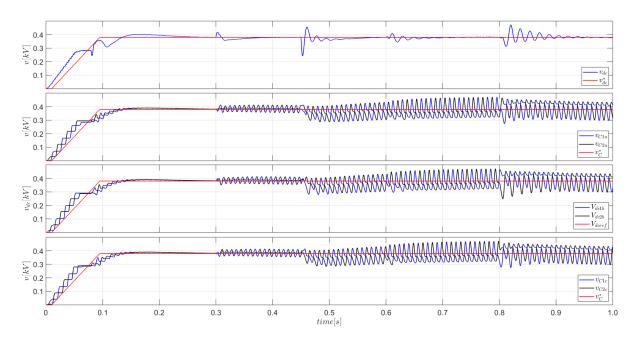

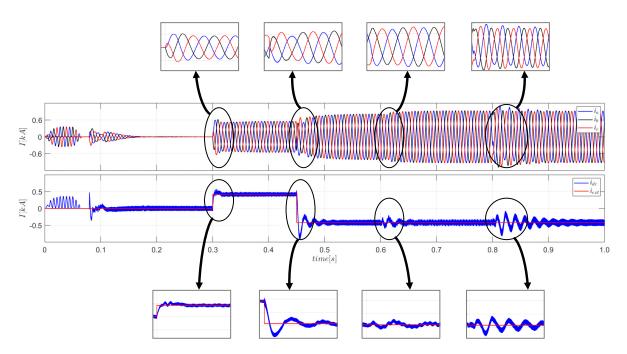

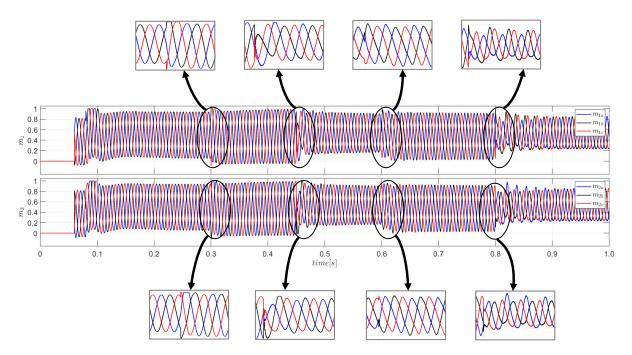

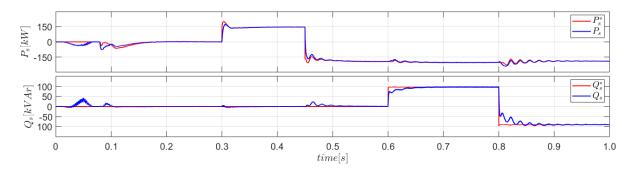

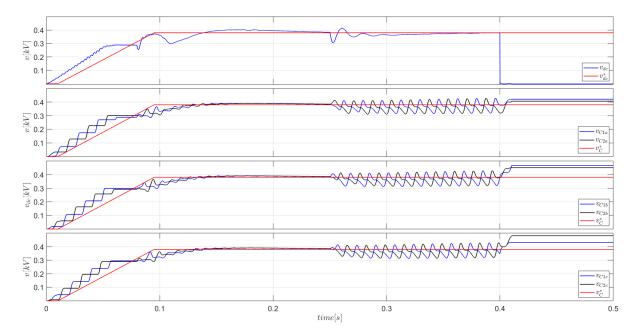

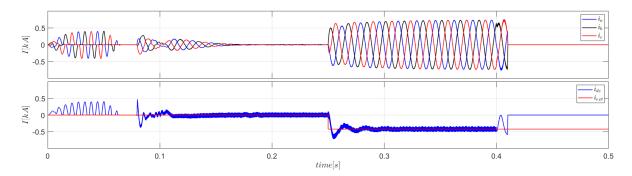

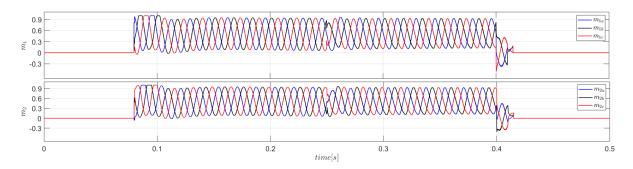

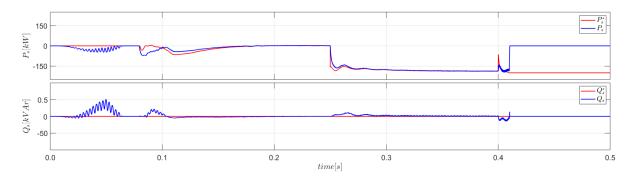

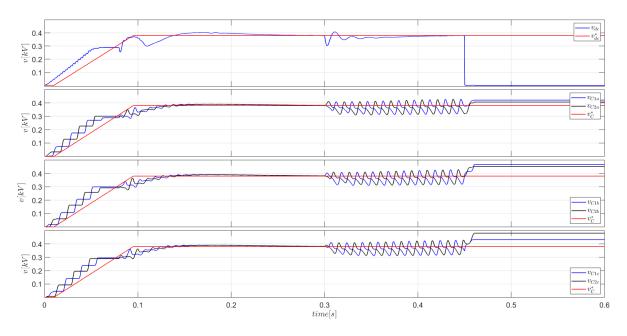

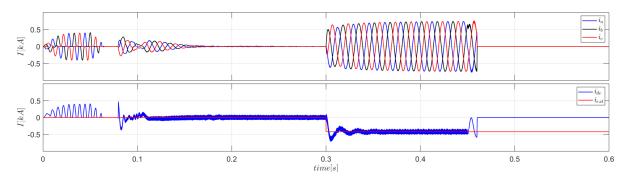

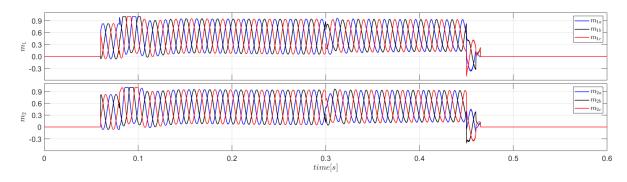

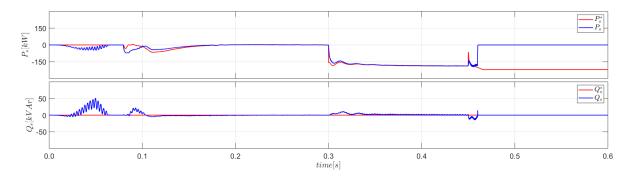

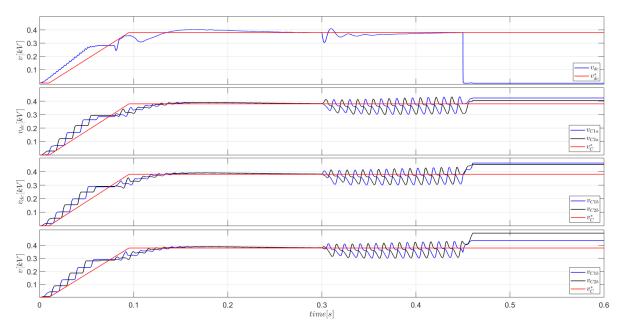

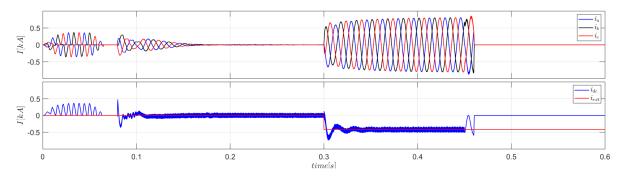

As it was outlined in this chapter of the thesis, the protection of the low-voltage dc systems against short circuit currents is a challenge and although there are a number of methods currently proposed in the literature the lack of a mature, economical and effective protection method can still be seen. Among the proposed techniques, one can name the utilization of a converters with the ability to tolerate dc-side faults. Furthermore, by increasing the complexity of the LVDC systems, which is a result of the growing interest in DERs and microgrids, among others, having the possibility of bidirectional power flow between the ac and dc grid is a necessity. As a result, this thesis focuses on addressing the aforementioned challenge/requirements, and proposes a new topology and control method for a bidirectional ac/dc converter which can tolerate the dc-side faults.