#### ADAPTIVE EMBEDDED TECHNOLOGIES: HARDWARE ACCELERATION

By: Ryan Meghdies-Vardeh

Computer Engineering, BEng Ryerson University, Toronto, Canada, 2012

A thesis presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Applied Science in the Program of Electrical and Computer Engineering

> Toronto, Ontario, Canada, 2015 ©Ryan Meghdies-Vardeh 2015

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public

Adaptive Embedded Technologies: Hardware Acceleration Master of Applied Science, 2015 Ryan Meghdies-Vardeh Electrical and Computer Engineering Ryerson University

### ABSTRACT

This thesis establishes the benefits of multi-architecture systems by using reconfigurable modules in conjunction with a case integration strategy to improve system performance. The modules and strategies discussed in this thesis provide opportunities to the improve system performance of processing units designed for the consumer market.

The primary objective for this work is to improve the performance of consumer processors using programmable logic, while ensuring the changes are abstracted from operating systems and software applications. This thesis accomplishes this using specified integration strategies, protocols and through optimization of device drivers.

iii

### ACKNOWLEDGMENTS

First and foremost I thank my family for their motivation and pushing me to be the ambitious and creative man I am today.

There have been a number of notable educators who have inspired me and helped guide me through my undergrad and post-graduate studies. Dr. Vadim Geurkov has worked with me over the last 4 years. With his supervision, I was awarded a bronze medal for my undergraduate project. More recently, he has helped inspire and guide me with the work in this thesis and that found in [1]. Dr. Lev Kirischian provided an academic foundation for which my research began and provided opportunities which helped me pursue my areas of interest.

Finally, I would like to thank AMD who gave me an opportunity to work with cutting edge hardware design and design verification methodologies. In particular my mentor Darlington Opera who helped train me and challenge me and Behrooz Karimian who worked with me in endeavours related to the inventions found in this thesis.

iv

# TABLE OF CONTENTS

| AUTHOR                  | 'S DECLARATION                           | ii   |

|-------------------------|------------------------------------------|------|

| ABSTRAC                 | Т                                        | iii  |

| ACKNOW                  | LEDGMENTS                                | iv   |

| LIST OF 1               | CABLES                                   | vii  |

| LIST OF F               | IGURES                                   | viii |

|                         | APPENDICES                               |      |

|                         | JCTION                                   |      |

|                         | tual Property                            |      |

|                         |                                          |      |

|                         |                                          |      |

| -                       | R I<br>OTIVATION                         |      |

|                         | BJECTIVE                                 |      |

|                         | FFECTIVE CONTRIBUTIONS                   |      |

|                         | HESIS ORGANIZATION                       |      |

|                         |                                          |      |

| -                       | R II:<br>ACKGROUND                       | _    |

| <b>2.1 Б</b> /<br>2.1.1 | Insight Into Modern Applications         |      |

| 2.1.1                   | Implementation                           |      |

| 2.1.2                   | Verification Tools                       |      |

| 2.1.4                   | ASIC & FPGA Architectures                |      |

| 2.2 F(                  | OUNDATION OF MODERN RESEARCH             |      |

| 2.2.1                   | Reconfigurable Technology                |      |

| 2.2.2                   | Existing DPR Applications                |      |

| 2.2.3                   | Theoretical DPR Gains                    |      |

|                         | KISTING METHODS & TECHNIQUES             |      |

| 2.3.1                   | Intel Develops FPGA-Based Coprocessors   |      |

| 2.3.2                   | Existing Mixed Chips                     |      |

| 2.3.3                   | Embedding ARM Processors Into FPGAs      |      |

|                         | R III:                                   |      |

| 3.1 CO                  | OMPARATIVE ANALYSIS OF EXITING SOLUTIONS |      |

| 3.1.1                   | Coprocessor Systems – FPGAs + CPUs/GPUs  |      |

| 3.1.2                   | System Customization                     |      |

| 3.1.3                   | Hardware Acceleration                    |      |

| 3.1.4                   | Protocols & Flashing                     |      |

| 3.1.5                   | Custom SOC                               |      |

| 3.1.6                   | Power Advantages                         |      |

| 3.1.7                   | Life Time                                |      |

|                         | ODIFYING THE APPROACH                    |      |

| 3.2.1                   | Hardware Acceleration Islands            |      |

| 3.2.2                   | Internal Connections                     |      |

| 3.2.3                   | Pre-emptive Hardware Adaptation          |      |

| СНАРТЕ                  | R IV:                                    |      |

| <b>4.1 De</b> | monstrating Performance                   |     |  |

|---------------|-------------------------------------------|-----|--|

| 4.1.1         | Reconfigurable Hardware Benefits          | 62  |  |

| 4.1.2         | Improved Application Performance          | 64  |  |

| 4.1.3         | Modern Design Technique                   | 70  |  |

| <b>4.2</b> Au | tomated System Adaptation Capabilities    | 71  |  |

| 4.2.1         | Manually Calculated Optimization Strategy | 72  |  |

| 4.2.2         | Specifications of System                  | 73  |  |

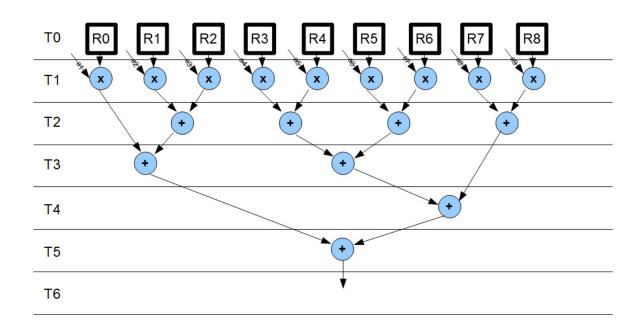

| 4.2.3         | System Sequencing Graph                   | 76  |  |

| 4.2.4         | Evaluating System Options                 |     |  |

| 4.2.5         | Mini-Max Variant                          |     |  |

| 4.2.6         | Min Resource Analysis                     |     |  |

| Calcula       | ations:                                   |     |  |

| 4.2.7         | Max Resource Analysis                     |     |  |

| 4.2.8         | Critical Variant                          |     |  |

| 4.2.9         | Critical Variant, Adder                   |     |  |

| 4.2.10        | Critical Variant, Multiplier              |     |  |

| 4.2.11        | Critical Variant, Clk                     |     |  |

| 4.2.12        | Execution Time Boundary                   |     |  |

| 4.2.13        | Power Boundary                            |     |  |

| 4.2.14        | Area Optimization                         | 90  |  |

| 4.2.15        | Resource Binding                          | 91  |  |

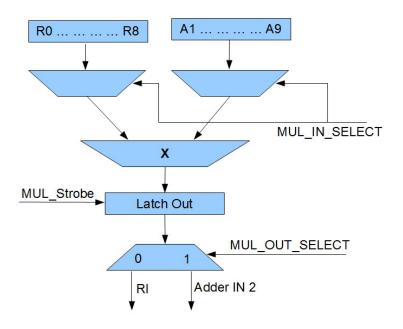

| 4.2.16        | Multiplexing Scheme                       | 93  |  |

| 4.2.17        | Block Design Using Optimization Strategy  | 95  |  |

| CHAPTER       | V:                                        |     |  |

|               | FECTIVE COMPARISON                        |     |  |

| -             | JF-ADAPTING SYSTEMS                       |     |  |

|               | JF-TESTING CAPABILITIES                   |     |  |

| REFERENC      | CES                                       | 123 |  |

| GLOSSARY      | GLOSSARY                                  |     |  |

## LIST OF TABLES

| TABLE 1 – FPGA DESIGN [17]<br>TABLE 2 – ASIC DESIGN [17]<br>TABLE 3 - FIR FILTER EVALUATION [24]                             | 15 |

|------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE 2 – ASIC DESIGN [17]                                                                                                   | 15 |

| TABLE 3 - FIR FILTER EVALUATION [24]                                                                                         | 26 |

| TABLE 4 – HARDWARE ACCELERATED EMBEDDED SYSTEMS COMPARISON [25]                                                              | 27 |

| TABLE 5 - HARDWARE ACCELERATED EMBEDDED SYSTEMS COMPARISON [23]                                                              |    |

| TABLE 6 - 2ND ORDER EQUATION OF FILTER BLOCKS<br>TABLE 7 - TRANSFER FUNCTION EXPANSION RESULTS                               | 74 |

| TABLE 7 - TRANSFER FUNCTION EXPANSION RESULTS                                                                                | 74 |

| TABLE 8 - OPERATION VARIABLE ASSIGNMENT                                                                                      | 75 |

| TABLE 9 - RESOURCE OPTIONS                                                                                                   | 78 |

| TABLE 10 - MULTIPLIER COSTS                                                                                                  | 79 |

| TABLE 9 - RESOURCE OPTIONS<br>TABLE 10 - MULTIPLIER COSTS<br>TABLE 11 - ADDER COSTS<br>TABLE 12 - SYSTEM CONSTRAINTS         | 79 |

| TABLE 12 - SYSTEM CONSTRAINTS                                                                                                | 80 |

| TABLE 13 - MINIMUM RESOURCE SCHEDULE                                                                                         | 80 |

| TABLE 14 - MAXIMUM RESOURCE SCHEDULE                                                                                         | 81 |

| TABLE 15 - ADDER CRITICAL VARIANT SCHEDULE                                                                                   | 83 |

| TABLE 16 - MULTIPLIER CRITICAL VARIANT SCHEDULE                                                                              | 84 |

| TABLE 17 - CLOCK CRITICAL VARIANT SCHEDULE                                                                                   | 85 |

| TABLE 17 - CLOCK CRITICAL VARIANT SCHEDULE<br>TABLE 18 - SCHEDULE OF OPTIMAL VARIANT<br>TABLE 19 - ADDER MULTIPLEXING SCHEME | 92 |

| TABLE 19 - ADDER MULTIPLEXING SCHEME                                                                                         | 93 |

| TABLE 20 - MULTIPLIER MULTIPLEXING SCHEME                                                                                    | 94 |

# **LIST OF FIGURES**

| FIGURE 1 – BIT STREAM CONFIGURATION [12]<br>FIGURE 2 - DESIGN OF AN FPGA [15] | 10 |

|-------------------------------------------------------------------------------|----|

|                                                                               |    |

| FIGURE 3 – THE OPERATIONAL DIFFERENCE OF ASICS AND FPGAS [16]                 |    |

| FIGURE 4 – FPGA HARDWARE OVERHEAD                                             |    |

| FIGURE 6 – HARDWARE MODULE WITHOUT PARTIAL RECONFIGURATION                    |    |

| FIGURE 7 – HARDWARE MODULE WITH PARTIAL RECONFIGURATION                       | 20 |

| FIGURE 8 - AMDAHL'S LAW: SPEEDUP IN RELATION TO PORTION OF PROGRAM BEING      |    |

| ACCELERATED                                                                   |    |

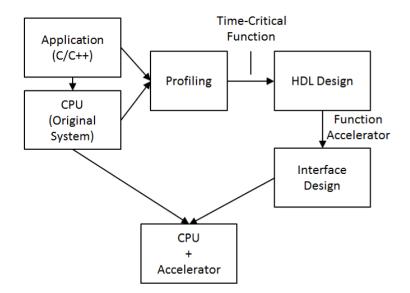

| FIGURE 9 - ACCELERATION DESIGN FLOW [24]                                      | 24 |

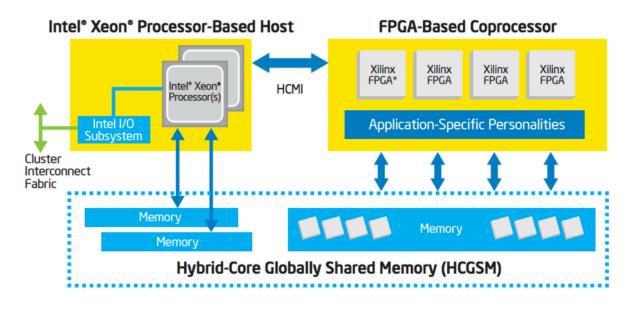

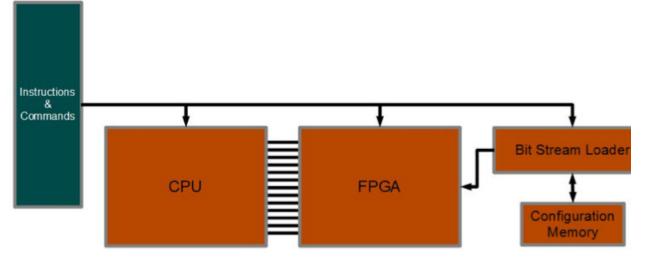

| FIGURE 10 - THE COPROCESSOR APPROACH [28]                                     | 31 |

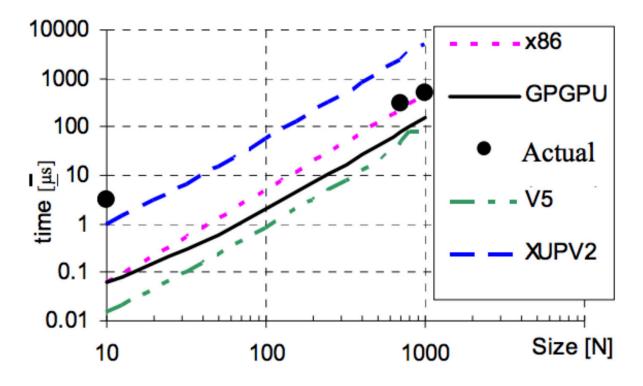

| FIGURE 11 - MULTI-ARCHITECTURE PERFORMANCE COMPARISON [29]                    | 32 |

| FIGURE 12 - DATA TRANSFER TIME ANALYSIS                                       |    |

| FIGURE 13 - XILINX'S ALL PROGRAMMABLE SOC [33]                                |    |

| FIGURE 14 - ISOLATED TECHNOLOGIES, PCIE CONNECTION [34]                       |    |

| FIGURE 15 - MULTIMEDIA SYSTEM WITH BLOCK DIAGRAM [35]                         | 51 |

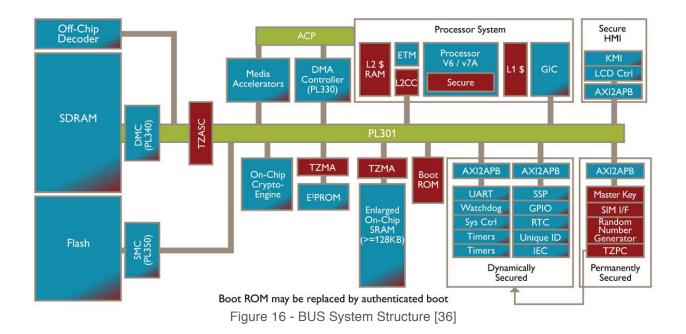

| FIGURE 16 - BUS SYSTEM STRUCTURE [36]                                         |    |

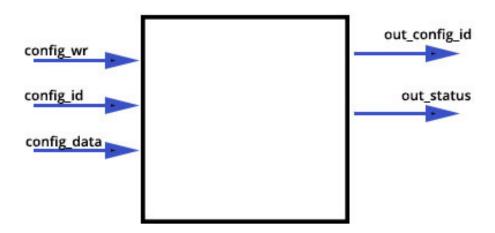

| FIGURE 17 - REQUIRED CONTROL SIGNALS FOR HWAI                                 |    |

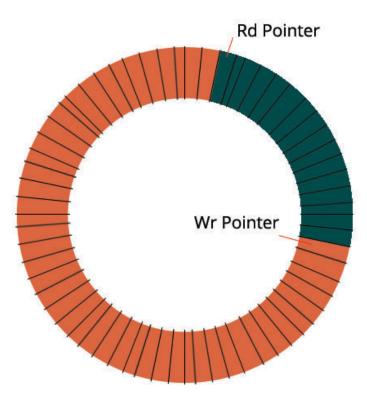

| FIGURE 18 - RING BUFFER / INSTRUCTION BUFFER                                  |    |

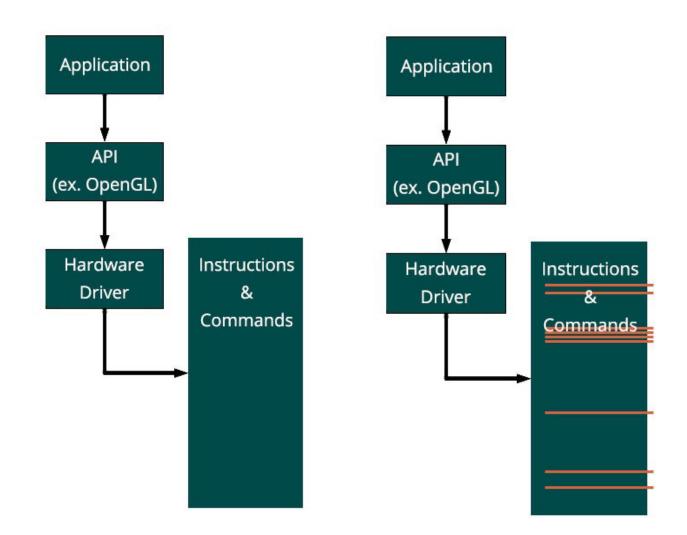

| FIGURE 19 - PRE-EMPTIVE ADAPTIVE HARDWARE                                     |    |

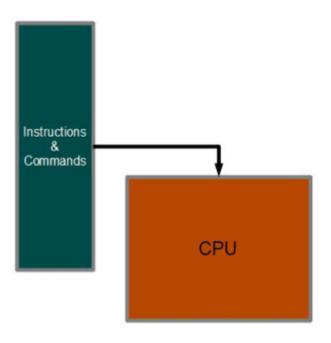

| FIGURE 20 - TRADITIONAL SYSTEM ARCHITECTURE OVERVIEW                          | 59 |

| FIGURE 21 - PROGRAMMABLE SOC (EX INTEL'S E600 SERIES)                         |    |

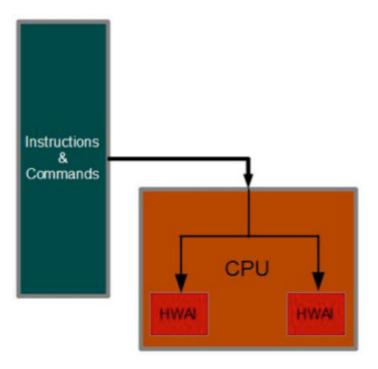

| FIGURE 22 - CPU WITH HWAI                                                     |    |

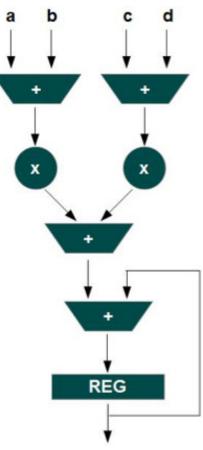

| FIGURE 23 - STREAM PROCESSING UNIT                                            |    |

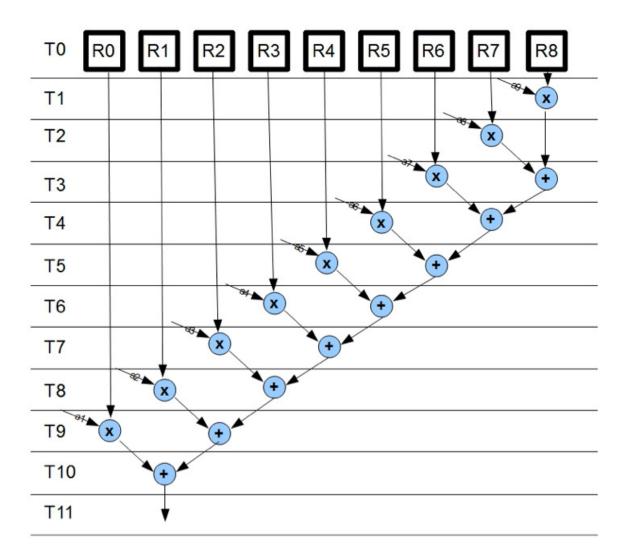

| FIGURE 24 - UNCONSTRAINED SEQUENCING GRAPH                                    |    |

| FIGURE 25 - MINIMUM RESOURCE SEQUENCING GRAPH                                 |    |

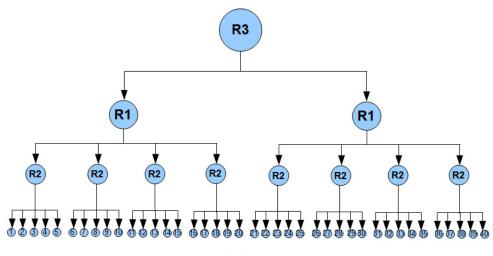

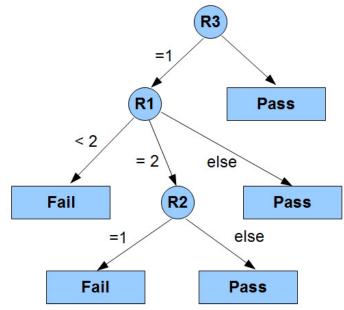

| FIGURE 26 - ACG OF EXECUTION TIME                                             |    |

| FIGURE 27 - SYNTAX TREE OF EXECUTION TIME                                     |    |

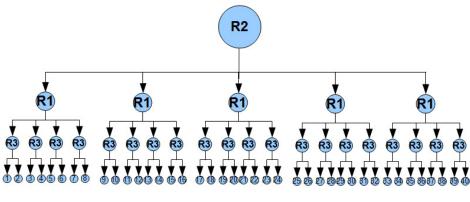

| FIGURE 28 - POWER ACG                                                         |    |

| FIGURE 29 - POWER BOUNDARY SYNTAX TREE                                        |    |

| FIGURE 30 - AREA ACG                                                          | 91 |

| FIGURE 31 - BOUND SEQUENCING GRAPH                                            | 92 |

| FIGURE 32 - ADDER MUX PLAN                                                    |    |

| FIGURE 33 - MULTIPLIER MUX PLAN                                               |    |

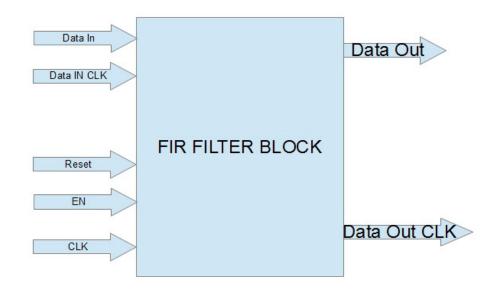

| FIGURE 34 - FIR BLOCK SYMBOL                                                  |    |

|                                                                               |    |

# LIST OF APPENDICES

| APPENDIX A: UVM / SYSTEMVERILOG<br>RTL & Test Bench Code                                                                                                             | 100 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| RTL & Test Bench Code                                                                                                                                                |     |

|                                                                                                                                                                      |     |

| Makefile<br>test.sv<br>fifo.vh<br>fifo_agent.svh<br>fifo_driver.svh<br>fifo_env.sv<br>fifo_monitor.svh<br>fifo_sanity.sv<br>fifo_scoreboard.svh<br>fifo_seq_item_svh |     |

| fifo.vh                                                                                                                                                              |     |

| fifo.v                                                                                                                                                               |     |

| fifo_agent.svh                                                                                                                                                       |     |

| fifo_driver.svh                                                                                                                                                      |     |

| fifo_env.sv                                                                                                                                                          |     |

| fifo_monitor.svh                                                                                                                                                     |     |

| fifo_sanity.sv                                                                                                                                                       |     |

| fifo_scoreboard.svh                                                                                                                                                  |     |

| fifo_seq_item.svh                                                                                                                                                    |     |

| fifo sequence library syb                                                                                                                                            | 116 |

| fifo sequencer syh                                                                                                                                                   | 117 |

| fifo_tb_wrapper_io.sv                                                                                                                                                |     |

| fifo_tb.sv                                                                                                                                                           |     |

| fifo_tb_wrapper_io.sv<br>fifo_tb.sv<br>test_top.sv                                                                                                                   | 120 |

| APPENDIX B: ABOUT AMD                                                                                                                                                |     |

### INTRODUCTION

#### **Intellectual Property**

At the time in which this paper was written, Ryan Meghdies-Vardeh had submitted multiple patent applications to Advanced Micro Devices, Inc. (AMD). AMD has decided to pursue the protection of two of those filings [2] and [3]. A third filing, is discussed in the future work section is likely the most promising of the three: [1]. The research compiled for this thesis lead to the invention of these patents. See Appendix B to learn more about AMD.

#### **Overview**

This thesis provides an introductory analysis of General Purpose Processors (GPP) and Field Programmable Gate Arrays (FPGA) architectures, their benefits and drawbacks. In the past, consumer processors and reprogrammable logic, have not worked in conjunction with one another. Traditional processing architectures are considered to be the superior choice when there is enough volume demand and sufficient research and development resources. In contrast, FPGAs provided a platform that would significantly lower venture development costs and thereby make it possible for individuals and corporations to invest in, and more importantly afford to, develop new hardware solutions.

In this thesis, we identify that CPUs/GPUs and FPGAs have their own unique benefits and the architecture of the future will strategically approach the integration of these two technologies. It is important to note that this work targets consumer market devices. There are two key contribution to this future looking architecture presented in this thesis. First using through the "Hardware Acceleration Islands" (HWAI), a design strategy which strategically embeds DPR enabled FPGAs within exiting processor designs (without requiring software changes, minimizing risk and research and development costs). Secondly, by offering a technique that will enhance the HWAI modules and optional optimizations to processor device drivers.

### **CHAPTER I**

#### **1.1 MOTIVATION**

With the end of Moore's Law [4] engineers must make use of smarter and more innovative processor architecture design concepts. Traditional brute force approaches translate into larger systems that are power hungry and more costly to manufacture. This is no longer a feasible technique as mobile processing and portable devices become the focus of the consumer market. As seen in the figure below [5], existing architecture designs are for the first time becoming smaller and engineers are looking for new ways to generate greater performance without proportional overhead.

#### 1.2 OBJECTIVE

A successful solution would be one that minimizes the research and development risks, is easy to integrate within existing processor designs, and delivers worthwhile performance improvements using innovative system design. The "Hardware Acceleration Islands" in conjunction with the proposed case integration strategy offers such benefits, so as to make market adoption feasible and profitable for semiconductor manufacturing companies.

While this thesis targets consumer market processors, it is important to recognize that most modern supercomputers look to high-end consumer processors (GPUs and CPUs) [6].

#### **1.3 EFFECTIVE CONTRIBUTIONS**

There were a number of problems that arose in developing solutions for the aforementioned problems while staying within the constraints of the objective goals. As a result, it is recommended to use the hardware solution in conjunction with the protocol and strategy.

The hardware solution injects programmable logic into processor technology on the same die using similar strategies to embedded microprocessors. Using the proposed strategy, these hardware acceleration islands can absorb high-performance tasks and reduce area by also absorbing infrequent or temporal hardware logic. This methodology will not require any 3<sup>rd</sup> party software changes. Modifying device drivers will be sufficient to hide the suggested system changes. Future works may require optimizations to existing operating system settings.

There is also a protocol that hardware systems can take advantage of to improve the efficiency of the hardware acceleration islands. The protocol will work to minimize/eliminate delays in the pipeline and requires minimal hardware overhead (only 2 control signals).

#### 1.4 THESIS ORGANIZATION

The first chapter will share the motivation of this research, what are the problems being solved and why they are necessary to be addressed. The objective of this thesis is clarified as it presents a unique area and set of goals.

The organization of the remainder of this thesis (chapter 2 and onwards) is structured to provide sufficient background to the build-up towards the primary design work found here. Chapter 2 will outline existing solutions similar to the work of this thesis or attempting to solve similar problems. The pros and cons of each will be evaluated. The following chapter will explain the new approach / primary work of this thesis. Chapter 3 will walk through the details of how to recreate this work.

With a strong understanding of the design work, chapter 4 will discuss the implementation and practical examination of the design work to evaluate the performance and tools to be used. In the final two chapters the obtained results will be compared with similar works and finally the future work for myself and hopefully to motivate other individuals to pursue this avenue of research and development.

### **CHAPTER II:**

#### 2.1 BACKGROUND

#### 2.1.1 Insight Into Modern Applications

Since the introduction of FPGA technology, hardware developers have been working to make use of each architecture's relative benefits. Today these architectures are used in conjunction with each other. ASIC developers now commonly implement SOC designs on FPGAs, validating them thoroughly before investing the millions necessary to tape-out the product in the form of an ASIC. This is referred to as "FPGA Prototyping". Understanding such background and the progression of FPGA technology will provide a clearer image of the direction and impact of this architecture. While this thesis will not dive into this FPGA prototyping, it is helpful to understand 3 key benefits that this methodology provides.

1) Reliable Verification: Implementing designs on FPGAs is a reliable way to ensure the final ASIC will be functionally correct. Previously verification efforts were much more costly (in terms of research and development) or almost non-existent. Previous to FPGA prototyping, ASIC manufacturers relied primarily on software to verify their designs. About a third of all current SOC designs are fault-free during first silicon pass, with nearly half of all re-spins caused by functional logic errors [7].

2) Time-to-Market (TTM): FPGA prototyping has enabled hardware designers to shorten the TTM period. Since less verification resources are required and verification

accounts for as much as 80% of the design process, designers can save money and release new products faster, which in-turn increases the rate of innovation. In a consumer driven market that is keen on technology, meeting deadlines set according to demand peaks is critical to a corporations' success. These peaks present a small window in the market, and missing it could render a project useless thereby costing the company the much of the capital which was invested in the product (typically the research is reused for the progression of IP(s) [8].

3) Development Cost: By reducing the number of re-spins required through FPGA prototyping, hardware design corporations are able to save millions of dollars. These re-spins are caused by a number of factors including: firmware issues, power issues, mixed-signal interface related issues, race condition issues (that were not detected by PD (Physical Design) software, clocking domain issues, functional issues, and more [9]. In [10], there are five precautionary steps that are listed in which corporations take to minimize their risk of having a re-spin:

- a) Constraint random verification

- b) More effective block (IP) level verification

- c) Verification reuse from block level to System level

- d) Architecture of test bench using reusable methodologies

- e) A reusable and scalable verification

#### 2.1.2 Implementation

The implementation modules, located in Appendix A, demonstrate how "Constraint random verification" and "More effective block (IP) level verification" are achieved and being approached within the modern day hardware design industry. The technologies made use of are the latest solutions used by the most renowned hardware design corporations and design teams. In fact, many companies are still moving to this methodology. The demand for this can be seen by the sheer number of job postings to simply help convert/create design and design verification environments to make use of these techniques.

#### 2.1.3 Verification Tools

It is well known that verification efforts can account for 60 to 80 percent of the hardware development process [11]; where larger designs typically requiring the higher percentages. There are a number of different stages when it comes to hardware verification, most stages run in parallel during the course of a project. In one of the first stages, engineers develop their concept design modules and algorithms using software. Software verification is highly effective at finding high level faults in a design due to two key characteristics: easy development (fast and low cost approach), as well as fast results (compile times for an FPGA can take hours when making even the smallest changes and can take an exorbitant amount of time to simulate). However, software verification is not without its limitations. Software is limited in its ability to mimic

hardware. While software models have made leaps and bounds in this area even capable of modeling the timing delay between modules, hardware and software are still inherently distinct and therefore limited in verifying the design. They are however an effective emulation tool for the conceptual design of the module (ex. testing algorithms which will be implemented in hardware).

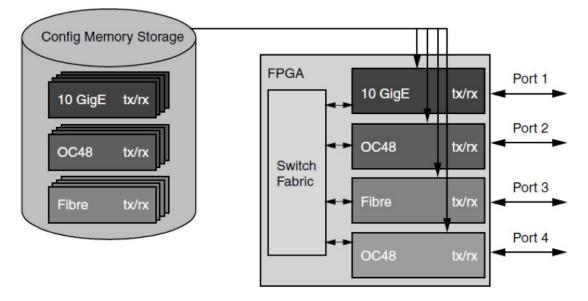

In addition to software verification, engineering teams develop and implement their designs using "Hardware Description Languages" or HDLs. The two foundational HDLs include VHDL (VHSIC Hardware Description Language) & Verilog. The code found in these .vhdl and .v files (respectively to the languages above), are then translated to the required format as per a specific architecture/technology (an ASIC, Xilinx Kintex 7 FPGA, Altera Cyclone V FPGA, etc.). For example, a bit stream is generated based on the internal structure and resources available within the specific FPGA being used. This bit stream is used to program the FPGA being used by configuring the hardware, typically through JTAG interface, by filling in LUTs, configuring routing, and manipulating other resources.

Figure 1 – Bit Stream Configuration [12]

From a verification perspective there are a number of options for engineers to verify their code at this stage, of which two fundamental concepts are discussed. First, engineers will often include additional verification oriented code that is built into the language (VHDL / Verilog) to ensure some conditions within respective states are met. Secondly, if the correct arguments are passed when invoking modern hardware simulators, such as VCS developed by Synopsys Inc., then files containing the values of registers and pins are dumped. These files can then be examined to determine if the behaviour is as expected.

Processor systems have become far more advanced, consequently hardware design files have grown exponentially larger over the last years. As a result, improved verification environments (speed, flexibility, features) have become a central focus in the hardware design industry. With this growing demand, two key issues were identified: a limited library to verify hardware and manually analyzing the waves was extremely time consuming and difficult. When engineers looked at these limitations they had two goals: (1) To expand the available verification environment and enable hardware designers to build with ease similar to that which software provides. (2) To automate the manual processes that tended are labour intensive and repetitive (both characteristics for opportunities to develop a software solution).

In 2002, engineers released the revolutionary HDL (Hardware Description Language) - HVL (Hardware Verification Language) combination based on extensions to Verilog [13]. While there were predecessors which SystemVerilog inherited from, SystemVerilog provided superior functionality and modern features. As a result, SystemVerilog was selected as the IEEE standard in 2005 and by 2009 was merged with the base Verilog standard [14]. This decision demonstrates just how significant of a relationship existed between the hardware design and design verification world. To this day, SystemVerilog remains as the foundation to which more advanced tools are built on top of. It is not to be taken for granted by any means or compared against UVM (Universal Verification Methodology). UVM is built upon SystemVerilog, and as such should be identified as an extension. This is worth mentioning when examining the implementation found in Appendix A.

#### 2.1.4 ASIC & FPGA Architectures

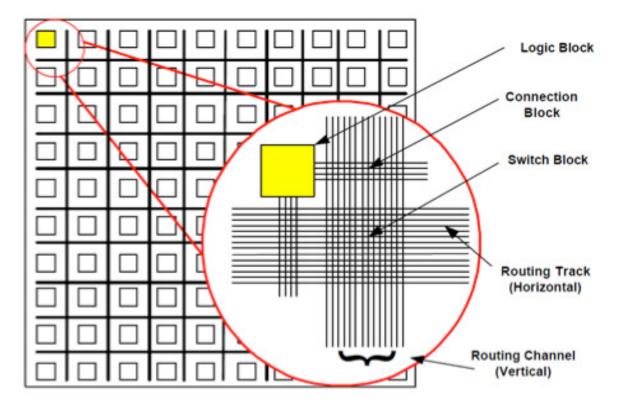

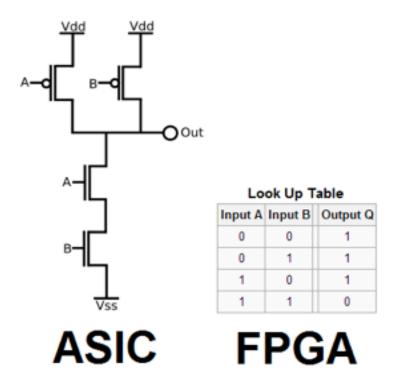

Field Programmable Gate Arrays have come a long way in recent years and continue to make leaps and bounds in the semiconductor industry. Their unique ability to be reconfigured is the reason why FPGAs are able to take on varying complex tasks that with an optimized hardware configuration. In order to accomplish hardware reconfigurability, FPGAs are designed using a distinct hardware layout, as seen in Figure 2 bellow. Logic blocks are LUT representations of the logic gates used inside ASICs (refer to Figure 2). These logic blocks are linked together using routing lines and switching blocks are used to select which logic blocks will be connected together.

Figure 2 - Design of an FPGA [15]

Figure 3 – The Operational Difference of ASICs and FPGAs [16]

An FPGA's ability to adapt to situations using its reconfigurable properties means that the hardware can be optimized based on the task at hand. These adaptive characteristics allow engineers to modify their designs (perhaps for optimizations or handling new protocols), or upload completely different designs onto a chip. For instance, an FPGA can be configured to be a router in one instance and a graphics processing unit in another. System architectures are classified with three parameters:

- i. Components: the set of function made available by the hardware architecture

- ii. Links: the interconnects between the components

- iii. Procedures: the set of variations of functions and links in time

ASICs use a "fixed components, fixed links, variable procedures" architecture. While FPGAs on the other hand use a "fixed components, variable links, variable procedures" architecture [17]. This is also how our brains are designed, and despite running at an operating frequency of approximately 10 Hz, the human mind is the most advanced processing unit. This added variance allows us to optimize performance for various tasks, but also comes at a cost.

One question to be asking is why we still use ASICs if FPGAs have such a large advantage in being reconfigurable? It is important to note that although FPGAs and ASICs could theoretically be interchanged (for example ASIC designs are often implemented on FPGAs for prototyping and testing purposes), FPGAs will never replace

ASICs completely. This is because they serve different purposes and thus each has its own advantages, see Table 1 and 2:

| Advantage                               | Brief                                           |

|-----------------------------------------|-------------------------------------------------|

| Faster time-to-market                   | No layout, masks or other manufacturing         |

|                                         | steps are needed                                |

| No upfront non-recurring expenses (NRE) | Costs typically associated with an ASIC design  |

| Simpler design cycle                    | Due to software that handles much of the        |

|                                         | routing, placement, and timing                  |

| More predictable project cycle          | Due to elimination of potential re-spins, wafer |

|                                         | capacities, etc.                                |

| Field reprogramability                  | A new bitstream can be uploaded remotely        |

Table 1 – FPGA Design [17]

| Advantage              | Brief                                        |  |  |

|------------------------|----------------------------------------------|--|--|

| Full custom capability | For design since device is manufactured to   |  |  |

|                        | design specs                                 |  |  |

| Lower unit costs       | For very high volume designs                 |  |  |

| Smaller form factor    | Since device is manufactured to design specs |  |  |

Table 2 – ASIC Design [17]

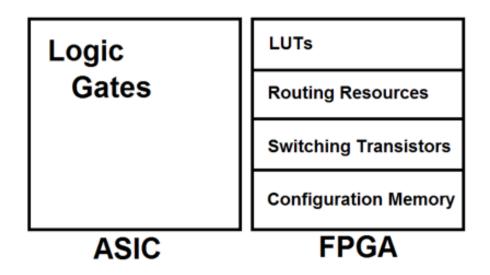

The reconfigurable properties of FPGAs come at a cost however. FPGAs have a large hardware overhead in comparison with ASICs, thus increasing the size and cost of the units (see Figure 4). Additionally, since software handles most of the routing, placement, and timing within FPGAs, the layout is not the optimal solution (even though the software runs several optimization algorithms) [18]. So although this creates a simpler design cycle, ASICs have a performance advantage. As a consequence of not having a design implemented using the optimal layout, the clock frequency also has to be decreased according to the slowest path in the circuit [19].

Figure 4 – FPGA Hardware Overhead

As the name states, ASICs are specific to an application and therefore are optimized for those task(s). Therefore, in systems where tasks are fixed, ASICs are the better solution. However, in situations where a systems' tasks are continually changing, a ASIC architectures may not be the ideal/optimized method of implementation. Despite the hardware overhead of an FPGA, the unique ability to be reconfigured is the reason why FPGAs are able to take on complex tasks with an optimal hardware configuration and outperform traditional processor architectures using less space and power consumption.

In the past, when a system [implemented on an FPGA] would switch tasks and require a different hardware configuration, this meant the FPGA had to be placed in shutdown mode while loading the new configuration file onto the chip (this is known as static reconfiguration). This limitation significantly impacts the performance of a system, and hence the applications for which an FPGA's adaptive properties would be required. Engineers recognized this setback was restricting the performance capabilities that FPGAs had to offer. After several years of research, Xilinx discovered the solution: Dynamic Partial Reconfiguration.

#### 2.2 FOUNDATION OF MODERN RESEARCH

#### 2.2.1 Reconfigurable Technology

Dynamic Partial Reconfiguration takes the adaptive properties of an FPGA to a whole new level. DPR allows selected "parts" of an FPGA to be reprogrammed with new functionality while the remainder of the FPGA continues to operate (hence the word "partial" in dynamic partial reconfiguration). Observe Figure 3 bellow, "Part A" of the FPGA is going to be reconfigured. During this reconfiguration time, the module is shut down and the rest of the system continues under normal operation. When "Part A" has finished being reconfigured, it will turn on and resume operation with its new hardware configuration [20].

Figure 5 – Operation of Dynamic Partial Reconfiguration

Dynamic partial reconfiguration is not supported on all FPGAs. In fact, up until recently Altera (one of Xilinx's primary competitors) did not support partially reconfigurable FPGAs. The first FPGA to support DPR was Xilinx's Virtex II Pro. Partial reconfiguration addresses three fundamental needs by enabling the designer to:

- 1. Reduce cost and/or board space

- 2. Change a design in the field

- 3. Reduce power consumption

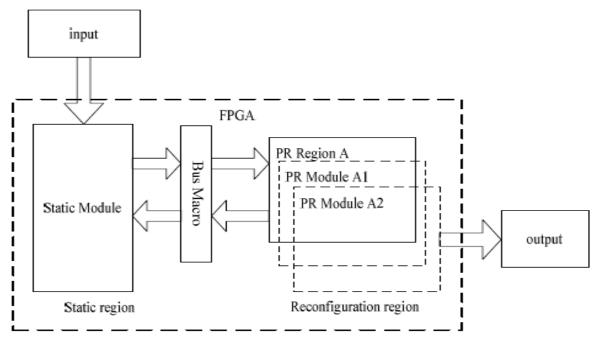

Dynamic partial reconfiguration enables designers to fit more logic into an existing device by time-multiplexing hardware dynamically on a single FPGA. This also translates into a smaller and less expensive device. The advantages of DPR are clearly seen when comparing Figures 6 and 7, which are two different implementations of the same hardware functionality [12].

Figure 6 – Hardware Module without Partial Reconfiguration

Figure 7 – Hardware Module with Partial Reconfiguration

DPR provides real-time flexibility for the protocols available in any given moment. This can translate into cost savings of several orders of magnitude compared to traditional processors, since the architecture cannot be reprogrammed to support a new protocol.

With partial reconfiguration, designers can time multiplex parts of their designs on the FPGA. As long as the stages of the design are independent, this can be done as many times as needed. Using this methodology then requires a much smaller FPGA chip since not every part of the design is needed 100% of the time. Using a smaller FPGA also means that the power consumption and timing (because everything is closer) is exponentially more optimal [21]. Additional advantages of partial reconfiguration include:

- Enables the use of new techniques in design security

- Improves FPGA fault tolerance

- Accelerates configurable computing

- Reduces bit stream storage requirements

#### 2.2.2 Existing DPR Applications

Dynamic Partial Reconfiguration in FPGAs is still a fairly new concept that has not been taken advantage of fully. FPGAs that support DPR can be utilized in many applications to increase performance, while reducing costs, area consumption, and power consumption.

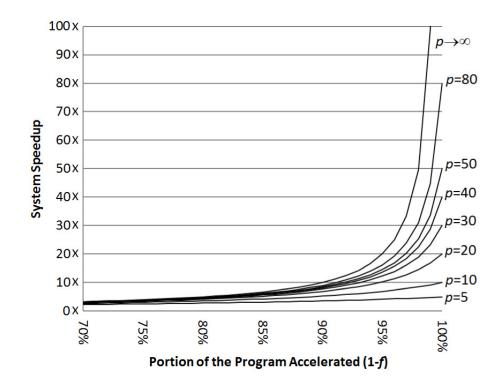

A hardware accelerator is an optimized functional block used to offload a specific task or set of tasks from a general purpose processor (GPP). Hardware accelerators are optimized frequently used in systems today to improve performance and decrease dynamic power consumption. However, according to Amdahl's Law hardware accelerating a task can only accelerate the overall performance according to how often that task is used during execution time. Figure 8 bellow further exemplifies this [22].

Figure 8 - Amdahl's Law: Speedup In Relation To Portion of Program Being Accelerated

Using dedicated hardware to accelerate a particular task has proven to be a very effective method for improving the performance of a system [23]. However, if every task had its own dedicated set of hardware the static power and area consumption would be astronomical. One may be able to see where DPR enabled systems can solve this problem, while maintaining the same performance benefits to the system. For instance, in most systems not all tasks are used in one instance. So if those tasks were loaded into configuration memory, then each module could be loaded onto chip (the FPGA) as needed. By following the suggested strategy being proposed here, only the tasks being used are loaded into hardware but the system still has access to all the dedicated hardware sets.

What [24] proposes is that hardware accelerators in the past can increase performance and reduce power consumption, but overlook the interface between CPU's and FPGA hardware accelerators. The model they present is to analyze the application running on the GPP (in this case a CPU), and profile the application to determine which time-critical functions should be accelerated. At this point the correct IP module will be loaded onto the FPGA. However, the way in which the CPU and the FPGA interface to each other will also affect the performance of the overall system. The results can be seen in Table 3 and will be further discussed below.

Figure 9 – Acceleration Design Flow [24]

The research and findings found in [25], compliments that of [24]. Using FPGAs to hardware accelerate embedded systems is a popular and promising area of research. The benefits and possibilities are promising and will truly expand the capabilities of present day embedded systems. The basic premise of [25] is that FPGAs in embedded systems can raise the abstraction level without imposing new tools and practices for design engineers and corporations. By taking an OOP approach (expressed in UML and implemented in C++) software coding efforts are significantly reduced. Not only provides a golden reference model, but may also be used in the actual implementation of the hardware design. This can prove especially useful in today's semiconductor industry. Since about 80% of the time needed to design an ASIC is spent in verification efforts, overlapping the time spent on developing Bus Function Models (BFMs) for the test bench and the actual RTL design could reduce the cost of processor design significantly [26]. For example, assuming 100% of the 30% design time could be

transferred to verification efforts that would mean a cost saving of 30%. The proposed methodology being indicated here is what top engineers are striving to achieve. However, what typically prevents them is the amount of resources and risk involved in making such drastic changes. With the approach discussed in this thesis and the tools discussed in Chapter one such results can be achieved. The results will be further discussed in the following section.

#### 2.2.3 Theoretical DPR Gains

FPGAs are particularly suited for accelerating compute intensive algorithms that can take advantage of massive hardware parallelism. This is especially true for FPGAs that are DPR enabled, since the hardware can adapt to the exact compute operations being executed. Additionally, being able to reconfigure hardware during run time without stalling or impairing the performance of a system, makes this all the more promising. This in effect makes the hardware appear as if all tasks are in hardware and available to be called upon at any given time. The philosophy behind this appears to mimic that of virtual memory. In short, a system may only have a few megabytes of memory, but by virtualizing memory on external storage it appears to the user that the system memory is much greater.

This visualization of the hardware follows the same principles by context switching between hardware configurations. In multitasking contexts, virtualizing

hardware translates to superior hardware utilization and much greater performance can be achieved [27]. This is truly reflected in Table 3 bellow.

It can be seen that using a general processor architecture means the implementation must be completed using software. This abstraction means higher frequencies and hence power consumption. Using DPR to hardware accelerate this design proves to improve performance by factors greater than 50 times. The area in this design does increase; this is due to the initial hardware overhead that FPGAs introduce. However, as the design size increases, the initial investment of hardware overhead is disguised by the hardware virtualization capabilities.

|                |     |                | CPU @                  | 25MHz        | CPU @                  | 50MHz        | CPU @ 1                | 100MHz       |

|----------------|-----|----------------|------------------------|--------------|------------------------|--------------|------------------------|--------------|

| FIR<br>Version | CPU | Logic<br>Cells | Exec.<br>Time<br>(ms)* | Power<br>(W) | Exec.<br>Time<br>(ms)* | Power<br>(W) | Exec.<br>Time<br>(ms)* | Power<br>(W) |

|                | e   | 2795           | 276.80                 | 0.06         | 138.40                 | 0.11         | 69.20                  | 0.19         |

| SW             | s   | 3768           | 156.00                 | 0.08         | 78.00                  | 0.13         | 39.00                  | 0.25         |

|                | f   | 4309           | 125.00                 | 0.08         | 62.50                  | 0.14         | 31.25                  | 0.25         |

|                | e   | 4781           | 4.24                   | 0.07         | 2.12                   | 0.11         | 1.06                   | 0.20         |

| Avalon         | s   | 5850           | 1.68                   | 0.08         | 0.84                   | 0.13         | 0.42                   | 0.25         |

|                | f   | 6390           | 1.36                   | 0.08         | 0.68                   | 0.14         | 0.34                   | 0.25         |

| Avalon         | e   | 5087           | 4.25                   | 0.07         | 2.12                   | 0.11         | 1.06                   | 0.20         |

| (FIFO)         | S   | 5967           | 1.68                   | 0.08         | 0.84                   | 0.14         | 0.42                   | 0.25         |

| (ГПО)          | f   | 6498           | 1.36                   | 0.08         | 0.68                   | 0.14         | 0.34                   | 0.26         |

|                | e   | 4720           | 3.32                   | 0.07         | 1.66                   | 0.11         | 0.83                   | 0.20         |

| CI             | s   | 5660           | 1.32                   | 0.08         | 0.66                   | 0.13         | 0.33                   | 0.25         |

|                | f   | 6189           | 1.32                   | 0.08         | 0.66                   | 0.13         | 0.33                   | 0.25         |

| TCM            | f   | 6316           | 1.36                   | 0.08         | 0.68                   | 0.14         | 0.34                   | 0.26         |

| C2H            | e   | 4992           | 44.40                  | 0.07         | 22.20                  | 0.11         | 11.10                  | 0.21         |

|                | s   | 5895           | 18.22                  | 0.08         | 9.11                   | 0.14         | 4.56                   | 0.25         |

|                | f   | 6452           | 14.64                  | 0.08         | 7.32                   | 0.14         | 3.66                   | 0.26         |

\* Execution Time for 1000 samples.

Table 3 - FIR Filter Evaluation [24]

Area cost with FPGAs is one of the biggest issues. The problem lies in what was discussed in the introduction and observed in Table 4. This is why existing FPGA solutions have not taken off in high volume design cases. As further discussed in [25], the capabilities to abstract hardware at a level where designers can overlap design and verifications efforts also come at a cost in the area designs consume. That being said, perhaps further research could uncover a more optimal method that will not increase the ASIC's area. Once again similar to the finding in [24], [25] has a small increase in hardware resources (area) required but performance increase of an order 10.

|            |                 | all software | hard accelerated    |

|------------|-----------------|--------------|---------------------|

|            | Slices          | 3,575        | 3,718               |

| Area       | BRAM            | 13           | 15                  |

|            | DSP48           | 0            | 1                   |

|            | PPC405          | 1            | 1                   |

|            | DCM             | 1            | 1                   |

|            | total           | 0.3831       | 0.0394              |

| Time (sec) | Matrix::macc    | 0.1177       | 0.0224              |

|            | angleCalc::exec | 0.2469       | 0.0082              |

| Eroa (Mbz) | of tests        | 300          | PPC: 300, hard: 100 |

| Freq (Mhz) | max             | 300          | PPC: 300, hard: 166 |

Table 4 – Hardware Accelerated Embedded Systems Comparison [25]

We have discussed and observed situations where FPGAs increase the area being consumed and yet other scenarios that decrease the area being consumed. The designer must truly consider the goals, meaning what the constraints and optimizations for the given project are. Once these functional specifications are gathered, the designer can analyze the technical specifications of the system and the resources available.

The conclusion of [23] supports the findings of this thesis, one can see that hardware accelerators can (but don't always) improve throughput and lower power consumption. When approaching the problem by proposing re-ordering the requests put on the accelerators and thereby decreasing the associated overhead with the DPR enabled system. What my work establishes and what [23] was working towards, is that an accelerator must be able to maintain performance between context switching, so by reducing this overhead and general switching occurrences, performance can be improved. Implementation results for a number of applications can be seen in table 5 bellow showing how such a strategy can improve performance:

| Accelerator   | Context Size<br>in IBM WSP (byte) | Throughput<br>Improvement (%) |

|---------------|-----------------------------------|-------------------------------|

| Decompression | 2500                              | 26.7                          |

| XML           | 256                               | 15.8                          |

| RegX          | 192                               | 9.9                           |

| Cryptography  | 64                                | 4.0                           |

Table 5 - Hardware Accelerated Embedded Systems Comparison [23]

The designs he has implemented are larger than the ones found in previous papers, and provide a much better estimate as the FPGA overhead is better disguised. As seen the throughput has once again been improved (although not as much), but the area differences are equal or less than in the FPGA implementation. This is why the designer needs to follow careful methodology to determine the correct resources to implement the design on.

# 2.3 EXISTING METHODS & TECHNIQUES

The industry recognizes the powerful benefits of reprogrammable logic and FPGA-like resources. Many leading industry and academic research and development sources have concluded the benefits of converging the two worlds of processor and FPGA technology. However, thus far implemented systems and proposed architectures have failed to meet the objective goals found in this paper.

Due to a large granularity approach, such systems cannot strategically extract benefits of each technology. The cost, risk, and performance suffers for consumer related processing applications. Reprogrammable logic resources will always consume more area and be slower than ASIC logic, however it is also true that they consume less power and are faster at processing algorithms than processors and even DSPs. It is for this reason, the fusion of these technologies needs to follow a specific set of rules in order to extract the benefits of each technology and develop the innovative consumer processing architecture of tomorrow.

Below are examples of how researchers have approached this concept and what some semiconductor manufacturers have created.

### 2.3.1 Intel Develops FPGA-Based Coprocessors

Intel is one of the largest semiconductor manufacturers in the world. They have been a world leader in developing innovative processor technologies. Given their success they have invested significant resources into the research of architecture design improvements.

Intel has made progress in developing processors that make use of FPGA embedded technology [28]. As can be observed in the figure below, the approach is one that provides greater potential and flexibility, excluding the consumer market CPUs/GPUs. As mentioned in chapter 2, FPGAs makes the hardware design process far more affordable for companies to develop systems. However, what must be highlighted is how significant an impact FGPAs have had on accelerating the innovation within the hardware industry.

Figure 10 - The Coprocessor Approach [28]

Hardware is extremely expensive to manufacture using traditional semiconductor fabrication plants. The cost is so astronomical that unless millions of chips are being fabricated, it is typically not worthwhile or feasible to invest in exploring hardware solutions. With the introduction of FPGAs however, this all changed. Today developing a hardware module is an affordable option for fuelling growth in the hardware industry, through the enablement of small projects, small ventures and custom solutions. Moreover, as demonstrated in [29] FPGA fabrication technology and architecture advancements have further enabled engineers endeavours and expanded the realm of possibility. The compute capabilities in today's FPGAs are tremendous, depending on applications certainly surpassing the performance of other technologies as seen below.

Figure 11 - Multi-Architecture Performance Comparison [29]

## 2.3.2 Existing Mixed Chips

It is commonly known that processors (including CPUs and GPUs) contain microcontroller(s) within their design. This embedded controller provides flexibility to a processor for particular set of tasks and frequently improves performance through measured analysis of a hardware pipeline. This can show up in area reductions, power reductions and other key performance metrics.

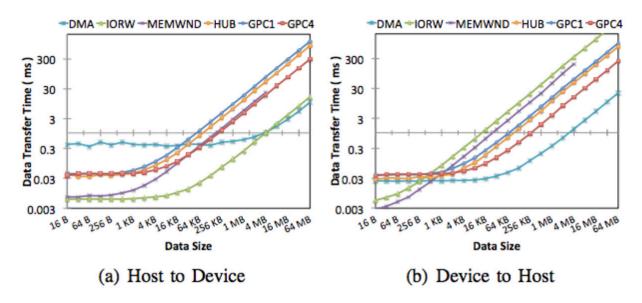

Heterogeneous compute devices such as this are become extremely popular, so much so in fact that the Heterogeneous System Architecture (HSA) Foundation was established in 2012 to focus on such efforts [30]. The HSA foundation is a not-for-profit that develops industry standards to improve innovative efforts of heterogeneous computing devices. Unfortunately, thus far such efforts have primarily focused on large processor systems working together. As found in [31] other heterogeneous computing devices are emerging, the Intel Many Integrated Core (MIC) and the AMD Fusion technology. [31] is able to unlock additional performance using the microcontrollers found in GPUs. As seen in the figure below, the methods assist with the reduction of data transfer times through a method titled "Microcontroller-based data transfer".

Figure 12 - Data Transfer Time Analysis

Altera and Xilinx have released the new generation FPD-Microprocessor mixed chips that consist of microcontrollers and programmable logic, though these ICs are aimed at embedded system markets only and provide limited amount of processing power compared to high-end processors. This idea has not been explored at high-end CPU/GPU chipset market. Solutions (such as netbooks, tablets, mobile devices and embedded systems) that are power, cost, and space sensitive will benefit tremendously from the solution that is proposed here.

By introducing reconfigurable FPGA blocks within ASICs, systems would have far greater flexibility to the large main chips in order to satisfy the dynamic feature requirements of different O.E.Ms and system architects. The solution (embedding nonvolatile programmable logic blocks) promises cost reduction, flexibility, performance enhancements, and size/power reduction from system engineering perspective. Such is the proposal of this thesis.

#### 2.3.3 Embedding ARM Processors Into FPGAs

Semiconductor companies are making the opposite efforts to integrate traditional processor technologies (ARM processors) into their systems. Xilinx has been extremely successful at building processing systems that offer a number of benefits to the hardware development industry. Recall from previous chapters, FPGAs have enabled hardware companies and developers to perform research and development affordably. It was explained how this lead to improved innovation. To expand the level of system flexibility Xilinx has set a high priority towards integrating both technologies. Today's Xilinx Zynq systems are a testimony to the incredible performance and opportunities that these systems possess [32].

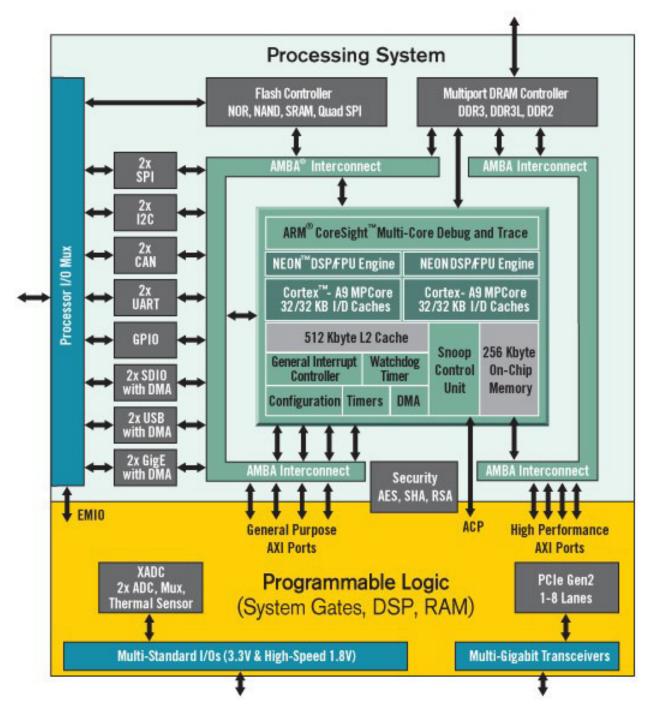

Xilinx Corporation markets the Zynq platform as an "All Programmable SOC"; this is an accurate term to describe the flexibility of the system platform. Developers are able to provide instructions through software, which can be run on the ARM core(s), while the programmable hardware can mange computation data processing. The system can execute applications in real time and optimize system interfaces through programmable I/O [33].

Figure 13 - Xilinx's All Programmable SOC [33]

# **CHAPTER III:**

# 3.1 COMPARATIVE ANALYSIS OF EXITING SOLUTIONS

The problem solved in the proposed work is to improve the performance of existing main stream systems (CPUs, GPUs) by incorporating programmable embedded logic into each ASIC strategically. FPGAs are known for their performance in highly algorithmic contexts, which are especially common within GPUs. As computing takes on more complex algorithms, today's processors can benefit with the proposed design. It improves the overall performance by accelerating algorithms and offloading certain intensive CPU or GPU tasks. In an example used in section 4.1, we see an increase of performance of 0.5% at a system level and as much as 80% on a block level.

Due to the design strategy proposed here and the characteristics of the technology being used, the proposed solution would be a low risk endeavour that corporations could quickly adopt into upcoming technologies. Moving towards the proposed designs would be a step towards a future looking architecture that outperforms existing architectures. Additional benefits will be further discussed later.

The common execution processor stages (IF, ID, ED, MEM, WB) introduce high overhead in comparison with a stream processors, especially in terms of power and delay (see implementation results). Processors break up large tasks into small operations and take them on accordingly. This introduces hazards and high overheads,

in comparison to a hardware acceleration unit which reprogrammable logic could provide replicate within an ASIC.

#### 3.1.1 Coprocessor Systems – FPGAs + CPUs/GPUs

As discussed above there are a number of semiconductor companies investing into solutions that integrate traditional processor technologies with FPGAs. This has been extremely effective at custom project solutions. As shown by [33], significant performance and flexibility can be achieved at low design costs. Xilinx brags about the lower BOM cost, higher systems performance, and lower system power they are able to provide with this type of architecture. Such an architecture is not far from the other methods proposed by Intel and Altera (at least in the system examples used here), however they have improved on the interface connections.

It should be understood, that the analysis of the pros and cons of this previous approach must be addressed in a context for which these systems were not designed. Therefore, it is not a criticism of the solution as it addresses a different problem all together. The objective of this thesis is, to the best of my knowledge conceptually different from all others.

When FPGAs and consumer processors (CPUs/GPUs) are connected to work together as coprocessors the system chip becomes very large. The cost of the chip significantly increases and large overhead IPs must be developed to manage the

connection. The two technologies stand alone in comparison with what this thesis proposes. Hence, the memory, contexts, tasks, and all other internal aspects of each technology are unknown to the other.

Moreover, due to the architecture the connections can become extremely slow in comparison the proposed design. Take for example the Altera system below.

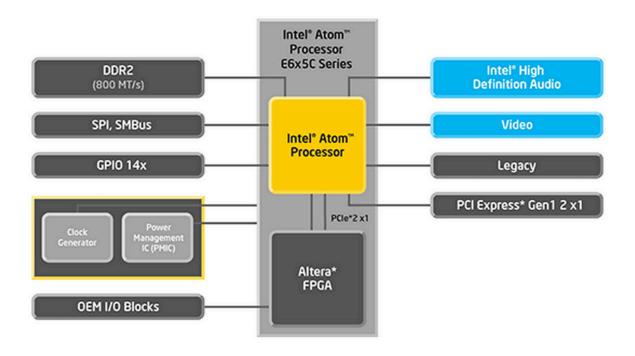

Figure 14 - Isolated Technologies, PCIE Connection [34]

The Altera FPGA and Atom processor are connected via PCIE. Such transfer speeds are considered to have extremely high latency. Communication is ineffective and it is desirable to avoid "team work" between the two technologies.

This isolation and lack of awareness are exactly what the "Hardware Acceleration Islands" and supporting strategies resolve. By removing this high latency connection, and improving communication between the two technologies the new system can build upon the success of both CPUs/GPUs and FPGAs.

Moreover, the proposed designs accomplish something very unique to the hardware development industry. That is, that they do not require a new software to be developed within the consumer market. This system not only adds performance to existing CPUs and GPUs, but packages it in such a way that hides these changes from hardware and software layers above (with the exception of device drivers and potentially minimal operating system optimizations).

## 3.1.2 System Customization

The suggested design does not have as much customization and flexibility for after the market adjustments. Since this system is targeting consumer devices too much flexibility will start to slow down the system and loose the initial benefits purposed. That said, consumer CPUs and GPUs hardware design companies have incredibly large and robust systems that require lengthy development cycles. To ensure functionality, time is taken to verify each IP and final SOCs (see section 2.2). Therefore, it can be expected that such projects will not / should not add greater customization than necessary and according to the strategies outlined in this thesis.

The customization that is provided according to this work will be nearly or just as effective as the isolated task unit in the alternative hardware solutions. However, when

considering the context of the system the Hardware Acceleration Islands will be far more performant.

## 3.1.3 Hardware Acceleration

By embedding FPGAs into current processors (such as CPUs and GPUs), algorithms and tasks can be offloaded to the DPR enabled programmable logic.

The programmable logic can be modified using run time reconfiguration and a bit stream uploaded characterized by the context of the system during runtime without impacting the performance of the rest of the system. Moreover, due to the granularity of these embedded reprogrammable modules and the stream processing characteristics of FPGAs the performance benefits and flexibility is precisely what engineers are looking to achieve.

Looking at the system implementation example in the following chapter, it is evident that engineers could benefit by embedding an adaptive hardware acceleration unit. Moreover, when an FPGA logic block is introduced for hardware acceleration, depending on the interfaces, there may be opportunities to assist with varying tasks and secondary system requirements. While the FPGA may not be the most effective at routing and decision-making, there are areas within system processing where FPGAs would far surpass (such highly mathematical system contexts).

#### 3.1.4 Protocols & Flashing

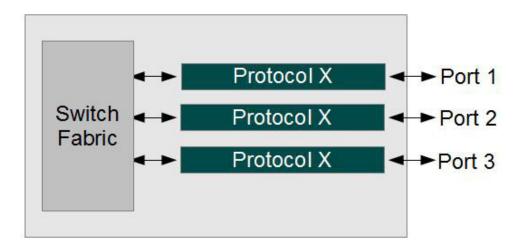

Custom SOCs are a growing market within the hardware design industry. The ability to add levels of flexibility and custom protocol support is a sought after trait. While it is costly, the return on investment is clearly justifiable.

There are a number of blocks within existing systems that have high demands in terms of the sheer number of protocols they are required to support. While some systems can afford to use software, most solutions require a hardware dedicated data path solution. Supporting a protocol is no small task; these dedicated pipelines are designed for each protocol which incoming data from the block interface will traverse.

The lists below are just basic protocols and codecs that many modern systems need to support. There are several others including a number of other categories that are not included here:

- H263

- H264

- VC1 Advanced

- VC1 Main (RCV)

- MPEG2 (DXVA)

- MPEG2 (Native)

• MPEG4

By using the proposed HWAI unit, not only could engineers target these with less hardware overhead but the complexity of the hardware would be far less. This would result in lower research and development costs and verification efforts. This is because by using a HWAI unit, the solutions become straightforward and simple problems that are less prone to errors. Currently engineers are faced with needing to come up with optimization strategies that, while ingenious, can be quite complex.

HWAI allows live system reprogramming. Moreover, new protocols could be downloaded post-silicon to consumer devices. Those bit streams can be implemented within the programmable logic constraints. This not only provides far-superior flexibility but also customizability. Hardware/software developers can create their own modules (ex. Apple/Intel's Thunderbolt protocol) without requiring extremely expensive hardware re-designs. The alternative for this today is to use slow software support.

## 3.1.5 Custom SOC

There is a growing demand for custom SOCs. As the use cases have grown and costs become difficult to manage, semi-conductor corporations are looking to build SOCs with greater and simpler customizability. ARM has been a leader in this regard; their success over these last years speaks for itself. ARM offers great performance using simple designs that are highly customizable.

The flexibility that reconfigurable systems offer is considered highly advantageous and powerful in today's industry. The reconfigurable nature of these blocks would allow CPU designers to create a new type of custom SOC that enables customers to flash their own configurations and modules. In specific, the internal FPGA could be flashed at any time, allowing for native hardware support for any task that can fit the logic cells available on the reprogrammable logic.

Using reconfigurable logic creates a unique opportunity to provide incredible flexibility while improving system performance. The simplicity and effectiveness of such a design truly stands out from existing custom IP solutions. The market this would attract and cost saving advantages that this design would provide to customers would be a unique and powerful combination.

#### 3.1.6 Power Advantages

Currently semi-conductor corporations are investing a large amount of resources into power management. As an industry engineers are approaching this by developing new power efficient designs. To further those efforts, HWAI would allow design team to make use of embedded reprogrammable logic to implement power management strategies using a central logic unit.

As an added benefit for the custom SOC use case, customers can define and flash their own power templates.

Today, hardware accelerators inside processors are fixed. It is obvious that if one could decrease the execution time, the overall power consumption decreases. Therefore, by hardware accelerating portions of applications (such as an edge detection algorithm within a GPU) engineers can reduce power consumption. Consider the following general relationships:

- if  $\uparrow$  performance by  $\uparrow$  frequency, then power consumption  $\uparrow$

- if ↑ performance by dedicated hardware, then power consumption ↓

- if  $\uparrow$  area, then  $\uparrow$  cost

- if  $\uparrow$  area, then strong chance  $\uparrow$  power consumption

## 3.1.7 Life Time

Given a system with such adaptive properties, as described in this work, design teams could reconfigure processors that have already been taped-out. This feature could be used to add dedicated hardware support for a new protocol that might be needed down the road, or to improve the performance of a task, power options and other customizations where allowable through the use of HWAI.

# 3.2 MODIFYING THE APPROACH

There are three parts that are necessary when considering the proposed design found in this thesis. Each aspect must be calculated and assessed carefully in order to achieve the objective goals.

The name of the proposed design work (as described in my patent filings) is "Hardware Acceleration Islands" or sometimes abbreviated as HWAI.

In the past, corporations researching this area have only looked at involving FPGAs and ASICs through methods that are insufficient for the consumer market (as discussed in the previous chapter). As an example, simply stitching these large architectures together through a traditional bus produced high latency and did not allow for cooperation without significant overhead.

While this approach was necessary for the past, this will not be the case in the near future. Previous strategies were required because the technologies (transistor gate sizes) greatly differed. CPUs and GPUs are continuously leading the way making use of the latest transistor technology. FPGAs have remained behind on the advancements being made (due to unique issues that must be overcome). However, that gap is shrinking as time passes and this approach becomes even more alluring.

The reason for this gap shrink is in the fact that current transistor technology is reaching its limitations. There are only a few atoms across the gate of a transistor. By decreasing it any further quantum physics becomes a factor affecting the behaviour of the transistor. Due to this hurdle and the increased number of resources being invested in recent years toward FPGAs, FPGA technologies have nearly closed the gap.

Therefore the previous strategy will no longer be necessary in order to avoid compromising. Moreover, the previous strategy contains 1 major flaw. FPGAs will never take the place of traditional processor architectures, and the proposed products have far too much overhead in the way they attempt to fuse the two technologies together. Rather than simply stitching these two technologies together I propose a far more strategic approach that will harness the benefits of both architecture individually. GPP systems currently dominate the market. The process of stitching an FPGA to a GPP costs a lot of money and the use reprogrammable use cases are limited in a large granularity implementation. This means high cost, high risk, and low gain. Alternatively, with my proposal, engineers take existing processor design and analyze the architectures strategically with a set of rules and strategies to identify locations to embed

HWAI. This is not a big task from a research and development point of view. During a design process there are design problems that simply highlight the benefits of the FPGA architecture. Similarly, most CPUs and GPUs already have microcontrollers embedded inside to help with regard to specific problems that would be solved more optimally by a microcontroller.

In recent years there have been a number of systems developed that contain a stitched CPU and FPGA architecture. The hardware design corporation leading the way in this regard is, Xilinx with their Zynq-7000 All Programmable SOC. The All Programmable SOC such as the Zynq-7000 has its place, however, the work discussed below targets hardware developers who are looking for innovative solutions within consumer processors. As they serve to improve the flexibility of modern day processors through a low cost, low risk approach that would be simple to implement across the industry. Providing a number of benefits that will be discussed below.

Previous to the Zynq-7000, Intel released the E600 series to harness the power of FPGAs, but they also simply adjoined an FPGA to an existing processor. This is not the strategy being proposing. Rather than trying to reinvent a new architecture, it is clear that ASICs are the superior architecture for CPU and GPU technologies. However, the proposed work compliments traditional processor architectures by harnessing the power of each technology in calculated locations.

There are a number of key benefits that this will offer to current semi-conductor design teams. The following sections are dedicated to the approach and benefits analysis of HWAI and what it offers.

#### 3.2.1 Hardware Acceleration Islands

By embedding HWAI into current ASIC systems (such as CPUs and GPUs), algorithms and tasks can be offloaded to the DPR enabled programmable logic. The key for the success of this is to follow the rules closely.

The programmable logic can be modified using run time reconfiguration and a bit stream uploaded characterized by the context of the system during run-time without impacting the performance of the rest of the system. Moreover, due to the granularity of these embedded reprogrammable modules and the stream processing characteristics of FPGAs the performance benefits and flexibility is precisely what engineers are looking to achieve.

The rules to create system performance improvements are as follows:

- 1) Identify system blocks that:

- Contain logic which are infrequently active or infrequent enough that the a bit stream of comparable logic can be uploaded within comparable or better timing. These are especially common in multimedia and power logic.

- Implement complex algorithms that do not require mainly interfaces/variables to be executed and do not have dependencies and are not atomic in nature.

- Frequently are modified during custom SOC projects or that would benefit performance and effective system lifetime through adaptable logic.

- Target the smallest division of logic. Remember bit stream sizes increase exponentially to the size of the design.

- Determine routing overhead from FPGA to ensure the size will not push chip outside of specifications.

- Compare the performance of the existing logic to a model of an optimized model (ideally developed as a streaming unit).

- 5) Power saving and cost benefits will be proportional to the decrease in frequency requirements, saved leakage current, area reduction, the simplification of the design (design, verification, research and development), and other factors.

Following this analysis and justification, the development is extremely simplified and the programmable logic can be embedded accordingly to replace existing blocks.

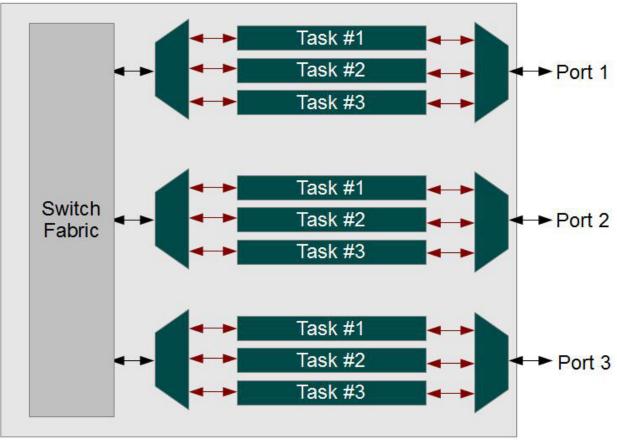

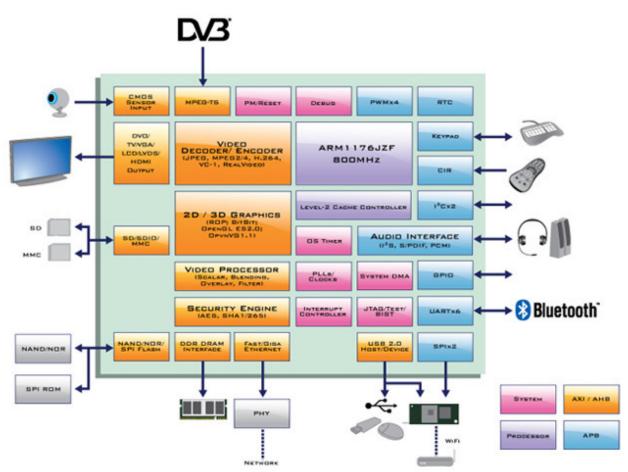

As previously suggested, a particular example where HWAI would be extremely beneficial would be within media blocks (see section 3.1.4). See the figure below and compare with Figures 6 and 7, focusing on the "Video Decoder / Encoder" block.

Figure 15 - Multimedia System with Block Diagram [35]

An alternative method to the above would be based on a bus system structure (see figure below). This method would be suitable for high performance computing. Today corporations such as NVIDIA have modified their processor designs to optimize for high performance computing systems. This is extremely expensive and has cause them to take a very reserved approach driven primarily by the following:

Justification = (Additional Cost Per Unit × # of Units Sold) - (Estimated # of Additional Units Sold \* Profits Per Unit) While this does not account for indirect benefits (especially for marketing), in general as long as "Justification" is greater than 0 the project is justifiable.

In a CPU or GPU that follows a bus architecture, adding multiple Hardware Acceleration Islands (with a calculated number of LUTs) to the bus could provide dynamic support to the system.

## 3.2.2 Internal Connections

The physical connections of HWAI to the system must be considered. Depending on the contextual placement of the programmable logic block and the support the unit will provide will impact how the connections will be established.

The control signals and data signals will have to remain consistent to duplicate the functionality. However, the method in which the module reprogrammability can be implemented will require a set of additional control signals. See the figure below:

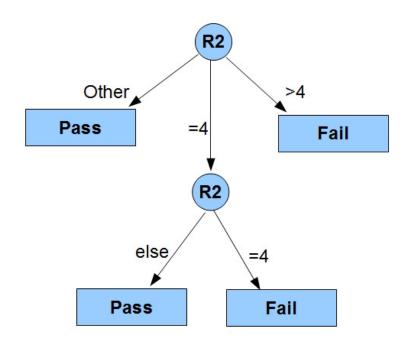

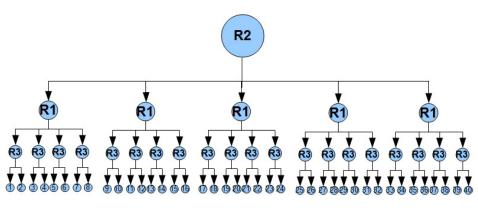

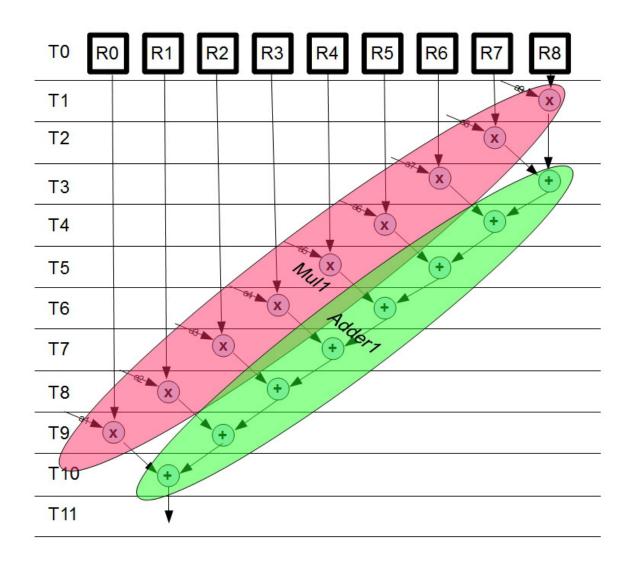

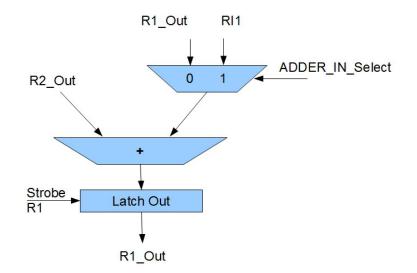

Figure 17 - Required Control Signals for HWAI