# A FRAMEWORK AND METHOD FOR THE RUN-TIME ON-CHIP SYNTHESIS OF MULTI-MODE SELF-ORGANIZED RECONFIGURABLE STREAM PROCESSORS

by

Victor Dumitriu

Bachelor of Engineering (B.Eng.), Ryerson University, Toronto 2006

Master of Applied Science (MASc), Ryerson University, Toronto 2008

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2015

©Victor Dumitriu, 2015

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

### A Framework and Method for the Run-Time On-Chip Synthesis of Multi-Mode Self-Organized Reconfigurable Stream Processors

Victor Dumitriu

Doctor of Philosophy, 2015,

Electrical and Computer Engineering,

Ryerson University

#### ABSTRACT

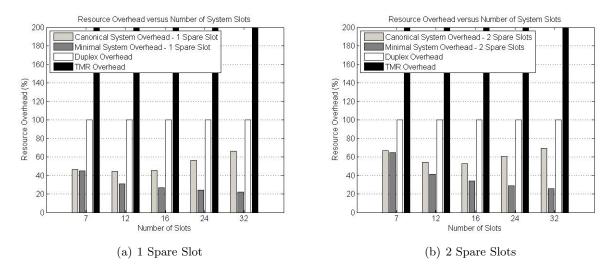

A number of modern digital processing systems implement complex multi-mode applications with high performance requirements and strict operating constraints; examples include video processing and telecommunication applications. A number of these systems use increasingly large FPGAs as the implementation medium, due to reduced development costs. The combination of increases in FPGA capacity and system complexity has lead to a non-linear increase in system implementation effort. If left unchecked, implementation effort for such systems will reach the point where it becomes a design and development bottleneck. At the same time, the reduction in transistor size used to manufacture these devices can lead to increased device fault rates. To address these two problems, the Multi-mode Adaptive Collaborative Reconfigurable self-Organized System (MACROS) Framework and design methodology is proposed and described in this work. The MACROS Framework offer the ability for run-time architecture adaptation by integrating FPGA configuration into regular operation. The MACROS Framework allows for run-time generation of Application-Specific Processors (ASPs) through the deployment, assembly and integration of pre-built functional units; the framework further allows the relocation of functional units without affecting system functionality. The use of functional units as building blocks allows the system to be implemented on a piece-by-piece basis, which reduces the complexity of mapping, placement and routing tasks; the ability to relocate functional units allows fault mitigation by avoiding faulty regions in a device. The proposed framework has been used to implement multiple video processing systems which were used as verification and testing instruments. The MACROS framework was found to successfully support run-time architecture adaptation in the form of functional unit deployment and relocation in high performance systems. For large systems (more than 100 functional units), the MACROS Framework implementation effort, measured as time cost, was found to be one third that of a traditional (monolithic) system; more importantly, in MACRO Systems this time cost was found to increase linearly with system complexity (the number of functional units). When considering fault mitigation capabilities, the resource overhead associated with the MACROS Framework was found to be up to 85~% smaller than a traditional Triple Module Redundancy (TMR) solution.

### Acknowledgments

The author wishes to thank Dr. Lev Kirischain for sharing his knowledge and experiences, as well as providing support in his role as doctoral studies supervisor.

Additionally, the author wishes to acknowledge the support of the Department of Electrical and Computer Engineering at Ryerson University, the CMC Microsystems Corporation for providing all required CAD tools and systems, the Ontario Centers of Excellence (OCE), Federal Development (FedDev) Ontario, Connect Canada and the Natural Sciences and Engineering Research Council (NSERC) of Canada for financial support during the period of study.

The author also wish to acknowledge the support of industrial partners: MDA Space Missions, Soft-R US Inc. and UBS Ltd. for professional consulting and financial support. The author would like to acknowledge Dr. Karen Safaryan for his valuable consultations and assistance during the R&D projects and internship.

Finally, the author wishes to thank his family for the unwavering support they have provided across the years of study; the presented research would not have been possible without them.

# Contents

| List of Tables |       |         | 5                                                                            | xi  |

|----------------|-------|---------|------------------------------------------------------------------------------|-----|

| Lis            | st of | Figure  | es                                                                           | xii |

| 1              | Intr  | oducti  | ion                                                                          | 1   |

|                | 1.1   | Motiva  | ation                                                                        | 1   |

|                |       | 1.1.1   | Trends in Modern Digital System Design                                       | 1   |

|                |       | 1.1.2   | Manufacturing Trends and Device Resilience                                   | 6   |

|                | 1.2   | Modul   | lar And Dynamic Systems                                                      | 9   |

|                | 1.3   | Resear  | rch Objective                                                                | 11  |

|                | 1.4   | Contri  | ibution                                                                      | 13  |

|                | 1.5   | Thesis  | S Document Structure                                                         | 14  |

| 2              | Bac   | kgroui  | nd and Related Work                                                          | 16  |

|                | 2.1   | Introd  | luction                                                                      | 16  |

|                | 2.2   | Mecha   | anisms for Functional Unit Deployment and Relocation in Dynamically Recon-   |     |

|                |       | figural | ble Field-Programmable Gate Arrays (FPGAs)                                   | 17  |

|                |       | 2.2.1   | Dynamic Partial Reconfiguration in Modern FPGAs                              | 17  |

|                |       | 2.2.2   | Free Functional Unit Placement and Relocation                                | 20  |

|                | 2.3   | On-Ch   | nip Communication Architectures for Dynamic Partially Reconfigurable Systems | 3   |

|                |       | 2.3.1   | Shared Buses                                                                 | 23  |

|                |       | 2.3.2   | Network-on-Chip                                                              | 24  |

|                |       | 2.3.3   | Fully-Connected Crossbar                                                     | 26  |

|   |     | 2.3.4 Additional Communication Architectures                                                    | 27 |

|---|-----|-------------------------------------------------------------------------------------------------|----|

|   | 2.4 | Board and System-Level Run-Time Assembly and Integration Methods                                | 28 |

|   | 2.5 | Mechanisms for On-Chip Processor Assembly                                                       | 30 |

|   |     | 2.5.1 Configuration Control                                                                     | 31 |

|   |     | 2.5.2 Configuration Scheduling                                                                  | 31 |

|   |     | 2.5.3 Link Establishment                                                                        | 32 |

|   | 2.6 | Mechanisms for Functional Unit Integration                                                      | 33 |

|   | 2.7 | Fault Mitigation Using Dynamic Partial Reconfiguration of FPGAs                                 | 34 |

|   |     | 2.7.1 Scrubbing-Based Fault Mitigation                                                          | 35 |

|   |     | 2.7.2 Fault Mitigation Using Both Scrubbing and Relocation                                      | 36 |

|   | 2.8 | Summary                                                                                         | 38 |

| 3 | MA  | CROS Framework Operating Principles                                                             | 39 |

|   | 3.1 | Introduction                                                                                    | 39 |

|   | 3.2 | Run-time Architecture-to-Mode Adaptation                                                        | 40 |

|   | 3.3 | Digital Data Streams and Stream Workload                                                        | 43 |

|   |     | 3.3.1 Digital Data Stream Definition                                                            | 43 |

|   |     | 3.3.2 Stream Workload Structure                                                                 | 44 |

|   | 3.4 | Mode-Based Architecture Changes and Stream Workloads                                            | 45 |

|   | 3.5 | Seamless Run-Time Architecture Adaptations                                                      | 46 |

|   | 3.6 | Summary                                                                                         | 49 |

| 4 | Mu  | ti-mode Adaptive Collaborative self-Organized System (MACROS) Frame-                            |    |

|   | wor | k Mechanisms                                                                                    | 51 |

|   | 4.1 | Introduction                                                                                    | 51 |

|   | 4.2 | Functional Unit Deployment and Relocation                                                       | 52 |

|   |     | $4.2.1  \hbox{Partially Reconfigurable Region Structure and Functional Unit Placement} \ . \ .$ | 53 |

|   |     | 4.2.2 Free Functional Unit Deployment and Relocation                                            | 55 |

|   |     | 4.2.3 Functional Unit Deployment and Relocation in MACROS Framework Systems                     | 56 |

|   | 4.3 | On-Chip Communication Architectures                                                             | 57 |

|   |     | 4.3.1 Communication Requirements                                                                | 58 |

|   |     | 4.3.2   | Communication Infrastructure Analysis                                                    | 59 |

|---|-----|---------|------------------------------------------------------------------------------------------|----|

|   |     | 4.3.3   | MACROS Framework Communication Architecture                                              | 62 |

|   |     | 4.3.4   | Delay Variation Mitigation                                                               | 63 |

|   | 4.4 | On-Cl   | nip Assembly Mechanism                                                                   | 64 |

|   |     | 4.4.1   | Functional Unit Allocation and Configuration Scheduling Analysis                         | 65 |

|   |     | 4.4.2   | Connectivity Change Analysis                                                             | 67 |

|   |     | 4.4.3   | Non-Preemptive Connectivity Change Algorithms                                            | 69 |

|   | 4.5 | Functi  | ional Unit Integration Mechanisms                                                        | 74 |

|   |     | 4.5.1   | Scheduling and Data Synchronization in Multi-Mode and Dynamically Re-                    |    |

|   |     |         | configurable Pipe-Lined and Data-Flow Environments $\ \ldots \ \ldots \ \ldots \ \ldots$ | 75 |

|   |     | 4.5.2   | Scheduler Implementation Solutions                                                       | 75 |

|   | 4.6 | Centra  | al Versus Distributed Control Structures in the MACROS Framework                         | 79 |

|   | 4.7 | Summ    | ary                                                                                      | 82 |

| 5 | MA  | CROS    | Framework Architecture                                                                   | 83 |

|   | 5.1 | Introd  | uction                                                                                   | 83 |

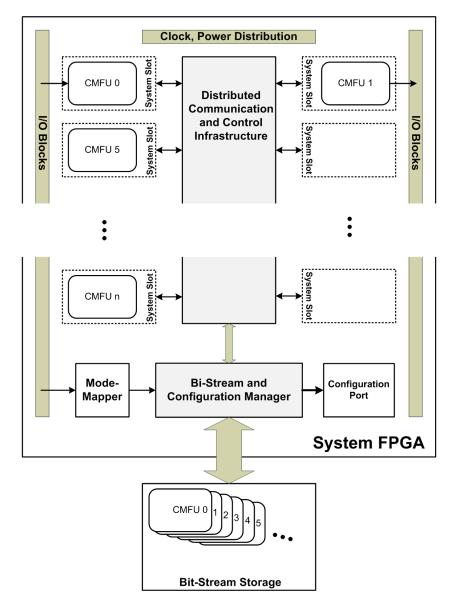

|   | 5.2 | Top-L   | evel MACROS Framework Architecture                                                       | 83 |

|   |     | 5.2.1   | Top-Level Architecture                                                                   | 84 |

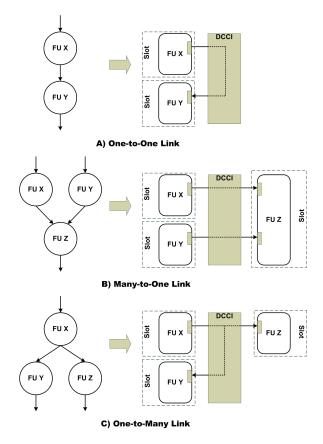

|   |     | 5.2.2   | Link Structures in the MACROS Framework                                                  | 86 |

|   |     | 5.2.3   | Data and Control Flow                                                                    | 87 |

|   |     | 5.2.4   | System-Level Customization                                                               | 89 |

|   | 5.3 | Collab  | porative Macro-Function Unit                                                             | 89 |

|   |     | 5.3.1   | Collaborative Macro-Function Unit (CMFU) Responsibilities and Behavior $$ .              | 90 |

|   |     | 5.3.2   | CMFU Structure                                                                           | 90 |

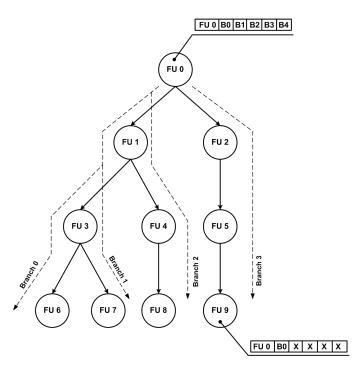

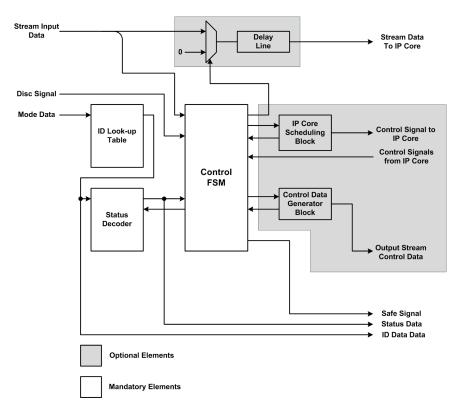

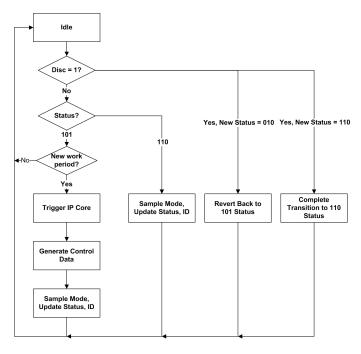

|   |     | 5.3.3   | Co-Op Unit Structure and Behavior                                                        | 93 |

|   |     |         |                                                                                          |    |

|   |     | 5.3.4   | CMFU Customization                                                                       | 97 |

|   | 5.4 |         | CMFU Customization                                                                       |    |

|   | 5.4 |         |                                                                                          |    |

|   | 5.4 | Distril | outed Communication and Control Infrastructure                                           | 98 |

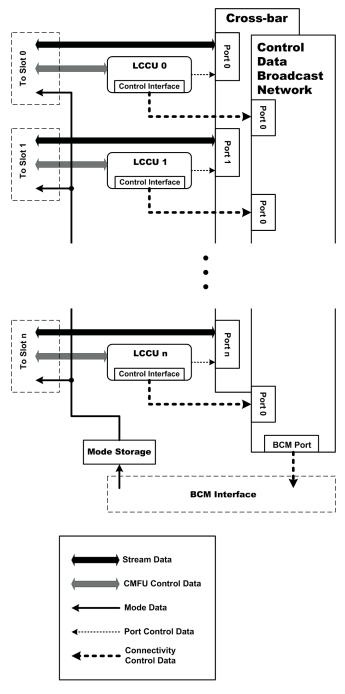

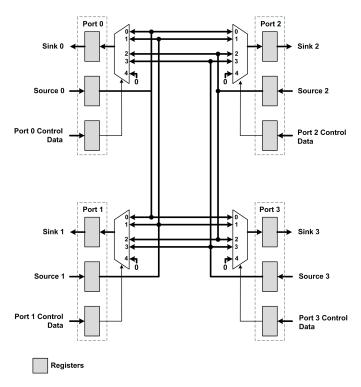

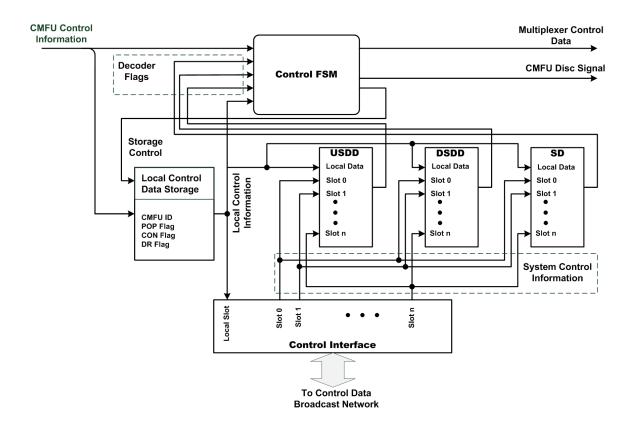

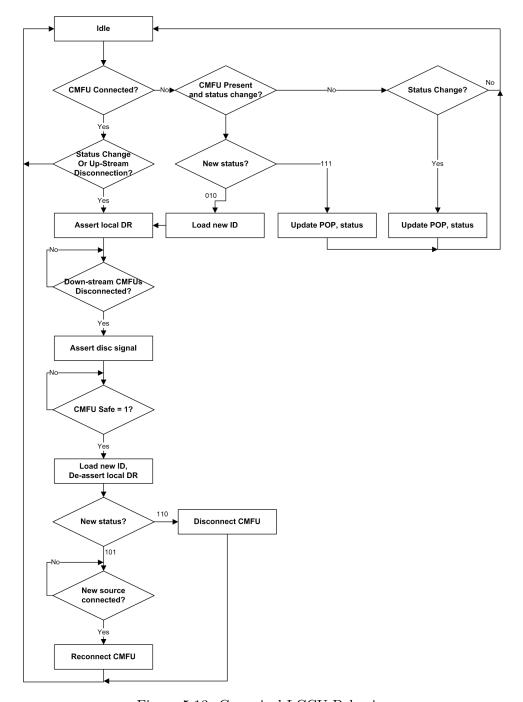

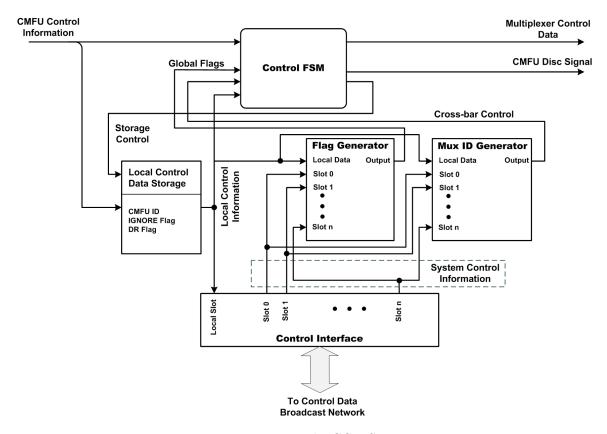

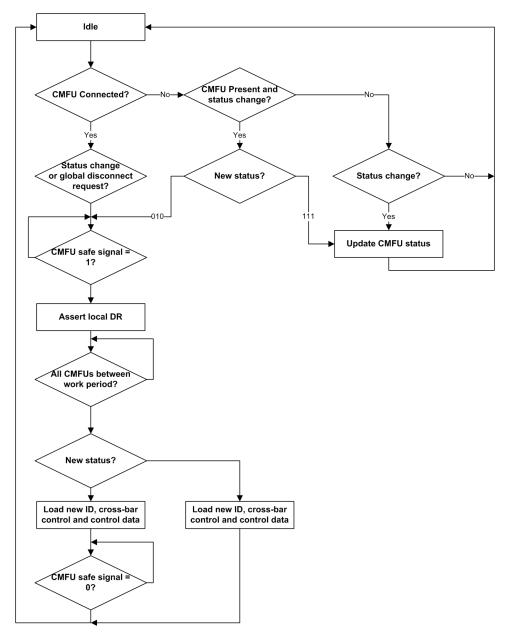

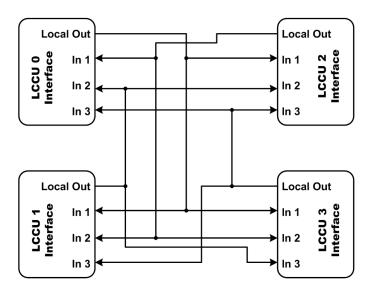

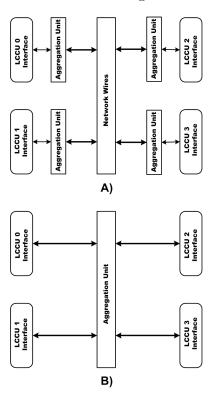

|   |     | 5.4.3   | Local Connection Control Unit                                            | 102 |

|---|-----|---------|--------------------------------------------------------------------------|-----|

|   |     | 5.4.4   | Control Data Broadcast Network                                           | 108 |

|   |     | 5.4.5   | DCCI Customization                                                       | 110 |

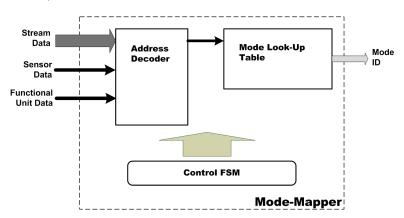

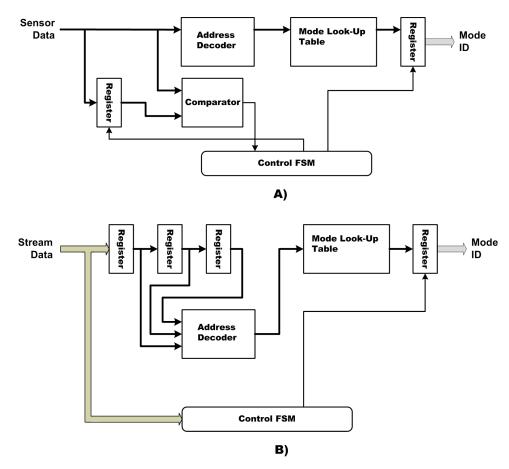

|   | 5.5 | Mode-   | Mapper                                                                   | 112 |

|   | 5.6 | Bit-str | ream and Configuration Manager                                           | 114 |

|   |     | 5.6.1   | Bit-stream and Configuration Manager (BCM) Responsibilities and Behavior | 114 |

|   |     | 5.6.2   | BCM Structure                                                            | 115 |

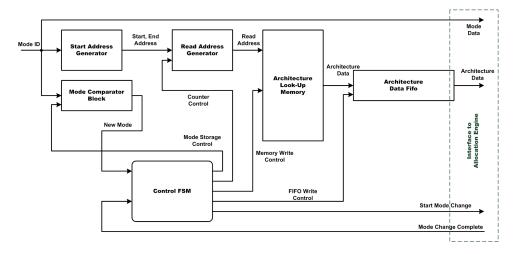

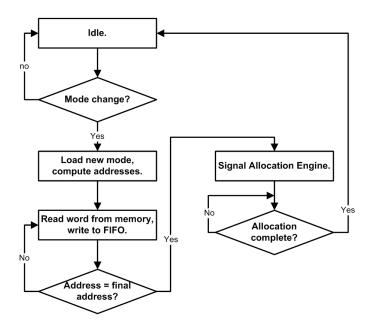

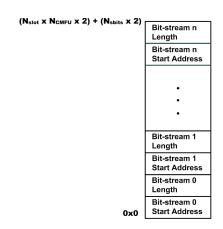

|   |     | 5.6.3   | Architecture Look-Up Engine                                              | 117 |

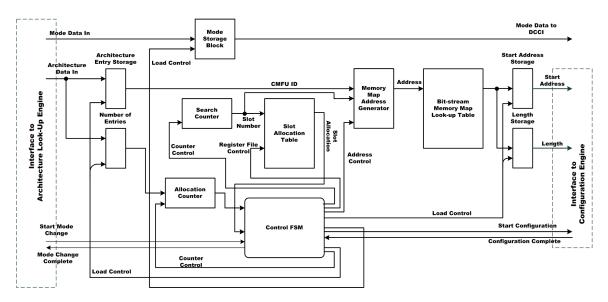

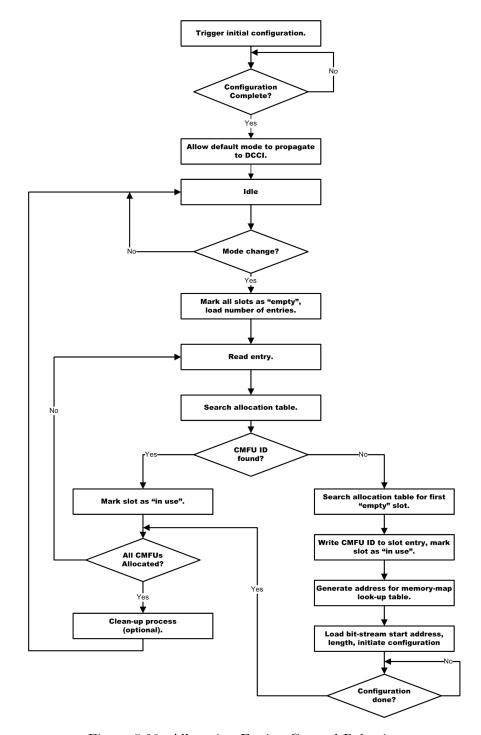

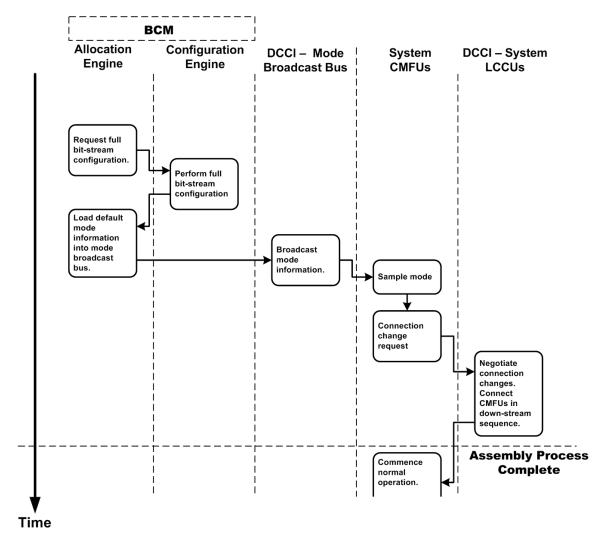

|   |     | 5.6.4   | Allocation Engine                                                        | 119 |

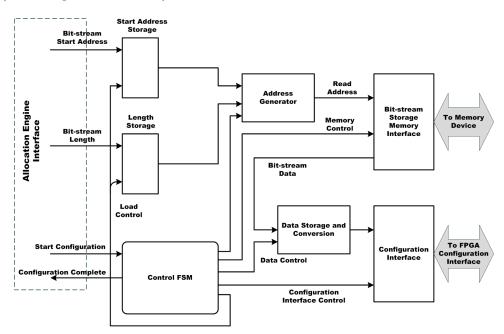

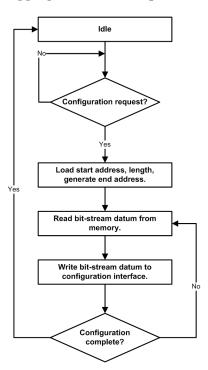

|   |     | 5.6.5   | Configuration Engine                                                     | 122 |

|   |     | 5.6.6   | BCM Customization                                                        | 124 |

|   | 5.7 | Summ    | ary                                                                      | 125 |

| 6 | MA  | CROS    | Framework Run-Time Behavior                                              | 127 |

|   | 6.1 | Introd  | uction                                                                   | 127 |

|   | 6.2 | Multi-  | Mode Application Behavior in MACROS Systems                              | 127 |

|   |     | 6.2.1   | System Start-Up                                                          | 128 |

|   |     | 6.2.2   | Normal Processing Operations                                             | 129 |

|   |     | 6.2.3   | Run-Time Mode-Based ASP Generation                                       | 130 |

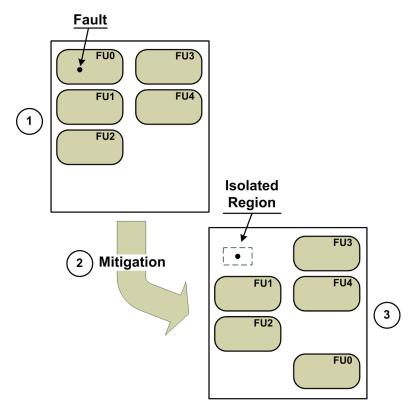

|   | 6.3 | Fault 1 | Mitigation Behavior in the MACROS Framework                              | 131 |

|   |     | 6.3.1   | Targeted Fault Model                                                     | 132 |

|   |     | 6.3.2   | MACROS Framework Fault Mitigation Principle                              | 133 |

|   |     | 6.3.3   | BCM Behavior for Fault Mitigation                                        | 134 |

|   |     | 6.3.4   | Relocation-Based Fault Mitigation Process                                | 136 |

|   |     | 6.3.5   | Extensions for Fault Tolerance in MACROS Framework Systems $\dots \dots$ | 137 |

|   | 6.4 | Summ    | ary                                                                      | 139 |

| 7 | MA  | CROS    | Framework Experiments                                                    | 141 |

|   | 7.1 | Introd  | uction                                                                   | 141 |

|   | 7.2 | Genera  | al Experimental Set-Up                                                   | 141 |

|   | 7.3 | Experi  | ment: Framework Verification and Performance Measurements                | 149 |

|              |        | 7.3.1 Experimental Application                                                | 143 |

|--------------|--------|-------------------------------------------------------------------------------|-----|

|              |        | 7.3.2 Experimental Architecture                                               | 44  |

|              | 7.4    | Experiment: Monolithic System Implementation Effort Measurement               | 49  |

|              | 7.5    | Experiment: Frameworks Resource Cost Measurements                             | 151 |

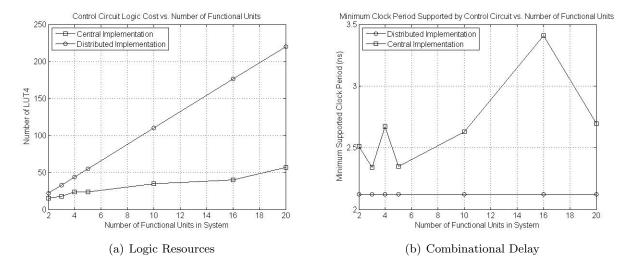

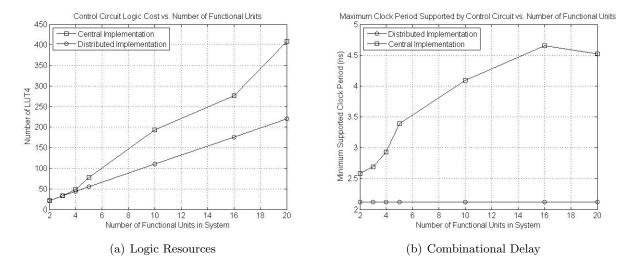

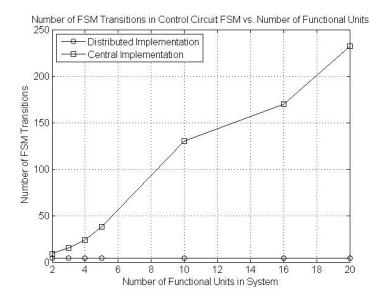

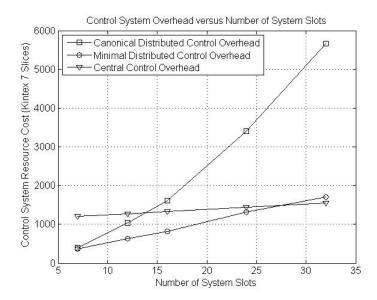

|              | 7.6    | Experiment: Central Versus Distributed Control System Analysis                | 152 |

|              | 7.7    | Experiment: Communication Architecture Performance Measurements               | 155 |

|              | 7.8    | Summary                                                                       | 157 |

| 8            | Res    | ults and Analysis 1                                                           | .58 |

|              | 8.1    | Introduction                                                                  | 158 |

|              | 8.2    | MACROS Framework Verification                                                 | 159 |

|              | 8.3    | Multi-Mode Run-Time Architecture Adaptation Timing Analysis                   | 160 |

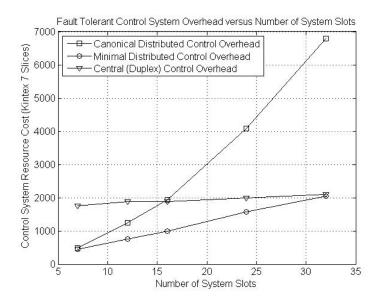

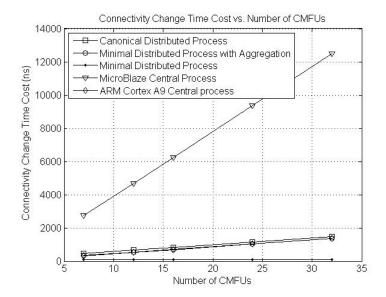

|              | 8.4    | Control System Performance and Resource Cost Analysis                         | 163 |

|              | 8.5    | Communication Architecture Performance and Resource Cost Analysis             | 171 |

|              | 8.6    | Modular Implementation Effort Analysis                                        | 174 |

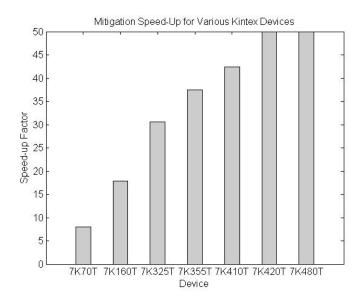

|              | 8.7    | Fault Mitigation Analysis                                                     | 179 |

|              | 8.8    | Complete Architectural Comparisons                                            | 182 |

|              | 8.9    | Summary                                                                       | 184 |

| 9            | Cor    | nclusion 1                                                                    | .86 |

|              | 9.1    | Problems in Modern Digital System Design and the Concept of Modular Dynamic   |     |

|              |        | Systems                                                                       | 186 |

|              | 9.2    | The MACROS Framework: Run-time Architecture Adaptation in Stream Processors 1 | 187 |

|              | 9.3    | Future Work                                                                   | 190 |

| Bi           | ibliog | graphy 1                                                                      | .92 |

| $\mathbf{G}$ | lossa  | $_{ m ry}$                                                                    | 206 |

# List of Tables

| 8.1  | Bit-Stream Sizes Configuration Times                                              |

|------|-----------------------------------------------------------------------------------|

| 8.2  | Application-Specific Processor (ASP) Generation Cost Values for the Canonical and |

|      | Minimal System                                                                    |

| 8.3  | Stream Interrupt Factors for the Canonical and Minimal System                     |

| 8.4  | MACROS Test System Resource Cost                                                  |

| 8.5  | Control Overhead in the MACROS Framework                                          |

| 8.6  | Crossbar Size in Relation to Number of Ports                                      |

| 8.7  | Network-on-Chip (NoC) and Crossbar Comparison                                     |

| 8.8  | Data-Rate per MHz for Various Communication Architectures                         |

| 8.9  | Implementation Times for Canonical System                                         |

| 8.10 | Implementation Times for Minimal System                                           |

| 8.11 | Static 1X Implementation Time on Various FPGA Devices                             |

| 8.12 | Static 1X Implementation Time Using Constraints (XC7VX980T) 176                   |

| 8.13 | Static 1X, 2X, 3X and 4X Implementation Times on XC7VX980T FPGA $$ 177            |

| 8.14 | Static 1X, 2X, 3X and 4X Implementation Times on XC7V980T FPGA $\dots \dots 177$  |

| 8.15 | Implementation Time Cost Using Hierarchical Design                                |

# List of Figures

| 1.1 | Multi-Mode Stream Processor Example                                              | 4  |

|-----|----------------------------------------------------------------------------------|----|

| 1.2 | Resource Capacity in Modern FPGA Devices                                         | 5  |

| 1.3 | Manufacturing Process for Virtex Device Families                                 | 7  |

| 2.1 | Configuration Memory Architectures                                               | 19 |

| 2.2 | Slot-Based and Region-Based Partially Reconfigurable Regions                     | 21 |

| 2.3 | Multiplexer-Based Shared Bus                                                     | 24 |

| 2.4 | Mesh and Fat Tree NoC Topologies                                                 | 25 |

| 2.5 | Basic Crossbar Structure                                                         | 26 |

| 2.6 | Multiplexer-Based Fully Connected Crossbar                                       | 27 |

| 3.1 | Traditional and Dynamically Reconfigurable System Implementations of Multi-Modal |    |

|     | Processing Circuits                                                              | 41 |

| 3.2 | Fault Mitigation in a Dynamic System                                             | 42 |

| 3.3 | Workload Example in a Video Processor                                            | 45 |

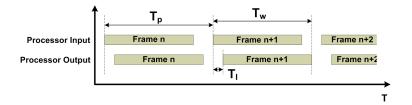

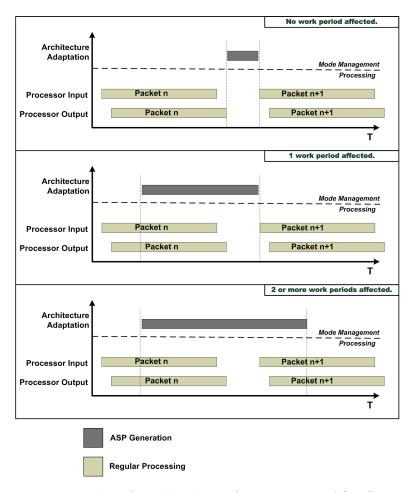

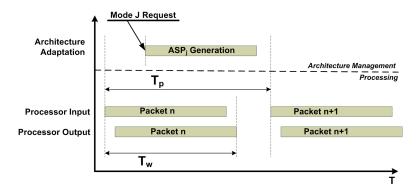

| 3.4 | Examples of Workload Interference Due to ASP Generation                          | 47 |

| 3.5 | Overlap of Processing and Configuration                                          | 48 |

| 4.1 | Module Communication Methods in Region-Based Systems                             | 54 |

| 4.2 | Effects on Static Nets Due to Bit-stream Manipulation                            | 55 |

| 4.3 | Static Net Routing For PRR Avoidance                                             | 56 |

| 4.4 | Comparison of Deployment and Relocation Methods and PRR Structures               | 57 |

| 4.5 | Concurrent Links in Stream Processing Systems                                    | 58 |

| 4.6  | Link Contention in Mesh NoC                                              | 60  |

|------|--------------------------------------------------------------------------|-----|

| 4.7  | Link Contention in Dynamic Systems                                       | 61  |

| 4.8  | Wire Length Variation in Dynamic Systems                                 | 64  |

| 4.9  | Delay Variation Conversion Into Latency Variation                        | 65  |

| 4.10 | Allocation Algorithms for Different Slot Configurations                  | 66  |

| 4.11 | Preemptive Mode Change                                                   | 68  |

| 4.12 | Non-Preemptive Mode Change                                               | 69  |

| 4.13 | Graph Representation of a Stream Processor                               | 70  |

| 4.14 | Example of the Canonical Connectivity Change Process                     | 71  |

| 4.15 | Canonical Connectivity Change Process                                    | 72  |

| 4.16 | Seamless Mode Change Using the Canonical Process                         | 73  |

| 4.17 | Minimal Connectivity Change Process                                      | 73  |

| 4.18 | Feasibility of Minimal Connectivity Change Process                       | 73  |

| 4.19 | Minimal Connectivity Change Process Example                              | 74  |

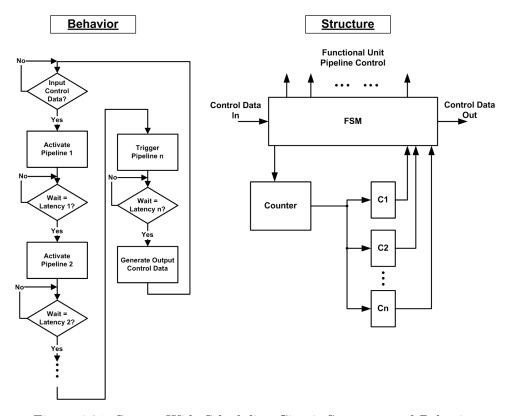

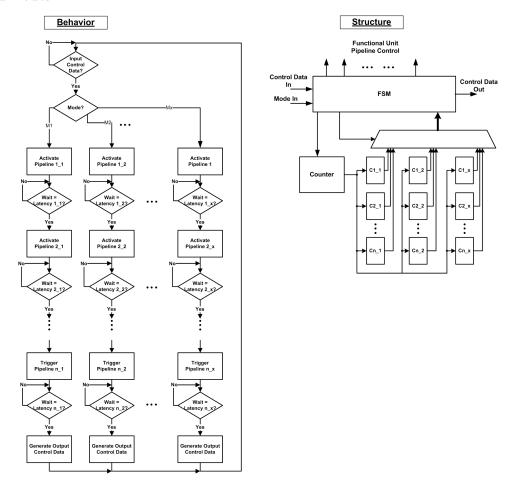

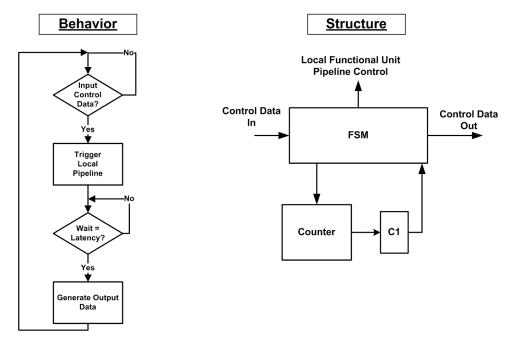

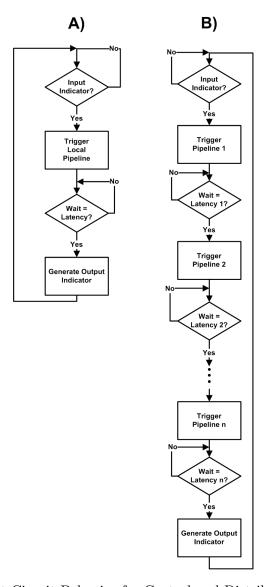

| 4.20 | Data-flow Synchronization in MACRO Systems                               | 76  |

| 4.21 | System-Wide Scheduling Circuit Structure and Behavior                    | 76  |

| 4.22 | Central Scheduling Circuit Structure and Behavior in Multi-Mode Scenario | 77  |

| 4.23 | Distributed Scheduling Circuit Structure and Behavior                    | 78  |

| 4.24 | Distributed Connectivity Control Concept                                 | 81  |

| 5.1  | MACRO System Architecture                                                | 85  |

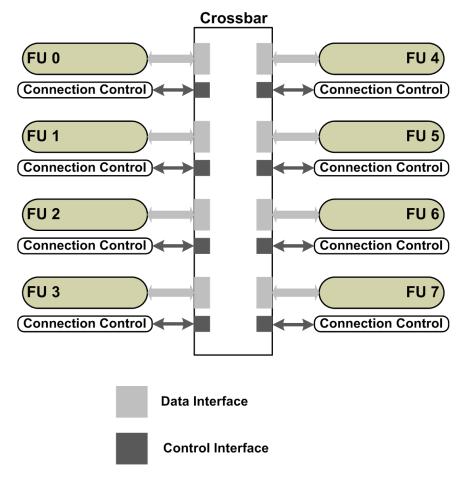

| 5.2  | Link Types Encountered in Pipe-lined and Data-Flow Systems               | 87  |

| 5.3  | Link Support in the MACROS Framework                                     | 88  |

| 5.4  | CMFU General Behavior                                                    | 91  |

| 5.5  | CMFU Structure                                                           | 91  |

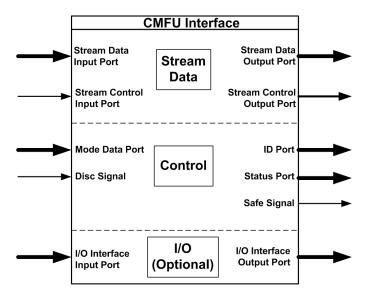

| 5.6  | CMFU Interface                                                           | 92  |

| 5.7  | CMFU Identification Process                                              | 93  |

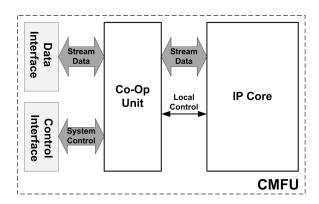

| 5.8  | Co-Op Unit Structure                                                     | 95  |

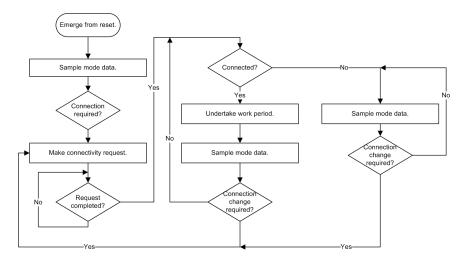

| 5.9  | Co-Op Unit Behavior                                                      | 96  |

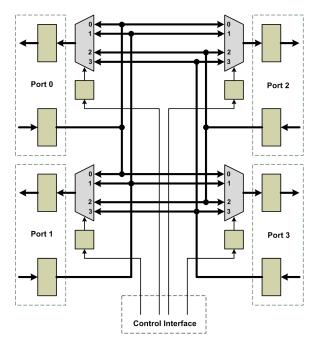

| 5 10 | DCCI Structure                                                           | 100 |

| 5.11 | 4-Port Crossbar Example                                                        |

|------|--------------------------------------------------------------------------------|

| 5.12 | Canonical Local Connection Control Unit (LCCU) Structure                       |

| 5.13 | Canonical LCCU Behavior                                                        |

| 5.14 | Minimal LCCU Structure                                                         |

| 5.15 | Minimal LCCU Behavior                                                          |

| 5.16 | Point-to-point Link Broadcast Network                                          |

| 5.17 | Aggregation Element-Based Broadcast Network: A) Multiple Aggregation Elements; |

|      | B) Single Aggregation Element                                                  |

| 5.18 | Mode-Mapper General Architecture                                               |

| 5.19 | Example Mode-Mapper Architectures                                              |

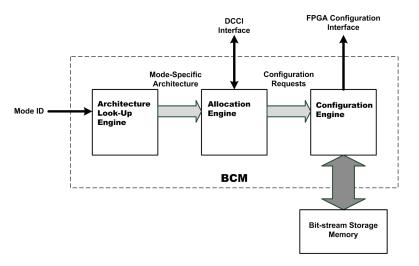

| 5.20 | BCM General Architecture                                                       |

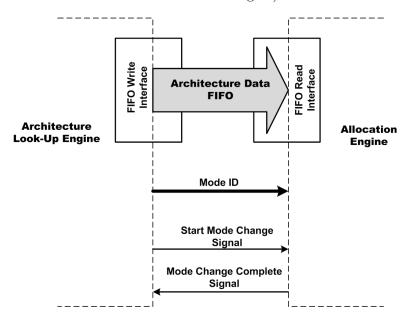

| 5.21 | Interface Between The Architecture Look-Up Engine and Allocation Engine 116    |

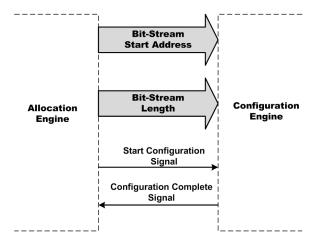

| 5.22 | Interface Between The Allocation Engine and Configuration Engine               |

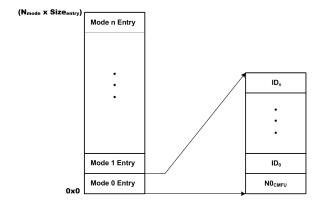

| 5.23 | Mode-Specific Architecture Look-Up Table Structure                             |

| 5.24 | Architecture Look-Up Engine General Architecture                               |

| 5.25 | Architecture Look-Up Engine General Behavior                                   |

| 5.26 | Memory Map Structure for the Bit-stream Storage Memory                         |

| 5.27 | Allocation Engine General Architecture                                         |

| 5.28 | Allocation Engine General Behavior                                             |

| 5.29 | Configuration Engine General Architecture                                      |

| 5.30 | Configuration Engine General behavior                                          |

| 6.1  | MACRO System Start-Up Process                                                  |

| 6.2  | Distributed Scheduling Process                                                 |

| 6.3  | Run-Time ASP Generation Procedure - CMFU Configuration                         |

| 6.4  | Comparison of Mitigation Procedures                                            |

| 6.5  | Distributed Nature of DCCI System                                              |

| 6.6  | Allocation Engine Behavior for Fault Mitigation                                |

| 6.7  | Relocation-Based Mitigation Procedure                                          |

| 7.1  | Experimental Setup Using an Integrated Logic Analyzer                          |

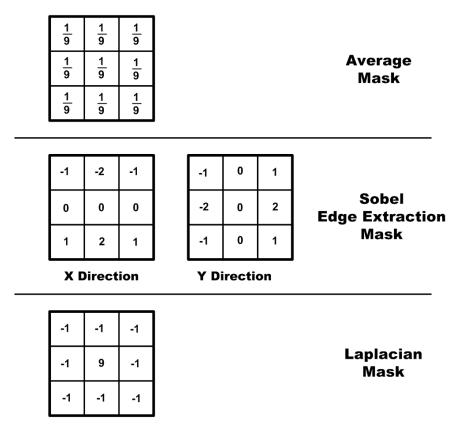

| 7.2  | Spatial Masking Procedure                                                           |

|------|-------------------------------------------------------------------------------------|

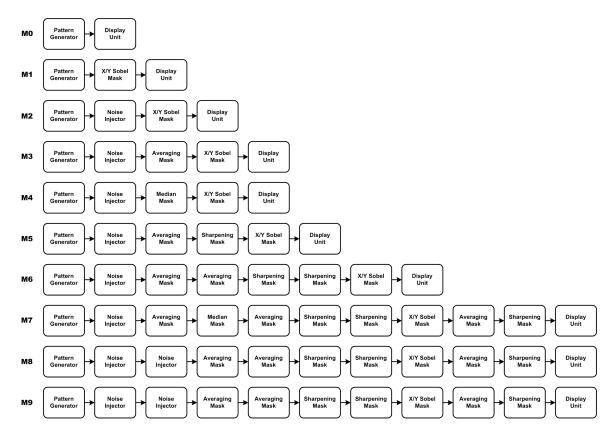

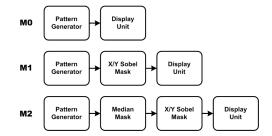

| 7.3  | Video Test Application                                                              |

| 7.4  | Application Spatial Masks                                                           |

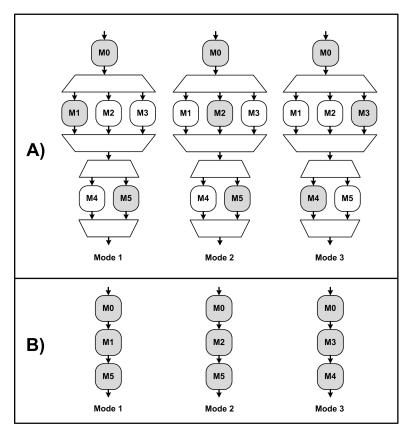

| 7.5  | Modes for Run-time Architecture Adaptation Tests                                    |

| 7.6  | Modes for Run-time Fault Mitigation Tests                                           |

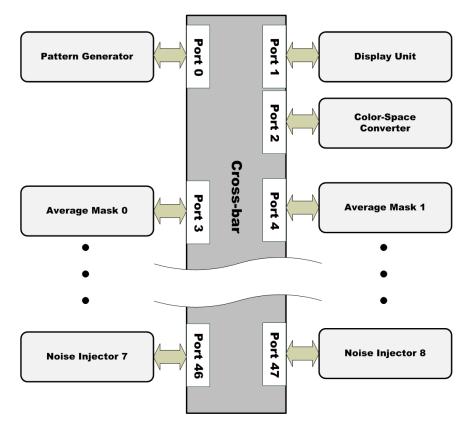

| 7.7  | MACROS Framework Test Architecture                                                  |

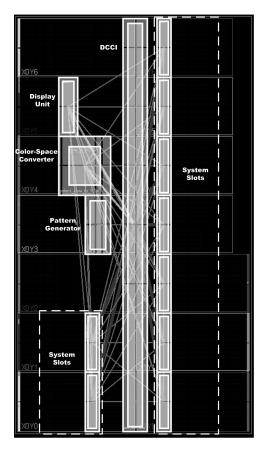

| 7.8  | System On-Chip Layout for Test System Using Canonical LCCUs                         |

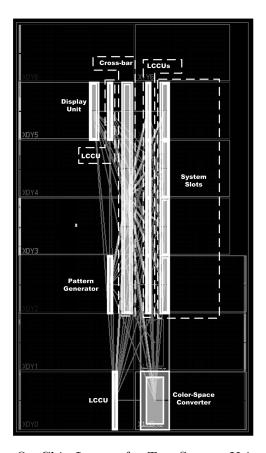

| 7.9  | System On-Chip Layout for Test System Using Minimal LCCUs                           |

| 7.10 | Static Test System                                                                  |

| 7.11 | Test Circuit Behavior for Central and Distributed Schedulers                        |

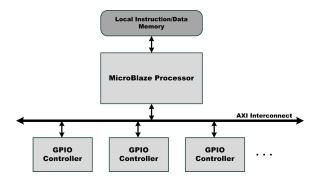

| 7.12 | Single Instruction-Based Processor Test System                                      |

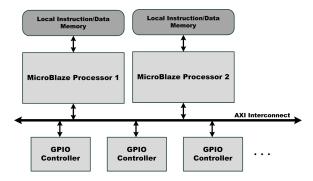

| 7.13 | Duplex Instruction-Based Processor Test System                                      |

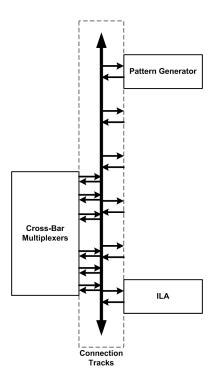

| 7.14 | Crossbar Performance Test System                                                    |

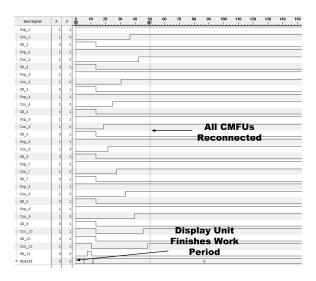

| 8.1  | Canonical Connectivity Change Procedure Timing Results                              |

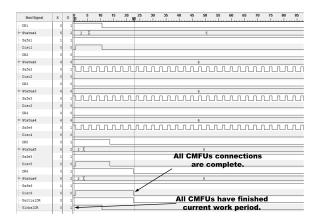

| 8.2  | Minimal Connectivity Change Procedure Timing Results                                |

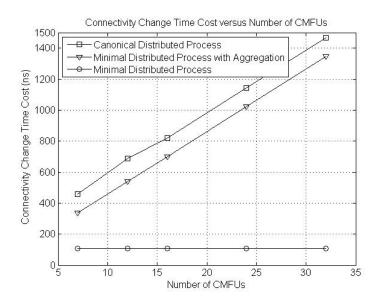

| 8.3  | Connectivity Change Time Cost for Various System Sizes                              |

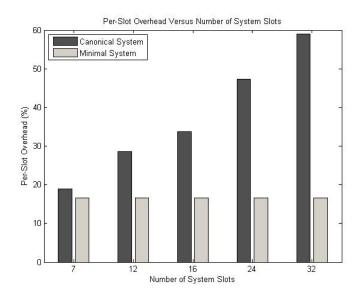

| 8.4  | Per-slot Overhead in Different Sized Systems                                        |

| 8.5  | Comparison Between Central and Distributed Control                                  |

| 8.6  | Comparison Between Central and Distributed Control in Multi-Mode System $\dots$ 167 |

| 8.7  | Finite-State Machine (FSM) State Transition Comparison Between Central and Dis-     |

|      | tributed Control in Multi-Mode Systems                                              |

| 8.8  | Control System Overhead Comparison for Various Sized Systems                        |

| 8.9  | Fault Tolerant Control System Overhead Comparison for Various Sized Systems 170     |

| 8.10 | Connectivity Change Time Cost Comparison Between Central and Distributed Ap-        |

|      | proaches                                                                            |

| 8.11 | Full Versus Partial Bit-stream Component Mitigation Speedup                         |

| 8 12 | Resource Overhead Comparison for Fault Mitigation Methods                           |

### Chapter 1

### Introduction

#### 1.1 Motivation

#### 1.1.1 Trends in Modern Digital System Design

#### **Application Complexity**

Integrated circuit manufacturing methods have advanced at a steady pace over the last 70 years, allowing for the inclusion of an ever increasing number of on-chip elements, through manufacturing method improvements and the miniaturization of component feature sizes. At the same time, applications have advanced in complexity at an even more rapid pace, such that the increased capabilities of integrated circuits (and the systems they create) have constantly been taxed to the limit.

Modern-day applications continue to exhibit the same complexity increases, in particular in the multimedia and telecommunications fields, which rely on complex real-time processing tasks, applied to high volumes of information in limited time periods (some modern applications can exhibit data rates in the hundreds of Gigabits per second). This complexity is increased further, as system requirements often impose hard constraints on size, cost, and power consumption, both in consumer-oriented systems as well as infrastructure components.

One of the ways in which modern applications have significantly increased complexity is through the incorporation of multiple modes of operation. The specifications for these applications include multiple variations in the application algorithm, designed to offer various features or trade-offs in various situations. Depending on the application, these variations in algorithm can number in the tens or hundreds, and when taken into account, they lead to extremely large, complex system implementations. Two examples are described briefly in the following paragraphs: the Digital Video Broadcasting - Satellite to Hand-held (DVB-SH) transmission standard and the H.264 Video Coding standard.

The DVB-SH standard (ETSI EN 302 583) describes a method of providing satellite communication services to hand held devices [1]. The standard specifies the framing structure of the data stream, the coding method and the modulation method. The system receives as input an Moving Pictures Experts Group (MPEG) Transport Stream which it frames, codes and then modulates for RF transmission. The standard specifies both satellite and terrestrial transmission; the terrestrial transmission path uses Orthogonal Frequency Division Multiplexing (OFDM) transmission, while the satellite path can use either OFDM or Time-Division Multiplexing (TDM) transmission [2]. Both transmission paths share a common section, however, where framing and coding takes place. This common path itself supports one of two modes of operation, based on whether a regular or low latency stream is received. The main operations performed in both cases are framing, Forward Error Correction (FEC) coding using the Third Generation Partnership Project 2 (3GPP2) turbo code [3], convolutional time interleaving, stream adaption for low latency streams and multiplexing between stream types.

In the modulation phase, each modulation scheme supports different data rates through different modulation variations. TDM transmission supports Quadrature Phase Shift Keying (QPSK), 8 Phase Shift Keying (PSK) and 16 Amplitude and Phase Shift Keying (APSK) modulation [2]. OFDM likewise supports QPSK modulation, as well as Quadrature Amplitude Modulation (QAM) 16 modulation [2]. Furthermore, the OFDM transmission mode supports 8k, 4k, 2k and 1k modes, each of which specifies a different number of carriers. By taking into account both transmission modes, the modulation variations, the different number of carriers for OFDM transmission, the emerging system exhibits a large number of variations in operating mode. The FEC coding step can be treated as a stand-alone application in its own right, and also includes multiple operating modes (see [3] for further details).

The ITU-T H.264 advanced video coding standard specifies a compression and coding technique which allows video information to be treated as general computer data, and be stored or transmitted

efficiently over various mediums [4]. The H.264 compression method relies on the extraction of differences between frames to achieve high compression rates; for any sequence of frames, only a subset of frames need to be processed completely, while remaining frames are represented by their difference from one (or more) of the complete frames. Complete frames are referred to as Intra-frames (I-frames), while difference-based frames are referred to as predictive-frames (P-frames) and bi-directional frames (B-frames, so named because they use both future and past frames to compute differences).

The H.264 standard incorporates the concept of profiles and levels [4]. Different profiles specify different compression variations as well as different coding methods. These profiles vary in complexity as well as the obtainable compression rate, and are aimed at different applications. Variations between profiles include the representation of color information (for example using various YCbCr variations), the bit-width used, whether B-frames are supported or the type of coding being used. In addition, each profile can specify different levels, which refer to the maximum bit-rate a decoder must support, in terms of frame rate and frame size. Currently, 11 profiles exist; some profiles including multiple variations.

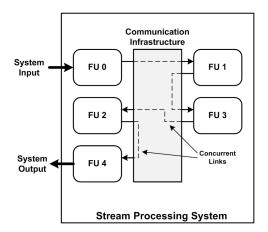

#### Implementation Methods

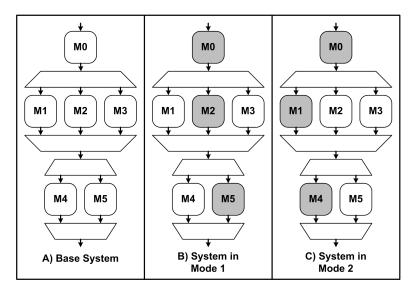

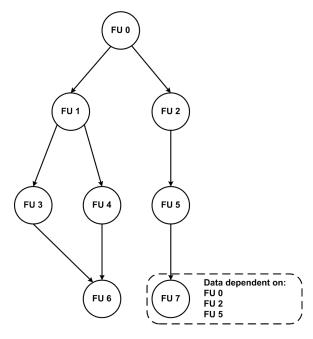

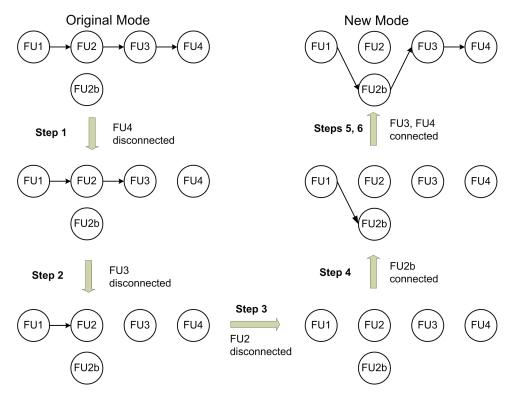

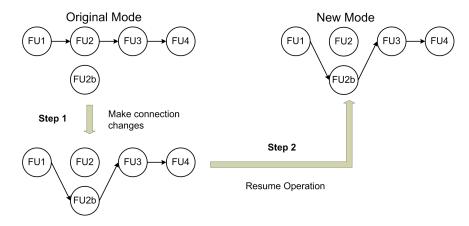

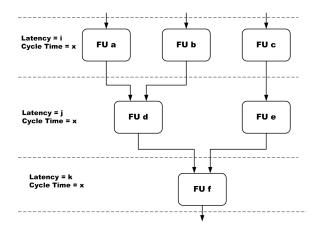

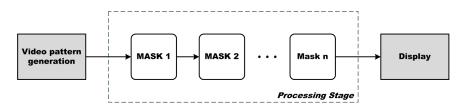

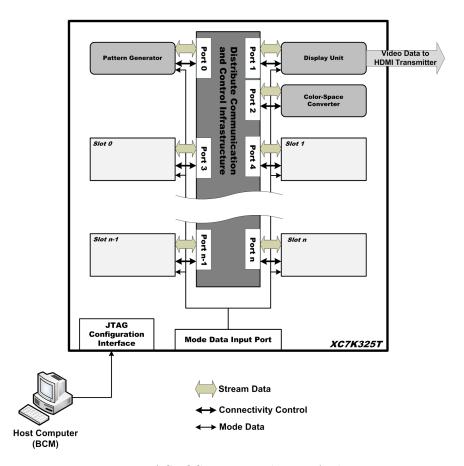

These types of applications (high data-rate stream processing) rely on macro-function specific pipeline circuits to achieve the necessary processing rate while meeting energy consumption requirements; sequential, instruction-based processors are not generally used in these instances, as their achievable performance is limited, and entails increased power consumption (due to the use of increased processor operating frequencies). Given that a specific functionality is implemented as a specific circuit, variations in functionality are implemented as multiple circuits. A multi-mode application-specific system is usually implemented as a collection of functional units, only some of which are active at any point in time (see Figure 1.1). These systems can be very large (in terms of system gates), and very complex to implement; part of this complexity stems from the fact that all functional units needed by the system must be present in the system at all times, regardless of whether they are active or not.

Traditionally, these types of systems were implemented as Application-Specific Integrated Circuits (ASICs), and incurred the costs associated with this approach (manufacturing, testing). How-

Figure 1.1: Multi-Mode Stream Processor Example

ever, the aforementioned advances in integrated circuit manufacturing technology have resulted in the emergence of a second implementation medium for digital systems. The capabilities of Programmable Logic Devices (PLDs), and in particular FPGAs have expanded in terms of the number and type of resources being integrated and the achievable system performance (logic delays and achievable operating frequencies).

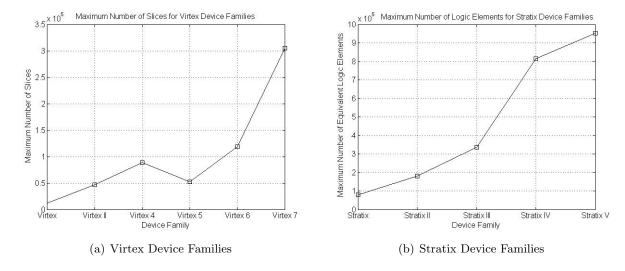

The pace at which FPGAs have grown is illustrated in Figures 1.2(a) and 1.2(b), which show the progression of logic capacity in the Virtex [5, 6, 7, 8, 9, 10] and Stratix [11, 12, 13, 14, 15] device families, offered by Xilinx and Altera Corporation, respectively; Slices are listed for Virtex devices and equivalent Logic Elements are listed for Stratix devices. Both figures show an almost continuous increase when going from one family to the next; in the case of the transition from Virtex 4 to Virtex 5, while the total number of slices drops slightly, the capacity of each slice is doubled. The actual system capacity is, in fact, larger, as micro-architectures have shifted from 4-input Look-Up Table (LUT) to 6-input ones [16, 17].

The above trends look set to continue: as outlined in the International Technology Road-Map for Semiconductors, feature sizes for on-chip logic are expected to continue dropping in the next 15 years, and device integration is expected to continue increasing [18]. There is no reason to assume FPGA devices will deviate from this trend; on the contrary, the two largest FPGA manufacturers are pursuing new manufacturing methods aimed at very large scale integration. Xilinx has introduced the use of the Stacked Silicon Interconnect (SSI) in the largest of the Virtex 7 FPGAs [10], while

Figure 1.2: Resource Capacity in Modern FPGA Devices

Altera is developing FPGA architectures targeting the Intel 14 nm Tri-Gate Process [19]; both these technologies will help increase the attainable device size.

As a result, due to both general manufacturing improvements as well as improvements in microarchitecture design and implementation, modern FPGAs have gotten closer to ASIC devices in

terms of accommodated performance and system size. In fact, FPGAs are now large enough to

accommodate complete Systems on Chip (SoCs), and incorporate heterogeneous components such

as memory blocks and dedicated multipliers to further facilitate this task. At the same time, the

design and implementation of systems on FPGAs is less expensive, complex and time-consuming

than ASIC implementations, due to the exclusion of manufacturing considerations; thanks to integrated Computer-Aided Design (CAD) tool-flows, a system designer can obtain a working prototype

quickly using FPGA implementation. When short and medium-length production runs are considered, the reduced design and implementation cost associated with FPGAs makes up for the

base cost of the FPGA itself, and has led to system designers increasingly adopting FPGAs as

implementation platforms instead of ASICs.

#### The Problem of Increasing Implementation Effort

The current situation can be summarized as follows: currently, FPGA devices can accommodate large systems-on-chip (exceeding 50 million system gates), and all indicators point towards a continued increase in their resource capacity. At the same time, there is no shortage of complex, high

data rate applications, which are being implemented as very large, monolithic systems; because of their reduced design and development cost, a number of such systems are implemented using FPGA devices. In essence, designers are driven to implement ever larger and more complex systems, which is currently possible thanks to ever larger FPGA devices which can accommodate said systems.

However, the continued increase of FPGA capacities and the systems they accommodate has exposed a limitation of the traditional design process being used: the effort associated with implementing large designs is increasing in a non-linear fashion. The normal design flow consists of synthesis, translation, placement and routing of a given design; of these four tasks, placement and routing belong to a class of problems know as NP-hard [20], meaning that the computation time for these tasks will increase exponentially in relation to the size of the circuits being implemented. This is due in large part to the fact that design implementation is reduced to the placement and routing of mostly fine-grain elements (look-up tables and D Flip-Flops). Implementation times for modern devices range from minutes to more than a day, for systems that can reach 50 million equivalent system gates; this increase in implementation time is not linear in relation to system size, despite various attempts to optimize and improve the process [21, 22, 23].

If application complexity and FPGAs size continue to increase as they have (and all evidence indicates that they will), then the effort required to implement the resulting systems onto the available devices (which look set to reach and then exceed 100 million system gates in the near future) will become a major bottleneck in FPGA-based on-chip system design.

#### 1.1.2 Manufacturing Trends and Device Resilience

#### Reduced Feature Size and Radiation-Induced Faults

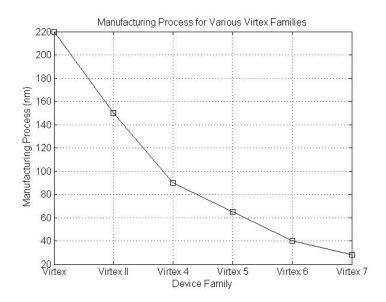

As stated previously, circuit integration has continued at a relatively steady pace, resulting in the continued on-chip resource capacity increase seen in the previous section. This increase in integration has been driven in large part by a continued decrease in the minimum feature size used in manufacturing processes [24]. Figure 1.3 shows this trend represented in FPGA manufacturing, showing the feature size of the manufacturing process used for the various Virtex families of devices [5, 6, 7, 8, 9, 10]; as can be seen, the feature size has dropped rapidly, meaning that transistors in a Virtex 7 device are much smaller than those found in the original Virtex family.

Figure 1.3: Manufacturing Process for Virtex Device Families

This reduction in transistor size has led to the creation of ever-larger devices (in terms of capacity); however, this reduction has also had less beneficial consequences. One of the fields which has seen a significant increase in FPGA adoption rates is that of space-borne computing platforms [25]. These types of systems benefit from the reduced development costs associated with FPGA system deployment, as well as the power efficiency of FPGA-based processing systems. However, these systems differ from their terrestrial counter-parts in that their operating environment is much more in-hospitable; specifically, radiation levels are much higher.

The increased radiation level increases the incidence of faults in FPGA-based systems; these faults take on both transient and permanent forms. Transient faults are caused by high-energy particle strikes to the FPGA fabric; they are referred to as Single Event Effects (SEEs) and come in the form of Single Event Upsets (SEUs) and Single Event Functional Interrupts (SEFIs) [26]. These effects can affect all resource types inside an FPGA, including configuration memory; when affecting logic and memory, their effect appears as temporary corruption of system data, and can be addressed through the use of Error-Correction Codes (ECCs). When configuration memory is affected, transient faults must be mitigated by re-writing the configuration memory of the device with the correct values, a process known as *scrubbing* [27].

Permanent faults can have multiple causes: radiation, manufacturing faults, thermal cycling. Radiation-induced faults are caused by large Total Ionizing Dose (TID) exposure [28], or single event latch-up. The thermal variation in space-borne environments can cause break-down in onchip structures. Finally, hidden manufacturing defects can affect some portion of the device; this problem can be further exacerbated by the thermal cycling process. Permanent faults cannot be eliminated; mitigation techniques rely on avoiding faulty regions of the device, most often through module redundancy.

The continued reduction in transistor size has increased the severity of radiation-induced permanent and transient faults. High-energy particle strikes can cause Multiple-Event Upsets (MEUs), and similar total ionizing doses can result in higher fault rates in modern devices. The reduction in transistor size has placed a much heavier emphasis on fault mitigation mechanisms in these types of systems, particularly for permanent faults.

#### The Problem of Increasing Fault Rates with Decreasing Transistor Size

Given the continued planned decrease in transistor sizes, the problem of radiation-induced transient and permanent faults looks set to migrate to terrestrial system. While the terrestrial environment does not exhibit the same radiation levels as orbital and inter-planetary systems, background levels of radiation nonetheless exist. This background radiation can affect on-chip structures if they are small enough; in fact, modern Dynamic Random-Access Memory (DRAM) devices already exhibit this problem. Such devices have taken advantage of improved manufacturing methods to provide increased memory capacity through reduction of the capacitive memory elements used; however, such systems have to rely on error-correction codes, as bit values are routinely affected by radiation effects [29, 30].

The continued reduction in transistor size looks set to increase the incidence of radiation-induced faults, both transient and permanent, in both space-borne and terrestrial applications. While fault-tolerant design methods do exist, they currently rely on module and system-level redundancy; taking this approach will not be sustainable as system size continues to increase, and the implementation complexity problem described above fully takes hold.

#### 1.2 Modular And Dynamic Systems

As described above, current design methods prescribe the implementation of multi-mode systems (in particular processing systems using application-specific architectures) as large, monolithic structures. When implemented using FPGA devices (an approach which is becoming common) these systems are translated into large, monolithic net-lists, which must then be mapped, placed and routed [31]. These net-lists are translated into device-specific primitives such as look-up tables, D flip-flops, memory blocks, multiplier blocks [32, 33, 34]; of these, look-up tables and D flip-flops have fine granularity in relation to the total system size, and they, very often, make up the majority of a design. Because of this, mapping, placement and routing tasks must operate primarily on large numbers of fine-grain elements while meeting various constraints (area or combinational delay), which makes these tasks NP-hard in nature. Modern CAD systems attempt to avoid this problem by using various heuristic approaches (for example, Simulated Annealing [21, 22]) to find near-optimal solutions for each task without an exhaustive search. However, the heuristic methods used must still search large solution spaces due to the fine-grained nature of the building blocks used.

As established in Section 1.1.1, multi-mode systems can be logically divided into a collection of on-chip functional units. These functional units can be considered to be coarse-grained building blocks of the system; however, as described above, during the implementation process they are reduced to their component building blocks (LUTs and flip-flops) and treated as large flat collections of small elements. If the modular nature of the design could be extended into the implementation phase, then the NP-hard nature of the implementation task could be controlled such that it would result in a reduced implementation effort. Specifically, the implementation task would be applied to smaller modules of the system (individual functional units), where the problem complexity would be limited by the reduced size of the design being implemented. In essence, rather than having to address one large NP-hard optimization problem, a designer would have to deal with a linear combination of small NP-hard problems.

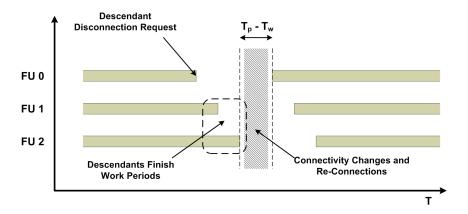

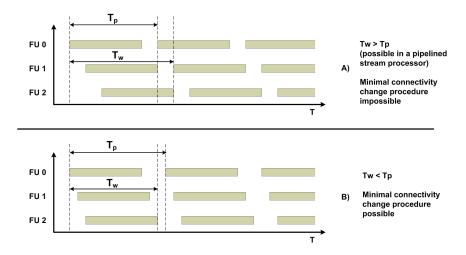

A second observation can be made about multi-mode systems: at any one time, only a subset of all system functional units are active, as dictated by the current operating mode, while all others are idle (see Figure 1.1 above). An ideal implementation of these systems would be one where the system always consists of only active functional units. This implies that such a system would be able to change its architecture to one of multiple variants at run-time; each architecture would correspond to a different system mode, and would consist of different combinations of Functional Units. Each mode-specific architecture would then be smaller in complexity and size than a traditional implementation containing all needed functional units.

The second potential problem afflicting modern FPGA-based digital systems is a potential increased incidence of faults (both transient and permanent) as transistor sizes continue to shrink. Transient fault can be mitigated through the use device reconfiguration (scrubbing); however, permanent faults cannot be mitigated as easily. The current defense against permanent faults is the use of various levels of redundancy; however, this approach relies on the addition of a large resource overhead to a system, and further exacerbates the problem of implementation complexity and effort.

A potential alternative mitigation solution to permanent system faults can be arrived at by extending the idea of run-time changing system architecture described above. If architectural differences could be extended to include the physical location of functional units inside a target device, then permanent faults could be mitigated through architecture changes, such that the faulty region of the device could be avoided.

These three theoretical ideas can be unified into the concept of a Modular and Dynamic System. Such a system would be implemented not as a single, monolithic design but as a collection of functional units; mapping, placement and routing activities would be applied to functional units as opposed to complete systems. These functional units would then be assembled and integrated into an ASP at run-time. Changes in mode would be reflected by changes in the combination of functional units present in the system, and the ASP being implemented. Permanent faults would be mitigated through re-location of functional units to different regions of the same device. Such a system would lead to reduced implementation effort due to the fact that the implementation is itself modular and limits the mapping, placement and routing tasks to smaller portions of the design (functional units). Furthermore, the system would exhibit increased cost-efficiency by only housing active functional units. Finally, the system would offer increased fault tolerance, in particular to permanent faults which are more difficult to address.

The current discussion is aimed at FPGA-based systems; conventional implementations using

FPGA devices employ device configuration as a simple start-up step, to be performed only once. However, the field-programmable nature of these devices means that configuration activities can be integrated into run-time system behavior; this, in turn, could lead to a dynamic system architecture, as described above. This approach would be limited in large part by the configuration time needed to program the FPGA being used (which may be prohibitively large). However, a number of modern FPGA devices support a feature called dynamic partial reconfiguration [35], which allows portions of the configuration memory to be written, while the rest of the device continues to operate normally; this capability can reduce the impact of configuration activities by limiting the amount of data being configured at any time. Thus, Modular and Dynamic Systems implemented using Dynamic Partially Reconfigurable FPGAs could offer a solution to the two problems introduced above.

#### 1.3 Research Objective

Based on the above preamble, the objective of the presented research was the development of a framework for the creation of Modular and Dynamic FPGA-based digital processing systems; the modular and dynamic nature of these systems would be achieved through run-time integration of dynamic partial reconfiguration activities. Such systems would permit modular implementation of macro-function oriented functional units, run-time generation of mode-specific architectures through assembly and integration of said functional units with a dedicated on-chip infrastructure and fault mitigation capabilities via on-chip functional unit relocation.

The main emphasis of the framework being introduced was the development of high data-rate stream processing systems; as described in previous sections, stream processing applications are becoming increasingly prevalent. More importantly, streaming applications (in particular high data rate ones) impose strict requirements on the system implementation; these requirements must be taken into consideration when implementing architecture adaptation procedures, lest these procedures interfere with and degrade the performance of such systems. Thus, the method being proposed was built from the ground up to address stream processing tasks. Having said this, the same design method is applicable to non-streaming applications, where the operating constraints may be different or more lax.

To accomplish the above objective, a number of uncertainties were identified which led to topics of research. These topics were investigated, and the results of these investigations were then combined into the framework being presented. Both the uncertainties and their associated topics of research are listed below.

- **Uncertainty 1:** What mechanism is used for the on-chip allocation and relocation of functional units, and what are the characteristics of this mechanism?

- **Topic 1:** Research into functional unit allocation and relocation mechanisms in dynamic partially reconfigurable FPGAs. Emphasis is placed on analysis of Dynamic Partial Reconfiguration (DPR) support in modern FPGAs, and mechanisms based on DPR to support functional unit allocation and relocation.

- **Uncertainty 2:** How can on-chip functional units communicate, and what impact will the dynamic nature of the system have on said communications?

- **Topic 2:** Research into available on-chip communication architectures. Emphasis is placed on support for high data-rate communications and the impact of dynamic architecture changes on communication activities.

- **Uncertainty 3:** How will a complete ASP be assembled from individual functional units?

- **Topic 3:** Research into processor on-chip assembly procedures and mechanisms using dynamic functional units. Emphasis is placed on communication link establishment in response to changing system modes.

- **Uncertainty 4:** Once the application-specific processor is assembled (i.e. is structurally complete) how will individual functional units (with individual behavior) be integrated into a *working* processor.

- **Topic 4:** Research into functional unit integration procedures and mechanisms. Emphasis placed on scheduling and synchronization of processing activities.

The topic of application analysis and segmentation into functional units was not one of the objectives of the presented research; this topic has received attention in recent years and a number

of research works and solutions have been proposed (e.g. [36], [37]). The presented research assumes the use of a separate mechanism for application segmentation and functional unit generation. Likewise, fault detection was *not* part of the proposed research objectives, as a significant body of work already exists addressing this topic [38].

#### 1.4 Contribution

The main contributions of the presented work are the identification of the two main problems described in Section 1.1 (those being increasing implementation complexity for large systems and a potential increase in the incidence of faults in these systems), the proposal of a potential approach to solving these problems for a class of applications (stream processing), the identification of mechanisms which can support this approach, and their investigation. This investigation consisted of the implementation of tests systems, and the collection of results; these results verified that the proposed approach A) can address the problems initially identified and B) can do so more effectively, for the given application class, than existing approaches.

The result of this research work is the proposal of the MACROS Framework, which specifies the architecture and behavior for a class of run-time reconfigurable stream processors. The systems are considered Multi-mode Adaptive due to their ability to adapt their on-chip architecture in response to changes in algorithm, data structure or constraints associated with a given application [39, 40]. They are Reconfigurable because they make use of the configuration capabilities of modern FPGA devices to implement on-chip architecture adaptation [41, 42]. Finally, the systems are referred to as Collaborative and self-Organized because they implement a distributed assembly and integration mechanism [43]; the mechanism functionality is divided between system functional units and a distributed control infrastructure. In this way, the number of central points of failure in the system is reduced [44, 45].

Systems built using the MACROS Framework have the ability to run-time self-assemble and self-integrated into mode-dependent application-specific processors using a library of macro-operation functional units (derived from pre-existing Intellectual Property (IP) Cores) and a dedicated on-chip infrastructure which supports these assembly and integration operations. Run-time mode changes are reflected in the system architecture through changes in the distribution of functional units

present and their interconnection. A second type of architecture change is also supported, whereby the physical on-chip location of functional units can change without affecting the functionality of the ASP being implemented.

The presented framework offers the following four primary benefits:

- 1. By supporting run-time assembly and integration of complete processors from parts (functional units and an infrastructure), the proposed framework allows for the *modular implementation* of a given system. In this way, the problem of increasing implementation effort can be mitigated by imposing limits on the complexity of mapping, placement and routing tasks; these tasks are applied to individual functional units and the on-chip infrastructure, as opposed to complete systems.

- 2. By supporting run-time architecture changes through functional unit allocation in response to mode changes, the proposed framework supports run-time architecture-to-task adaptation. This feature allows for improved power and cost efficiency when implementing complex stream processing systems.

- 3. By supporting functional unit relocation without affecting processor functionality, the proposed framework offers a fault mitigation mechanism which can address the increased incidence of both transient and *permanent* faults in modern FPGA-based systems. Secondly, by making functional unit relocation the primary repair mechanism in all fault cases, the repair time can be controlled and kept constant, regardless of the fault type encountered.

- 4. By explicitly targeting streaming applications, the proposed framework offers a method for the integration of run-time architecture adaptation operations into stream processing workloads while minimizing or eliminating the impact of these operations, thus allowing for seamless changes in system architecture with no interruption in processing tasks.

#### 1.5 Thesis Document Structure

The remainder of the document is organized as described below:

Chapter 2 will present background material and related works addressing the research topics

identified in Section 1.3. This chapter constitutes the first step in investigation process which will result in the selection of mechanisms for the MACROS Framework.

- Chapter 3 will present the basic principle of operation of MACROS Framework systems. The basic behavior identified in this chapter will then act as the specification for the class of systems defined by the proposed framework. Based on analysis of the presented behavior, fundamental characteristics and performance metrics for this system class are also established.

- Chapter 4 will present a comparative analysis of mechanisms in the four topics of research identified in Chapter 1. Using the material presented in Chapters 2 and 3, the analysis of Chapter 4 will result in a selection of specific mechanisms which will be integrated into the framework.

- Chapter 5 will present the full MACROS framework architectural template. The presented architecture will reflect the analysis and selection made in Chapter 4.

- Chapter 6 will describe the run-time behavior specified by the MACROS framework, consisting of run-time system assembly, mode-specific ASP generation and run-time fault repair procedures via functional unit relocation.

- Chapter 7 will describe the test procedures used to verify and analyzed the proposed design method, including the structure of constructed test systems and the measurement procedures used.

- Chapter 8 will present the results obtained, including performance and resource characteristics, as well as associated implementation effort. Where possible, these results yielded by the proposed design approach will be compared with existing approaches in the field. Chapter 8 constitutes the final step of the investigation process into the topics of research identified in Chapter 1, by validating the mechanism selection made in Chapter 4 through experimental results.

Chapter 9 will conclude the thesis.

### Chapter 2

## Background and Related Work

#### 2.1 Introduction

Having established a number of research topics in need of investigation as prerequisites to the chosen goal - a design method for digital processors with run-time adaptive architectures based on dynamic partially reconfigurable FPGAs - the first step in the investigation process is survey and analysis of existing work in the given field. This chapter will tackle the first of these two items, by presenting background information and surveys of existing works for the four topics identified in Chapter 1.

The chapter will begin with an analysis of mechanisms for functional unit deployment and relocation in modern FPGA devices. Following this, various architectures for on-chip communications will be presented; in each case, the basic principle of operation will be identified. Third, mechanisms for on-chip system assembly will be analyzed; the topics being addressed are configuration control and system link establishment. Once the topic of system assembly is covered, the related topic of system integration is addressed, paying particular attention to scheduling of processing activities and data synchronization.

Finally, the topic of Fault Tolerance methods using dynamic partial reconfiguration will be discussed. This form of fault tolerance actively relies on some or all of the other mechanisms identified above. Thus, a system that can support functional unit deployment and relocation, run-time assembly and integration can automatically support some forms of fault mitigation using these capabilities. However, existing research works have traditionally addressed Fault Tolerance

capabilities in such systems as a separate topic; thus, as a reflexion of this trend, they are presented in a separate, stand-alone section.

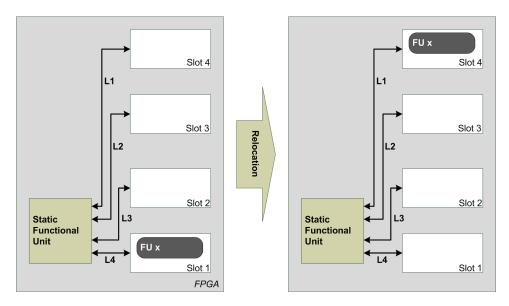

# 2.2 Mechanisms for Functional Unit Deployment and Relocation in Dynamically Reconfigurable FPGAs

Dynamic Partially Reconfigurable FPGAs allow run-time deployment of functional units via write procedures to portions of their configuration memory. The characteristics and limitations of this process must be established, given that this feature is the corner-stone of the proposed design method. For the systems being proposed, free functional unit deployment is desired, as it increases the flexibility of the system and allows more efficient utilization of system resources. Furthermore, functional unit relocation is a form of free deployment, in that the same functional unit is redeployed to a different region of the device. As such, the topics of free functional unit placement (the ability to deploy a functional unit to one of multiple on-chip locations) and relocation (the ability to move a deployed functional unit from one on-chip location to another) must also be investigated.

#### 2.2.1 Dynamic Partial Reconfiguration in Modern FPGAs

Modern FPGA devices incorporate a large number of configurable logic resources (most often implemented using look-up tables which act as programmable logic functions), augmented by additional types of resources: memory blocks, dedicated multiplication and adder blocks, input/output blocks, clock generation blocks and others [32, 33, 34, 46, 47]. In addition, an FPGA contains routing resources and configuration memory used to store the configuration information for all programmable resources. To accomplish a given circuit, FPGA basic blocks are configured and connected together to achieve the desired functionality. A given circuit will result in a global configuration for a given FPGA; the needed configuration information is stored in a file, commonly referred to as a configuration bit-stream.

FPGAs can be categorized according to the type of configuration memory they use; the two categories are based on the use of volatile (e.g. [10, 15]) and non-volatile (e.g. [48]) configuration memory. Given that the inclusion of non-volatile memory requires specialized manufacturing pro-

cesses, the majority of medium and large FPGAs currently available make use of volatile memory. These devices loose their configuration information when not powered, and require an initial configuration step prior to regular operation when powered on. To accommodate this step, such devices incorporate a number of configuration interfaces, including serial (e.g. Joint Test Action Group (JTAG) port, serial port) and parallel ones (e.g. [49]), all connected to a configuration controller. Corrupted bit-streams can lead to incorrect circuit structure, meaning that the implemented circuits either do not meet the original specification, or can outright damage the device. To avoid this, modern devices make use of Cyclic Redundancy Check (CRC) codes to ensure that the bit-stream structure remains intact as it is transferred to the configuration circuitry [49].

The principle of DPR is an extension of regular configuration support. The principle states that configuration memory can be made addressable (with a certain minimum addressable word), and portions of the configuration memory (and, therefore, the implemented functionality) can be changed while the rest of the device continues to operate. In this way, portions of the circuit structure can be changed at run-time, and yield run-time adaptive architecture changes. This feature can be extended further through the inclusion of an internal configuration access port on-chip (e.g. ICAP [49]); in this way, an FPGA device now has the ability to change its own architecture at run-time by accessing its own configuration memory.

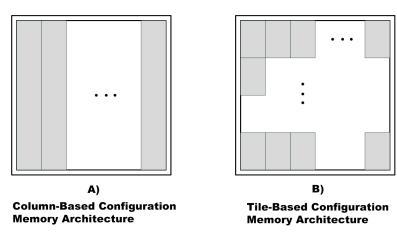

The partial reconfiguration capabilities of a given device are defined in large part by the minimum addressable configuration memory element of the device architecture. At the fine-grain end of the scale, certain devices allow bit-streams to address the configuration memory for single logic blocks; however, this approach leads to high addressing overhead for the configuration memory, and can become prohibitively expensive as the device size increases. At the coarse-grain end of the scale are column based devices (Virtex II [6]); in these devices, the minimum configuration memory addressable element controls a column of resources spanning the full height of the device (and some fixed width, see Figure 2.1 - A). This approach reduces addressing overhead, but at the cost of functional unit allocation flexibility.

A third approach lies in the middle, and has been adopted in a large number of modern FPGA families (Virtex 4, 5, 6 and 7 Series [7, 8, 9, 10]): tile-based configuration memories. In these devices, the minimum addressable configuration memory element is a tile, which controls a column of resources; however, this column does not span the full length of the FPGA (see Figure 2.1 -

Figure 2.1: Configuration Memory Architectures

B). In such devices, individual tiles contain a specific type of configurable resource (logic blocks, memories, multiply-accumulate units). Given the prevalence of tile-based architectures in modern devices, the remainder of this work will address exclusively tile-based architectures.

Beyond the basic considerations discussed above, the capabilities of dynamic partially reconfigurable FPGAs are manufacturer- and family-dependent. For the remainder of this document, all discussions will use as example Xilinx modern FPGA families (Virtex 4, 5, 6 and 7-series families [7, 8, 9, 10]). The reason for this is the fact that, for a long period of time, including the time when the presented research was first began, Xilinx devices were the only ones to support dynamic partial reconfiguration. However, the presented design method, and the class of systems it leads to can be implemented using any FPGA device which supports free functional unit placement and relocation (for example, the Stratix V FPGA [15]).

A dynamic partially reconfigurable system is logically and structurally divided into two parts: a static portion of the system, and dynamic portions (i.e. those that change via the loading of partial bit-streams at run-time). Certain infrastructure elements must always be in the static portion of the system, such as clock generation elements [35]; clock distribution to dynamic partially reconfigurable regions is controlled by the DPR CAD tool-chain, as it is dependent on device microarchitecture. Likewise, Input/Output (I/O) blocks are often considered static in nature, given that they exhibit fixed connections at the system level. Finally, if on-chip functional units are used to perform configuration activities (using an on-chip configuration access port), then these units must be static (they cannot change their own architecture). The remainder of a given device

can be segmented into one or more *Partially Reconfigurable Regions (PRRs)* [35]; these region are reserved for the housing of dynamic elements of the system, and are targeted by partial bit-streams. Dynamic functional units housed in these PRRs are referred to as *Partially Reconfigurable Modules (PRMs)* [35].

#### 2.2.2 Free Functional Unit Placement and Relocation

The structure of PRRs being deployed, as well as the method through which functional units are placed and relocated in these regions define the capabilities of a system, and impose requirements on its structure. The PRRs structure of a system can follow one of two approaches, as described below:

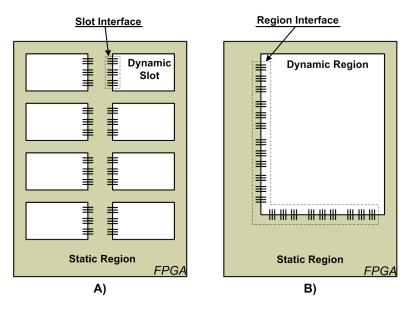

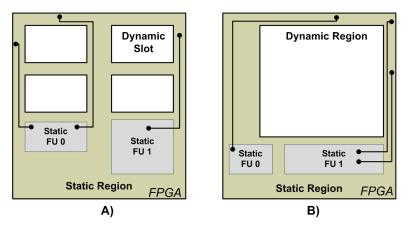

Slot-based approach: The slot-based system is the simplest conceptually: a set of partially reconfigurable regions inside the target FPGA are reserved as system slots at design time. Each system slot accommodates only one functional unit, regardless of the actual size of the unit; thus, the number of slots in the system must be equal to the maximum number of concurrent functional units. Each slot contains a set amount of various resources, and slots must be allocated such that all functional units fit in all slots (meaning that the available type and amount of resources per slot are enough for each module type). This system arrangement is shown in Figure 2.2 - A.

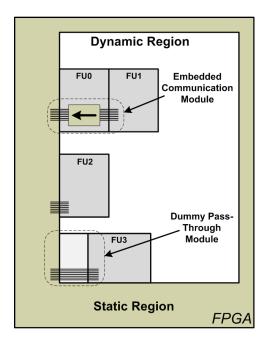

Region-based approach: The region-based approach reserves one or more large (usually rectangular) region inside the target FPGA. These regions will house all system functional units, with more than one unit housed in each region. In this approach, functional unit placement is dictated by the minimum addressable element of the target FPGA micro-architecture, the distribution of resources in the region and its boundaries. This type of functional unit deployment is shown in Figure 2.2 - B.

Likewise, the allocation and relocation of functional units to PRR can be implemented in one of two ways:

**Separate Bit-streams:** Each functional unit net-list is mapped to each slot region in the system, and bit-streams are generated for each mapping. This leads to  $number of slots \times 10^{-5}$

Figure 2.2: Slot-Based and Region-Based Partially Reconfigurable Regions

number of functional units bit-streams.

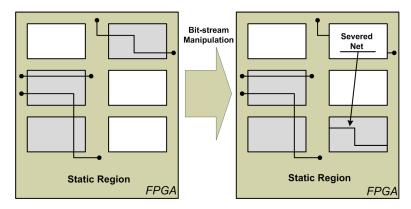

Bit-Stream Manipulation: Only one bit-stream is created per functional unit, mapped to a target region which can accommodate the given unit (assuming the right combination of resources is available). This base bit-stream is then manipulated at run-time, prior to being downloaded to the target FPGA, so that it targets a different region of the device.

Of the above combinations of PRR structures and allocation and relocation mechanisms, the simplest to implement is a slot-based approach using multiple separate bit-streams. This approach is currently directly supported by DPR CAD tool-chains [35]. However, this approach has two primary limitations: a large number of partial bit-streams must be stored, and the fixed nature of slots may lead to internal fragmentation and wasted resources. Multiple slot-based reconfigurable computing architectures have been proposed, including [50, 51, 52, 53, 54, 55, 56]

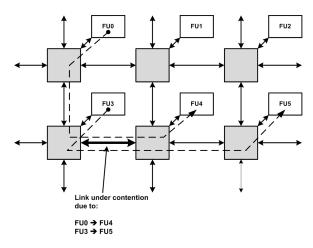

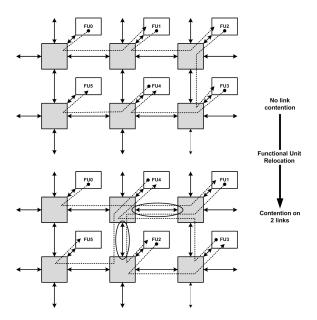

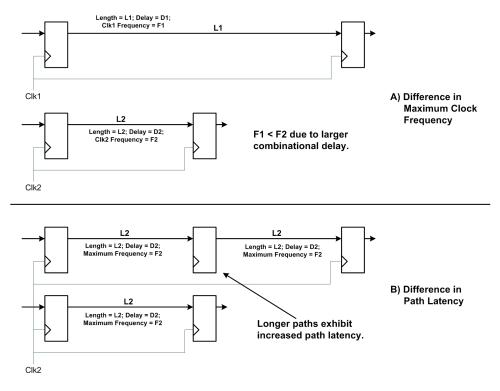

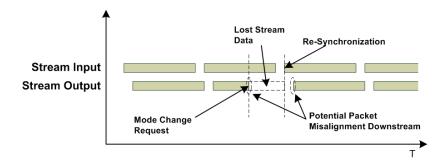

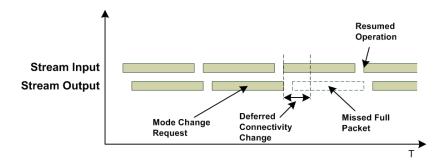

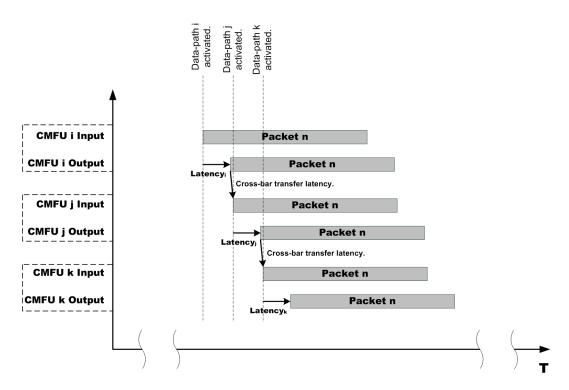

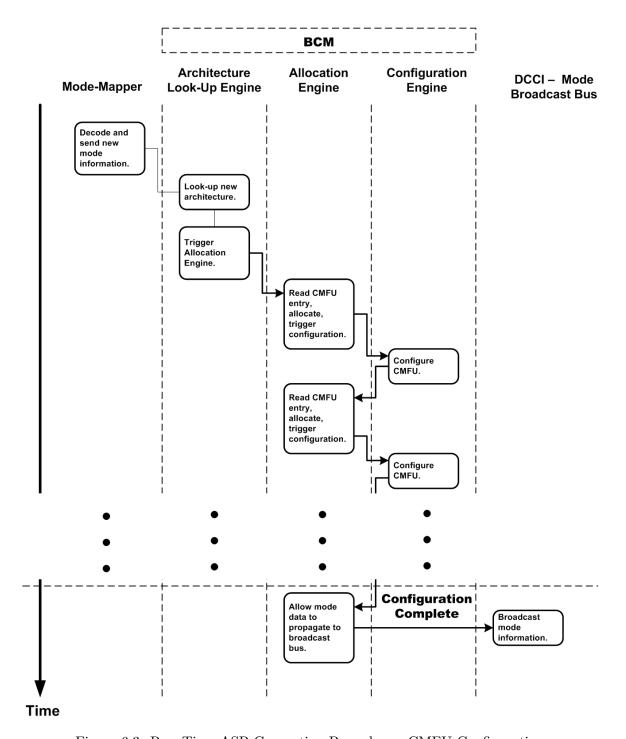

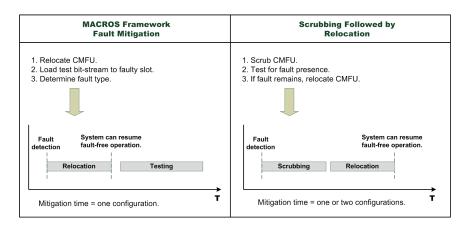

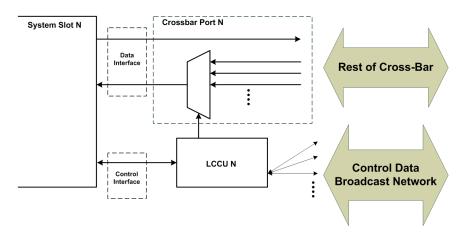

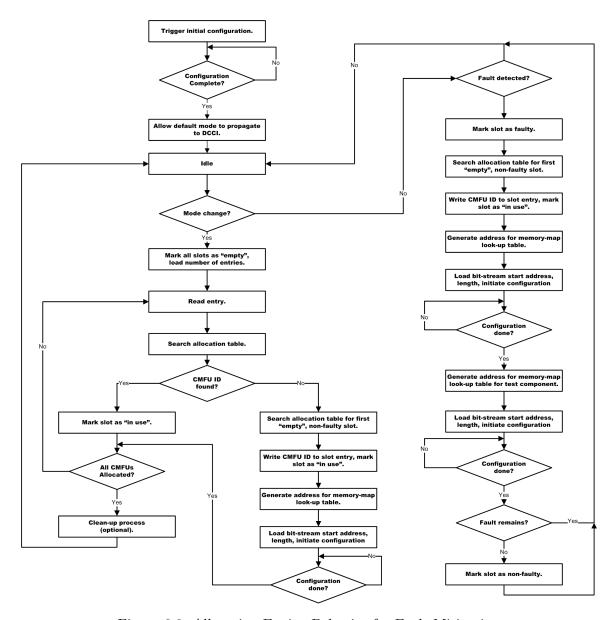

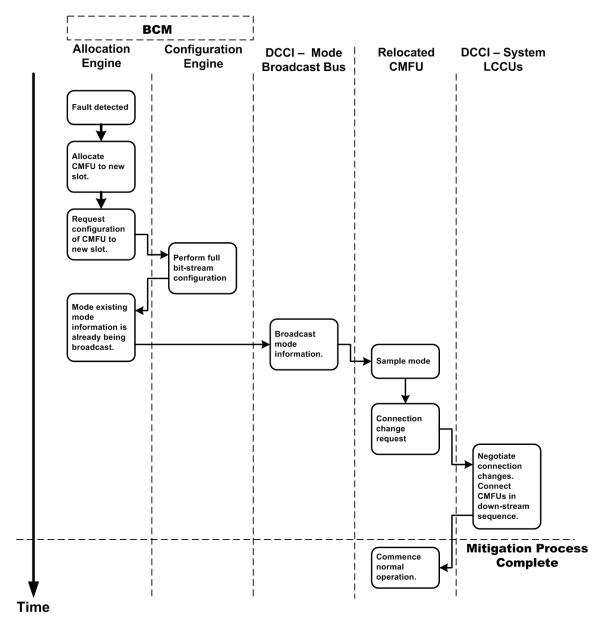

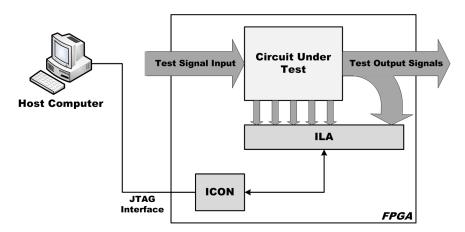

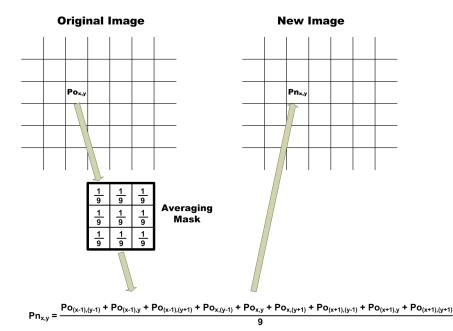

Because of the above limitations associated with slot-based PRRs and the use of separate bitstreams, mechanisms oriented towards region-based PRRs have been pursued; these mechanisms rely on bit-stream manipulation for both allocation and relocation. A method for functional unit allocation and relocation in column-oriented devices is presented in [57], targeting Virtex E devices; the proposed approach allows communication between modules through shared buses embedded in each unit, using tri-state buffers. An updated communication method is presented in [58], based on shift register embedded in deployed functional units. A column-oriented relocation method is presented in [59]; the method relies on bit-stream manipulation and can relocate full column bit-streams, as well as portions of a column via merging of target and destination bit-streams.