## Time-Mode Signal Processing and Application in $\Delta\Sigma$ ADC Design

Guangyu Zhu

A thesis submitted to the department of

Electrical and Computer Engineering

$\mathrm{in}$

the faculty of Engineering and Architectural Science

in partial fulfillment of the requirements for the degree of

Master of Science

Ryerson University Oct. 2014

Copyright © 2014 Guangyu Zhu All Rights Reserved

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

#### ABSTRACT

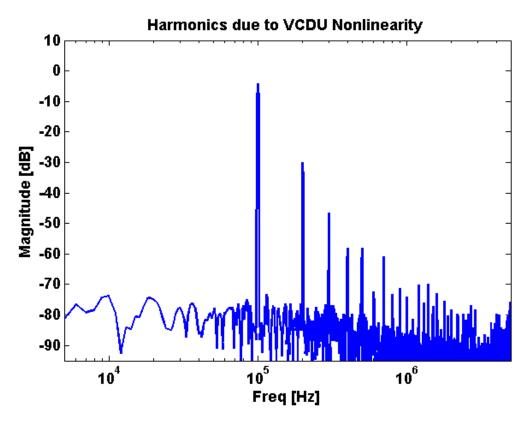

An all-digitally implemented  $1^{st}$  order and a  $2^{nd}$  order time-mode  $\Delta\Sigma$  ADCs are proposed and presented in this dissertation. Each proposed  $\Delta\Sigma$  ADC consists of a voltage-totime integration converter, a seven-stage gated ring oscillator functioning as a 3-bit quantizer, and a 7-stage digital differentiator that provides noise-shaping and frequency feedback. The  $2^{nd}$  order architecture differs from the  $1^{st}$  order by cascading two digital differentiators. The  $2^{nd}$  order design improves noise-shaping characteristic and SNDR. However it does not effectively suppress the harmonic tones due to the non-linear effect of the circuit components. Thus a detailed analysis of the nonlinear characteristics of the modulator is conducted. Designed in IBM 130 nm 1.2 V CMOS technology and with a 100 kHz 100 mV input, the  $1^{st}$  order time-mode  $\Delta\Sigma$  ADC exhibits an SNDR of 45.5 dB over 0.4 MHz bandwidth with power dissipation of 1.1mW. In comparison, the  $2^{nd}$  order ADC provides 54.8 dB SNDR, which equivalently offers an ENOB of 8.8 and it consumes 1.45 mW RMS power. The figureof-merit of the  $2^{nd}$  order time-mode  $\Delta\Sigma$  ADC is 407 pJ/step. Since the order of the system cannot be increased by simply cascading more differentiator stages, a time-mode  $\Delta\Sigma$  ADC architecture employing a time-mode loop filter is suggested in the last chapter. Several key building blocks including a time amplifier, time register and time adder for implementing such a loop filter are presented. The time amplifier has an input dynamic range of 50ps and provides a gain of 20. The implemented time register has a dynamic range of 5ns and a peak error of  $\pm 2\%$  over the 5ns full scale. The time adder remains high accuracy as long as the input time difference is no greater than 1.6ns.

Keywords: TMSP, time-difference variable, open-loop ADC, closed-loop ADC,  $\Delta\Sigma$  ADC, VTC, voltage-controlled delay unit, current-starved inverter, pulse generator, GRO, delay line, TDC, VCO-based quantizer, digital counter, digital differentiator, noise-shaping, SNDR, SFDR, OSR, ENOB, harmonics, FFT, time-mode loop filter, time amplifier, time register, gated delay cell, time adder, time accumulator.

#### ACKNOWLEDGMENTS

First and foremost I would like to express my sincere gratitude towards my supervisors Professor Fei Yuan and Professor Gul Khan for continuous support for my graduate study and research. Specially I'd like to thank Prof. Fei Yuan for his invaluable advice, countless constructive ideas and feedback throughout my graduate study. I thank my colleagues Yushi Zhou and Shaul Peker for offering me kindly help with the CAD tools and useful suggestions on the chip tape-out. This dissertation would not come to completion without the help and support from these aforementioned individuals.

I appreciate the opportunity offered by the department to pursue my M.A.Sc. degree at Ryerson University. I gratefully acknowledge the funding from the Ontario Graduate Scholarship in Science and Technology and fabrication services and CAD tools from CMC Microsystems.

Finally, I want to thank my dearest parents. Without their financial supports over the past 6 years, I would never be able to obtain my Bachelor's degree and M.A.Sc. degree in electrical engineering in a Canadian Educational Institute.

# Table of Contents

| Li            | st of                | Tables                                          | xiii |

|---------------|----------------------|-------------------------------------------------|------|

| $\mathbf{Li}$ | st of                | Figures                                         | xv   |

| $\mathbf{Li}$ | st of                | Abbreviations                                   | xix  |

| 1             | Intr                 | roduction                                       | 1    |

|               | 1.1                  | Motivation                                      | 1    |

|               | 1.2                  | Overview of Time-Mode Signal Processing         | 2    |

|               | 1.3                  | Current Literatures on Time-Mode ADC            | 3    |

|               | 1.4                  | Thesis Outline                                  | 4    |

| <b>2</b>      | $\operatorname{Tim}$ | ne-Mode ADC Design                              | 5    |

|               | 2.1                  | Conventional ADC and Design Specifications      | 5    |

|               |                      | 2.1.1 Introduction to Conventional ADC          | 5    |

|               |                      | 2.1.2 ADC Performance and Design Specifications | 7    |

|               | 2.2                  | Introduction to Time-Mode ADC                   | 9    |

|               |                      | 2.2.1 Open-Loop Time-Mode ADC                   | 9    |

|               |                      | 2.2.2 Closed-Loop ADC                           | 13   |

|               | 2.3                  | Summary on Time-Mode ADC                        | 16   |

|               |                      |                                                 |      |

### 3 Time-Mode ADC Circuit Components

|   | 3.1 | Voltag           | ge-to-Time Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

|---|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 3.1.1            | Direct VCDU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18 |

|   |     | 3.1.2            | Current-Starved VCDU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 |

|   |     | 3.1.3            | Summary on VTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19 |

|   | 3.2 | Time-            | Mode Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 |

|   |     | 3.2.1            | Regenerative Time Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

|   |     | 3.2.2            | DLL-based Time Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 |

|   |     | 3.2.3            | Charge-Pump Time Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|   |     | 3.2.4            | Dual-Slope Time Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24 |

|   | 3.3 | Time-            | to-Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 |

|   |     | 3.3.1            | Direct-Counter TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26 |

|   |     | 3.3.2            | Delay-Line-based TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

|   |     | 3.3.3            | Direct-Counter TDC with Gated-Delay Interpolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28 |

|   |     | 3.3.4            | Delay-Line TDC with Sub-Gate Delay Interpolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28 |

|   |     | 3.3.5            | Vernier Delay-Line TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |

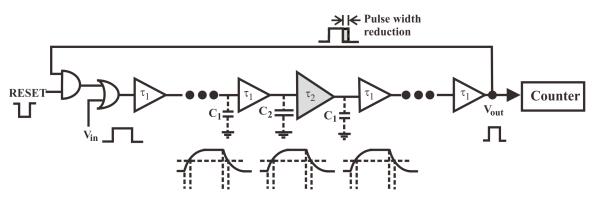

|   |     | 3.3.6            | Pulse-Shrinking TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

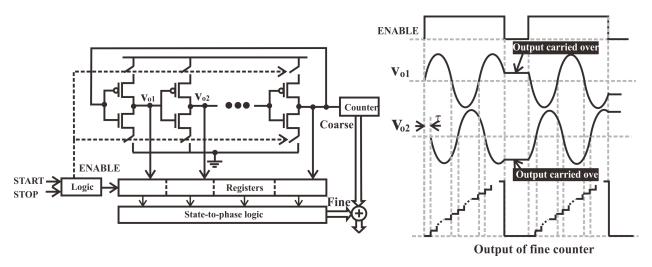

|   |     | 3.3.7            | Gated-Ring-Oscillator-based TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

|   | 3.4 | Summ             | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36 |

| 4 | Pro | $\mathbf{posed}$ | Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

|   | 4.1 | Prior            | Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

|   |     | 4.1.1            | Single-Bit Closed-Loop Time-Mode $\Delta\Sigma$ ADC $\hfill \hfill $ | 37 |

|   |     | 4.1.2            | Multi-bit Time-Mode $\Delta\Sigma$ ADC with VCO-based Qauntizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 |

|   |     | 4.1.3            | Thesis Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41 |

|   | 4.2 | Propo            | sed All Digital 1 <sup>st</sup> Order Time-Mode $\Delta\Sigma$ ADC $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42 |

|    |       | 4.2.1   | System Model                                                                                       | 42 |

|----|-------|---------|----------------------------------------------------------------------------------------------------|----|

|    |       | 4.2.2   | Frequency Domain View and Analysis                                                                 | 43 |

|    | 4.3   | Circui  | t Implementation                                                                                   | 45 |

|    |       | 4.3.1   | Voltage-to-Time Integrator                                                                         | 45 |

|    |       | 4.3.2   | Pulse Generator                                                                                    | 46 |

|    |       | 4.3.3   | Gated-Ring-Oscillator                                                                              | 47 |

|    |       | 4.3.4   | Digital Differentiator                                                                             | 50 |

|    |       | 4.3.5   | Frequency Feedback                                                                                 | 52 |

|    | 4.4   | Simula  | ation Result of the Proposed $1^{st}$ Order $\Delta\Sigma$ ADC $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 54 |

|    | 4.5   | Design  | n of $2^{nd}$ Order $\Delta\Sigma$ ADC                                                             | 56 |

|    |       | 4.5.1   | System Model and Frequency Domain Analysis                                                         | 56 |

|    |       | 4.5.2   | Simulation Result                                                                                  | 57 |

|    | 4.6   | Other   | Time-Mode Circuit Components                                                                       | 58 |

|    |       | 4.6.1   | Time Amplifier                                                                                     | 58 |

|    |       | 4.6.2   | Time Register                                                                                      | 58 |

|    |       | 4.6.3   | Time Adder                                                                                         | 59 |

|    | 4.7   | Summ    | ary on Proposed Works                                                                              | 69 |

| 5  | Disc  | cussion | and Conclusion                                                                                     | 71 |

| 6  | Futu  | ure Wo  | orks                                                                                               | 75 |

| Bi | bliog | raphy   |                                                                                                    | 77 |

# List of Tables

| 2.1 | Performance comparison of open-loop time-mode ADCs      | 12 |

|-----|---------------------------------------------------------|----|

| 2.2 | Performance comparison of closed-loop time-mode ADCs    | 15 |

| 3.1 | Performance comparison of time amplifiers               | 25 |

| 3.2 | Performance comparison of time-to-digital converters    | 35 |

| 4.1 | Performance comparison of time-mode $\Delta\Sigma$ ADCs | 58 |

# List of Figures

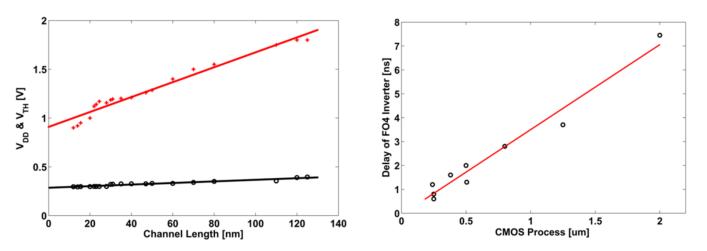

| 1.1 | Left: Power Supply and Threshold Voltage Scaling in CMOS Technology.<br>Right: Improvement in Delay for an FO4 Inverter due to Scaling                                                                                                                                                                                                   | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

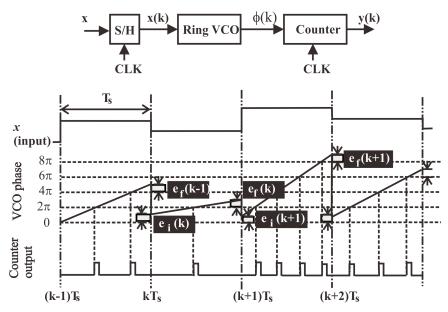

| 2.1 | VCO quantizer. The residue phase of phase $k - 1$ , denoted by $e_f(k - 1)$ , is carried over to phase k as its initial phase, denoted by $e_i(k)$ , i.e. $e_i(k) = e_f(k-1)$ .                                                                                                                                                          | 11 |

| 2.2 | $\Sigma\Delta$ ADC proposed by Straayer and Perrott [1]                                                                                                                                                                                                                                                                                  | 14 |

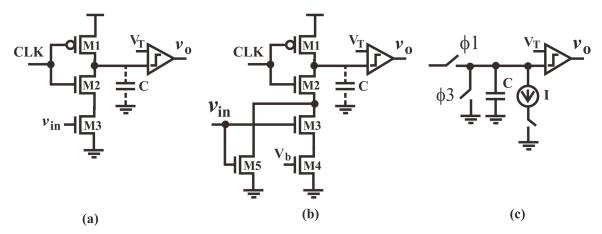

| 3.1 | Voltage-to-time converters. (a) Current-starved VTC with input-controlled variable resistor M3. (b) Current-starved VTC with improved linearity and conversion gain. (c) Sample-and-hold VTC. The sampling capacitor is charged in phase $\phi_1$ , drained in phase $\phi_2$ , and reset in phase $\phi_3$ to remove residual charge.   | 20 |

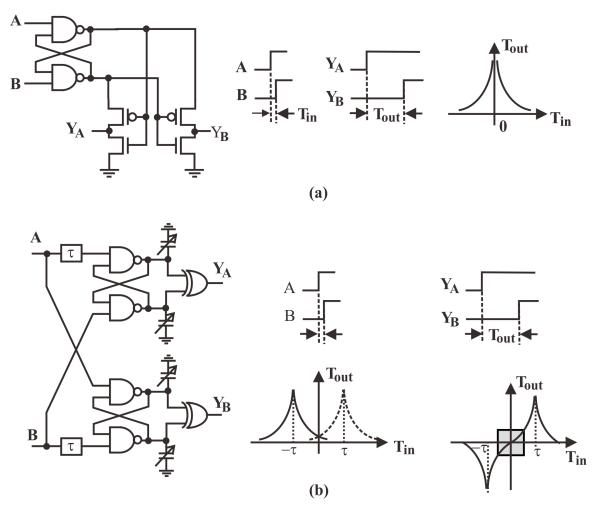

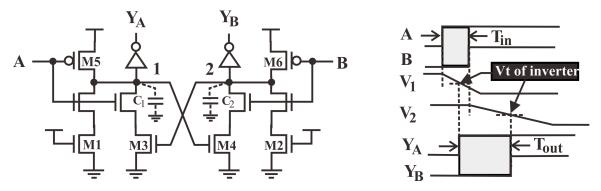

| 3.2 | (a) RS-latch time amplifier [2]. (b) RS-latch time amplifier with an improved input range [3]                                                                                                                                                                                                                                            | 21 |

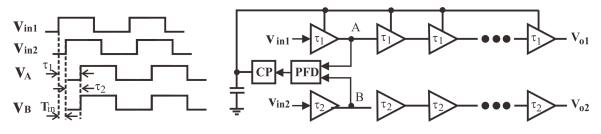

| 3.3 | DDL-based time amplifier proposed by Rashidzadeh <i>et al.</i> [4]. $\ldots$ .                                                                                                                                                                                                                                                           | 22 |

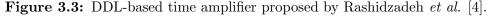

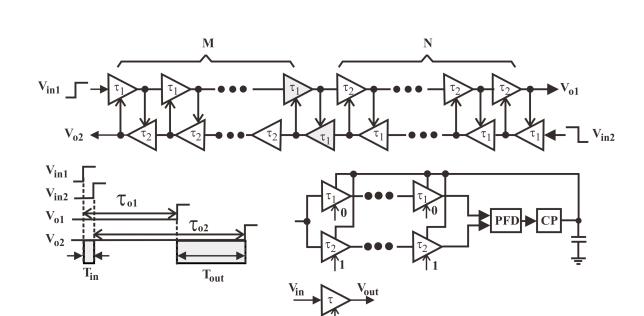

| 3.4 | Time amplifier proposed by Nakura <i>et al.</i> [5]. Top : Configuration. Bottom left : Wave forms. Bottom right : DDL to preciously control the ratio of $\tau_2$ to $\tau_1$ . The number of the delay cells in the two paths of the ratio control DDL is set such that the delay of the two delay lines is the same                   | 23 |

| 3.5 | 2x-time amplifier proposed by Lee <i>et al.</i> [6]                                                                                                                                                                                                                                                                                      | 24 |

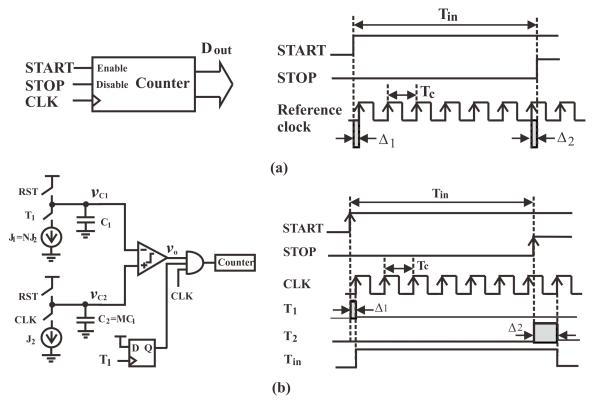

| 3.6 | (a) Direct-counter TDC. The counter starts at START=1 and stops at STOP=1. $\Delta_1$ and $\Delta_2$ are quantization errors with $\Delta_1, \Delta_2 \leq T_c$ . The input in the time domain is represented by : $T_{in} = nT_c + \Delta_1 + \Delta_2$ . (b) Direct-counter TDC with pulse stretching                                  | 27 |

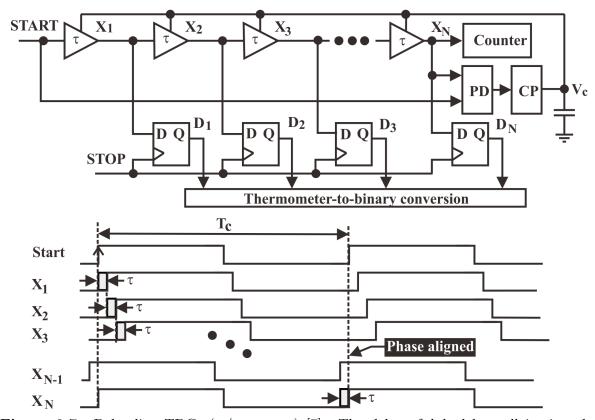

| 3.7 | Delay-line TDCs (w/o counter) [7]. The delay of kth delay cell is given by $\tau_k = \tau + \Delta \tau_k$ where $\tau$ is nominal value of the delay and $\Delta \tau_k$ is the random deviation of the delay from $\tau$ . When the counter is added, it becomes a direct-counter TDC with gate-delay interpolation [7, 8, 9, 10, 11]. | 29 |

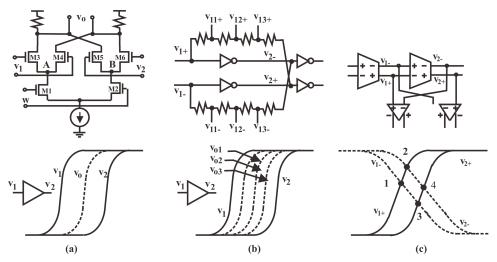

| 3.8  | (a) Interpolation using the weighted sum of the voltage of the adjacent delay stages [12]. (b) Interpolation using resistor networks [13]. (c) Interpolation using hierarchical tree [14] | 30 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

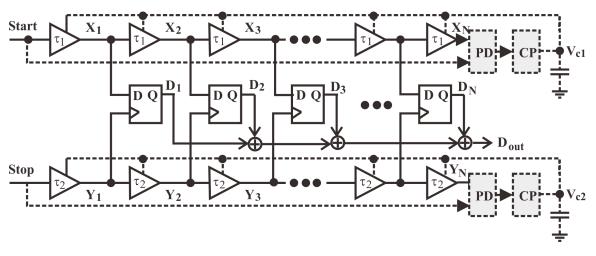

| 3.9  | Vernier delay line TDCs                                                                                                                                                                   | 31 |

| 3.10 | Cyclic Vernier delay line TDCs.                                                                                                                                                           | 32 |

| 3.11 | Pulse shrinking TDC                                                                                                                                                                       | 34 |

| 3.12 | Gated ring oscillator TDC                                                                                                                                                                 | 35 |

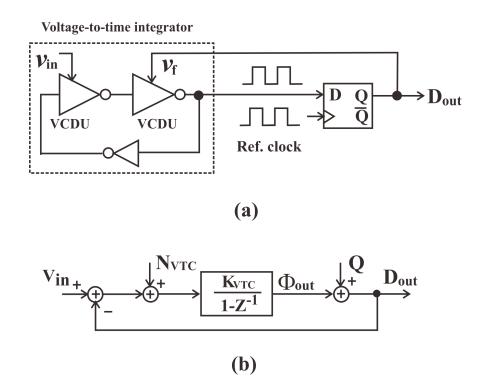

| 4.1  | Single-bit Time-Mode $\Delta\Sigma$ ADC                                                                                                                                                   | 38 |

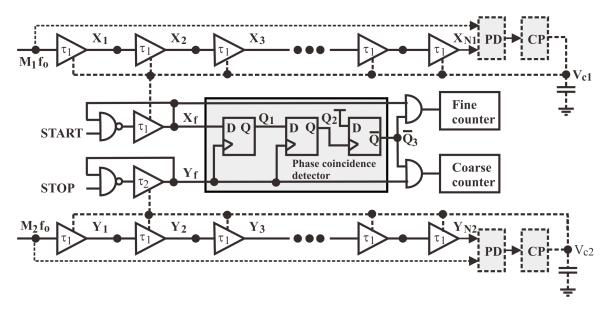

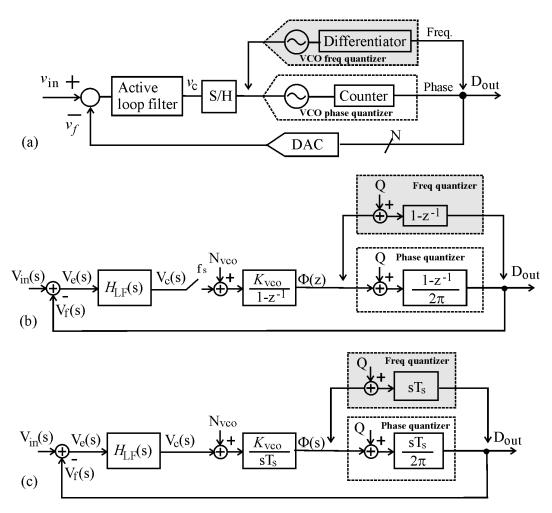

| 4.2  | Time-mode $\Delta\Sigma$ modulators with VCO phase and frequency quantizers                                                                                                               | 40 |

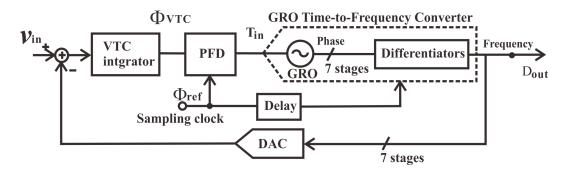

| 4.3  | $\Delta\Sigma$ ADC with phase feedback.                                                                                                                                                   | 41 |

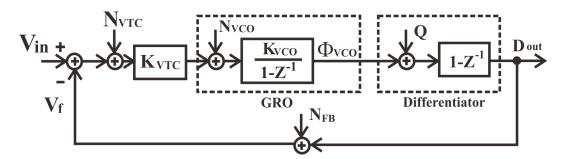

| 4.4  | System Model of the Proposed $1^{st}$ Order $\Delta\Sigma$ ADC                                                                                                                            | 43 |

| 4.5  | Frequency Domain View of the Proposed $1^{st}$ Order $\Delta\Sigma$ ADC                                                                                                                   | 44 |

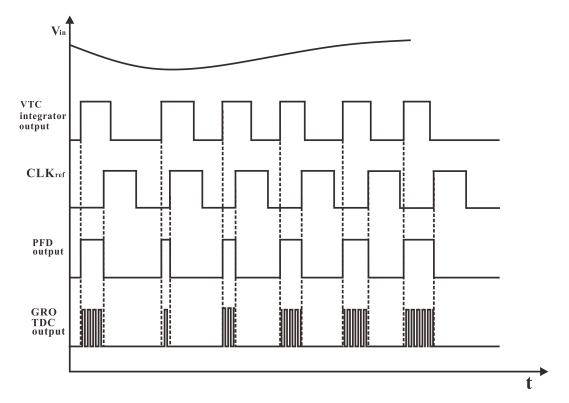

| 4.6  | Timing diagram of the critical nodes of proposed all digital time-mode $\Delta\Sigma$ ADC                                                                                                 | 45 |

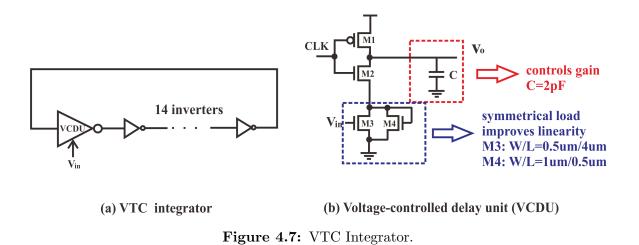

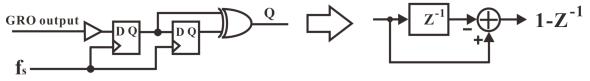

| 4.7  | VTC Integrator.                                                                                                                                                                           | 46 |

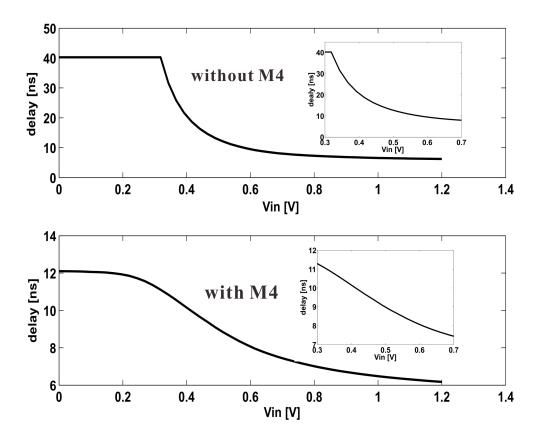

| 4.8  | Improved Linearity by Adding M4                                                                                                                                                           | 47 |

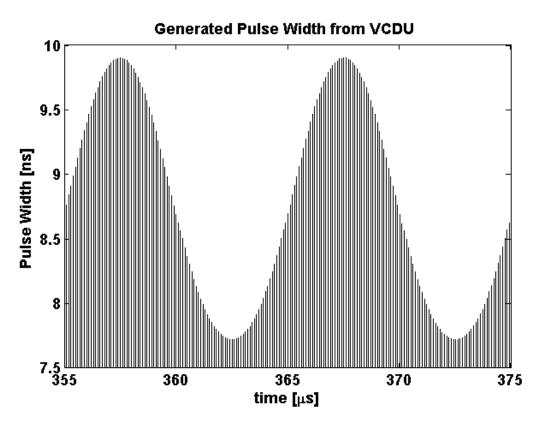

| 4.9  | Output Delay from the VCDU with a Sinusoid Input Voltage                                                                                                                                  | 48 |

| 4.10 | FFT showing harmonics of the Simulated Non-linear VCDU                                                                                                                                    | 49 |

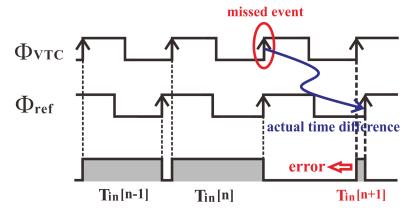

| 4.11 | Phase wrapping due to Phase Accumulation.                                                                                                                                                 | 49 |

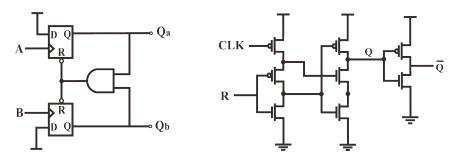

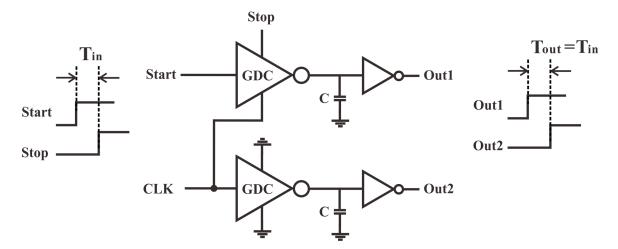

| 4.12 | Left: Schematic of DFF-based PFDs. Right : Schematic of true single phase clocked DFFs                                                                                                    | 50 |

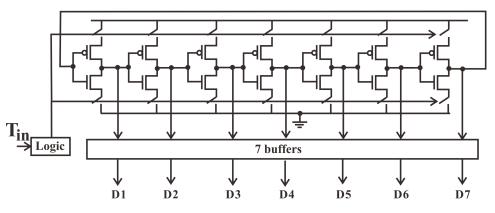

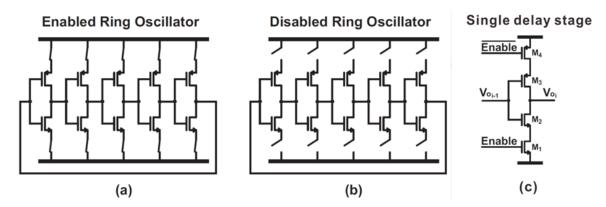

| 4.13 | A 7-Stage Gated-Ring-Oscillator.                                                                                                                                                          | 50 |

| 4.14 | GRO Implementation.                                                                                                                                                                       | 51 |

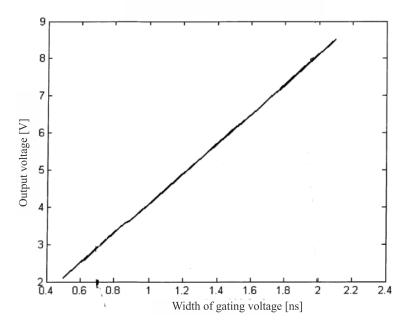

| 4.15 | Simulated GRO Characteristics by Sweeping Input Pulse Width                                                                                                                               | 51 |

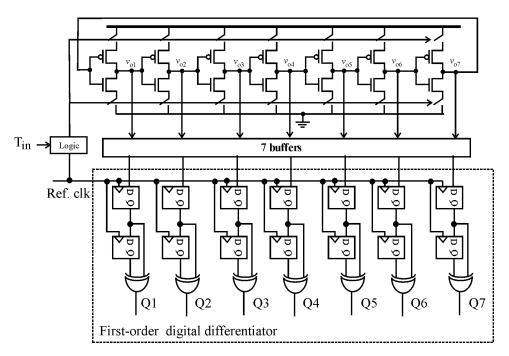

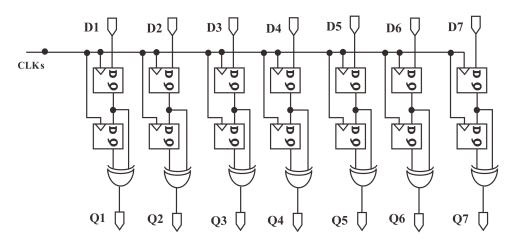

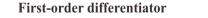

| 4.16 | Implementation of 7-Stage Digital Digital Differentiator.                                                                                                                                 | 52 |

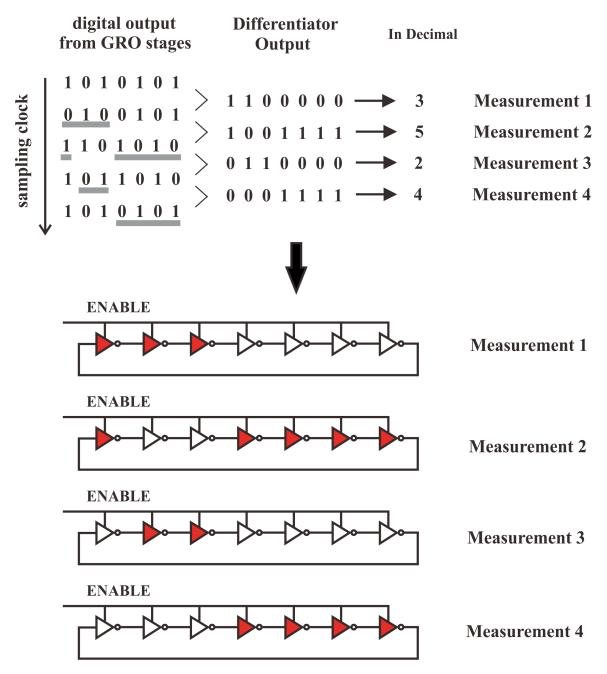

| 4.17 | Operation of Digital Differentiator.                                                                                                                                                      | 53 |

| 4.18 | Transfer Function of Digital Differentiator.                                                                 | 54 |

|------|--------------------------------------------------------------------------------------------------------------|----|

| 4.19 | VCDU with Negative Feedback.                                                                                 | 54 |

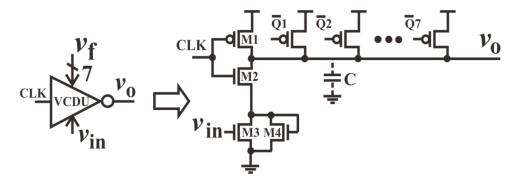

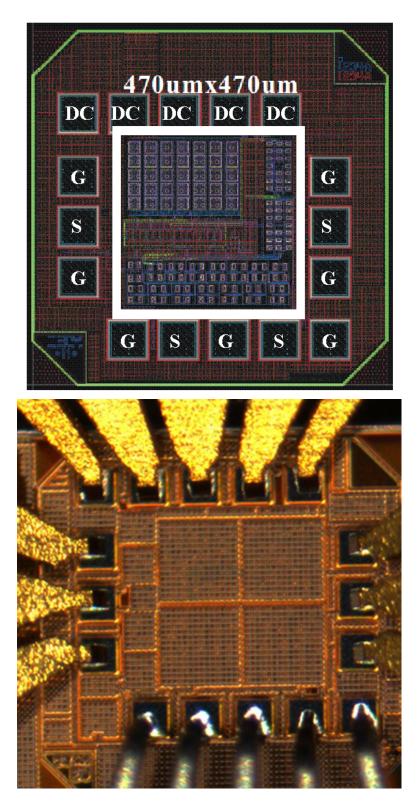

| 4.20 | Layout of proposed all-digital time-mode first-order $\Delta\Sigma$ modulator                                | 61 |

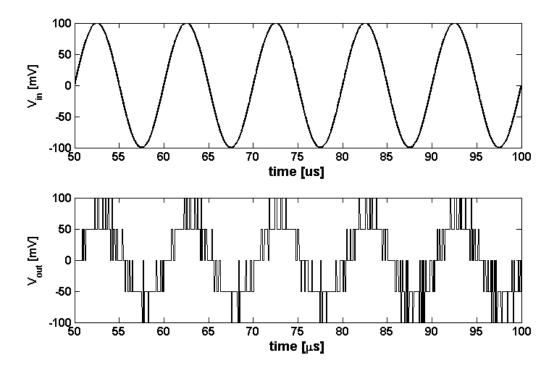

| 4.21 | Simulated Waveform of the Proposed $1^{st}$ Order $\Delta \Sigma$ ADC                                        | 62 |

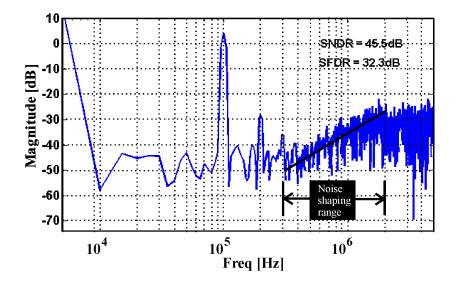

| 4.22 | FFT of the Simulated Output Waveform of the $1^{st}$ Order $\Delta\Sigma$ ADC                                | 62 |

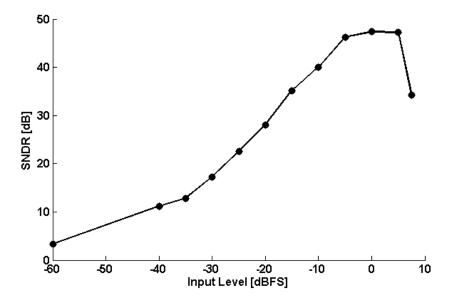

| 4.23 | Simulated dynamic range of proposed all-digital time-mode first-order $\Delta\Sigma$ ADC.                    | 63 |

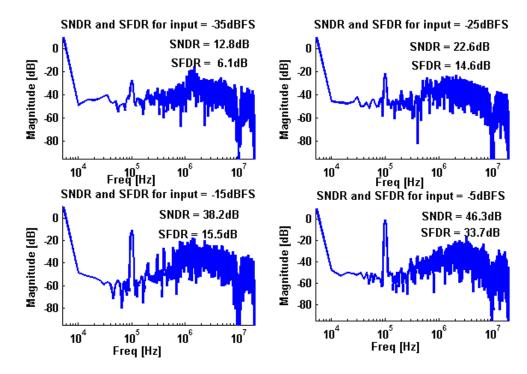

| 4.24 | Simulated spectrum of proposed all-digital time-mode first-order $\Delta\Sigma$ ADC at various input levels. | 63 |

| 4.25 | System Model of the Proposed $2^{nd}$ Order $\Delta \Sigma$ ADC                                              | 64 |

| 4.26 | Frequency Domain View of the Proposed $2^{nd}$ Order $\Delta\Sigma$ ADC                                      | 64 |

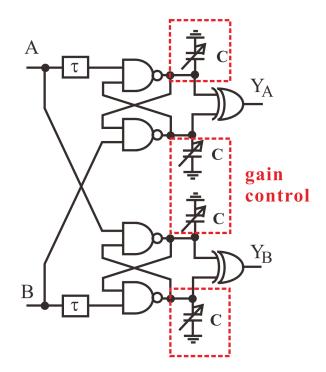

| 4.27 | Implementation of a $2^{nd}$ Order Digital Differentiators                                                   | 64 |

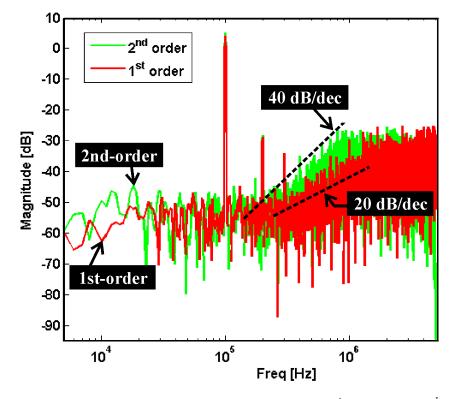

| 4.28 | FFT of the Output Waveform for the Proposed $2^{nd}$ Order $\Delta\Sigma$ ADC                                | 65 |

| 4.29 | Comparison between the Proposed $1^{st}$ Order and $2^{nd}$ Order $\Delta\Sigma$ ADC                         | 65 |

| 4.30 | MULTEX Circuit for a Regenerative Time Amplifier.                                                            | 66 |

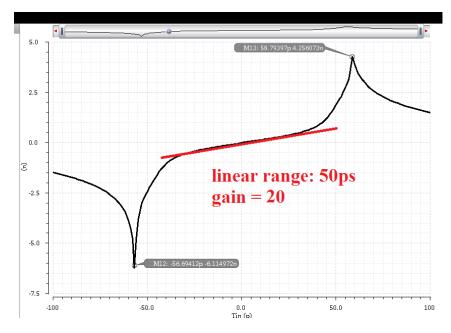

| 4.31 | Time Amplifier Linear Range and Gain.                                                                        | 66 |

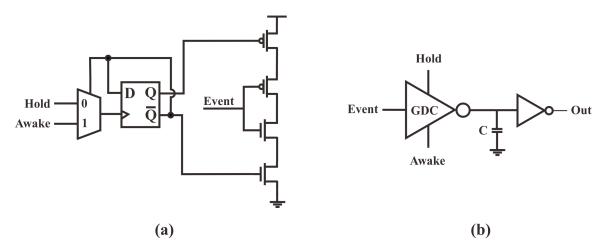

| 4.32 | Implementation of a Gated Delay Cell                                                                         | 67 |

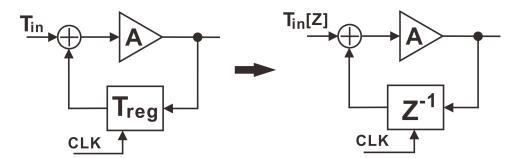

| 4.33 | Implementation of a Time Register                                                                            | 67 |

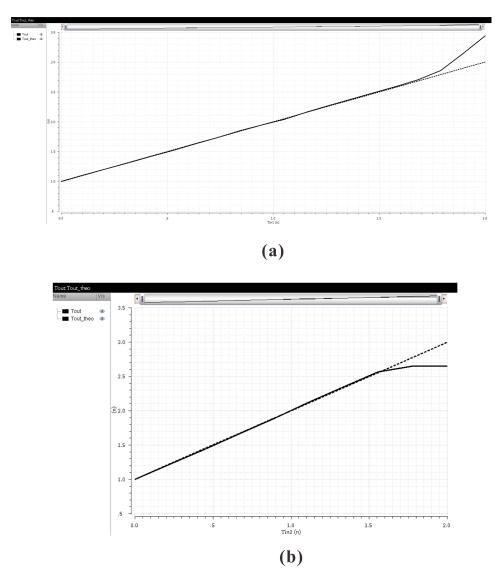

| 4.34 | Performance of the Simulated Time Register                                                                   | 67 |

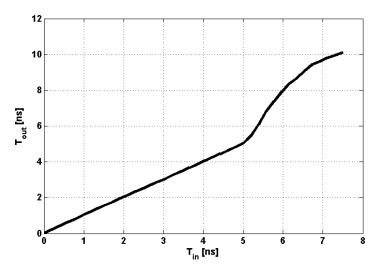

| 4.35 | Using an Time Subtracter as an Adder                                                                         | 68 |

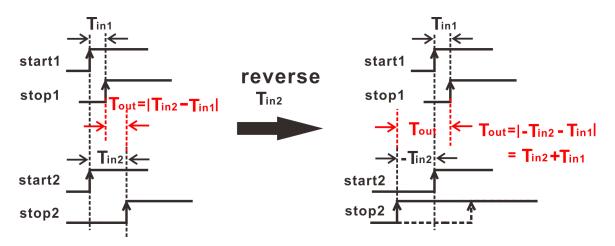

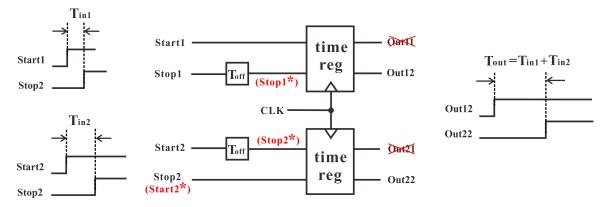

| 4.36 | Using an Time Subtracter as an Adder by Adding $T_{off}$ and Switching the inputs of $T_{in2}$ .             | 68 |

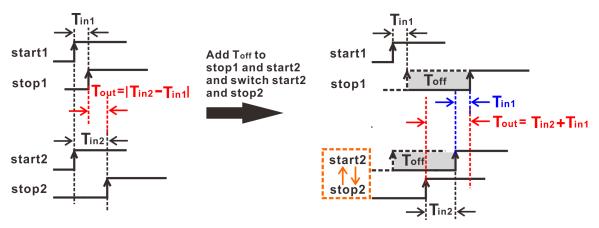

| 4.37 | Implementation Details of the Time Adder                                                                     | 69 |

| 4.38 | Implementation Details of the Time Adder                                                                     | 70 |

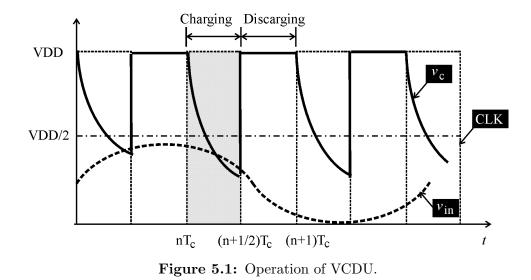

| 5.1  | Operation of VCDU.                                                                                           | 73 |

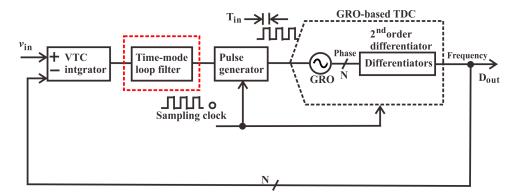

| 6.1  | System Model of a $3^{rd}$ Order Time-Mode $\Delta\Sigma$ ADC                                                | 75 |

# List of Abbreviations

| ADC  | Analog-to-Digital Converter           |

|------|---------------------------------------|

| BW   | Bandwidth                             |

| CMOS | Complementary MetalOxideSemiconductor |

| CP   | Charge Pump                           |

| DAC  | Digital-to-Analog Converter           |

| DEM  | Dynamic Element Matching              |

| DLL  | Delay-Locked-Loop                     |

| FFT  | Fast Fourier Transform                |

| FO4  | Fan-out of 4                          |

| GDC  | Gated Delay Cell                      |

| GRO  | Gated Ring Oscillotor                 |

| GSM  | Global System for Mobile              |

| LSB  | Least Significant Bit                 |

| MASH | Multi-stage Noise Shaping             |

| OSR  | Over Sampling Ratio                   |

| PD   | Phase Detector                        |

| PFD  | Phase Frequency Detector              |

| PLL  | Phase-Locked Loop                     |

| PSD  | Power Spectral Density               |

|------|--------------------------------------|

| PVT  | Process (supply-)Voltage Temperature |

| PWM  | Pulse Width Modulation               |

| SAR  | (Successive Approximation Register   |

| S/H  | Sample-and-Hold                      |

| SNDR | Signal-to-Noise-and-Distortion Ratio |

| SNR  | Signal-to-Noise Ratio                |

| SQNR | Signal-to-Quantization-Noise Ratio   |

| TDC  | Time-to-Digital Converter            |

| VCO  | Voltage-Controlled Oscillator        |

| VTC  | Voltage-to-Time Converter            |

| XOR  | Exclusive OR                         |

## Chapter 1

## Introduction

This chapter explains the motivation of this dissertation by introducing a circuit topology, known as time-mode circuits, for signal processing. Time-mode circuits where information is represented by the time difference variables possess a number of intrinsic characteristics that are scaled well with technology, making them a viable option to implement some key building blocks of mixed-signal systems such as analog-to-digital converters and phase-locked loops for signal processing.

### 1.1 Motivation

The rapid advance of CMOS technologies has primarily been geared towards optimizing the performance of digital systems. It is evident in Fig.1.1 Left that the power supply  $V_{DD}$  of CMOS circuit has dramatically dropped while the threshold voltage  $V_{TH}$  has very slow decline with technology scaling over the past years. Consequently, analog circuits are not only losing the benefit of process-controlled components, but they also must cope with rapidly voltage headroom loss. In addition to deteriorating signal-to-noise ratio, the shrinking voltage headroom also signifies the effect of the nonlinear characteristics of MOS transistors, while meeting ever-demanding performance specifications [15, 16, 17]. Although current-mode approaches offer an alternative means to combat voltage headroom loss, the existence of low-impedance nodes throughout current-mode circuits gives rise to high power consumption [18]. The improved switching characteristics of MOS transistors from technology scaling offer a superior timing accuracy quantified by the ratio of FO4 to the period of analog signals that has well surpassed the voltage resolution of analog circuits. As a result, a new design

paradigm where information is represented by the time difference of Boolean signals rather than the nodal voltages or branch currents of electric networks offers a new means to combat the scaling-induced design challenges that were once seemed unconquerable.

**Figure 1.1:** Left: Power Supply and Threshold Voltage Scaling in CMOS Technology. Right: Improvement in Delay for an FO4 Inverter due to Scaling

### 1.2 Overview of Time-Mode Signal Processing

Unlike voltage-mode or current-mode circuits, time-mode circuits depict an analog signal using the time difference between the rising edges of two digital signals with the time difference directly proportional to the amplitude of the analog signal. Because time-mode circuits perform analog signal processing in the digital domain, not only their performance scales well with technology, these circuits also offer a superior speed with low power consumption, enabling them to process high-frequency signals without sacrificing power consumption. Since the inception of time-mode signal processing, an immense effort has been made on researching for design techniques and exploring applications of time-mode circuits. Time-mode analog-to-digital converters with resolution up to 12.5 bits, bandwidth up to 20 MHz, signal-to-noise ratio (SNR) over 80 dB, and signal-to-noise-pulse-distortion-ratio (SNDR) over 70 dB have been reported [1, 19, 20]. Time-mode circuits have also been used in audio [21], medical imaging [22], instrumentations [23], infinite-impulse-response (IIR) filters [24], finite-impulse-response (FIR) filters [25], and anti-imaging filters [26], frequency synthesizers [27, 28], delay-locked loops (DLL) [29], multi-Gbps serial links [30], and programmable band/channel select filters for software-defined radio [31], to name a few. In spite of these development, there are very few literatures that offer a comprehensive treament of the principle and design techniew of CMOS time-mode circuits for mixed-signal processing. Therefore a comprehensive treatment of time-mode circuits with an emphasis on both the principle and design techniques of the building blocks is provided in the next few chapters as part of this dissertation.

#### **1.3** Current Literatures on Time-Mode ADC

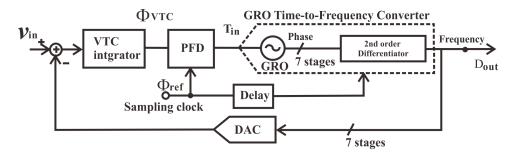

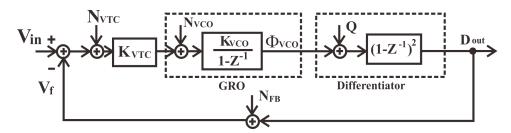

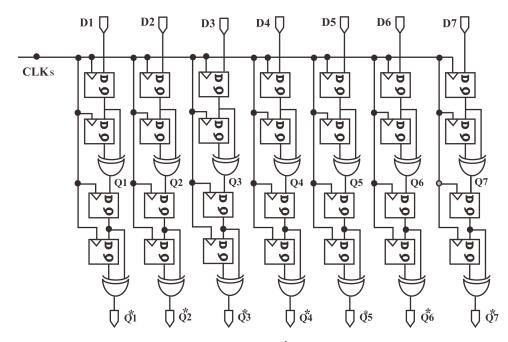

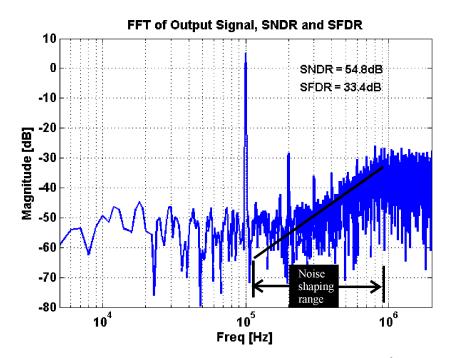

Time-mode approaches of signal precessing represent analog signals as timing information of digital signals. They benefit from technology scaling and compensate deteriorated voltage accuracy in voltage-mode approaches. Therefore they offer a technology-friendly alternative means for data conversion [15, 17]. Li *et al.* showed that time-mode data conversion can be achieved by converting input voltage into time variables using a voltage-to-time converter (VTC) and then quantizing the time variable using a time-to-digital converter (TDC)[32]. Itawa et al. demonstrated a time-mode ADC implemented using a multi-stage ring VCO in conjuction with a reset counter[33]. The VCO-based ADC in Itawa's design allows the voltage-to-time conversion to operate in continuous time domain. In addition, this VCObased ADC possesses inherent first-order noise-shaping. However, the conversion speed and samping rate is limited by the reset time of the counter. Hence the reset counter is undesired especially in  $\Delta\Sigma$ ADCs which require high OSR to achieve better SNDR. Hovin *et al.* replaced the reset counters with digital differentiators to achieve the same first-order noise-shaping [34, 35]. This type of VCO-based time-mode ADC offers the key advantage of high speed due to the absence of counters and an improved resolution, thereby permitting a large OSR. Straaver et al. showed that gated ring oscillator-based TDC also possess the desired firstorder noise-shaping characteristics [19].